Similar presentations:

LMK04832 vs LMK0482x Comparison Analysis

1. LMK04832 vs LMK0482x Comparison Analysis

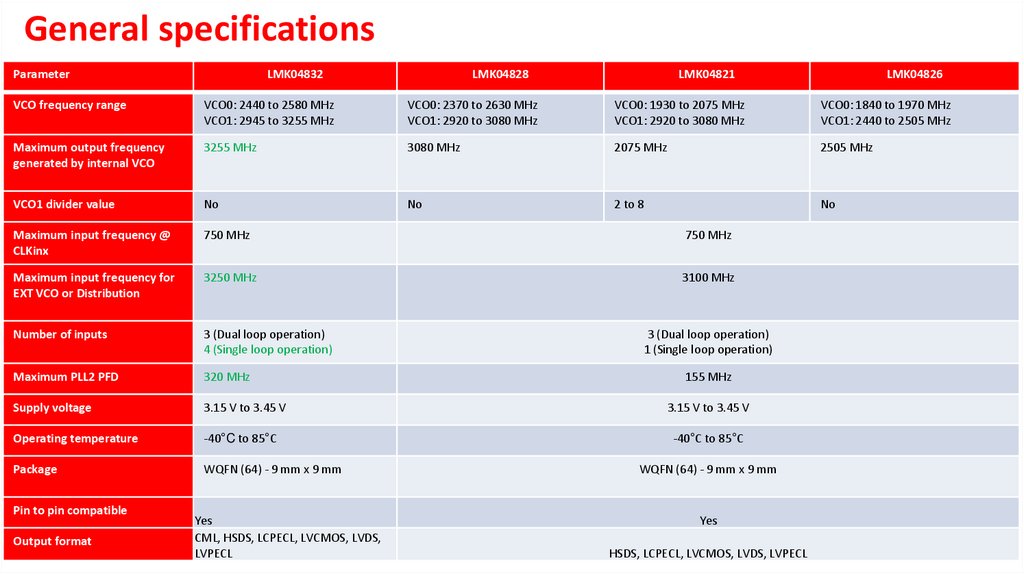

2. General specifications

ParameterLMK04832

LMK04828

LMK04821

LMK04826

VCO frequency range

VCO0: 2440 to 2580 MHz

VCO1: 2945 to 3255 MHz

VCO0: 2370 to 2630 MHz

VCO1: 2920 to 3080 MHz

VCO0: 1930 to 2075 MHz

VCO1: 2920 to 3080 MHz

VCO0: 1840 to 1970 MHz

VCO1: 2440 to 2505 MHz

Maximum output frequency

generated by internal VCO

3255 MHz

3080 MHz

2075 MHz

2505 MHz

VCO1 divider value

No

No

2 to 8

No

Maximum input frequency @

CLKinx

750 MHz

750 MHz

Maximum input frequency for

EXT VCO or Distribution

3250 MHz

3100 MHz

Number of inputs

3 (Dual loop operation)

4 (Single loop operation)

Maximum PLL2 PFD

320 MHz

Supply voltage

3.15 V to 3.45 V

3.15 V to 3.45 V

Operating temperature

-40°C to 85°C

-40°C to 85°C

Package

WQFN (64) - 9 mm x 9 mm

Pin to pin compatible

Output format

Yes

CML, HSDS, LCPECL, LVCMOS, LVDS,

LVPECL

3 (Dual loop operation)

1 (Single loop operation)

155 MHz

WQFN (64) - 9 mm x 9 mm

Yes

HSDS, LCPECL, LVCMOS, LVDS, LVPECL

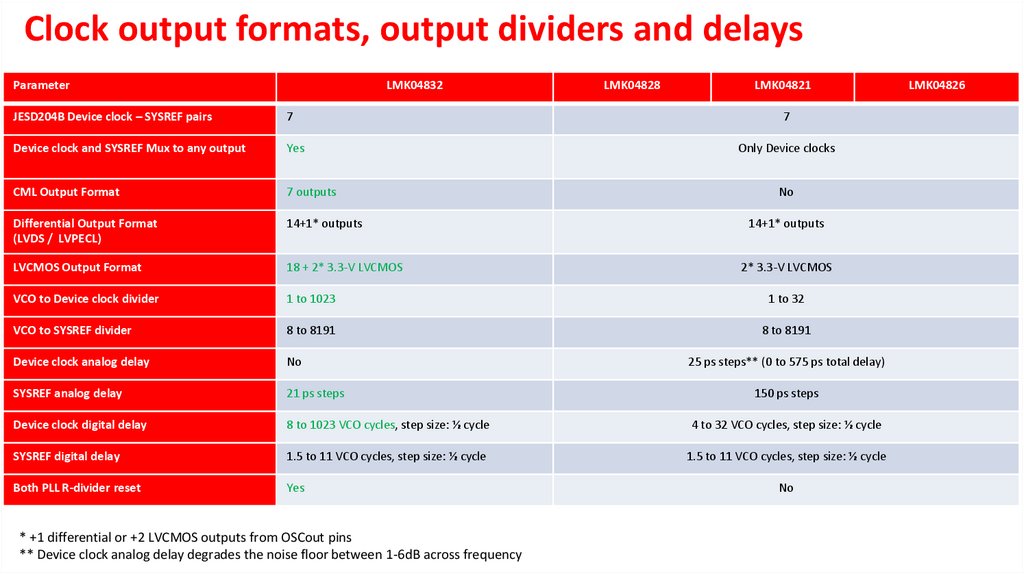

3. Clock output formats, output dividers and delays

ParameterLMK04832

LMK04828

LMK04821

JESD204B Device clock – SYSREF pairs

7

7

Device clock and SYSREF Mux to any output

Yes

Only Device clocks

CML Output Format

7 outputs

Differential Output Format

(LVDS / LVPECL)

14+1* outputs

14+1* outputs

LVCMOS Output Format

18 + 2* 3.3-V LVCMOS

2* 3.3-V LVCMOS

VCO to Device clock divider

1 to 1023

1 to 32

VCO to SYSREF divider

8 to 8191

8 to 8191

Device clock analog delay

No

SYSREF analog delay

21 ps steps

Device clock digital delay

8 to 1023 VCO cycles, step size: ½ cycle

4 to 32 VCO cycles, step size: ½ cycle

SYSREF digital delay

1.5 to 11 VCO cycles, step size: ½ cycle

1.5 to 11 VCO cycles, step size: ½ cycle

Both PLL R-divider reset

Yes

* +1 differential or +2 LVCMOS outputs from OSCout pins

** Device clock analog delay degrades the noise floor between 1-6dB across frequency

No

25 ps steps** (0 to 575 ps total delay)

150 ps steps

No

LMK04826

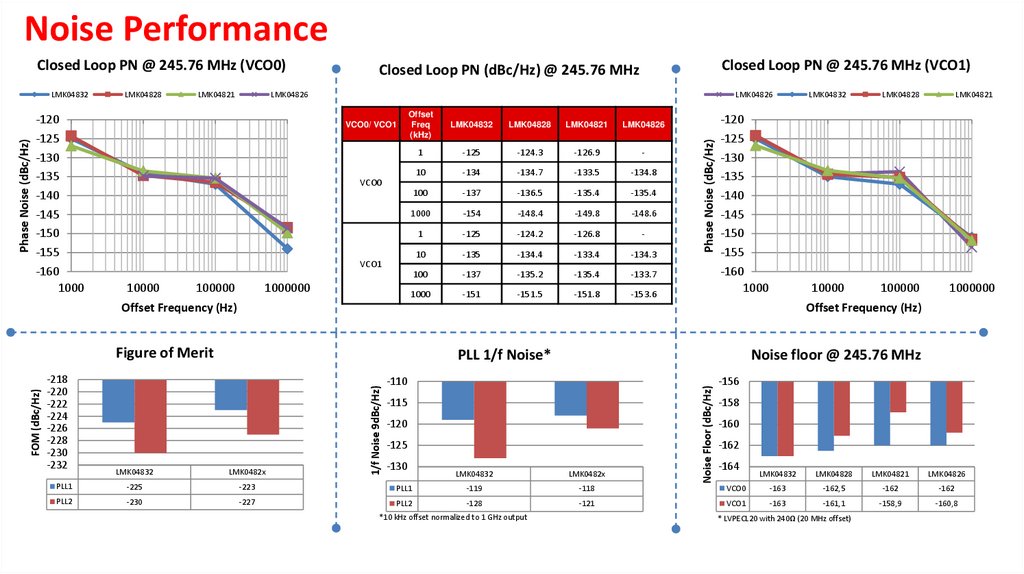

4. Noise Performance

Closed Loop PN @ 245.76 MHz (VCO0)-120

-125

-130

-135

-140

-145

-150

-155

-160

1000

LMK04828

LMK04821

LMK04826

LMK04826

VCO0/ VCO1

Offset

Freq

(kHz)

LMK04832

LMK04828

LMK04821

LMK04826

1

-125

-124.3

-126.9

-

10

-134

-134.7

-133.5

-134.8

100

-137

-136.5

-135.4

-135.4

1000

-154

-148.4

-149.8

-148.6

1

-125

-124.2

-126.8

-

VCO0

10

-135

-134.4

-133.4

-134.3

100

-137

-135.2

-135.4

-133.7

1000

-151

-151.5

-151.8

-153.6

VCO1

10000

100000

1000000

Phase Noise (dBc/Hz)

Phase Noise (dBc/Hz)

LMK04832

Closed Loop PN @ 245.76 MHz (VCO1)

Closed Loop PN (dBc/Hz) @ 245.76 MHz

-120

-125

-130

-135

-140

-145

-150

-155

-160

1000

Offset Frequency (Hz)

LMK04821

10000

100000

1000000

LMK04832

LMK0482x

PLL1

-225

-223

PLL2

-230

-227

Noise floor @ 245.76 MHz

-110

-115

-120

-125

-130

Noise Floor (dBc/Hz)

PLL 1/f Noise*

1/f Noise 9dBc/Hz)

FOM (dBc/Hz)

LMK04828

Offset Frequency (Hz)

Figure of Merit

-218

-220

-222

-224

-226

-228

-230

-232

LMK04832

-156

-158

-160

-162

-164

LMK04832

LMK0482x

LMK04832

LMK04828

LMK04821

PLL1

-119

-118

VCO0

-163

-162,5

-162

-162

PLL2

-128

-121

VCO1

-163

-161,1

-158,9

-160,8

*10 kHz offset normalized to 1 GHz output

* LVPECL20 with 240Ω (20 MHz offset)

LMK04826

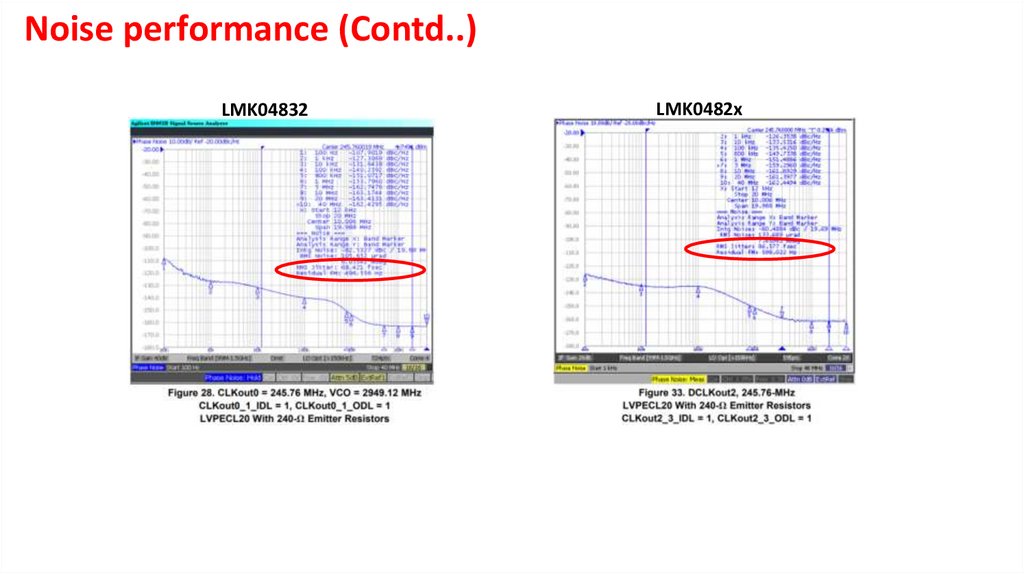

5. Noise performance (Contd..)

LMK04832LMK0482x

electronics

electronics