Similar presentations:

Микропроцессорные системы

1.

Микропроцессорныесистемы

2.

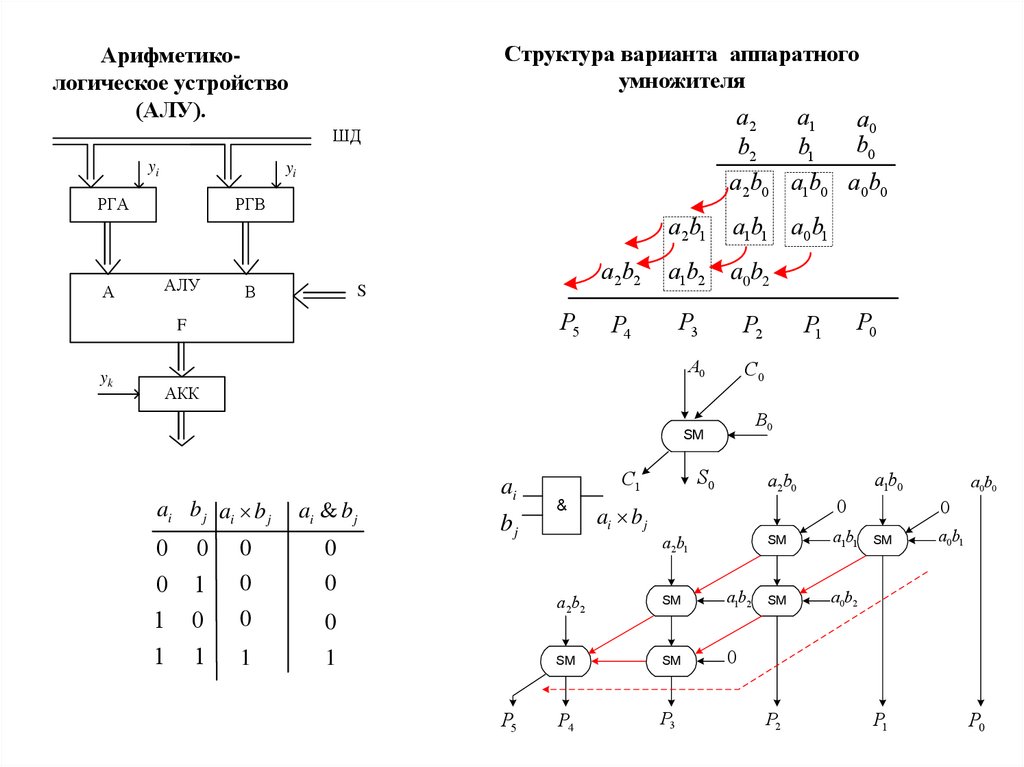

Структура варианта аппаратногоумножителя

Арифметикологическое устройство

(АЛУ).

a2

a1

a0

b0

b2

b1

a2b0 a1b0 a0b0

ШД

yi

yi

РГА

А

РГВ

АЛУ

В

S

P5

F

yk

a2b1

a1b1 a0b1

a2b2

a1b2

a0b2

P4

P3

P2

A0

P0

P1

C0

АКК

B0

SM

ai b j ai b j

ai b j

0

0

0

0

0

1

0

0

1

0

0

0

1

1

1

1

ai

bj

P5

S0

C1

&

a1b0

a2b0

0

ai b j

a2b1

a2b2

SM

a1b2

SM

SM

0

P4

P3

SM

a1b1

SM

a0b2

P2

a0b0

0

SM

P1

a0b1

P0

3.

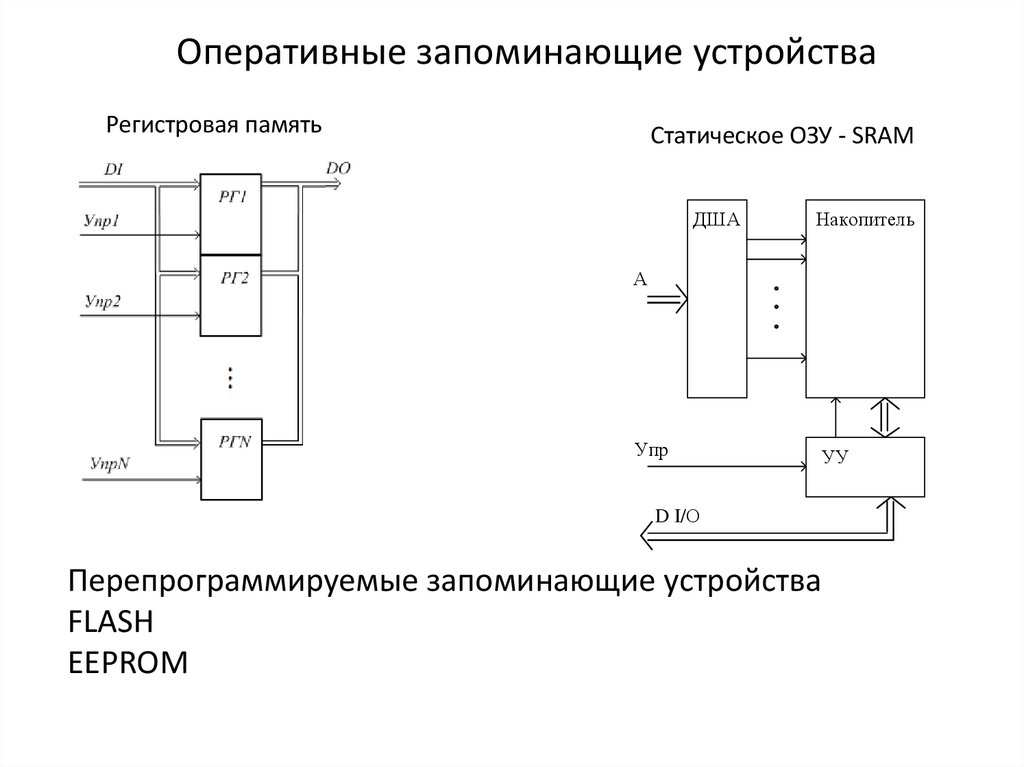

Оперативные запоминающие устройстваРегистровая память

Статическое ОЗУ - SRAM

ДША

Накопитель

А

Упр

УУ

D I/О

Перепрограммируемые запоминающие устройства

FLASH

EEPROM

4.

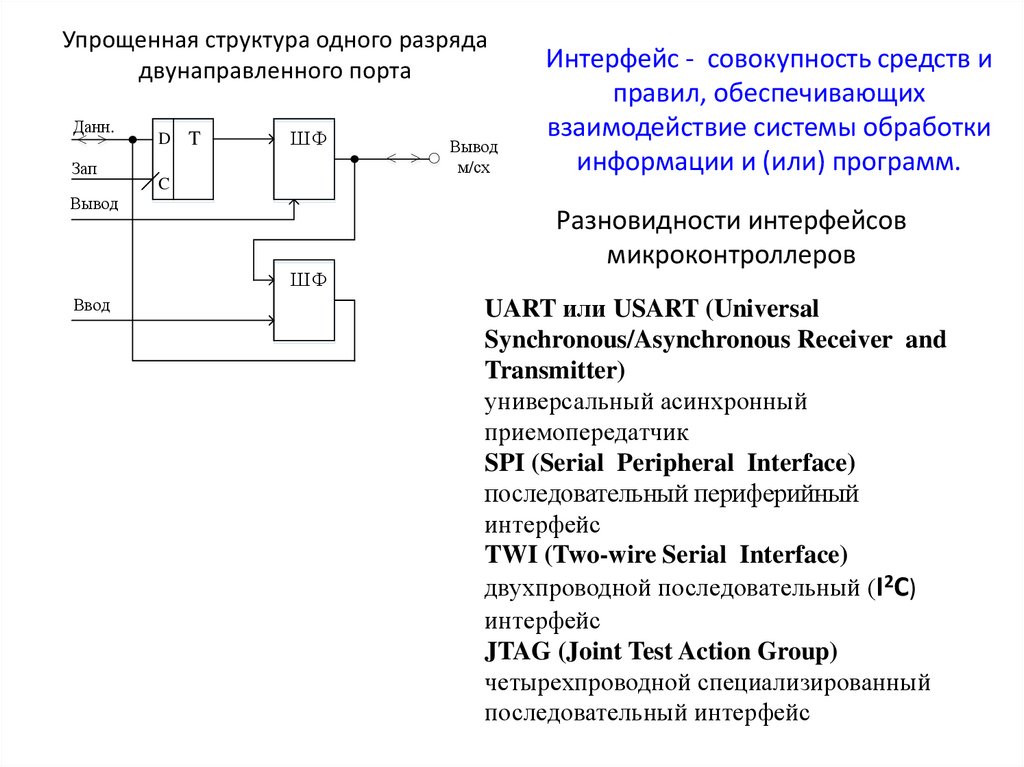

Упрощенная структура одного разрядадвунаправленного порта

Данн.

Зап

D

T

ШФ

C

Вывод

ШФ

Ввод

Вывод

м/сх

Интерфейс - совокупность средств и

правил, обеспечивающих

взаимодействие системы обработки

информации и (или) программ.

Разновидности интерфейсов

микроконтроллеров

UART или USART (Universal

Synchronous/Asynchronous Receiver and

Transmitter)

универсальный асинхронный

приемопередатчик

SPI (Serial Peripheral Interface)

последовательный периферийный

интерфейс

TWI (Two-wire Serial Interface)

двухпроводной последовательный (I2C)

интерфейс

JTAG (Joint Test Action Group)

четырехпроводной специализированный

последовательный интерфейс

5.

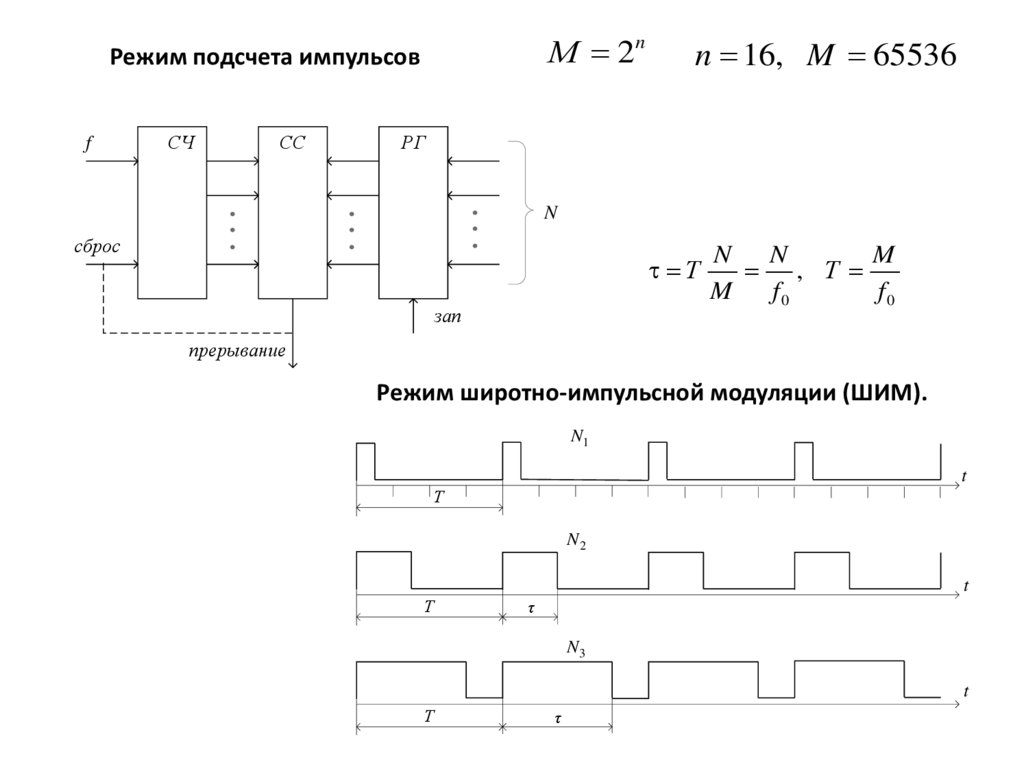

М 2nРежим подсчета импульсов

f

СЧ

СС

n 16, M 65536

РГ

N

сброс

Т

зап

N

N

M

, T

M

f0

f0

прерывание

Режим широтно-импульсной модуляции (ШИМ).

N1

t

Т

N2

t

Т

τ

N3

t

Т

τ

6.

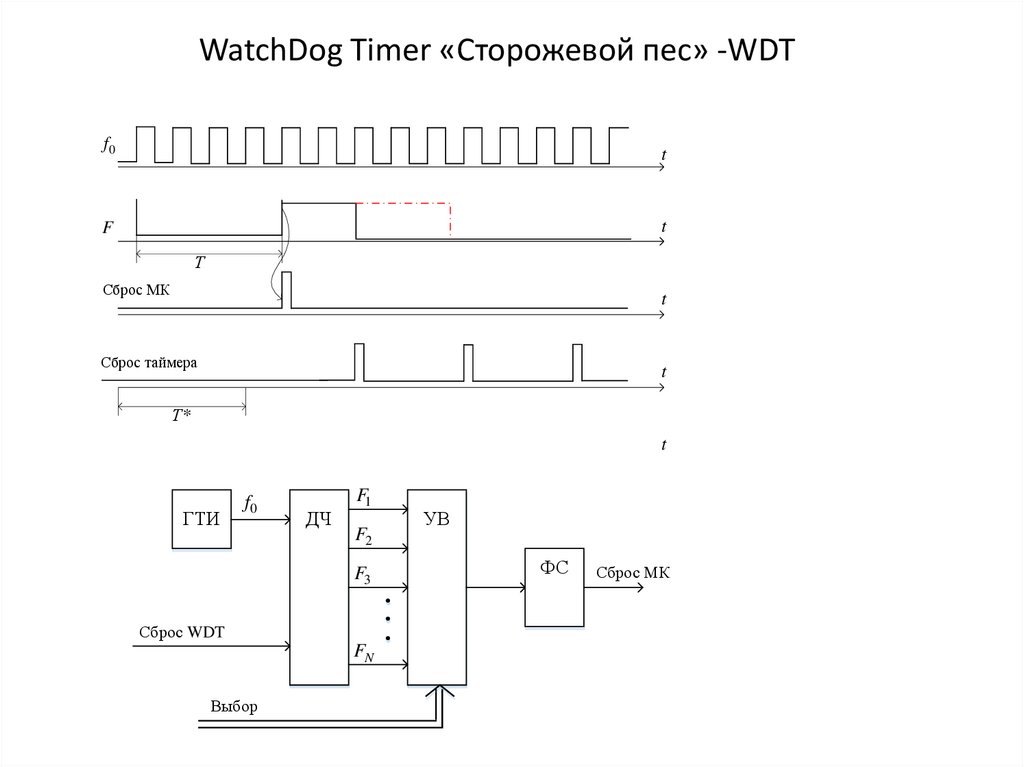

WatchDog Timer «Сторожевой пес» -WDTf0

t

F

t

Т

Сброс МК

t

Сброс таймера

t

Т*

t

ГТИ

f0

ДЧ

F1

F2

F3

Сброс WDT

FN

Выбор

УВ

ФС

Сброс МК

7.

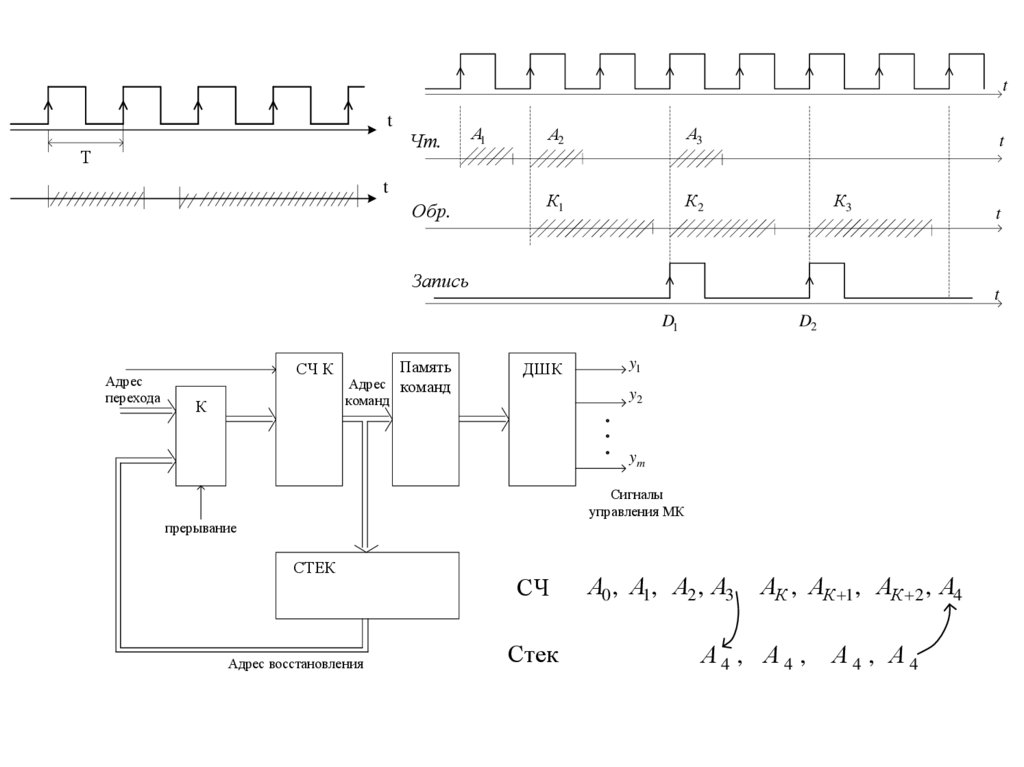

tt

Чт.

Т

t

Обр.

А1

А2

А3

К1

К2

t

К3

Запись

t

D2

D1

Адрес

перехода

СЧ К

Память

Адрес команд

ДШК

y1

y2

команд

К

ym

Сигналы

управления МК

прерывание

СТЕК

Адрес восстановления

t

СЧ

Стек

А0 , А1, А2 , А3

АК , АК 1, АК 2 , А4

А4 , А4 ,

А4 , А4

electronics

electronics