Similar presentations:

Микропроцессорные системы

1.

Общие принципы построения микропроцессорных систем2.

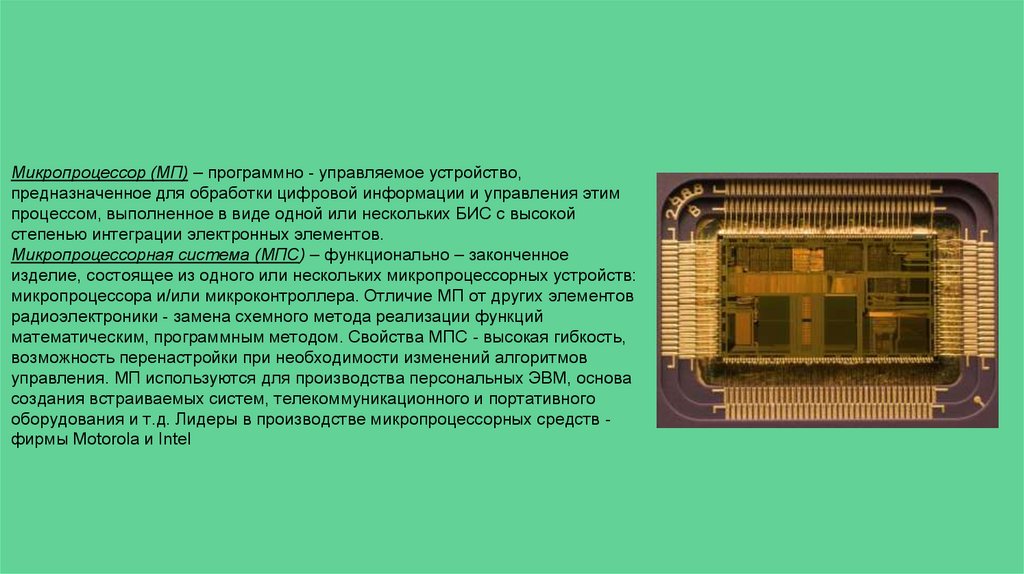

Микропроцессор (МП) – программно - управляемое устройство,предназначенное для обработки цифровой информации и управления этим

процессом, выполненное в виде одной или нескольких БИС с высокой

степенью интеграции электронных элементов.

Микропроцессорная система (МПС) – функционально – законченное

изделие, состоящее из одного или нескольких микропроцессорных устройств:

микропроцессора и/или микроконтроллера. Отличие МП от других элементов

радиоэлектроники - замена схемного метода реализации функций

математическим, программным методом. Свойства МПС - высокая гибкость,

возможность перенастройки при необходимости изменений алгоритмов

управления. МП используются для производства персональных ЭВМ, основа

создания встраиваемых систем, телекоммуникационного и портативного

оборудования и т.д. Лидеры в производстве микропроцессорных средств фирмы Motorola и Intel

3.

В основу построения МПС положено три принципа.1. Принцип модульности - система строится на основе ограниченного

количества типов конструктивно и функционально законченных модулей.

Модульный подход способствует стандартизации элементов, приводит к

сокращению затрат на проектирование систем, упрощает изменение

конфигурации системы.

2. Принцип магистральности определяет характер связей между блоками

МПС – все блоки соединяются с единой системной шиной. Выделяют два

способа: с помощью произвольных связей и упорядоченных связей

(магистральный способ). Последний позволяет минимизировать количество

связей между блоками, повысить регулярность операционного устройства и

УУ, обеспечить стандартизацию интерфейсов, сократить число выводов БИС.

Принцип регулярности предполагает повторяемость элементов структуры и

связей между ними.

3. Принцип микропрограммного управления состоит в возможности

осуществления микрокоманд (сдвигов, пересылок информации, логических

операций). Микропрограммное управление за счет возможности смены

микропрограмм повышает гибкость устройства, за счет распределенности

памяти обеспечивает параллельное решение задач, за счет применения

освоенных БИС повышает надежность системы, за счет регулярности

структуры упрощает контроль функционирования устройства.

4.

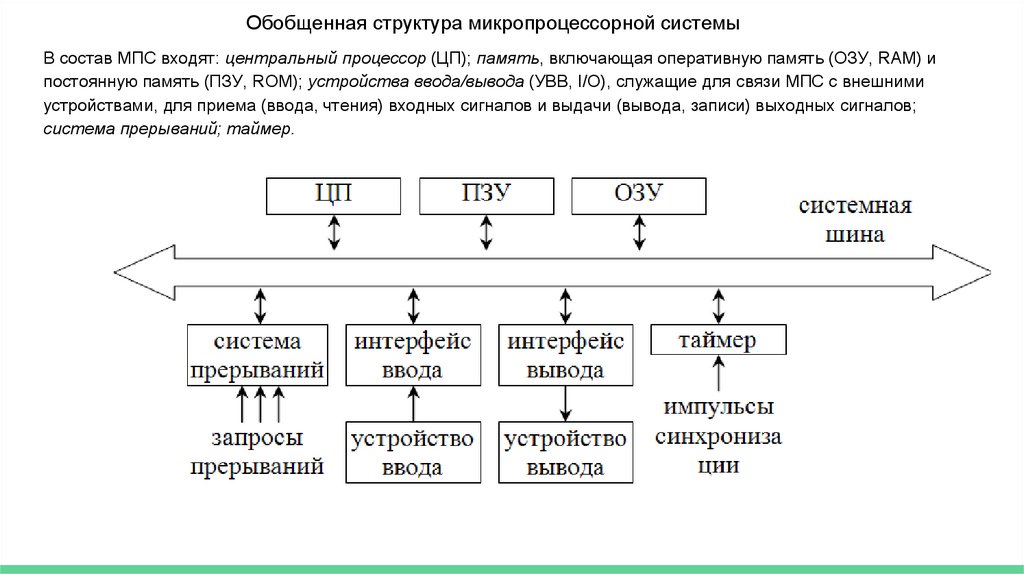

Обобщенная структура микропроцессорной системыВ состав МПС входят: центральный процессор (ЦП); память, включающая оперативную память (ОЗУ, RAM) и

постоянную память (ПЗУ, ROM); устройства ввода/вывода (УВВ, I/O), служащие для связи МПС с внешними

устройствами, для приема (ввода, чтения) входных сигналов и выдачи (вывода, записи) выходных сигналов;

система прерываний; таймер.

5.

Модуль ЦП осуществляет обработку данных и управляет модулями системы. Основные узлы БИС МП: устройствоуправления (УУ) с регистром команд (РгК) и дешифратором команд (ДШК); АЛУ; аккумулятор (А) - основной рабочий

регистр; регистры общего назначения (РОН) со счетчиком команд (СК). Центральный процессор, кроме БИС МП,

содержит схемы синхронизации и интерфейса с системной шиной, осуществляет выборку кодов команд из памяти,

дешифрует их и выполняет. Устройства ввода/вывода предназначены для ввода информации в МП или вывода

информации (дисплеи, печатающие устройства, клавиатура, ЦАП и АЦП). Интерфейсы ввода/вывода - совокупность

шин для передачи информации. Блок ИФ служит для сопряжения МПС и ВУ по электрическим и временным

параметрам. Система прерываний позволяет МПС реагировать на внешние сигналы – запросы прерываний,

источниками которых могут быть: сигналы готовности от ВУ. При появлении запроса на прерывание ЦП прекращает

выполнение основной программы и переходит к выполнению подпрограммы обслуживания запроса прерывания. Для

построения системы прерываний МПК содержат БИС специальных программируемых контроллеров прерываний.

Таймер предназначен для реализации функций, связанных с отсчетом времени. После того как МП загружает в таймер

число, задающее частоту, задержку или коэффициент деления, таймер реализует необходимую функцию.

Модуль ЦП

6.

Архитектурные особенности и функциональные возможности 16-разрядныхмикропроцессоров.

К 16-разрядным МП первого поколения принадлежат МП i8086/i8088 и i80186/i80188, к МП второго поколения - i80286.

Микропроцессор выполняет операции над 8- и 16-разрядными данными, представленными в двоичном или двоично-десятичном

виде, может обрабатывать отдельные биты, а также строки или массивы данных. Имеет встроенные аппаратные средства

умножения и деления. МП имеет внутреннее сверхоперативное запоминающее устройство (СОЗУ) емкостью 14x16 байт. Шина

адреса является 20-разрядной, что позволяет адресовать 220= 1 048 576 ячеек памяти (1 Мбайт).

Пространство адресов ввода/вывода составляет 64 Кбайт. В БИС i8086 реализована многоуровневая векторная система

прерываний с количеством векторов до 256. Предусмотрена также организация прямого доступа к памяти, по которому МП

прекращает работу и переводит шины адреса, данных и управления в высокоимпедансное состояние.

+

Среднее время выполнения команды занимает 12 тактов. Особенностью МП i8086 является возможность частичной

реконфигурации аппаратной части для обеспечения работы в двух режимах - минимальном и максимальном. Режимы работы

задаются аппаратно. В минимальном режиме, используемом для построения однопроцессорных систем, МП самостоятельно

формирует все сигналы управления внутренним системным интерфейсом. В максимальном режиме, используемом для

построения мультипроцессорных систем, МП формирует на линиях состояния двоичный код, который зависит от типа цикла шины.

В соответствии с этим кодом системный контроллер К1810ВГ88 формирует сигналы управления шиной. Контакты, которые

освободились в результате кодирования информации, используются для управления мультипроцессорным режимом. При

использовании арифметического сопроцессора необходимо выбирать максимальный режим.

7.

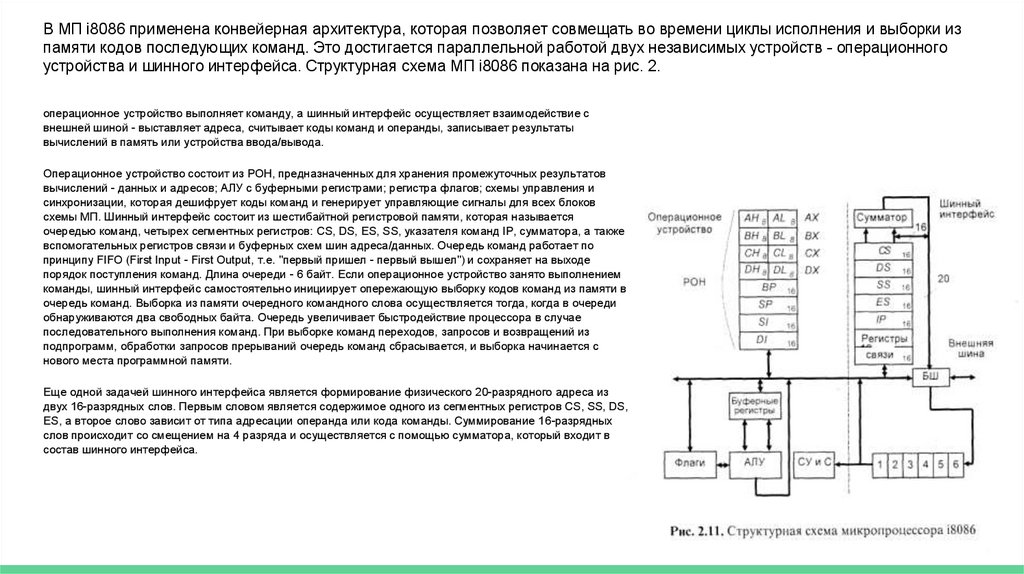

В МП i8086 применена конвейерная архитектура, которая позволяет совмещать во времени циклы исполнения и выборки изпамяти кодов последующих команд. Это достигается параллельной работой двух независимых устройств - операционного

устройства и шинного интерфейса. Структурная схема МП i8086 показана на рис. 2.

операционное устройство выполняет команду, а шинный интерфейс осуществляет взаимодействие с

внешней шиной - выставляет адреса, считывает коды команд и операнды, записывает результаты

вычислений в память или устройства ввода/вывода.

Операционное устройство состоит из РОН, предназначенных для хранения промежуточных результатов

вычислений - данных и адресов; АЛУ с буферными регистрами; регистра флагов; схемы управления и

синхронизации, которая дешифрует коды команд и генерирует управляющие сигналы для всех блоков

схемы МП. Шинный интерфейс состоит из шестибайтной регистровой памяти, которая называется

очередью команд, четырех сегментных регистров: СS, DS, ЕS, SS, указателя команд IP, сумматора, а также

вспомогательных регистров связи и буферных схем шин адреса/данных. Очередь команд работает по

принципу FIFO (First Input - First Output, т.е. "первый пришел - первый вышел") и сохраняет на выходе

порядок поступления команд. Длина очереди - 6 байт. Если операционное устройство занято выполнением

команды, шинный интерфейс самостоятельно инициирует опережающую выборку кодов команд из памяти в

очередь команд. Выборка из памяти очередного командного слова осуществляется тогда, когда в очереди

обнаруживаются два свободных байта. Очередь увеличивает быстродействие процессора в случае

последовательного выполнения команд. При выборке команд переходов, запросов и возвращений из

подпрограмм, обработки запросов прерываний очередь команд сбрасывается, и выборка начинается с

нового места программной памяти.

Еще одной задачей шинного интерфейса является формирование физического 20-разрядного адреса из

двух 16-разрядных слов. Первым словом является содержимое одного из сегментных регистров СS, SS, DS,

ЕS, а второе слово зависит от типа адресации операнда или кода команды. Суммирование 16-разрядных

слов происходит со смещением на 4 разряда и осуществляется с помощью сумматора, который входит в

состав шинного интерфейса.

8.

Особенности системы команд языка Ассемблер для разных типов микропроцессоров.Команда определяет операцию, которую выполняет МП над данными и содержит информацию о том, где будет

помещен результат операции, а также об адресе следующей команды.

Формат команды - состав, назначение и расположение полей кода команды; содержит операционную (код

операции) и адресную части (информация об адресах операндов, результате операции и следующей команде).

Длина формата команды определяет скорость ее выполнения и зависит от способа адресации операндов.

Существуют следующие способы адресации.

Прямая – адрес операнда указан непосредственно в команде.

Косвенная – указывается регистр, в котором хранится адрес ячейки памяти, содержащей операнд.

Непосредственная – операнд содержится во втором и третьем байтах команды.

Регистровая (неявная) - команда указывает на регистр или пару регистров, в которых записаны данные.

Стековая - адрес определяется указателем стека. Кроме перечисленных, существуют способы адресации:

автоинкрементная (автодекрементная), страничная, индексная, относительная.

9.

Организация устройств ввода/вывода информации в микропроцессорных системах.Одной из важнейших задач проектирования МПС является организация взаимодействия с устройствами

ввода/вывода (УВВ) - источниками и приемниками данных. К устройствам ввода относятся переключатели,

клавиатура, аналого-цифровые преобразователи (АЦП), датчики двоичной информации, а к устройствам вывода индикаторы, светодиоды, дисплеи, печатающие устройства, цифроаналоговые преобразователи (ЦАП),

транзисторные ключи, реле, коммутаторы. Примерами устройств одновременно и ввода и вывода являются

накопители на гибких и жестких магнитных дисках. УВВ различаются: разрядностью данных, быстродействием,

управляющими сигналами, типом протокола обмена, т.е. определенным порядком обмена. Данные в УВВ

изменяются в произвольный или определенный момент времени. Соединение УВВ с системной шиной МПС

осуществляется с помощью интерфейса ввода/вывода, который согласовывает сигналы УВВ с системной шиной

МПС. Как правило, интерфейс состоит из одного или нескольких портов ввода/вывода и схем управления ими.

Четырёхканальный аналого-цифровой

преобразователь

10.

Вводом-выводоминформации называют процесс передачи данных между микропроцессором и основной памятью(ОЗУ, ПЗУ), между микропроцессором и внешними устройствами, а также между основной памятью и внешними

устройствами. Различают три режима ввода-вывода: программный, по прерываниям и прямой доступ к памяти.

11.

Программный ввод-вывод инициируется программой работымикропроцессора, т.е. в определенных местах программы записываются

команды опроса портов или обращения к памяти, под управлением которых

осуществляется процесс ввода-вывода. Поэтому программный ввод-вывод

называют еще синхронным режимом ввода-вывода, т.е. управляемым

командами микропроцессора. Эти команды выполняются немедленно, если

внешние устройства имеют свойство постоянной готовности к приему или

передаче данных. Такими устройствами могут быть, например, светодиодные

или ЖК-индикаторы на выходе порта вывода или набор кнопок на входе

порта ввода. Если внешнее устройство таким свойством не обладает, то при

выполнении команды необходимо осуществлять проверку управляющего

сигнала готовности внешнего устройства к передаче или приему данных.

Если готовность устройства не подтверждается, то микропроцессор

переходит в режим ожидания активного уровня сигнала готовности.

Недостатком такой организации ввода-вывода являются большие временные

затраты на ожидание готовности медленного внешнего устройства. Однако

такой способ ввода-вывода имеет преимущество, заключающееся в простой

аппаратной реализации. Поэтому такой режим ввода-вывода используется

преимущественно для осуществления обмена данными с устройствами

постоянно готовыми к этому обмену.

12.

Ввод-вывод по прерываниям производится по инициативе внешних устройств и вводится принеобходимости помимо выполнения основной программы организовать обработку

информации от этих устройства по мере ее поступления. Например, прерывание может

формироваться бинарным датчиком или компаратором, сравнивающим аналоговое

напряжение с некоторой аналоговой уставкой в системе контроля. По прерыванию может

подключаться клавиатура в микропроцессорной системе. Поскольку режим ввода-вывода по

прерыванию активизируется внешним устройством, то его называют еще

асинхроннымвводом-выводом. При этом микропроцессор должен прервать выполнение

основной программы и перейти к подпрограмме обработки устройства, запросившего

прерывания.

Компаратор

13.

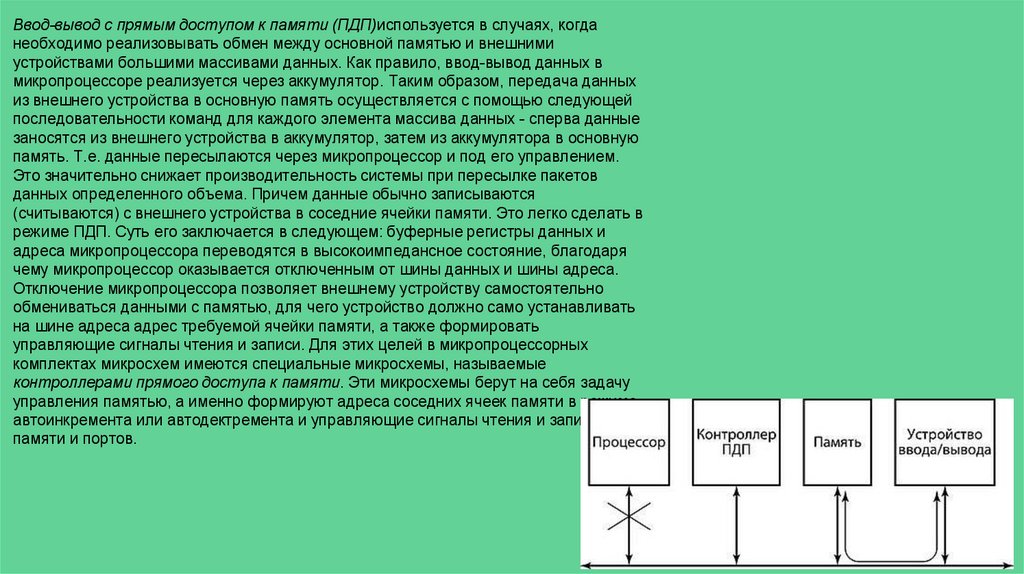

Ввод-вывод с прямым доступом к памяти (ПДП)используется в случаях, когданеобходимо реализовывать обмен между основной памятью и внешними

устройствами большими массивами данных. Как правило, ввод-вывод данных в

микропроцессоре реализуется через аккумулятор. Таким образом, передача данных

из внешнего устройства в основную память осуществляется с помощью следующей

последовательности команд для каждого элемента массива данных - сперва данные

заносятся из внешнего устройства в аккумулятор, затем из аккумулятора в основную

память. Т.е. данные пересылаются через микропроцессор и под его управлением.

Это значительно снижает производительность системы при пересылке пакетов

данных определенного объема. Причем данные обычно записываются

(считываются) с внешнего устройства в соседние ячейки памяти. Это легко сделать в

режиме ПДП. Суть его заключается в следующем: буферные регистры данных и

адреса микропроцессора переводятся в высокоимпедансное состояние, благодаря

чему микропроцессор оказывается отключенным от шины данных и шины адреса.

Отключение микропроцессора позволяет внешнему устройству самостоятельно

обмениваться данными с памятью, для чего устройство должно само устанавливать

на шине адреса адрес требуемой ячейки памяти, а также формировать

управляющие сигналы чтения и записи. Для этих целей в микропроцессорных

комплектах микросхем имеются специальные микросхемы, называемые

контроллерами прямого доступа к памяти. Эти микросхемы берут на себя задачу

управления памятью, а именно формируют адреса соседних ячеек памяти в режиме

автоинкремента или автодектремента и управляющие сигналы чтения и записи

памяти и портов.

14.

Кроме информационных линийадреса и данных,

микропроцессор

снабжен

управляющими выводами, образующими вместе с

Управляющие

сигналы

типового

микропроцессора.

выводами системного контроллера шину управления микропроцессорной системы. Управлюющие сигналы индивидуальны

для каждого типа микропроцессора, но, тем не менее, можно выделить характерные для почти всех микропроцессоров

сигналы. В некоторых случаях определенные сигналы исключают друг друга, поэтому присутствуют либо те, либо другие.

Разобъем управляющие сигналы для удобства в функциональные группы. Сигналы управления чтением/записью

предназначены для активизации периферийного модуля в режим выдачи данных на шину данных или приема данных с шины

данных. В общем случае режим чтения характеризуется тем, что микропроцессор запрашивает данные от периферийного

модуля, а режим записи - тем, что микропроцессор выставляет данные периферийному модулю. У некоторых

микропроцессоров эти сигналы представлены группой сигналов системной шины управления, рассмотренных ранее в теме

структурной организации микропроцессорной системы:

RDM(readmemory, чтение памяти) - сигнал инициализации чтения из модулей запоминающих устройств

(выходной сигнал);

WRM(writememory, запись в память) - сигнал инициализации записи в модули запоминающих устройств

(выходной сигнал);

RDIO(readinput/output, чтение порта) - сигнал инициализации чтения из порта ввода (выходной сигнал);

WRIO(writeinput/output, запись в порт) - сигнал инициализации записи в порт вывода (выходной сигнал).

15.

Сигналы управления прерыванием обычно представлены двумя сигналами:INT(interrupt, прерывание) – входной сигнал от периферийного модуля

(контроллера прерывания), запрашивающего процесс ввода-вывода по

прерыванию. В ответ на этот сигнал микропроцессор должен запустить

обрабатывающую прерывание подпрограмму. Анализируется этот

сигнал в последнем такте последнего машинного цикла, т.е. в конце

выполнения текущей команды;

INTA(interruptacknowledge, подтверждение прерывания) – выходной

сигнал от микропроцессора, подтверждающий прерывание и

сообщающий периферийному модулю (контроллеру прерывания) о

готовности микропроцессора приступить к обслуживанию прерывания.

По этому сигналу внешнее устройство (контроллер прерывания) должен

выставить на шину данных код команды прерывания, в которой

закодирован номер устройства, запрашивающего прерывание.

16.

Сигналы управления режимом прямого доступа к памятиформируютгруппу из двух сигналов:

HOLD(hold, захват шин) – входной сигнал от периферийного устройства,

запрашивающего процесс ввода-вывода в режиме ПДП. Этот сигнал

анализируется обычно между машинными циклами. В ответ на этот

сигнал микропроцессор должен перевести свои буферные регистры,

связывающие его с шинами данных и адреса, в высокоимпедансное

состояние. В результате микропроцессор осовобождает шины и

внешнее устройство начинает обмен данными с памятью напрямую без

участия микропроцессора;

HLDA(holdacknowledge, подтверждение захвата) – выходной сигнал от

микропроцессора, подтверждающий, что микропроцессор перевел свои

буферные регистры в высокоимпедансное состояние и освободил

шины.

17.

Сигналыуправления

ожиданием

служат

для

синхронизации

микропроцессора с медленными устройствами ввода-вывода. Не всегда

внешнее устройство может мгновенно отреагировать и подготовиться к режиму

приема или записи по сигналамRDIOилиWRIO(RDилиWR). Если внешнее

устройство медленное, то ему необходимо время для формирования данных

или включения в соответствующий режим. Для синхронизации работы

микропроцессора с медленными устройствами ввода-вывода используются

следующие сигналы:

RDY(ready, готовность) – входной сигнал от внешнего устройства,

являющийся признаком того, что оно готово к обмену данными. Если

этот сигнал имеет пассивный уровень, то микропроцессор переходит в

такты ожидания готовности внешнего утройства. В течение этого

времени микропроцессор не выполняет никаких действий, а только

анализирует сигнал готовности;

WAIT(wait, ожидание) – выходной сигнал, являющийся признаком того,

что микропроцессор находится в тактах ожидания сигнала готовности.

18.

Дополнительные сигналыобеспечивают синхронизацию работы микропроцессора ссистемным контроллером, шинными формирователями, схемой тактового генератора и

начальной установки. К ним можно отнести следующие сигналы:

SYNC(synchronization, синхронизация) – выходной сигнал, вырабатываемый

микропроцессором в начале каждого машинного цикла. Он служит для записи в

системный контроллер служебной информации, из которой системный контроллер

формирует дополнительные сигналы управления (например,RDM, WRM,RDIOиWRIO);

ALE(addresslatchenable, фиксация адреса) – выходной сигнал микропроцессора,

имеющего мультиплексированную шину данных/адреса. Мультиплесированная шина

позволяет уменьшить количество выводов микросхемы микропроцессора, поскольку

разряды шины данных и адреса реализуются в таких микропроцессорах на одних и тех

же выводах. В начале машинного цикла всегда должен быть выставлен адрес внешнего

устройства или ячейки памяти, а лишь затем произведен обмен информацией. Поэтому

шину данных и адреса можно объединить в одну мультиплексированную шину. Но

адрес должен удерживаться на время всего машинного цикла. Для этого сигналомALE,

который выставляется активным вместе с выставлением адреса на

мультиплексированной шине, адрес записывается во внешний регистр (шинный

формирователь) и там защелкивается до следующего машинного цикла. Затем

мультиплексированная шина переключается в режим шины данных;

RST(reset, сброс) – входной сигнал сброса, обнуляющий регистр микропроцессора,

содержащий адреса подлежащих выполнению команд и называемыйсчетчиком команд.

В результате программа начинает выполняться с нулевого адреса, т.е. с начала;

CLK(clock, тактирование) – вход (входы) сигналов тактового генератора. Эти сигналы

синхронизируют работу микропроцессора. По этим сигналам часто оценивают

производительность микропроцессора.

19.

Отличия микроконтроллера от микропроцессораИсточник: YouTube-канал

Радиолюбитель TV

electronics

electronics