Similar presentations:

Пристрої програмованої логіки (ППЛ). Прості програмовані логічні пристрої (SPLD). Лекція 2-10

1.

Харківський національний університет радіоелектронікиЛЕКЦІЯ 2-10

ПРИСТРОЇ ПРОГРАМОВАНОЇ

ЛОГІКИ (ППЛ)

Прості програмовані логічні пристрої

(SPLD)

Складні програмовані логічні пристрої

(CPLD)

Кафедра КІТС

Корабльов М.М.

2.

Харківський національний університет радіоелектронікиЗагальні відомості та класифікація ПЛІС (PLD)

Застосування великих інтегральних схем (ВІС) в цифрових системах

дозволяє істотно поліпшити їх експлуатаційні можливості (підвищити

надійність і швидкодію, понизити споживану потужність і габаритні

розміри). Підвищення спеціалізації ВІС при поліпшенні вказаних вище

показників завжди вступає в протиріччя з їх універсальністю, що

розширює їх необхідну номенклатуру і зменшує обсяг випуску.

Усунути вказане протиріччя між спеціалізацією і універсальністю

можна шляхом розробки ВІС, алгоритми роботи яких можуть бути

змінені шляхом створення програмованих систем. Під програмованістю

розуміється не здатність реалізувати заданий алгоритм обробки вхідних

кодів, змінюючи програму роботи, як це робить мікропроцесор, а

можливість зміни внутрішньої структури ВІС так, щоб вона

забезпечувала реалізацію заданих функцій на апаратному рівні.

Основною перевагою програмованих логічних інтегральних схем

(ПЛІС) перед спеціалізованими ВІС являється малий час виготовлення

з наперед заданими характеристиками. Можливість програмування

ПЛІС досягається шляхом надмірності їх апаратної частини, тобто

потрібно введення додаткових виводів і структур налаштування,

додавання інформаційних ланцюгів і т.д. Тому реальна швидкодія

пристроїв, виконаних на ПЛІС, їх споживання і інші характеристики

будуть завжди гірші, ніж у пристроїв на спеціалізованих ВІС.

Кафедра КІТС

Корабльов М.М.

3.

Харківський національний університет радіоелектронікиЗагальні відомості та класифікація ПЛІС (PLD)

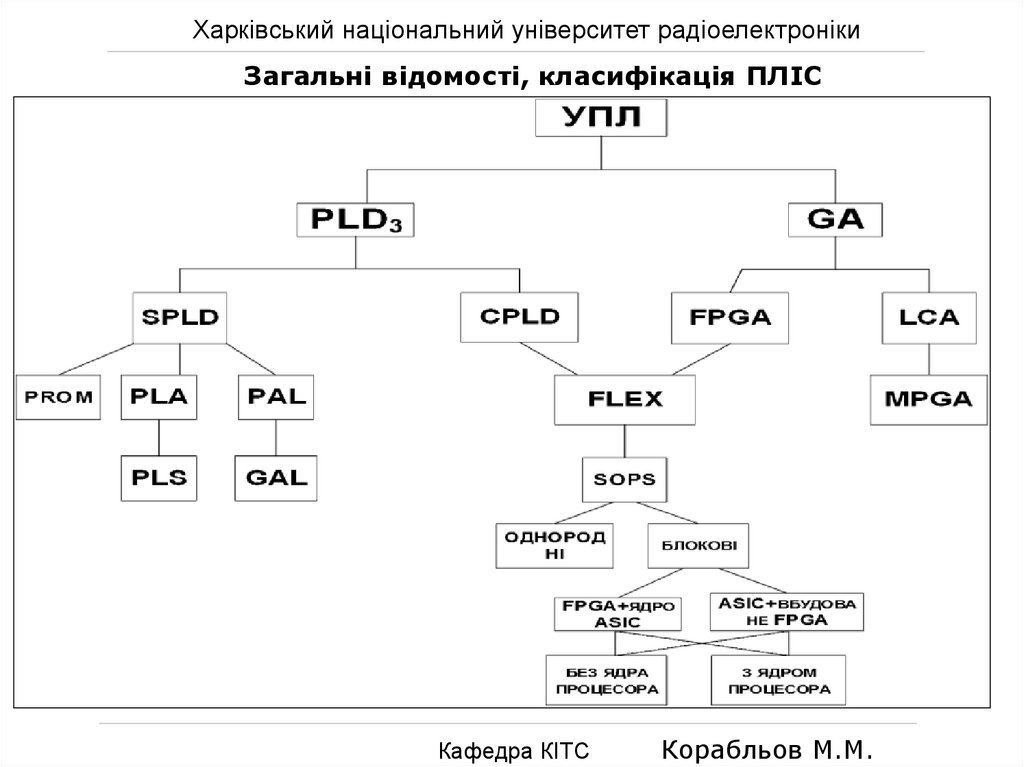

ПЛІС можна класифікувати по багатьом ознакам, в першу чергу це:

рівень інтеграції і зв’язана з ним логічна складність;

архітектура (тип функціональних блоків, характер системи їх

з'єднань);

число допустимих циклів програмування;

тип конфігурації пам'яті;

ступінь залежності затримок сигналів від шляхів їх

розповсюдження;

компонентна база (КМОН, ТТЛ, КА та інші);

однорідність чи гібридність.

Класифікація ПЛІС за архітектурними ознаками

Кафедра КІТС

Корабльов М.М.

4.

Харківський національний університет радіоелектронікиЗагальні відомості, класифікація ПЛІС

Кафедра КІТС

Корабльов М.М.

5.

Харківський національний університет радіоелектронікиЗагальні відомості, класифікація ПЛІС

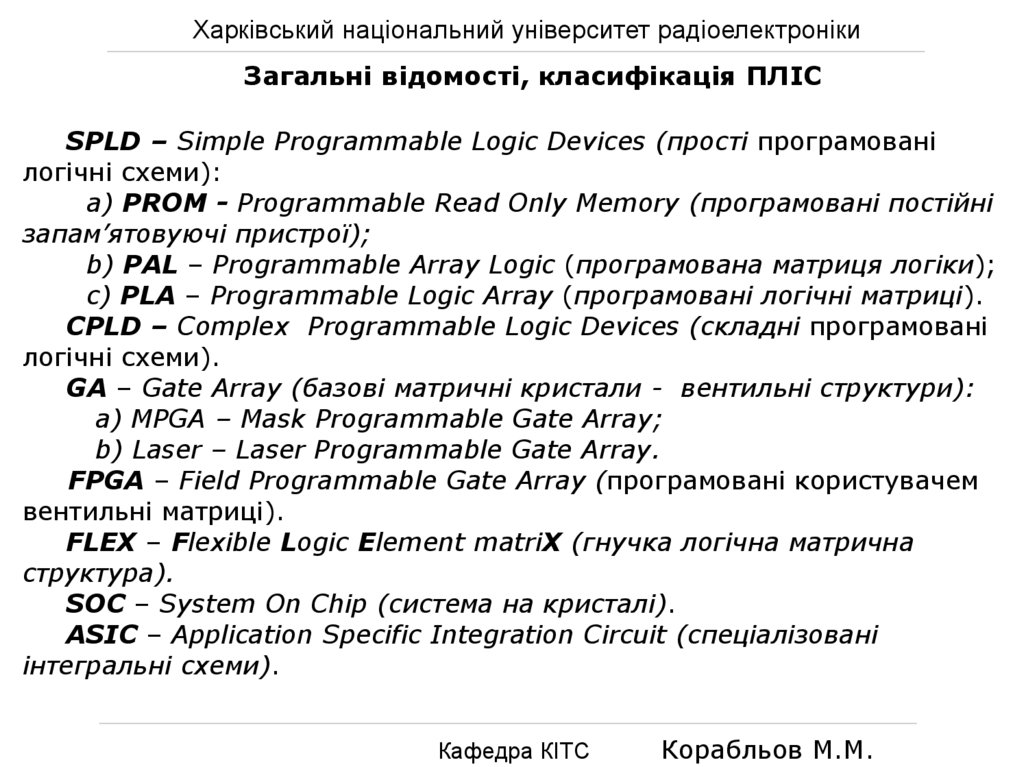

SPLD – Simple Programmable Logic Devices (прості програмовані

логічні схеми):

a) PROM - Programmable Read Only Memory (програмовані постійні

запам’ятовуючі пристрої);

b) PAL – Programmable Array Logic (програмована матриця логіки);

c) PLA – Programmable Logic Array (програмовані логічні матриці).

CPLD – Complex Programmable Logic Devices (складні програмовані

логічні схеми).

GA – Gate Array (базові матричні кристали - вентильні структури):

a) MPGA – Mask Programmable Gate Array;

b) Laser – Laser Programmable Gate Array.

FPGA – Field Programmable Gate Array (програмовані користувачем

вентильні матриці).

FLEX – Flexible Logic Element matriX (гнучка логічна матрична

структура).

SOC – System On Chip (система на кристалі).

ASIC – Application Specific Integration Circuit (спеціалізовані

інтегральні схеми).

Кафедра КІТС

Корабльов М.М.

6.

Харківський національний університет радіоелектронікиУзагальнена структурна схема SPLD

Блок термів (кон'юнкцій) є матрицею логічних елементів І, а блок

диз'юнкцій - матрицею логічних елементів АБО. Тому послідовне

з'єднання таких матриць дозволяє реалізувати логічну функцію

довільного виду. Отримання конкретних логічних функцій припускає

виконання конкретних з'єднань в матрицях елементів І та АБО.

Міняючи з'єднання елементів в матрицях І та АБО, можна

настроювати властивості пристрою. Можливі три варіанти:

- постійна структура матриці I ([І]- const) і програмована структура

матриці АБО ([АБО]-program) - PROM;

- програмована структура матриці І ([І] - program) і постійна

структура матриці АБО ([АБО]-const) - PAL;

- програмована структура як матриці І ([І]- program), так і матриці

АБО ([АБО]-program) - PLA.

Кафедра КІТС

Корабльов М.М.

7.

Харківський національний університет радіоелектронікиПрості програмовані логічні пристрої (SPLD) на PROM

У структурі PROM легко можна виділити блоки, що відповідають

узагальненій структурній схемі SPLD. Роль постійної структури матриці

І ([І]- const) виконує дешифратор, перетворюючий n вхідних сигналів

хi в 2n вихідних сигналів N. Така побудова матриці І припускає цілком

певну структуру програмованої матриці АБО ([АБО]-program), функції

якої, по суті, вироджуються до рівня підключення до виходу сигналів

або лог. 0, або лог.1.

Особливості використання PROM в якості SPLD:

- PROM реалізує логічну функцію, представлену у вигляді

довершеної диз’юнктивної нормальної форми, тобто логічна функція

має бути представлена сумою конституент одиниці, тому для технічної

реалізації її мінімізація не потрібна;

- PROM дозволяє реалізувати тільки повністю визначені логічні

функції, тому потрібна однозначність їх значень для усіх можливих

комбінацій вхідних змінних.

Кафедра КІТС

Корабльов М.М.

8.

Харківський національний університет радіоелектронікиПрості програмовані логічні пристрої (SPLD) на PROM

Використання PROM на прикладі реалізації трьох логічних

функцій

Кафедра КІТС

Корабльов М.М.

9.

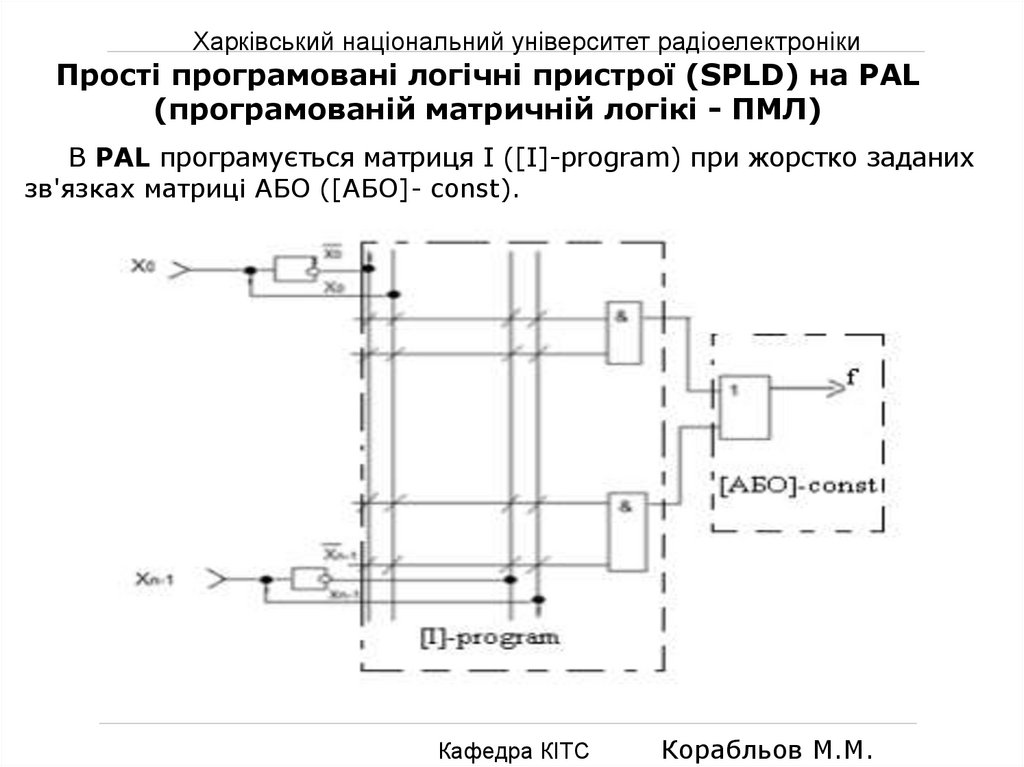

Харківський національний університет радіоелектронікиПрості програмовані логічні пристрої (SPLD) на PAL

(програмованій матричній логікі - ПМЛ)

В PAL програмується матриця I ([І]-program) при жорстко заданих

зв'язках матриці АБО ([АБО]- const).

Кафедра КІТС

Корабльов М.М.

10.

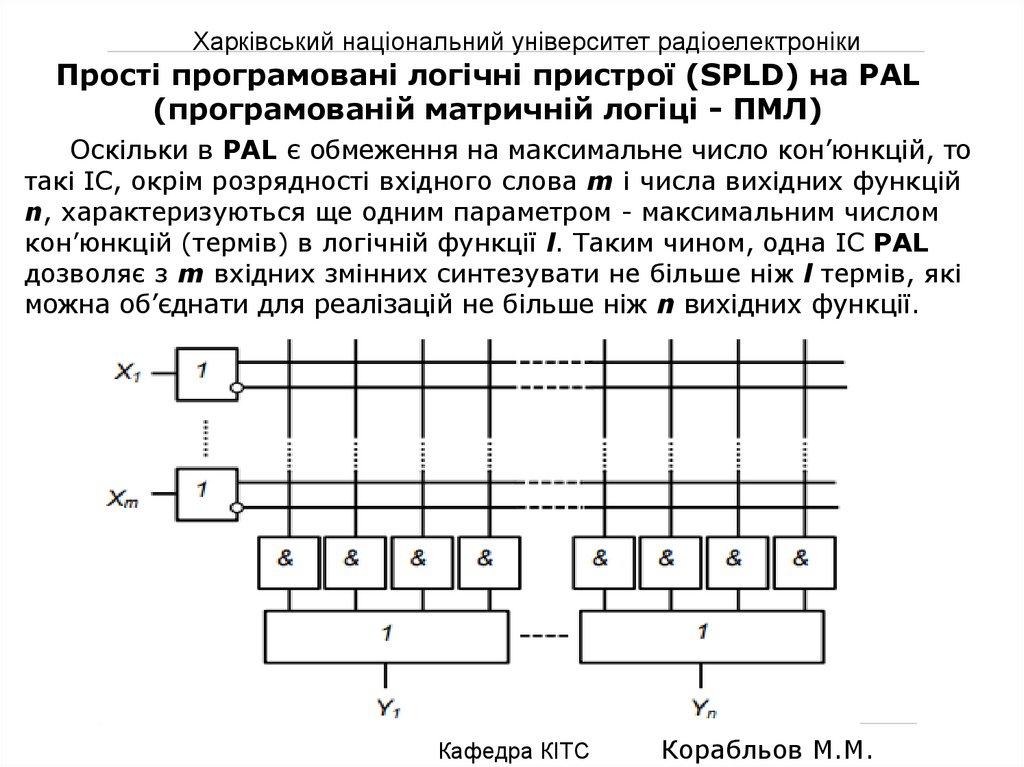

Харківський національний університет радіоелектронікиПрості програмовані логічні пристрої (SPLD) на PAL

(програмованій матричній логіці - ПМЛ)

Оскільки в PAL є обмеження на максимальне число кон’юнкцій, то

такі ІС, окрім розрядності вхідного слова m і числа вихідних функцій

n, характеризуються ще одним параметром - максимальним числом

кон’юнкцій (термів) в логічній функції l. Таким чином, одна ІС PAL

дозволяє з m вхідних змінних синтезувати не більше ніж l термів, які

можна об’єднати для реалізацій не більше ніж n вихідних функції.

Кафедра КІТС

Корабльов М.М.

11.

Харківський національний університет радіоелектронікиПрості програмовані логічні пристрої (SPLD) на PLA

(програмованих логічних матрицях - ПЛМ)

PLA забезпечують можливість зміни зв'язків як в матриці І ([I]program), так і в матриці АБО ([АБО]- program). цей тип ПЛІС досить

складний для більшості користувачів з точки зору їх програмування.

Наявність програмованого з'єднання в обох матрицях спричиняє

збільшення розмірів, падіння надійності і швидкодії в порівнянні з PAL.

Кафедра КІТС

Корабльов М.М.

12.

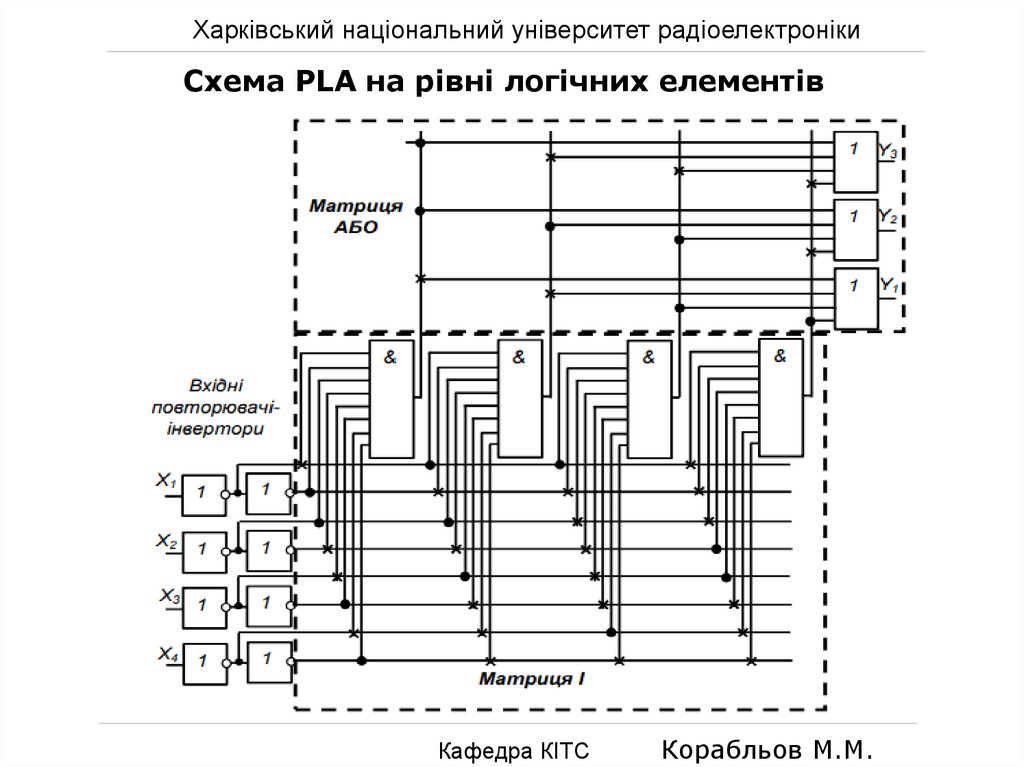

Харківський національний університет радіоелектронікиСхема PLA на рівні логічних елементів

Кафедра КІТС

Корабльов М.М.

13.

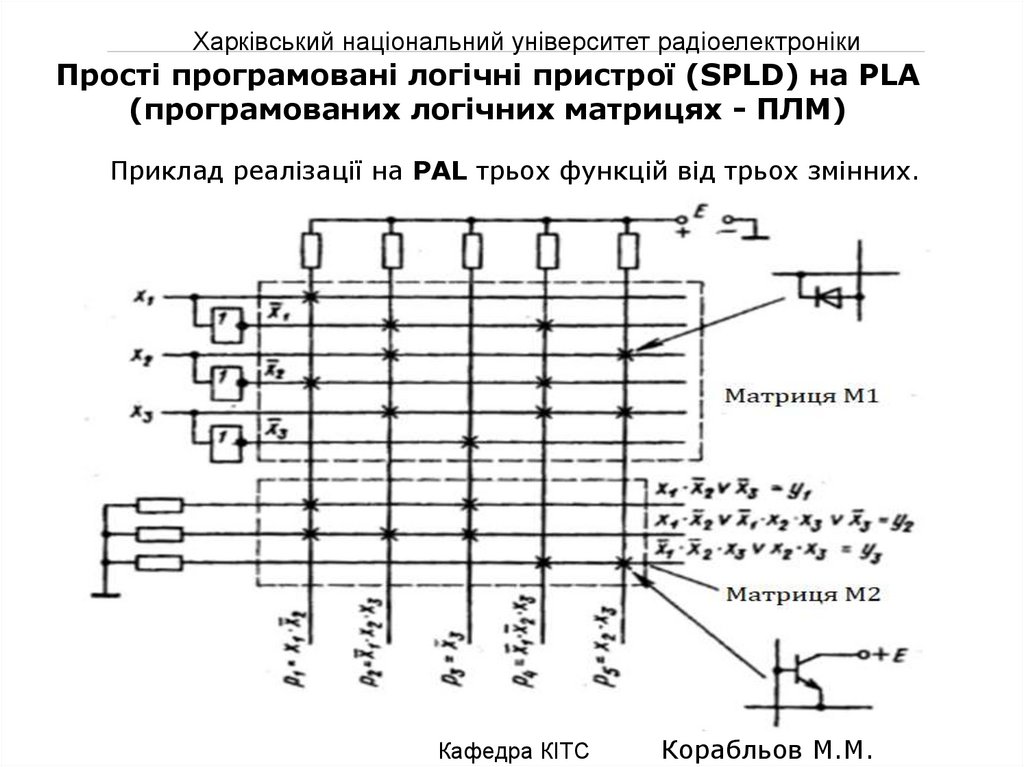

Харківський національний університет радіоелектронікиПрості програмовані логічні пристрої (SPLD) на PLA

(програмованих логічних матрицях - ПЛМ)

Приклад реалізації на PAL трьох функцій від трьох змінних.

Кафедра КІТС

Корабльов М.М.

14.

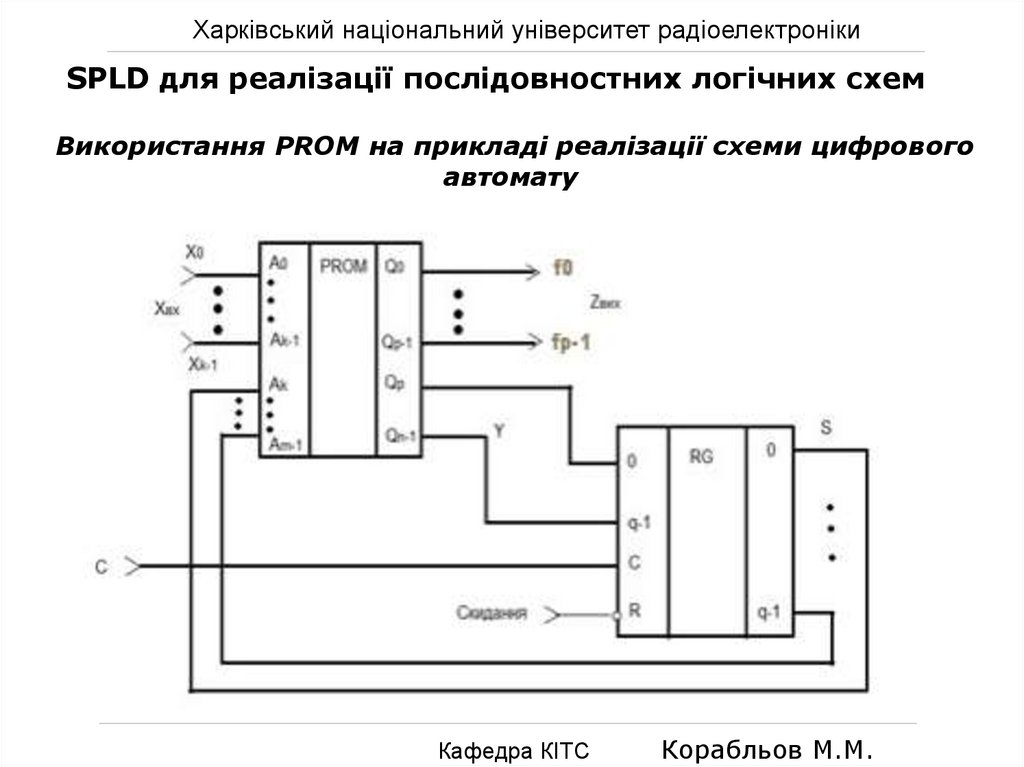

Харківський національний університет радіоелектронікиSPLD для реалізації послідовностних логічних схем

Використання PROM на прикладі реалізації схеми цифрового

автомату

Кафедра КІТС

Корабльов М.М.

15.

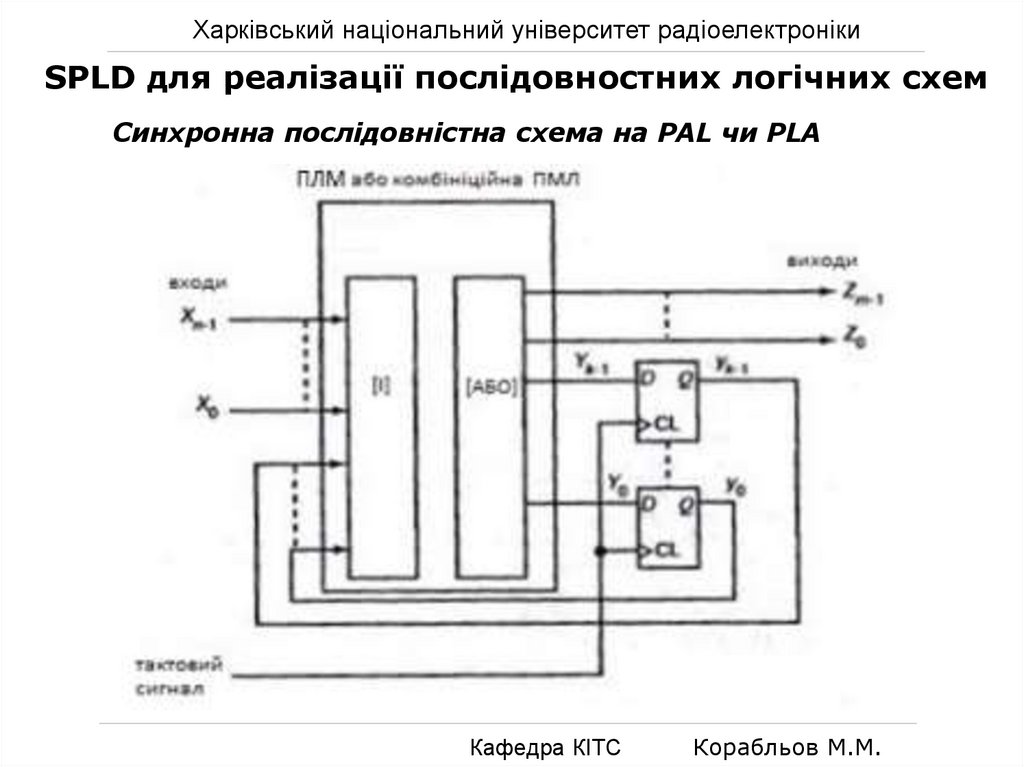

Харківський національний університет радіоелектронікиSPLD для реалізації послідовностних логічних схем

Синхронна послідовністна схема на PAL чи PLA

Кафедра КІТС

Корабльов М.М.

16.

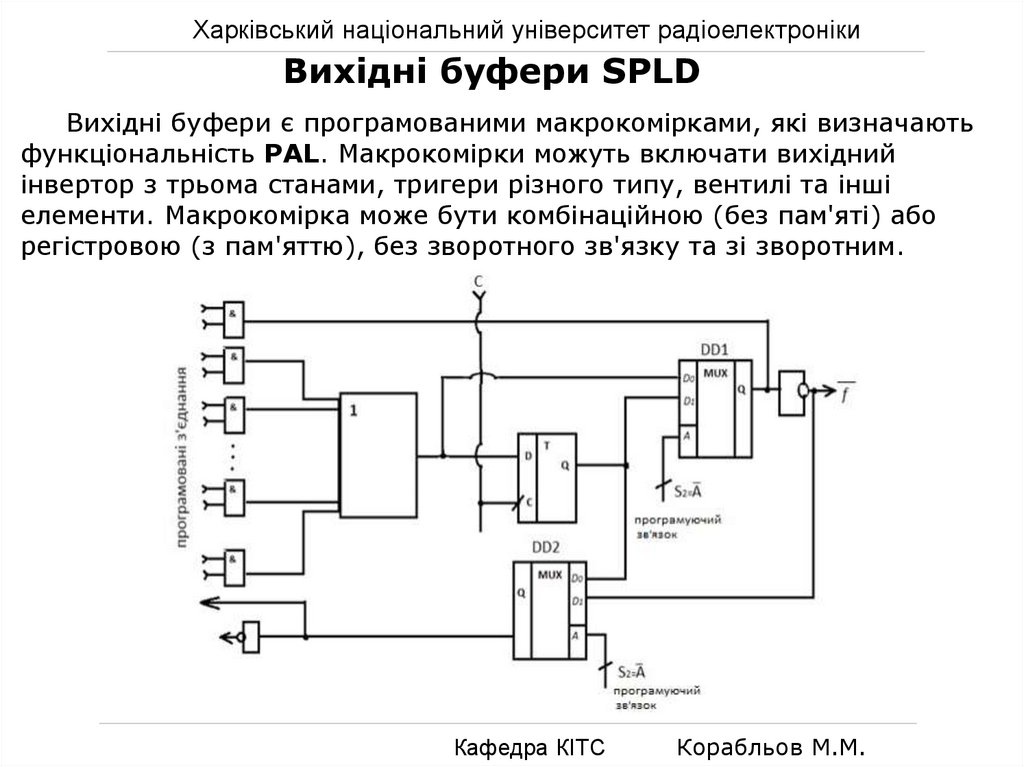

Харківський національний університет радіоелектронікиВихідні буфери SPLD

Вихідні буфери є програмованими макрокомірками, які визначають

функціональність PAL. Макрокомірки можуть включати вихідний

інвертор з трьома станами, тригери різного типу, вентилі та інші

елементи. Макрокомірка може бути комбінаційною (без пам'яті) або

регістровою (з пам'яттю), без зворотного зв'язку та зі зворотним.

Кафедра КІТС

Корабльов М.М.

17.

Харківський національний університет радіоелектронікиСкладні програмовані логічні пристрої (CPLD)

CPLD – мікросхеми високого рівня інтеграції, основними частинами

яких є:

1. Функціональні блоки (ФБ).

2. Система комутації, що дозволяє поєднувати ФБ в єдиний

пристрій, яка виконана у вигляді програмованої матриці з'єднань (ПМЗ).

3. Блоки введення-виведення (БВВ).

m

ФБ 1

n

:

:

БВВ

:

:

ПМС

:

:

m

ФБ N

n

GTS

GCK

GSR

Кафедра КІТС

Корабльов М.М.

18.

Харківський національний університет радіоелектронікиСТРУКТУРА CPLD

Програмована логічна інтегральна схема CPLD складається з кількох

макрокомірок, розміщених на одному кристалі. Кожна макрокомірка

з'єднана з блоками введення-виводу, що здійснюють формування

необхідного виду входів або виходів для роботи із зовнішніми схемами.

Крім того, всі макрокомірки та блоки введення-виведення пов'язані між

собою внутрішніми паралельними шинами.

Приклад внутрішньої схеми CPLD наведено рисунку.

Кафедра КІТС

Корабльов М.М.

19.

Харківський національний університет радіоелектронікиCPLD може містити N ФБ, кожен з яких може мати n

макрокомірок.

ФБ отримують інформацію від ПМЗ (m вхідних сигналів),

кожен ФБ може формувати n вихідних сигналів, які можуть

подаватися в ПМЗ або БВВ.

ПМЗ забезпечує повну комутованість ФБ, тобто можливість

подавати сигнали з будь-якого виходу на будь-який вхід.

БВВ пов'язані зовнішніми двонаправленими виводами і

можуть бути запрограмовані як на вхід, так і на вихід.

Нижні три виходи можуть використовуватися як для

введення-виведення, так і для подачі зовнішніх керуючих

сигналів.

Крім зазначених частин в CPLD можуть входити :

• Контролюючі зовнішні інтерфейси jTAG (для тестування

мікропрограми).

• Контролер для управління операціями програмування та

ін.

Кафедра КІТС

Корабльов М.М.

20.

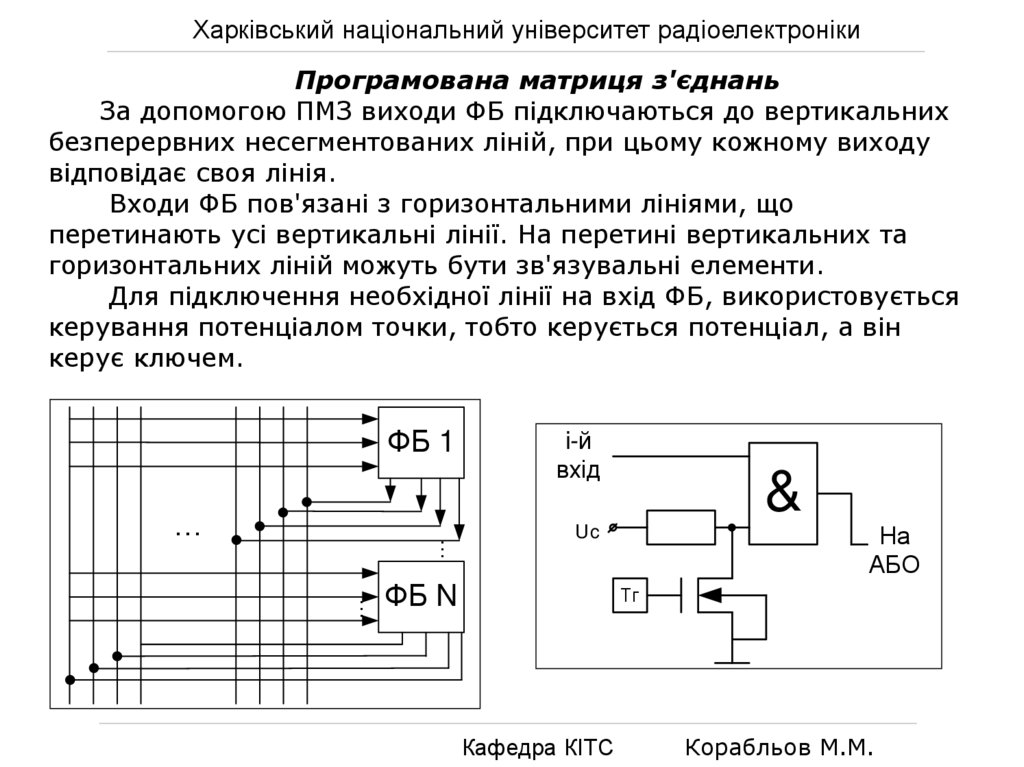

Харківський національний університет радіоелектронікиПрограмована матриця з'єднань

За допомогою ПМЗ виходи ФБ підключаються до вертикальних

безперервних несегментованих ліній, при цьому кожному виходу

відповідає своя лінія.

Входи ФБ пов'язані з горизонтальними лініями, що

перетинають усі вертикальні лінії. На перетині вертикальних та

горизонтальних ліній можуть бути зв'язувальні елементи.

Для підключення необхідної лінії на вхід ФБ, використовується

керування потенціалом точки, тобто керується потенціал, а він

керує ключем.

ФБ 1

…

…

i-й

вхід

&

Uc

…

ФБ N

На

АБО

Тг

Кафедра КІТС

Корабльов М.М.

21.

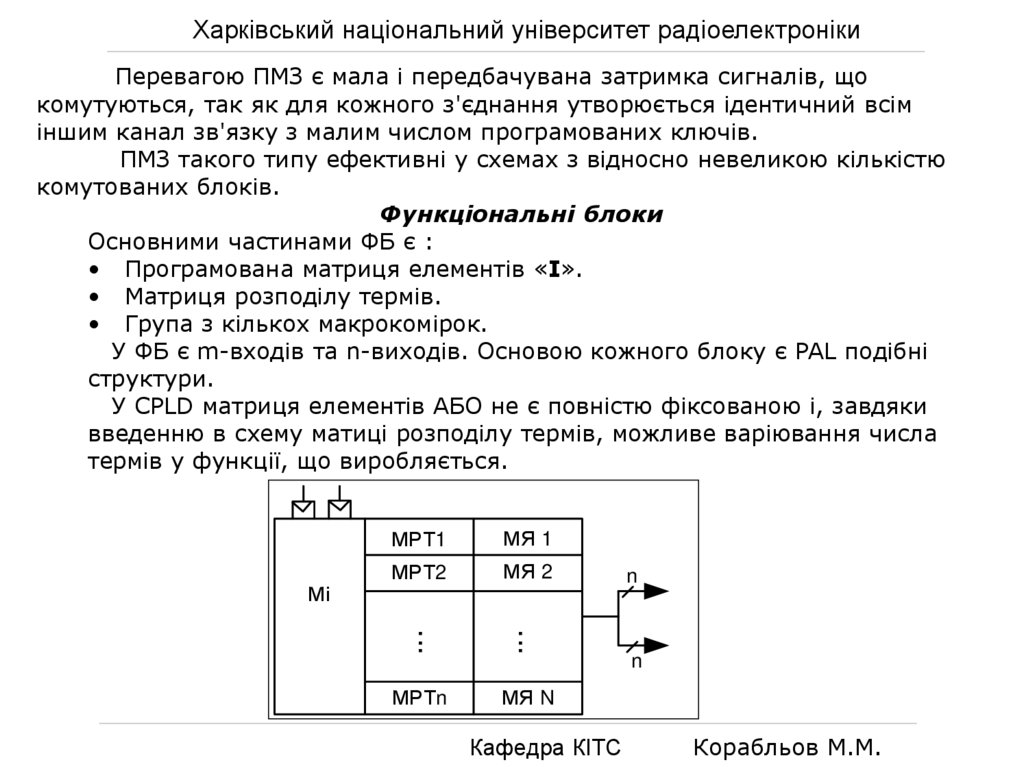

Харківський національний університет радіоелектронікиПеревагою ПМЗ є мала і передбачувана затримка сигналів, що

комутуються, так як для кожного з'єднання утворюється ідентичний всім

іншим канал зв'язку з малим числом програмованих ключів.

ПМЗ такого типу ефективні у схемах з відносно невеликою кількістю

комутованих блоків.

Функціональні блоки

Основними частинами ФБ є :

• Програмована матриця елементів «І».

• Матриця розподілу термів.

• Група з кількох макрокомірок.

У ФБ є m-входів та n-виходів. Основою кожного блоку є PAL подібні

структури.

У CPLD матриця елементів АБО не є повністю фіксованою і, завдяки

введенню в схему матиці розподілу термів, можливе варіювання числа

термів у функції, що виробляється.

МЯ 1

МРТ2

МЯ 2

...

...

Мі

МРТ1

МРТn

МЯ N

Кафедра КІТС

n

n

Корабльов М.М.

22.

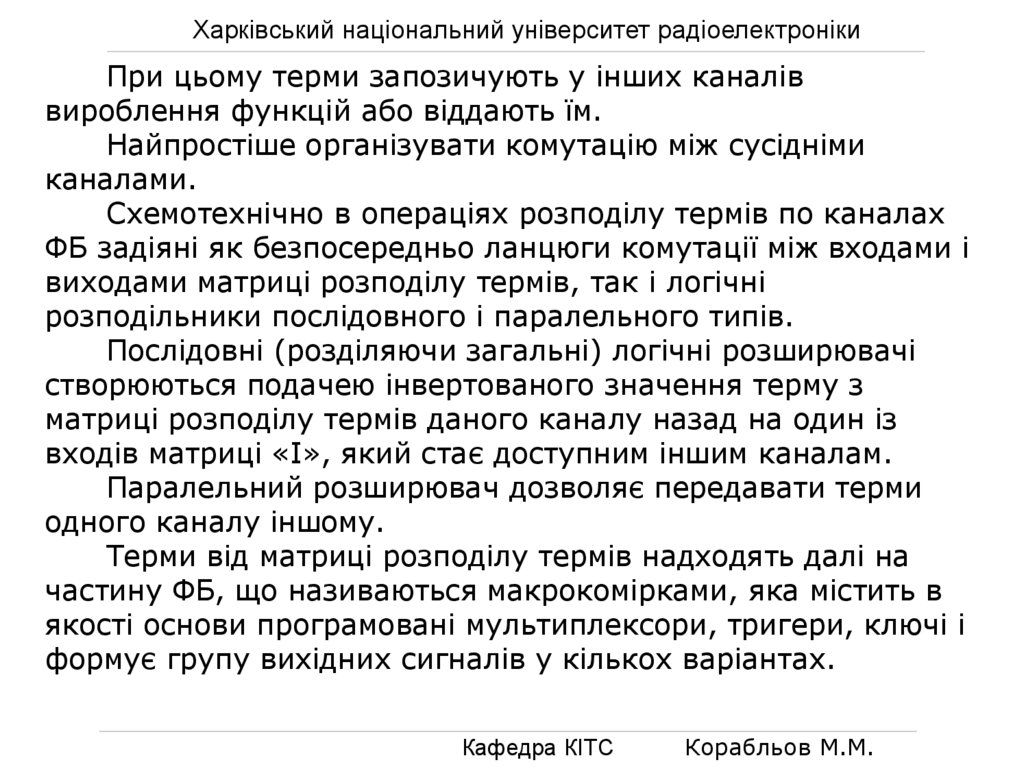

Харківський національний університет радіоелектронікиПри цьому терми запозичують у інших каналів

вироблення функцій або віддають їм.

Найпростіше організувати комутацію між сусідніми

каналами.

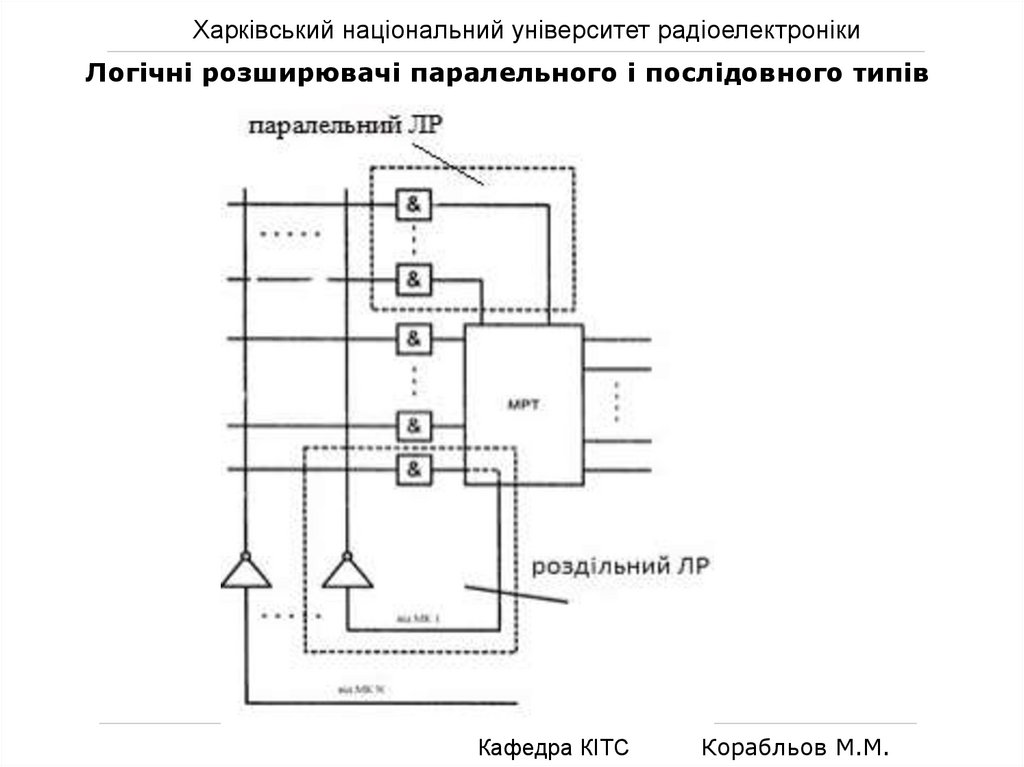

Схемотехнічно в операціях розподілу термів по каналах

ФБ задіяні як безпосередньо ланцюги комутації між входами і

виходами матриці розподілу термів, так і логічні

розподільники послідовного і паралельного типів.

Послідовні (розділяючи загальні) логічні розширювачі

створюються подачею інвертованого значення терму з

матриці розподілу термів даного каналу назад на один із

входів матриці «І», який стає доступним іншим каналам.

Паралельний розширювач дозволяє передавати терми

одного каналу іншому.

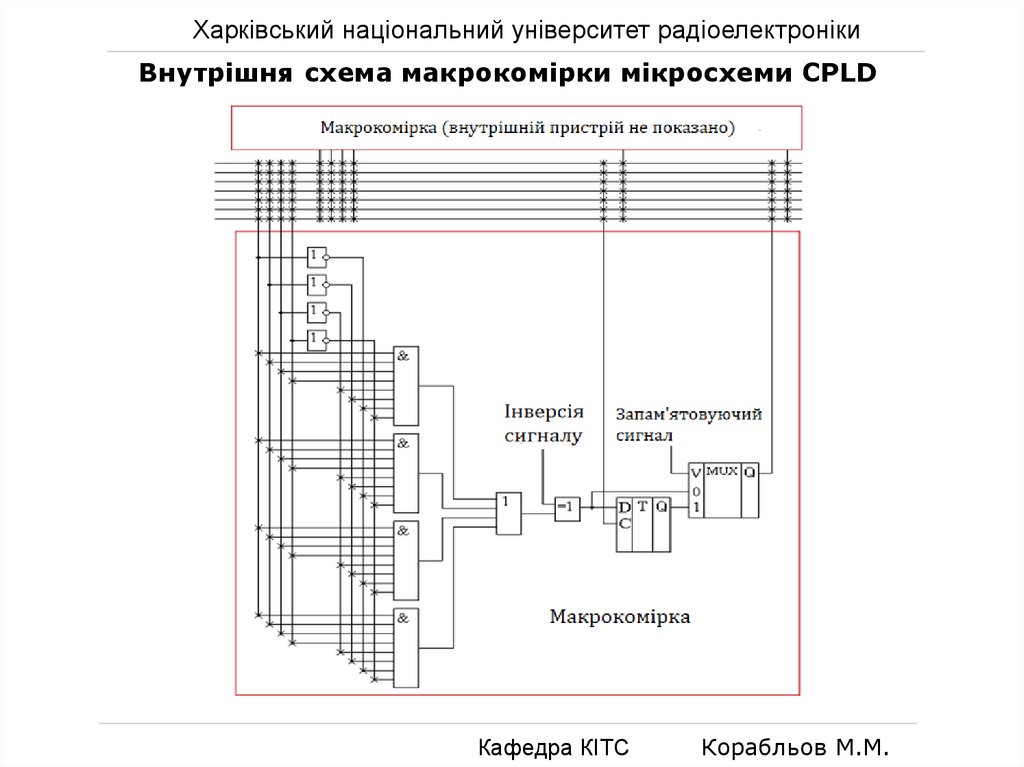

Терми від матриці розподілу термів надходять далі на

частину ФБ, що називаються макрокомірками, яка містить в

якості основи програмовані мультиплексори, тригери, ключі і

формує групу вихідних сигналів у кількох варіантах.

Кафедра КІТС

Корабльов М.М.

23.

Харківський національний університет радіоелектронікиЛогічні розширювачі паралельного і послідовного типів

Кафедра КІТС

Корабльов М.М.

24.

Харківський національний університет радіоелектронікиВнутрішня схема макрокомірки мікросхеми CPLD

Кафедра КІТС

Корабльов М.М.

25.

Харківський національний університет радіоелектронікиБлоки введення-виведення CPLD

Основою служать вхідний та вихідний буфери. Структурно БВВ можна

представити так:

до інших

МК

До

ПМС

1

Ucc

Від МК

PTOE

2

3

0

1

ПрСт

ОЕ

1

ПрКф

ПрК

GOE 1

int

GOE 2

Ucc

2

Згідно з прийнятою класифікацією в клас CPLD потрапляють ПЛІС з

рівнем інтеграції від 600 до 20000 еквівалентних вентилів, з числом

макрокомірок від 32 до 512, числом ФБ від 2 до 16 і часом розподілу сигналу

від входу до будь-якого виходу від 5 до 20 ns.

Кафедра КІТС

Корабльов М.М.

26.

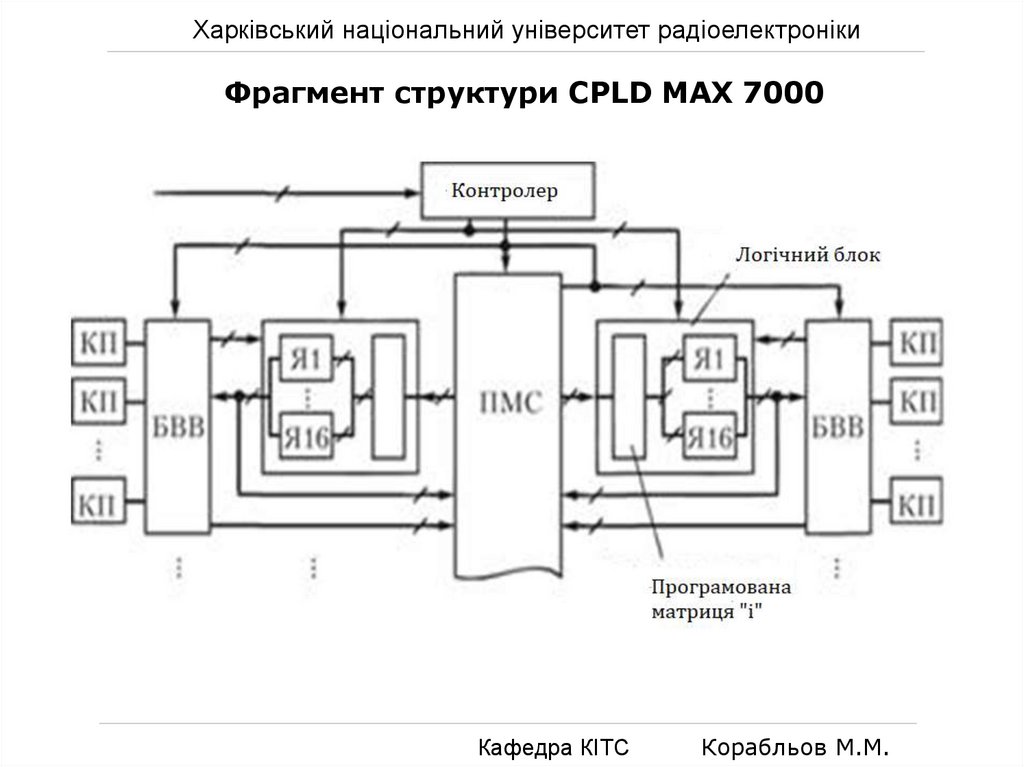

Харківський національний університет радіоелектронікиФрагмент структури CPLD МАХ 7000

Кафедра КІТС

Корабльов М.М.

27.

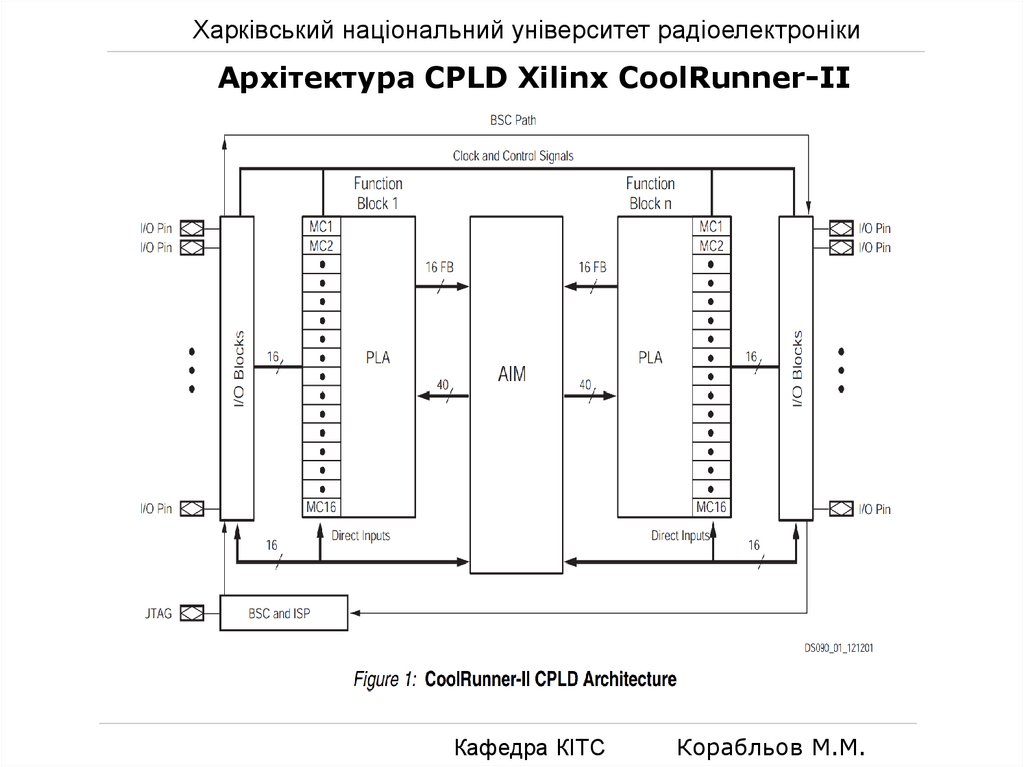

Харківський національний університет радіоелектронікиАрхітектура CPLD Xilinx CoolRunner-II

Кафедра КІТС

Корабльов М.М.

28.

Харківський національний університет радіоелектронікиАрхітектура CPLD Xilinx CoolRunner-II

Основні функції:

- Цей пристрій CPLD має кілька функціональних блоків,

починаючи з «Функціонального блоку 1» до «Функціонального

блоку n» (це число коливається від 2 до 32 у CPLD CoolRunner-II).

- 16 рядків виведення з кожного функціонального блоку

надходять до AIM (розширену матрицю міжз'єднань), тоді як 40

рядків сигналів вводяться у функціональні блоки з AIM.

- Кожен функціональний блок має 16 макроелементів (від MC1 до

MC16).

Кожен MacroCell має доступ до 16 сигналів із блоків вводу /

виведення.

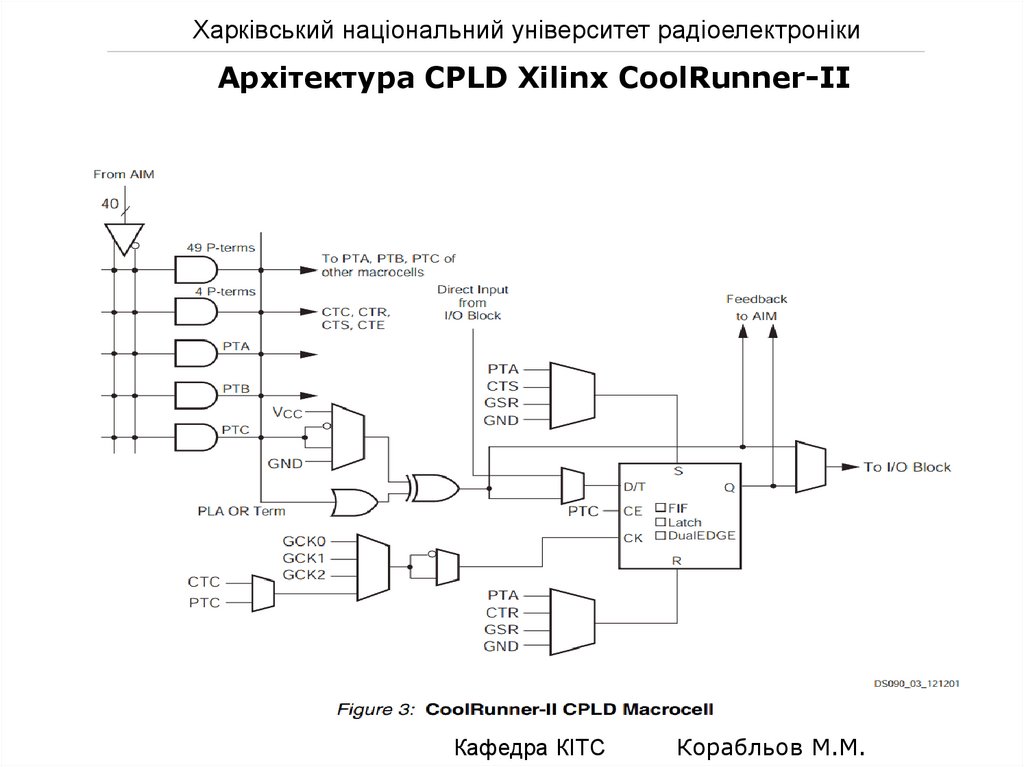

- Структура MacroCell показана нижче. Кожна макрокомірка

містить 1 масив тригерів та PLA із сумою продуктів, які користувачі

можуть використовувати для створення комбінаторної чи

послідовної логіки. Таким чином, максимальне число тригерів,

доступних CoolRunner-II CLPD (XC2C512), становить 512.

- AIM може бути запрограмована на з'єднання сигналів, як ми

хочемо. Але, як видно з другого пункту вище, кількість сигналів

обмежена для кожного функціонального блоку.

Кафедра КІТС

Корабльов М.М.

29.

Харківський національний університет радіоелектронікиАрхітектура CPLD Xilinx CoolRunner-II

Кафедра КІТС

Корабльов М.М.

30.

Харківський національний університет радіоелектронікиКонтрольні питання

1. Пристрої програмованої логіки, загальні

відомості, класифікація.

2. Прості програмовані логічні пристрої (SPLD):

PROM, PLA, PAL.

3. Складні програмовані логічні пристрої (CPLD).

4. Архітектура і структурна організація CPLD.

5. Програмована матриця з'єднань CPLD.

6. Функціональні блоки CPLD.

7. Блоки введення-виведення CPLD.

Кафедра КІТС

Корабльов М.М.

electronics

electronics