Similar presentations:

Комп’ютерна логіка (частина 1)

1.

Комп’ютерна логіка (частина 1)Національний університет «Львівська

політехніка»

399 слайдів

2. Лекція 1

• Вступ - мета та задачі курсу• Організаційні питання

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

2

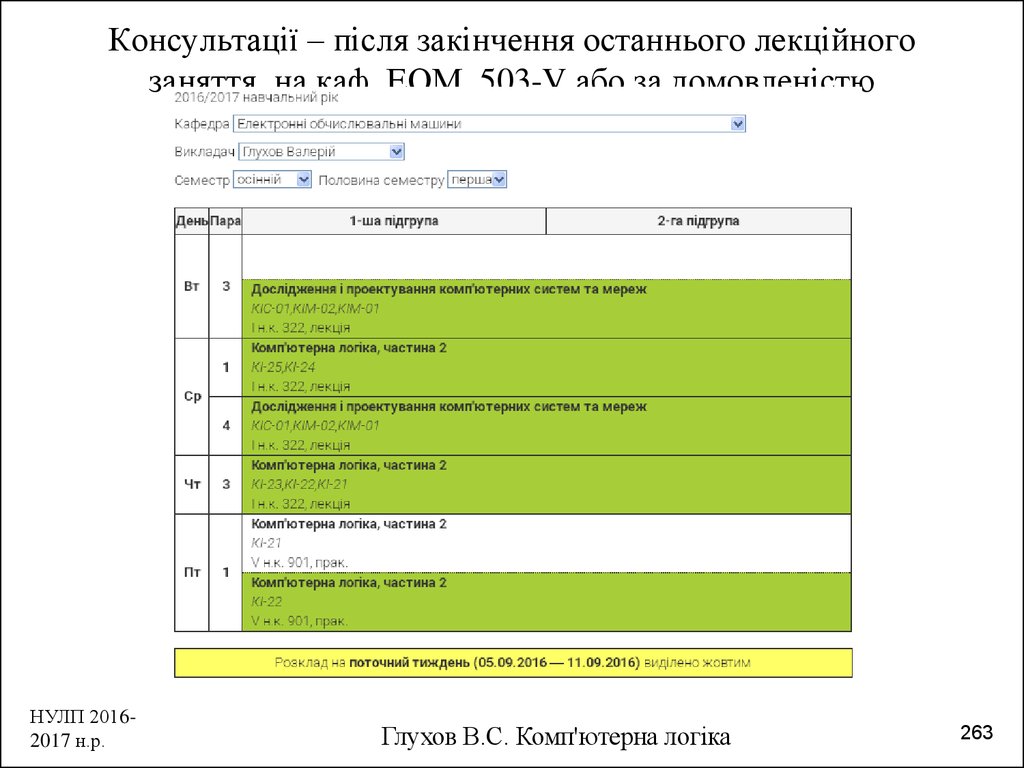

3. Розклад викладача, консультації – Пн, Чт після 2-ої пари, 503-V (каф. ЕОМ)

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

3

4. Комп’ютерна логіка

• ЛОГІКА - наука про закони і різновиди мислення, способи пізнаннята умови істинності знань і суджень

• КОМП’ЮТЕР – пристрій для передавання, зберігання та оброблення

інформації

• КОМП'ЮТЕРНА ЛОГІКА - умовна назва області досліджень, що

ставиться до прикладної логіки, у якій логічні методи застосовуються

для обробки даних і знань у комп'ютерних системах, при створенні

системних програм, що забезпечують функціонування ЕОМ, при

автоматизації програмування й при створенні ЕОМ нових поколінь. К.

л. може виступати як сукупність засобів для імітації пізнавальних

процесів у комп'ютерних системах з підвищеним рівнем

інтелектуальних можливостей, забезпечуючи пошук необхідних знань

для досягнення обраної мети й процес виводу результату, що

відповідає цієї мети.

• КОМП'ЮТЕРНА ЛОГІКА – наука про закони і різновиди мислення,

якими користуються люди коли описують роботу комп’ютерів та

працюють з ними (проектують, ремонтують, обслуговують,

користуються)

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

4

5. Національний університет “Львівська політехніка”

ІАРХ

ІБІД

ІГДГ

ІГСН

ІДН

ІЕПТ

ІНЕМ

ІЕСК

ІІМТ

ІКНІ

ІКТА

МІОК

ІППТ

ІПДО

ІНПП

ІМФН

ІТРЕ

ІХХТ

НУЛП 20162017 н.р.

Архітектури

Будівництва та інженерії довкілля

Геодезії

Гуманітарних та соціальних наук

Дистанційного навчання

Екології, природоохоронної діяльності та туризму ім. В’ячеслава

Чорновола

Економіки і менеджменту

Енергетики та систем керування

Інженерної механіки та транспорту

Комп'ютерних наук та інформаційних технологій

Комп'ютерних технологій, автоматики та метрології

Міжнародний інститут освіти, культури та зв’язків з діаспорою

Підприємництва та перспективних технологій

Післядипломної освіти

Права та психології

Прикладної математики та фундаментальних наук

Телекомунікацій, радіоелектроніки та електронної техніки

Хімії та хімічних технологій

Глухов В.С. Комп'ютерна логіка

5

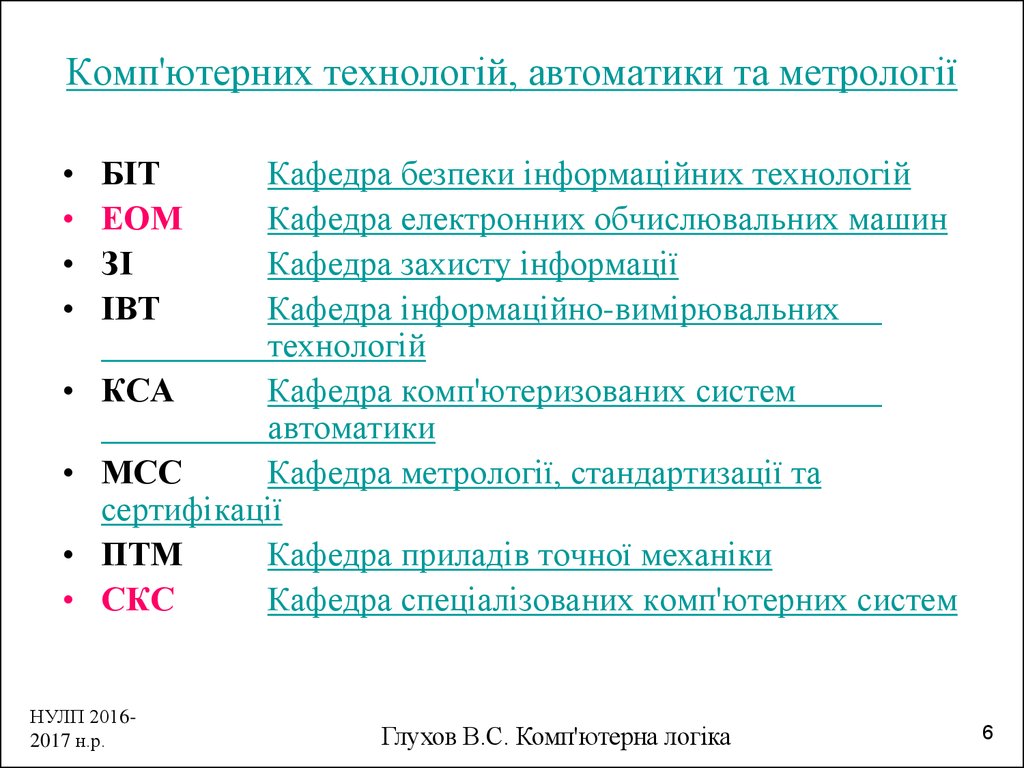

6. Комп'ютерних технологій, автоматики та метрології

БІТ

ЕОМ

ЗІ

ІВТ

Кафедра безпеки інформаційних технологій

Кафедра електронних обчислювальних машин

Кафедра захисту інформації

Кафедра інформаційно-вимірювальних

технологій

КСА

Кафедра комп'ютеризованих систем

автоматики

МСС

Кафедра метрології, стандартизації та

сертифікації

ПТМ

Кафедра приладів точної механіки

СКС

Кафедра спеціалізованих комп'ютерних систем

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

6

7. Кафедри ЕОМ та СКС

• Бакалаврат (каф. ЕОМ та СКС) Комп’ютерна інженерія• Магістри (спеціалізації каф. ЕОМ)

– Комп’ютерні системи та мережі

– Кіберфізичні системи

– Системне програмування

• Магістри (спеціалізація каф. СКС)

– Спеціалізовані комп’ютерні системи

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

7

8. Структура семестру

• 16 навчальних тижнів (16 лекцій, 8практичних)

• Заліковий тиждень

• Сесія (2 тижні)

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

8

9. Державна оцінка (залік)

• 1. За результатами семестрової контрольноїроботи

• 2а. Оцінка на комісії

– або

• 2б. Оцінка за результатами повторного

вивчення курсу

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

9

10. Стандартні вимоги до відповідей на заліках та іспитах

• Повинна бути дана відповідь на усі питаннябілету

• Під час підготовки до відповіді нічим не

можна користуватися

• Під час підготовки до відповіді ні с ким не

можна перемовлятися та обмінюватися

інформацією

• Для допуску до сесії потрібно виконати

навчальний план

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

10

11. Виконання навчального плану

• Студент погоджується самостійно опрацювати деякіпитання учбового плану

• Здана розрахункова робота (є оцінка)

• Виконано програму практичних занять

• Написано усі 16 лекційних контрольних робіт

• Дано відповідь на усі 10 питань семестрової контрольної

роботи

• Є конспект лекцій (приблизно 5 сторінок на лекцію)

• Правильно дано відповіді на усі питання тестів до 1-ої

частини Комп’ютерної логіки (1-ий курс) у ВНС

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

11

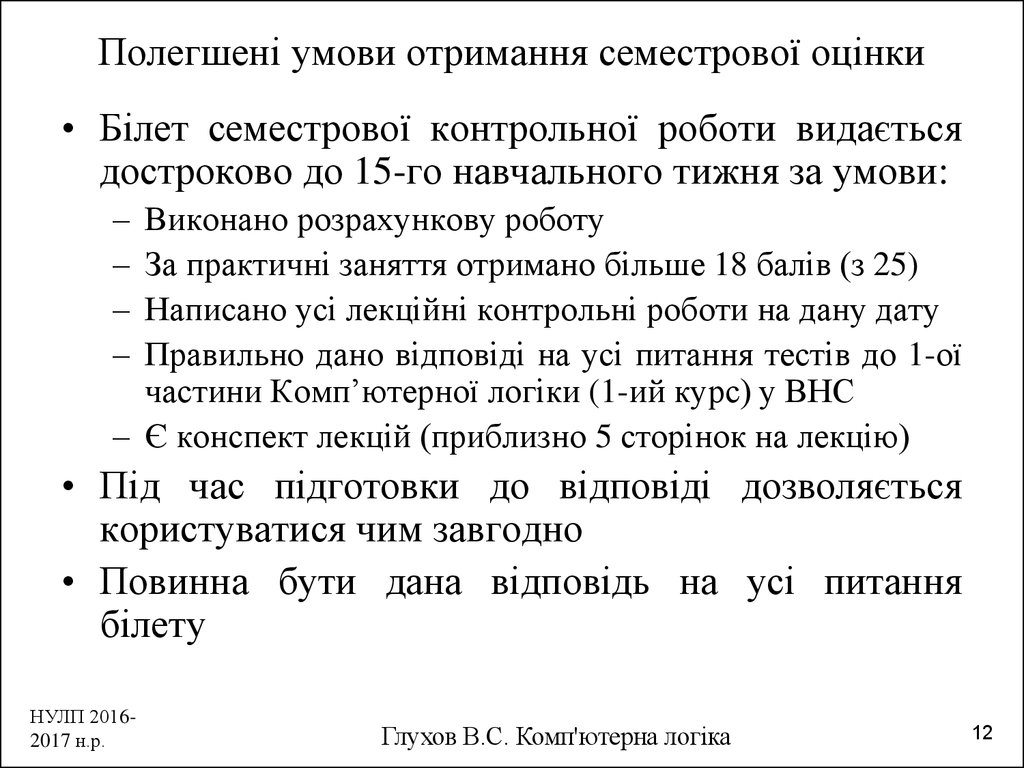

12. Полегшені умови отримання семестрової оцінки

• Білет семестрової контрольної роботи видаєтьсядостроково до 15-го навчального тижня за умови:

–

–

–

–

Виконано розрахункову роботу

За практичні заняття отримано більше 18 балів (з 25)

Написано усі лекційні контрольні роботи на дану дату

Правильно дано відповіді на усі питання тестів до 1-ої

частини Комп’ютерної логіки (1-ий курс) у ВНС

– Є конспект лекцій (приблизно 5 сторінок на лекцію)

• Під час підготовки до відповіді дозволяється

користуватися чим завгодно

• Повинна бути дана відповідь на усі питання

білету

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

12

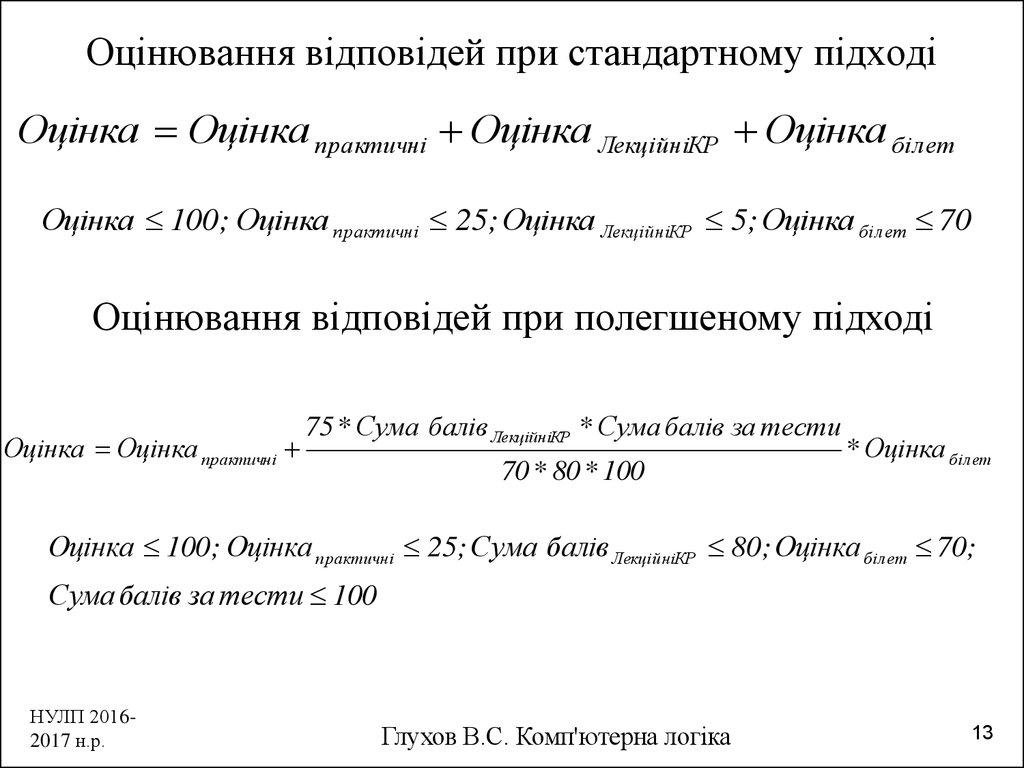

13. Оцінювання відповідей при стандартному підході

Оцінка Оцінка практичні Оцінка ЛекційніКР Оцінка білетОцінка 100; Оцінка практичні 25; Оцінка ЛекційніКР 5; Оцінка білет 70

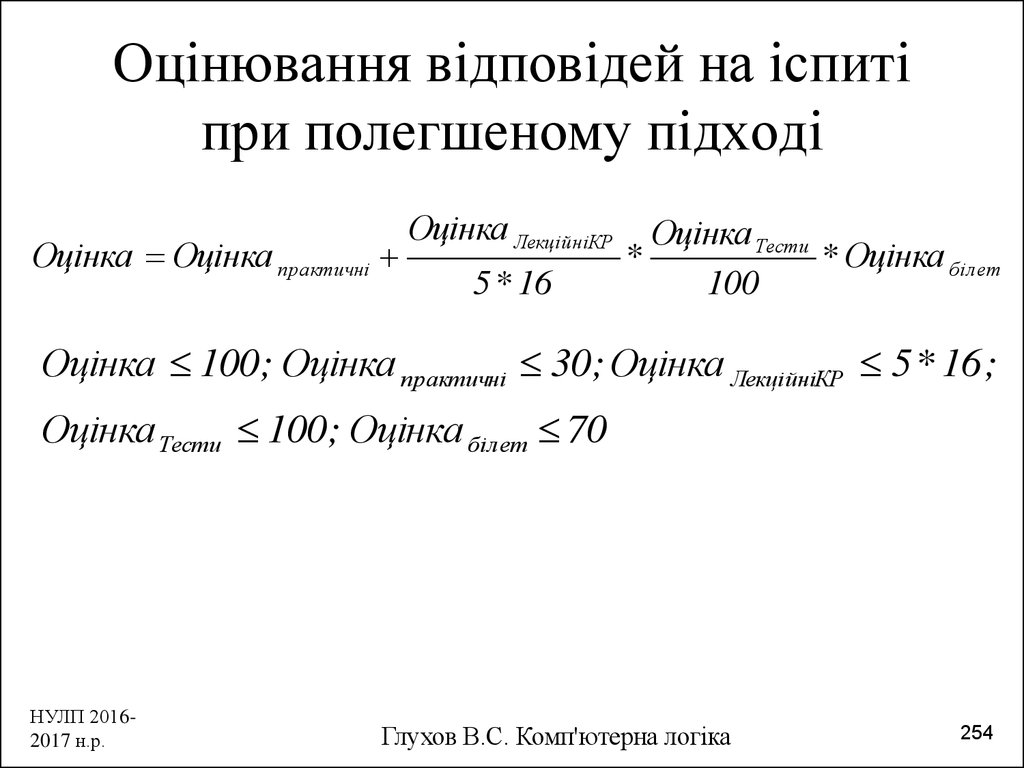

Оцінювання відповідей при полегшеному підході

Оцінка Оцінка практичні

75 * Сума балів ЛекційніКР * Сума балів за тести

70 * 80 * 100

* Оцінка білет

Оцінка 100; Оцінка практичні 25; Сума балів ЛекційніКР 80; Оцінка білет 70;

Сума балів за тести 100

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

13

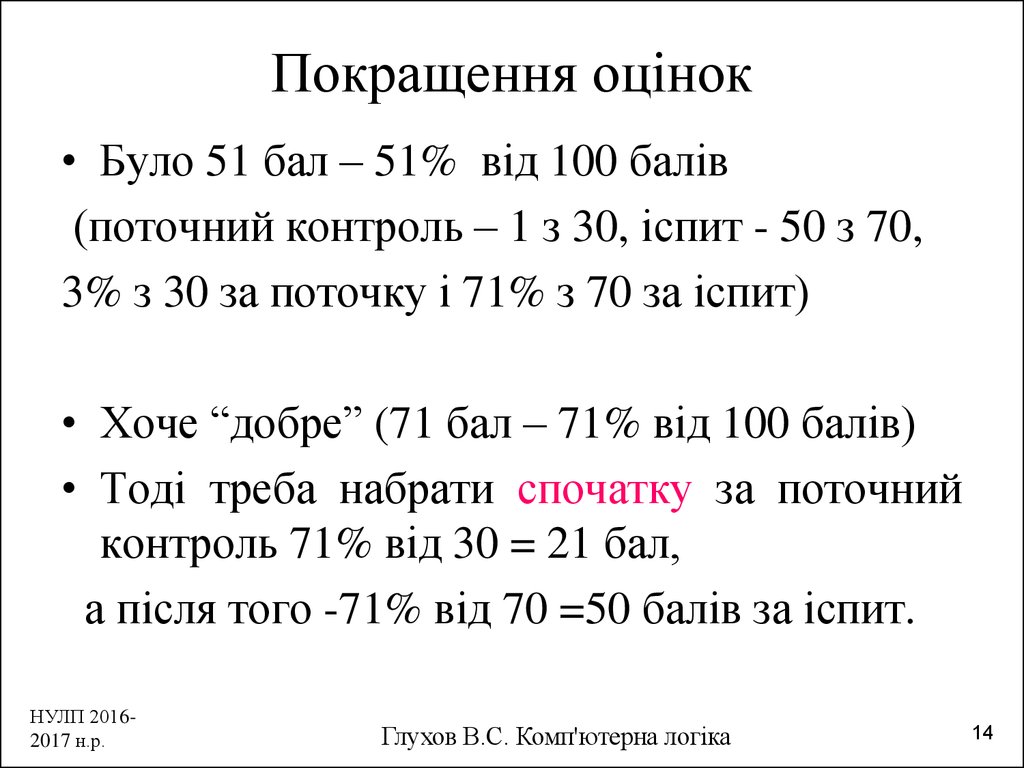

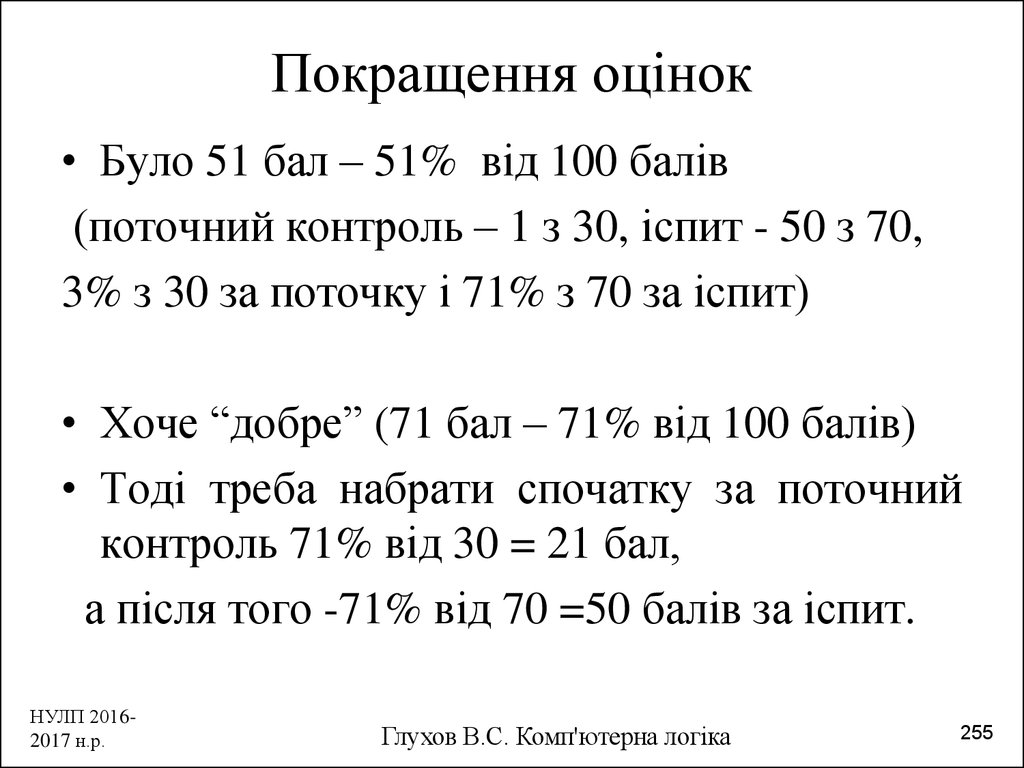

14. Покращення оцінок

• Було 51 бал – 51% від 100 балів(поточний контроль – 1 з 30, іспит - 50 з 70,

3% з 30 за поточку і 71% з 70 за іспит)

• Хоче “добре” (71 бал – 71% від 100 балів)

• Тоді треба набрати спочатку за поточний

контроль 71% від 30 = 21 бал,

а після того -71% від 70 =50 балів за іспит.

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

14

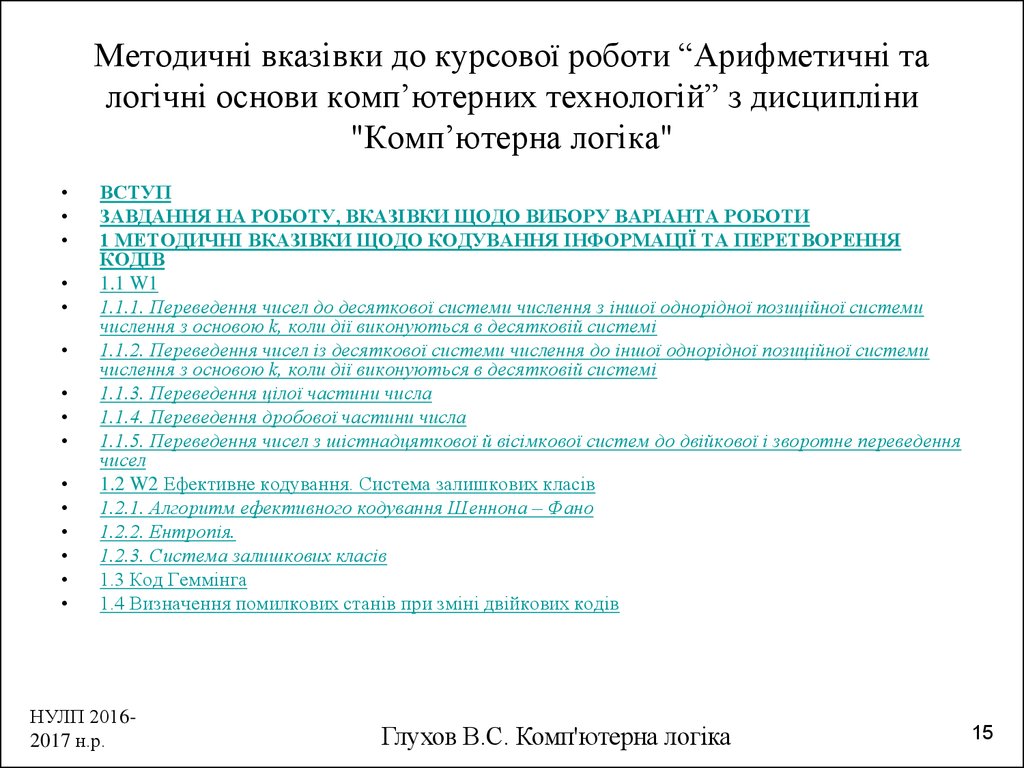

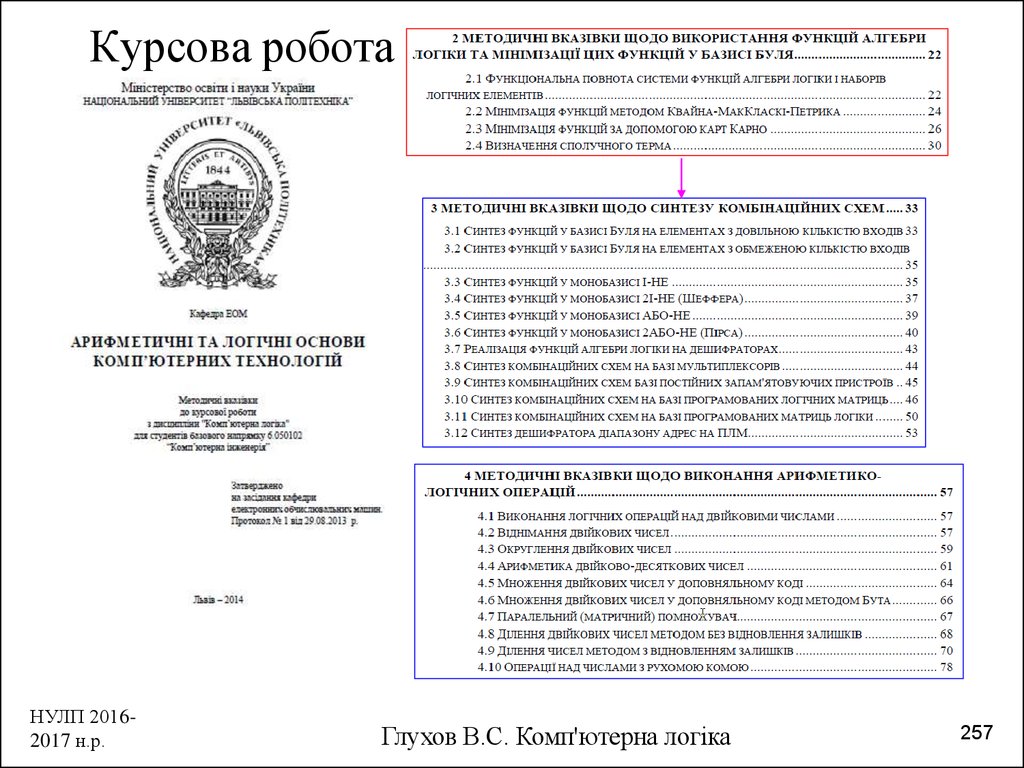

15. Методичні вказівки до курсової роботи “Арифметичні та логічні основи комп’ютерних технологій” з дисципліни "Комп’ютерна логіка"

Методичні вказівки до курсової роботи “Арифметичні талогічні основи комп’ютерних технологій” з дисципліни

"Комп’ютерна логіка"

ВСТУП

ЗАВДАННЯ НА РОБОТУ, ВКАЗІВКИ ЩОДО ВИБОРУ ВАРІАНТА РОБОТИ

1 МЕТОДИЧНІ ВКАЗІВКИ ЩОДО КОДУВАННЯ ІНФОРМАЦІЇ ТА ПЕРЕТВОРЕННЯ

КОДІВ

1.1 W1

1.1.1. Переведення чисел до десяткової системи числення з іншої однорідної позиційної системи

числення з основою k, коли дії виконуються в десятковій системі

1.1.2. Переведення чисел із десяткової системи числення до іншої однорідної позиційної системи

числення з основою k, коли дії виконуються в десятковій системі

1.1.3. Переведення цілої частини числа

1.1.4. Переведення дробової частини числа

1.1.5. Переведення чисел з шістнадцяткової й вісімкової систем до двійкової і зворотне переведення

чисел

1.2 W2 Ефективне кодування. Система залишкових класів

1.2.1. Алгоритм ефективного кодування Шеннона – Фано

1.2.2. Ентропія.

1.2.3. Система залишкових класів

1.3 Код Геммінга

1.4 Визначення помилкових станів при зміні двійкових кодів

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

15

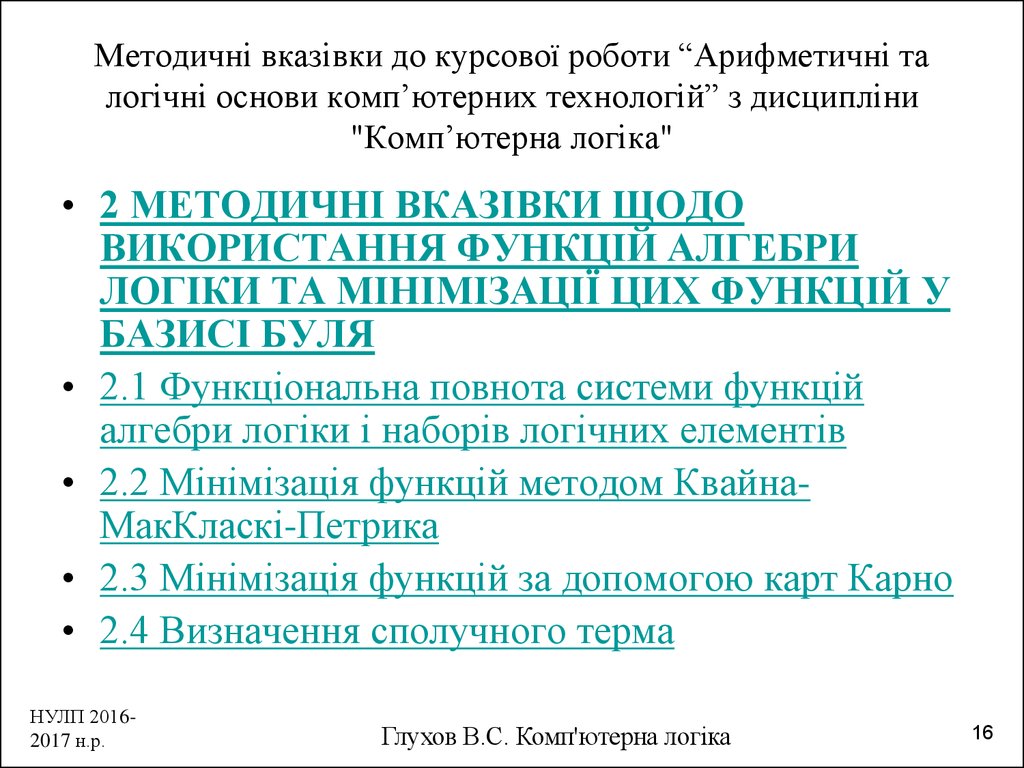

16. Методичні вказівки до курсової роботи “Арифметичні та логічні основи комп’ютерних технологій” з дисципліни "Комп’ютерна логіка"

Методичні вказівки до курсової роботи “Арифметичні талогічні основи комп’ютерних технологій” з дисципліни

"Комп’ютерна логіка"

• 2 МЕТОДИЧНІ ВКАЗІВКИ ЩОДО

ВИКОРИСТАННЯ ФУНКЦІЙ АЛГЕБРИ

ЛОГІКИ ТА МІНІМІЗАЦІЇ ЦИХ ФУНКЦІЙ У

БАЗИСІ БУЛЯ

• 2.1 Функціональна повнота системи функцій

алгебри логіки і наборів логічних елементів

• 2.2 Мінімізація функцій методом КвайнаМакКласкі-Петрика

• 2.3 Мінімізація функцій за допомогою карт Карно

• 2.4 Визначення сполучного терма

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

16

17. Робочий журнал

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

17

18. Відробка пропущених лекційних контрольних робіт

• Копія конспекту за пропущену лекцію(якщо у журналі є порожня клітинка або Н)

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

18

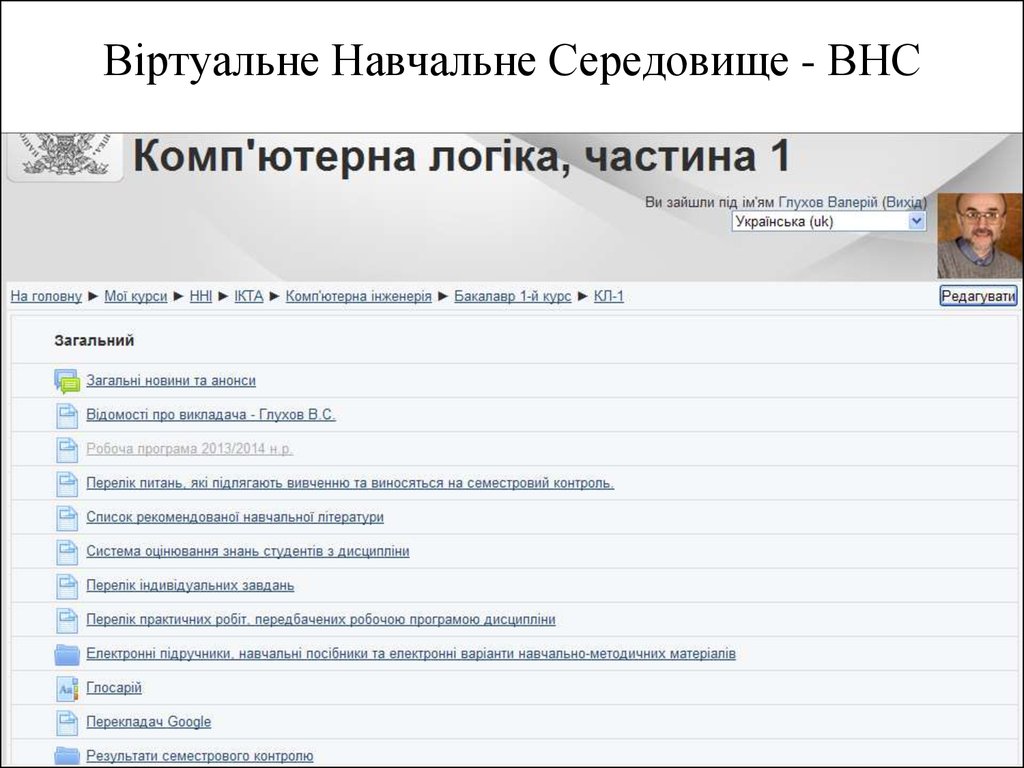

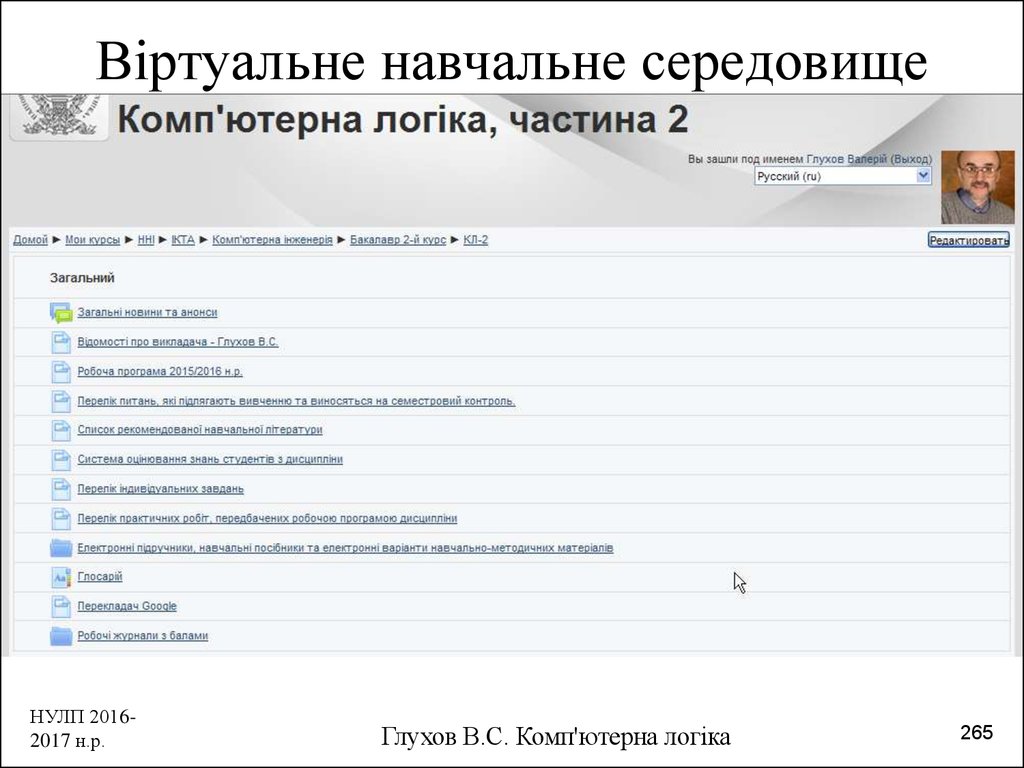

19. Віртуальне Навчальне Середовище - ВНС

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

19

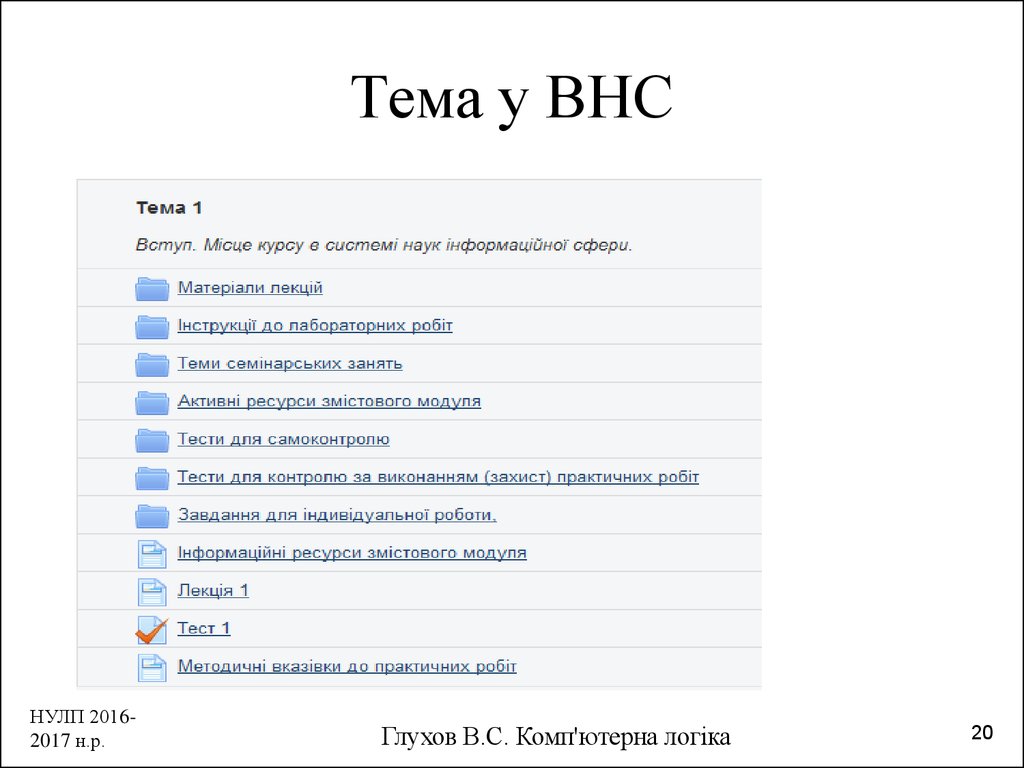

20. Тема у ВНС

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

20

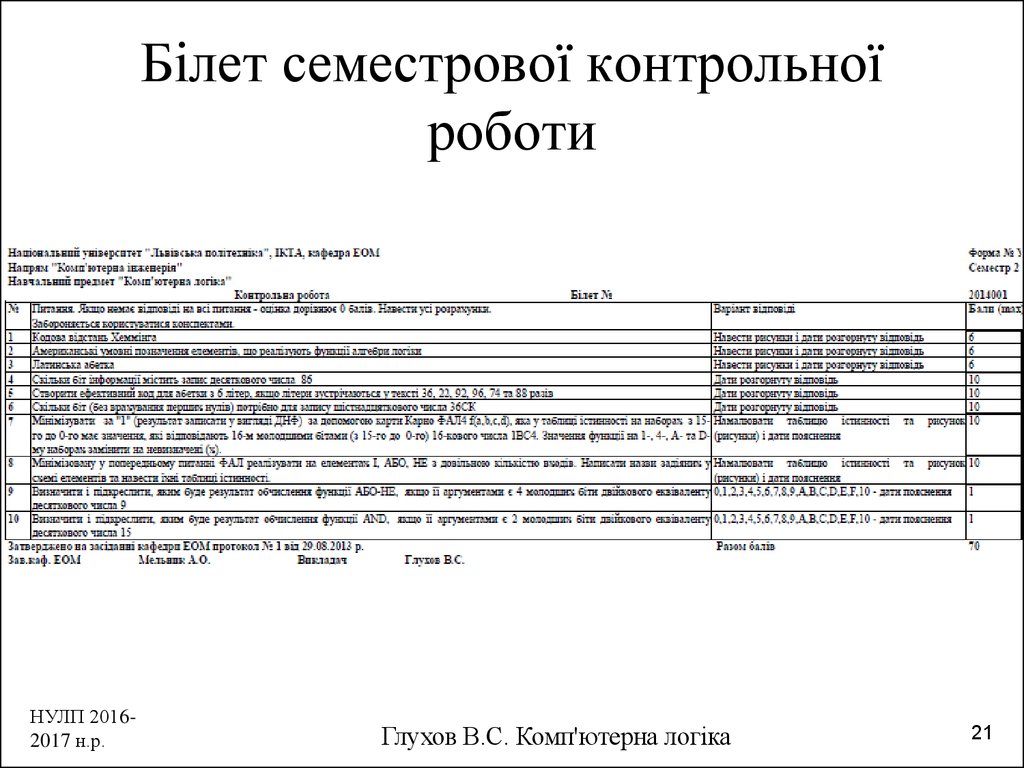

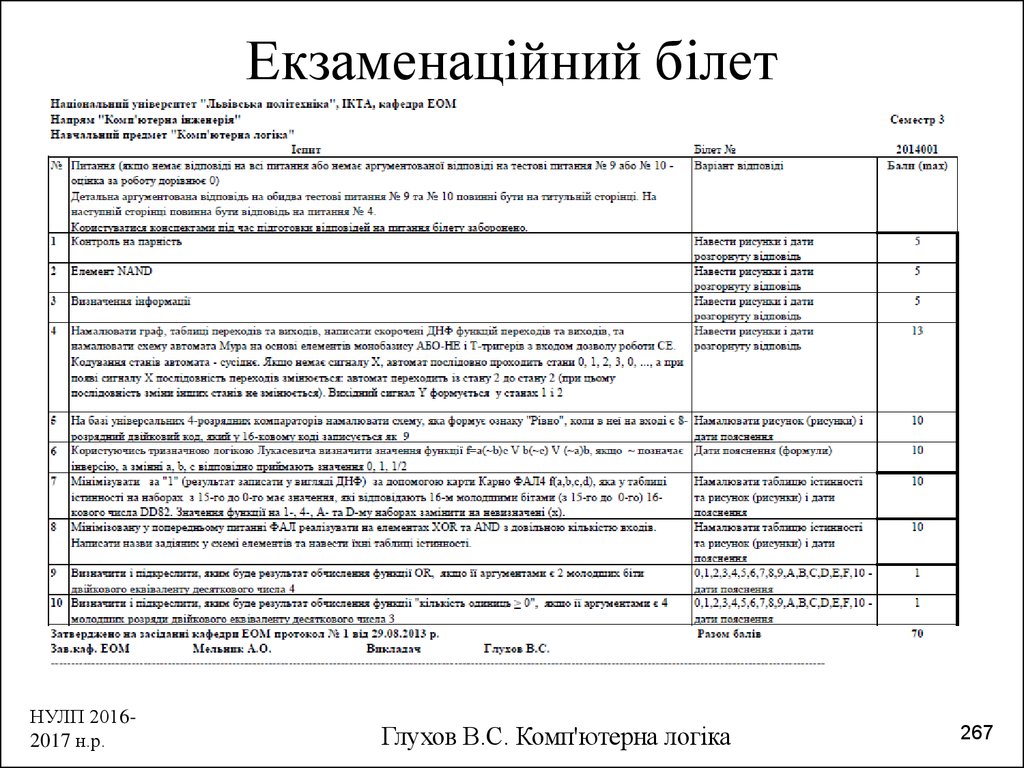

21. Білет семестрової контрольної роботи

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

21

22. Конспект

• Поле – для важливих приміток (дата, №лекції, № питання, NB, …)

• Основна частина – для скороченого запису

помилок, які робить викладач

– Графічна частина

– Текстові пояснення

• Знизу - № сторінки, Прізвище І.П.

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

22

23. Навички (компетенції) випускників

• конвертувати академічні знання і навички в результатипрактичного вирішення технічних задач;

• вирішувати складні задачі в галузі комп'ютерної техніки

та ефективно адаптуватися у швидко мінливому

середовищі;

• використовувати систематичний і методичний стиль

роботи;

• застосовувати правильну термінологію і позначення як у

письмовій формі так і в усній;

• обговорювати основні теорії та методи аналізу і обробки

аналогових і цифрових сигналів з використанням

правильної термінології;

• застосувати знання математики та фізики (у тому числі

теорії ймовірності, статистики та дискретної математики,

діференціального та інтегрального числення), інші

досягнення науки і техніки;

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

23

24. Навички (компетенції) випускників

• визначити, формулювати та проводити дослідження,направлені на вирішення інженерної завдачі за допомогою

відповідного огляду літератури, робити обгрунтовані

висновки;

• планувати і проводити експерименти та тести, а також

аналізувати та інтерпретувати отримані експериментальні

дані та робити обгрунтовані висновки;

• критично мислити, аналізувати і приймати рішення, які

належним чином враховують глобальні проблеми в

–

–

–

–

–

НУЛП 20162017 н.р.

бізнесі,

етиці,

моралі,

суспільстві і

навколишньому середовищі;

Глухов В.С. Комп'ютерна логіка

24

25. Навички (компетенції) випускників

• проектувати комп’ютерні системи, компоненти абопроцеси для задоволення бажаних потреб в рамках

реалістичних обмежень:

–

–

–

–

–

–

–

–

НУЛП 20162017 н.р.

економічних,

екологічних,

соціальних,

політичних,

етичних,

здоров'я та безпеки,

технологічності і

стійкості;

Глухов В.С. Комп'ютерна логіка

25

26. Навички (компетенції) випускників

• розробляти та реалізовувати апаратні засоби абопрограмне забезпечення системи вбудованих компонентів

для задоволення бажаних потреб та вимог, у тому числі:

–

–

–

–

–

–

–

–

НУЛП 20162017 н.р.

продуктивності,

економічної ефективності,

безпеки,

маса-габаритних характеристик,

часу,

споживання,

ефективності і

ергономічності та ефективності користувальницьких інтерфейсів;

Глухов В.С. Комп'ютерна логіка

26

27. Навички (компетенції) випускників

• розуміти вплив технічних рішень в соціальному контекстіі бути в змозі ефективно реагувати на потреби сталого

розвитку суспільства;

• бути в змозі оцінити можливості та обмеження теорій та

методів, застосовуваних на практиці;

• працювати в команді;

• ефективно працювати в рамках міждисциплінарних

команд, у тому числі вміння працювати з колегами для

того, щоб розробити і побудувати комплексну

комп’ютерну систему;

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

27

28. Навички (компетенції) випускників

• розуміти фундаментальні засади ефективного управління проектами;• визначити, формулювати і вирішувати технічні задачі;

• обговорювати концепції створення комп’ютерних системи та мереж,

особливостей використання Інтернет-технологій;

• визначати необхідність, проектувати, впроваджувати та оцінювати

життєздатність рішень для вбудованих комп’ютерних систем, що

працюють у реальному часі;

• виявляти, формулювати, аналізувати і створювати інженерні рішення

з використанням відповідних сучасних технологій, методів та

інструментів, в тому числі і з міжперсональним спілкуванням;

• доводи доцільність та правильність обраних теорій, методів, дизайну

та реалізацій;

• пояснювати та відстоювати методичний та системний підхід до

проектування;

• аргументувати вибрані рішення та пояснювати їхні обмеження;

• оцінювати сильні і слабкі сторони різних рішень і тестів;

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

28

29. Навички (компетенції) випускників

• підтримувати проектування для забезпеченням заданоїфункціональності

за

допомогою

розрахунків,

моделювання та імплементації результатів моделювання;

• комбінувати

варіанти

об'єднання

апаратного

і

програмного забезпечення для отримання бажаної

функціональності комп’ютерної системи;

• комбінувати загальнотехнічні та специфічні рішення при

роботі з комп’ютерними системами;

• представляти

результати

досліджень

у

вигляді

презентацій, публікації та / або доповідях на конференціях

та семінарах;

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

29

30. Навички (компетенції) випускників

• демонструвати розуміння та дотримуватися професійнихта етичних обов'язків;

• мати уявлення, розуміти необхідність та дотримуватися

особистої чесності, професійної етики та культурної

свідомості;

• розуміти і нести професійну, етичну і моральну

відповідальність;

• ефективно спілкуватися та обмінюватися технічною

інформацією в різних форматах і різними способами

(усно, письмово, електронними засобами) як із

спеціалістами так і з неспеціалістами в галузі

Комп’ютерної інженерії;

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

30

31. Навички (компетенції) випускників

визначити власні потреби в навчанні і планувати та здійснювати своє власне

навчання в різних середовищах навчання;

самостійно набувати ширшої освіти, необхідної для розуміння впливу

інженерних рішень в

–

–

–

–

глобальному,

економічному,

екологічному та

соціальному значеннях;

визнавати необхідність і здатність займатися самоосвітою протягом усього

життя;

розвиватися і підтримувати на належному сучасному рівні необхідні знання, а

також відповідний рівень компетентності в сучасних наукових технологіях

так, щоб бути в змозі формулювати і вирішувати нові технічні задачі і далі

розвивати і підтримувати свої професійні навички впродовж усієї кар'єри;

розуміти необхідність, прагнути до безперервного навчання, бути

винахідливим і здатним прийняти глобальні виклики та використати всі

можливості, щоб зробити позитивний вплив на суспільство;

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

31

32. Навички (компетенції) випускників

• демонструвати знання сучасних проблем;• розуміти і використовувати методи, навички та сучасні

інженерні інструменти необхідні для інженерної практики

з відповідними міркуваннями щодо забезпечення:

–

–

–

–

–

НУЛП 20162017 н.р.

громадського здоров'я та безпеки,

культурних,

соціальних,

моральних,

екологічних обмежень.

Глухов В.С. Комп'ютерна логіка

32

33. Спеціальні навички (компетенції) випускників

вбудовані комп'ютерні системи в споживчих товарах;

вбудовані комп'ютерні системи медичних пристроїв;

системи керування для автомобілів, літаків і поїздів;

широке коло додатків в областях:

– телекомунікацій,

– фінансових операцій,

– інформаційних систем

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

33

34. Спеціальні навички (компетенції) випускників

апаратно-програмні інтерфейси;

проектування НВІС;

проектування цифрових, аналогових та змішаних схем;

автоматизація проектування;

тестування та діагностика;

комп’ютерні мережі;

вбудовані комп’ютерні системи;

розробка програмного забезпечення для широкого кола

задач;

• кібер-фізичні системи;

• мови програмування: JAVA, C++, C, Assembly, VHDL,

Matlab, Python;

• операційні системи Android, iOS, UNIX, Linux, Windows.

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

34

35. Застосування придбаних навичок в проектуванні.

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

35

36. Вбудовані ЕОМ

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

36

37.

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

37

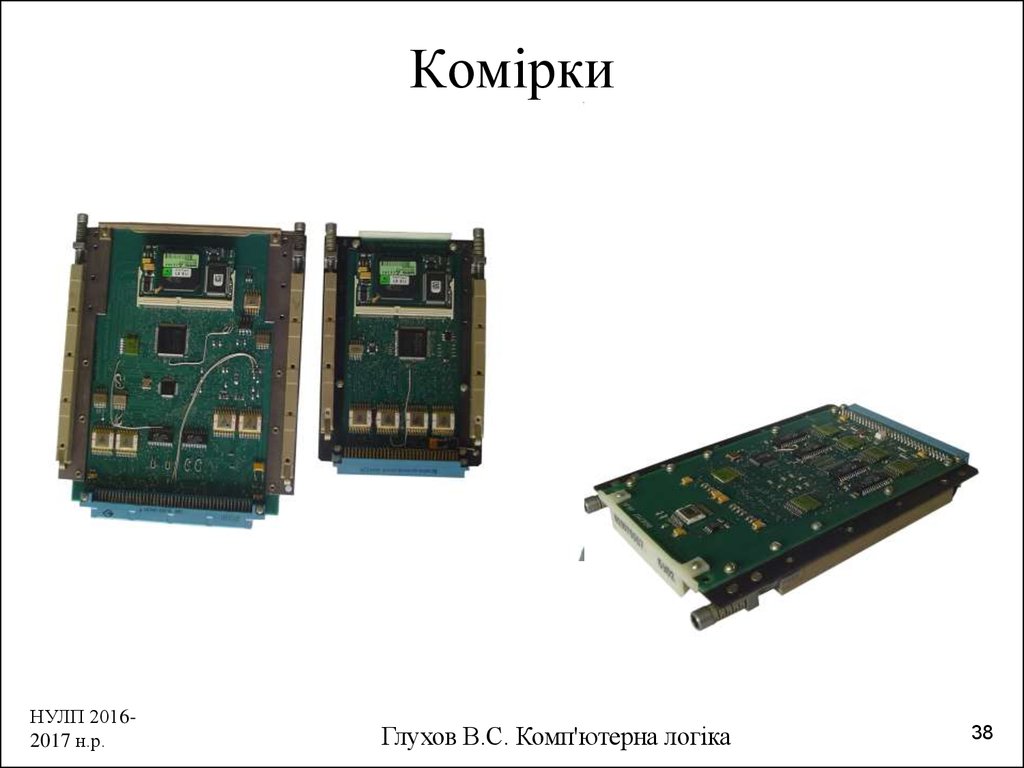

38. Комірки

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

38

39. (Львівський центр Інституту космічних досліджень НАН та ДКА України) Супутник Січ-2 на етапі відлагодження та тестування

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

39

40. Блоки і комірки для Січ-2 (Львівський центр Інституту космічних досліджень НАН та ДКА України)

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

40

41. Вбудована в атомну елекростанцію комп’ютерна система (НВО “Радій”, м. Кіровоград, 2010 р.)

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

41

42.

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

42

43.

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

43

44.

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

44

45.

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

45

46. У Львові 150 IT-компаній (Інформаційні Технології) 25 найбільших IT-компаній України http://jobs.dou.ua/top25/

№Компания

Δ Jul'15 /

Jan'16

Технические

специалисты

Вакансии

в Украине

1

EPAM Киев, Харьков, Львов, Днепропетровск, Винница

+500

3800

345

2

SoftServe Киев, Харьков, Львов, Днепропетровск, Ровно, ИваноФранковск, Черновцы

+44

3891

484

4

GlobalLogic Киев, Харьков, Львов, Николаев

+111

2360

174

5

Ciklum Киев, Харьков, Львов, Днепропетровск, Одесса, Винница

+44

2029

224

9

ELEKS Львов, Ивано-Франковск, Тернополь

-3

640

21

11

DataArt Киев, Харьков, Львов, Днепропетровск, Одесса, Херсон

+47

700

185

12

Lohika Systems Киев, Львов, Одесса

+8

588

20

14

ISD* Львов, Днепропетровск, Бердянск, Запорожье

-34

680

30

15

GeeksForLess Inc. Киев, Львов, Николаев

+2

550

15

17

Sigma Software Киев, Харьков, Львов, Одесса

+73

492

75

21

Plarium Киев, Харьков, Львов, Одесса

-40

145

48

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

46

47. Комп’ютерна логіка і „Комп’ютерна інженерія”

Архітектуракомп'ютерів

Комп’ютерні

системи

Комп'ютерна

схемотехніка

Теорія

алгоритмів

Програмування

Комп’ютерна

логіка

Математика

Фізика

Комп'ютерна

електроніка

НУЛП 20162017 н.р.

Філософія

Глухов В.С. Комп'ютерна логіка

47

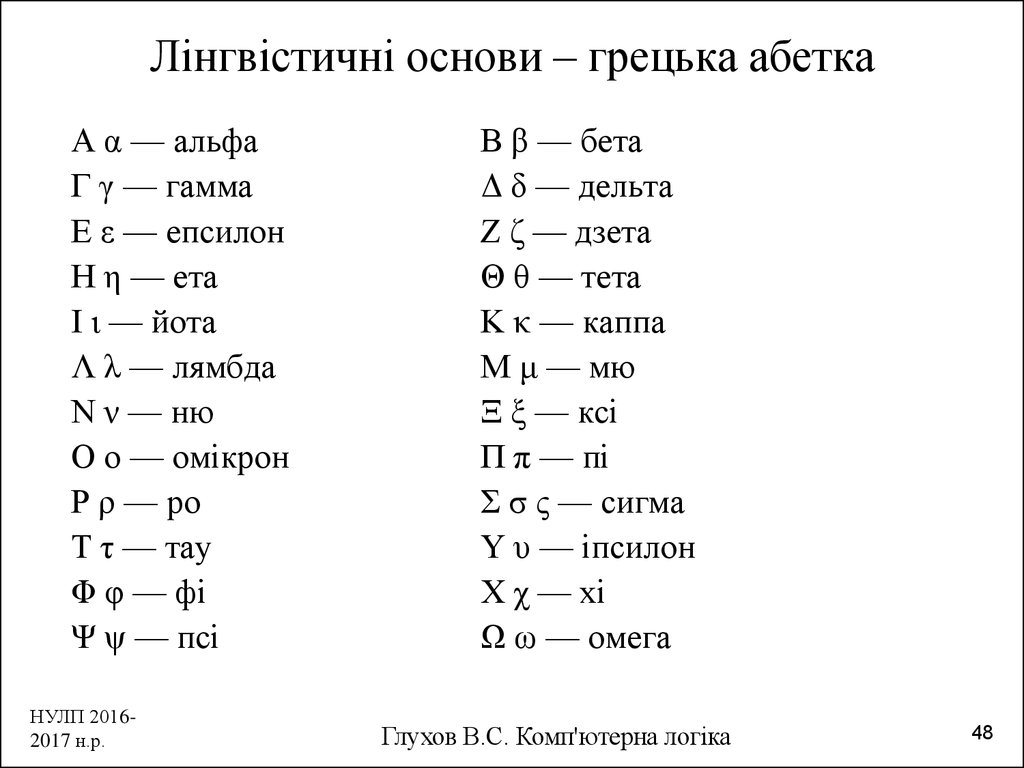

48. Лінгвістичні основи – грецька абетка

Α α — альфаΓ γ — гамма

Ε ε — епсилон

Η η — ета

Ι ι — йота

Λ λ — лямбда

Ν ν — ню

Ο ο — омікрон

Ρ ρ — ро

Τ τ — тау

Φ φ — фі

Ψ ψ — псі

НУЛП 20162017 н.р.

Β β — бета

Δ δ — дельта

Ζ ζ — дзета

Θ θ — тета

Κ κ — каппа

Μ μ — мю

Ξ ξ — ксі

Π π — пі

Σ σ ς — сигма

Υ υ — іпсилон

Χ χ — хі

Ω ω — омега

Глухов В.С. Комп'ютерна логіка

48

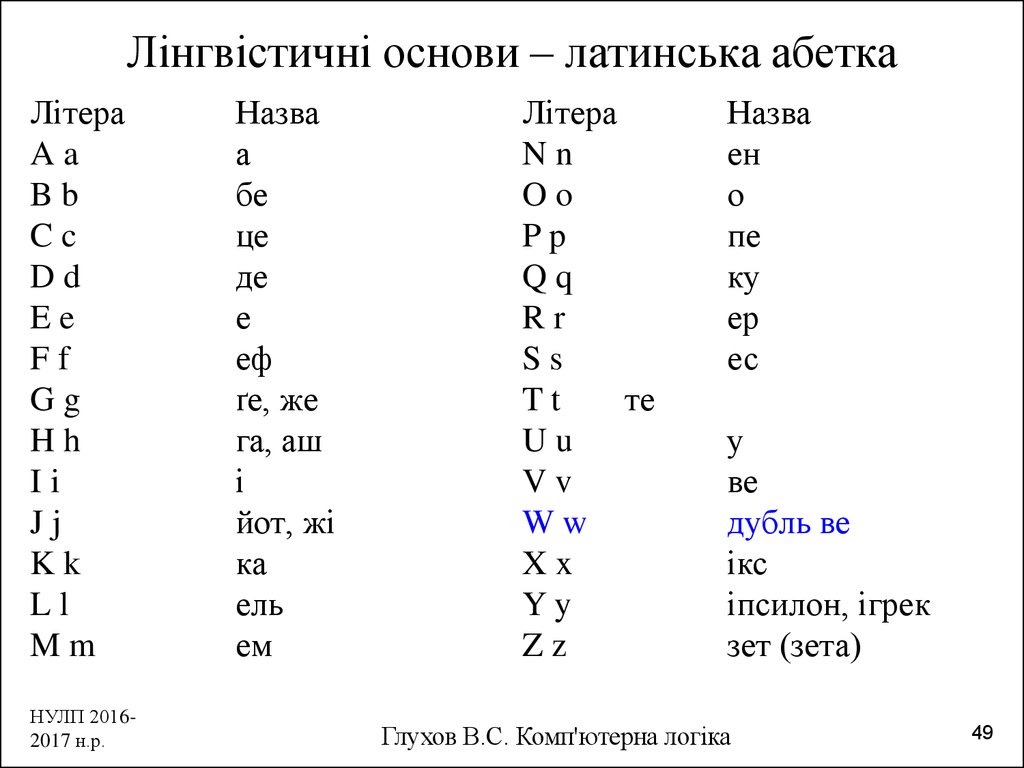

49. Лінгвістичні основи – латинська абетка

ЛітераAa

Bb

Cc

Dd

Ee

Ff

Gg

Hh

Ii

Jj

Kk

Ll

Mm

НУЛП 20162017 н.р.

Назва

а

бе

це

де

е

еф

ґе, же

га, аш

і

йот, жі

ка

ель

ем

Літера

Nn

Oo

Pp

Rr

Ss

Tt

те

Uu

Vv

Ww

Xx

Yy

Zz

Назва

ен

о

пе

ку

ер

ес

у

ве

дубль ве

ікс

іпсилон, ігрек

зет (зета)

Глухов В.С. Комп'ютерна логіка

49

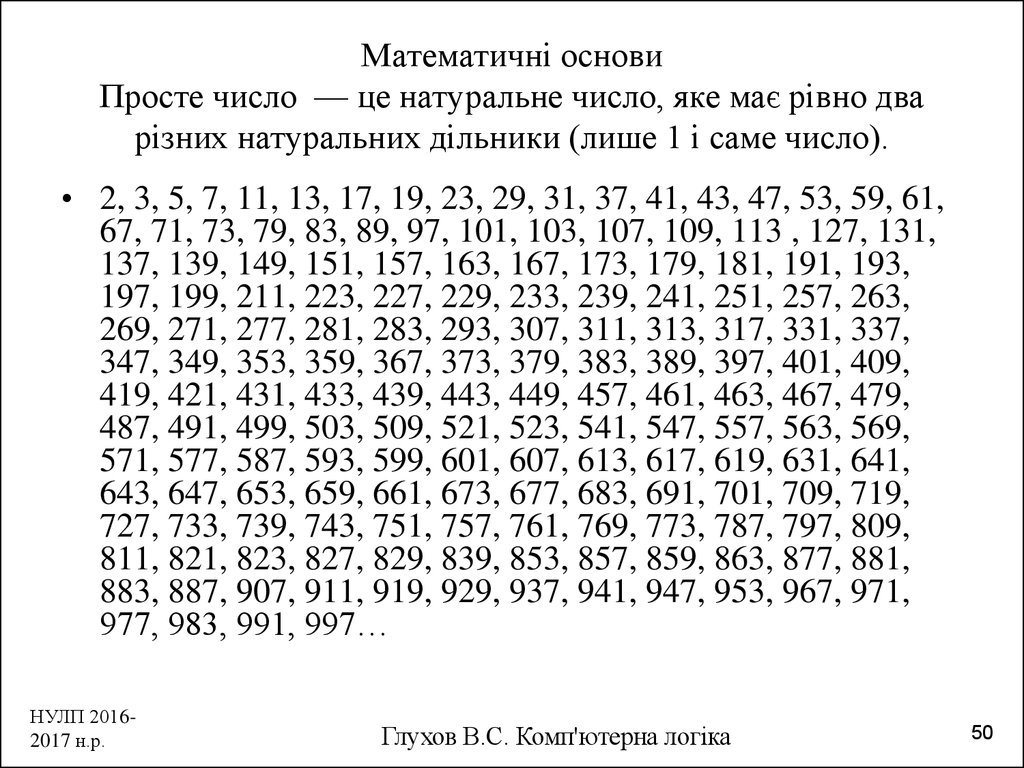

50. Математичні основи Просте число — це натуральне число, яке має рівно два різних натуральних дільники (лише 1 і саме число).

• 2, 3, 5, 7, 11, 13, 17, 19, 23, 29, 31, 37, 41, 43, 47, 53, 59, 61,67, 71, 73, 79, 83, 89, 97, 101, 103, 107, 109, 113 , 127, 131,

137, 139, 149, 151, 157, 163, 167, 173, 179, 181, 191, 193,

197, 199, 211, 223, 227, 229, 233, 239, 241, 251, 257, 263,

269, 271, 277, 281, 283, 293, 307, 311, 313, 317, 331, 337,

347, 349, 353, 359, 367, 373, 379, 383, 389, 397, 401, 409,

419, 421, 431, 433, 439, 443, 449, 457, 461, 463, 467, 479,

487, 491, 499, 503, 509, 521, 523, 541, 547, 557, 563, 569,

571, 577, 587, 593, 599, 601, 607, 613, 617, 619, 631, 641,

643, 647, 653, 659, 661, 673, 677, 683, 691, 701, 709, 719,

727, 733, 739, 743, 751, 757, 761, 769, 773, 787, 797, 809,

811, 821, 823, 827, 829, 839, 853, 857, 859, 863, 877, 881,

883, 887, 907, 911, 919, 929, 937, 941, 947, 953, 967, 971,

977, 983, 991, 997…

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

50

51. Таблиця множення

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

51

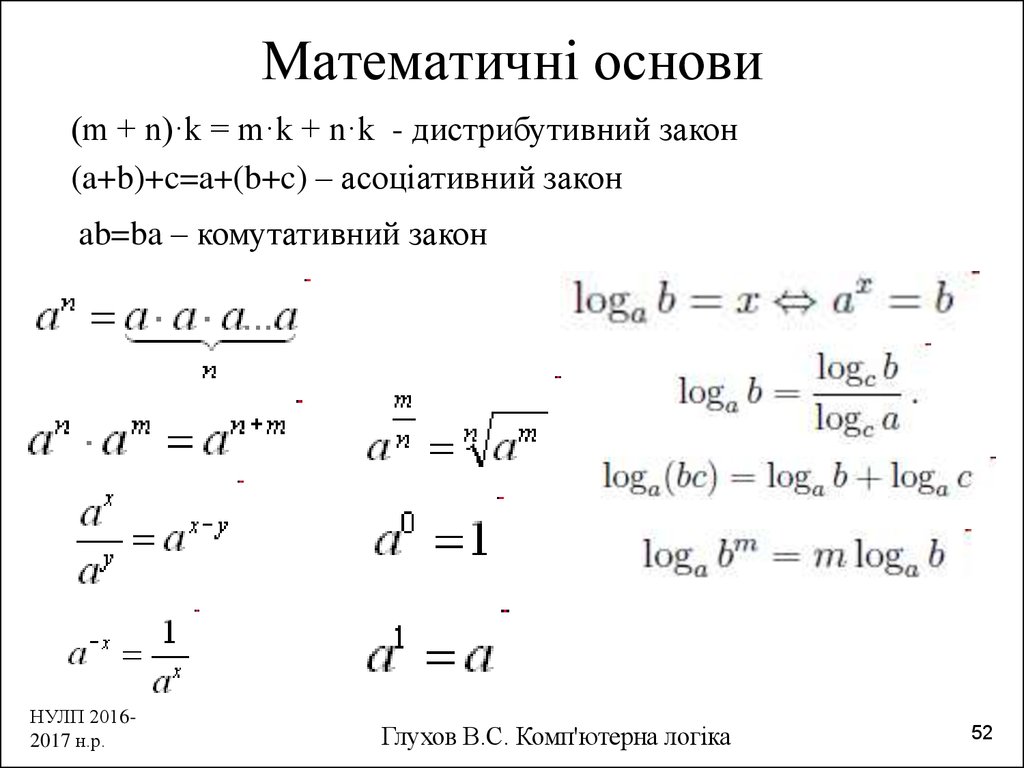

52. Математичні основи

(m + n)·k = m·k + n·k - дистрибутивний закон(a+b)+c=a+(b+c) – асоціативний закон

ab=ba – комутативний закон

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

52

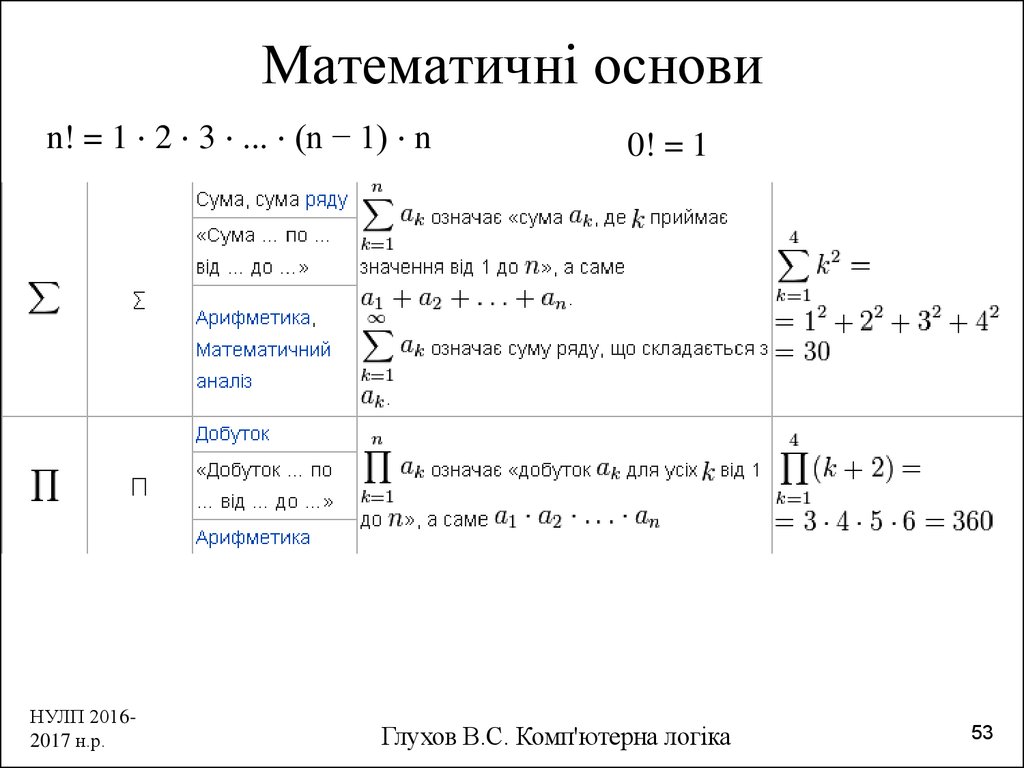

53. Математичні основи

n! = 1 ⋅ 2 ⋅ 3 ⋅ ... ⋅ (n − 1) ⋅ nНУЛП 20162017 н.р.

0! = 1

Глухов В.С. Комп'ютерна логіка

53

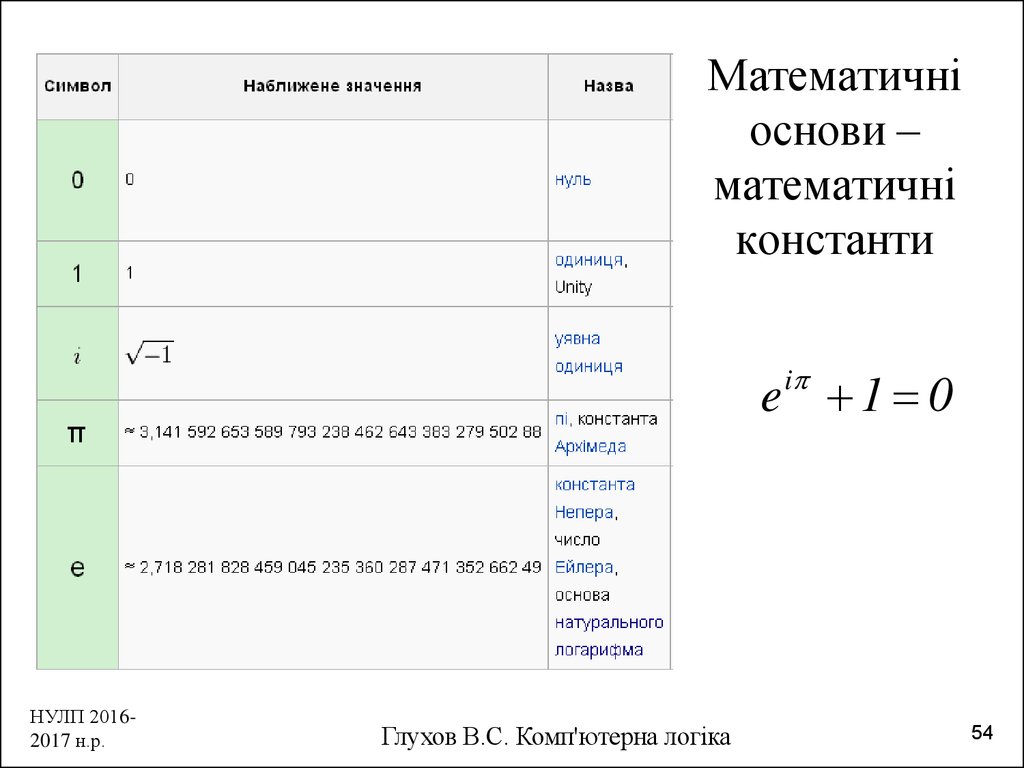

54. Математичні основи – математичні константи

ie 1 0

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

54

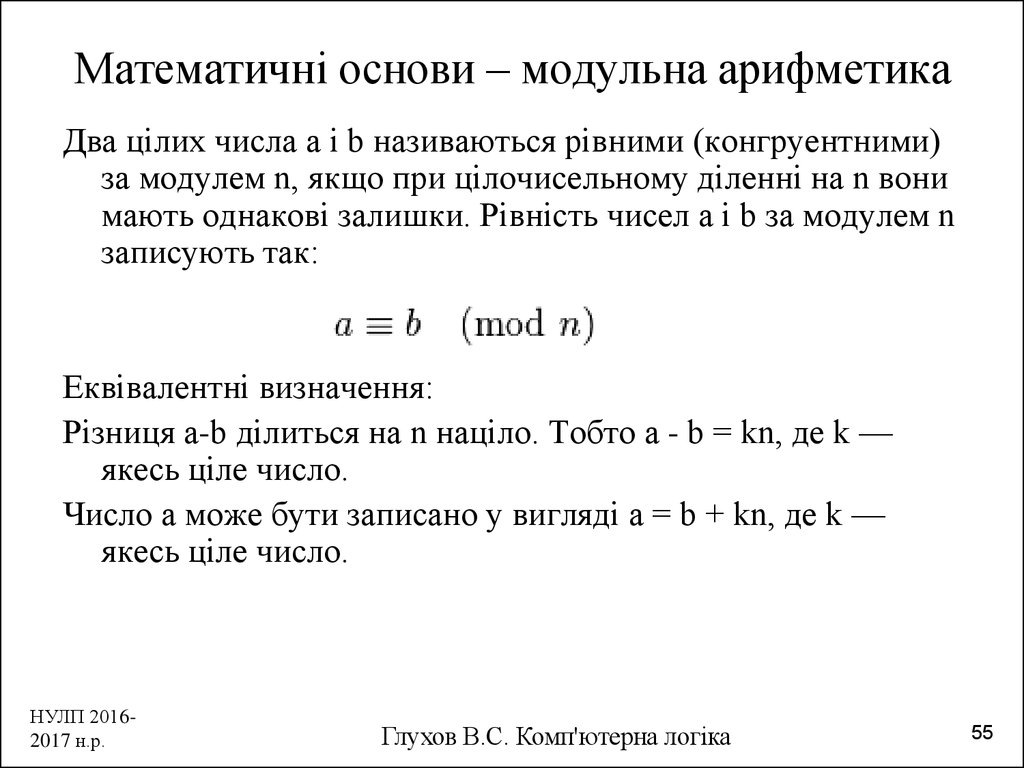

55. Математичні основи – модульна арифметика

Два цілих числа a і b називаються рівними (конгруентними)за модулем n, якщо при цілочисельному діленні на n вони

мають однакові залишки. Рівність чисел a і b за модулем n

записують так:

Еквівалентні визначення:

Різниця a-b ділиться на n націло. Тобто a - b = kn, де k —

якесь ціле число.

Число a може бути записано у вигляді a = b + kn, де k —

якесь ціле число.

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

55

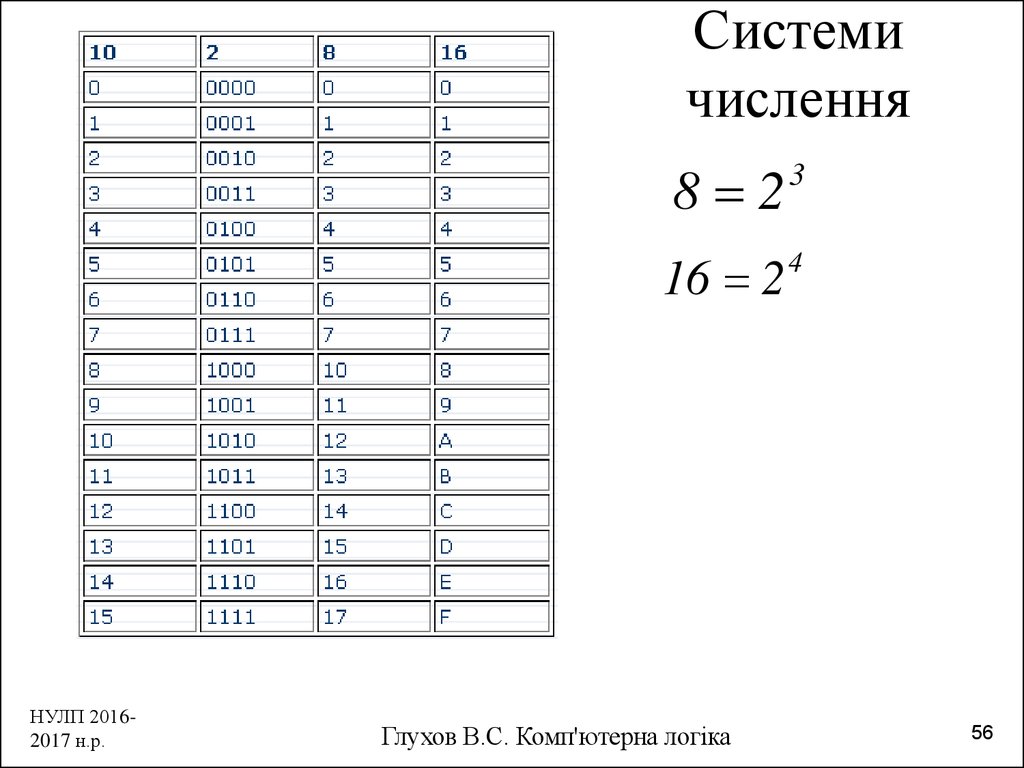

56. Системи числення

8 23

16 2

4

16 2 4

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

56

57. Позиційні системи числення

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

57

58. Степені 2

10-васистема

числення

2n

2-ва система

16-ва

числення

система

числення

1024

512

256

128

64

32

16

8

4

2

1

0,5

0,25

0,125

0,0625

0,03125

0,015625

0,007813

0,003906

0,001953

0,000977

10000000000

1000000000

100000000

10000000

1000000

100000

10000

1000

100

10

1

0,1

0,01

0,001

0,0001

0,00001

0,000001

0,0000001

0,00000001

0,000000001

0,0000000001

n

10

9

8

7

6

5

4

3

2

1

0

-1

-2

-3

-4

-5

-6

-7

-8

-9

-10

НУЛП 20162017 н.р.

400

200

100

80

40

20

10

8

4

2

1

0,8

0,4

0,2

0,1

0,08

0,04

0,02

0,01

0,008

0,004

8-ва

система

числення

Степені 2

2000

1000

400

200

100

40

20

10

4

2

1

0,4

0,2

0,1

0,04

0,02

0,01

0,004

0,002

0,001

0,0004

Глухов В.С. Комп'ютерна логіка

58

59. Фізичні основи

Напруга U (В), струм I (А), потужність P (Вт),опір R (Ом), ємність C (Ф), індуктивність L (Гн)

Закон Ома I = U/R

Потужність P = UI

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

59

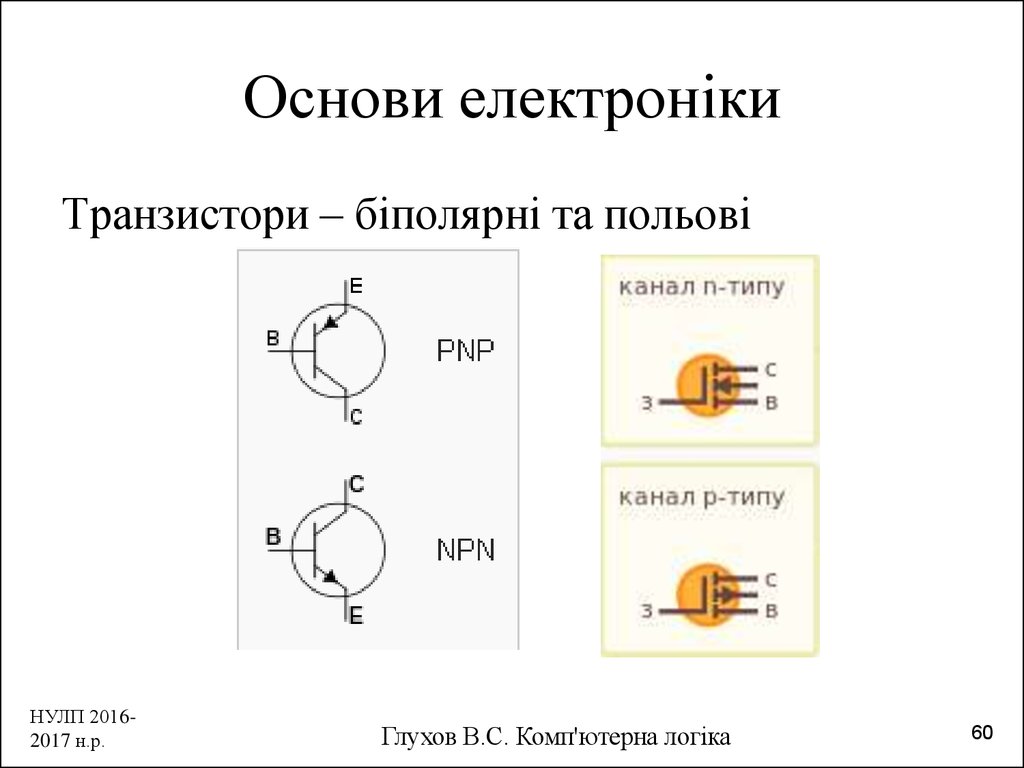

60. Основи електроніки

Транзистори – біполярні та польовіНУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

60

61. Швидкість, продуктивність

• v=F/t (F – шлях, об’єм води, кількістьоперацій, кількість інформації, …)

• v=(Fк-Fп)/(tк-tп)=ΔF/ Δt

• Δt →0 => dt

• v=dF/ dt – перша похідна

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

61

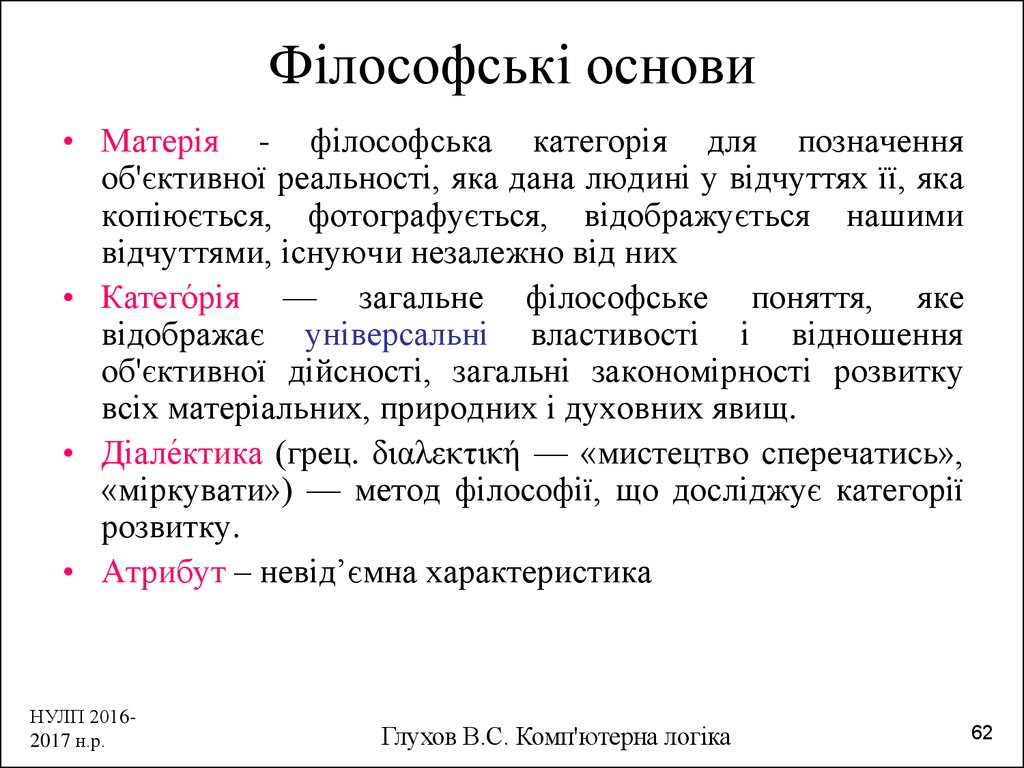

62. Філософські основи

• Матерія - філософська категорія для позначенняоб'єктивної реальності, яка дана людині у відчуттях її, яка

копіюється, фотографується, відображується нашими

відчуттями, існуючи незалежно від них

• Катего́рія — загальне філософське поняття, яке

відображає універсальні властивості і відношення

об'єктивної дійсності, загальні закономірності розвитку

всіх матеріальних, природних і духовних явищ.

• Діале́ктика (грец. διαλεκτική — «мистецтво сперечатись»,

«міркувати») — метод філософії, що досліджує категорії

розвитку.

• Атрибут – невід’ємна характеристика

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

62

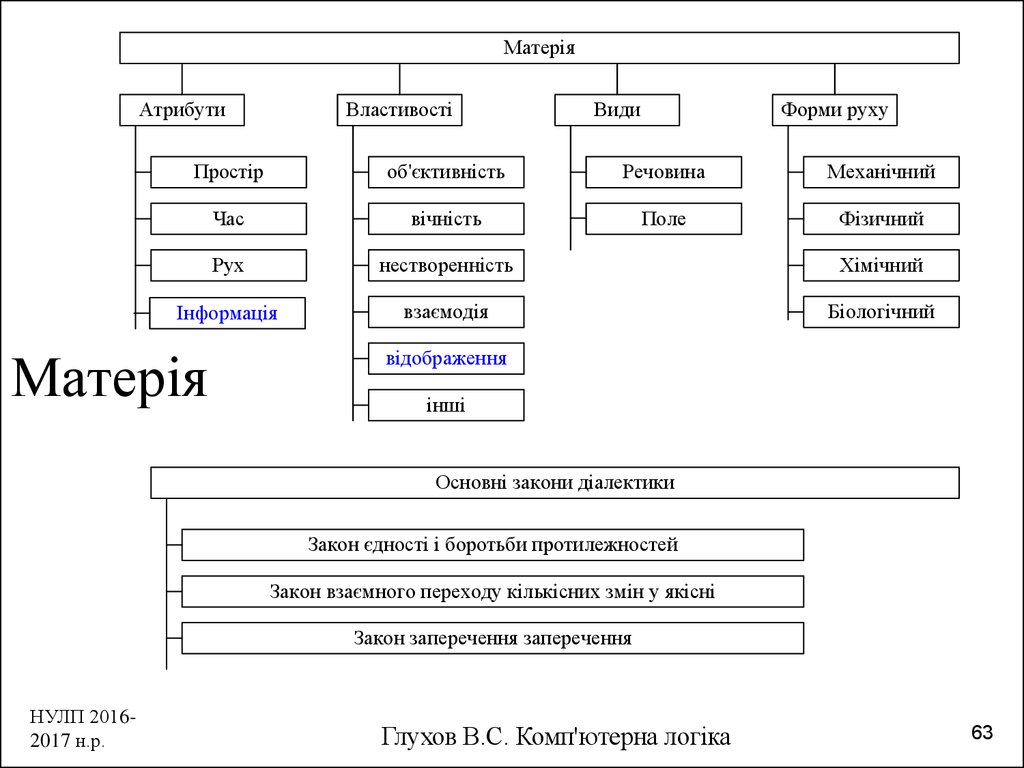

63. Матерія

АтрибутиВластивості

Види

Форми руху

Простір

об'єктивність

Речовина

Механічний

Час

вічність

Поле

Фізичний

Рух

нестворенність

Хімічний

Інформація

взаємодія

Біологічний

Матерія

відображення

інші

Основні закони діалектики

Закон єдності і боротьби протилежностей

Закон взаємного переходу кількісних змін у якісні

Закон заперечення заперечення

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

63

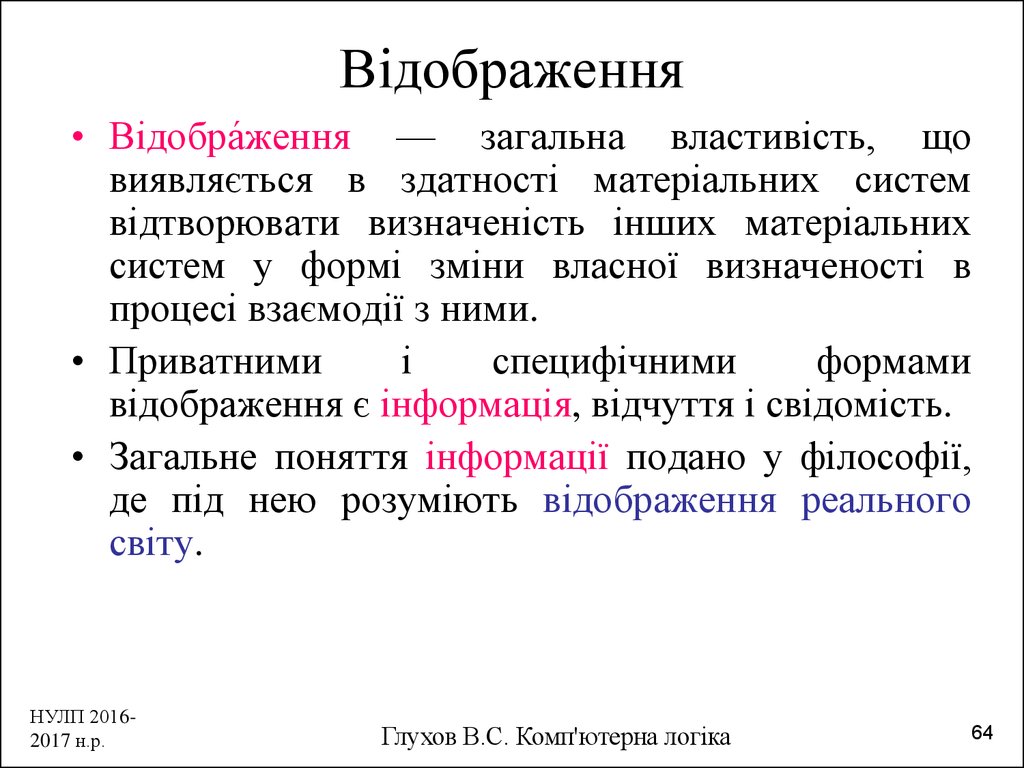

64. Відображення

• Відобра́ження — загальна властивість, щовиявляється в здатності матеріальних систем

відтворювати визначеність інших матеріальних

систем у формі зміни власної визначеності в

процесі взаємодії з ними.

• Приватними

і

специфічними

формами

відображення є інформація, відчуття і свідомість.

• Загальне поняття інформації подано у філософії,

де під нею розуміють відображення реального

світу.

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

64

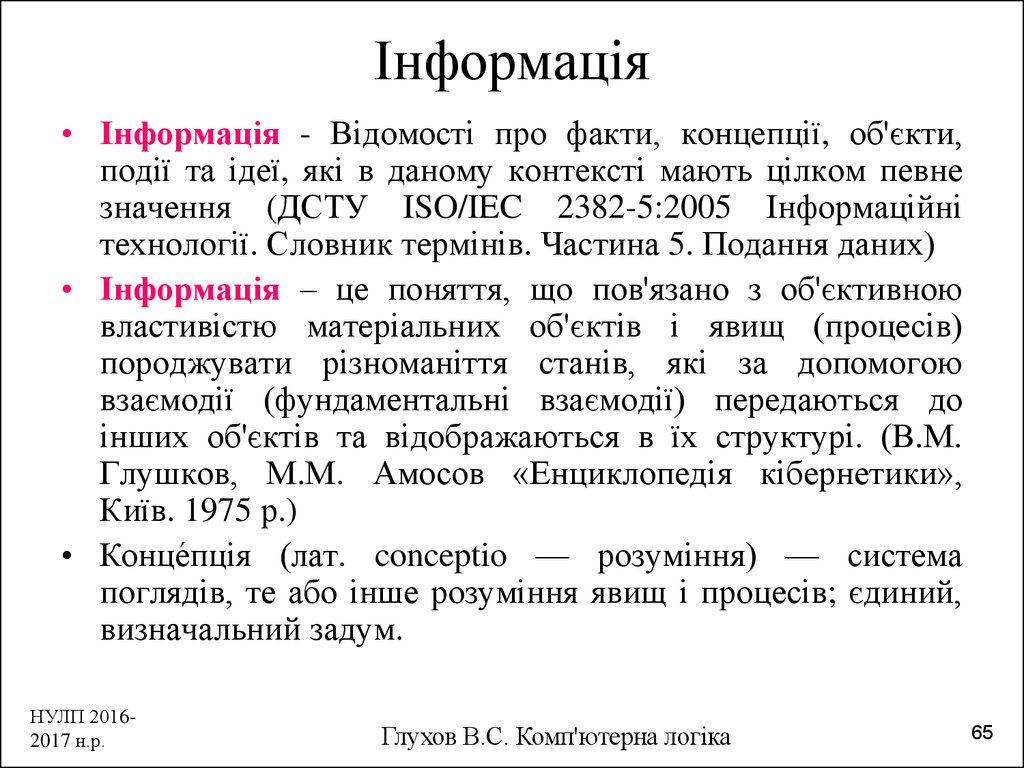

65. Інформація

• Інформація - Відомості про факти, концепції, об'єкти,події та ідеї, які в даному контексті мають цілком певне

значення (ДСТУ ISO/IEC 2382-5:2005 Інформаційні

технології. Словник термінів. Частина 5. Подання даних)

• Інформація – це поняття, що пов'язано з об'єктивною

властивістю матеріальних об'єктів і явищ (процесів)

породжувати різноманіття станів, які за допомогою

взаємодії (фундаментальні взаємодії) передаються до

інших об'єктів та відображаються в їх структурі. (В.М.

Глушков, М.М. Амосов «Енциклопедія кібернетики»,

Київ. 1975 р.)

• Конце́пція (лат. conceptio — розуміння) — система

поглядів, те або інше розуміння явищ і процесів; єдиний,

визначальний задум.

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

65

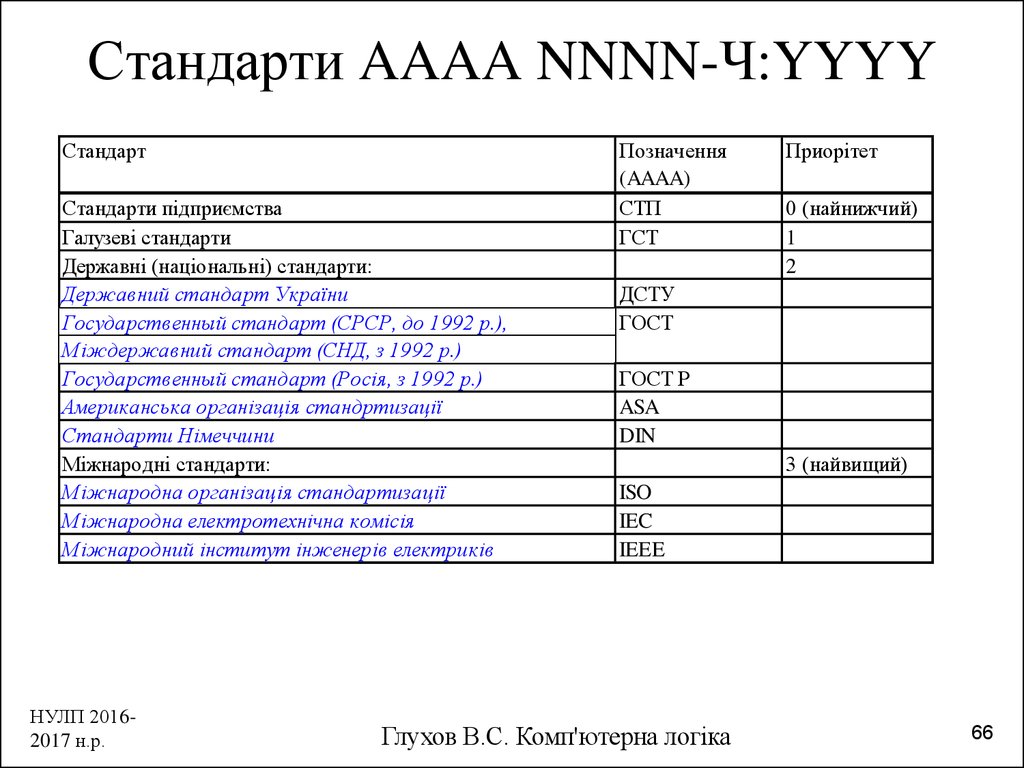

66. Стандарти AAAA NNNN-Ч:YYYY

СтандартСтандарти підприємства

Галузеві стандарти

Державні (національні) стандарти:

Державний стандарт України

Государственный стандарт (СРСР, до 1992 р.),

Міждержавний стандарт (СНД, з 1992 р.)

Государственный стандарт (Росія, з 1992 р.)

Американська організація стандртизації

Стандарти Німеччини

Міжнародні стандарти:

Міжнародна організація стандартизації

Міжнародна електротехнічна комісія

Міжнародний інститут інженерів електриків

НУЛП 20162017 н.р.

Позначення

(AAAA)

СТП

ГСТ

Приорітет

0 (найнижчий)

1

2

ДСТУ

ГОСТ

ГОСТ Р

ASA

DIN

3 (найвищий)

ISO

IEC

IEEE

Глухов В.С. Комп'ютерна логіка

66

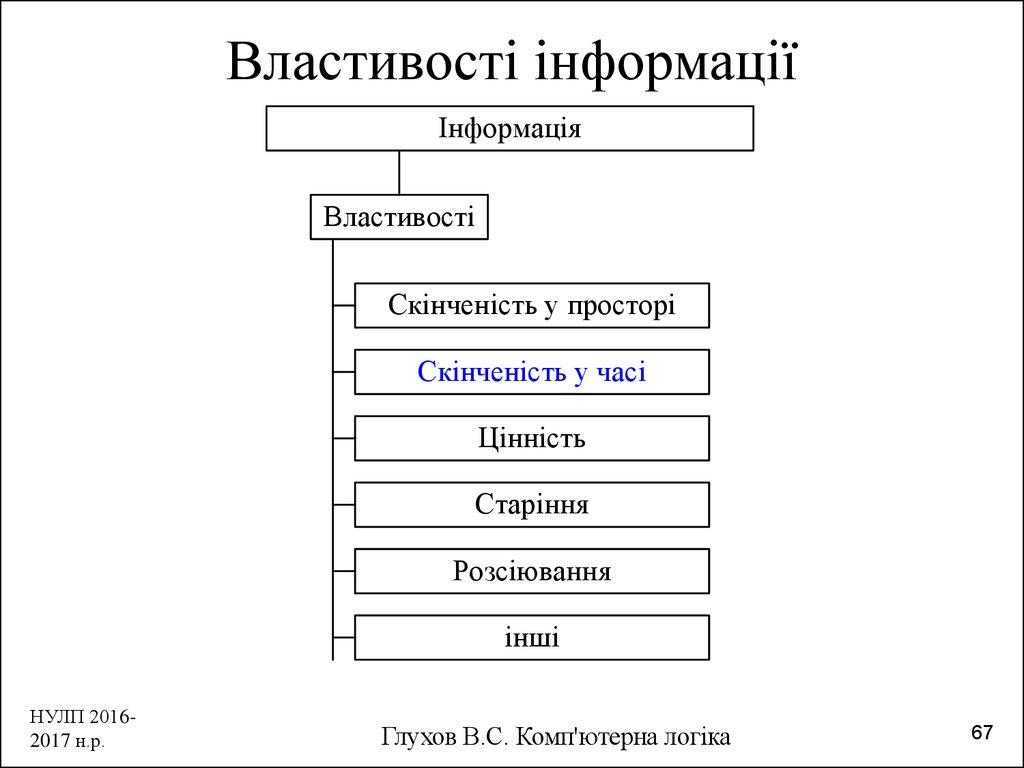

67. Властивості інформації

ІнформаціяВластивості

Скінченість у просторі

Скінченість у часі

Цінність

Старіння

Розсіювання

інші

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

67

68. Комп’ютерна логіка у системі наук інформаційної сфери

Наука і технікаМатерія

Речовина

Інформація

Поле

Отримання

Збереження

Перетворення

Пересилання

Комп’ютерна

логіка

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

68

69. Структурна схема процесу передачі або оброблення інформації

Джерелоінформації

Кодер

джерела

інформації

Кодер

захисту

інформації

Кодер

каналу /

обчислювача

Джерело

завад

Приймач

інформації

НУЛП 20162017 н.р.

Декодер

приймача

інформації

Декодер

захисту

інформації

Декодер

каналу /

обчислювача

Глухов В.С. Комп'ютерна логіка

Модулятор

Канал /

обчислювач

Демодулятор

69

70. Кодек, Модем

• Кодек = кодер + декодер• Модем = Модулятор + демодулятор

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

70

71. Баланс швидкостей

vi = vi1+vi2+…+vinvo = vo1+vo2+…+von

Повинно бути: vi ≤ vo .

Інакше швидкість заповнення пам’яті буде

v = vi -vo > 0

Джерело

інформації

1

Джерело

інформації

2

...

Джерело

інформації

n

НУЛП 20162017 н.р.

ti1

F

ti2

tin

V

to1

Приймач

інформації

1

to2

Приймач

інформації

2

...

tom

Приймач

інформації

m

Глухов В.С. Комп'ютерна логіка

71

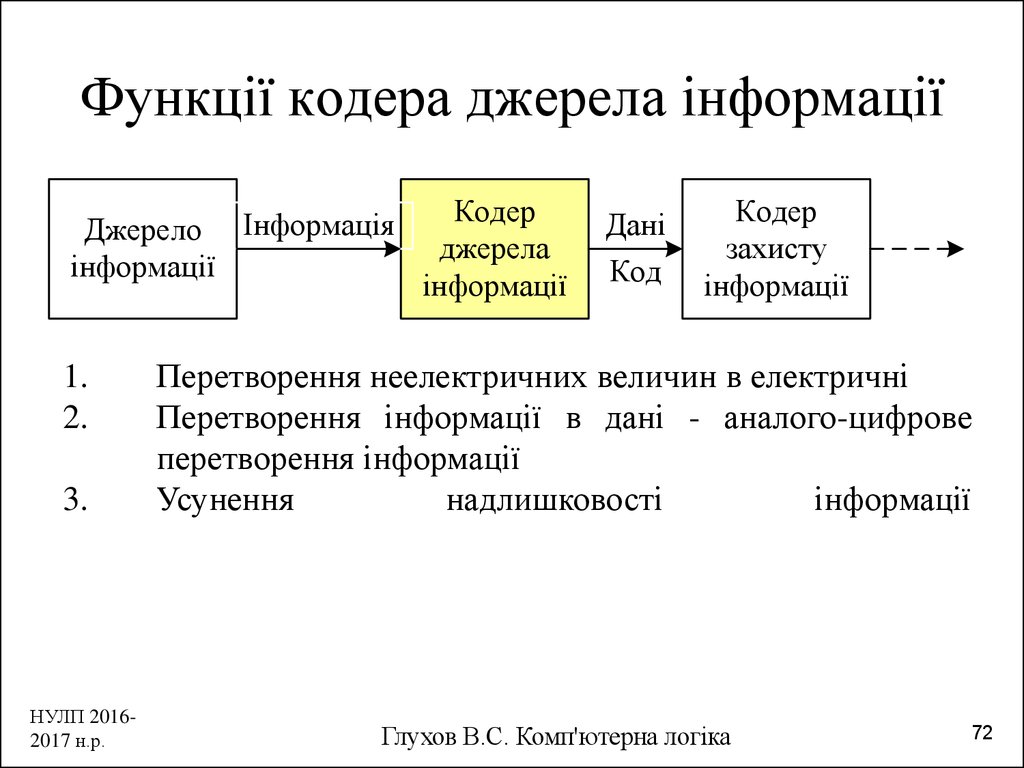

72. Функції кодера джерела інформації

Джерелоінформації

1.

2.

3.

НУЛП 20162017 н.р.

Інформація

Кодер

джерела

інформації

Дані

Код

Кодер

захисту

інформації

Перетворення неелектричних величин в електричні

Перетворення інформації в дані - аналого-цифрове

перетворення інформації

Усунення

надлишковості

інформації

Глухов В.С. Комп'ютерна логіка

72

73. Дані

• Дані - Інформація, представлена у вигляді, придатномудля обробки автоматичними засобами при можливій

участі людини

• Дискретний - Визначення, що відноситься до даних,

представлених окремими елементами, наприклад, знаками

або фізичними величинами, які приймають кінцеве число

цілком певних значень

• Числовий - Визначення, що відноситься до даних, які

складаються з чисел

• Цифровий - Визначення, що відноситься до даних, які

складаються з цифр

• Аналоговий - Визначення, що відноситься до даних, які

представлені безперервними значеннями будь-якої

фізичної змінної

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

73

74. Кодування

• Кодування даних КодуванняПроцес побудови даних з елементів скінченої множини за

встановленими правилами

• кодовий набір

Скінчена множина елементів, з яких будують дані при

кодуванні

• алфавіт

Кодовий набір, в якому встановлено відношення порядку

• кодон

Елемент кодового набору

• Код даних Код

Система, утворена кодовим набором і правилами, за

якими з елементів цього кодового набору будують дані

при кодуванні

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

74

75. Сигнал та повідомлення

• Сигнал - матеріальний носій інформації, якийвикористовується для передачі повідомлень в

системі зв'язку.

• Сигнал може генеруватися, але його прийом не

обов'язковий, на відміну від повідомлення, яке

розраховане

на

прийняття

приймаючою

стороною, інакше воно не є повідомленням.

• Сигналом може бути будь-який фізичний процес,

параметри якого змінюються відповідно до

переданого повідомлення.

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

75

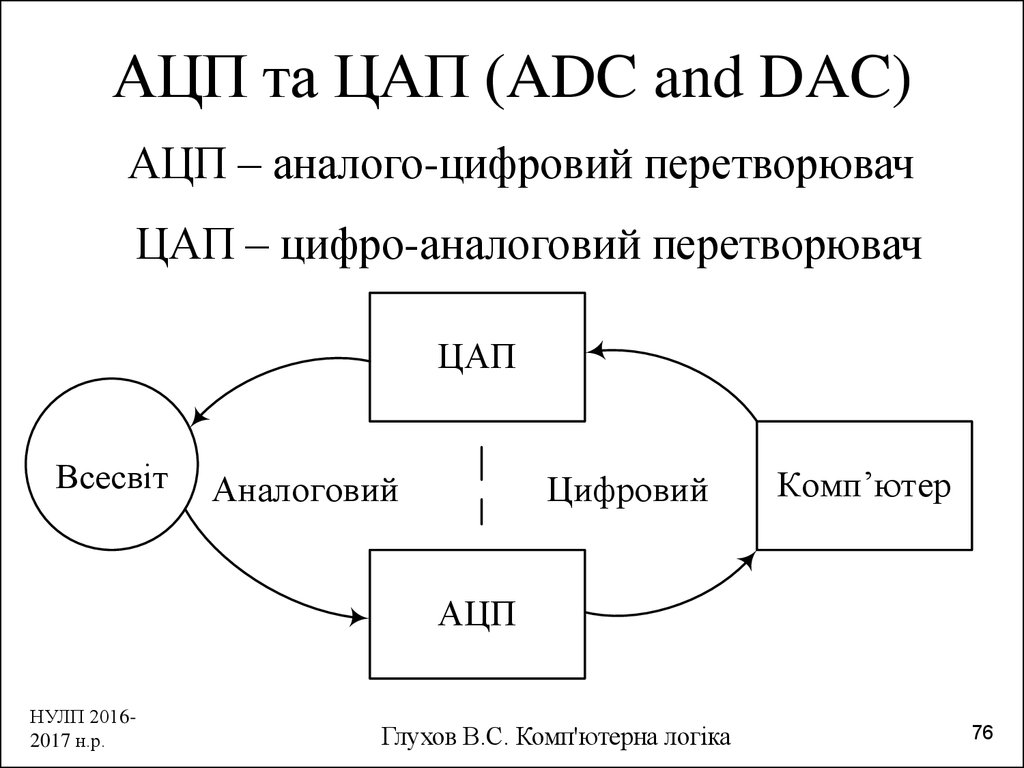

76. АЦП та ЦАП (ADC and DAC)

АЦП – аналого-цифровий перетворювачЦАП – цифро-аналоговий перетворювач

ЦАП

Всесвіт

Аналоговий

Цифровий

Комп’ютер

АЦП

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

76

77. Порівняння аналогових та цифрових методів обробки інформації

ХарактеристикаШвидкодія

Універсальність

Мікромініатюризація

Точність

Масштабування

Передача у просторі

Передача у часі

Завадостійкість

Надійність

НУЛП 20162017 н.р.

Аналогові

способи

+

Цифрові

способи

-

-

+

+

-

+

+

+

+

+

+

Глухов В.С. Комп'ютерна логіка

77

78. Найпоширеніший аналоговий обчислювач (комп’ютер, помножувач)

Кут повороту = U*I*t*kНУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

78

79. Дискретизація та квантування

• Під квантуванням (англ. quantization) неперервної абодискретної величини розуміють розбивку діапазону її

значень на кінцеве число інтервалів. Квантування часто

використовується при обробці цифрових сигналів, у тому

числі при стисканні звуку й зображень. Квантування

приводить сигнал до заданих значень, тобто, розбиває за

рівнем сигналу (на графіку — по горизонталі).

• Не слід плутати квантування з дискретизацією (і,

відповідно, рівень квантування з частотою дискретизації).

При дискретизації величина, що змінюється в часі

(сигнал) заміряється із заданою частотою (частотою

дискретизації), таким чином, дискретизація розбиває

сигнал за часовою складовою (на графіку — по вертикалі).

• Сигнал, до якого застосована дискретизація й

квантування, називається цифровим.

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

79

80. Дискретиза́ція

• Дискретиза́ція — перетворення функційнеперервних змінних у функції дискретних

змінних, за якими початкові неперервні

функції можуть бути відновлені із заданою

точністю.

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

80

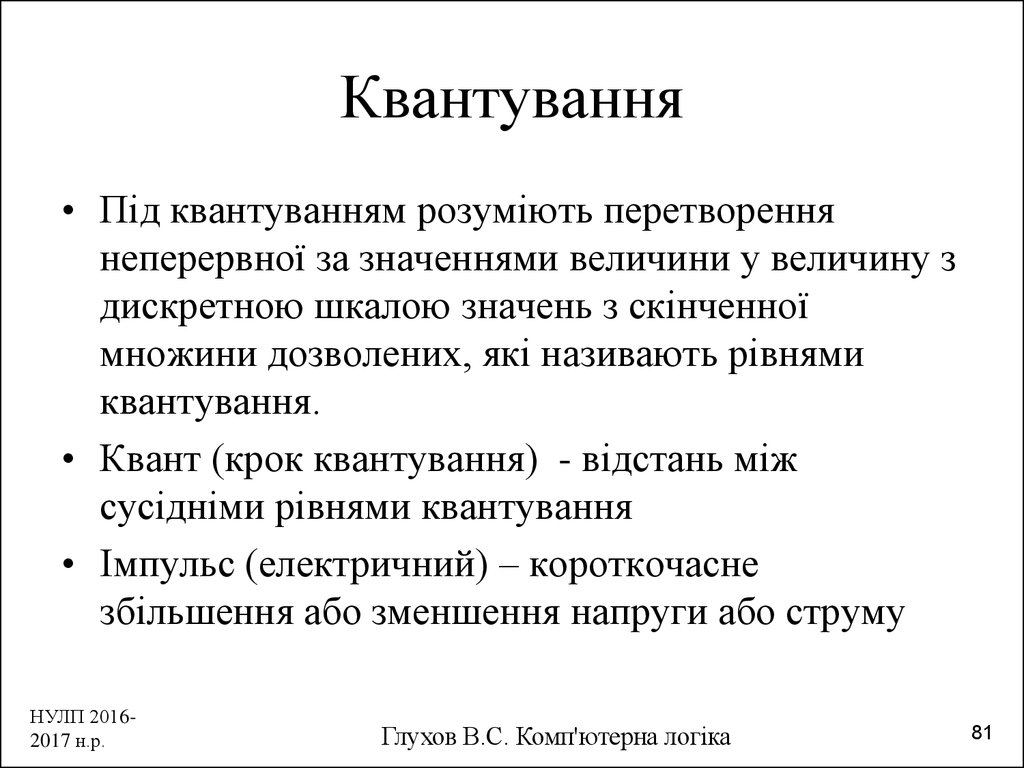

81. Квантування

• Під квантуванням розуміють перетвореннянеперервної за значеннями величини у величину з

дискретною шкалою значень з скінченної

множини дозволених, які називають рівнями

квантування.

• Квант (крок квантування) - відстань між

сусідніми рівнями квантування

• Імпульс (електричний) – короткочасне

збільшення або зменшення напруги або струму

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

81

82. Дискретизація та квантування

Неперервний у часі.Дискретний за рівнем

НУЛП 20162017 н.р.

Дискретний у часі.

Неперервний за рівнем

Дискретний у часі.

Дискретний за рівнем

Глухов В.С. Комп'ютерна логіка

82

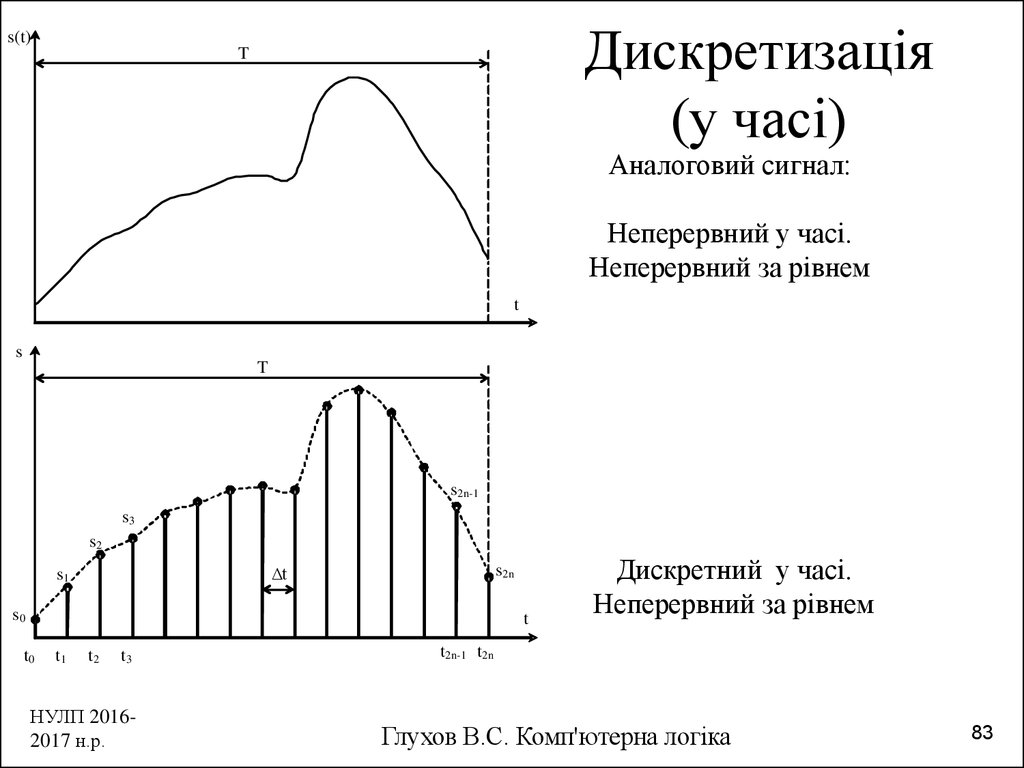

83. Дискретизація (у часі)

s(t)T

Аналоговий сигнал:

Неперервний у часі.

Неперервний за рівнем

t

s

T

s2n-1

s3

s2

s2n

Δt

s1

s0

t

t0

t1

t2

t3

НУЛП 20162017 н.р.

Дискретний у часі.

Неперервний за рівнем

t2n-1 t2n

Глухов В.С. Комп'ютерна логіка

83

84. Квантування за рівнем

s(t)T

Аналоговий сигнал:

t

s(t)

sk

Неперервний у часі.

Неперервний за рівнем

sk-1

Δs

s4

s3

Неперервний у часі.

Дискретний за рівнем

s2

s1

t

s0

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

84

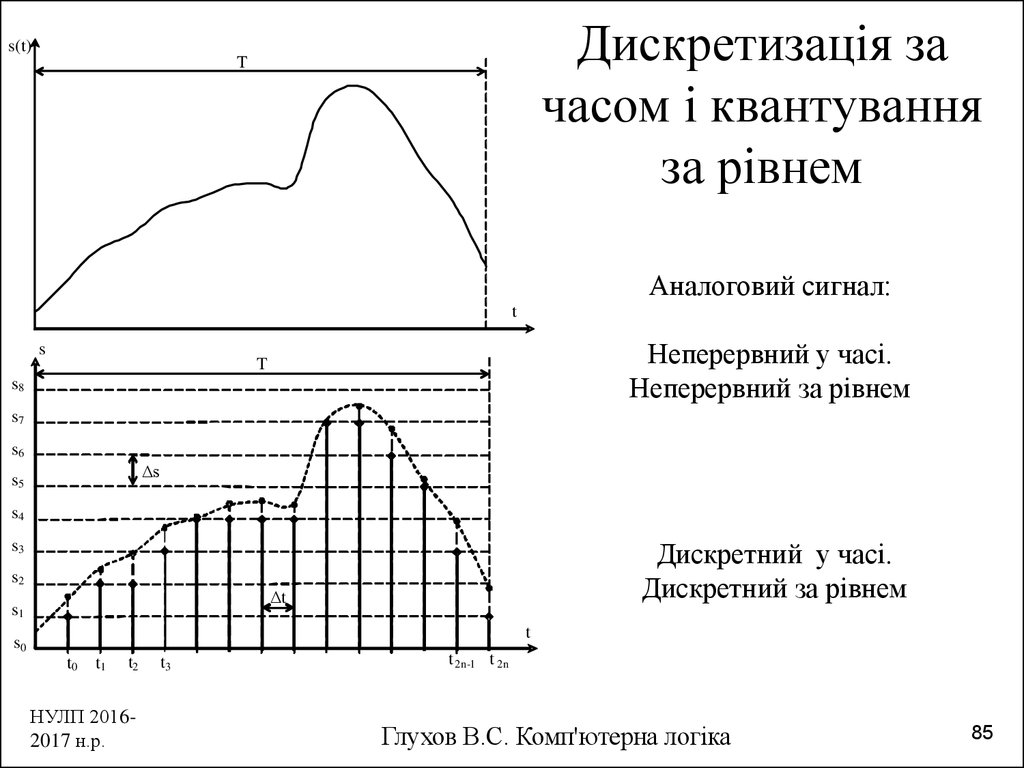

85. Дискретизація за часом і квантування за рівнем

s(t)T

Аналоговий сигнал:

t

s

Неперервний у часі.

Неперервний за рівнем

T

s8

s7

s6

Δs

s5

s4

Дискретний у часі.

Дискретний за рівнем

s3

s2

Δt

s1

t

s0

t0

t1

t2

НУЛП 20162017 н.р.

t3

t 2n-1 t 2n

Глухов В.С. Комп'ютерна логіка

85

86. Теорема Котельнікова – як часто треба вимірювати сигнал?

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

86

87. Переваги кодування двома символами

• Просто• Надійно

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

87

88. Варіанти представлення бітів інформації на фізичному рівні (варіанти сигналів)

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

88

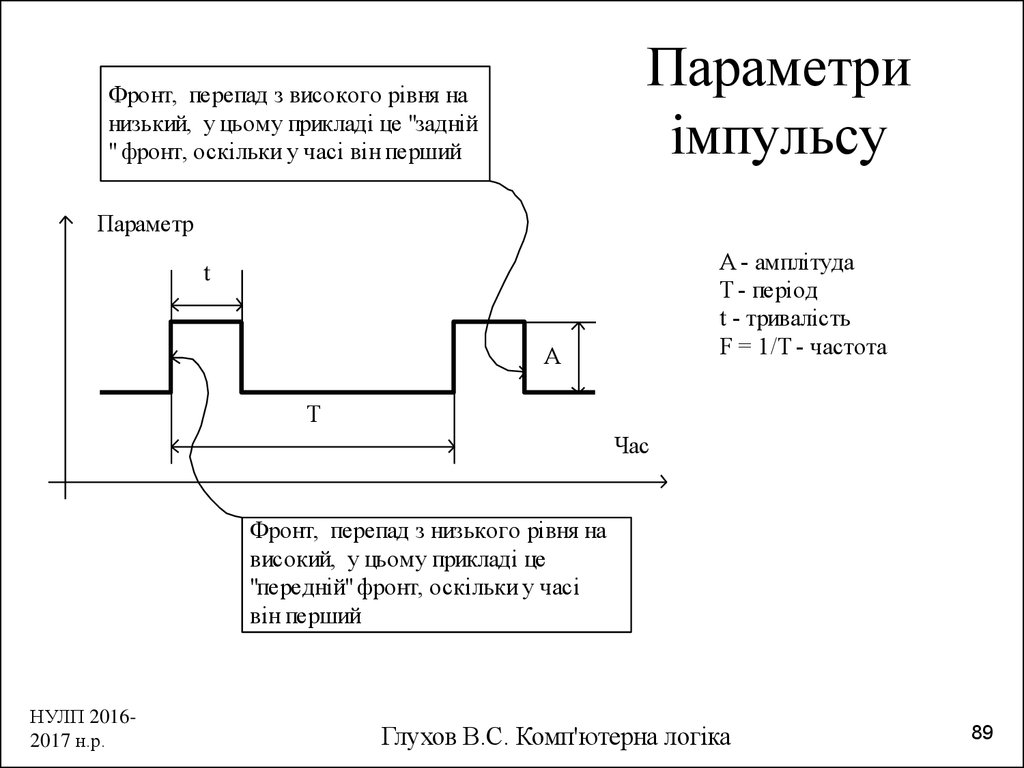

89. Параметри імпульсу

Фронт, перепад з високого рівня нанизький, у цьому прикладі це "задній

" фронт, оскільки у часі він перший

Параметр

A - амплітуда

T - період

t - тривалість

F = 1/T - частота

t

A

T

Час

Фронт, перепад з низького рівня на

високий, у цьому прикладі це

"передній" фронт, оскільки у часі

він перший

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

89

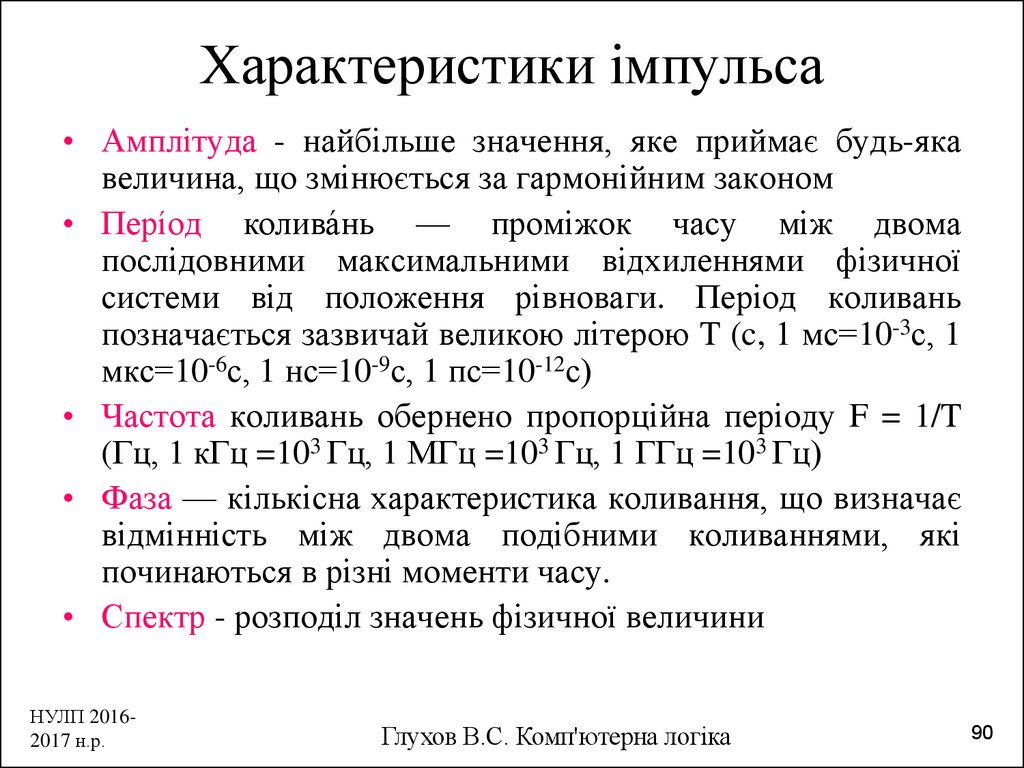

90. Характеристики імпульса

• Амплітуда - найбільше значення, яке приймає будь-якавеличина, що змінюється за гармонійним законом

• Перíод колива́нь — проміжок часу між двома

послідовними максимальними відхиленнями фізичної

системи від положення рівноваги. Період коливань

позначається зазвичай великою літерою T (c, 1 мс=10-3с, 1

мкс=10-6с, 1 нс=10-9с, 1 пс=10-12с)

• Частота коливань обернено пропорційна періоду F = 1/T

(Гц, 1 кГц =103 Гц, 1 МГц =103 Гц, 1 ГГц =103 Гц)

• Фаза — кількісна характеристика коливання, що визначає

відмінність між двома подібними коливаннями, які

починаються в різні моменти часу.

• Спектр - розподіл значень фізичної величини

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

90

91. Дані

• Числа– ФК

• Без знаку

• Із знаком (ПК, ОК, ДК, МДК)

– РК

• IEEE 754 (S, D, E, Q)

• Текст

– Укр (КОІ-8У), Рос (КОІ-7, КОІ-8Р), англ (ASCII)

– Windows 1251, UTF

• Відео

• Аудіо

• Інші

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

91

92. Числа з фіксованою комою

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

92

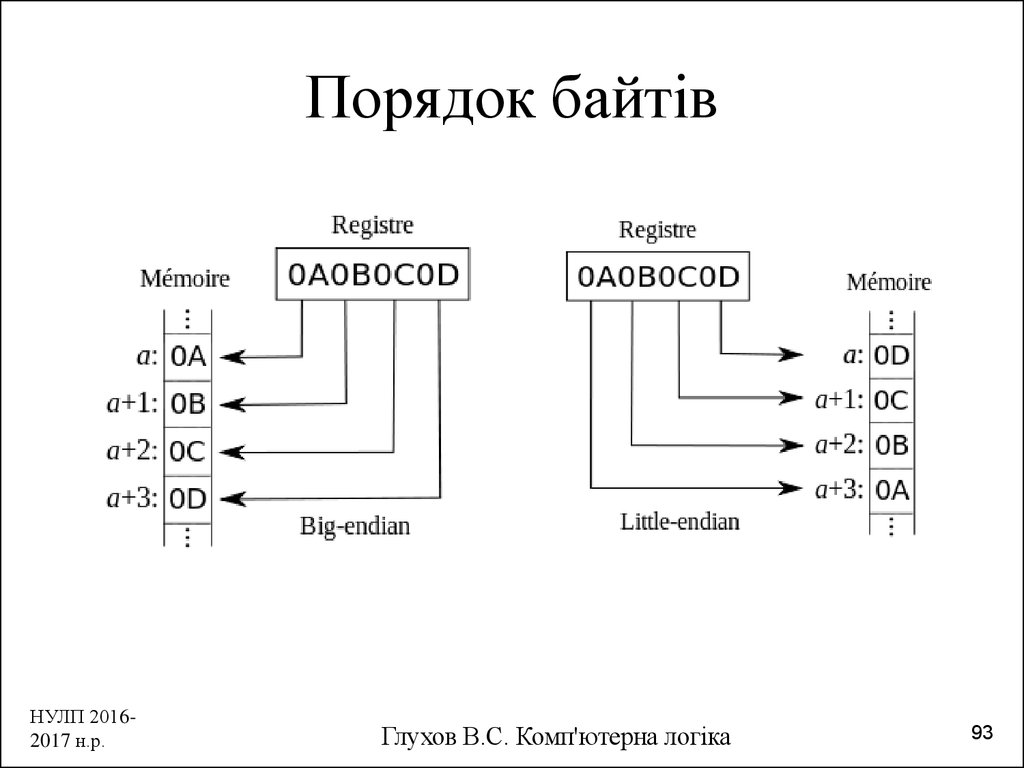

93. Порядок байтів

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

93

94. Числа з рухомою комою. Стандарт IEEE-754

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

94

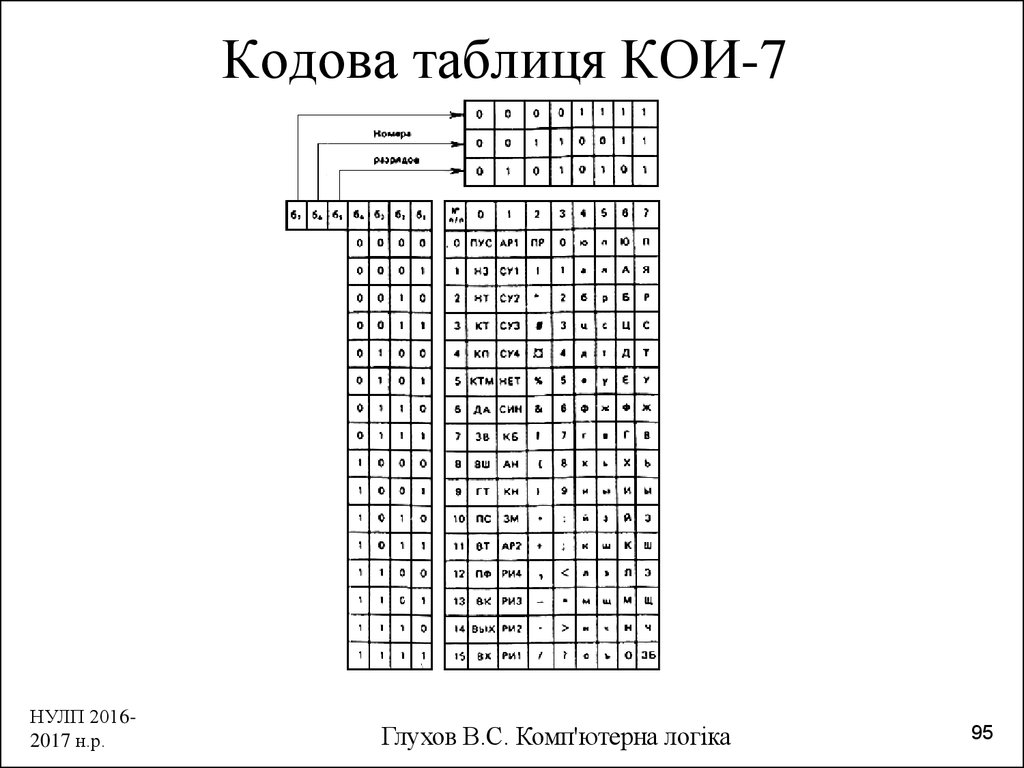

95. Кодова таблиця КОИ-7

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

95

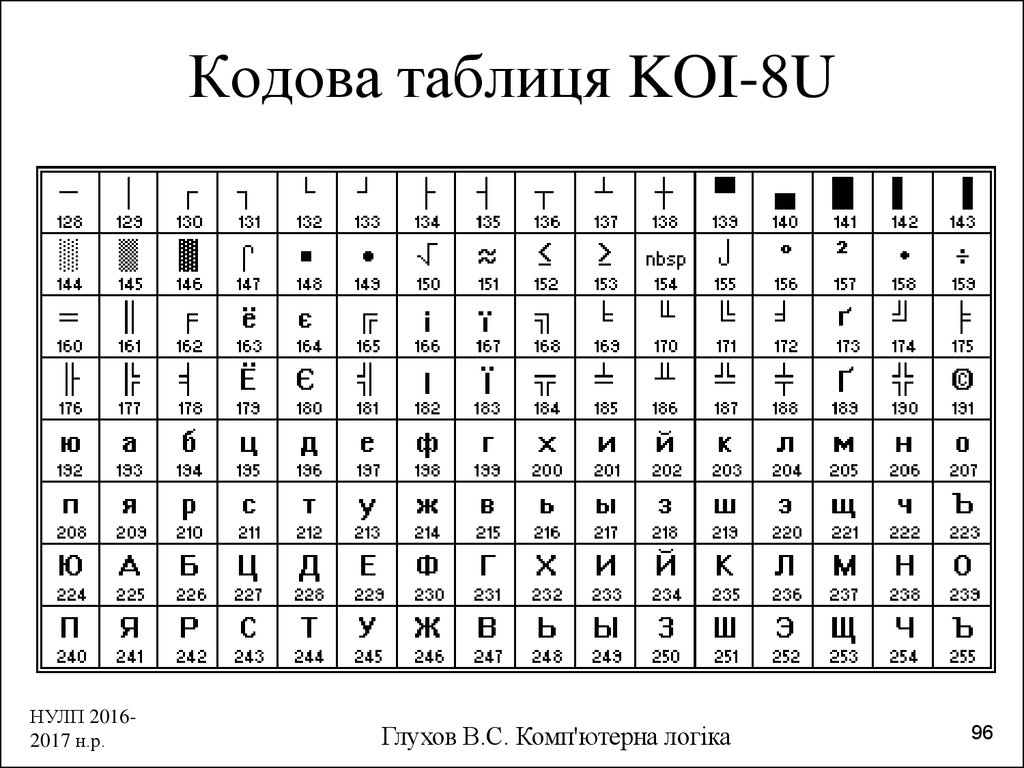

96. Кодова таблиця KOI-8U

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

96

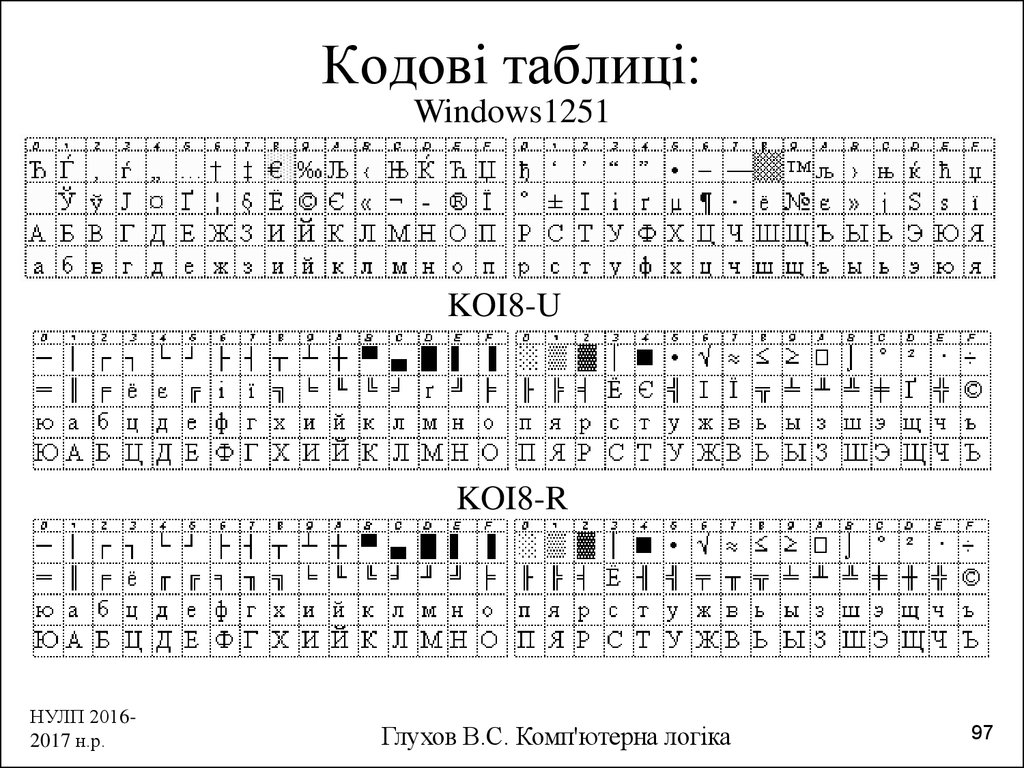

97. Кодові таблиці:

Windows1251KOI8-U

KOI8-R

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

97

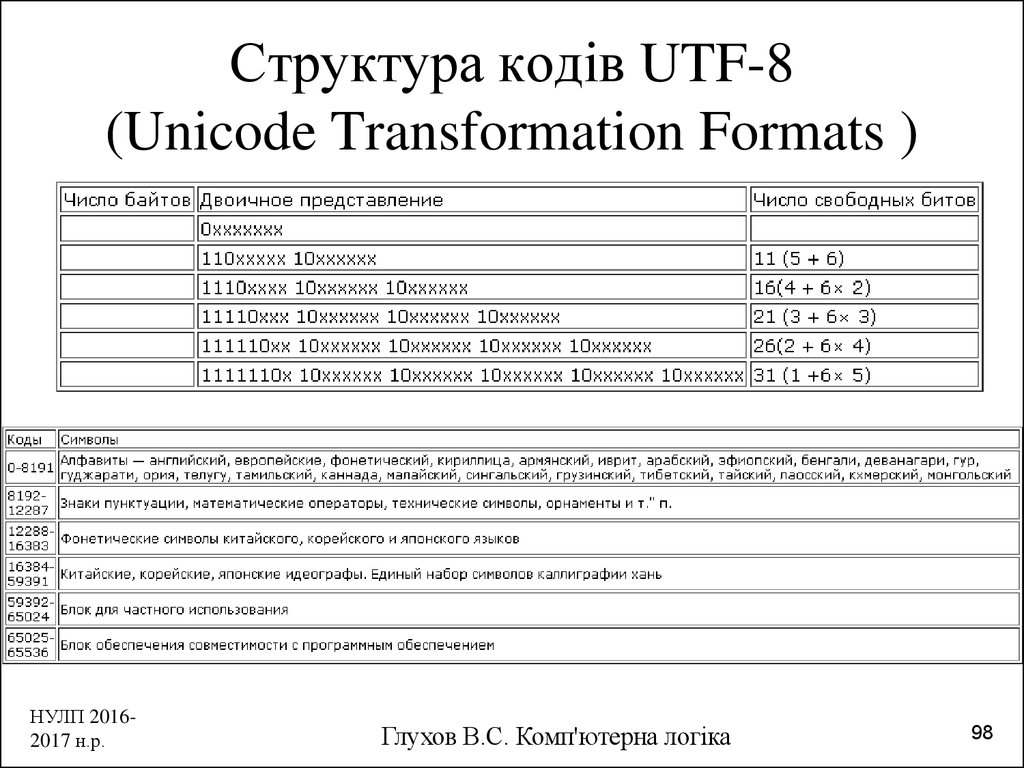

98. Структура кодів UTF-8 (Unicode Transformation Formats )

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

98

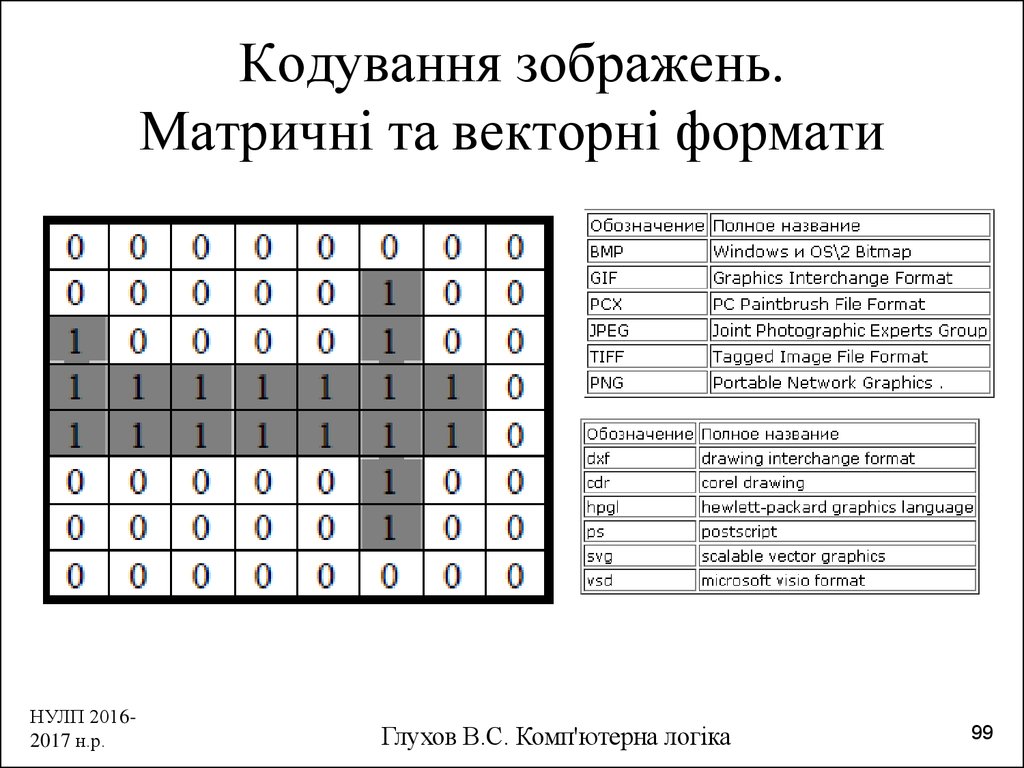

99. Кодування зображень. Матричні та векторні формати

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

99

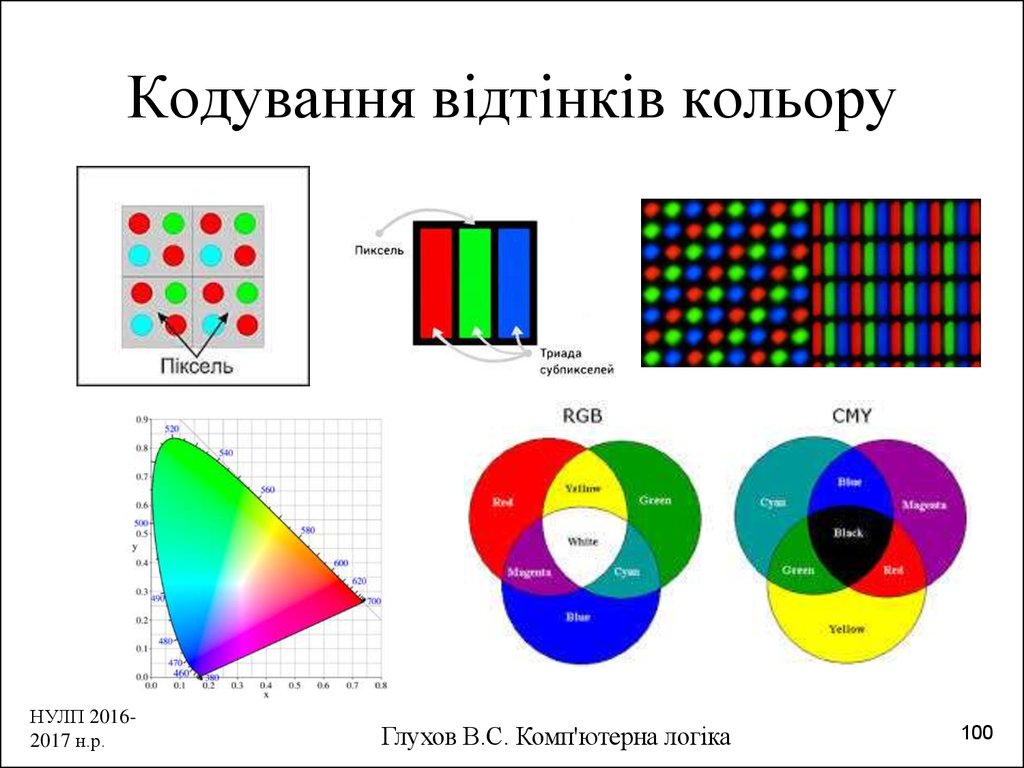

100. Кодування відтінків кольору

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

100

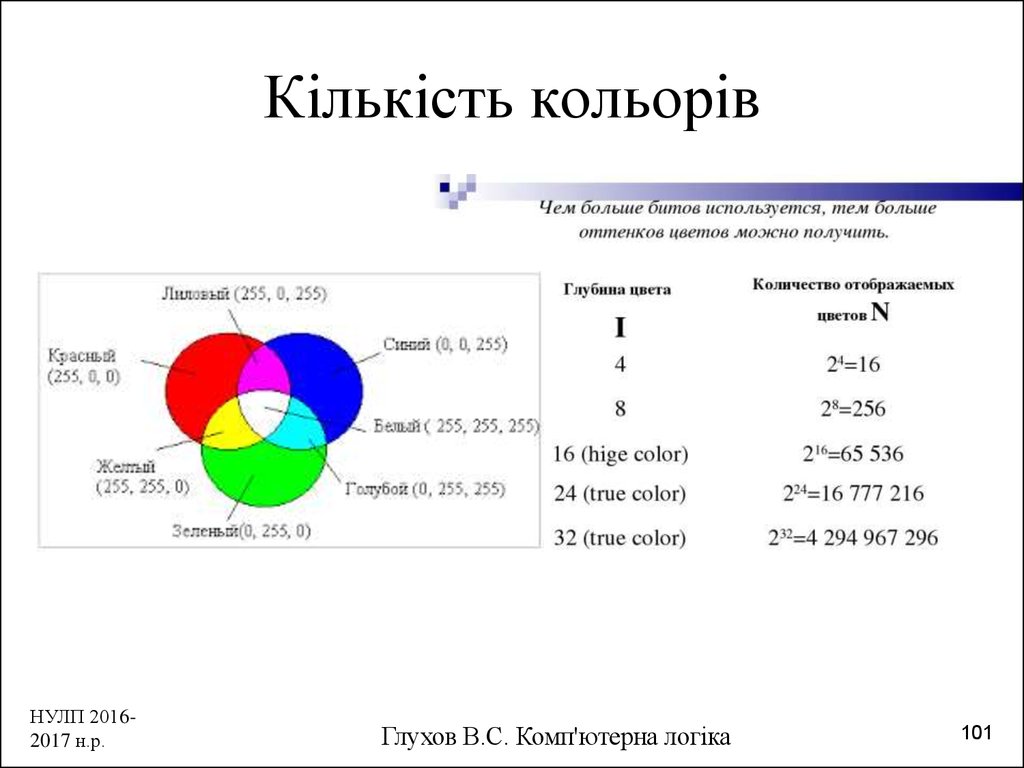

101. Кількість кольорів

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

101

102. Формати аудіфайлів

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

102

103. Міри інформації

Структурні

Семантичні

Статистичні

Інші

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

103

104. Структурні міри інформації

• 1.1 Фізичні – вага, швидкість, тиск, іншіфізичні величини

• 1.2 Геометричні – розміри, габарити

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

104

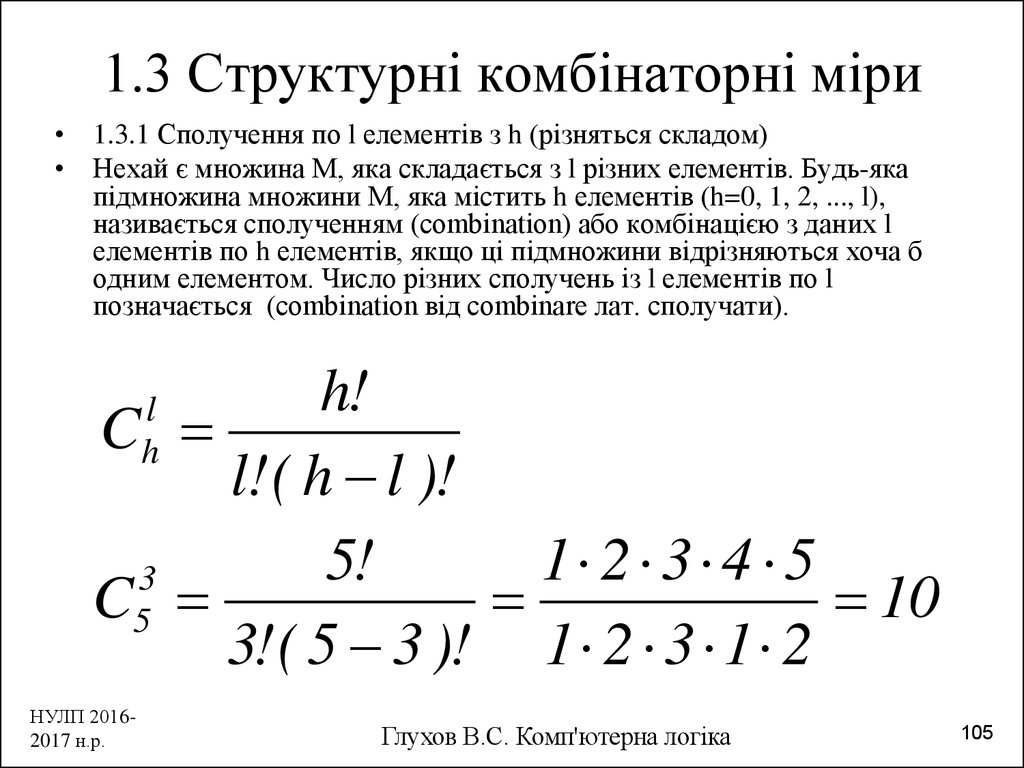

105. 1.3 Структурні комбінаторні міри

• 1.3.1 Сполучення по l елементів з h (різняться складом)• Нехай є множина М, яка складається з l різних елементів. Будь-яка

підмножина множини М, яка містить h елементів (h=0, 1, 2, ..., l),

називається сполученням (combination) або комбінацією з даних l

елементів по h елементів, якщо ці підмножини відрізняються хоча б

одним елементом. Число різних сполучень із l елементів по l

позначається (combination від combinare лат. сполучати).

h!

C

l! ( h l )!

5!

1 2 3 4 5

3

C5

10

3! ( 5 3 )! 1 2 3 1 2

l

h

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

105

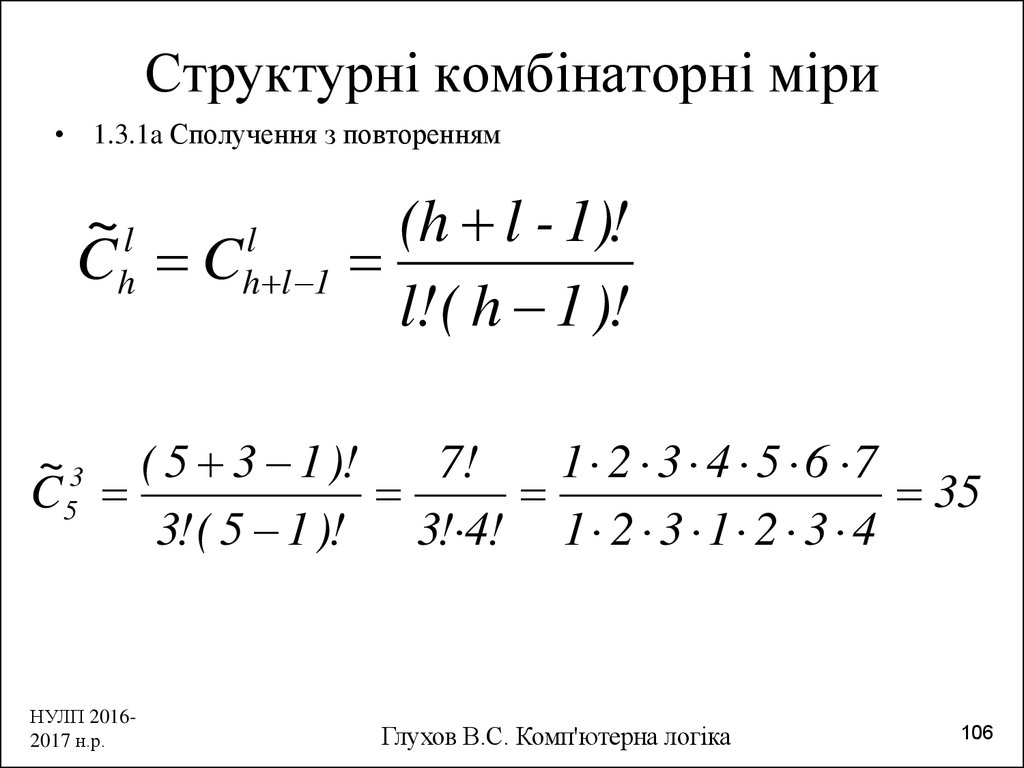

106. Структурні комбінаторні міри

• 1.3.1a Сполучення з повторенням(h l - 1)!

~l

l

Ch Ch l 1

l! ( h 1 )!

7!

1 2 3 4 5 6 7

~ 3 ( 5 3 1 )!

C5

35

3! ( 5 1 )! 3! 4! 1 2 3 1 2 3 4

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

106

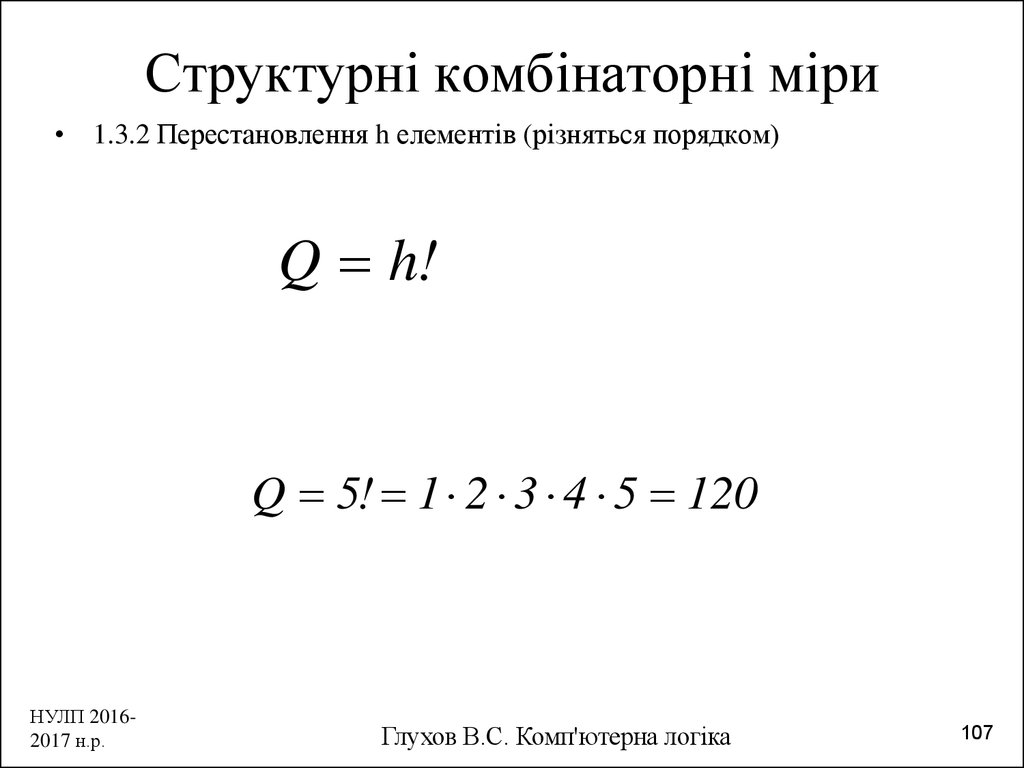

107. Структурні комбінаторні міри

• 1.3.2 Перестановлення h елементів (різняться порядком)Q h!

Q 5! 1 2 3 4 5 120

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

107

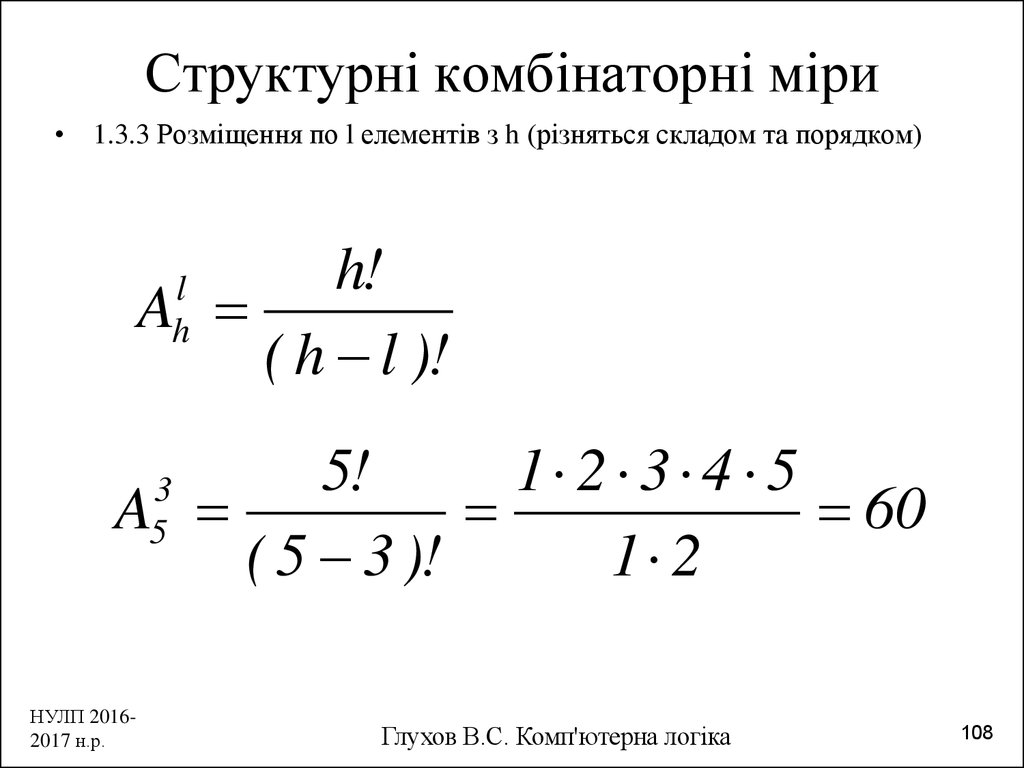

108. Структурні комбінаторні міри

• 1.3.3 Розміщення по l елементів з h (різняться складом та порядком)h!

A

( h l )!

l

h

5!

1 2 3 4 5

A

60

( 5 3 )!

1 2

3

5

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

108

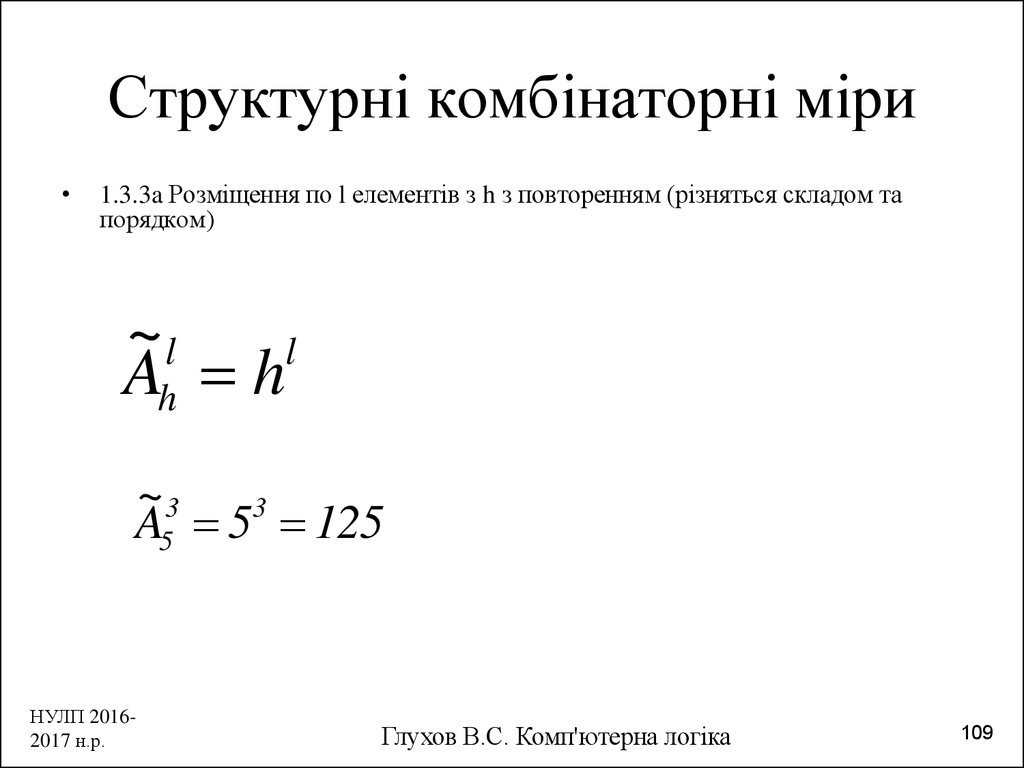

109. Структурні комбінаторні міри

1.3.3a Розміщення по l елементів з h з повторенням (різняться складом та

порядком)

~l

l

Ah h

~3

3

A5 5 125

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

109

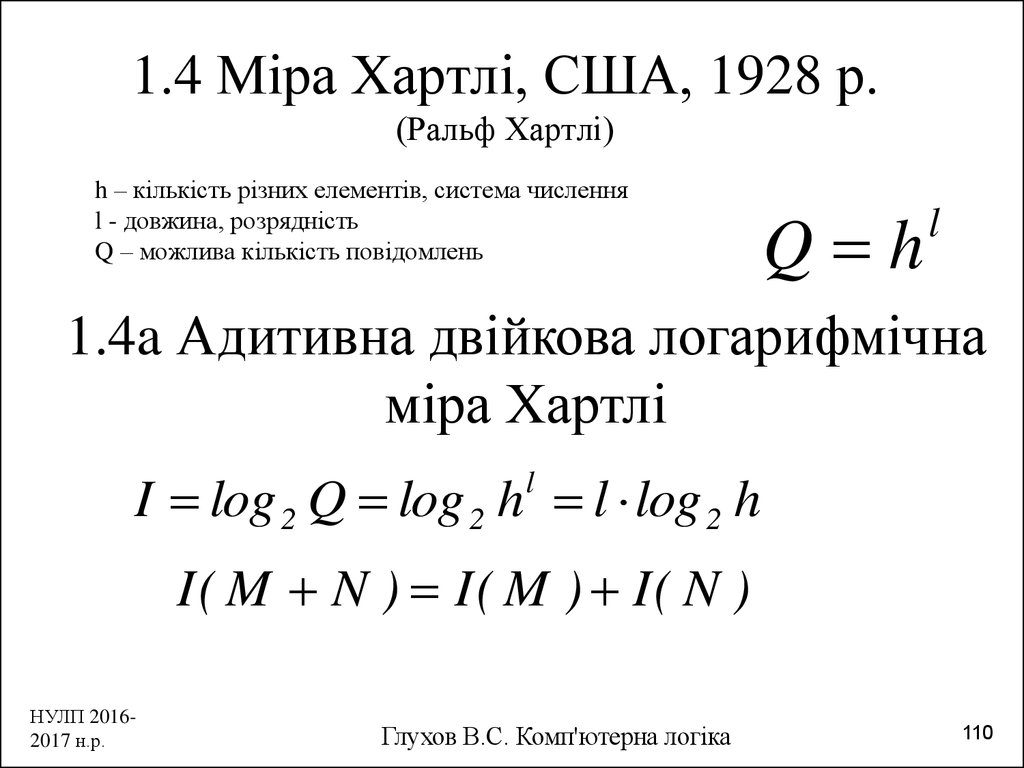

110. 1.4 Міра Хартлі, США, 1928 р. (Ральф Хартлі)

h – кількість різних елементів, система численняl - довжина, розрядність

Q – можлива кількість повідомлень

Q h

l

1.4a Адитивна двійкова логарифмічна

міра Хартлі

I log 2 Q log 2 h l log 2 h

l

I( M N ) I( M ) I( N )

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

110

111.

Одиниця кількості інформаціїI 1 log 2 Q log 2 h l log 2 h 1 log 2 2

l

• Один двійковий розряд – Binary Digit – bit (b, б)

• Байт (B, Б) – найчастіше це 8 біт.

I log 2 Q log 2 hl l log 2 h

M 613; I M log 2 613 9 ,26 10

M 61310 10011001012 10 біт

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

111

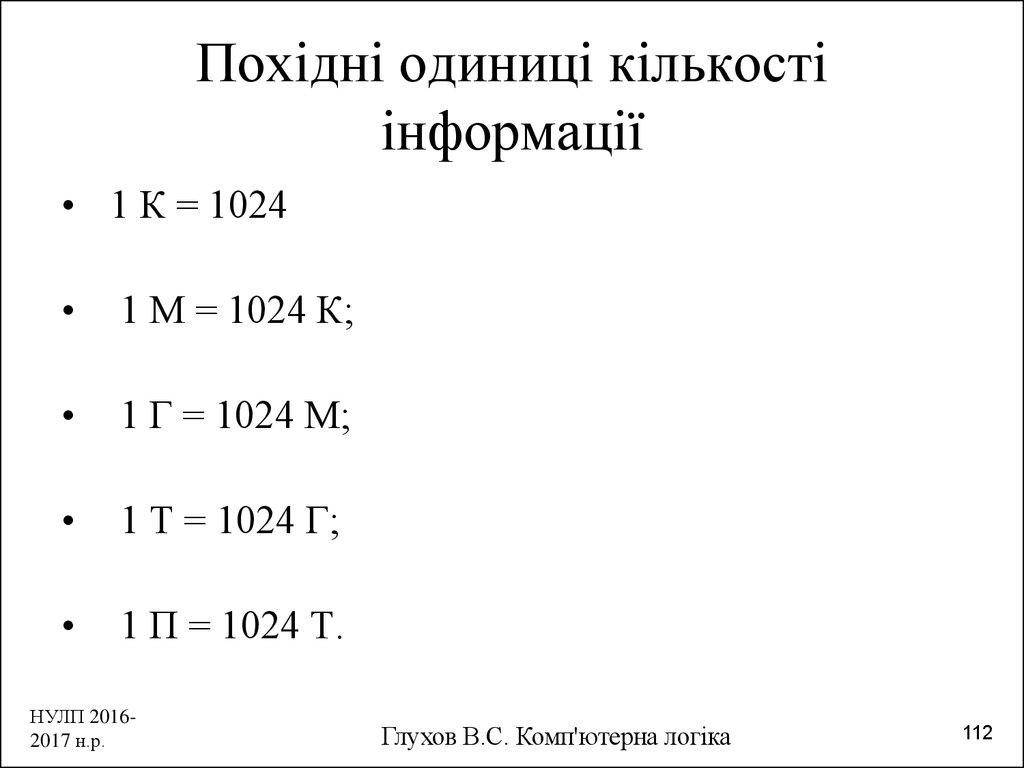

112. Похідні одиниці кількості інформації

• 1 К = 10241 М = 1024 К;

1 Г = 1024 М;

1 Т = 1024 Г;

1 П = 1024 Т.

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

112

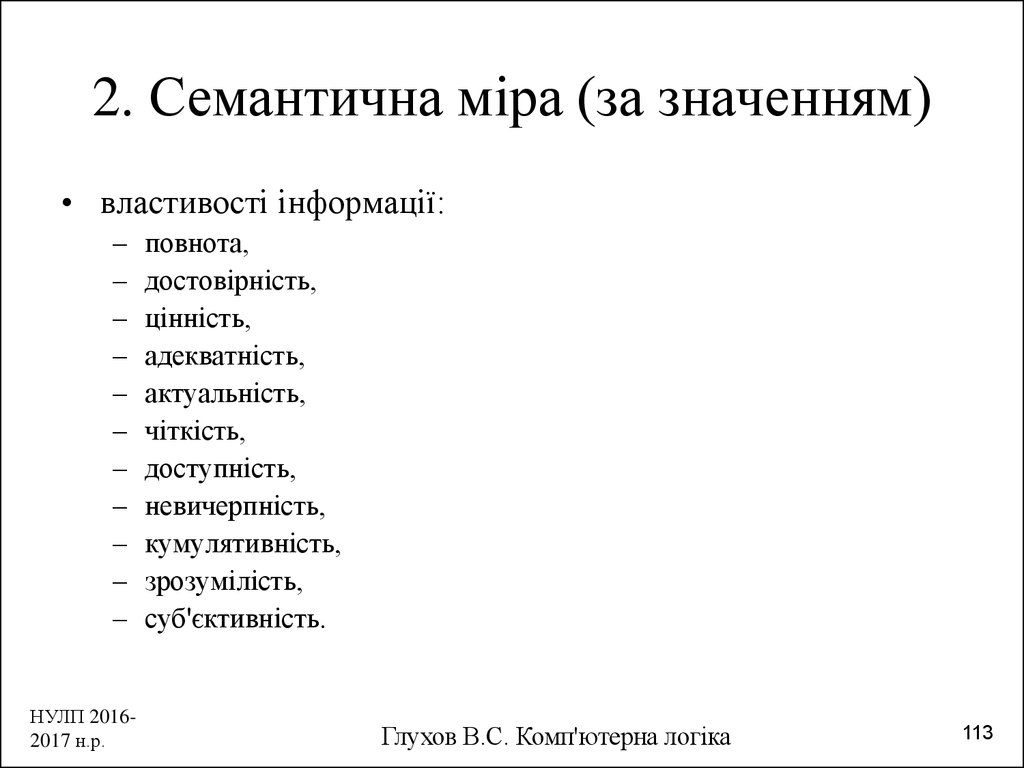

113. 2. Семантична міра (за значенням)

• властивості інформації:–

–

–

–

–

–

–

–

–

–

–

НУЛП 20162017 н.р.

повнота,

достовірність,

цінність,

адекватність,

актуальність,

чіткість,

доступність,

невичерпність,

кумулятивність,

зрозумілість,

суб'єктивність.

Глухов В.С. Комп'ютерна логіка

113

114. Семантична міра

• Повнотаінформації

характеризує

якість

інформації і визначає достатність даних для

прийняття рішень.

• Достовірність інформації - її властивість

відображати реальні об'єкти з необхідною

точністю.

• Цінність інформації не може бути абстрактною.

Інформація має бути корисною і цінною для

певної

категорії

користувачів.

Цінність

інформації залежить від того, які задачі можна

вирішувати за її допомогою.

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

114

115. Семантична міра

• Адекватність інформації характеризує ступіньвідповідності інформації реаліям. Адекватна

інформація - це повна і достовірна інформація.

• Актуальність інформації - ступінь зберігання

цінності інформації для керування в момент її

використання, що залежить від динаміки зміни її

характеристик і від інтервалу часу, що пройшов із

моменту виникнення певної інформації.

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

115

116. Семантична міра

• Своєчасність інформації - її надходженняне пізніше заздалегідь визначеного часу,

узгодженого з часом вирішення

поставленого перед користувачем завдання.

• Чіткість інформації - інформація має бути

зрозуміла для того, кому вона призначена.

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

116

117. Семантична міра

• Доступність інформації - це можливістьотримання і перетворення інформації.

• Точність інформації - ступінь подібності

отриманої інформації до реального стану

об'єкта, процесу, явища тощо.

• Суб'єктивність інформації. Інформація має

суб'єктивний характер, оскільки її цінність

визначається ступенем сприйняття суб'єкта

(одержувача інформації).

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

117

118. Семантична міра

• Корисна інформація - властивість, щозменшує невизначеність прийняття

рішення.

• Репрезентативність інформації правильність її відбору і формування для

адекватного відображення властивостей

об'єкта.

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

118

119. Семантична міра

• Змістовність інформації - це відношеннякількості семантичної інформації в

повідомленні до обсягу даних, які

обробляються.

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

119

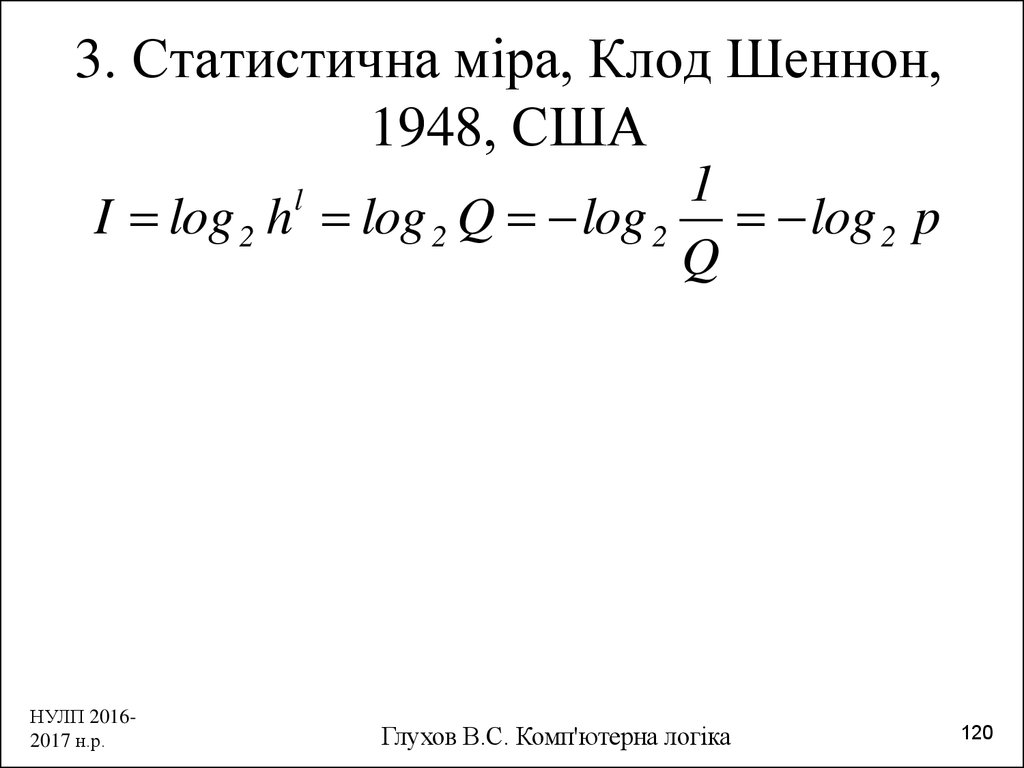

120. 3. Статистична міра, Клод Шеннон, 1948, США

1I log 2 h log 2 Q log 2 log 2 p

Q

l

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

120

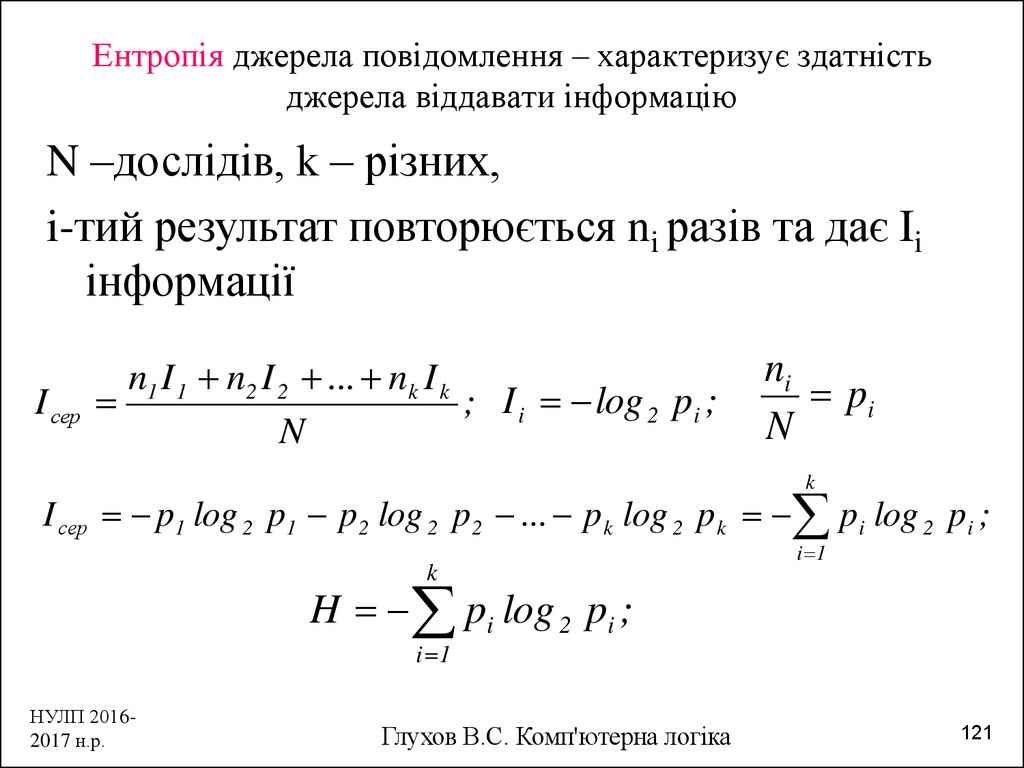

121. Ентропія джерела повідомлення – характеризує здатність джерела віддавати інформацію

N –дослідів, k – різних,i-тий результат повторюється ni разів та дає Ii

інформації

I сер

n1 I 1 n2 I 2 ... nk I k

; I i log 2 pi ;

N

ni

pi

N

k

I сер p1 log 2 p1 p 2 log 2 p 2 ... p k log 2 p k pi log 2 pi ;

k

i 1

H pi log 2 pi ;

i 1

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

121

122. Властивості ентропії

• Невід’ємна• = 0, коли ймовірність однієї події = 1

• Максимальна, коли ймовірності всіх подій

однакові

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

122

123. Залежність ентропії двох подій від їх імовірності

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

123

124. Кількість отриманої інформації

• I = Hпочаткове – HкінцевеНУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

124

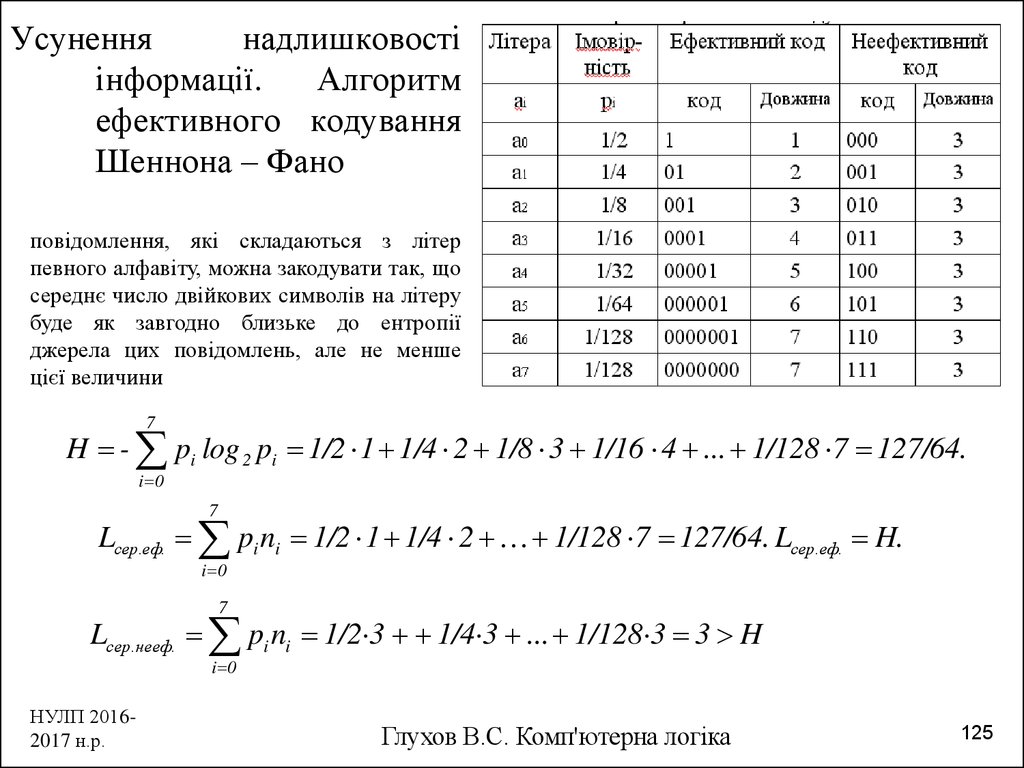

125. Усунення надлишковості інформації. Алгоритм ефективного кодування Шеннона – Фано

повідомлення, які складаються з літерпевного алфавіту, можна закодувати так, що

середнє число двійкових символів на літеру

буде як завгодно близьке до ентропії

джерела цих повідомлень, але не менше

цієї величини

7

H - pi log 2 pi 1/2 1 1/4 2 1/8 3 1/16 4 ... 1/128 7 127/64.

i 0

7

Lсер.еф. pi ni 1/2 1 1/4 2 1/128 7 127/64. Lсер.еф. H.

i 0

7

Lсер.нееф. pi ni 1/2·3 1/4·3 ... 1/128·3 3 H

i 0

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

125

126. Абетка Морзе

А.Б -…В .--

Л .-..

М -Н -.

Ц -.-.

Ч ---.

Ш ----

Г--.

Д -..

Е.

О --П .--.

Р .-.

Щ --.Ъ .--.-.

Ы -.--

Ж …З --..

И ..

С…

ТУ ..-

Ь -..Э ..-..

Ю ..--

Й .--К -.-

Ф ..-.

Х ….

Я .-.-

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

126

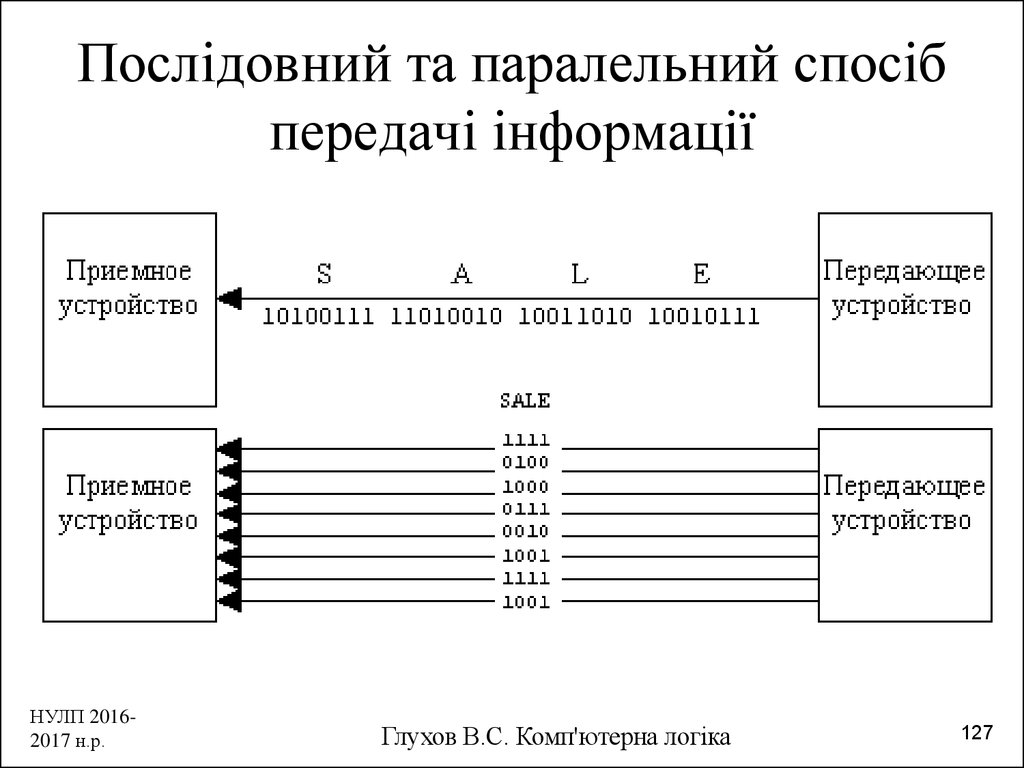

127. Послідовний та паралельний спосіб передачі інформації

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

127

128. Способи оброблення даних

XЦА1

Y1

ЦА3

ЦА2

Y=f(Y1,Y2)

Y2

а

X

ЦА1

Y1

ЦА2

Y=f(Y1)

б

X

ЦА1

X1=f(X,Y2)

ЦА2

Y=f(X1)

Y2=f(Y)

ЦА3

в

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

128

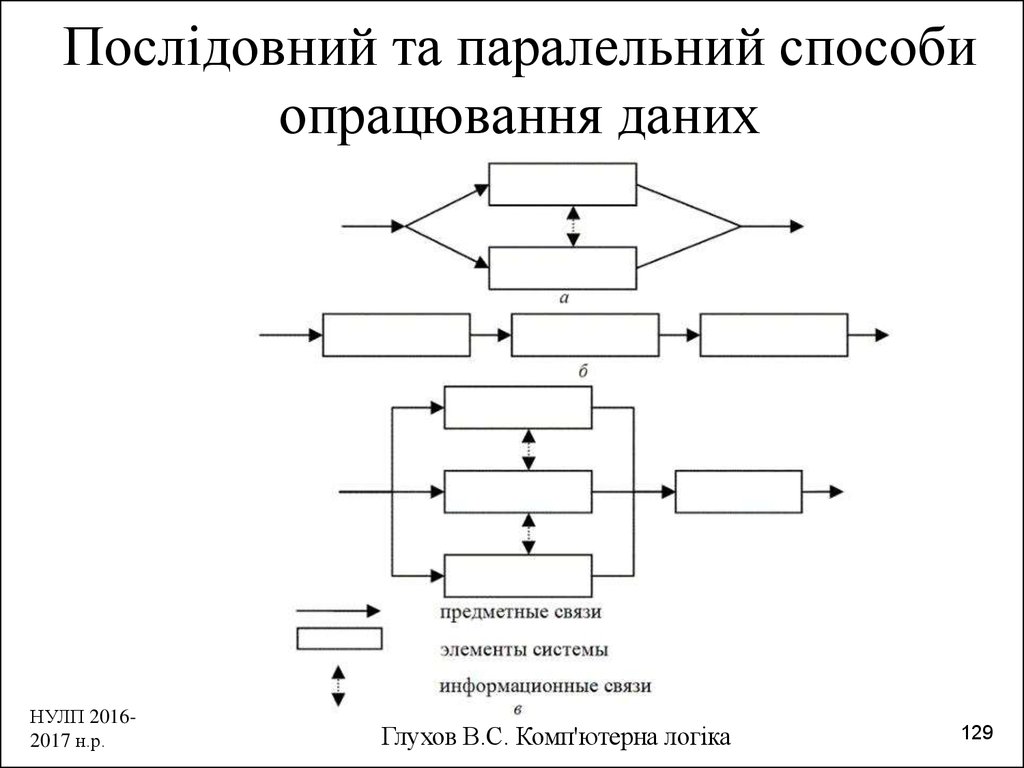

129. Послідовний та паралельний способи опрацювання даних

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

129

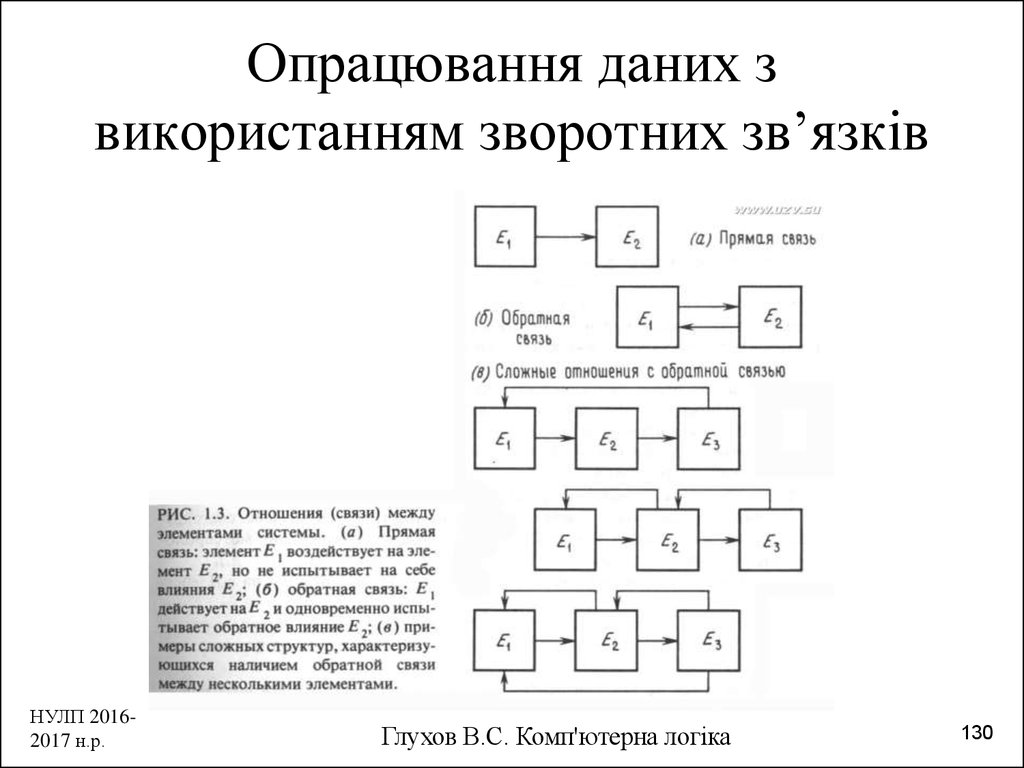

130. Опрацювання даних з використанням зворотних зв’язків

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

130

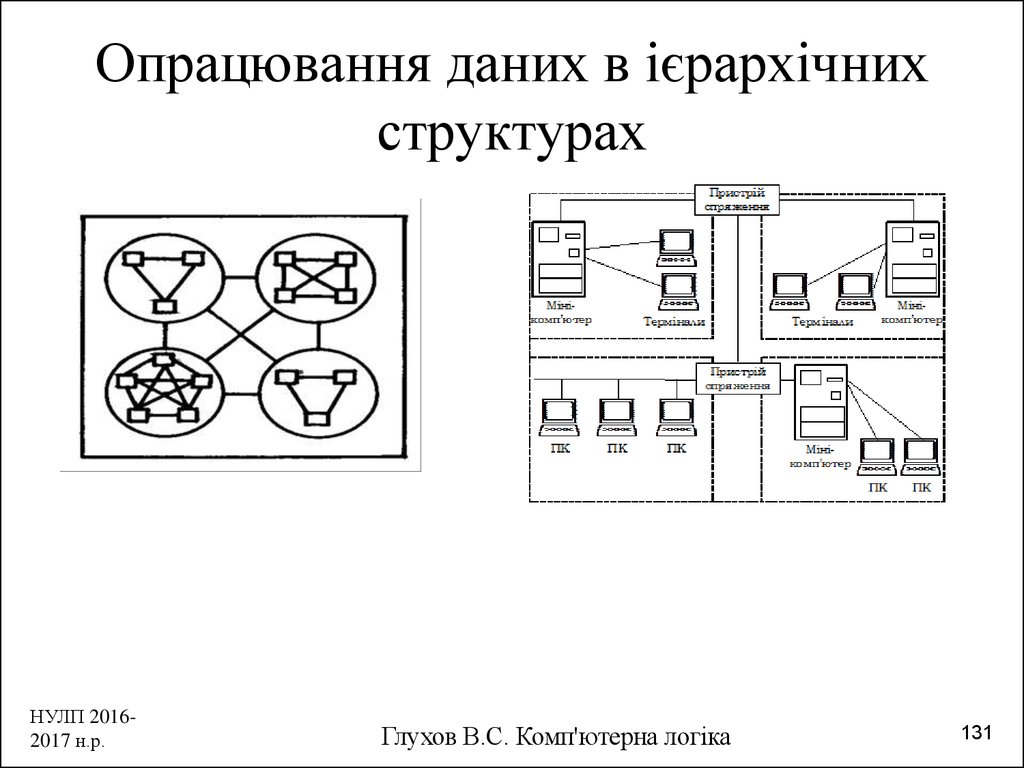

131. Опрацювання даних в ієрархічних структурах

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

131

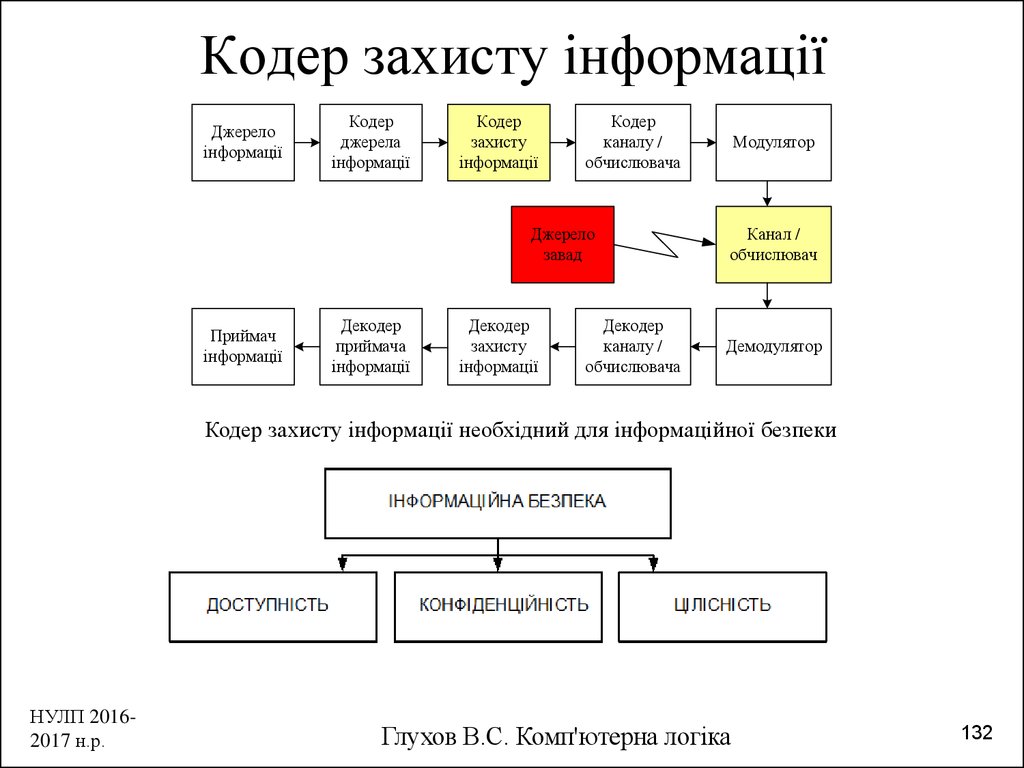

132. Кодер захисту інформації

Джерелоінформації

Кодер

джерела

інформації

Кодер

захисту

інформації

Кодер

каналу /

обчислювача

Джерело

завад

Приймач

інформації

Декодер

приймача

інформації

Декодер

захисту

інформації

Декодер

каналу /

обчислювача

Модулятор

Канал /

обчислювач

Демодулятор

Кодер захисту інформації необхідний для інформаційної безпеки

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

132

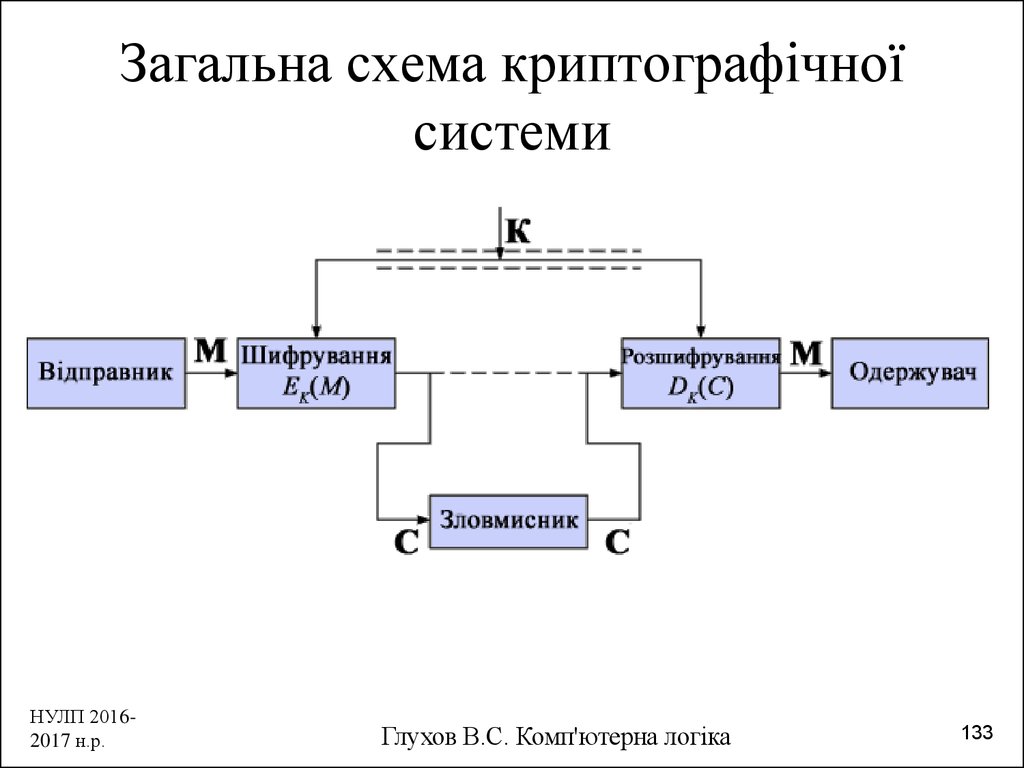

133. Загальна схема криптографічної системи

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

133

134. Перемішування

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

134

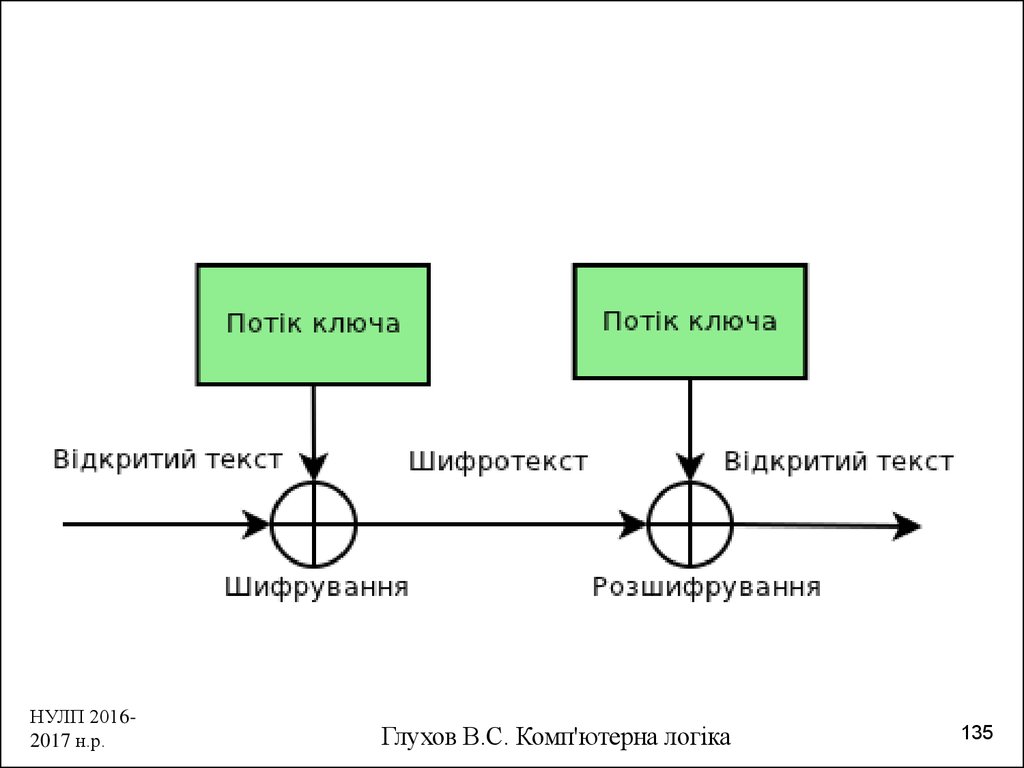

135.

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

135

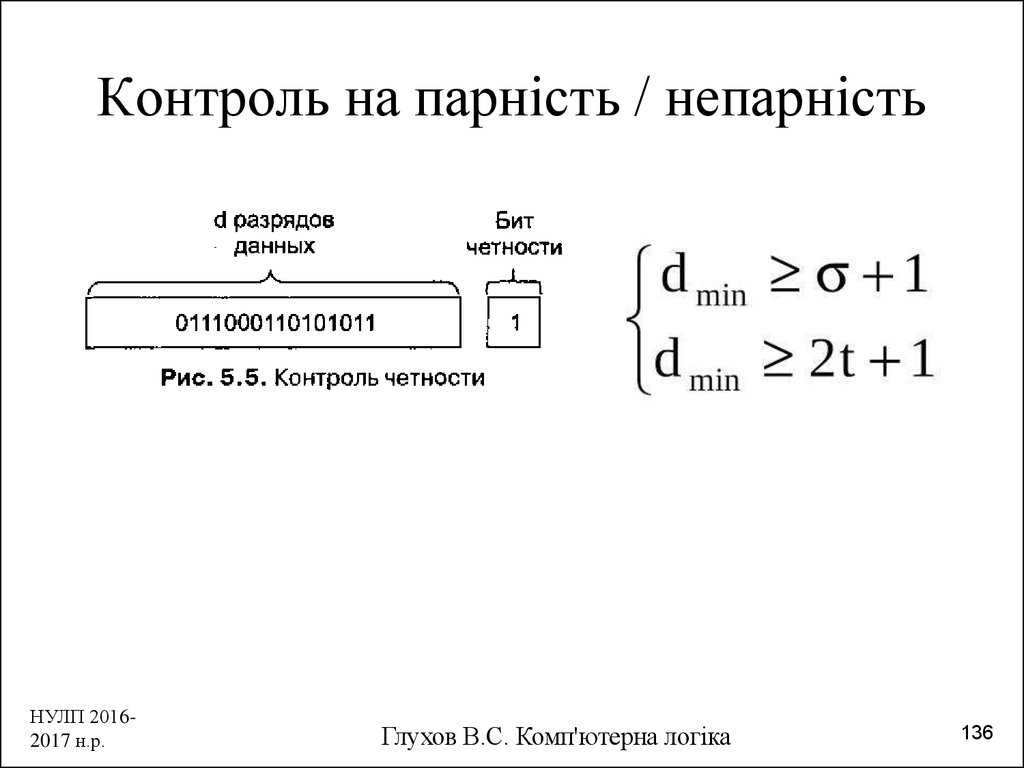

136. Контроль на парність / непарність

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

136

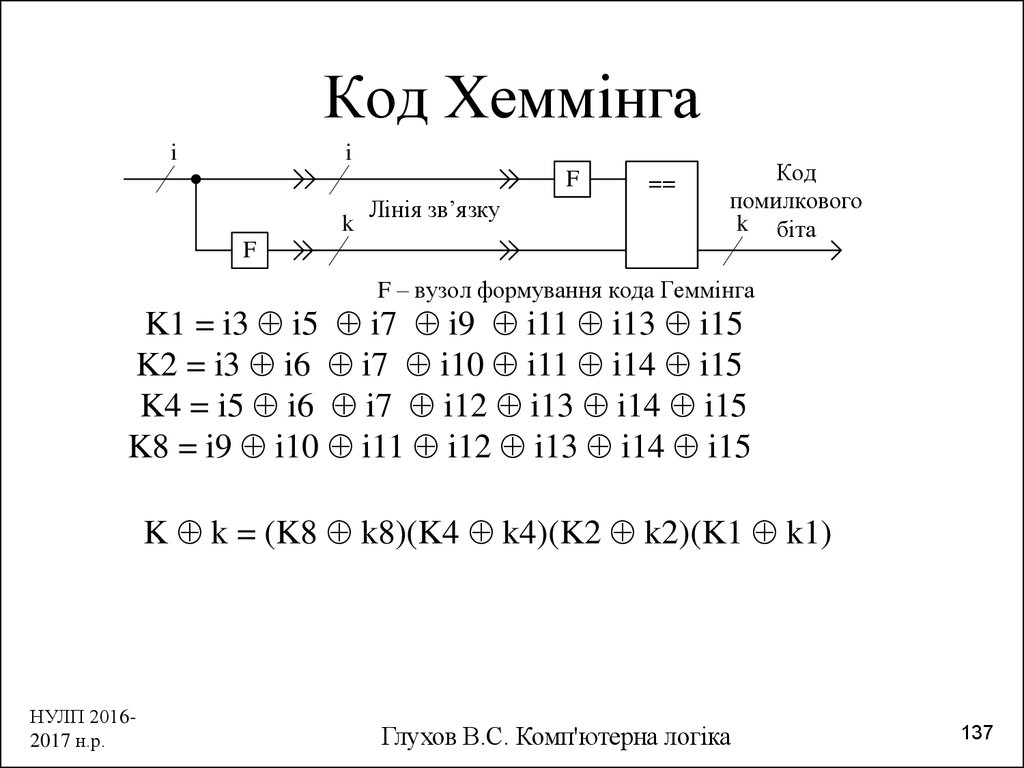

137. Код Хеммінга

ii

F

k

F

Лінія зв’язку

==

Код

помилкового

k біта

F – вузол формування кода Геммінга

K1 = i3 i5 i7 i9 i11 i13 i15

K2 = i3 i6 i7 i10 i11 i14 i15

K4 = i5 i6 i7 i12 i13 i14 i15

K8 = i9 i10 i11 i12 i13 i14 i15

K k = (K8 k8)(K4 k4)(K2 k2)(K1 k1)

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

137

138. Код Хеммінга

Таблиця 1.6.2n1

n2

n3

n4

n5

n6

n7

n8

n9

n10

n11

n12

n13

n14

n15

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

k1

k2

i3

k4

i5

i6

i7

k8

i9

i10

i11

i12

i13

i14

i15

k1 = i3 i5 i7 i9 i11 i13 i15;

k2 = i3 i6 i7 i10 i11 i14 i15;

k4 = i5 i6 i7 i12 i13 i14 i15;

k8 = i9 i10 i11 i12 i13 i14 i15;

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

138

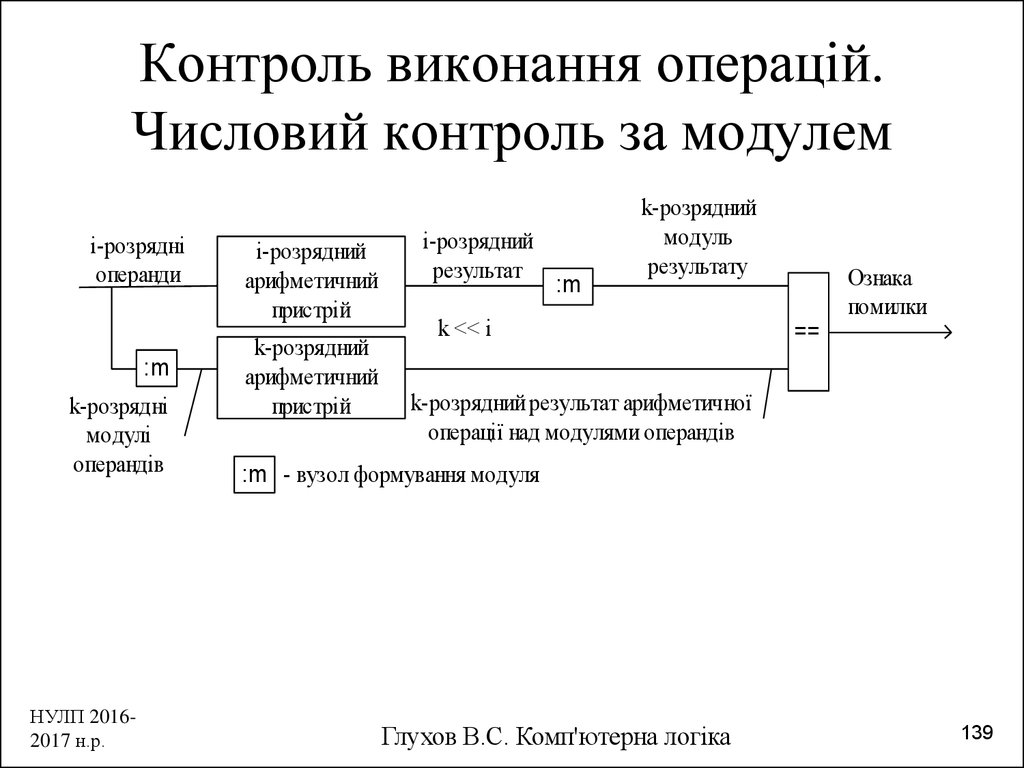

139. Контроль виконання операцій. Числовий контроль за модулем

i-розрядніоперанди

:m

k-розрядні

модулі

операндів

НУЛП 20162017 н.р.

i-розрядний

арифметичний

пристрій

k-розрядний

арифметичний

пристрій

i-розрядний

результат

:m

k-розрядний

модуль

результату

k << i

Ознака

помилки

==

k-розрядний результат арифметичної

операції над модулями операндів

:m - вузол формування модуля

Глухов В.С. Комп'ютерна логіка

139

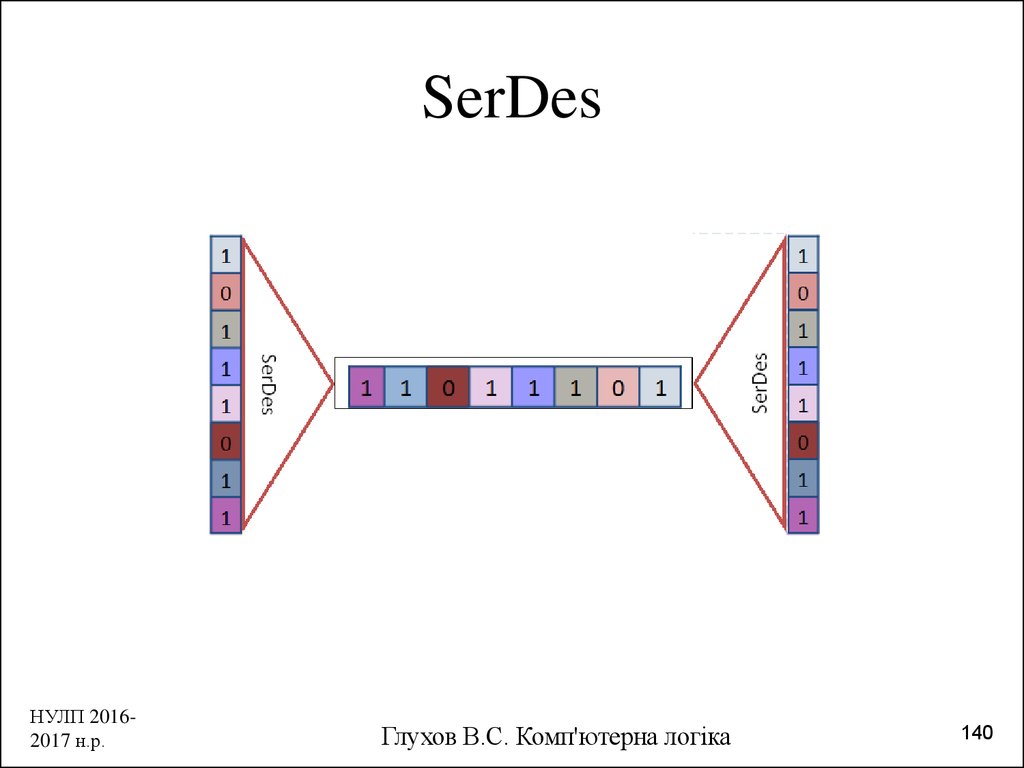

140. SerDes

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

140

141. Строб (вказівник, спрацьовувати)

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

141

142. Кодер захисту інформації

Джерелоінформації

Кодер

джерела

інформації

Кодер

захисту

інформації

Кодер

каналу /

обчислювача

Джерело

завад

Приймач

інформації

Декодер

приймача

інформації

Декодер

захисту

інформації

Декодер

каналу /

обчислювача

Модулятор

Канал /

обчислювач

Демодулятор

Кодер захисту інформації необхідний для інформаційної безпеки

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

142

143. Позиційні системи числення

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

143

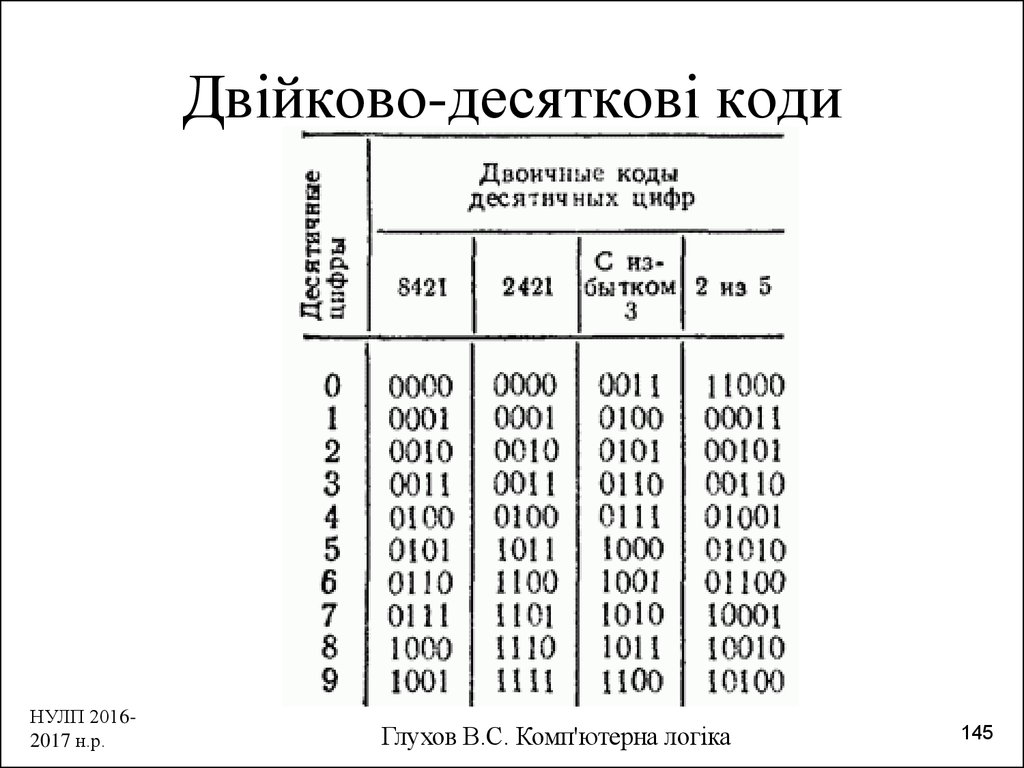

144. Двійково-десяткові коди

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

144

145. Двійково-десяткові коди

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

145

146. Трійкова симетрична (врівноважена) система числення

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

146

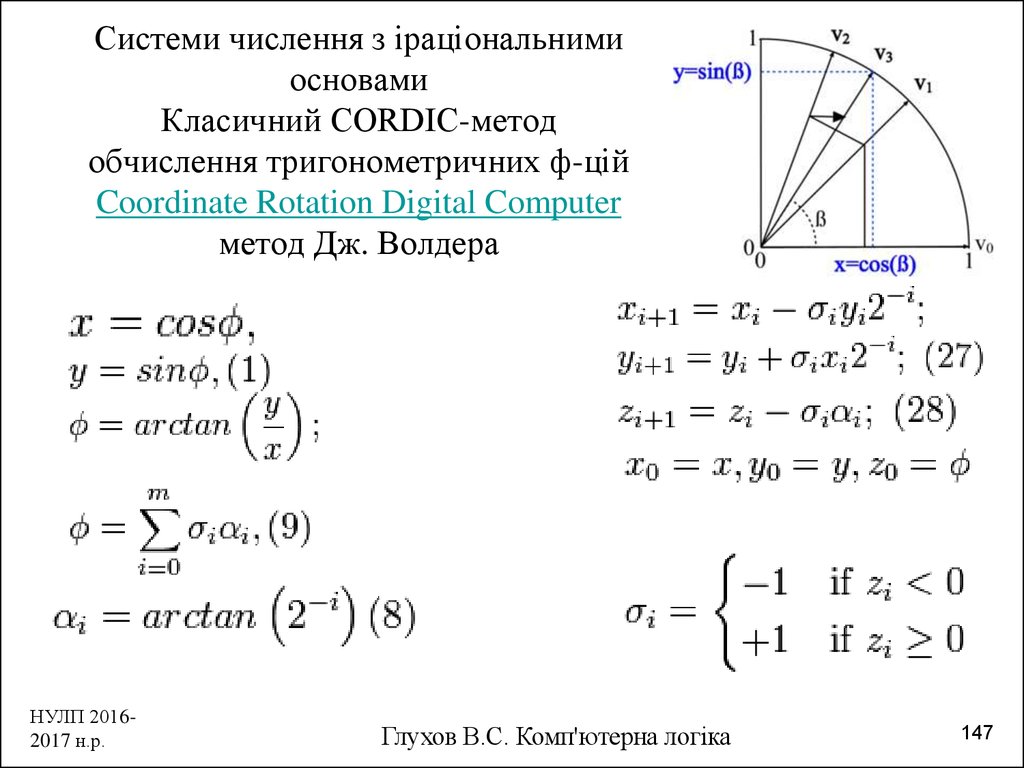

147. Системи числення з іраціональними основами Класичний CORDIC-метод обчислення тригонометричних ф-цій Coordinate Rotation Digital Computer метод Дж. Волдера

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

147

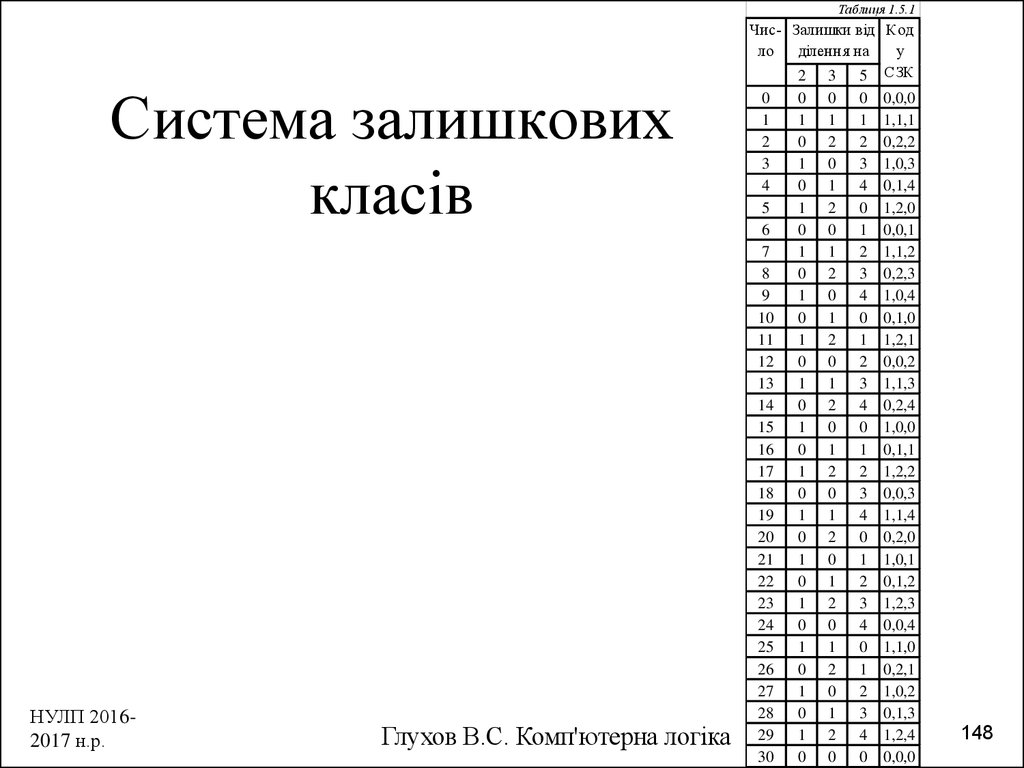

148. Система залишкових класів

Таблиця 1.5.1Система залишкових

класів

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

Чис- Залишки від Код

ло

ділення на

у

2 3 5 СЗК

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

0

1

2

0

1

2

0

1

2

0

1

2

0

1

2

0

1

2

0

1

2

0

1

2

0

1

2

0

1

2

0

0

1

2

3

4

0

1

2

3

4

0

1

2

3

4

0

1

2

3

4

0

1

2

3

4

0

1

2

3

4

0

0,0,0

1,1,1

0,2,2

1,0,3

0,1,4

1,2,0

0,0,1

1,1,2

0,2,3

1,0,4

0,1,0

1,2,1

0,0,2

1,1,3

0,2,4

1,0,0

0,1,1

1,2,2

0,0,3

1,1,4

0,2,0

1,0,1

0,1,2

1,2,3

0,0,4

1,1,0

0,2,1

1,0,2

0,1,3

1,2,4

0,0,0

148

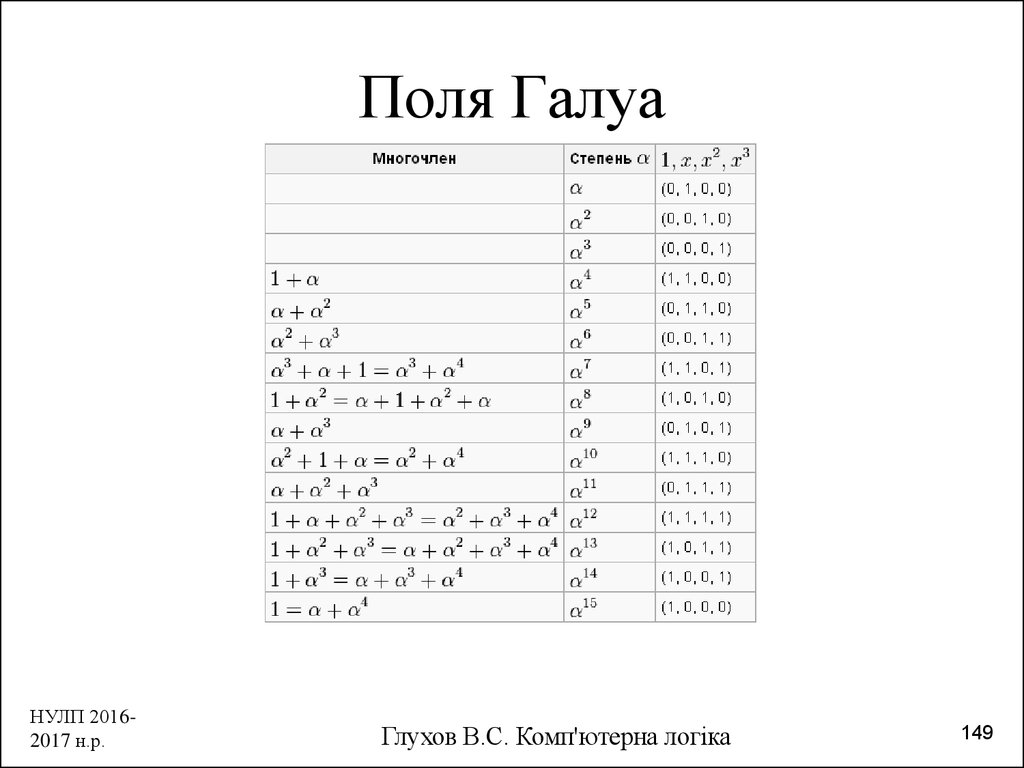

149. Поля Галуа

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

149

150. Сусідній код (код Грея)

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

150

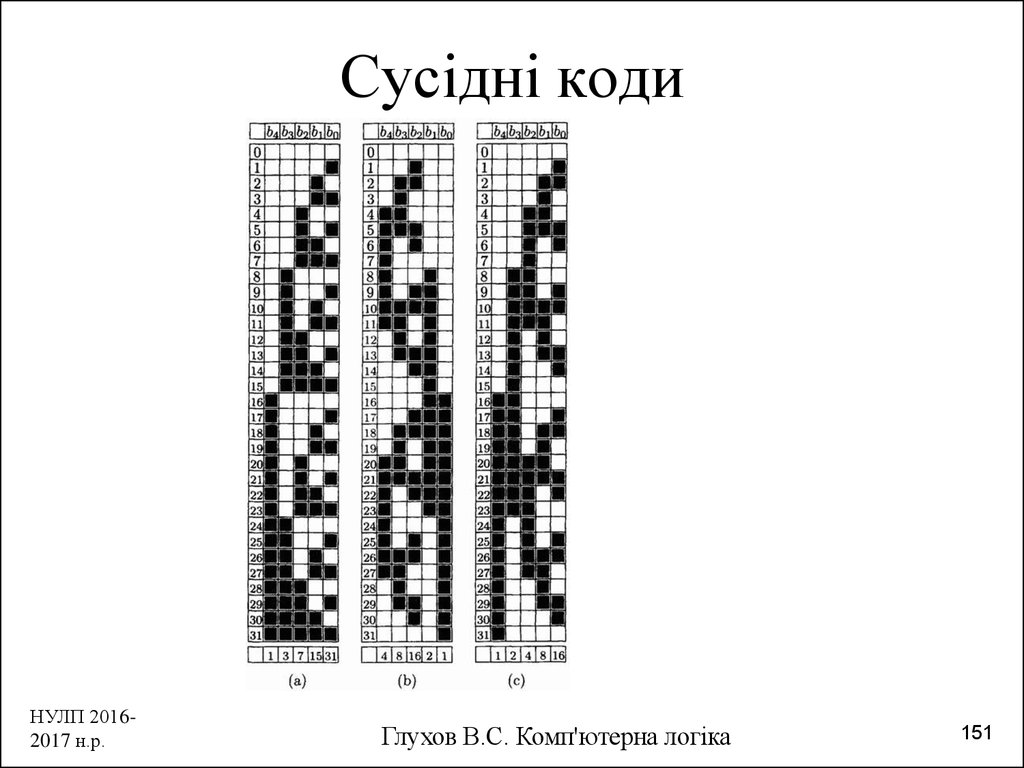

151. Сусідні коди

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

151

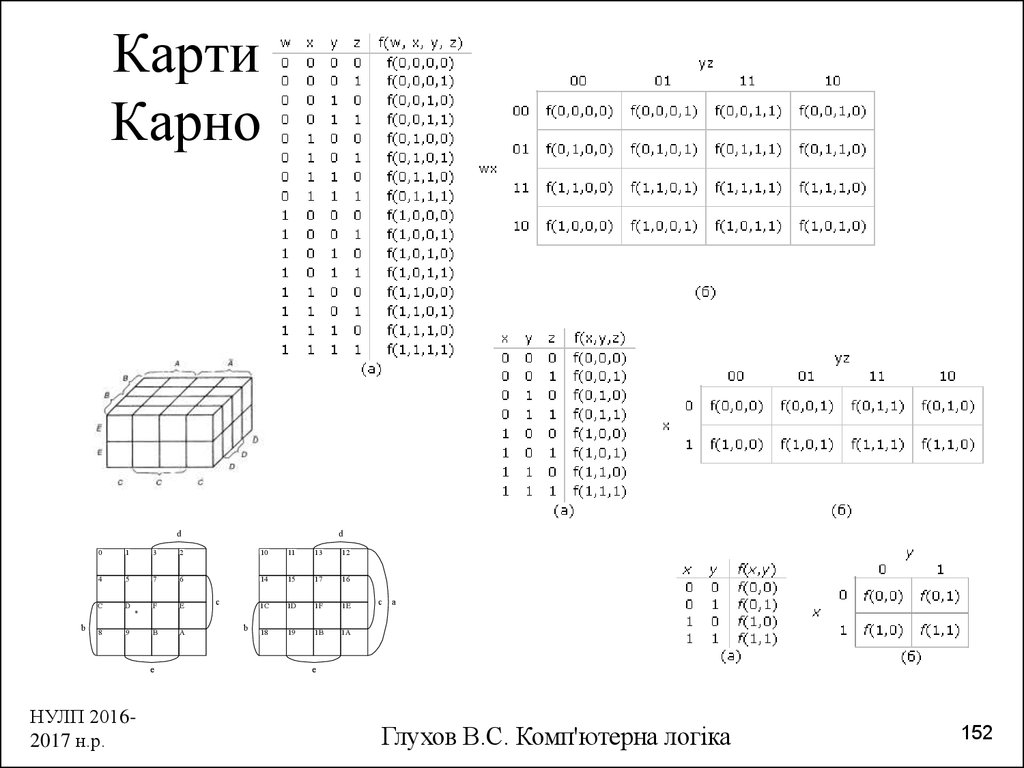

152. Карти Карно

db

d

0

1

3

2

10

11

13

12

4

5

7

6

14

15

17

16

8

C

D

F

E

8

1C

1D

1F

1E

8

9

B

A

18

19

1B

1A

*

e

НУЛП 20162017 н.р.

c

b

c

a

e

Глухов В.С. Комп'ютерна логіка

152

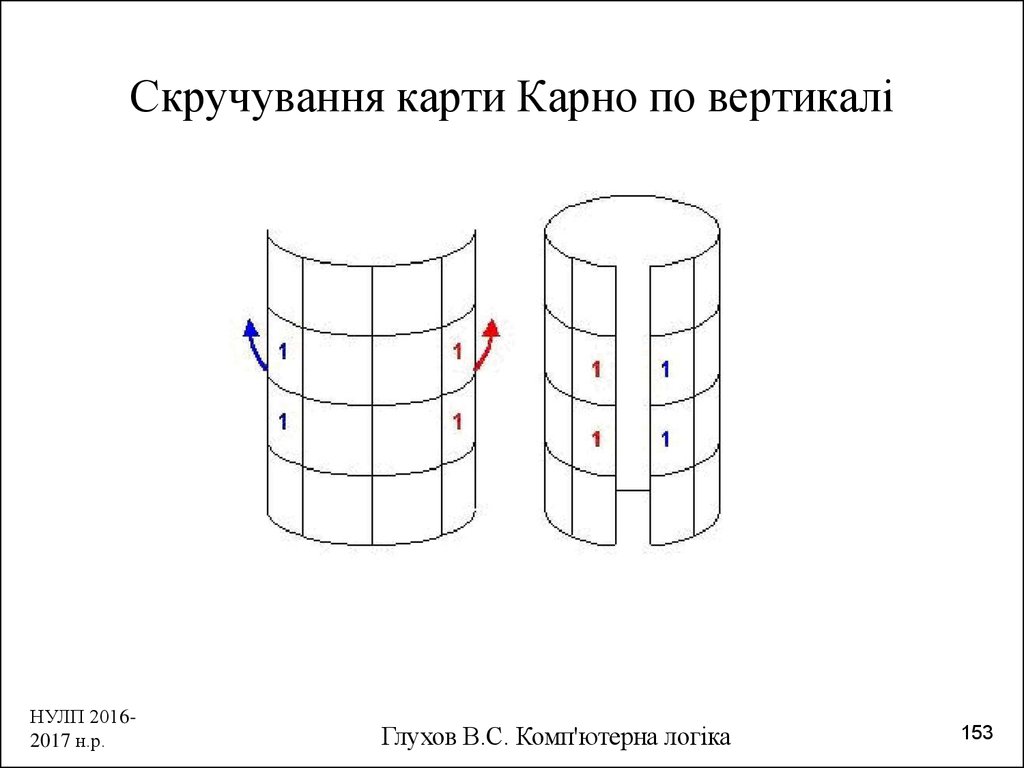

153. Скручування карти Карно по вертикалі

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

153

154. Структурна схема процесу передачі або оброблення інформації

Джерелоінформації

Кодер

джерела

інформації

Кодер

захисту

інформації

Кодер

каналу /

обчислювача

Джерело

завад

Приймач

інформації

НУЛП 20162017 н.р.

Декодер

приймача

інформації

Декодер

захисту

інформації

Декодер

каналу /

обчислювача

Глухов В.С. Комп'ютерна логіка

Модулятор

Канал /

обчислювач

Демодулятор

154

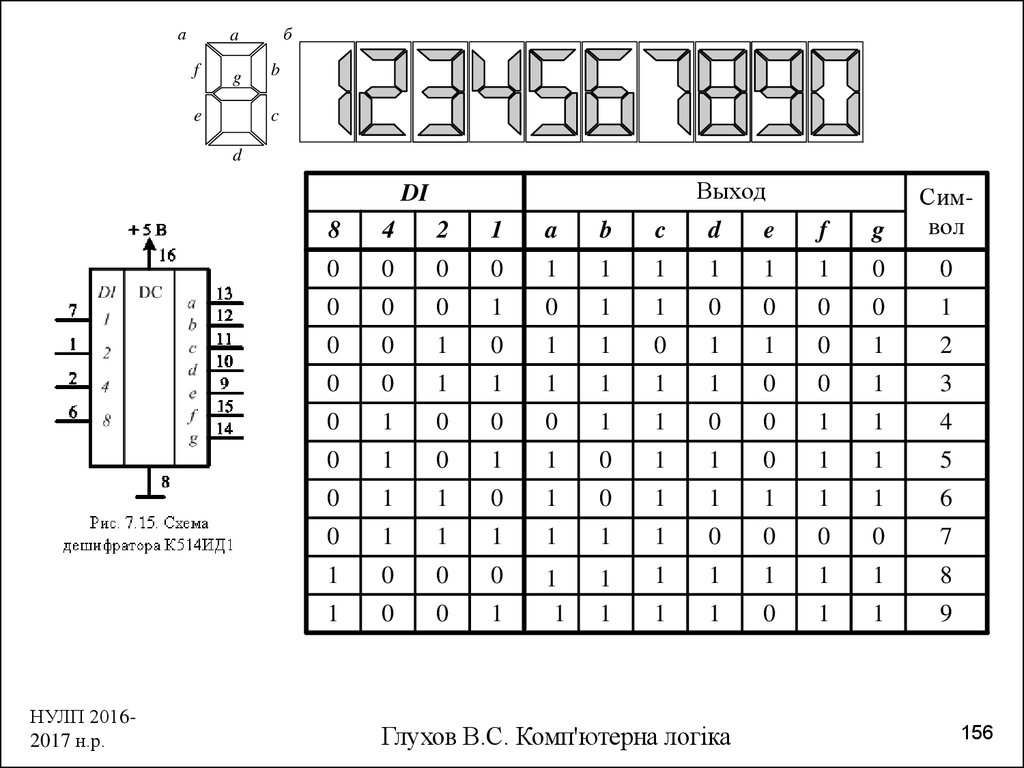

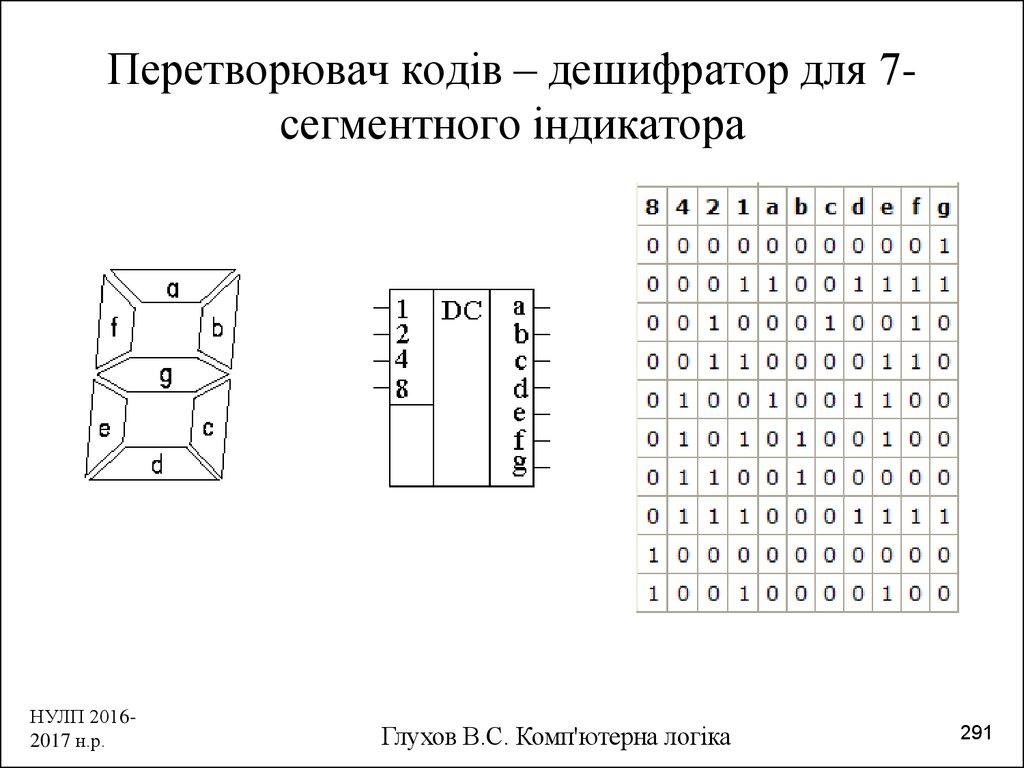

155. Семисегментний індикатор

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

155

156.

аб

a

f

g

e

b

c

d

Выход

8

4

2

1

a

b

c

d

e

f

g

Символ

0

0

0

0

1

1

1

1

1

1

0

0

0

0

0

1

0

1

1

0

0

0

0

1

0

0

1

0

1

1

0

1

1

0

1

2

0

0

1

1

1

1

1

1

0

0

1

3

0

1

0

0

0

1

1

0

0

1

1

4

0

1

0

1

1

0

1

1

0

1

1

5

0

1

1

0

1

0

1

1

1

1

1

6

0

1

1

1

1

1

1

0

0

0

0

7

1

0

0

0

1

1

1

1

8

0

0

1

1

1

1

1

1

1

1

1

0

1

1

9

DI

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

156

157. Алгоритм

• Система формальних правил або приписів,які

визначають

процес

досягнення

конкретної мети – перетворення деяких

даних у бажаний результат, а також набір

умов, які визначають порядок застосування

цих правил до даних, що обробляються

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

157

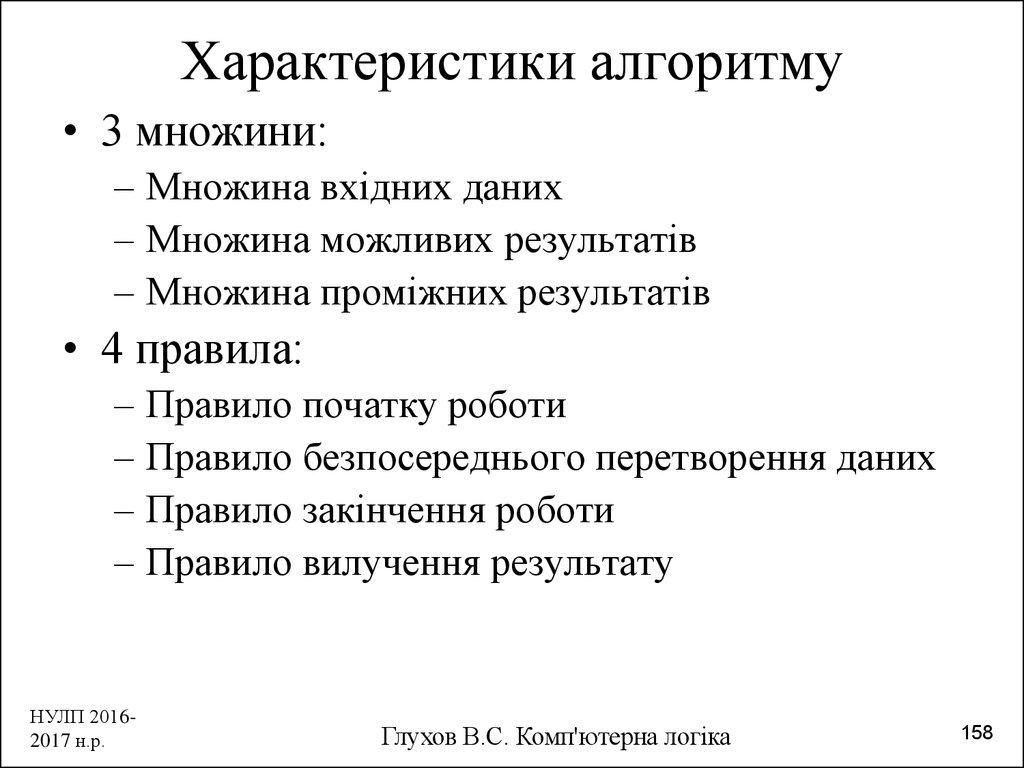

158. Характеристики алгоритму

• 3 множини:– Множина вхідних даних

– Множина можливих результатів

– Множина проміжних результатів

• 4 правила:

–

–

–

–

НУЛП 20162017 н.р.

Правило початку роботи

Правило безпосереднього перетворення даних

Правило закінчення роботи

Правило вилучення результату

Глухов В.С. Комп'ютерна логіка

158

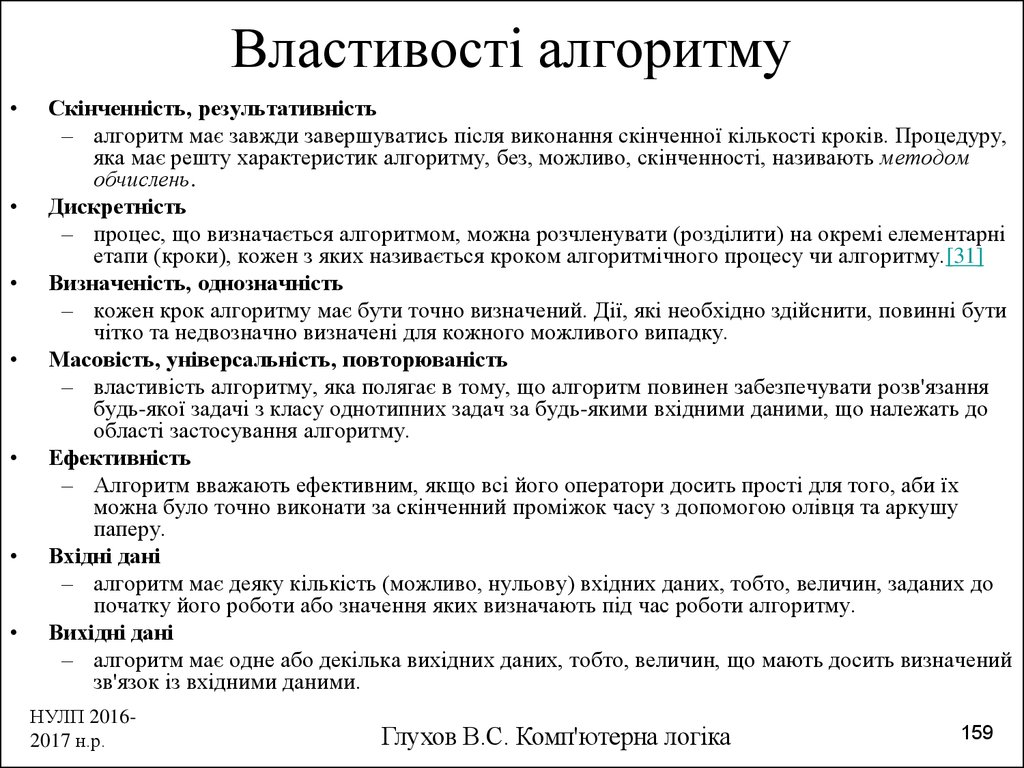

159. Властивості алгоритму

Скінченність, результативність

– алгоритм має завжди завершуватись після виконання скінченної кількості кроків. Процедуру,

яка має решту характеристик алгоритму, без, можливо, скінченності, називають методом

обчислень.

Дискретність

– процес, що визначається алгоритмом, можна розчленувати (розділити) на окремі елементарні

етапи (кроки), кожен з яких називається кроком алгоритмічного процесу чи алгоритму.[31]

Визначеність, однозначність

– кожен крок алгоритму має бути точно визначений. Дії, які необхідно здійснити, повинні бути

чітко та недвозначно визначені для кожного можливого випадку.

Масовість, універсальність, повторюваність

– властивість алгоритму, яка полягає в тому, що алгоритм повинен забезпечувати розв'язання

будь-якої задачі з класу однотипних задач за будь-якими вхідними даними, що належать до

області застосування алгоритму.

Ефективність

– Алгоритм вважають ефективним, якщо всі його оператори досить прості для того, аби їх

можна було точно виконати за скінченний проміжок часу з допомогою олівця та аркушу

паперу.

Вхідні дані

– алгоритм має деяку кількість (можливо, нульову) вхідних даних, тобто, величин, заданих до

початку його роботи або значення яких визначають під час роботи алгоритму.

Вихідні дані

– алгоритм має одне або декілька вихідних даних, тобто, величин, що мають досить визначений

зв'язок із вхідними даними.

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

159

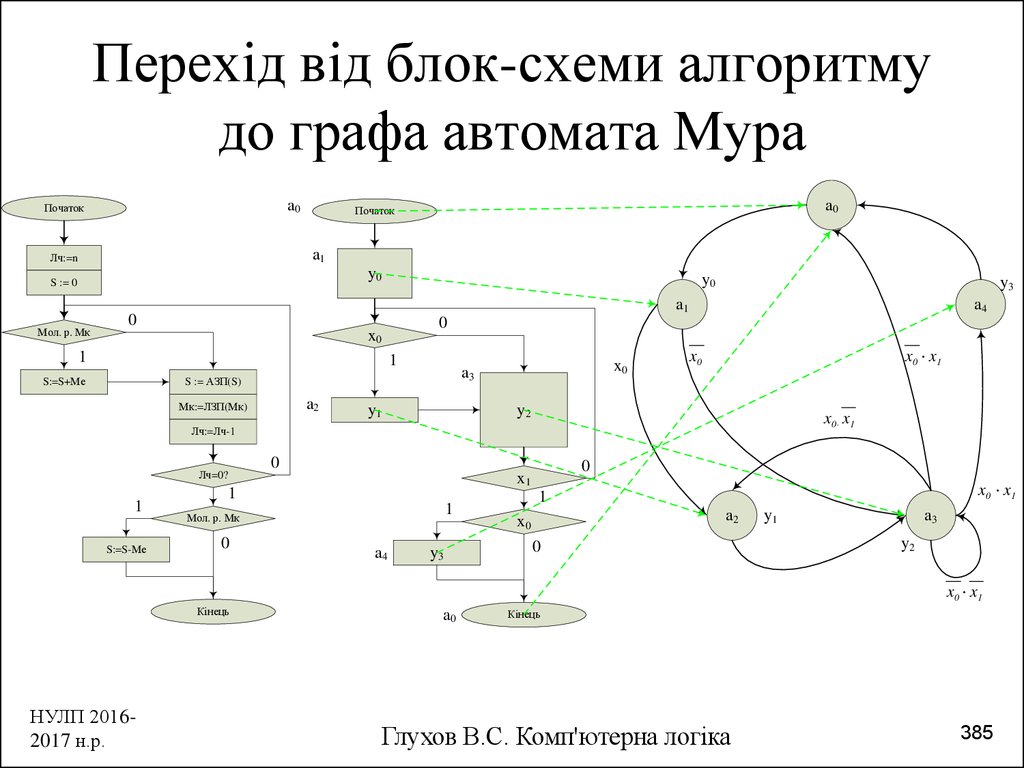

160. Представлення алгоритмів http://uk.wikipedia.org/wiki/Алгоритм

• У процесі розробки алгоритму можуть використовуватисьрізні способи його опису, які відрізняються за простотою,

наочністю, компактністю, мірою формалізації, орієнтації

на машинну реалізацію тощо.

–

–

–

–

–

словесна або вербальна (неформальні мови, формульно-словесна);

псевдокод (формальні алгоритмічні мови);

Таблична;

Часові діаграми;

схемна:

• Функціональні схеми;

• блок-схема, виконується за вимогами стандарту

• граф автомата

– інші

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

160

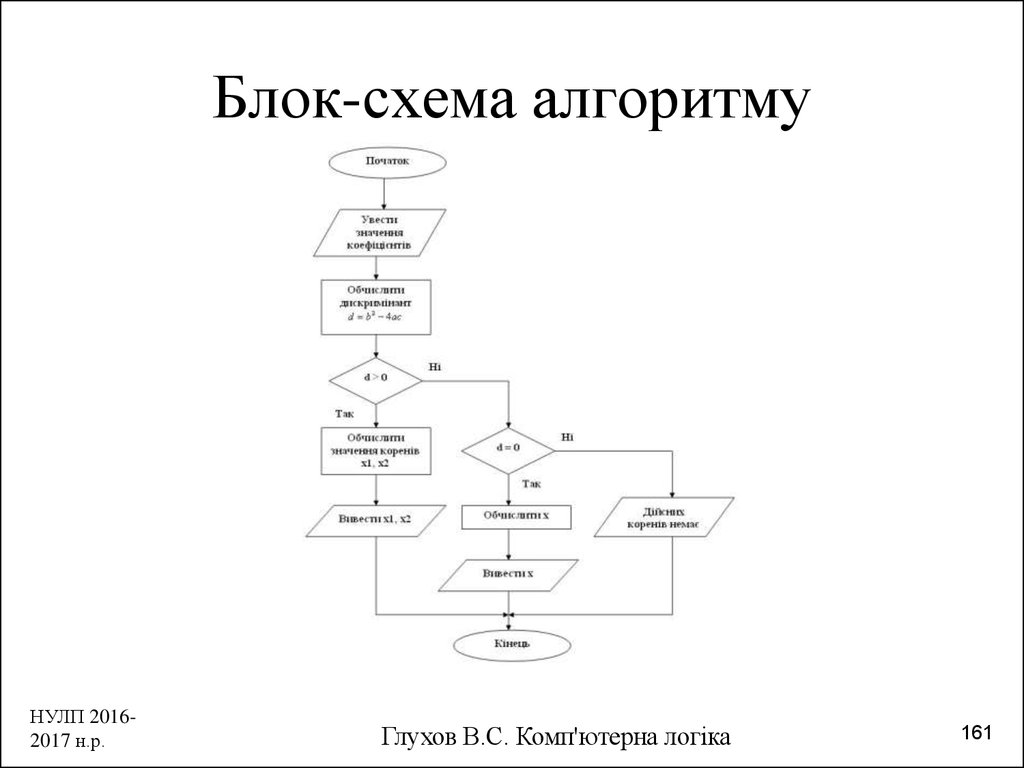

161. Блок-схема алгоритму

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

161

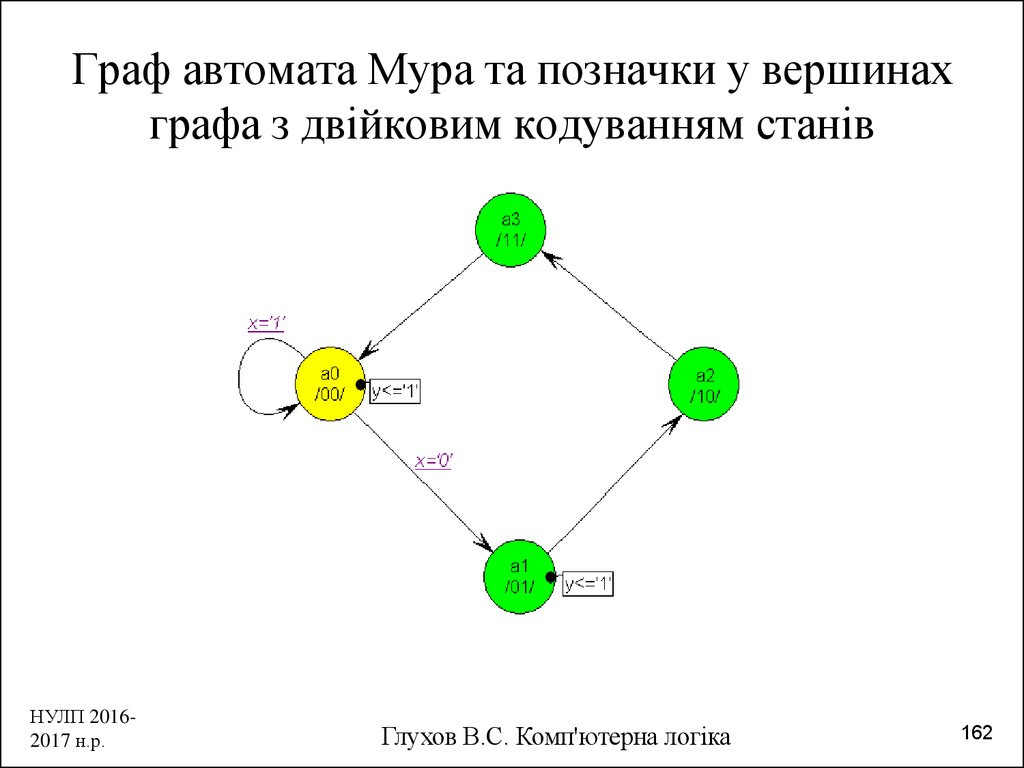

162. Граф автомата Мура та позначки у вершинах графа з двійковим кодуванням станів

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

162

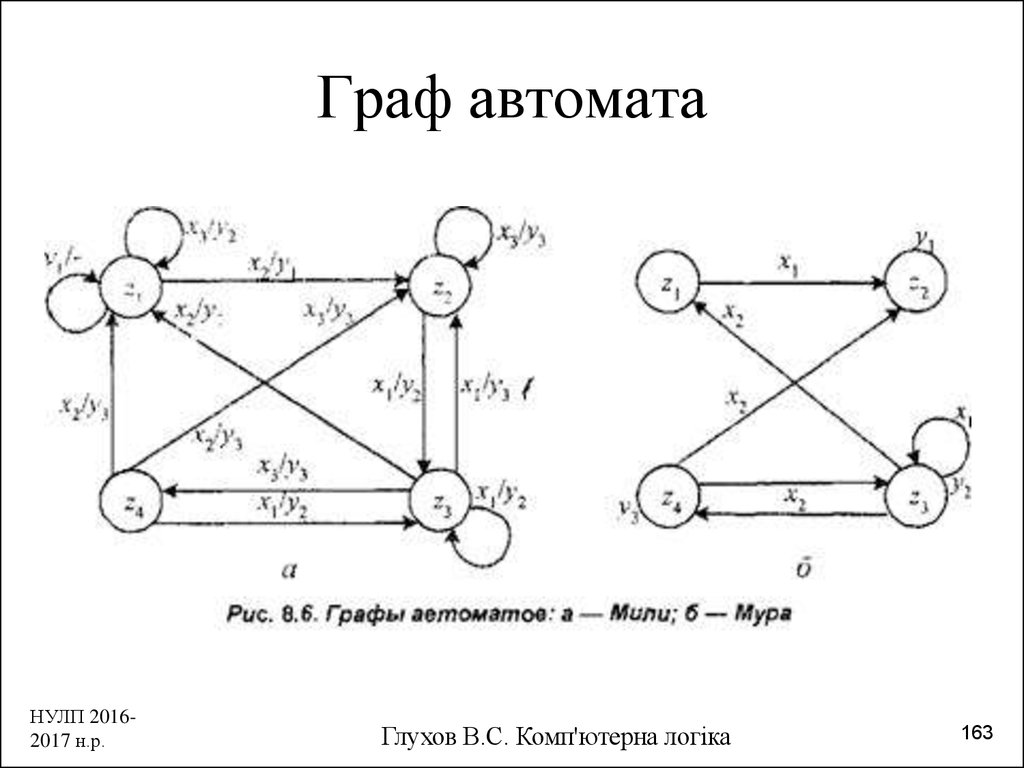

163. Граф автомата

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

163

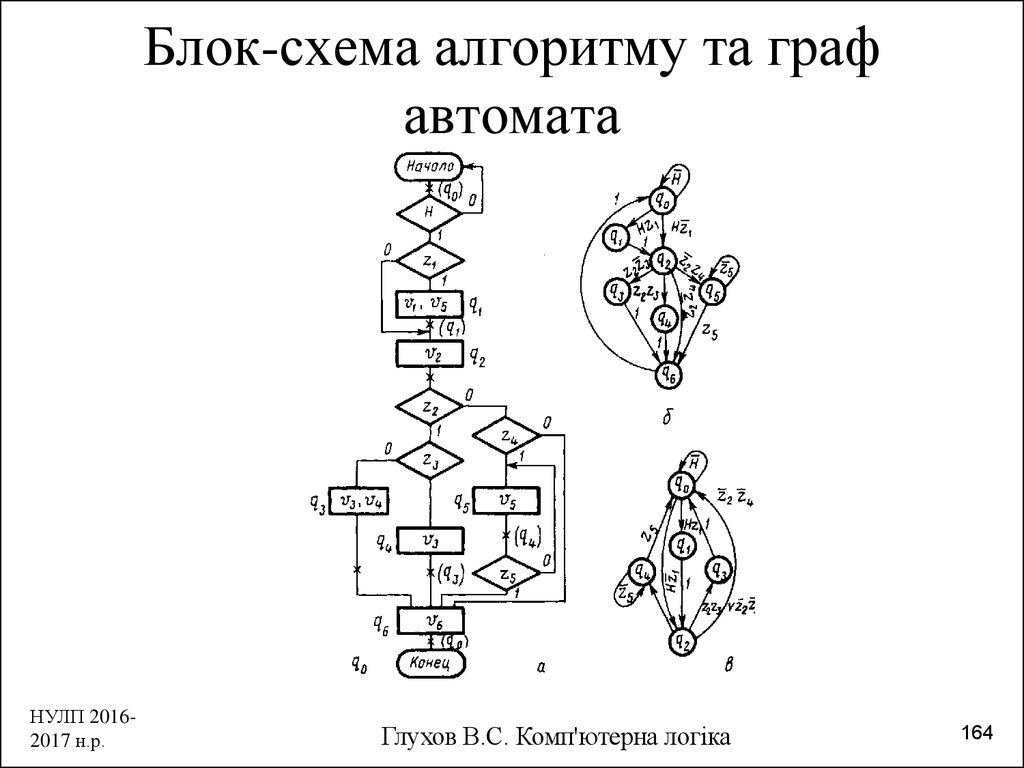

164. Блок-схема алгоритму та граф автомата

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

164

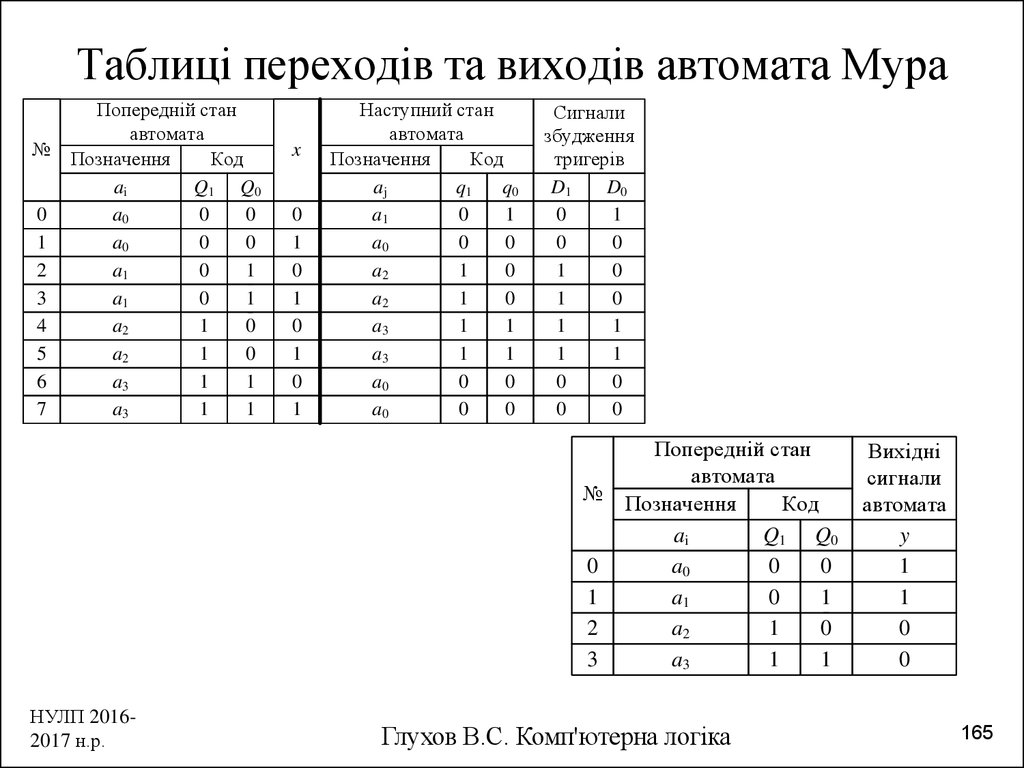

165. Таблиці переходів та виходів автомата Мура

№0

1

2

3

4

5

6

7

Попередній стан

автомата

Позначення

Код

ai

Q1 Q0

a0

0

0

a0

0

0

0

1

a1

0

1

a1

1

0

a2

1

0

a2

a3

1

1

1

1

a3

x

0

1

0

1

0

1

0

1

Наступний стан

автомата

Позначення

Код

aj

q1

q0

a1

0

1

a0

0

0

1

0

a2

1

0

a2

1

1

a3

1

1

a3

a0

0

0

0

0

a0

Сигнали

збудження

тригерів

D1

D0

0

1

0

0

1

0

1

0

1

1

1

1

0

0

0

0

№

0

1

2

3

НУЛП 20162017 н.р.

Попередній стан

автомата

Позначення

Код

ai

Q1 Q0

0

0

a0

0

1

a1

1

0

a2

1

1

a3

Глухов В.С. Комп'ютерна логіка

Вихідні

сигнали

автомата

y

1

1

0

0

165

166. Функціональна схема автомата Мура

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

166

167. Часова діаграма роботи автомата Мура

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

167

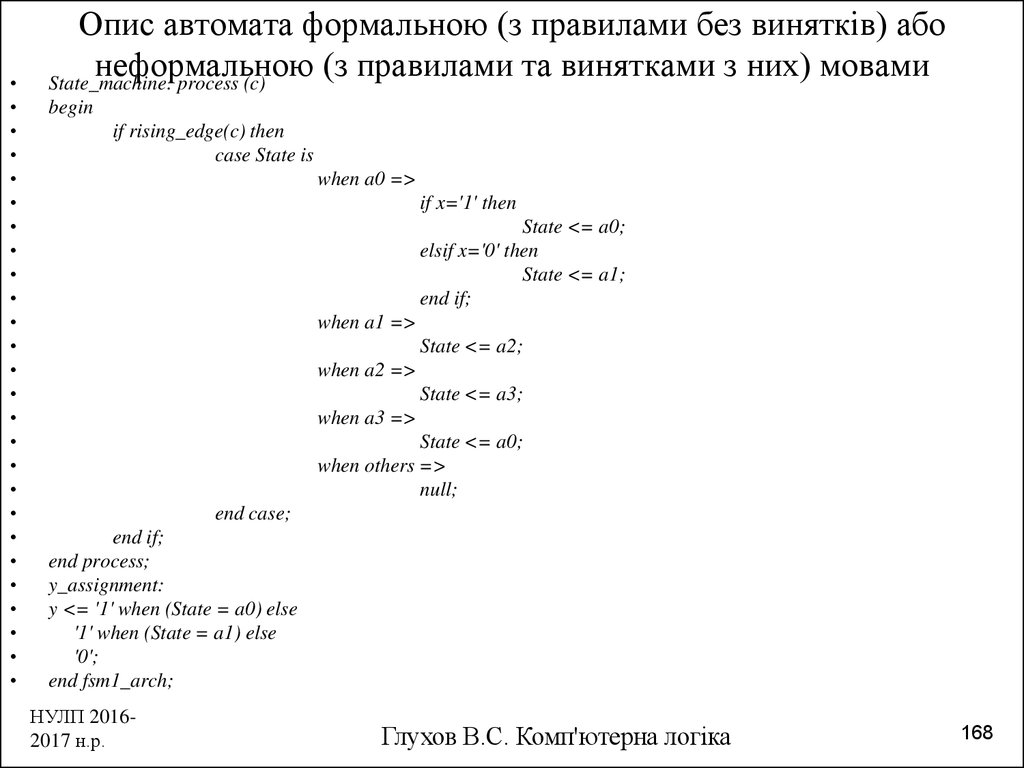

168. Опис автомата формальною (з правилами без винятків) або неформальною (з правилами та винятками з них) мовами

Опис автомата формальною (з правилами без винятків) або

неформальною (з правилами та винятками з них) мовами

State_machine: process (c)

begin

if rising_edge(c) then

case State is

when a0 =>

if x='1' then

State <= a0;

elsif x='0' then

State <= a1;

end if;

when a1 =>

State <= a2;

when a2 =>

State <= a3;

when a3 =>

State <= a0;

when others =>

null;

end case;

end if;

end process;

y_assignment:

y <= '1' when (State = a0) else

'1' when (State = a1) else

'0';

end fsm1_arch;

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

168

169. Теза Черча

Теза Черча• Теза Черча — для кожного алгоритму

може

бути

побудована

формальна

алгоритмічна система (ФАС), яка його

реалізує

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

169

170. Універсальні ФАС – можуть реалізувати будь-який алгоритм

Рекурсивні функції

Машина Тюринга

Машина Поста

Схеми Колмогорова-Успенського

Нормальні алгорифми Маркова

Скінченні цифрові автомати (комп’ютери та їх програми)

зараз ФАС –

– програма для універсального комп’ютера або

– новий (спеціалізований) комп’ютер і програма для нього

http://uk.wikipedia.org/wiki/Алгоритм

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

170

171. Повна побудова алгоритму

• формулювання задачі;• побудови моделі абстрактного алгоритм;

– АБСТРАКТНИЙ - той, що є наслідком мисленого виділення з усіх

ознак, властивостей і зв'язків конкретного предмета його основних,

найзагальніших;

розроблення абстрактного алгоритму;

перевіряння правильності абстрактного алгоритму;

реалізації структурного алгоритму;

аналізу алгоритму і його складності;

перевіряння реалізації структурного алгоритму;

оформлення документації.

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

171

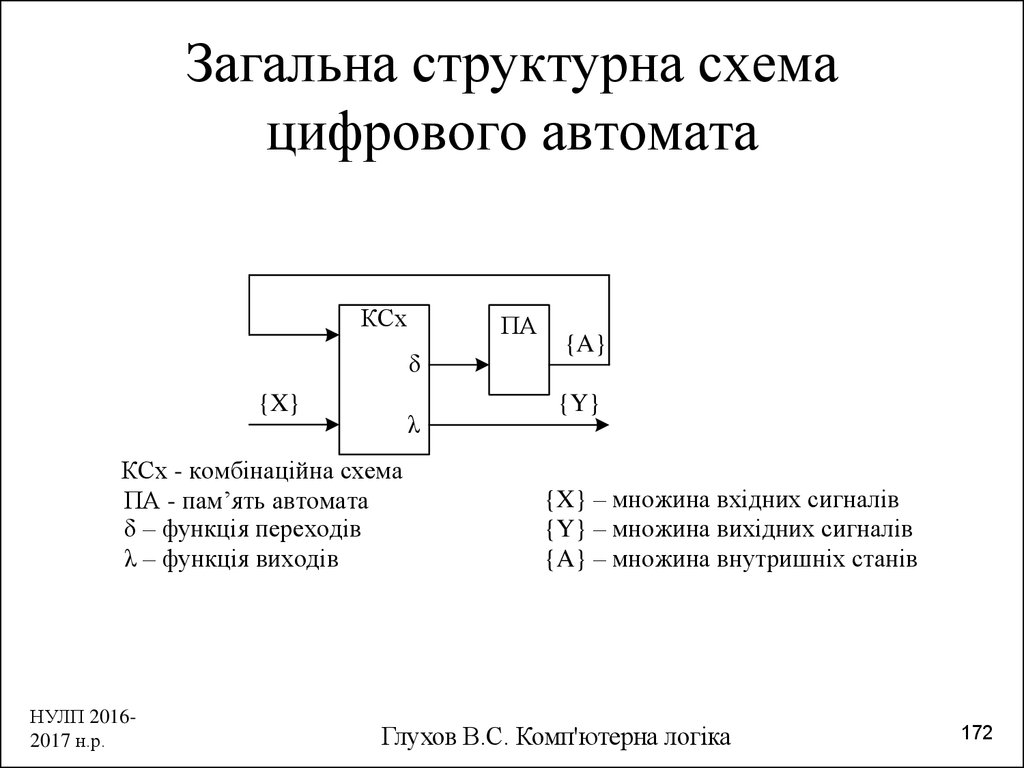

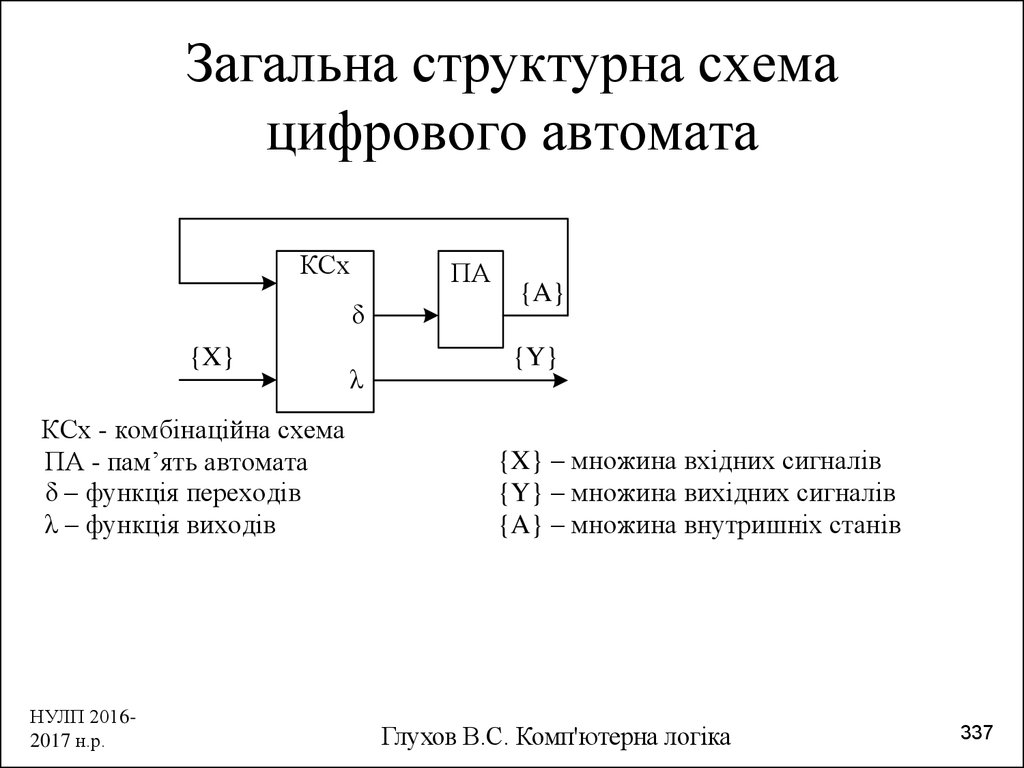

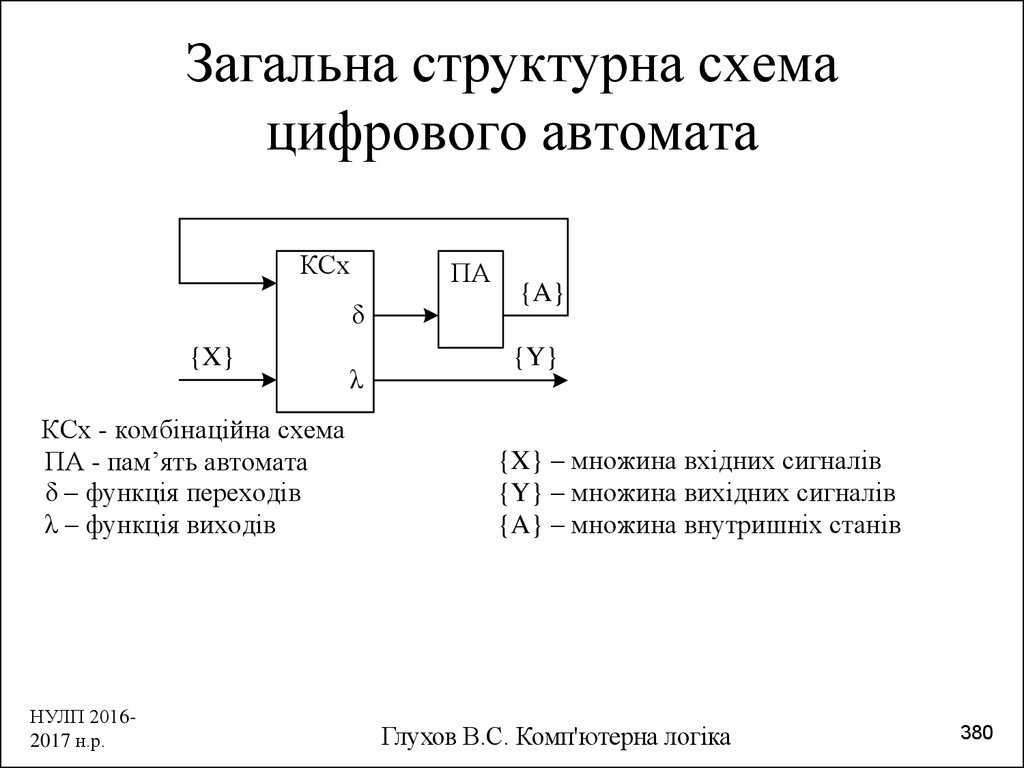

172. Загальна структурна схема цифрового автомата

КСхПА

δ

{X}

λ

КСх - комбінаційна схема

ПА - пам’ять автомата

δ – функція переходів

λ – функція виходів

НУЛП 20162017 н.р.

{A}

{Y}

{X} – множина вхідних сигналів

{Y} – множина вихідних сигналів

{A} – множина внутришніх станів

Глухов В.С. Комп'ютерна логіка

172

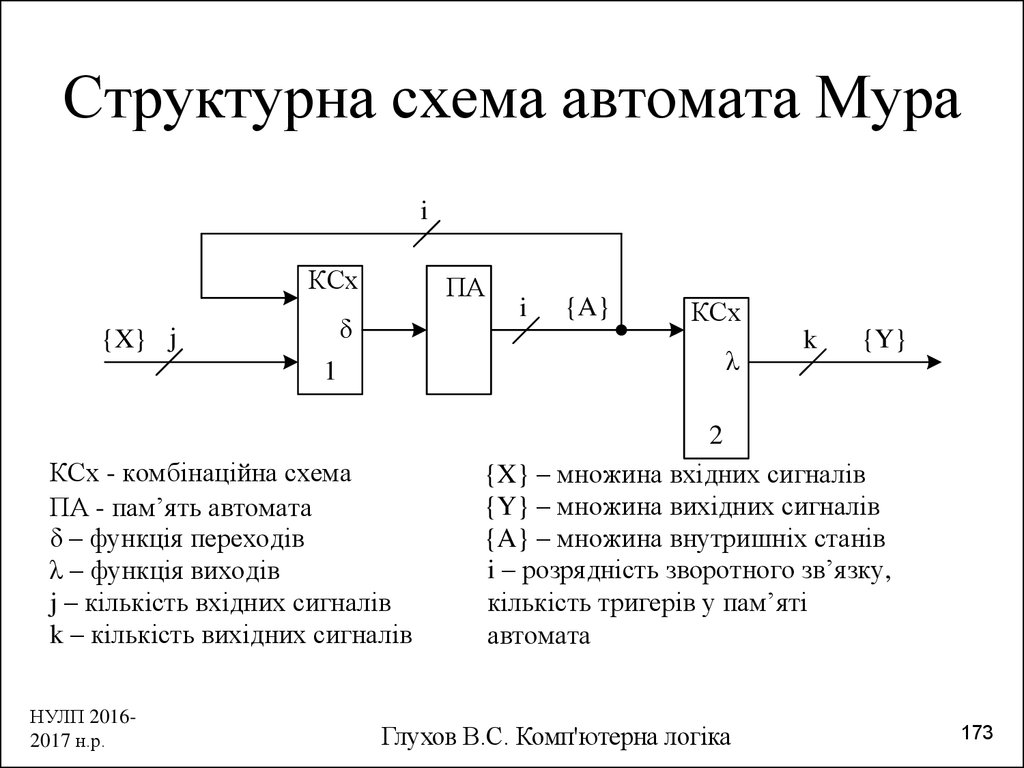

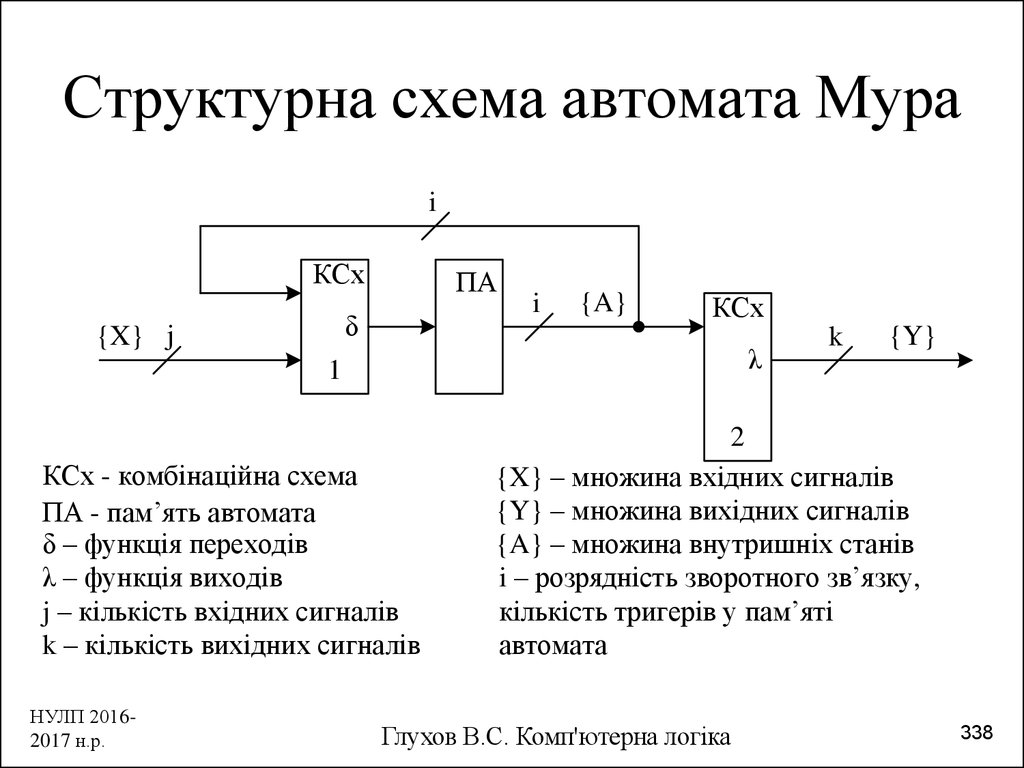

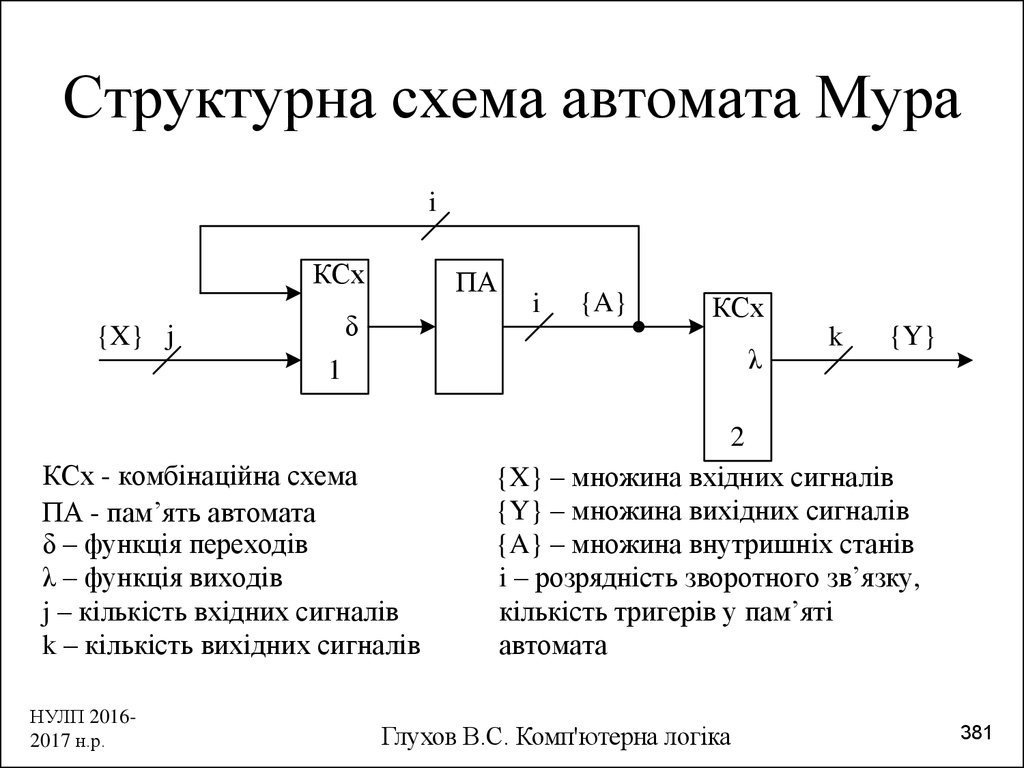

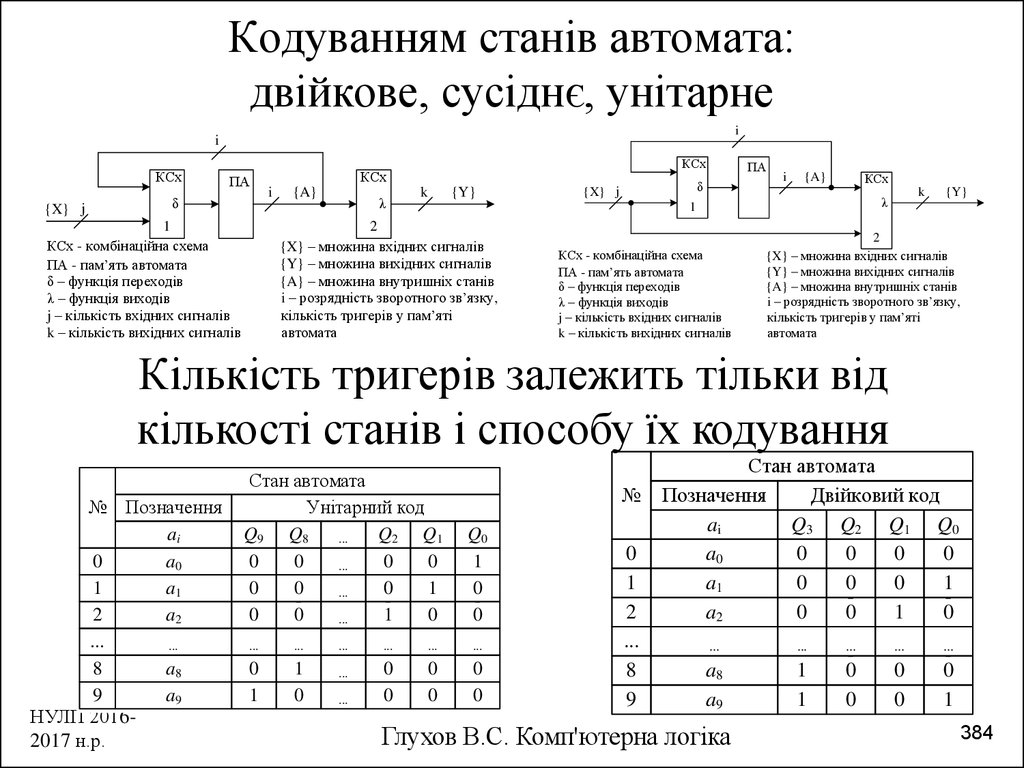

173. Структурна схема автомата Мура

iКСх

ПА

δ

{X} j

{A}

КСх

λ

1

КСх - комбінаційна схема

ПА - пам’ять автомата

δ – функція переходів

λ – функція виходів

j – кількість вхідних сигналів

k – кількість вихідних сигналів

НУЛП 20162017 н.р.

i

k

{Y}

2

{X} – множина вхідних сигналів

{Y} – множина вихідних сигналів

{A} – множина внутришніх станів

i – розрядність зворотного зв’язку,

кількість тригерів у пам’яті

автомата

Глухов В.С. Комп'ютерна логіка

173

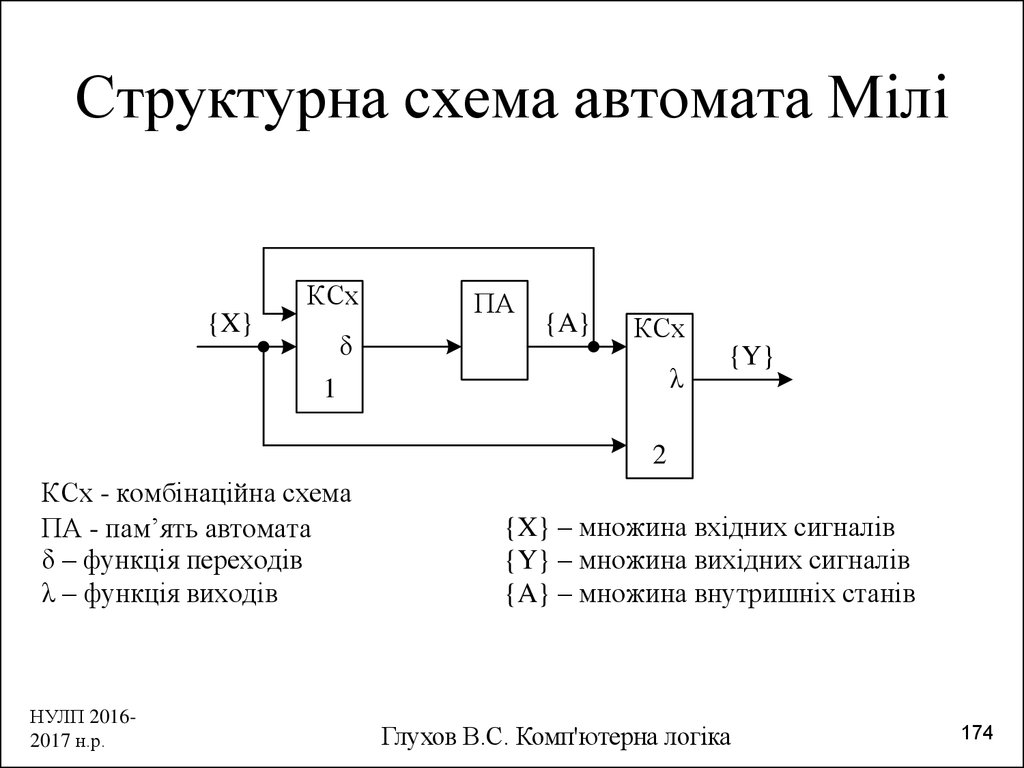

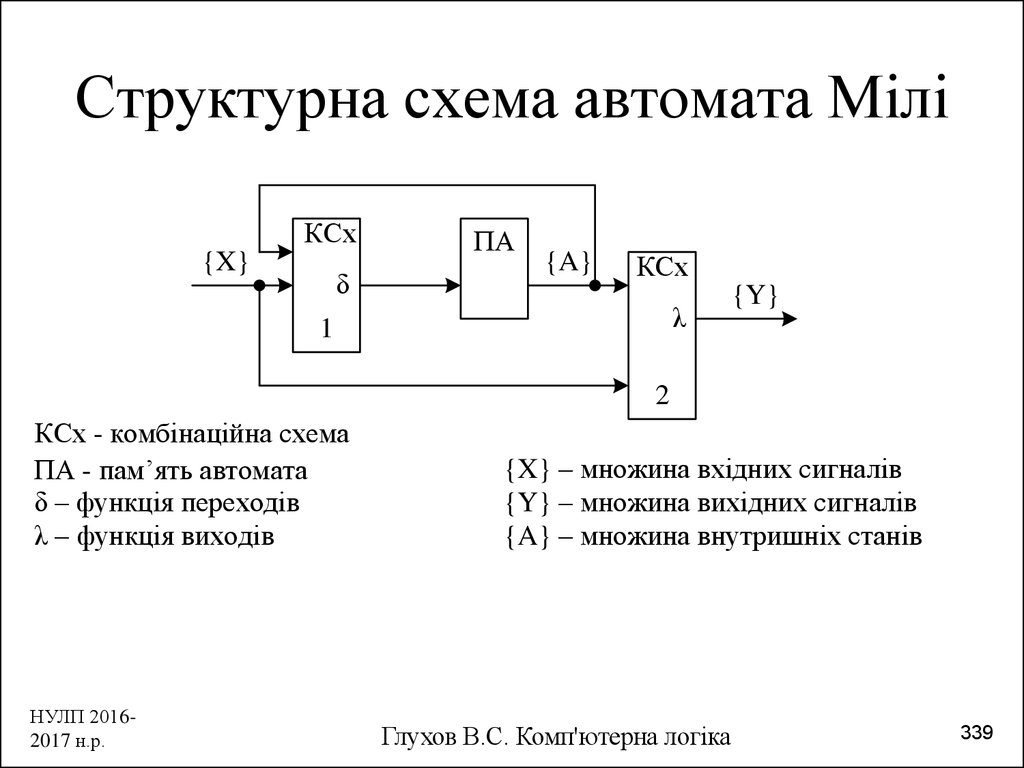

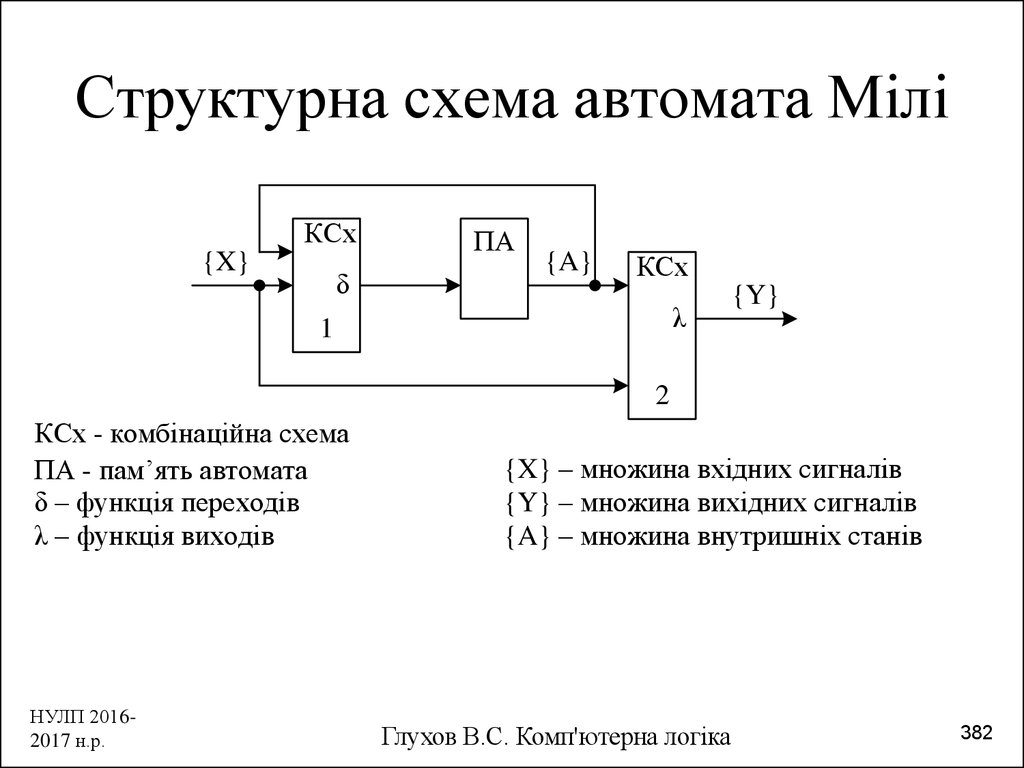

174. Структурна схема автомата Мілі

КСх{X}

δ

ПА

{A}

КСх

λ

1

{Y}

2

КСх - комбінаційна схема

ПА - пам’ять автомата

δ – функція переходів

λ – функція виходів

НУЛП 20162017 н.р.

{X} – множина вхідних сигналів

{Y} – множина вихідних сигналів

{A} – множина внутришніх станів

Глухов В.С. Комп'ютерна логіка

174

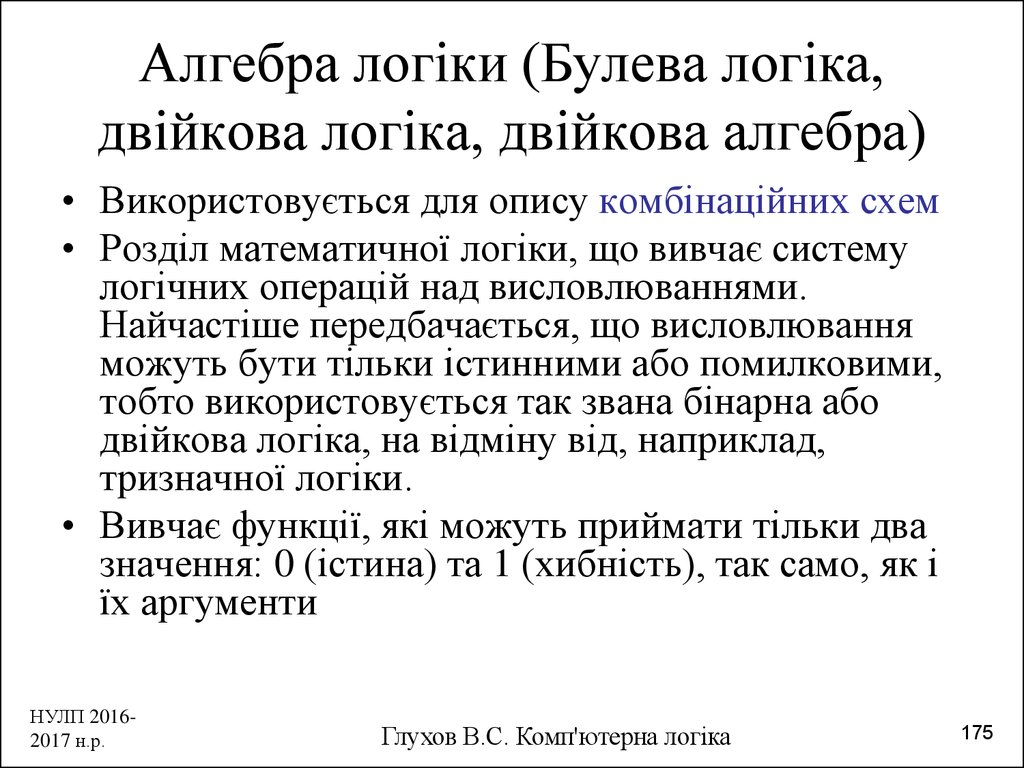

175. Алгебра логіки (Булева логіка, двійкова логіка, двійкова алгебра)

• Використовується для опису комбінаційних схем• Розділ математичної логіки, що вивчає систему

логічних операцій над висловлюваннями.

Найчастіше передбачається, що висловлювання

можуть бути тільки істинними або помилковими,

тобто використовується так звана бінарна або

двійкова логіка, на відміну від, наприклад,

тризначної логіки.

• Вивчає функції, які можуть приймати тільки два

значення: 0 (істина) та 1 (хибність), так само, як і

їх аргументи

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

175

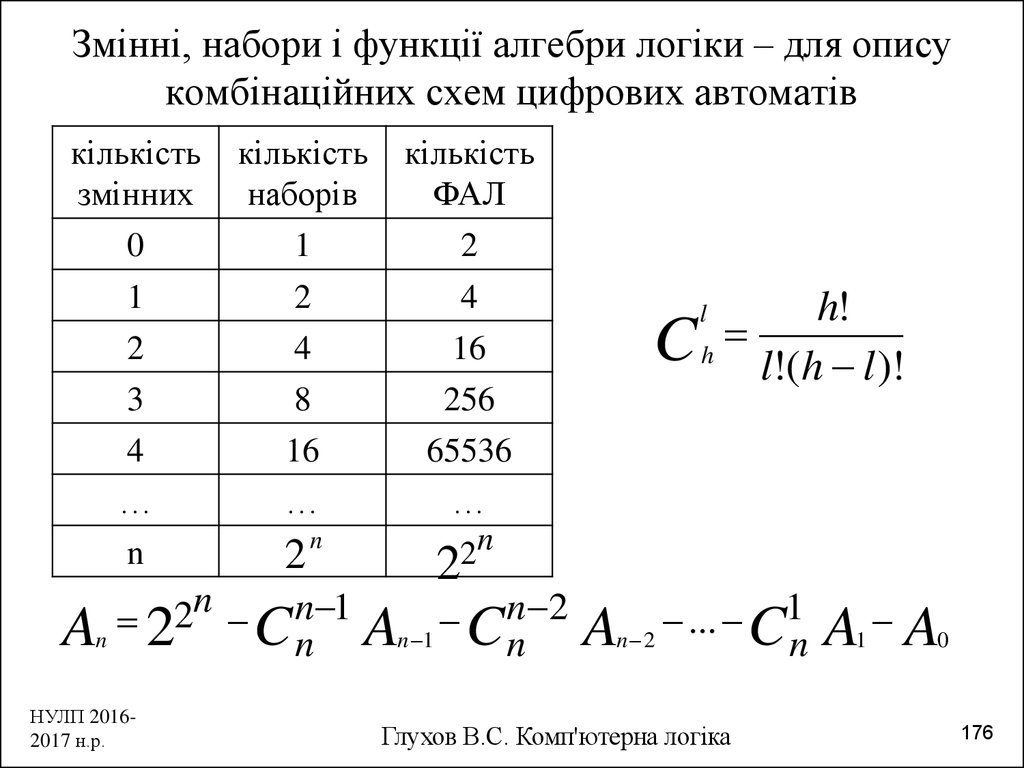

176. Змінні, набори і функції алгебри логіки – для опису комбінаційних схем цифрових автоматів

кількістьзмінних

0

кількість

наборів

1

кількість

ФАЛ

2

1

2

3

2

4

8

4

16

256

4

…

n

16

…

65536

…

n

2

2

2n

n

n 1

2

An 2 C n

НУЛП 20162017 н.р.

n 2

An 1 C n

h!

C h l!(h l )!

l

1

...

Cn

An 2

Глухов В.С. Комп'ютерна логіка

A A

1

0

176

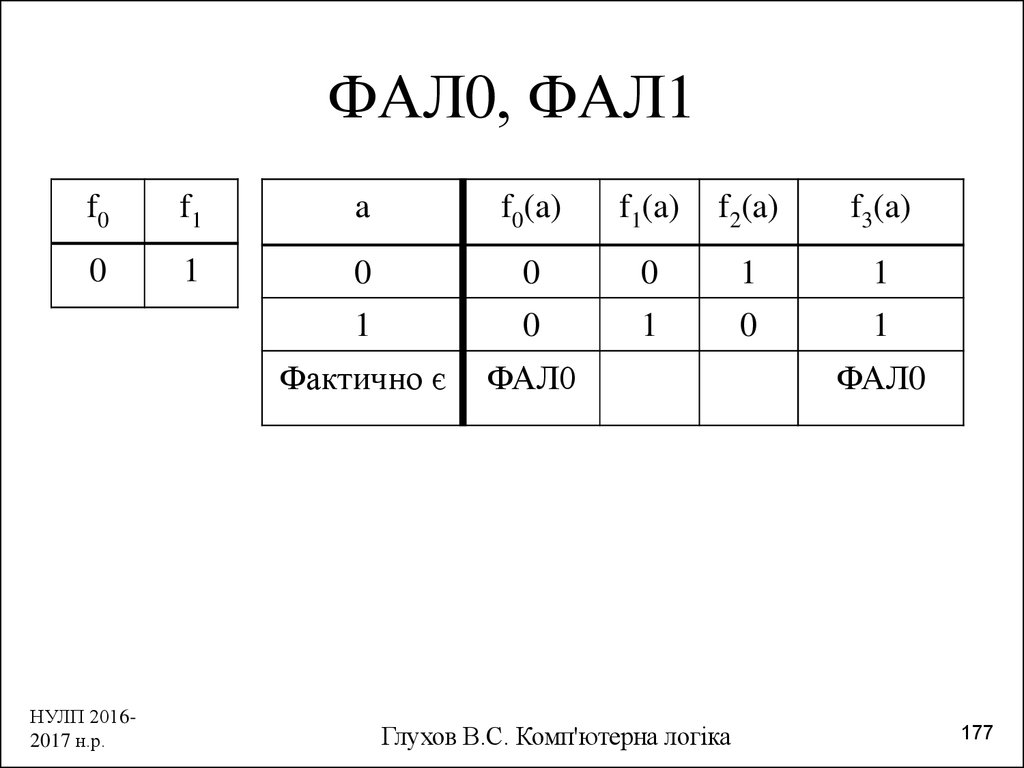

177. ФАЛ0, ФАЛ1

f0f1

a

f0(a)

f1(a)

f2(a)

f3(a)

0

1

0

0

0

1

1

1

0

1

0

1

Фактично є

ФАЛ0

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

ФАЛ0

177

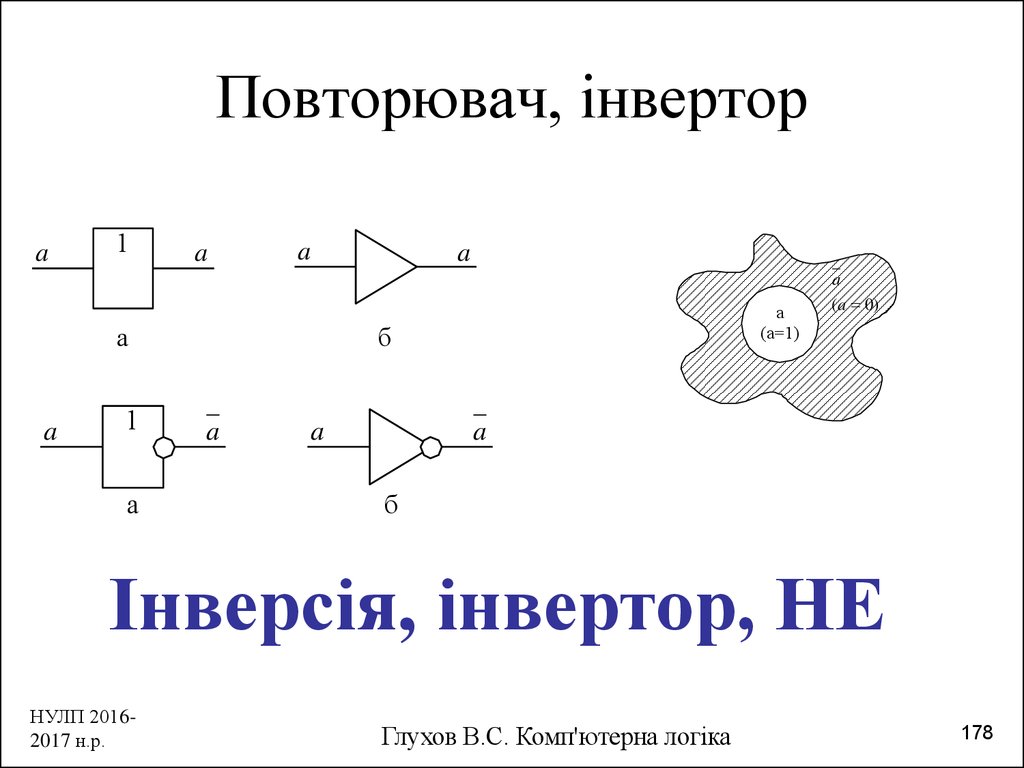

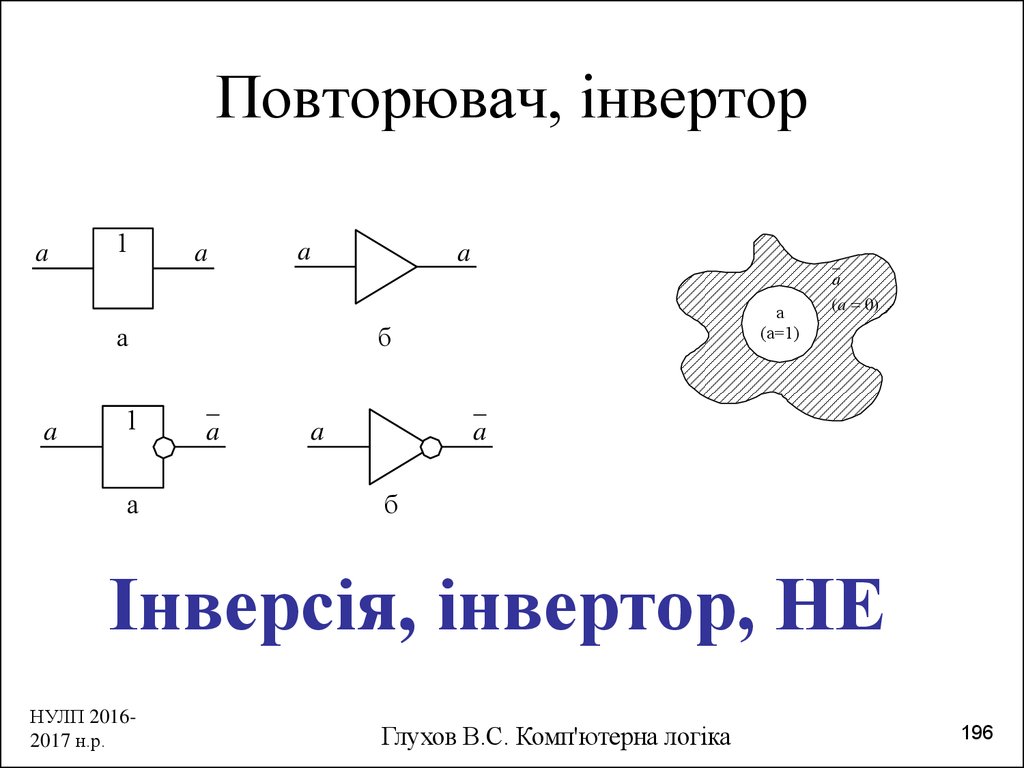

178. Повторювач, інвертор

a1

a

a

a

a

а

a

1

а

a

(a=1)

б

a

a

( a 0)

a

б

Інверсія, інвертор, НЕ

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

178

179. Функції алгебри логіки двох змінних

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

179

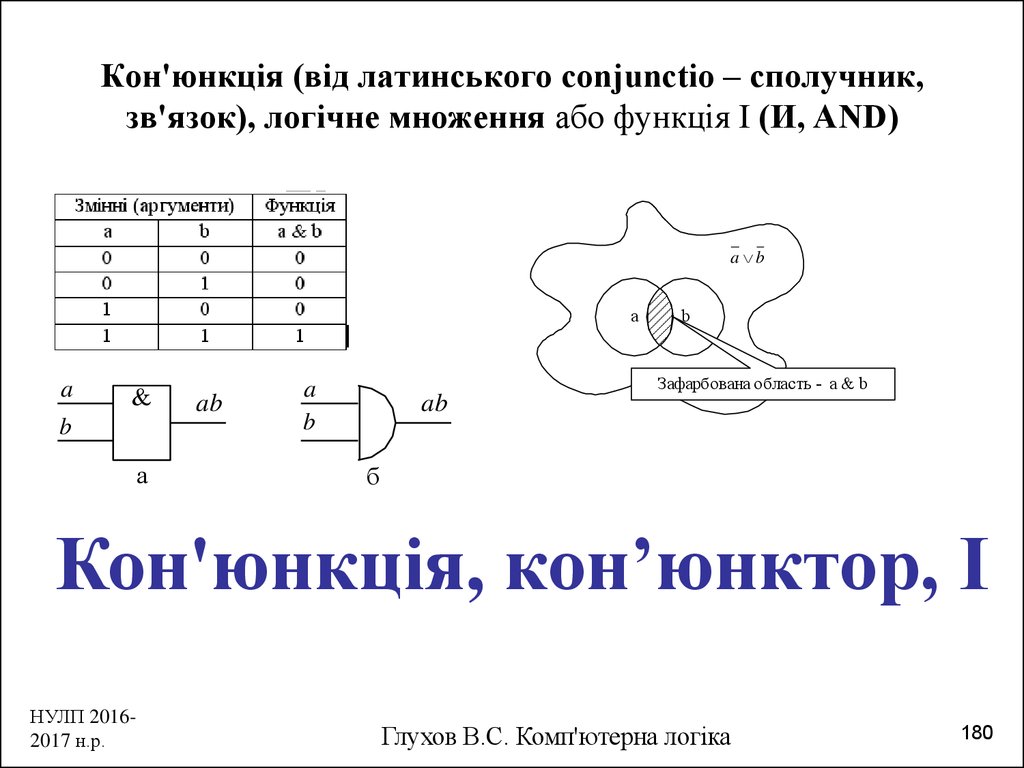

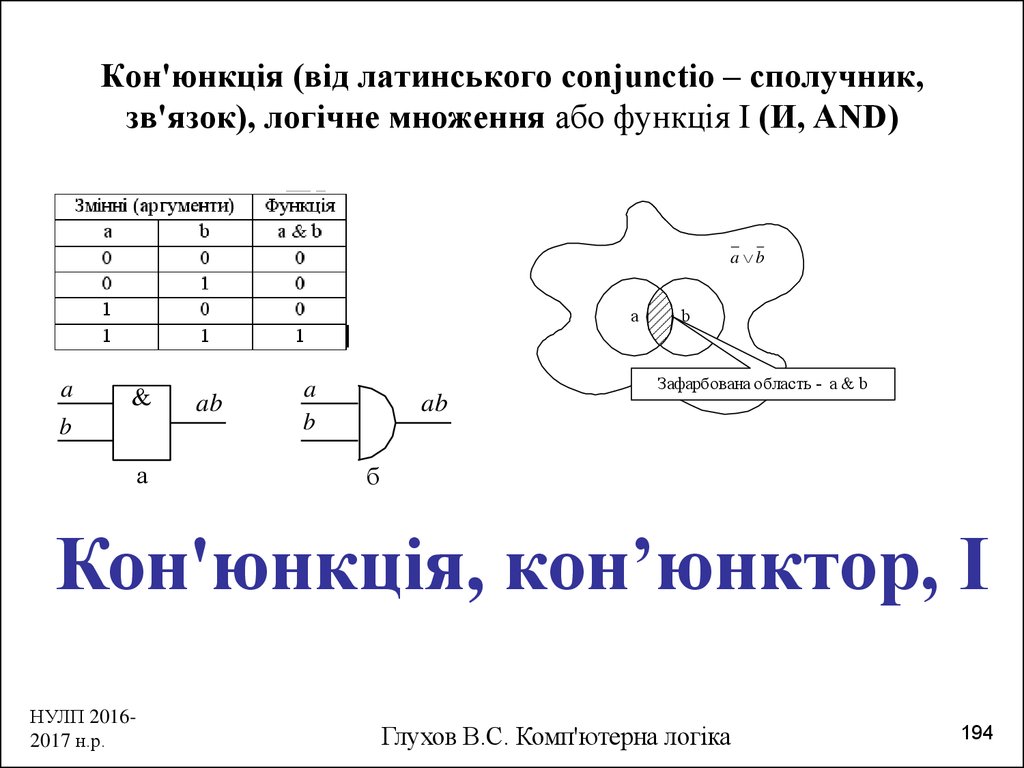

180. Кон'юнкція (від латинського conjunctio – сполучник, зв'язок), логічне множення або функція І (И, AND)

a ba

a

&

b

а

ab

b

Зафарбована область - a & b

a

b

ab

б

Кон'юнкція, кон’юнктор, І

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

180

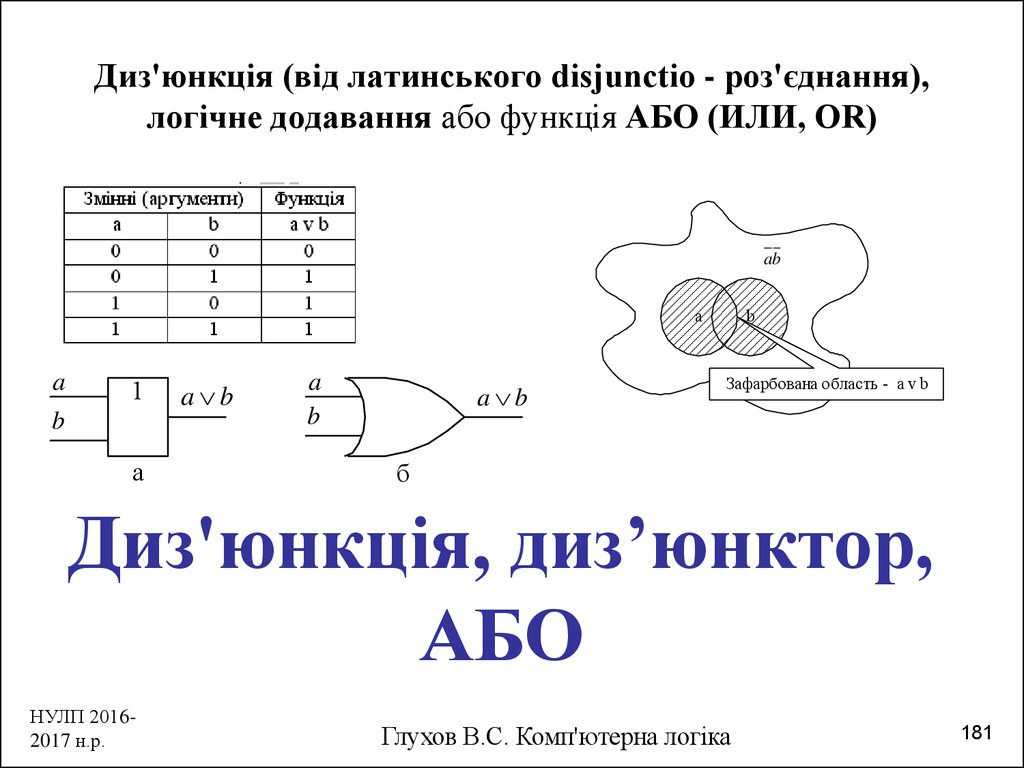

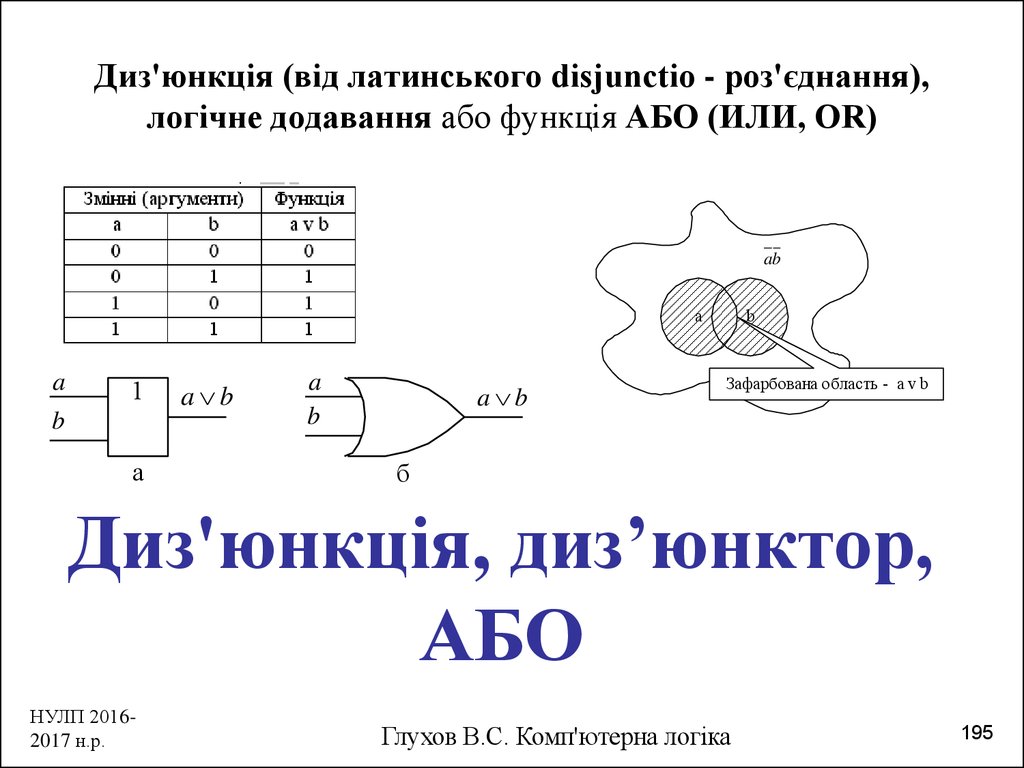

181. Диз'юнкція (від латинського disjunctio - роз'єднання), логічне додавання або функція АБО (ИЛИ, OR)

aba

a

1

b

а

a b

a

b

a b

b

Зафарбована область - a v b

б

Диз'юнкція, диз’юнктор,

АБО

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

181

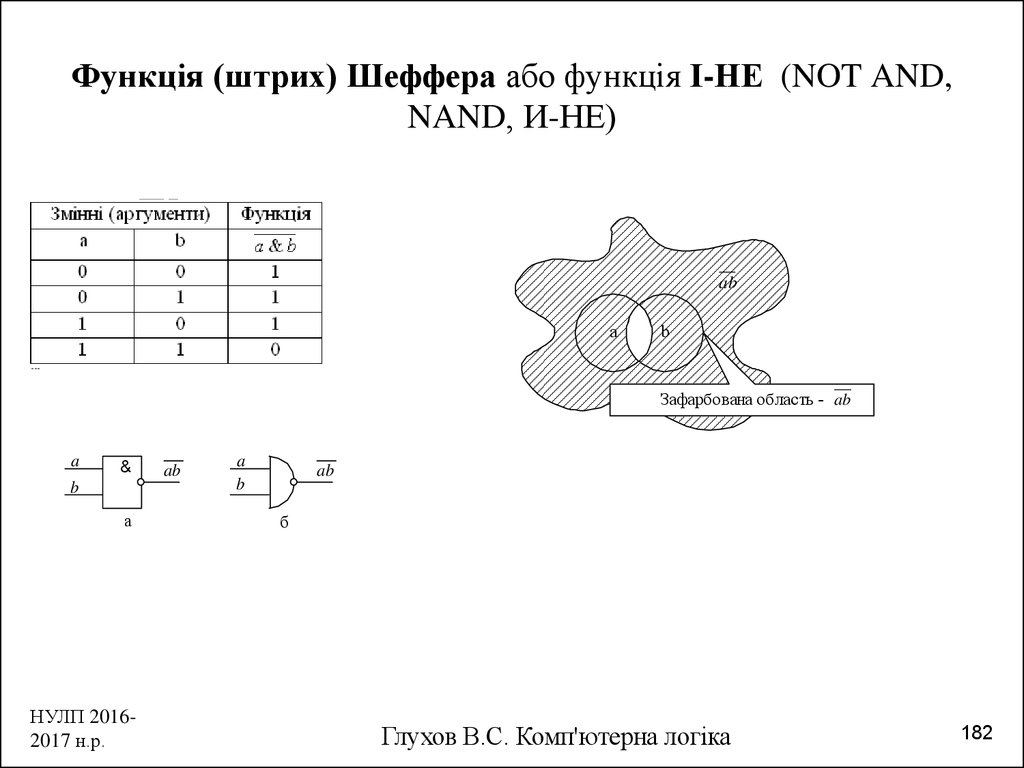

182. Функція (штрих) Шеффера або функція І-НЕ (NOT AND, NAND, И-НЕ)

aba

b

Зафарбована область - ab

a

&

b

а

НУЛП 20162017 н.р.

ab

a

b

ab

б

Глухов В.С. Комп'ютерна логіка

182

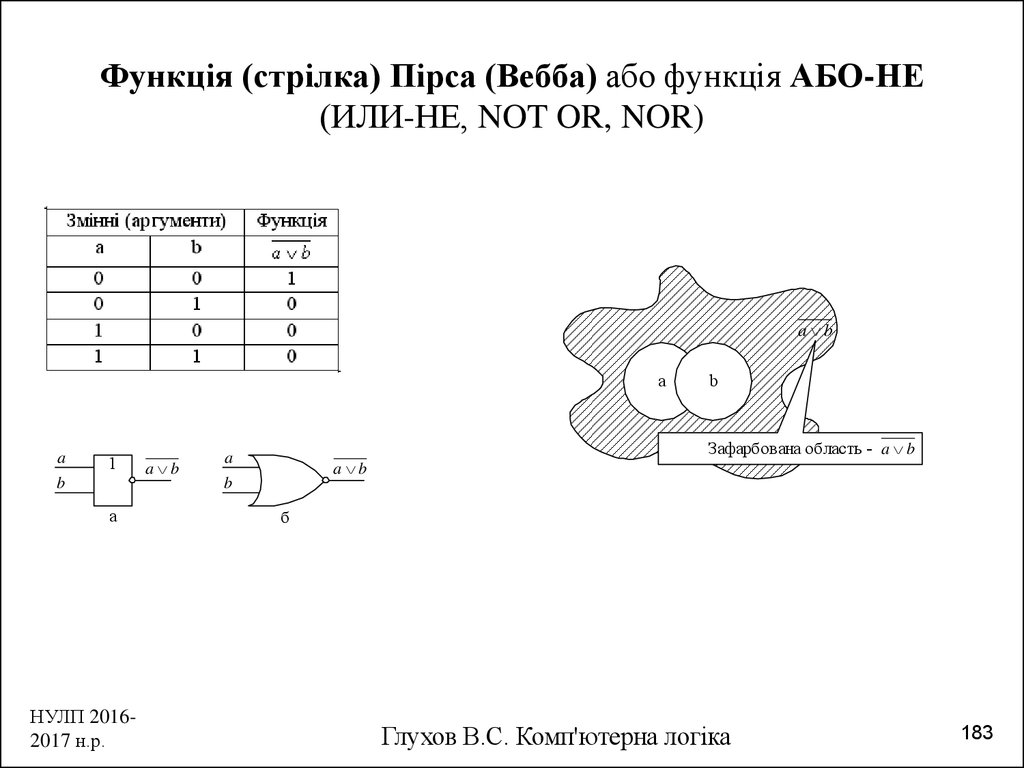

183. Функція (стрілка) Пірса (Вебба) або функція АБО-НЕ (ИЛИ-НЕ, NOT OR, NOR)

a ba

a

1

b

а

НУЛП 20162017 н.р.

a b

a

a b

b

b

Зафарбована область - a b

б

Глухов В.С. Комп'ютерна логіка

183

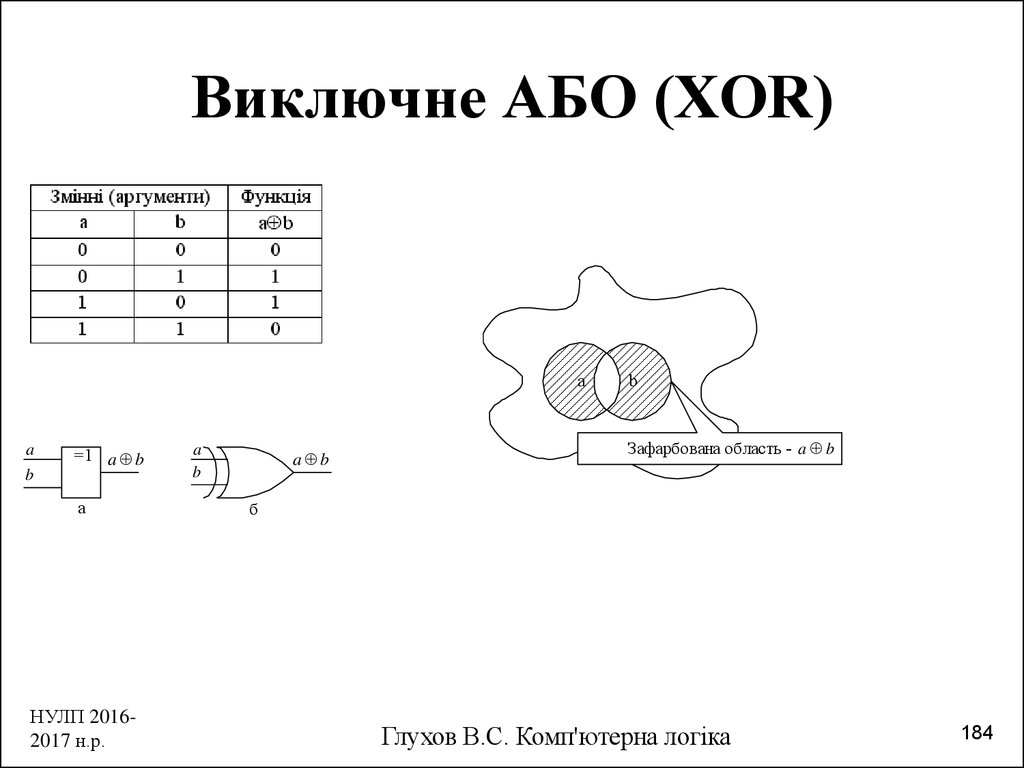

184. Виключне АБО (XOR)

aa

=1 a b

b

а

НУЛП 20162017 н.р.

a

b

a b

b

Зафарбована область - a b

б

Глухов В.С. Комп'ютерна логіка

184

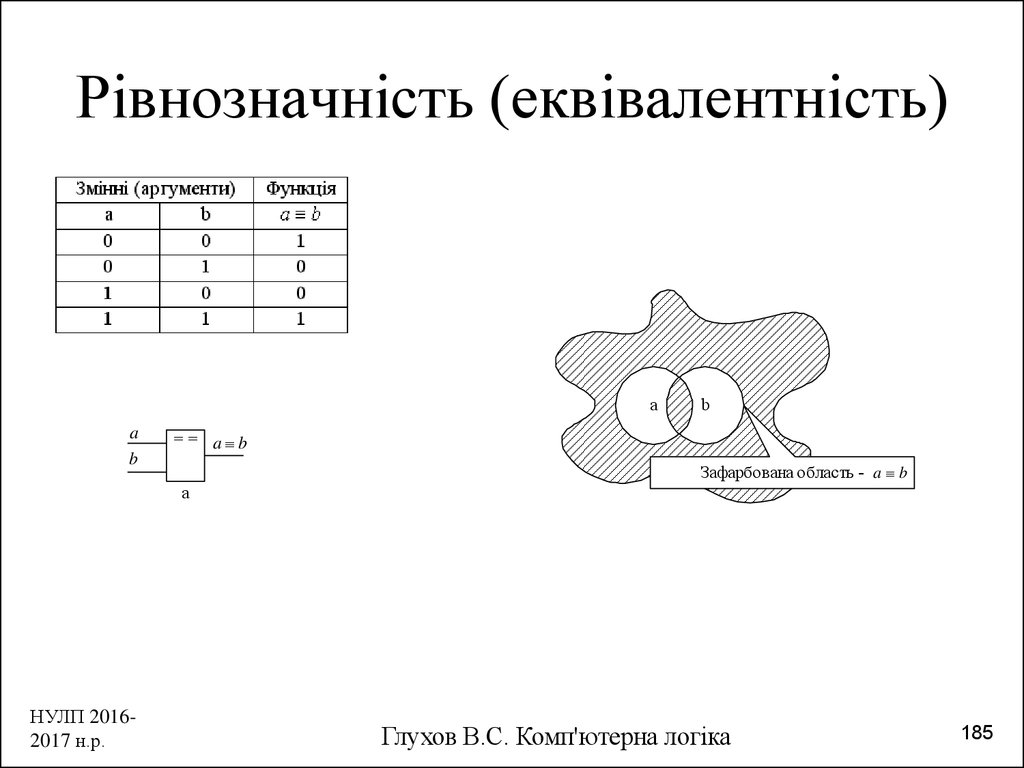

185. Рівнозначність (еквівалентність)

aa

b

b

= = a b

Зафарбована область - a b

а

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

185

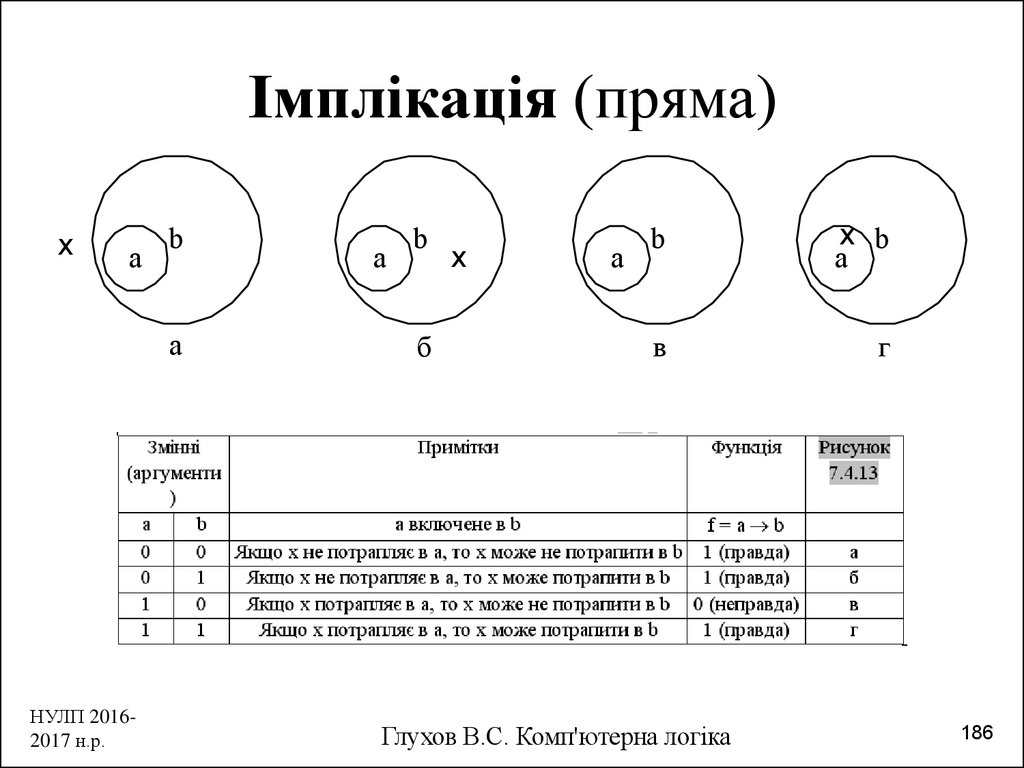

186. Імплікація (пряма)

xa

b

а

НУЛП 20162017 н.р.

a

b

б

x

a

b

x b

a

в

г

Глухов В.С. Комп'ютерна логіка

186

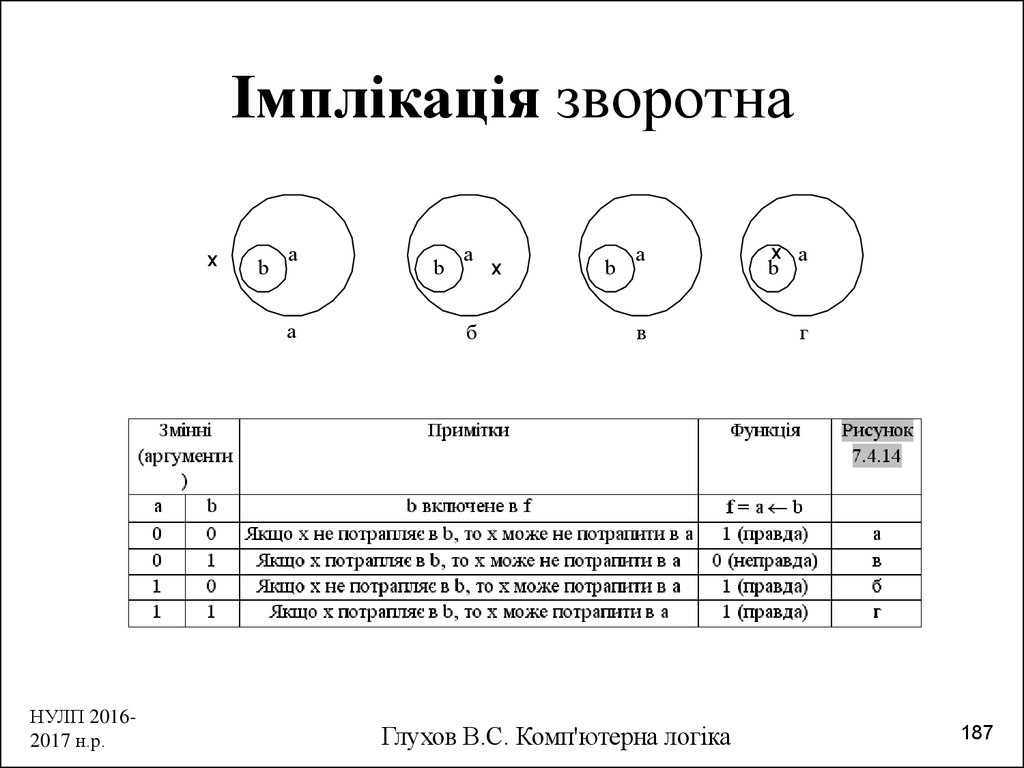

187. Імплікація зворотна

xb

a

а

НУЛП 20162017 н.р.

b

a

б

x

b

a

x a

b

в

г

Глухов В.С. Комп'ютерна логіка

187

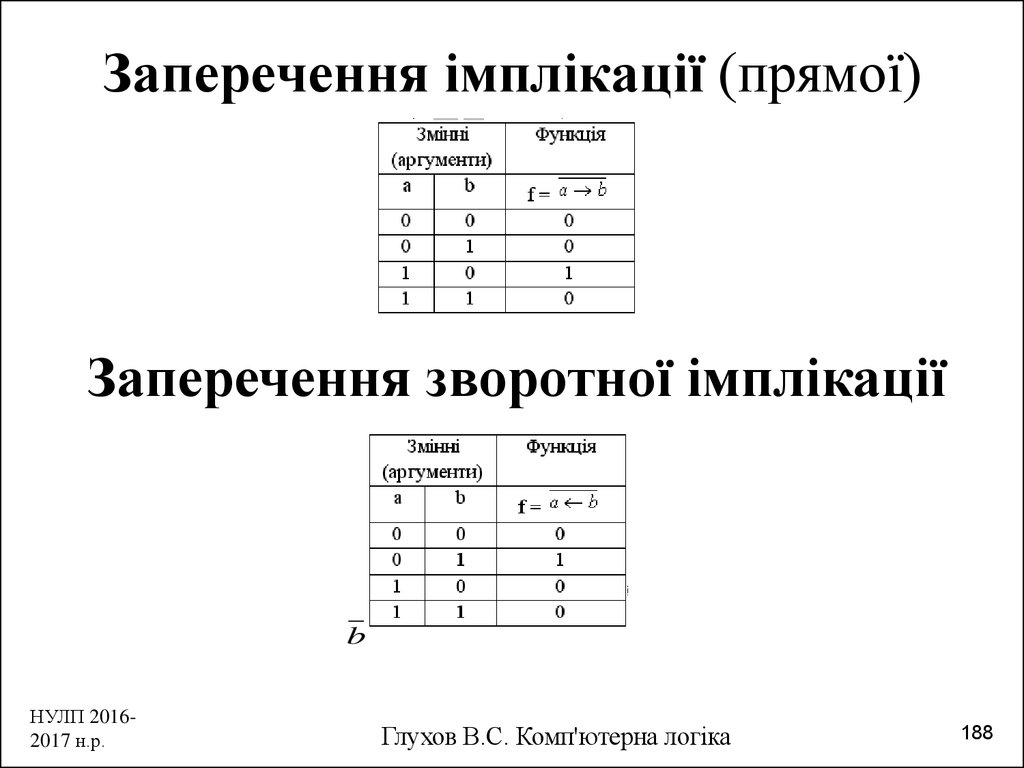

188. Заперечення імплікації (прямої)

Заперечення зворотної імплікаціїb

НУЛП 20162017 н.р.

Глухов В.С. Комп'ютерна логіка

188

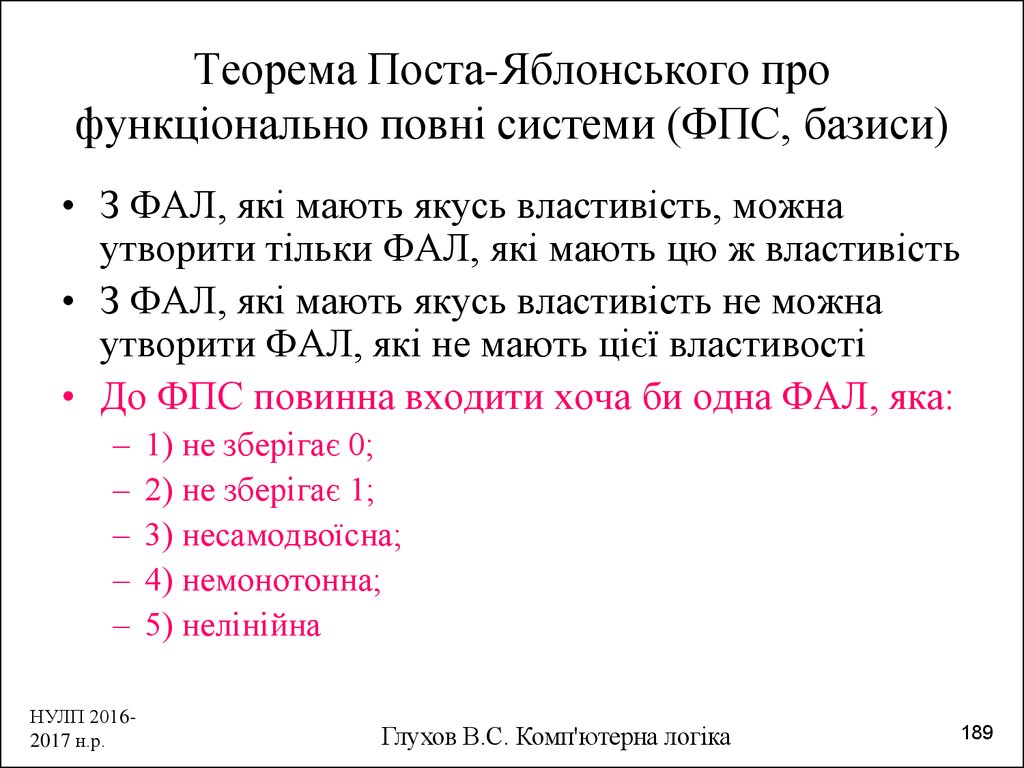

189. Теорема Поста-Яблонського про функціонально повні системи (ФПС, базиси)

• З ФАЛ, які мають якусь властивість, можнаутворити тільки ФАЛ, які мають цю ж властивість

• З ФАЛ, які мають якусь властивість не можна

утворити ФАЛ, які не мають цієї властивості

• До ФПС повинна входити хоча би одна ФАЛ, яка:

–

–

–

–

–

НУЛП 20162017 н.р.

1) не зберігає 0;

2) не зберігає 1;

3) несамодвоїсна;

4) немонотонна;

5) нелінійна

Глухов В.С. Комп'ютерна логіка

189

190. Властивості ФАЛ, монобазиси, базиси

0 1 Л М Сх0 0 0 1 1 Назва ФАЛ

х1 0 1 0 1

* *

f1

0 0 0 1 кон'юнкція, І

*

f7

0 1 1 1 диз'юнкція, АБО х0 v х1

1 1 0 0 інверсія х0

x0

НУЛП 20162017 н.р.

x

0

x

1

1

1

x

x

x

0

0

0

x

x

x

1

1

x

0

x

1

1

1

x

x

x

1

1

x

1

0

x

x

x

x

x

x

1

x

0

x

1

1

1

x

x

x

1

1

1

0

x

x

0

1

0

0

0

0

0

0

x

x

x

x

x

x

x

Глухов В.С. Комп'ютерна логіка

1

x

1

x

0

0

x

x

1

1

x

x

1

1

1

x

x

x

1

0

0

1

0

0

0

x

*

1

x

1

x

0

x

1

*

1

* *

x

0

x

1

1

0 1 Л М С

*

1

x

x

x

Властивості

0

x

1

1

1

1

f12

0

x

x

* * *

x

1

0

x

x

x

x

0 1 1 1 диз'юнкція, АБО х0 v х1

1 1 0 0 інверсія х0

x0

x

f7

*

Вираз

ФАЛ

x

х0 0 0 1 1 Назва ФАЛ

х1 0 1 0 1

x

x0 x1

*

Базис АБО, НЕ

0

*

*

Властивості

x0

x

f12 1 1 0 0 інверсія х0

0

x

x

x

x

x

* *

x

х0 ·х1

x

0 0 0 1 кон'юнкція, І

0 1 Л М С

x

f1

Вираз

ФАЛ

x

*

*

*

* * *

0

*

х0 0 0 1 1 Назва ФАЛ

х1 0 1 0 1

x

f14 1 1 1 0 І-НЕ (Шефера)

f15 1 1 1 1 константа "1"

1

1

x0

f12 1 1 0 0 інверсія х0

f13 1 1 0 1 імплікація пряма x0 x1

f15 1 1 1 1 константа "1"

x0 x1

x0 x1 x0 x1 *

f11

x1

0 1 1 0 сума за mod 2

*

Базис І, НЕ

* *

*

f6

x

f10

1 0 1 0 інверсія х1

1 0 1 1 імплікація звор.

x0 x1 x0 x1

х0 ·х1

1

1 0 0 1 рівнозначність

*

* *

0 0 0 1 кон'юнкція, І

0

f9

* *

Властивості

f1

0

f8

0 1 1 1 диз'юнкція, АБО х0 v х1

1 0 0 0 АБО-НЕ (Пірса) x0 x1

*

0 1 Л М С

0

f7

*

Вираз

ФАЛ

0 1 1 0 сума за mod 2

* * * * *

х1

*

x0 x1 x0 x1 *

х0 0 0 1 1 Назва ФАЛ

х1 0 1 0 1

x

f6

f4

*

Властивості

Базис Жегалкіна

0

f5

0 1 0 0 заборона по х0

0 1 0 1 х1

0

* * * * *

0

х0

x0 x1

f3

f12

*

x

x0 x1

*

0

f2

0 0 1 0 заборона по х1

0 0 1 1 х0

* *

0

* *

x

х0 ·х1

*

x

0 0 0 1 кон'юнкція, І

* *

1

f1

х0 ·х1

*

0

x

0 0 0 0 константа "0"

0 1 Л М С

f0

Вираз

ФАЛ

x

Властивості

Базис Буля

Вираз

ФАЛ

0

х0 0 0 1 1 Назва ФАЛ

х1 0 1 0 1

190

*

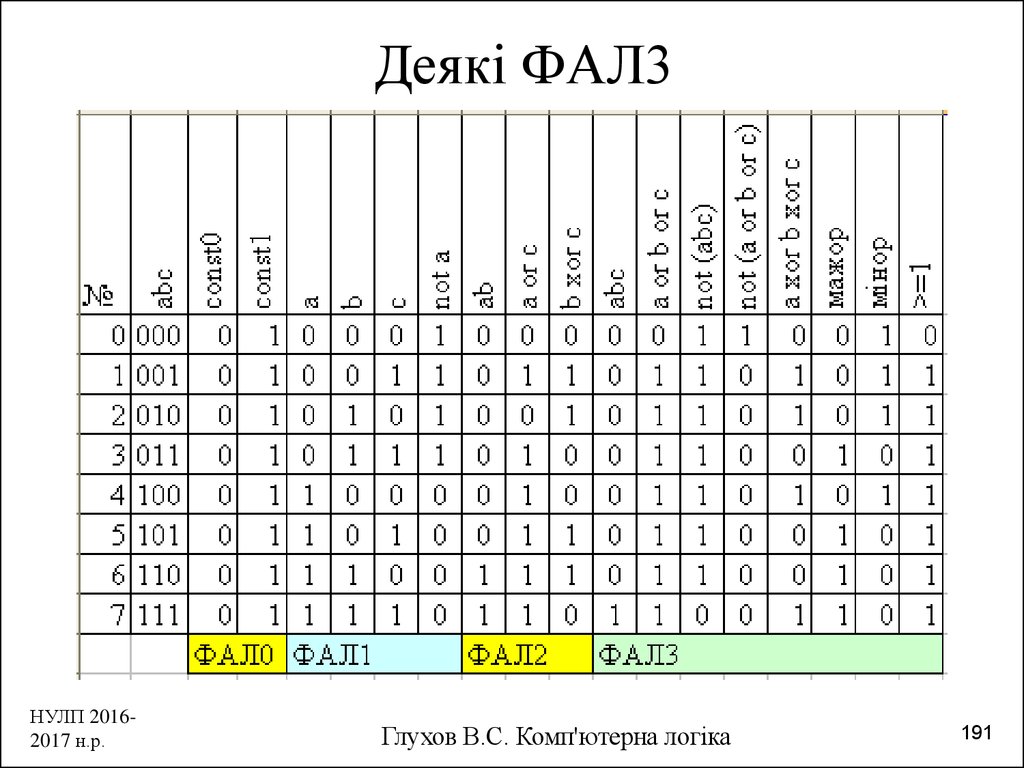

191. Деякі ФАЛ3

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

191

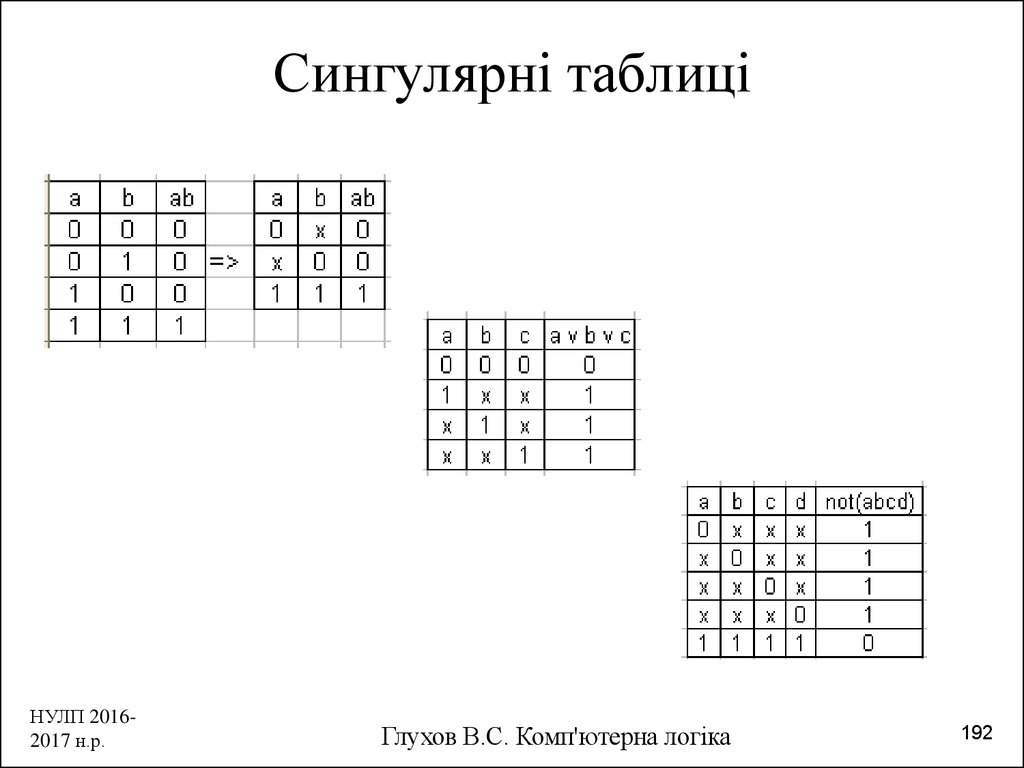

192. Сингулярні таблиці

НУЛП 20162017 н.р.Глухов В.С. Комп'ютерна логіка

192

193. Базис Буля

ab

a

&

a b ... z

...

z

елемент І (AND),

кон'юнктор

НУЛП 20162017 н.р.

b

1

a b ... z

...

z

елемент АБО (OR),

диз'юнктор

a

1

a

елемент НЕ (NOT),

інвертор

Глухов В.С. Комп'ютерна логіка

193

194. Кон'юнкція (від латинського conjunctio – сполучник, зв'язок), логічне множення або функція І (И, AND)

a ba

a

&

b

а

ab

b

Зафарбована область - a & b

a

b

ab

б