Similar presentations:

Комп’ютерна логіка (частина 2)

1.

Комп’ютерна логіка (частина 2)Національний університет «Львівська політехніка»

Lviv Polytechnic National University

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

1

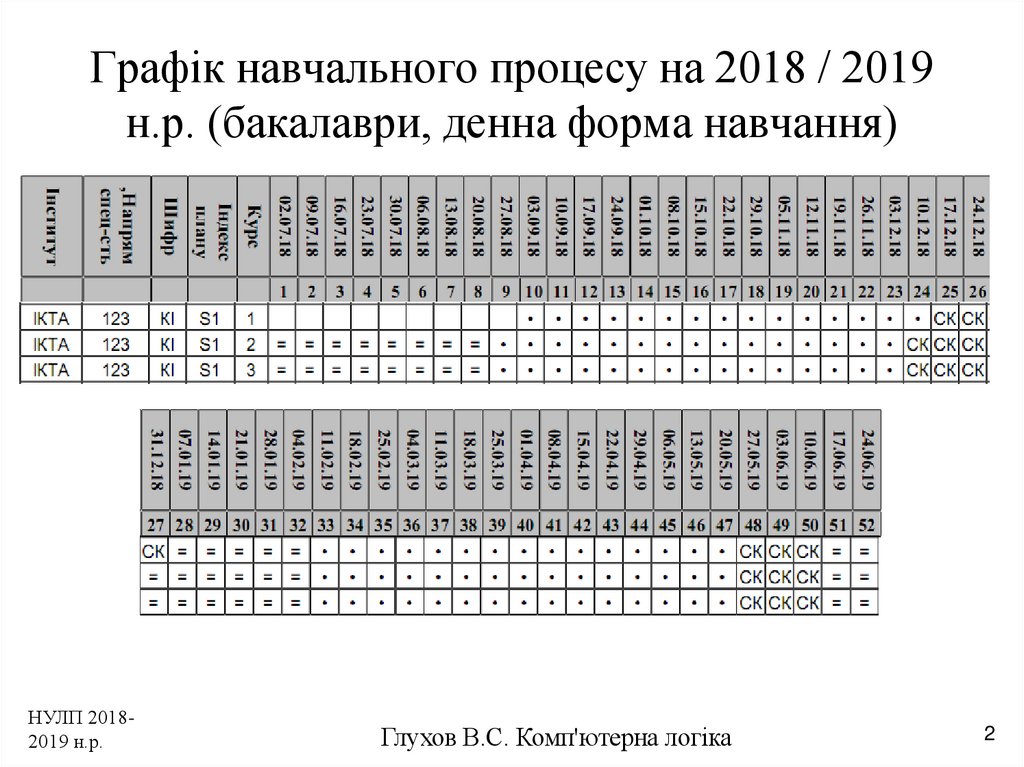

2. Графік навчального процесу на 2018 / 2019 н.р. (бакалаври, денна форма навчання)

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

2

3. Виконання навчального плану

Ліквідовано академрізницю

Здано повторний курс

Здано курсову роботу

Виконано програму практичних занять

Написано усі лекційні контрольні роботи

Дано правильні відповіді на усі тести

Є конспект лекцій (приблизно 5 сторінок на

лекцію)

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

3

4. Державна оцінка (іспит)

• 1. Оцінка на іспиті• 2. Оцінка на іспиті за талоном

• 3а. Оцінка на комісії

– або

• 3б. Оцінка за результатами повторного

вивчення курсу

Державна оцінка

(залік за курсову роботу)

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

4

5. Стандартні вимоги до відповідей на іспиті

• Повинна бути дана відповідь на усі питаннябілету

• Під час підготовки відповіді нічим не

можна користуватися

• Під час підготовки відповіді ні з ким не

можна перемовлятися та обмінюватися

інформацією

• Для допуску до іспиту потрібно виконати

навчальний план

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

5

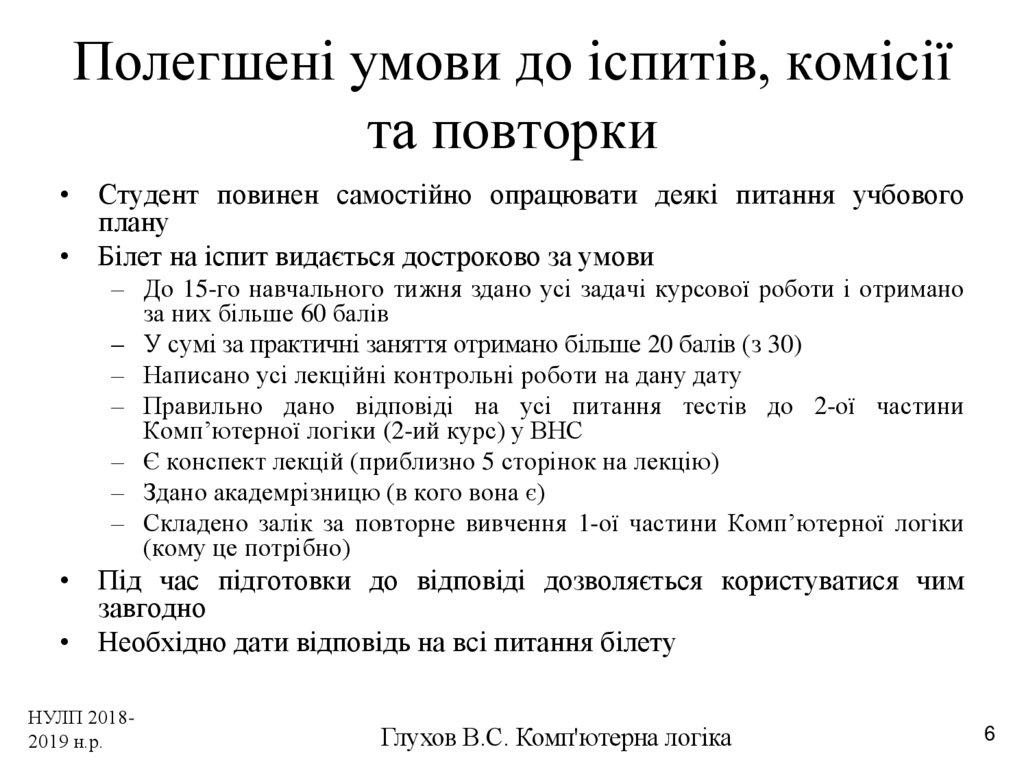

6. Полегшені умови до іспитів, комісії та повторки

• Студент повинен самостійно опрацювати деякі питання учбовогоплану

• Білет на іспит видається достроково за умови

– До 15-го навчального тижня здано усі задачі курсової роботи і отримано

за них більше 60 балів

– У сумі за практичні заняття отримано більше 20 балів (з 30)

– Написано усі лекційні контрольні роботи на дану дату

– Правильно дано відповіді на усі питання тестів до 2-ої частини

Комп’ютерної логіки (2-ий курс) у ВНС

– Є конспект лекцій (приблизно 5 сторінок на лекцію)

– Здано академрізницю (в кого вона є)

– Складено залік за повторне вивчення 1-ої частини Комп’ютерної логіки

(кому це потрібно)

• Під час підготовки до відповіді дозволяється користуватися чим

завгодно

• Необхідно дати відповідь на всі питання білету

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

6

7. Оцінювання відповідей при стандартному підході

Оцінка Оцінка практичні Оцінка ЛекційніКР 65 * Оцінка білет / 70Для іспиту:

Оцінка 100; Оцінка практичні 30; Оцінка ЛекційніКР 5; Оцінка білет 70

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

7

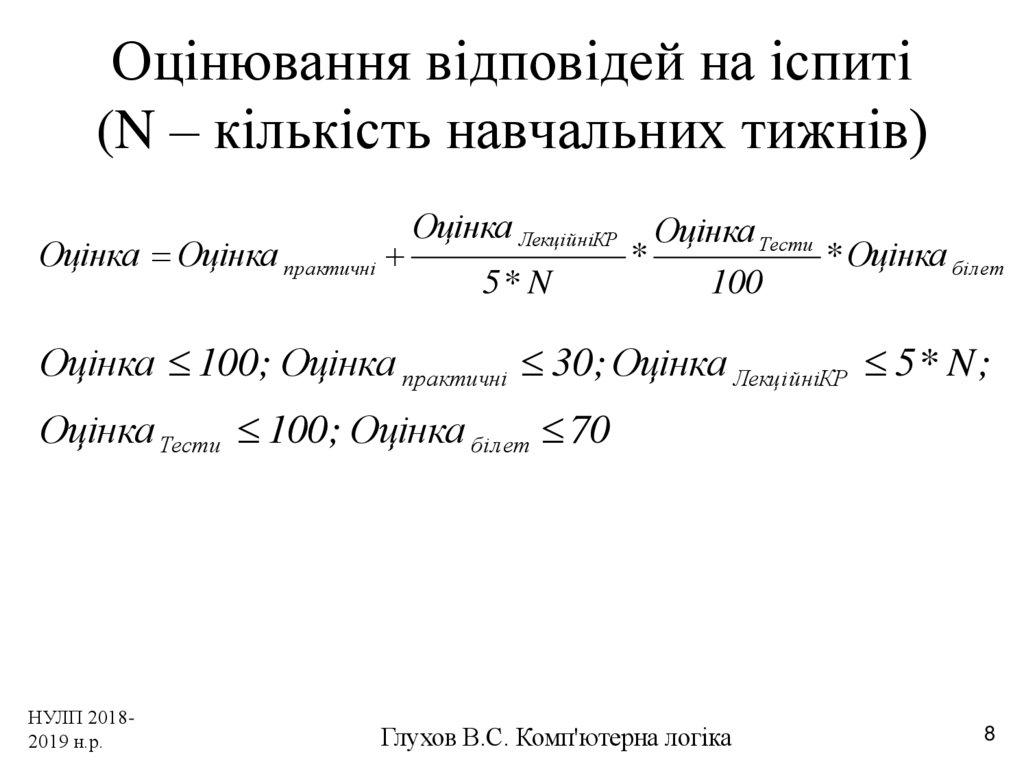

8. Оцінювання відповідей на іспиті (N – кількість навчальних тижнів)

Оцінка Оцінка практичніОцінка ЛекційніКР

5* N

Оцінка Тести

*

* Оцінка білет

100

Оцінка 100; Оцінка практичні 30; Оцінка ЛекційніКР 5* N ;

Оцінка Тести 100; Оцінка білет 70

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

8

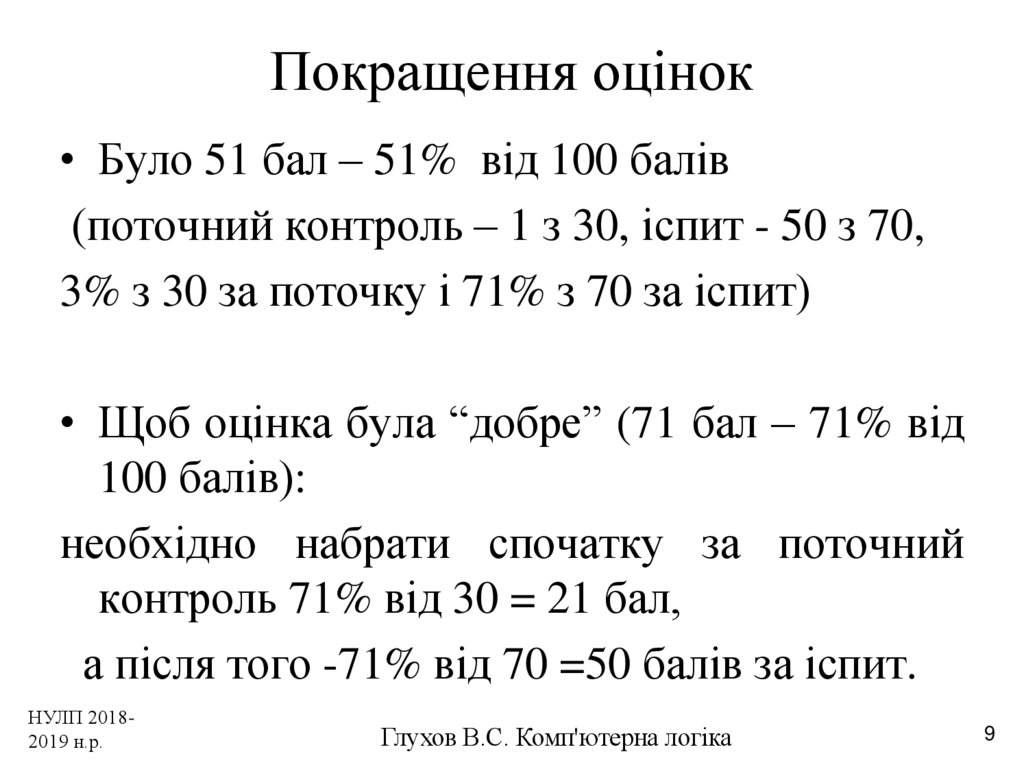

9. Покращення оцінок

• Було 51 бал – 51% від 100 балів(поточний контроль – 1 з 30, іспит - 50 з 70,

3% з 30 за поточку і 71% з 70 за іспит)

• Щоб оцінка була “добре” (71 бал – 71% від

100 балів):

необхідно набрати спочатку за поточний

контроль 71% від 30 = 21 бал,

а після того -71% від 70 =50 балів за іспит.

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

9

10. Відпрацювання пропущених лекційних контрольних робіт

• Копія власноручно написаного конспектулекції, на якій писали пропущену

контрольну роботу

• Ескізи

слайдів

в

конспекті,

що

демонструвалися на лекції, на якій писали

пропущену контрольну роботу

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

10

11. Курсова робота

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

11

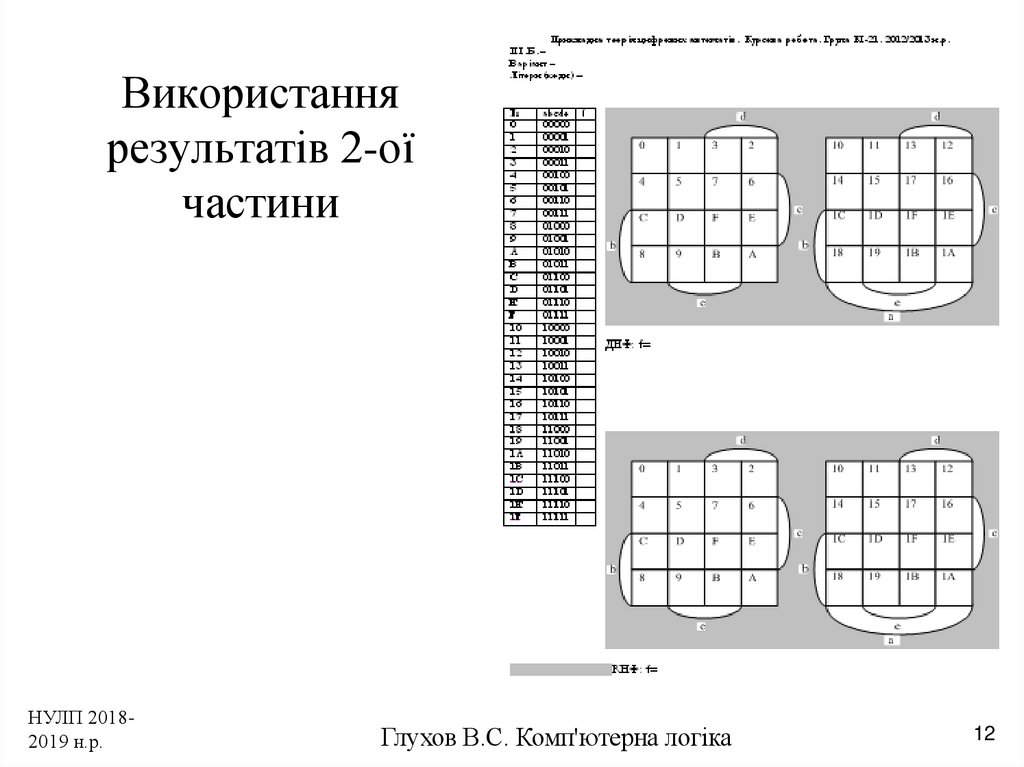

12. Використання результатів 2-ої частини

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

12

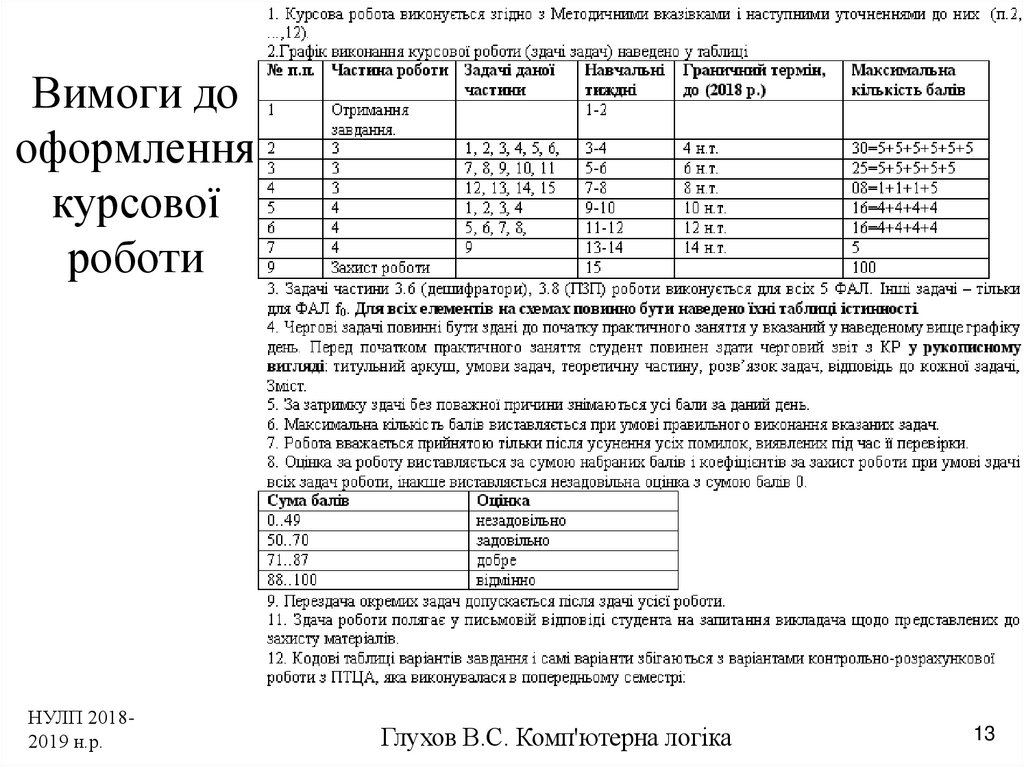

13. Вимоги до оформлення курсової роботи

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

13

14. Оцінювання курсової роботи

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

14

15. Розклад викладача

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

15

16. Консультації – після закінчення останнього лекційного заняття, на каф. ЕОМ, 503-V або за домовленістю

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

16

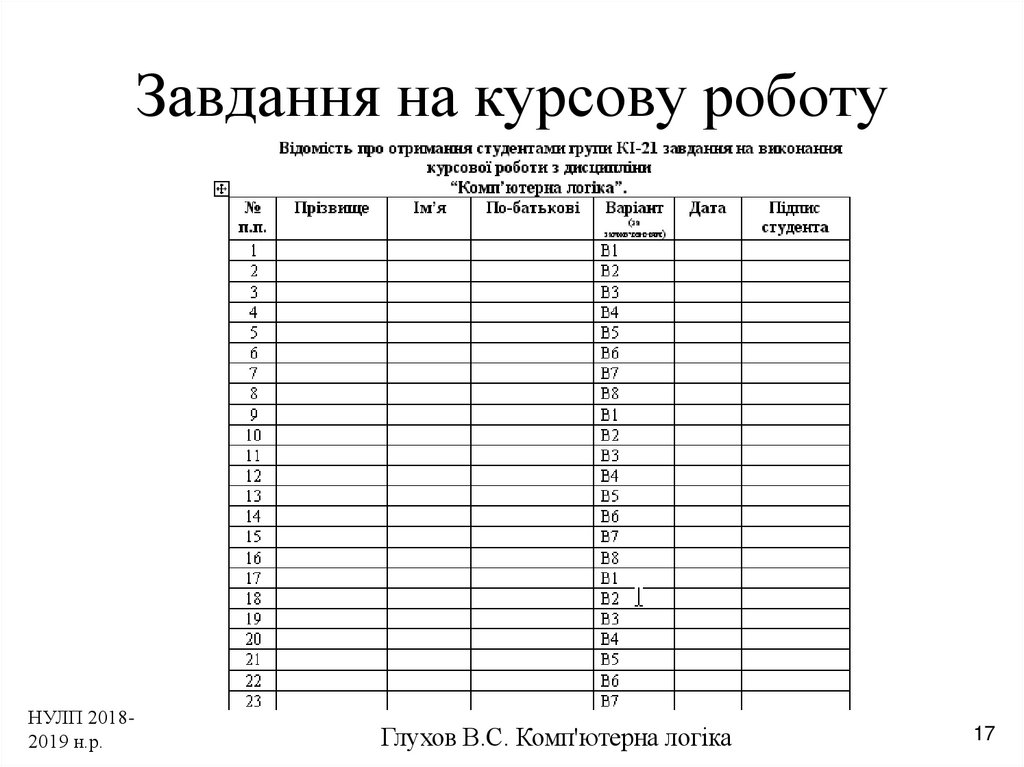

17. Завдання на курсову роботу

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

17

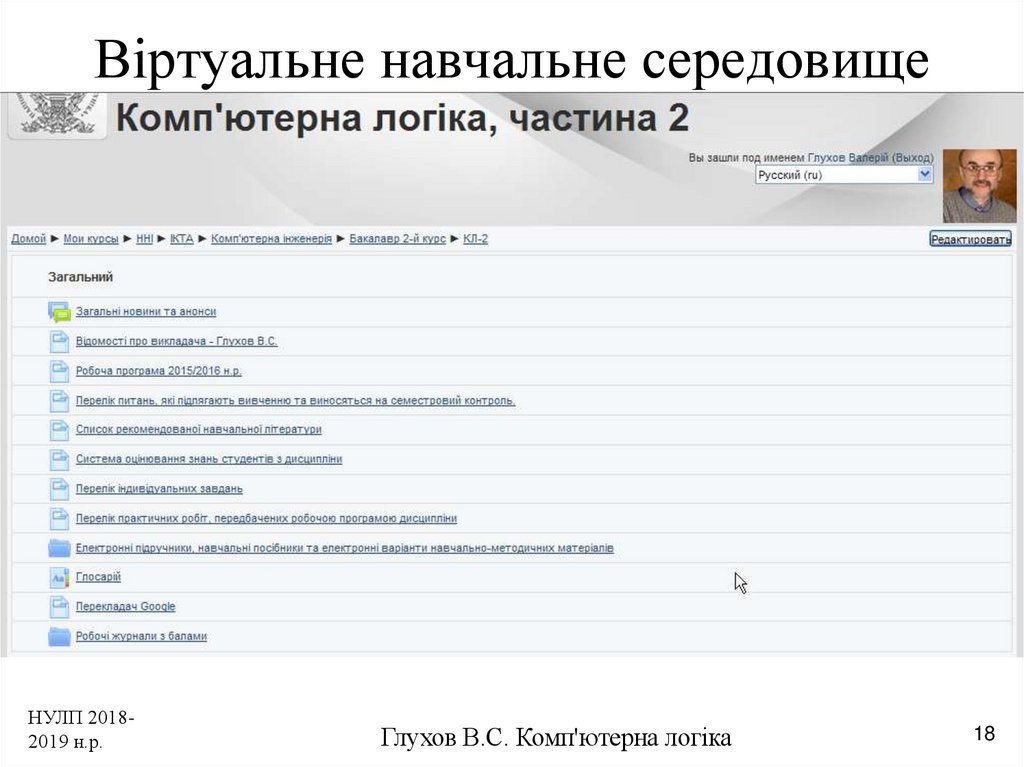

18. Віртуальне навчальне середовище

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

18

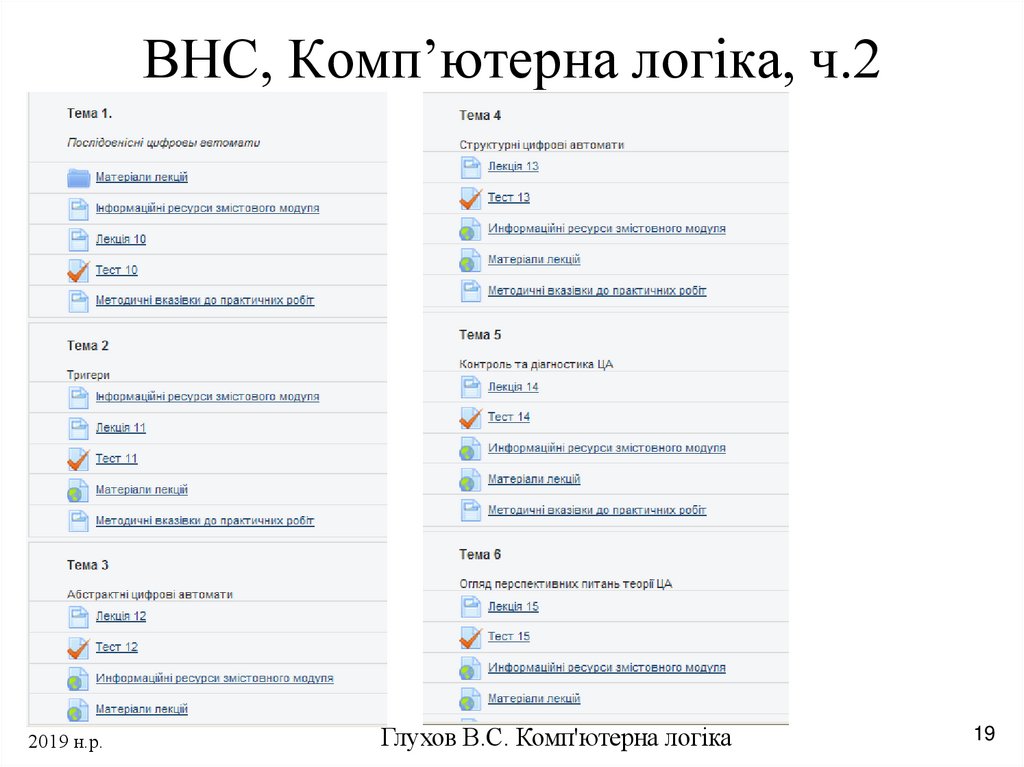

19. ВНС, Комп’ютерна логіка, ч.2

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

19

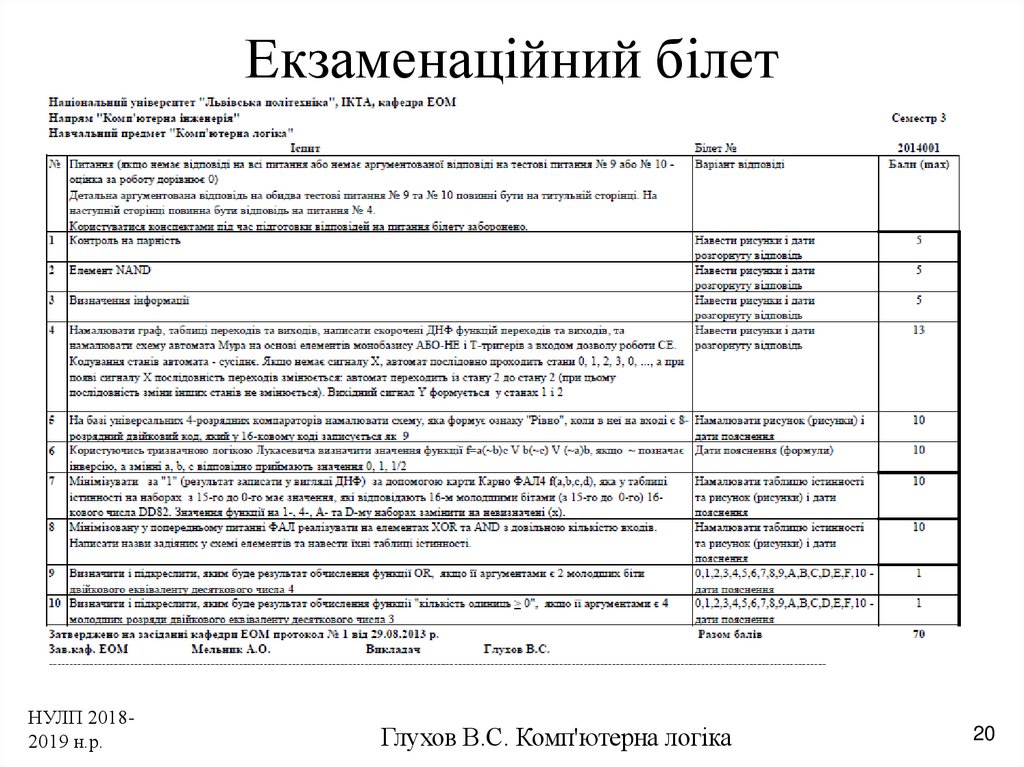

20. Екзаменаційний білет

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

20

21. Робочий журнал

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

21

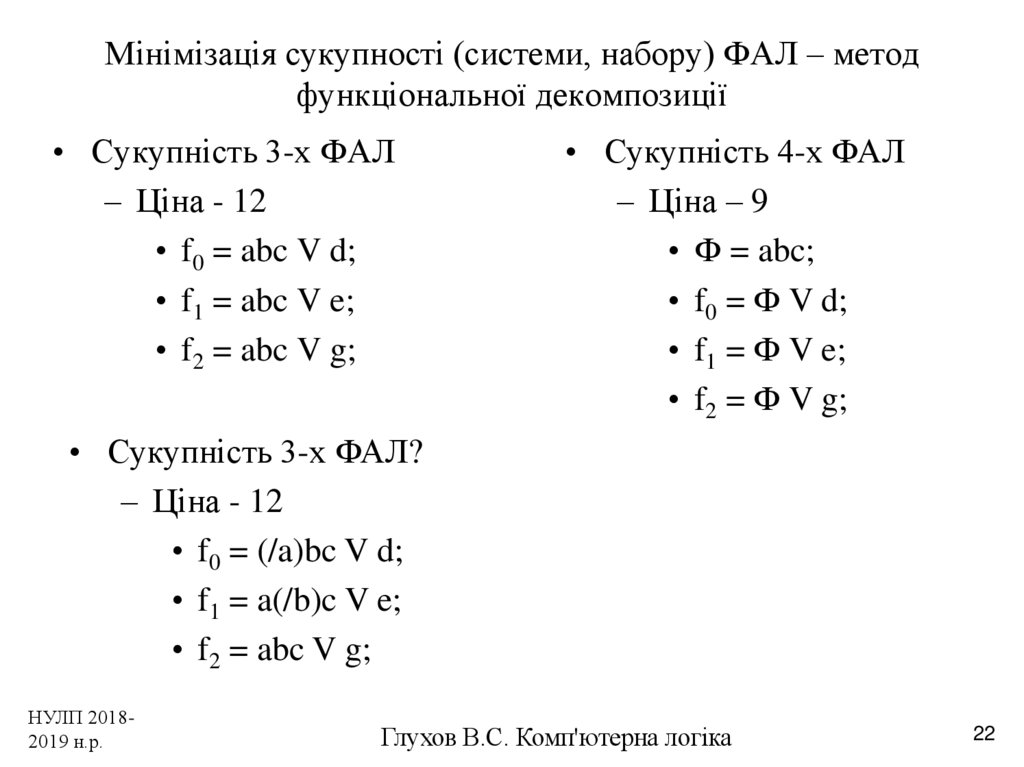

22. Мінімізація сукупності (системи, набору) ФАЛ – метод функціональної декомпозиції

• Сукупність 3-х ФАЛ– Ціна - 12

• f0 = abc V d;

• f1 = abc V e;

• f2 = abc V g;

• Сукупність 4-х ФАЛ

– Ціна – 9

• Ф = abc;

• f0 = Ф V d;

• f1 = Ф V e;

• f2 = Ф V g;

• Сукупність 3-х ФАЛ?

– Ціна - 12

• f0 = (/a)bc V d;

• f1 = a(/b)c V e;

• f2 = abc V g;

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

22

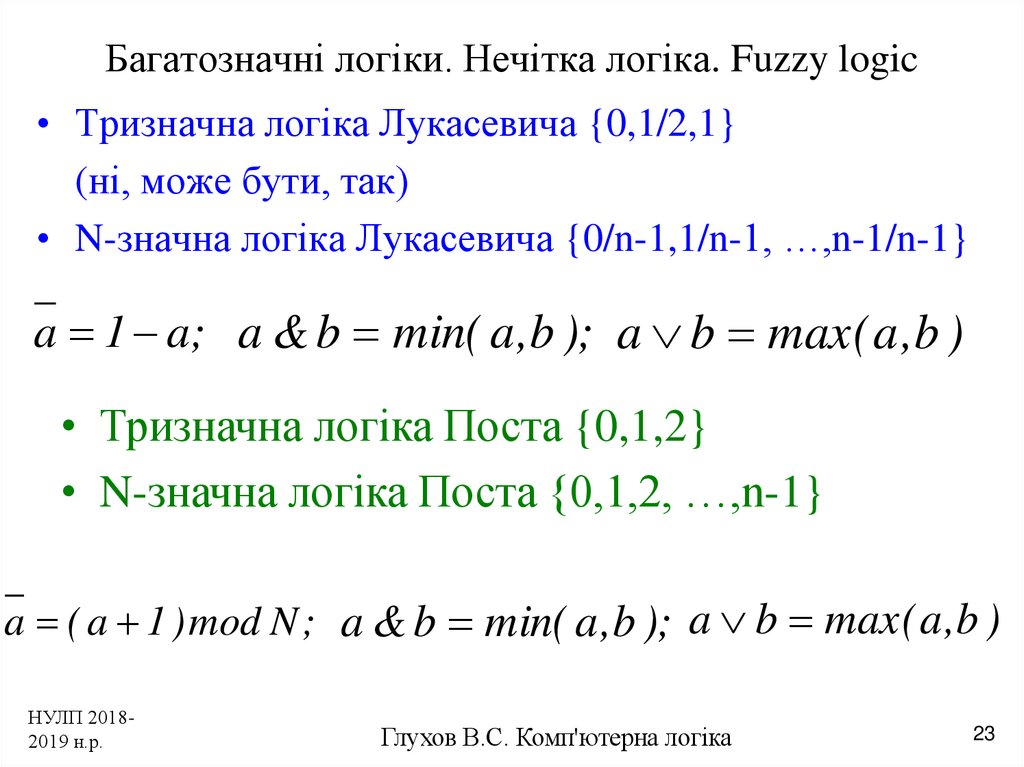

23. Багатозначні логіки. Нечітка логіка. Fuzzy logic

• Тризначна логіка Лукасевича {0,1/2,1}(ні, може бути, так)

• N-значна логіка Лукасевича {0/n-1,1/n-1, …,n-1/n-1}

a 1 a; a & b min( a ,b ); a b max( a ,b )

• Тризначна логіка Поста {0,1,2}

• N-значна логіка Поста {0,1,2, …,n-1}

a ( a 1 ) mod N ; a & b min( a ,b ); a b max( a ,b )

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

23

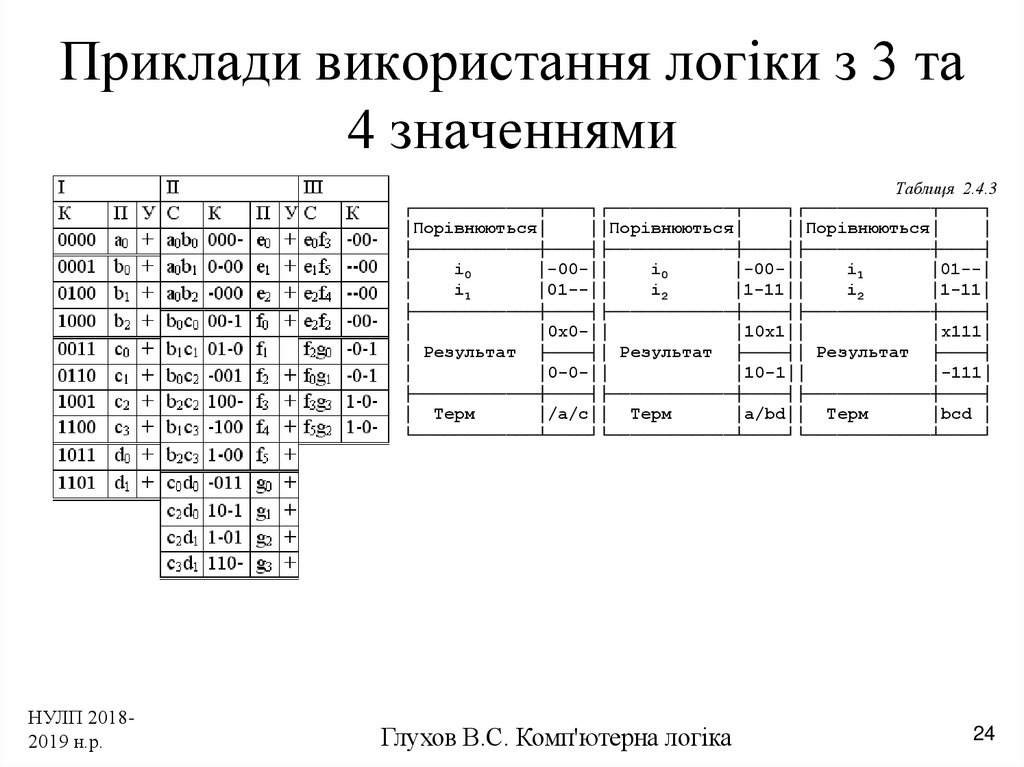

24. Приклади використання логіки з 3 та 4 значеннями

Таблиця 2.4.3┌────────────┬────┐┌────────────┬────┐┌────────────┬────┐

│Порівнюються│

││Порівнюються│

││Порівнюються│

│

├────────────┼────┤├────────────┼────┤├────────────┼────┤

│

і0

│-00-││

і0

│-00-││

і1

│01--│

│

і1

│01--││

і2

│1-11││

і2

│1-11│

├────────────┼────┤├────────────┼────┤├────────────┼────┤

│

│0x0-││

│10x1││

│x111│

│ Результат ├────┤│ Результат ├────┤│ Результат ├────┤

│

│0-0-││

│10-1││

│-111│

├────────────┼────┤├────────────┼────┤├────────────┼────┤

│ Терм

│/a/c││ Терм

│a/bd││ Терм

│bcd │

└────────────┴────┘└────────────┴────┘└────────────┴────┘

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

24

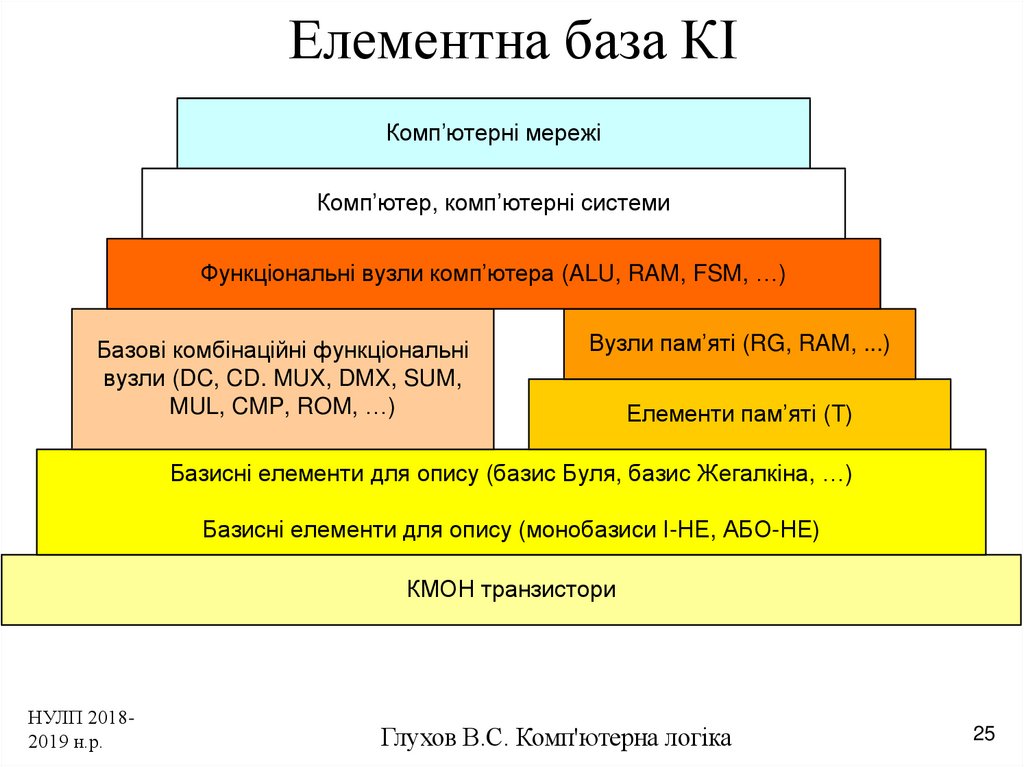

25. Елементна база КІ

Комп’ютерні мережіКомп’ютер, комп’ютерні системи

Функціональні вузли комп’ютера (ALU, RAM, FSM, …)

Базові комбінаційні функціональні

вузли (DC, CD. MUX, DMX, SUM,

MUL, CMP, ROM, …)

Вузли пам’яті (RG, RAM, ...)

Елементи пам’яті (T)

Базисні елементи для опису (базис Буля, базис Жегалкіна, …)

Базисні елементи для опису (монобазиси І-НЕ, АБО-НЕ)

КМОН транзистори

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

25

26. БАЗОВІ КОМБІНАЦІЙНІ ВУЗЛИ

дешифратори і демультиплексори;

мультиплексори;

шифратори;

перетворювачі кодів;

постійні запам’ятовуючі пристрої;

програмовані логічні матриці;

програмовані матриці логіки;

суматори і напівсуматори;

вузли порівняння;

арифметично-логічні пристрої;

вузли зсуву;

помножувачі;

вузли прискорення переносу;

інші.

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

26

27. Газорозрядні індикатори

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

27

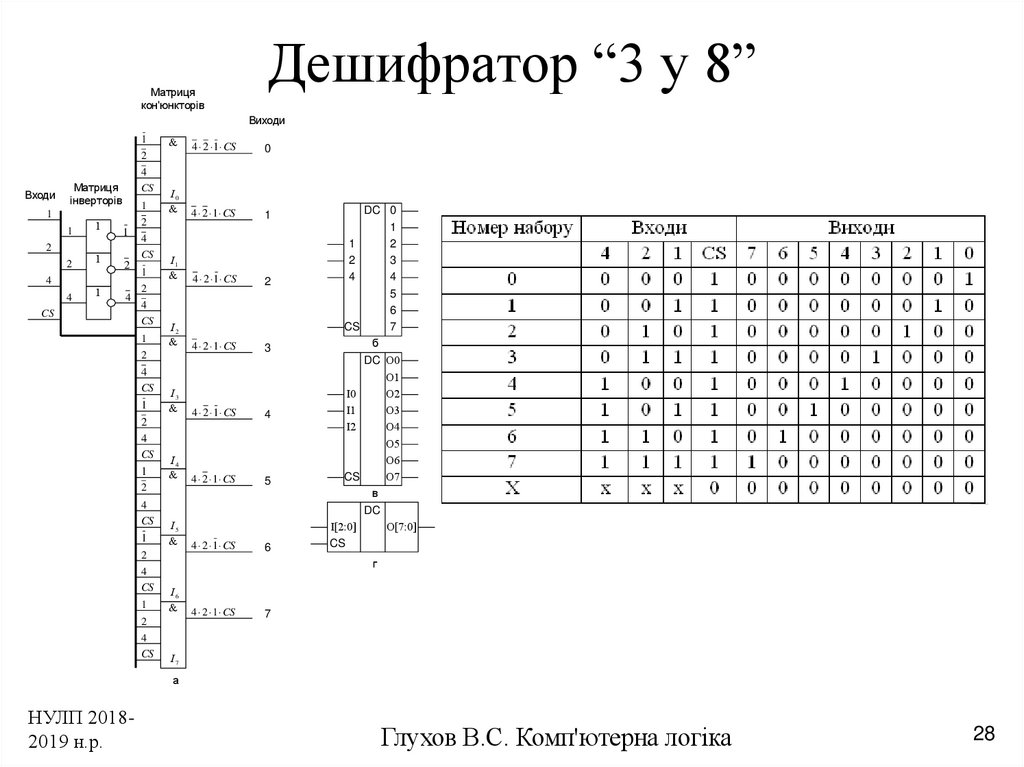

28. Дешифратор “3 у 8”

Матрицякон'юнкторів

Дешифратор “3 у 8”

Виходи

1

&

4 2 1 CS

0

І0

&

4 2 1 CS

1

2

Входи

4

CS

Матриця

інверторів

1

1

1

2

1

2

4

4

1

1

1

2

4

CS

2

4

CS

1

І1

&

4 2 1 CS

2

І2

&

4 2 1 CS

3

2

4

CS

1

2

4

CS

1

2

4

CS

1

1

2

4

CS

1

4 2 1 CS

4

I0

I1

I2

І4

&

4 2 1 CS

5

CS

І5

&

4 2 1 CS

6

I[2:0]

CS

DC O0

O1

O2

O3

O4

O5

O6

O7

в

DC

O[7:0]

г

І6

&

2

4

CS

CS

І3

&

2

4

CS

1

2

4

DC 0

1

2

3

4

5

6

7

б

4 2 1 CS

7

І7

а

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

28

29. Матрична схема дешифратора “3 у 8"

Матрична схема дешифратора “3 у 8"Матриця

інверторів

Матриця кон'юнкторів

І 0 І1 І 2 І 3 І 4 І 5 І 6 І 7

Входи

4

4

2

2

1

1

CS

0 1 2 3 4 5 6 7

Виходи

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

29

30. VHDL-опис дешифратора “3 у 8”

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.STD_LOGIC_UNSIGNED.all;

entity DC is

port (

O : out STD_LOGIC_VECTOR (7 downto 0);

I : in STD_LOGIC_VECTOR (2 downto 0);

CS : in STD_LOGIC);

end entity;

architecture DC_arch of DC is

begin

O(0) <= CS when (I = 0) else '0';

O(1) <= CS when (I = 1) else '0';

O(2) <= CS when (I = 2) else '0';

O(3) <= CS when (I = 3) else '0';

O(4) <= CS when (I = 4) else '0';

O(5) <= CS when (I = 5) else '0';

O(6) <= CS when (I = 6) else '0';

O(7) <= CS when (I = 7) else '0';

end architecture;

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

30

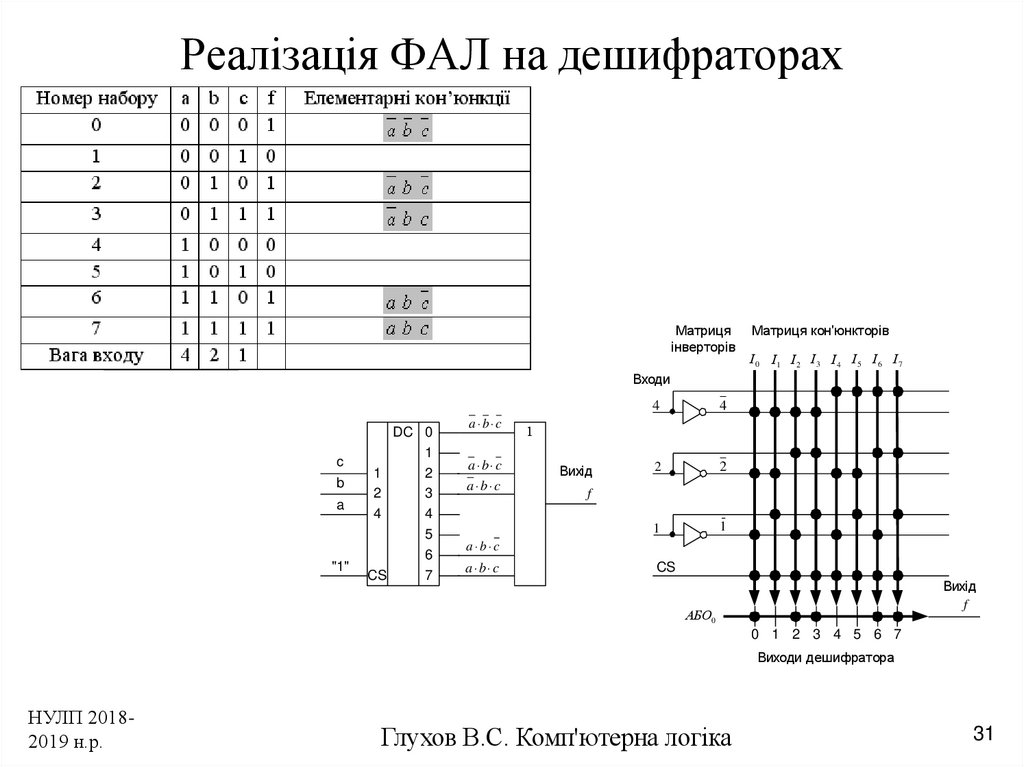

31. Реалізація ФАЛ на дешифраторах

Матрицяінверторів

Матриця кон'юнкторів

І 0 І1 І 2 І 3 І 4 І 5 І 6 І 7

Входи

c

b

a

"1"

1

2

4

CS

DC 0

1

2

3

4

5

6

7

a b c

a b c

a b c

4

4

2

2

1

1

1

Вихід

f

a b c

a b c

CS

Вихід

f

АБО0

0 1 2 3 4 5 6 7

Виходи дешифратора

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

31

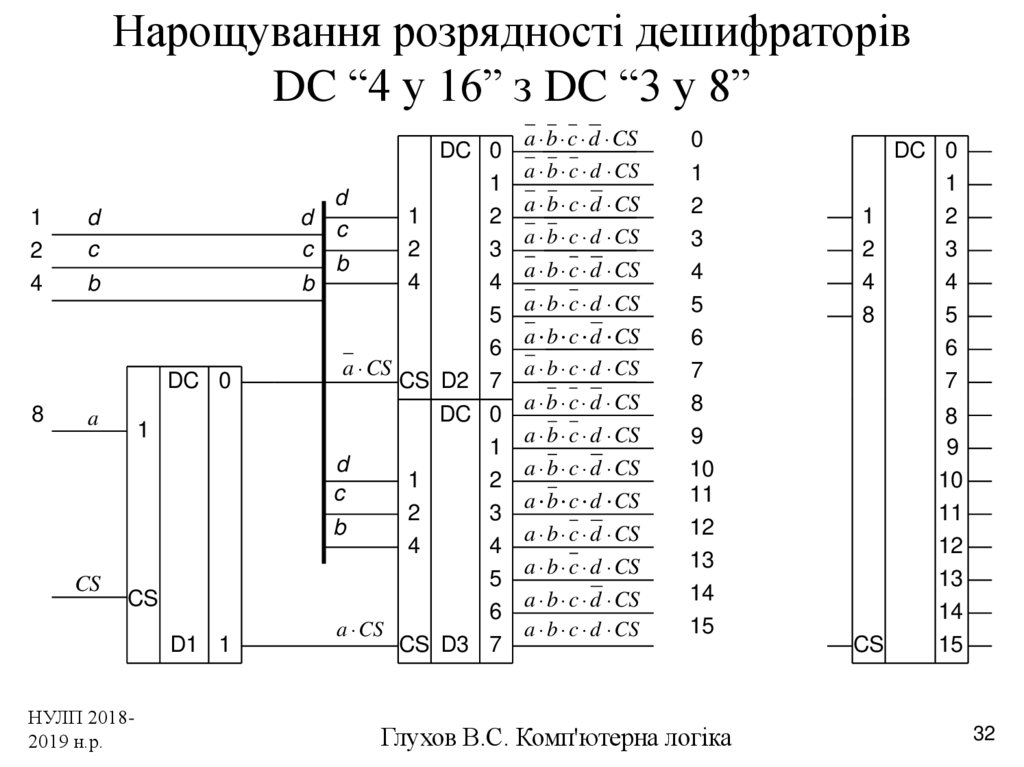

32. Нарощування розрядності дешифраторів DC “4 у 16” з DC “3 у 8”

12

4

d

c

d

c

b

b

DC 0

8

a

d

c

1

2

4

b

a CS

1

d

c

1

2

4

b

CS

CS

CS

D1 1

НУЛП 20182019 н.р.

a CS

CS

a b c d CS

DC 0

a b c d CS

1

a b c d CS

2

a b c d CS

3

a b c d CS

4

a b c d CS

5

a b c d CS

6

a b c d CS

D2 7

a b c d CS

DC 0

a b c d CS

1

a b c d CS

2

a b c d CS

3

a b c d CS

4

a b c d CS

5

a b c d CS

6

a b c d CS

D3 7

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Глухов В.С. Комп'ютерна логіка

1

2

4

8

CS

DC 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

32

33. Нарощування розрядності дешифраторів DC “3 у 8” з DC “1 у 2”

11

DC

0

ВК

1

1

DC

0

ВК

D1

1

ВК

1

1

DC

0

ВК

1

ВК D1 1

НУЛП 20182019 н.р.

ВК

D1

1

ВК

DC

D1

DC

D1

DC

D1

DC

D1

Глухов В.С. Комп'ютерна логіка

0

1

0

1

0

1

0

1

33

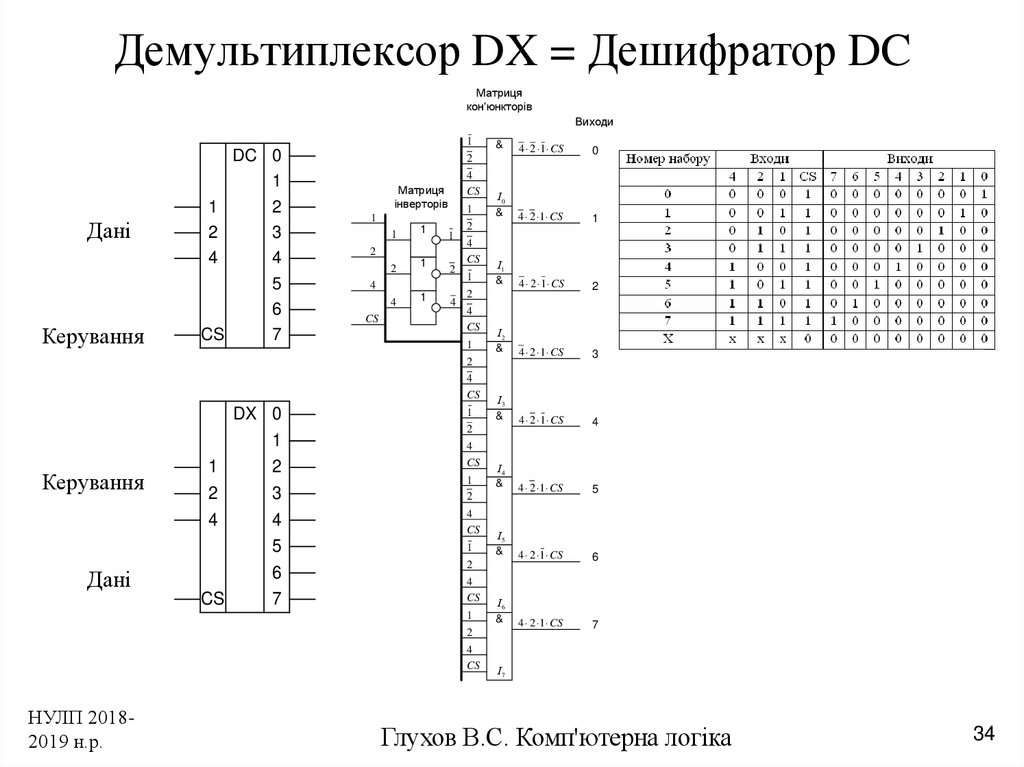

34. Демультиплексор DX = Дешифратор DC

Матрицякон'юнкторів

Виходи

1

Дані

Керування

1

2

4

CS

DC 0

1

2

3

4

5

6

7

&

4 2 1 CS

0

І0

&

4 2 1 CS

1

І1

&

4 2 1 CS

2

І2

&

4 2 1 CS

3

І3

&

4 2 1 CS

4

І4

&

4 2 1 CS

5

І5

&

4 2 1 CS

6

І6

&

4 2 1 CS

7

2

4

CS

Матриця

інверторів

1

1

1

1

2

1

4

1

1

2

2

4

CS

4

2

4

CS

1

2

4

CS

1

2

4

CS

Керування

1

2

4

Дані

CS

DX 0

1

2

3

4

5

6

7

1

2

4

CS

1

2

4

CS

1

2

4

CS

1

2

4

CS

НУЛП 20182019 н.р.

І7

Глухов В.С. Комп'ютерна логіка

34

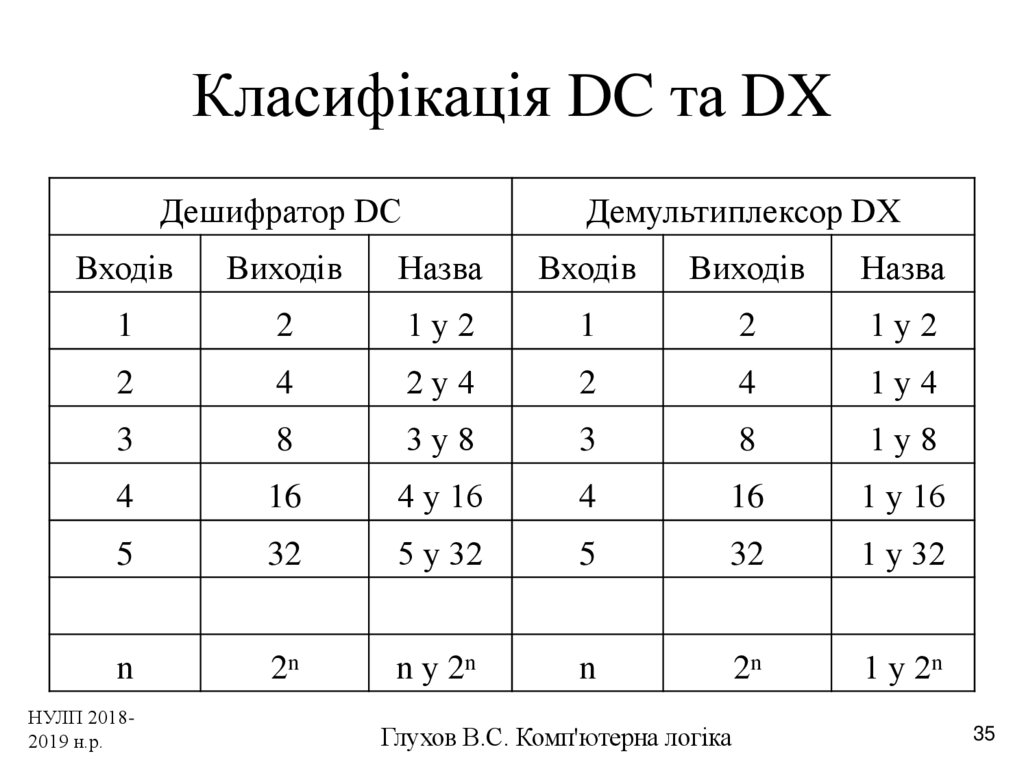

35. Класифікація DC та DX

Дешифратор DCДемультиплексор DX

Входів

Виходів

Назва

Входів

Виходів

Назва

1

2

1у2

1

2

1у2

2

4

2у4

2

4

1у4

3

8

3у8

3

8

1у8

4

16

4 у 16

4

16

1 у 16

5

32

5 у 32

5

32

1 у 32

n

2n

n у 2n

n

2n

1 у 2n

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

35

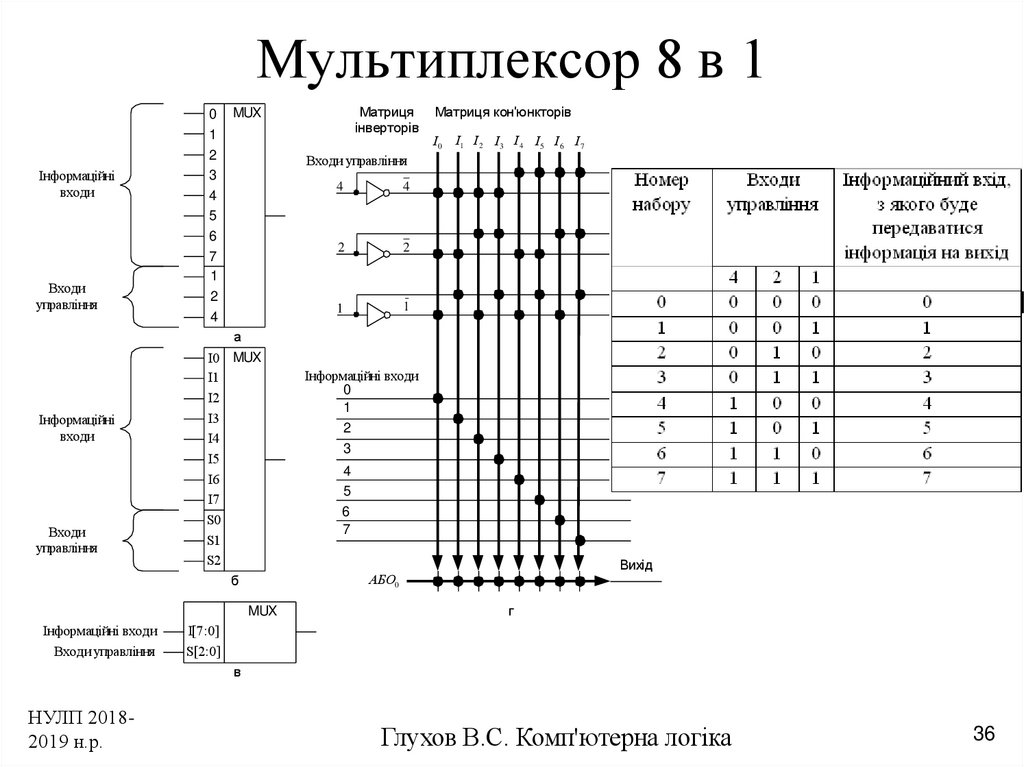

36. Мультиплексор 8 в 1

Інформаційнівходи

Входи

управління

Інформаційні

входи

Входи

управління

0

1

2

3

4

5

6

7

1

2

4

Матриця кон'юнкторів

І 0 І1 І 2 І 3 І 4 І 5 І 6 І 7

Входи управління

а

I0 MUX

I1

I2

I3

I4

I5

I6

I7

S0

S1

S2

б

MUX

Інформаційні входи

Входи управління

Матриця

інверторів

MUX

4

4

2

2

1

1

Інформаційні входи

0

1

2

3

4

5

6

7

Вихід

АБО0

г

I[7:0]

S[2:0]

в

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

36

37. VHDL-опис

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity mux is

port ( I : in std_logic_vector (7 downto 0);

S : in std_logic_vector (2 downto 0);

O : out std_logic);

end entity;

architecture mux_arch of mux is

begin

O <= I(CONV_INTEGER(S));

end architecture;

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

37

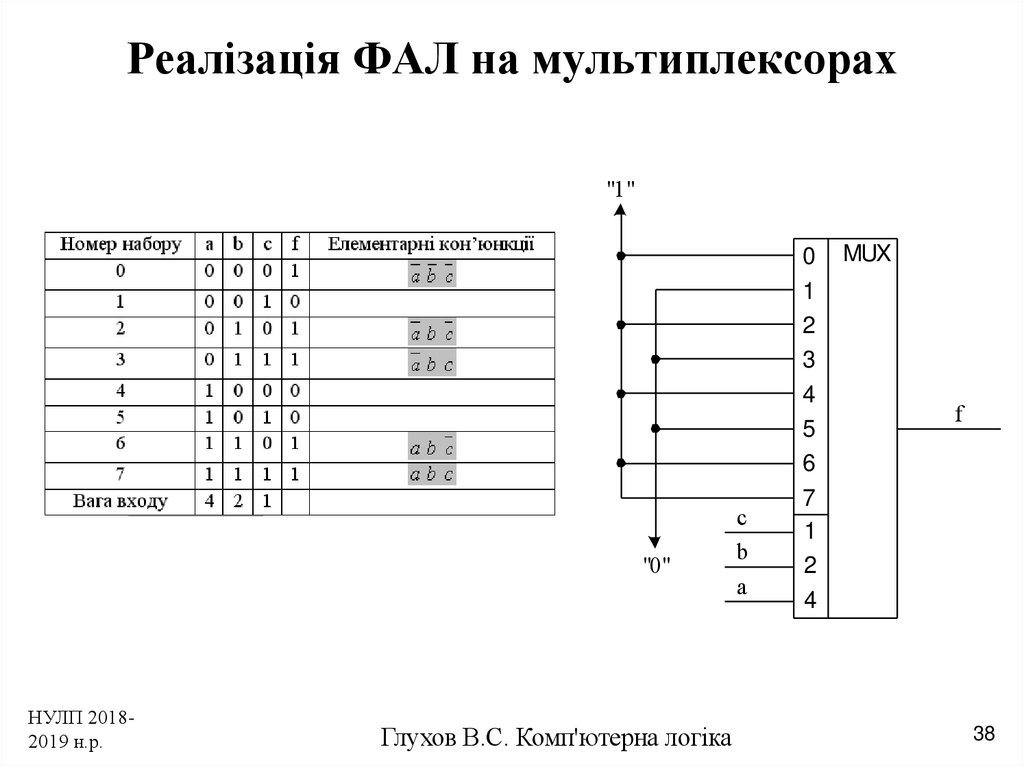

38. Реалізація ФАЛ на мультиплексорах

"1""0"

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

c

b

a

0

1

2

3

4

5

6

7

1

2

4

MUX

f

38

39. Нарощування розрядності мультиплексорів

01

2

3

4

5

6

7

1

1

2

2

4

4

8

9

10

11

12

13

14

15

1

2

4

НУЛП 20182019 н.р.

0

1

2

3

4

5

6

7

1

2

4

0

1

2

3

4

5

6

7

1

2

4

MUX

0

MUX

D1

MUX

0 MUX

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

8

1

1

D2

1

2

4

8

D2

Глухов В.С. Комп'ютерна логіка

39

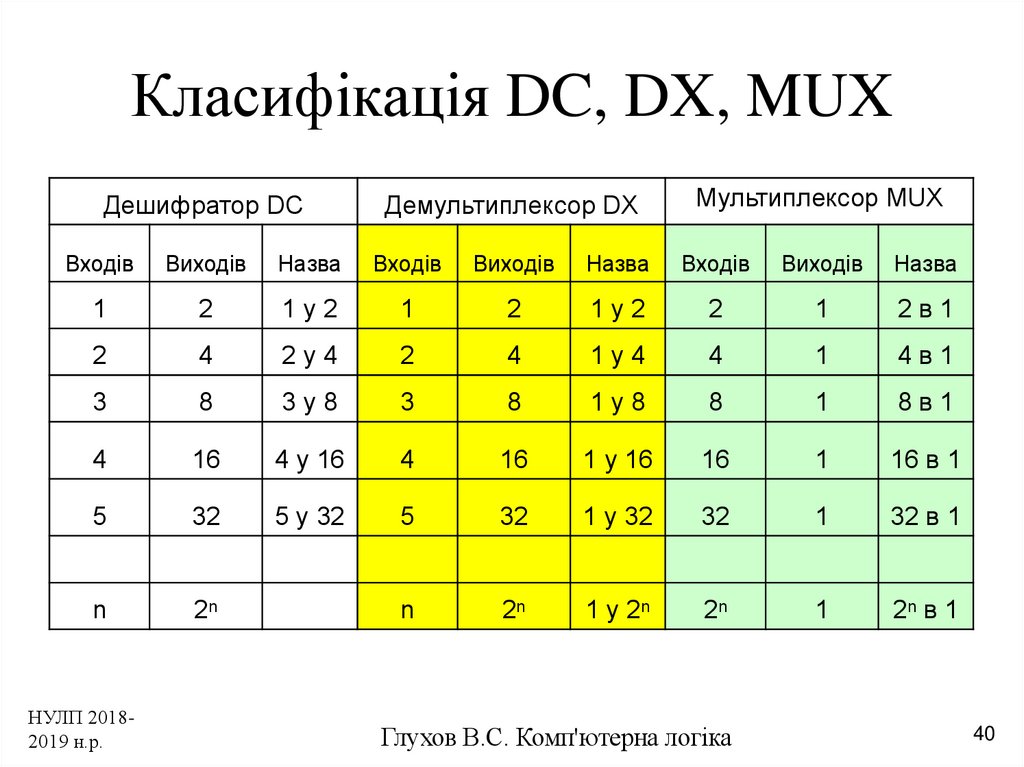

40. Класифікація DC, DX, MUX

Дешифратор DCДемультиплексор DX

Мультиплексор MUX

Входів

Виходів

Назва

Входів

Виходів

Назва

Входів

Виходів

Назва

1

2

1у2

1

2

1у2

2

1

2в1

2

4

2у4

2

4

1у4

4

1

4в1

3

8

3у8

3

8

1у8

8

1

8в1

4

16

4 у 16

4

16

1 у 16

16

1

16 в 1

5

32

5 у 32

5

32

1 у 32

32

1

32 в 1

n

2n

n

2n

1 у 2n

2n

1

2n в 1

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

40

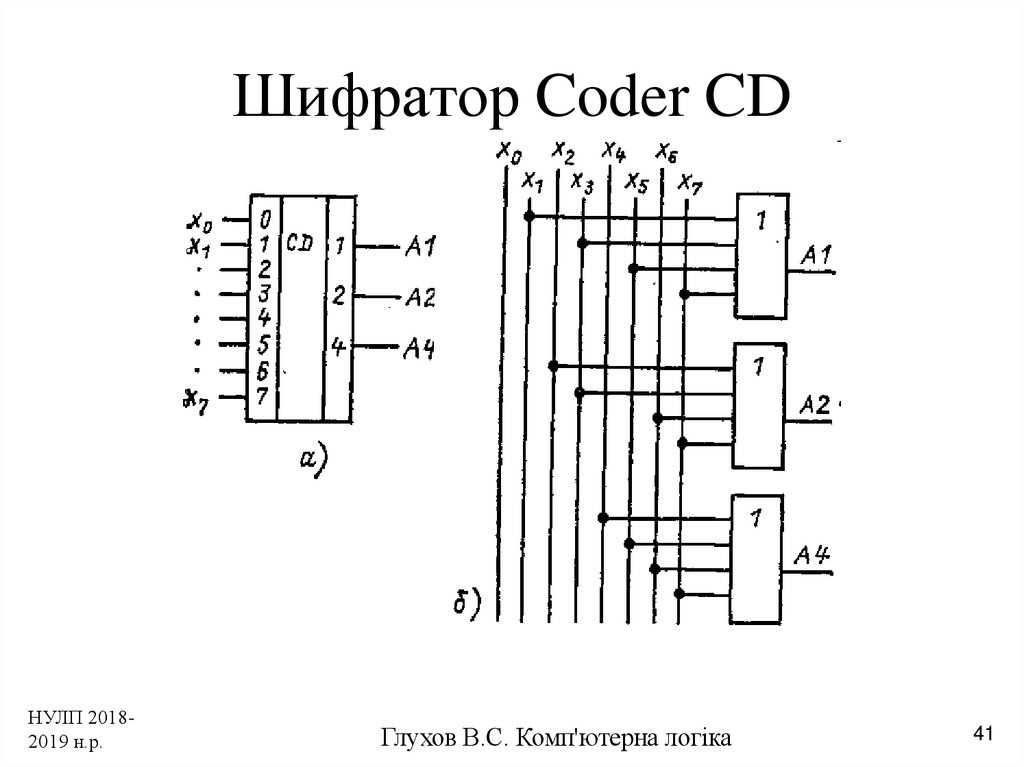

41. Шифратор Coder CD

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

41

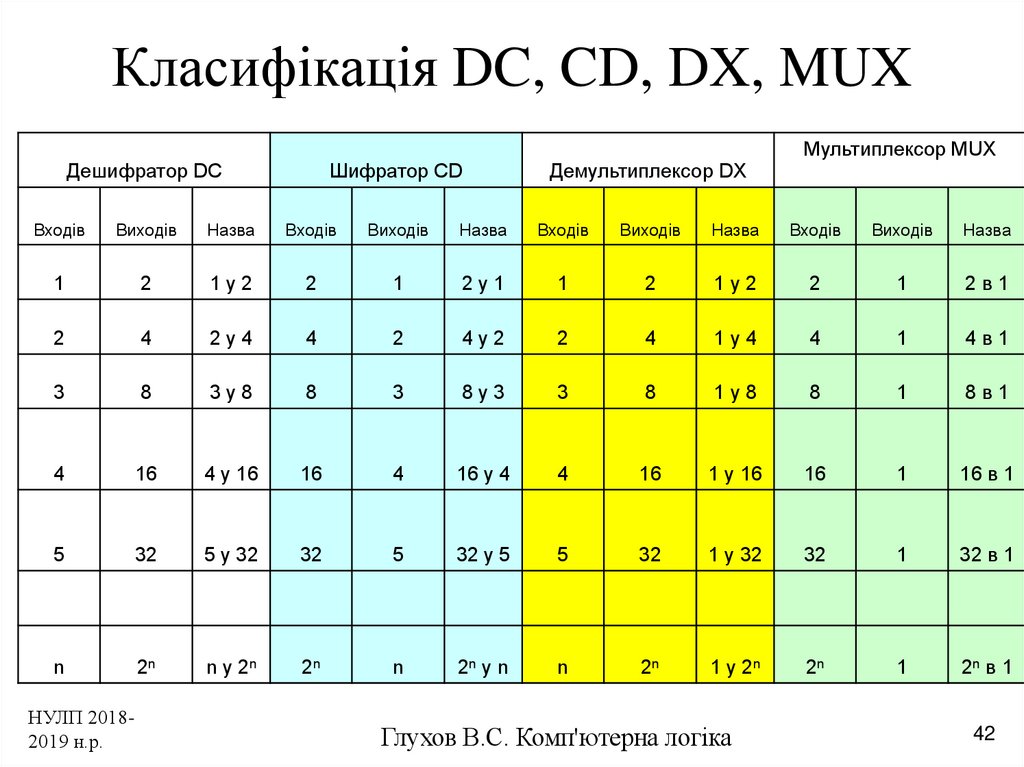

42. Класифікація DC, CD, DX, MUX

Дешифратор DCШифратор CD

Демультиплексор DX

Мультиплексор MUX

Входів

Виходів

Назва

Входів

Виходів

Назва

Входів

Виходів

Назва

Входів

Виходів

Назва

1

2

1у2

2

1

2у1

1

2

1у2

2

1

2в1

2

4

2у4

4

2

4у2

2

4

1у4

4

1

4в1

3

8

3у8

8

3

8у3

3

8

1у8

8

1

8в1

4

16

4 у 16

16

4

16 у 4

4

16

1 у 16

16

1

16 в 1

5

32

5 у 32

32

5

32 у 5

5

32

1 у 32

32

1

32 в 1

n

2n

n у 2n

2n

n

2n у n

n

2n

1 у 2n

2n

1

2n в 1

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

42

43. Пріоритетний шифратор

CD0

1

2

0

1

2

1

3

4

5

6

7

2

4

3

4

5

6

7

CD

1

2

4

RDY

7

6

5

4

3

2

1

0

4

2

1

1

0

0

0

0

0

0

0

1

1

1

0

1

0

0

0

0

0

0

1

1

0

0

0

1

0

0

0

0

0

1

0

1

0

0

0

1

0

0

0

0

1

0

0

0

0

0

0

1

0

0

0

0

1

1

0

0

0

0

0

1

0

0

0

1

0

0

0

0

0

0

0

1

0

0

0

1

0

0

0

0

0

0

0

1

0

0

0

Rd

0

1

2

3

4

5

6

7

6

5

4

3

2

1

0

4

2

1

1

X

X

X

X

X

X

X

1

1

1

1

0

1

X

X

X

X

X

X

1

1

0

1

0

0

1

X

X

X

X

X

1

0

1

1

1

0

0

0

1

X

X

X

X

1

0

0

1

2

0

0

0

0

1

X

X

X

0

1

1

1

0

0

0

0

0

1

X

X

0

1

0

1

0

0

0

0

0

0

1

X

0

0

1

1

0

0

0

0

0

0

0

1

0

0

0

1

0

0

0

0

0

0

0

0

X

X

X

0

7

4

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

y

43

44. Двійково-десяткові коди

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

44

45. Перетворювач кодів 8421 у 8421+3 DC + CD

Перетворювач кодів 8421 у 8421+3‘0’

DC + CD

DC

a1

a2

a4

a8

НУЛП 20182019 н.р.

1

2

4

8

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

0

1

2

3

4

5

6

7

8

9

a

b

c

d

e

f

‘0’

‘0’

‘0’

0

1

2

3

4

5

6

7

8

9

‘0’

‘0’

‘0’

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

CD

1

2

4

8

b1

b2

b4

b8

a1

a2

a4

a8

a1

a2

a4

a8

Глухов В.С. Комп'ютерна логіка

X/Y

b1

b2

b4

b8

b1

b2

b4

b8

45

46. Матрична схема перетворювача коду 8421 у код 8421+3

84

Дешифратор –

набір елементів І,

матриця І

2

1

АБО1

8

АБО2

4

АБО3

2

АБО4

1

Шифратор –

набір елементів

АБО, матриця АБО

I0 I1 I2 I3 I4 I5 I6 I7 I8 I9 I10 I11 I12 I13 I14 I15

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

46

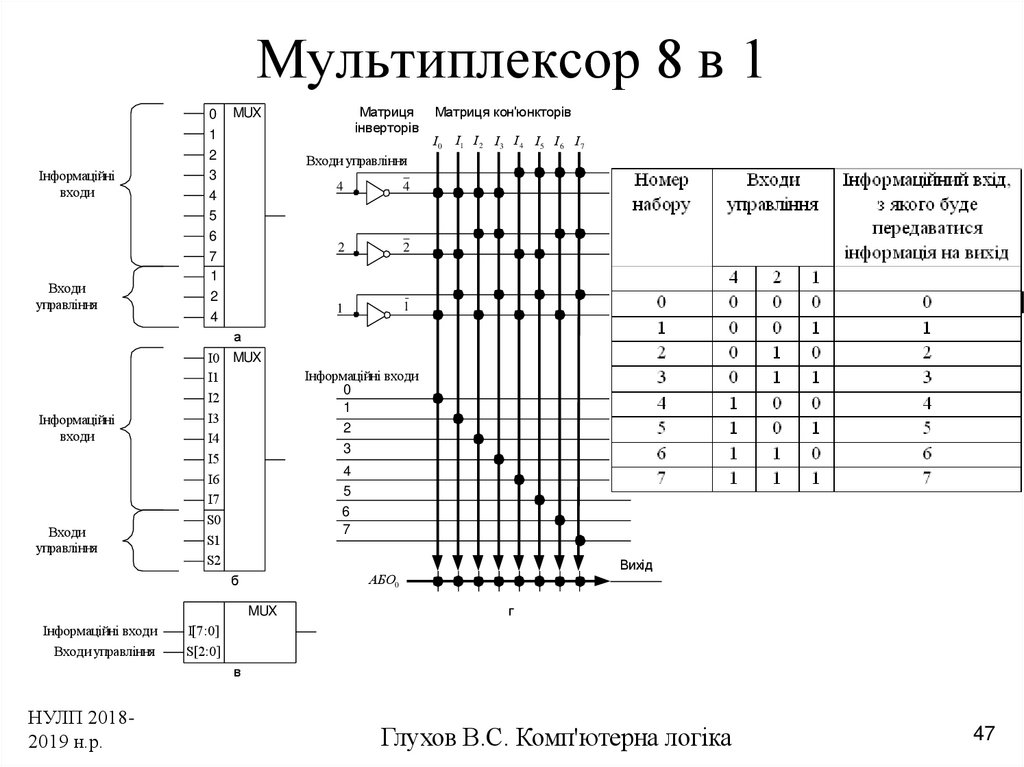

47. Мультиплексор 8 в 1

Інформаційнівходи

Входи

управління

Інформаційні

входи

Входи

управління

0

1

2

3

4

5

6

7

1

2

4

Матриця кон'юнкторів

І 0 І1 І 2 І 3 І 4 І 5 І 6 І 7

Входи управління

а

I0 MUX

I1

I2

I3

I4

I5

I6

I7

S0

S1

S2

б

MUX

Інформаційні входи

Входи управління

Матриця

інверторів

MUX

4

4

2

2

1

1

Інформаційні входи

0

1

2

3

4

5

6

7

Вихід

АБО0

г

I[7:0]

S[2:0]

в

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

47

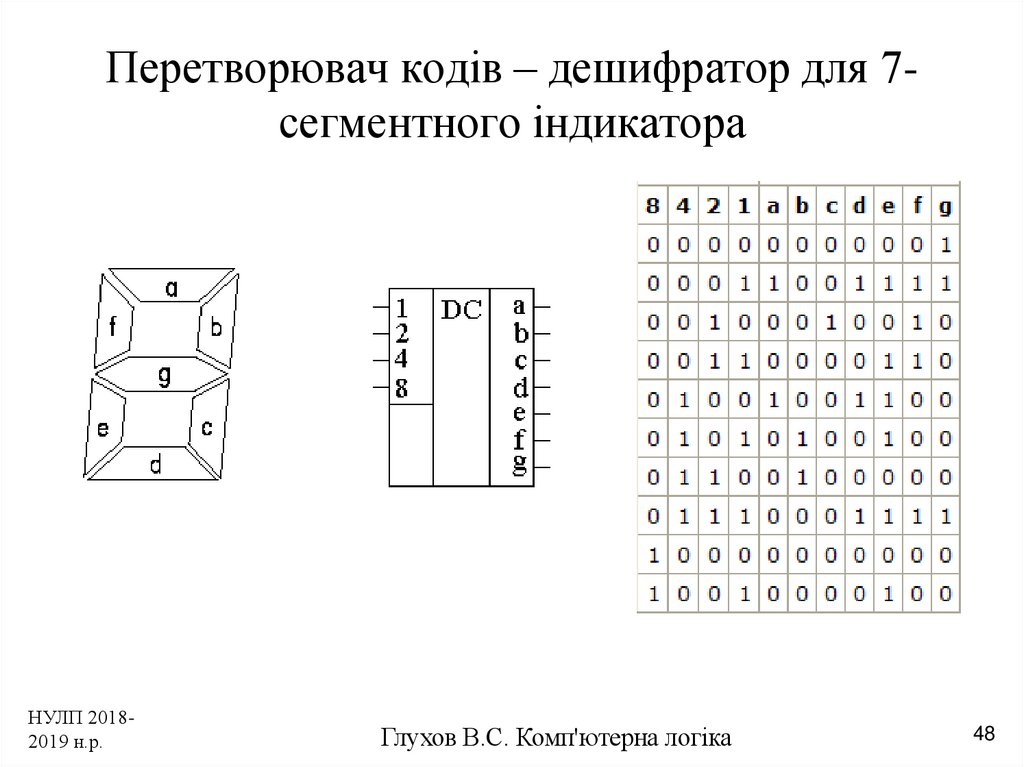

48. Перетворювач кодів – дешифратор для 7-сегментного індикатора

Перетворювач кодів – дешифратор для 7сегментного індикатораНУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

48

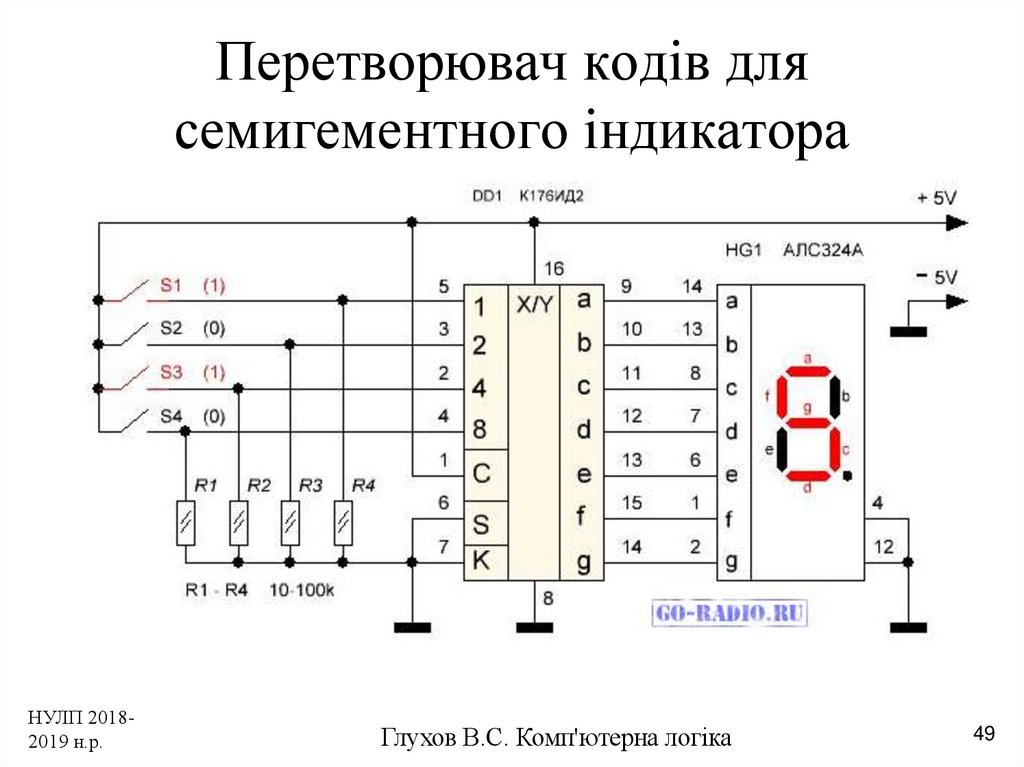

49. Перетворювач кодів для семигементного індикатора

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

49

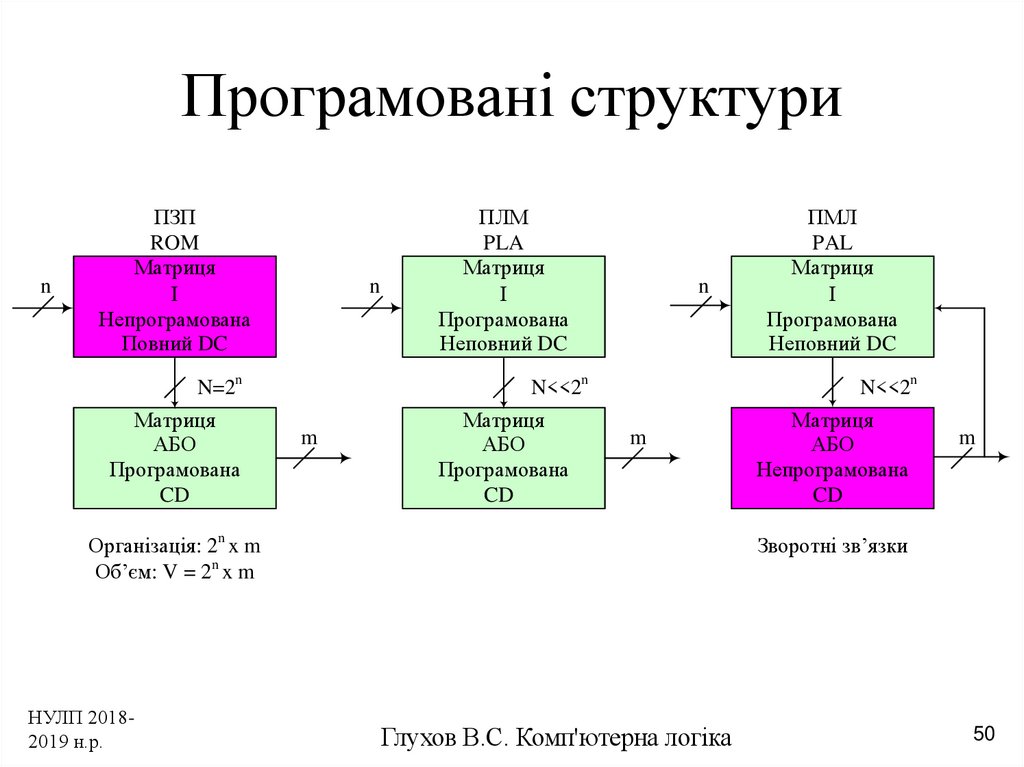

50. Програмовані структури

nПЗП

ROM

Матриця

І

Непрограмована

Повний DC

n

N=2n

Матриця

АБО

Програмована

CD

ПЛМ

PLA

Матриця

І

Програмована

Неповний DC

n

N<<2n

m

Матриця

АБО

Програмована

CD

N<<2n

m

Організація: 2n x m

Об’єм: V = 2n x m

НУЛП 20182019 н.р.

ПМЛ

PAL

Матриця

І

Програмована

Неповний DC

Матриця

АБО

Непрограмована

CD

m

Зворотні зв’язки

Глухов В.С. Комп'ютерна логіка

50

51. Постійний запам’ятовуючий пристій

Матриця кон'юнкторів(елементів І)

ROM

A0

A1

D0

D1

D2

D3

A2

Матриця І 0 І1 І 2 І 3 І 4 І 5 І 6 І 7

інверторів

Входи

A2

A2

A1

A1

A0

A0

CS

а

ROM

D[3:0]

A[2:0]

CS

б

CS

Виходи

- точки, де завжди

є з'єднання

- точки, де може бути

з'єднання

АБО0

D0

D1

D2

D3

АБО1

АБО2

АБО3

Матриця диз'юнкторів

(елементів АБО)

в

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

51

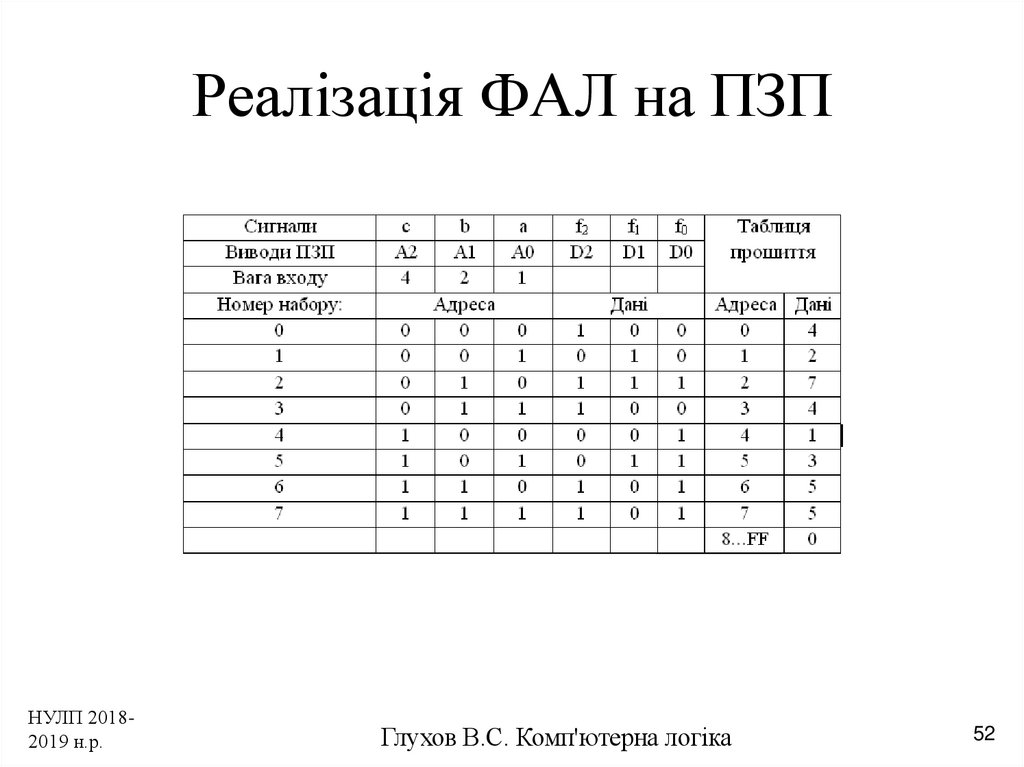

52. Реалізація ФАЛ на ПЗП

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

52

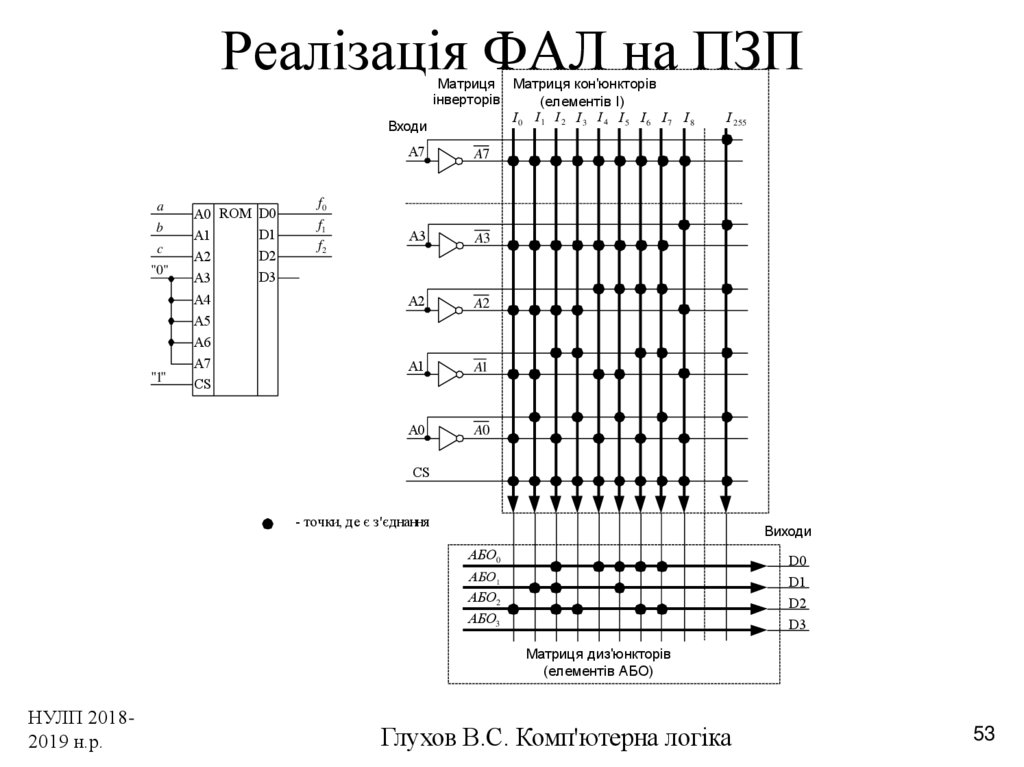

53. Реалізація ФАЛ на ПЗП

Входиa

b

c

"0"

"1"

A0 ROM D0

D1

A1

D2

A2

D3

A3

A4

A5

A6

A7

CS

Матриця Матриця кон'юнкторів

інверторів

(елементів І)

І 0 І1 І 2 І 3 І 4 І 5 І 6 І 7 І 8

A7

A7

A3

A3

A2

A2

A1

A1

A0

A0

І 255

f0

f1

f2

CS

- точки, де є з'єднання

Виходи

АБО0

D0

D1

D2

D3

АБО 1

АБО2

АБО3

Матриця диз'юнкторів

(елементів АБО)

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

53

54. Мультиплексор 8 в 1

Інформаційнівходи

Входи

управління

Інформаційні

входи

Входи

управління

0

1

2

3

4

5

6

7

1

2

4

Матриця кон'юнкторів

І 0 І1 І 2 І 3 І 4 І 5 І 6 І 7

Входи управління

а

I0 MUX

I1

I2

I3

I4

I5

I6

I7

S0

S1

S2

б

MUX

Інформаційні входи

Входи управління

Матриця

інверторів

MUX

4

4

2

2

1

1

Інформаційні входи

0

1

2

3

4

5

6

7

Вихід

АБО0

г

I[7:0]

S[2:0]

в

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

54

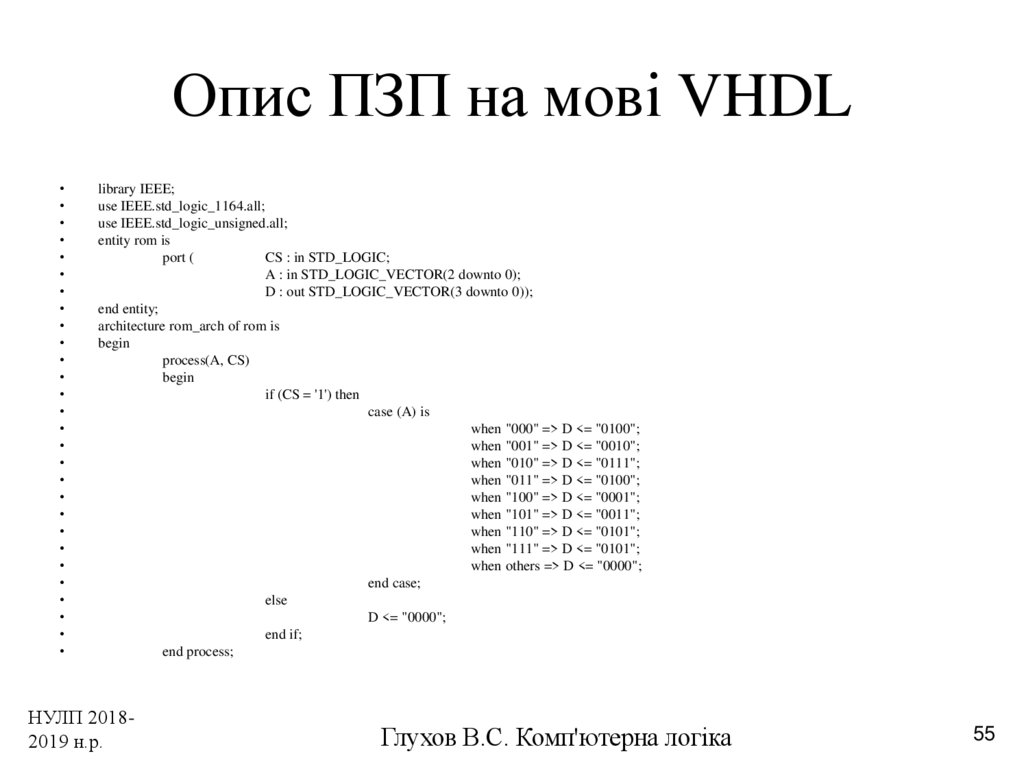

55. Опис ПЗП на мові VHDL

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity rom is

port (

CS : in STD_LOGIC;

A : in STD_LOGIC_VECTOR(2 downto 0);

D : out STD_LOGIC_VECTOR(3 downto 0));

end entity;

architecture rom_arch of rom is

begin

process(A, CS)

begin

if (CS = '1') then

case (A) is

when "000" => D <= "0100";

when "001" => D <= "0010";

when "010" => D <= "0111";

when "011" => D <= "0100";

when "100" => D <= "0001";

when "101" => D <= "0011";

when "110" => D <= "0101";

when "111" => D <= "0101";

when others => D <= "0000";

end case;

else

D <= "0000";

end if;

end process;

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

55

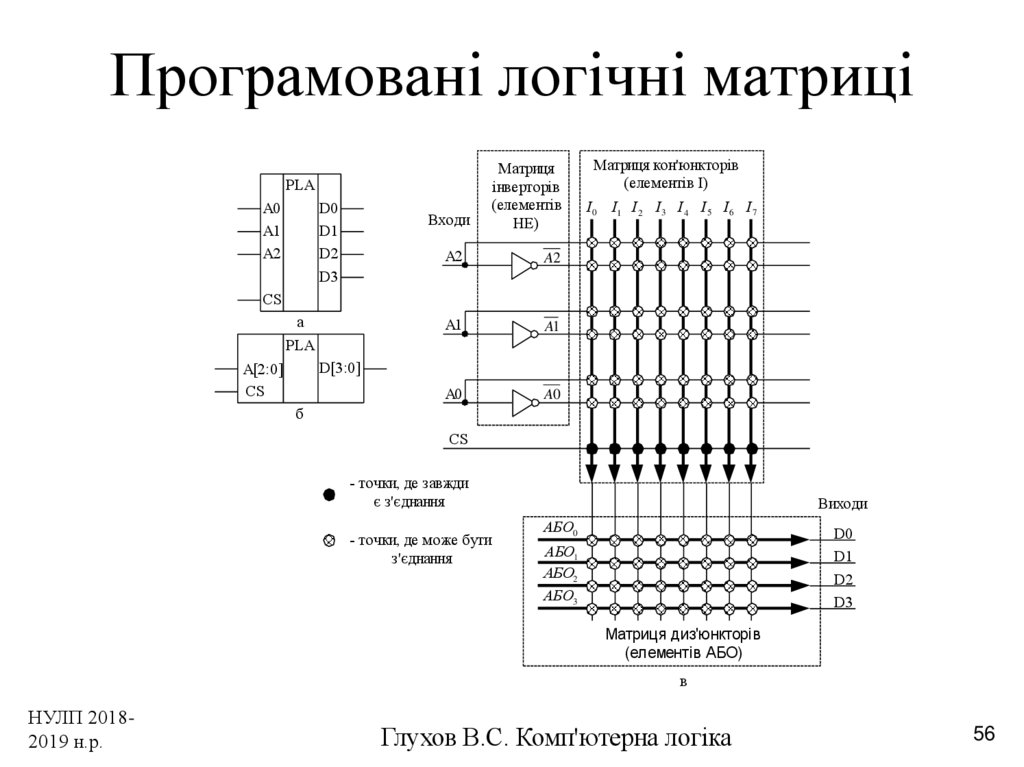

56. Програмовані логічні матриці

PLAD0

D1

D2

D3

A0

A1

A2

Входи

Матриця

інверторів

(елементів

НЕ)

A2

A2

A1

A1

A0

A0

Матриця кон'юнкторів

(елементів І)

І 0 І1 І 2 І 3 І 4 І 5 І 6 І 7

CS

а

PLA

D[3:0]

A[2:0]

CS

б

CS

- точки, де завжди

є з'єднання

- точки, де може бути

з'єднання

Виходи

АБО0

D0

D1

D2

D3

АБО1

АБО2

АБО3

Матриця диз'юнкторів

(елементів АБО)

в

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

56

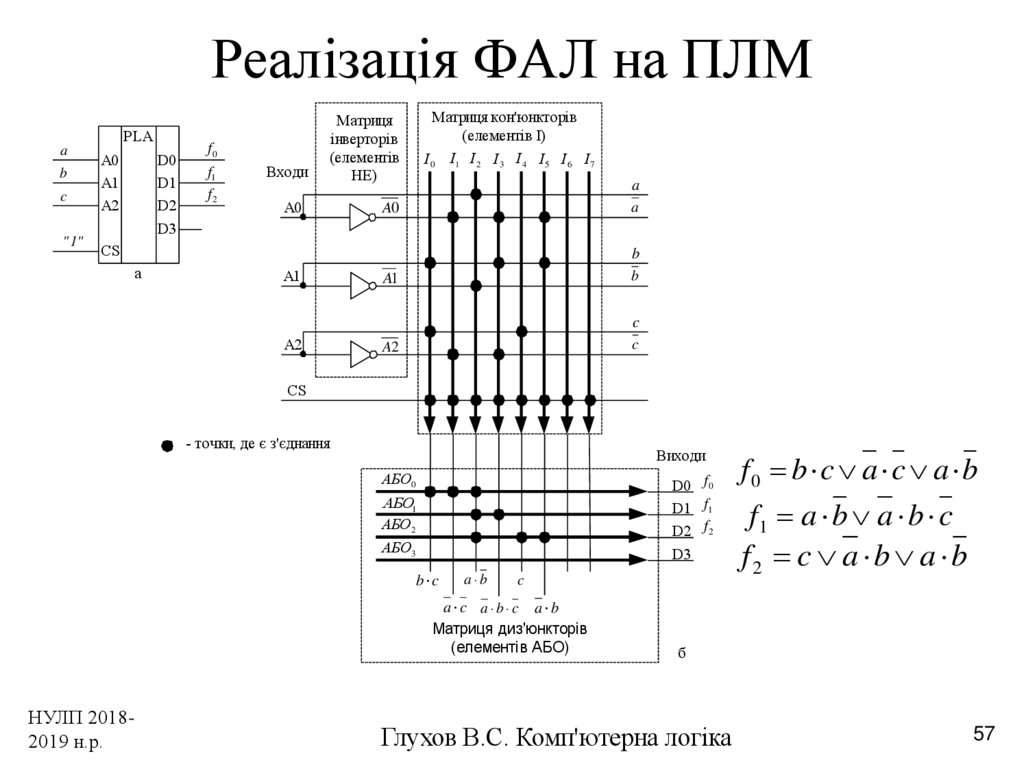

57. Реалізація ФАЛ на ПЛМ

PLAa

b

c

"1"

A0

A1

A2

D0

D1

D2

D3

f0

f1

f2

Входи

Матриця кон'юнкторів

(елементів І)

І 0 І1 І 2 І 3 І 4 І 5 І 6 І 7

Матриця

інверторів

(елементів

НЕ)

A0

A0

a

a

A1

b

b

A2

c

c

CS

а

A1

A2

CS

- точки, де є з'єднання

Виходи

АБО0

D0 f0

D1 f1

D2 f2

D3

АБО1

АБО 2

АБО3

b c

a b

c

a c a b c a b

Матриця диз'юнкторів

(елементів АБО)

НУЛП 20182019 н.р.

f0 b c a c a b

f1 a b a b c

f2 c a b a b

б

Глухов В.С. Комп'ютерна логіка

57

58. Таблиця прошиття ПЛМ

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

58

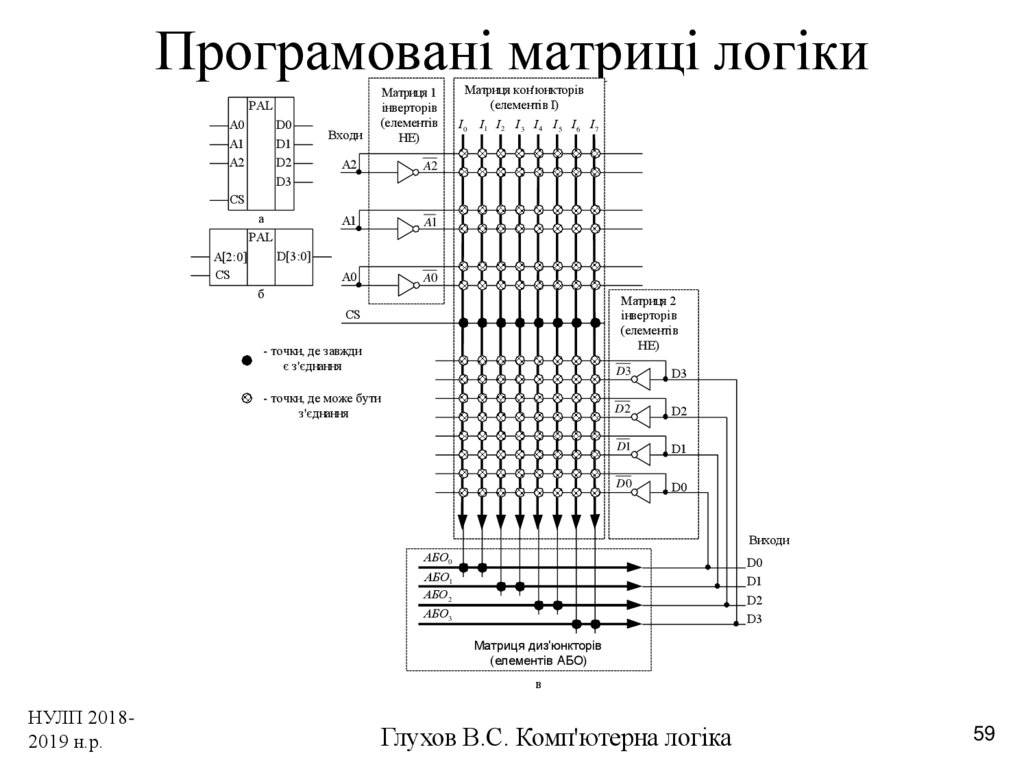

59. Програмовані матриці логіки

PALA0

A1

A2

D0

D1

D2

D3

Входи

Матриця 1

інверторів

(елементів

НЕ)

A2

A2

A1

A1

A0

A0

Матриця кон'юнкторів

(елементів І)

І 0 І1 І 2 І 3 І 4 І 5 І 6 І 7

CS

а

PAL

D[3:0]

A[2:0]

CS

б

Матриця 2

інверторів

(елементів

НЕ)

CS

- точки, де завжди

є з'єднання

D3

D3

- точки, де може бути

з'єднання

D2

D2

D1

D1

D0

D0

Виходи

АБО0

D0

D1

D2

D3

АБО1

АБО 2

АБО3

Матриця диз'юнкторів

(елементів АБО)

в

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

59

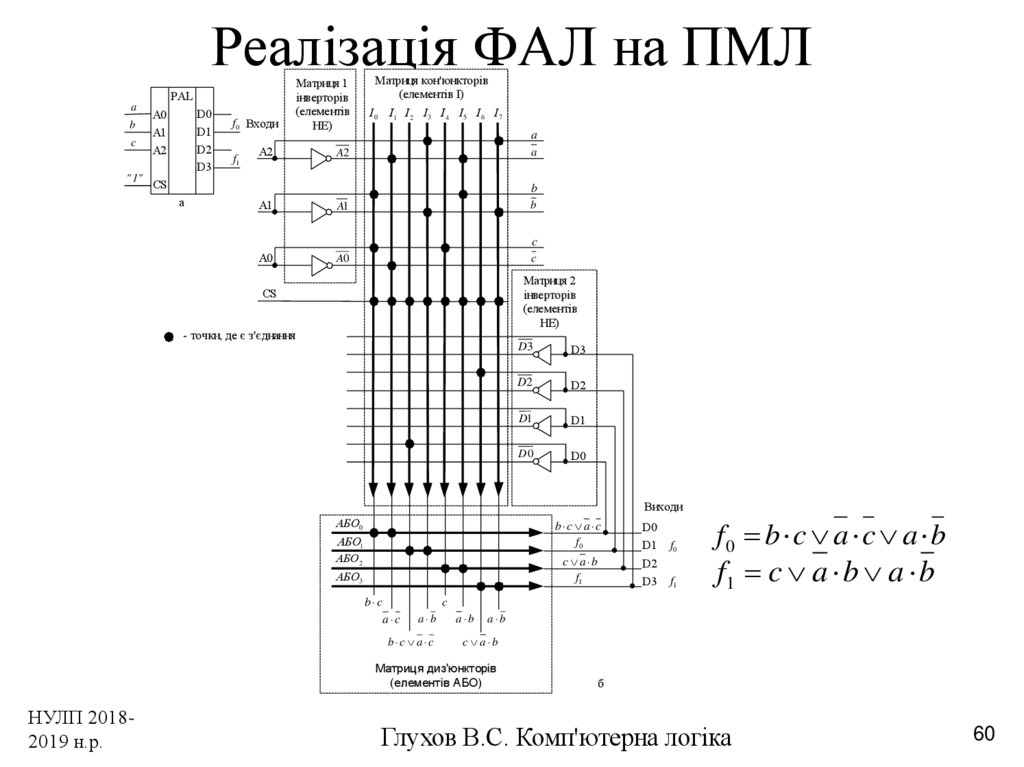

60. Реалізація ФАЛ на ПМЛ

PALa

b

c

"1"

D0

D1

D2

D3

A0

A1

A2

f0 Входи

f1

Матриця 1

інверторів

(елементів

НЕ)

Матриця кон'юнкторів

(елементів І)

І 0 І1 І 2 І 3 І 4 І 5 І 6 І 7

A2

a

a

A1

A1

b

b

A0

A0

c

c

A2

CS

а

Матриця 2

інверторів

(елементів

НЕ)

CS

- точки, де є з'єднання

D3

D3

D2

D2

D1

D1

D0

D0

Виходи

АБО0

АБО1

АБО 2

АБО3

b c

a c

D0

D1

c a b

f1

f0

D2

D3

f1

f0 b c a c a b

f1 c a b a b

c

a b

b c a c

a b

a b

c a b

Матриця диз'юнкторів

(елементів АБО)

НУЛП 20182019 н.р.

b c a c

f0

б

Глухов В.С. Комп'ютерна логіка

60

61. Таблиця прошиття ПМЛ

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

61

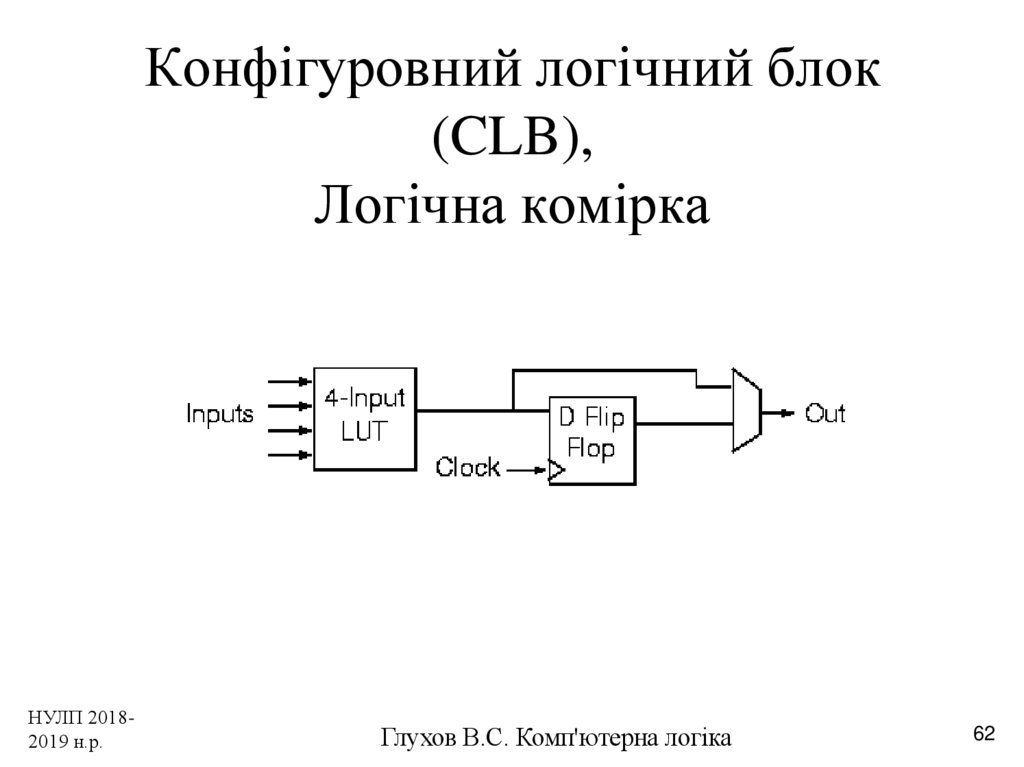

62. Конфігуровний логічний блок (CLB), Логічна комірка

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

62

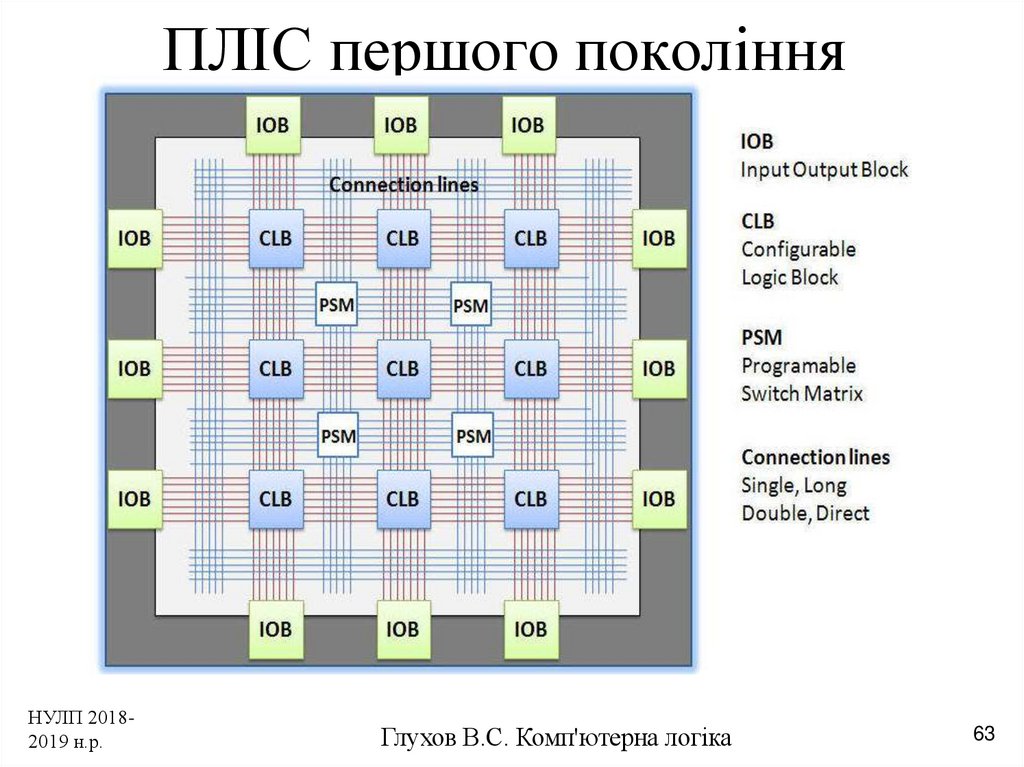

63. ПЛІС першого покоління

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

63

64. Конфігуровані логічні блоки (CLB) та електронні комутатори (PSM -Programmable switch matrix )

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

64

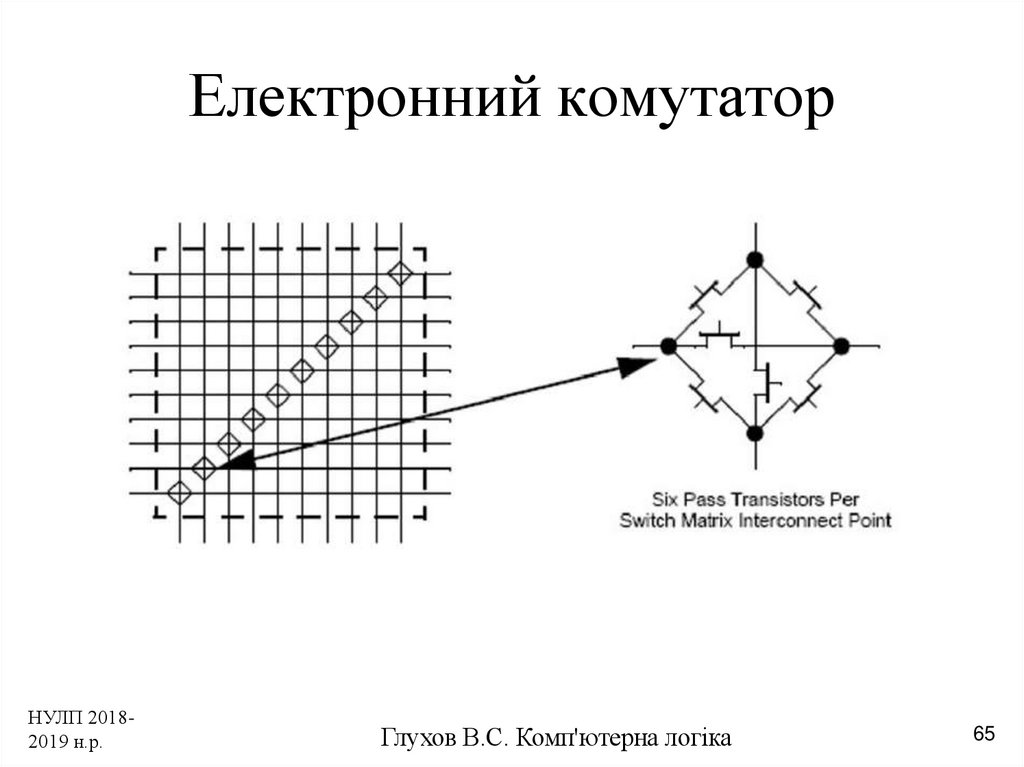

65. Електронний комутатор

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

65

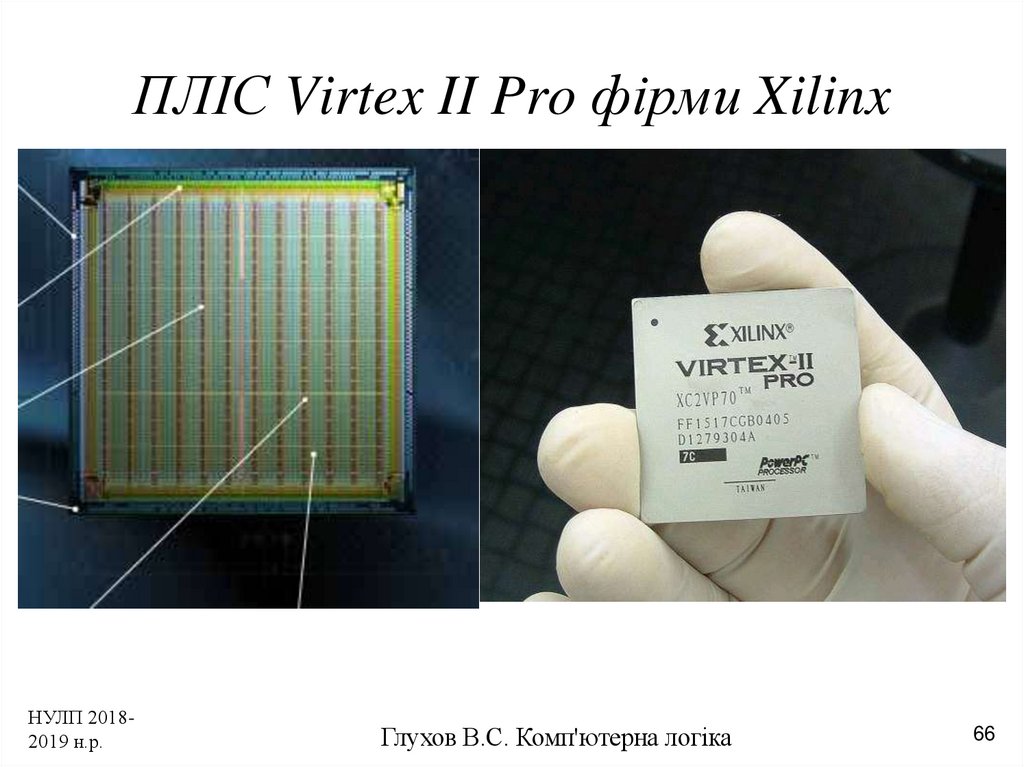

66. ПЛІС Virtex II Pro фірми Xilinx

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

66

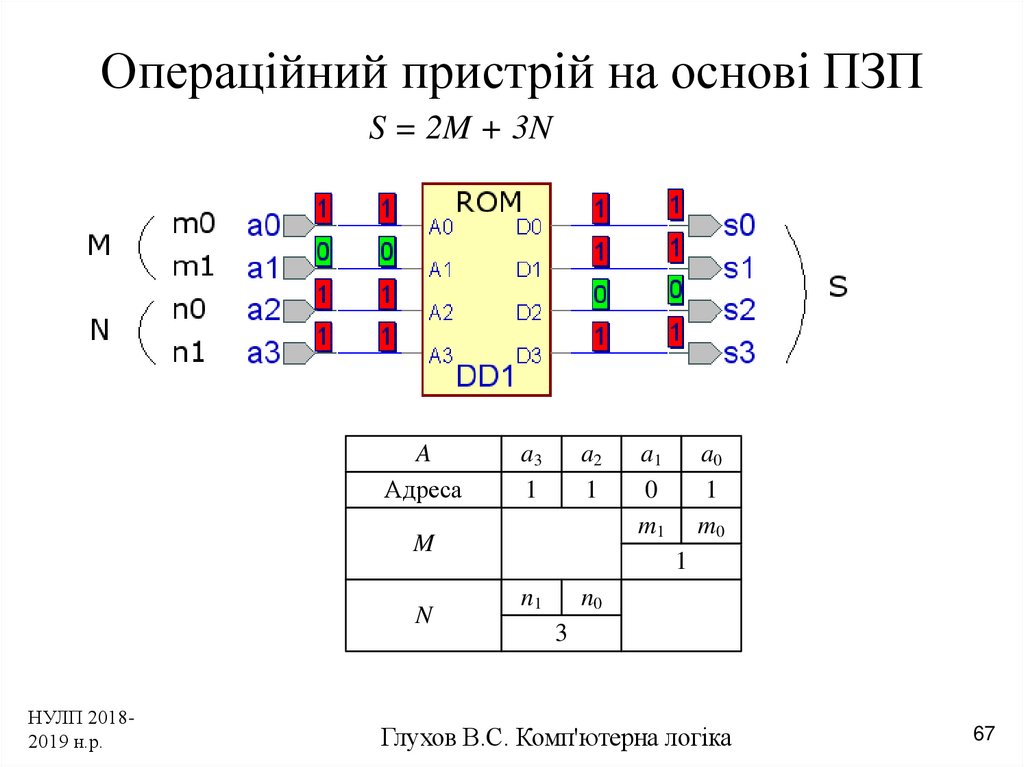

67. Операційний пристрій на основі ПЗП

S = 2M + 3NA

Адреса

a3

1

a2

1

M

N

НУЛП 20182019 н.р.

a1

0

m1

a0

1

m0

1

n1

n0

3

Глухов В.С. Комп'ютерна логіка

67

68. Таблиця прошиття ПЗП

A(адреса

ПЗП)

A10

a2

A2

n0

a3

A3

n1

НУЛП 20182019 н.р.

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

a0

A0

m0

a1

A1

m1

N

2M + 3N=S

M

S16

M

N

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

Дані

Розрахунок

Адреса

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

0

0

0

1

1

1

1

2

2

2

2

3

3

3

3

0

1

2

3

0

1

2

3

0

1

2

3

0

1

2

3

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

0

1

2

3

0

1

2

3

0

1

2

3

0

1

2

3

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

*0

*0

*0

*0

*1

*1

*1

*1

*2

*2

*2

*2

*3

*3

*3

*3

=

=

=

=

=

=

=

=

=

=

=

=

=

=

=

=

0

2

4

6

3

5

7

9

6

8

10

12

9

11

13

15

0

2

4

6

3

5

7

9

6

8

A

С

9

B

D

F

s3

D1

0

0

0

0

0

0

0

1

0

1

1

1

1

1

1

1

s2

D0

0

0

1

1

0

1

1

0

1

0

0

1

0

0

1

1

Глухов В.С. Комп'ютерна логіка

s1

D1

0

1

0

1

1

0

1

0

1

0

1

0

0

1

0

1

s0

D0

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

D

(дані

ПЗП)

0

2

4

6

3

5

7

9

6

8

A

С

9

B

D

F

68

69. Пам’ять перших комп’ютерів

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

69

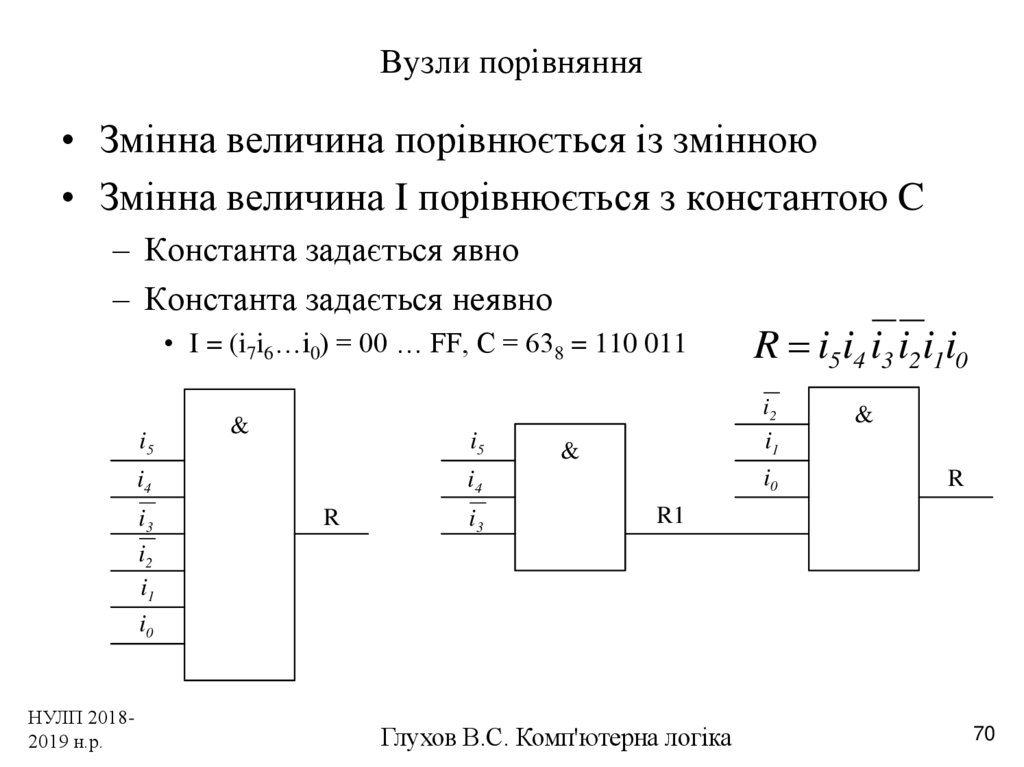

70. Вузли порівняння

• Змінна величина порівнюється із змінною• Змінна величина I порівнюється з константою C

– Константа задається явно

– Константа задається неявно

• I = (i7i6…i0) = 00 … FF, C = 638 = 110 011

i5

i2

&

i5

i4

i3

i2

i1

R i5 i4 i3 i2 i1i0

i1

&

i0

i4

R

i3

&

R

R1

i0

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

70

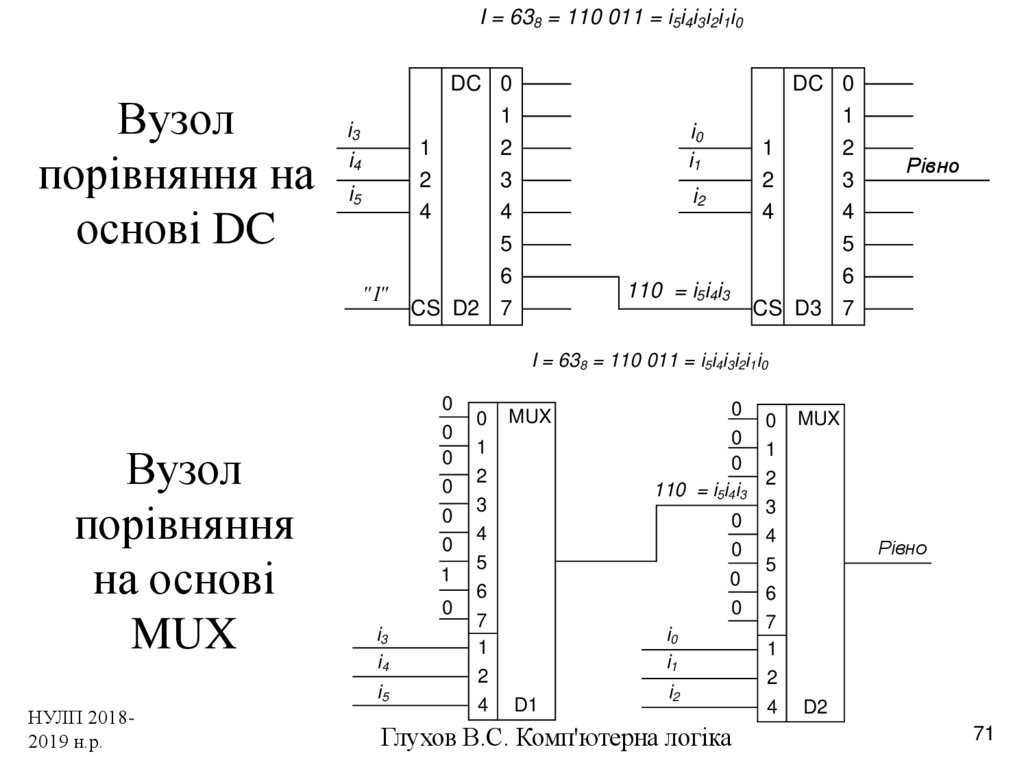

71. Вузол порівняння на основі DC

I = 638 = 110 011 = i5i4i3i2i1i0Вузол

порівняння на

основі DC

i3

i4

1

2

4

i5

" 1"

CS

DC 0

1

2

3

4

5

6

D2 7

i0

i1

i2

110 = i5i4i3

1

2

4

CS

DC 0

1

2

3

4

5

6

D3 7

Рівно

I = 638 = 110 011 = i5i4i3i2i1i0

Вузол

порівняння

на основі

MUX

0

0

0

0

0

0

1

0

i3

i4

i5

НУЛП 20182019 н.р.

0

1

2

3

4

5

6

7

1

2

4

MUX

D1

0

0

0

1

0

2

110 = i5i4i3

3

0

4

0

5

0

6

0

7

i0

1

i1

2

i2

4

Глухов В.С. Комп'ютерна логіка

MUX

Рівно

D2

71

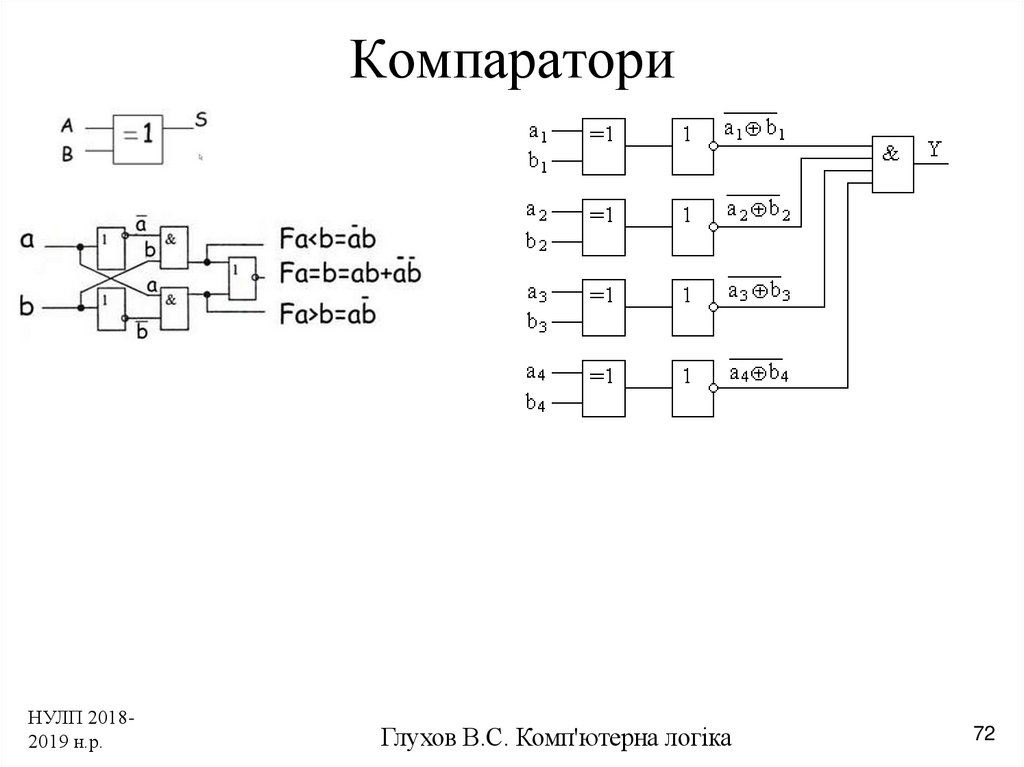

72. Компаратори

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

72

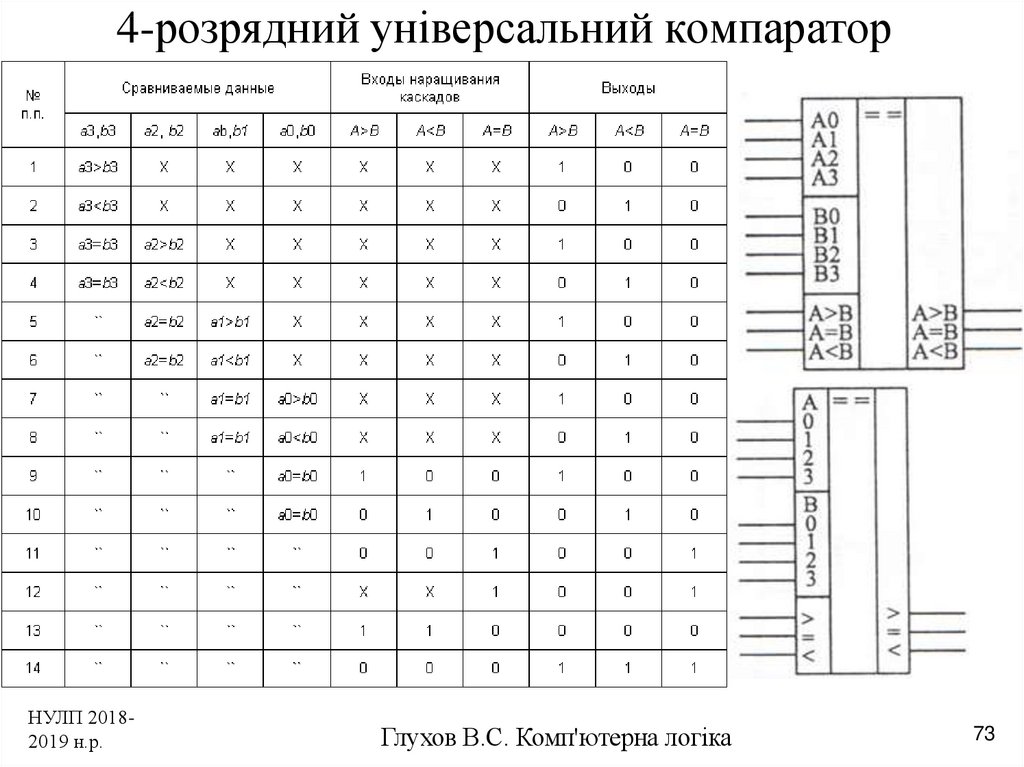

73. 4-розрядний універсальний компаратор

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

73

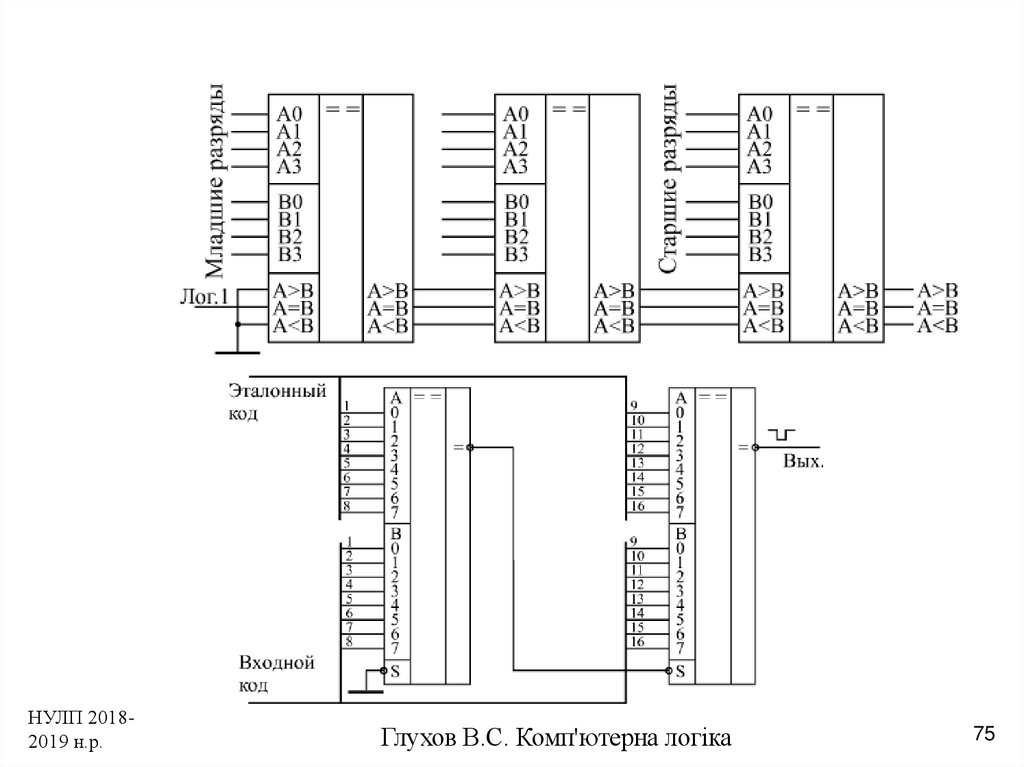

74. Багаторозрядні компаратори

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

74

75.

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

75

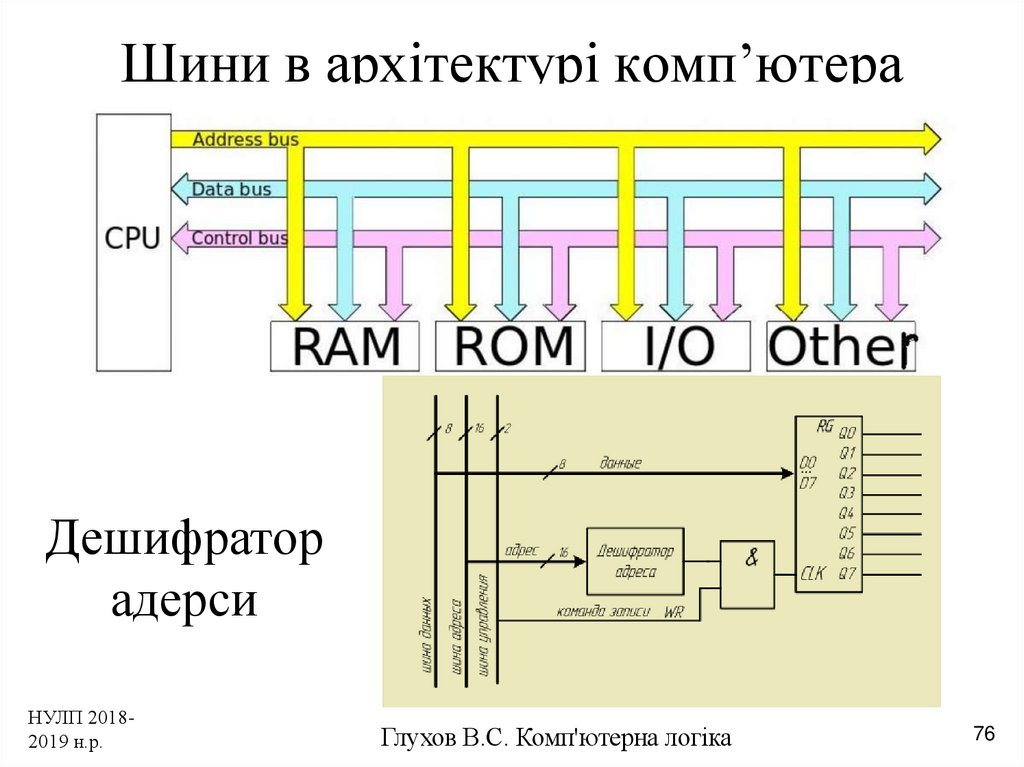

76. Шини в архітектурі комп’ютера

Дешифраторадерси

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

76

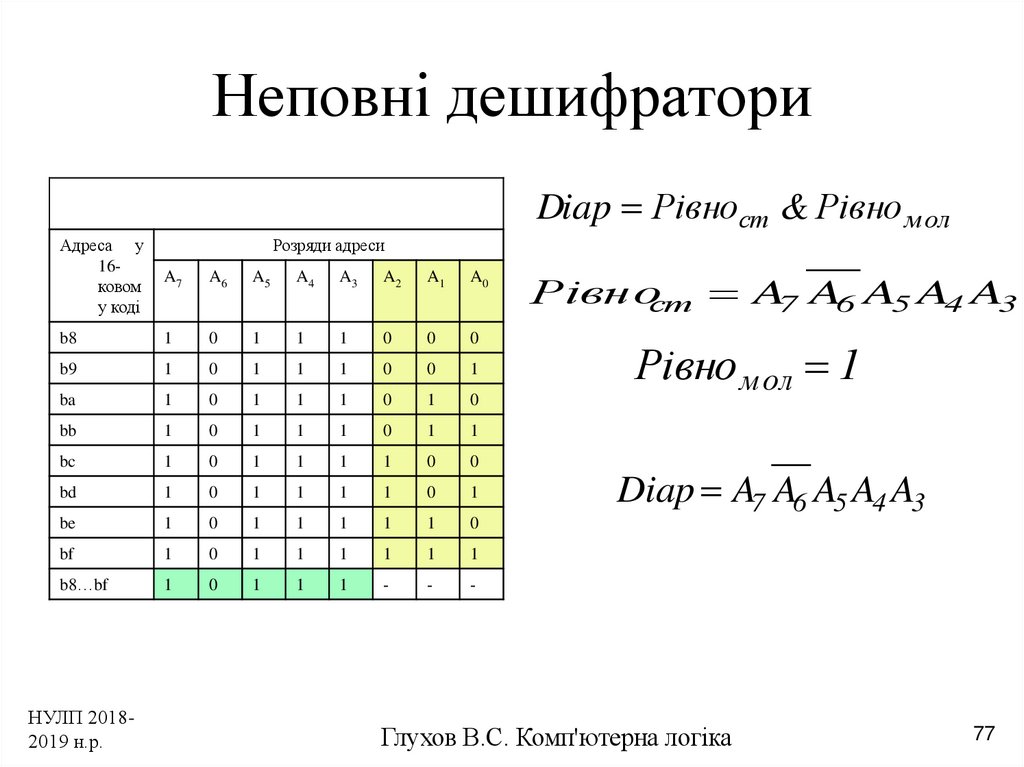

77. Неповні дешифратори

Diap Рівност & Рівно молАдреса у

16ковом

у коді

A7

A6

A5

A4

A3

A2

A1

A0

b8

1

0

1

1

1

0

0

0

b9

1

0

1

1

1

0

0

1

ba

1

0

1

1

1

0

1

0

bb

1

0

1

1

1

0

1

1

bc

1

0

1

1

1

1

0

0

bd

1

0

1

1

1

1

0

1

be

1

0

1

1

1

1

1

0

bf

1

0

1

1

1

1

1

1

b8…bf

1

0

1

1

1

-

-

-

НУЛП 20182019 н.р.

Розряди адреси

Рівн ост A7 A6 A5 A4 A3

Рівно мол 1

Diap A7 A6 A5 A4 A3

Глухов В.С. Комп'ютерна логіка

77

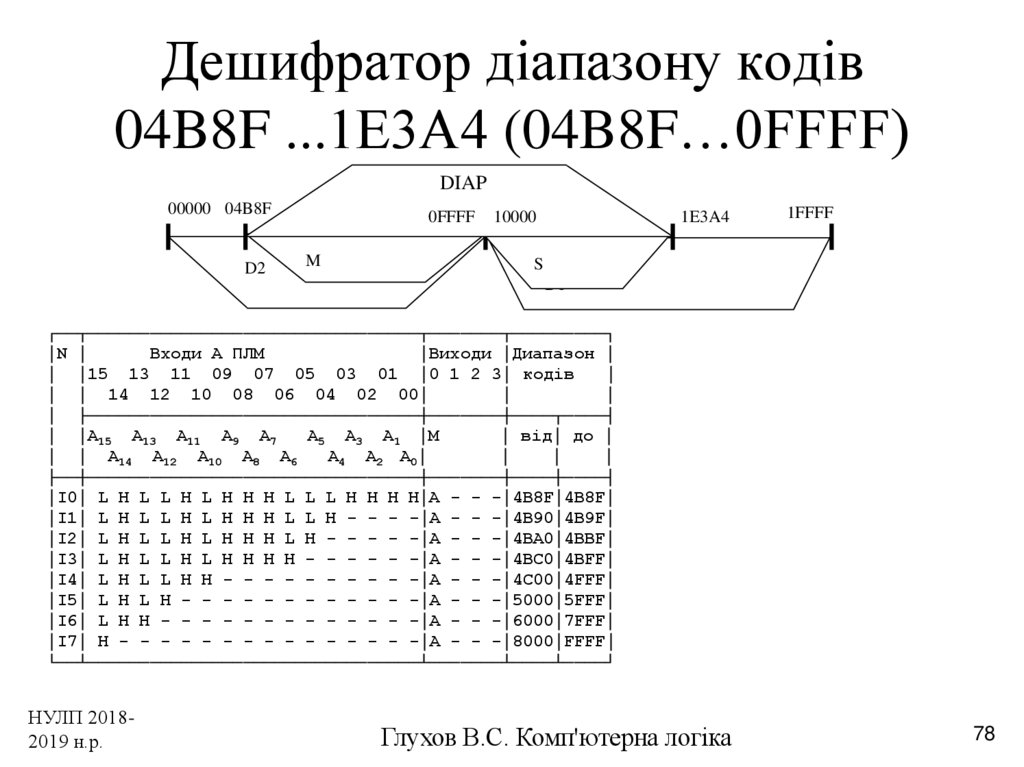

78. Дешифратор діапазону кодів 04B8F ...1Е3А4 (04B8F…0FFFF)

DIAP00000 04B8F

D2

0FFFF

M

10000

1E3A4

1FFFF

S

D1

┌──┬────────────────────────────────┬───────┬─────────┐

│N │

Входи A ПЛМ

│Виходи │Диапазон │

│ │15 13 11 09 07 05 03 01 │0 1 2 3│ кодів

│

│ │ 14 12 10 08 06 04 02 00│

│

│

│ ├────────────────────────────────┼───────┼────┬────┤

│ │A15 A13 A11 A9 A7

A5 A3 A1 │M

│ від│ до │

│ │ A14 A12 A10 A8 A6

A4 A2 A0│

│

│

│

├──┼────────────────────────────────┼───────┼────┼────┤

│I0│ L H L L H L H H H L L L H H H H│A - - -│4B8F│4B8F│

│I1│ L H L L H L H H H L L H - - - -│A - - -│4B90│4B9F│

│I2│ L H L L H L H H H L H - - - - -│A - - -│4BA0│4BBF│

│I3│ L H L L H L H H H H - - - - - -│A - - -│4BC0│4BFF│

│I4│ L H L L H H - - - - - - - - - -│A - - -│4C00│4FFF│

│I5│ L H L H - - - - - - - - - - - -│A - - -│5000│5FFF│

│I6│ L H H - - - - - - - - - - - - -│A - - -│6000│7FFF│

│I7│ H - - - - - - - - - - - - - - -│A - - -│8000│FFFF│

└──┴────────────────────────────────┴───────┴────┴────┘

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

78

79. Дешифратор діапазону кодів 04B8F ...1Е3А4 (10000…1E3A4)

DIAP00000 04B8F

D2

0FFFF

M

10000

1E3A4

1FFFF

S

D1

┌──┬────────────────────────────────┬───────┬─────────┐

│N │

Входи A ПЛМ

│ Виходи│Диапазон │

│ │15 13 11 09 07 05 03 01 │0 1 2 3│ кодів │

│ │ 14 12 10 08 06 04 02 00│

│

│

│ ├────────────────────────────────┼───────┼────┬────┤

│ │A15 A13 A11 A9 A7

A5 A3 A1 │S

│ від│ до │

│ │ A14 A12 A10 A8 A6

A4 A2 A0│

│

│

│

├──┼────────────────────────────────┼───────┼────┼────┤

│I0│ H H H L L L H H H L H L L H L L│A - - -│E3A4│E3A4│

│I1│ H H H L L L H H H L H L L L - -│A - - -│E3A0│E3A3│

│I2│ H H H L L L H H H L L - - - - -│A - - -│E380│E39F│

│I3│ H H H L L L H H L - - - - - - -│A - - -│E300│E37F│

│I4│ H H H L L L H L - - - - - - - -│A - - -│E200│E2FF│

│I5│ H H H L L L L - - - - - - - - -│A - - -│E000│E1FF│

│I6│ H H L - - - - - - - - - - - - -│A - - -│C000│DFFF│

│I7│ H L - - - - - - - - - - - - - -│A - - -│8000│BFFF│

│I8│ L - - - - - - - - - - - - - - -│A - - -│0000│7FFF│

└──┴────────────────────────────────┴───────┴────┴────┘

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

79

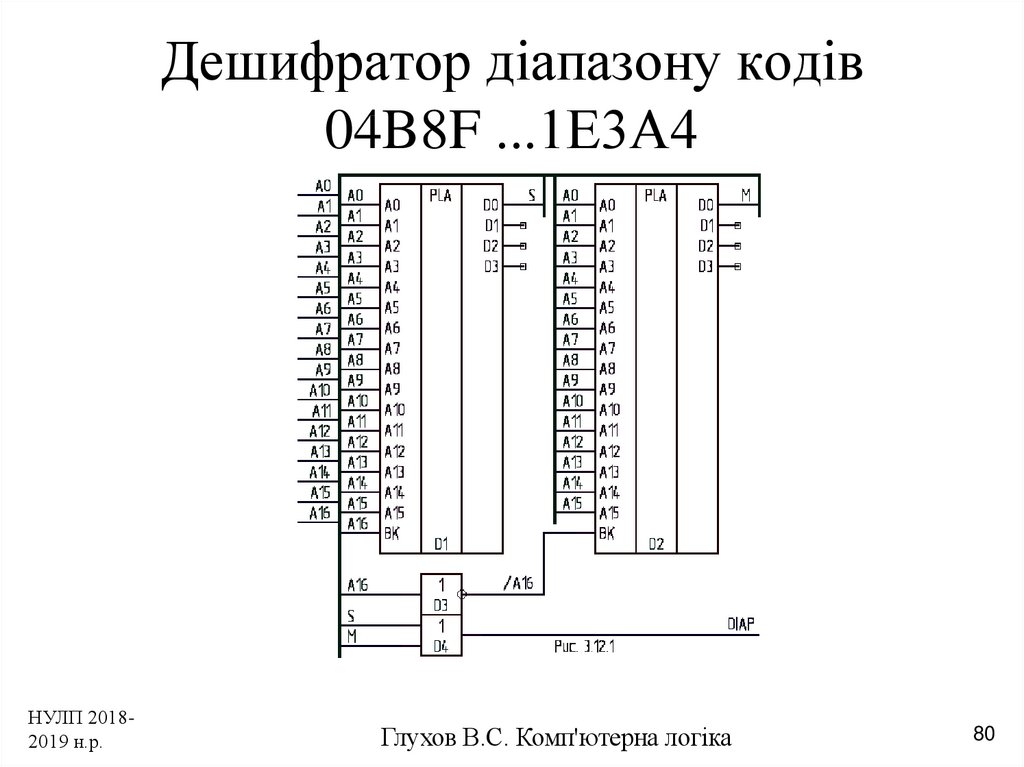

80. Дешифратор діапазону кодів 04B8F ...1Е3А4

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

80

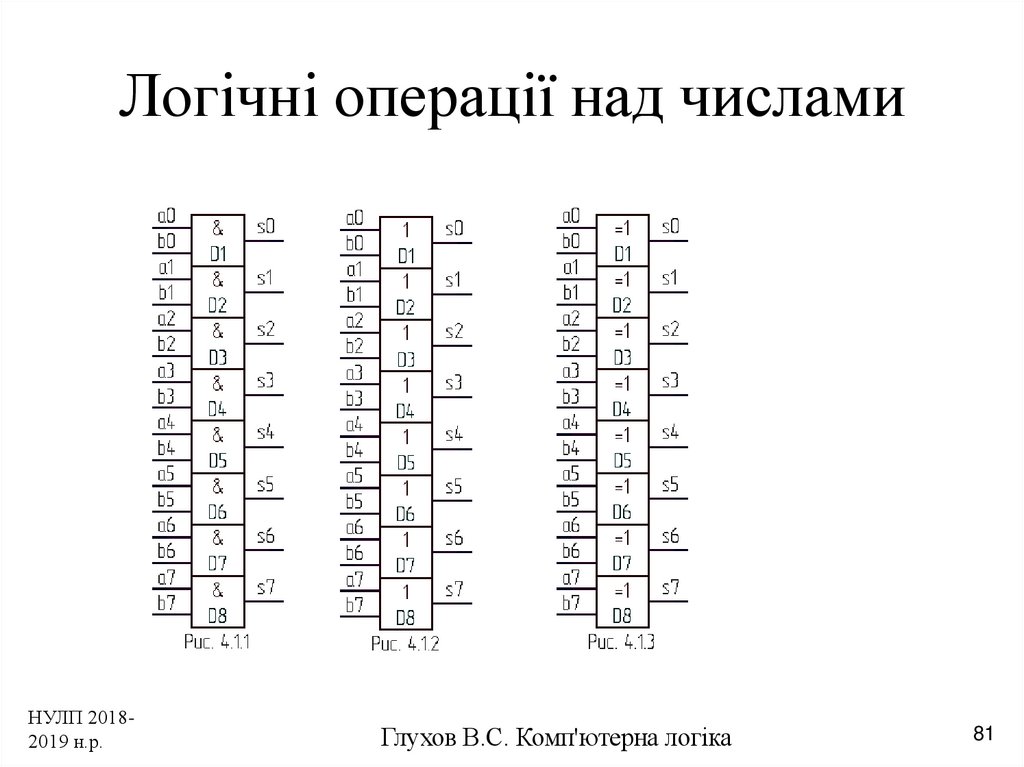

81. Логічні операції над числами

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

81

82. Зсуви

M=6m2 m1

1

1

m3

0

Co=0

m0

0

Ci=1

1

r3

1

0

r2

r1

R=D

1

r0

m3

0

Co=0

m3

0

m0

0

Ci=1

1

r3

Логічний зсув ліворуч

1

0

r2

r1

R=D

1

r0

1

r3

1

0

r2

r1

R=C

m0

0

0

r0

Циклічний зсув ліворуч

Арифметичний зсув ліворуч

m3

0

M=6

m2 m1

1

1

m0

0

1

r3

0

r2

1

r0

Ci=1

1

r1

R=B

M=6

m2 m1

1

1

M=6

m2 m1

1

1

Co=0

Логічний зсув праворуч

m3

0

M=6

m2 m1

1

1

m0

0

0

r3

0

r2

1

r0

1

r1

R=3

m3

0

M=6

m2 m1

1

1

m0

0

0

r3

0

r2

1

r0

Co=0

1

r1

R=3

Циклічний зсув праворуч

Арифметичний зсув праворуч

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

82

83. Двійковий суматор з наскрізним (послідовним) переносом

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

83

84. Суматор-віднімач

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

84

85. Повний однорозрядний двійковий суматор

Co ABC i ABCi ABCi ABCi BC i ACi ABS A BCi ABCi AB Ci ABCi

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

85

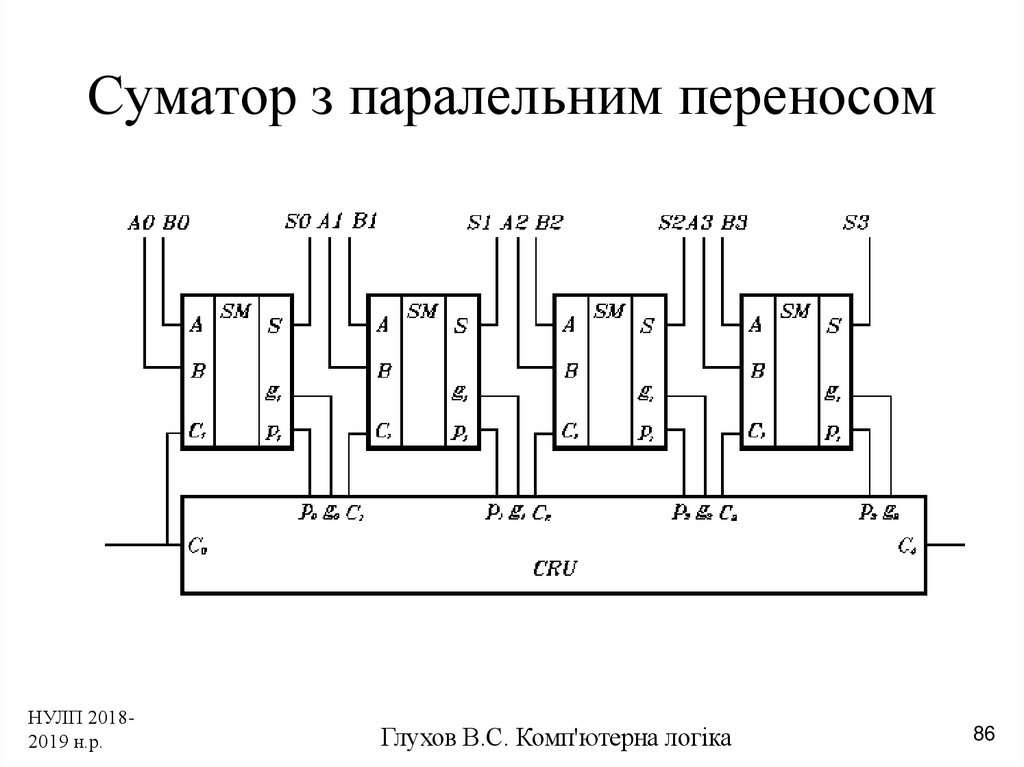

86. Суматор з паралельним переносом

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

86

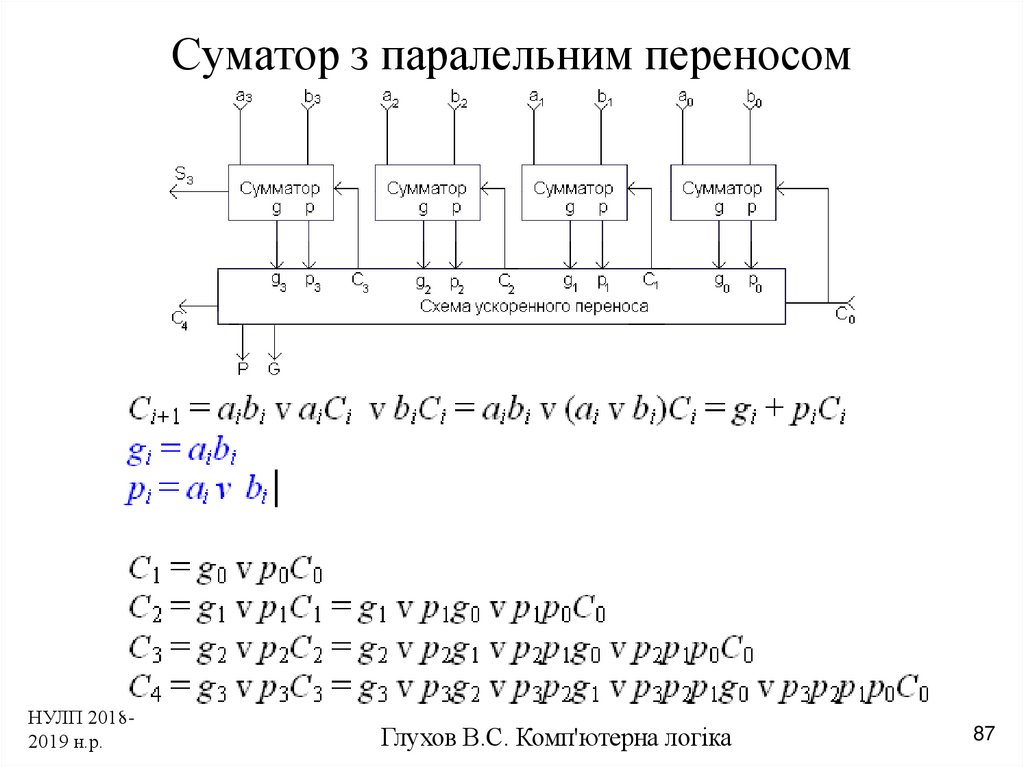

87. Суматор з паралельним переносом

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

87

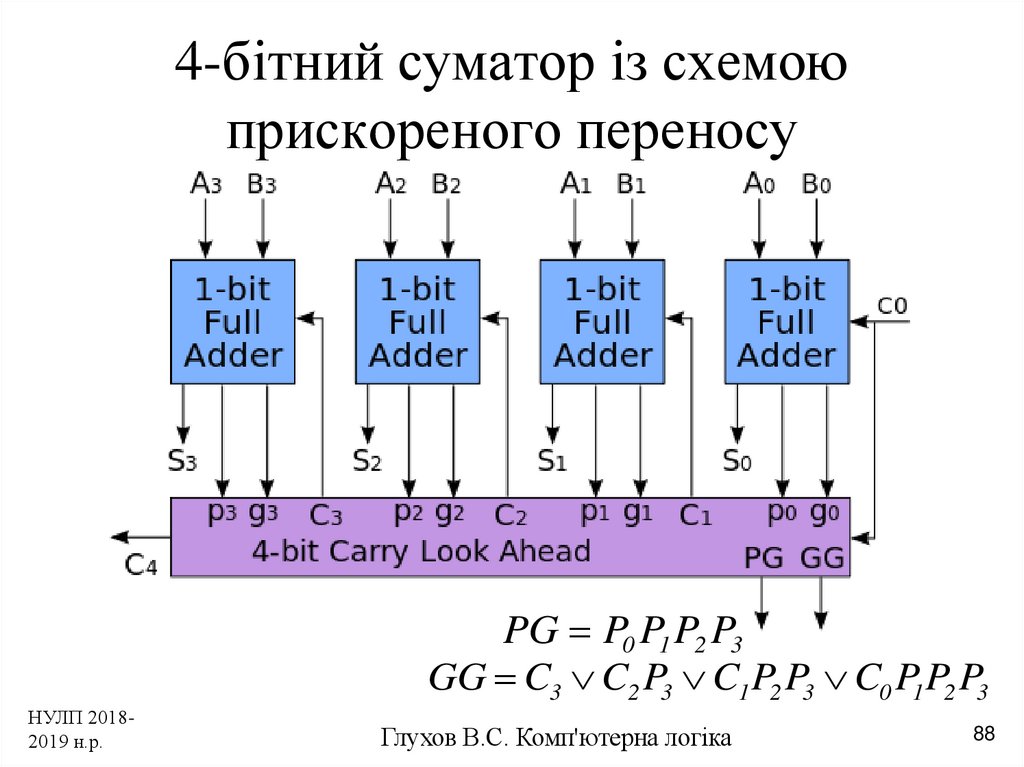

88. 4-бітний суматор із схемою прискореного переносу

PG P0 P1 P2 P3GG C3 C2 P3 C1 P2 P3 C0 P1 P2 P3

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

88

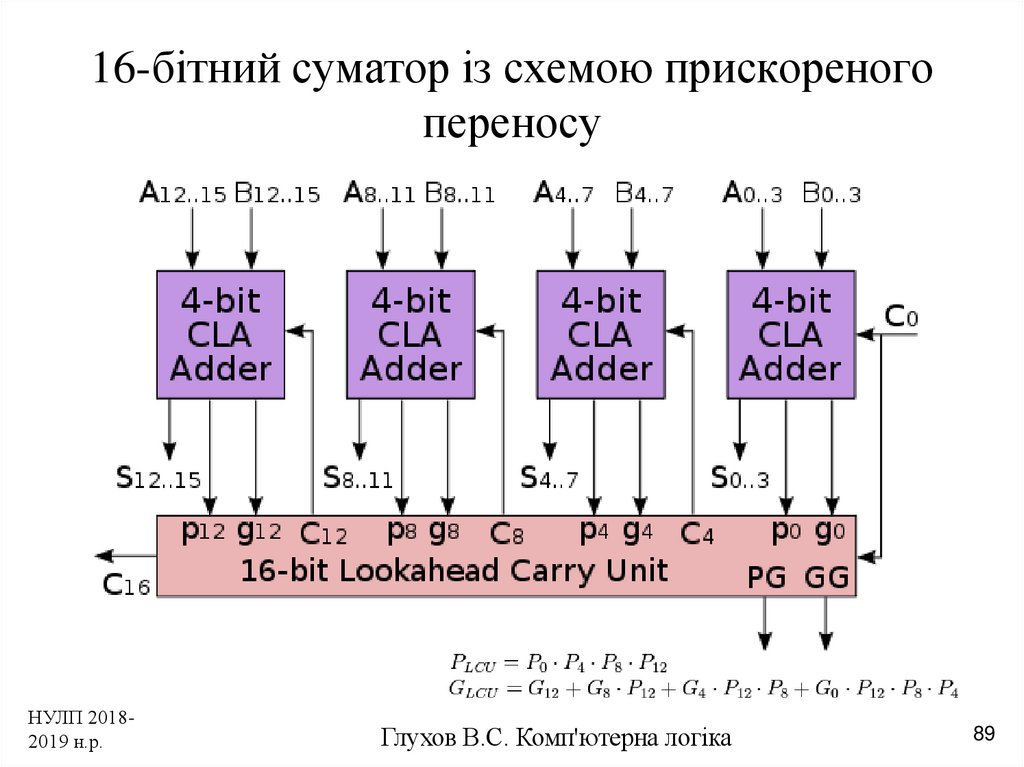

89. 16-бітний суматор із схемою прискореного переносу

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

89

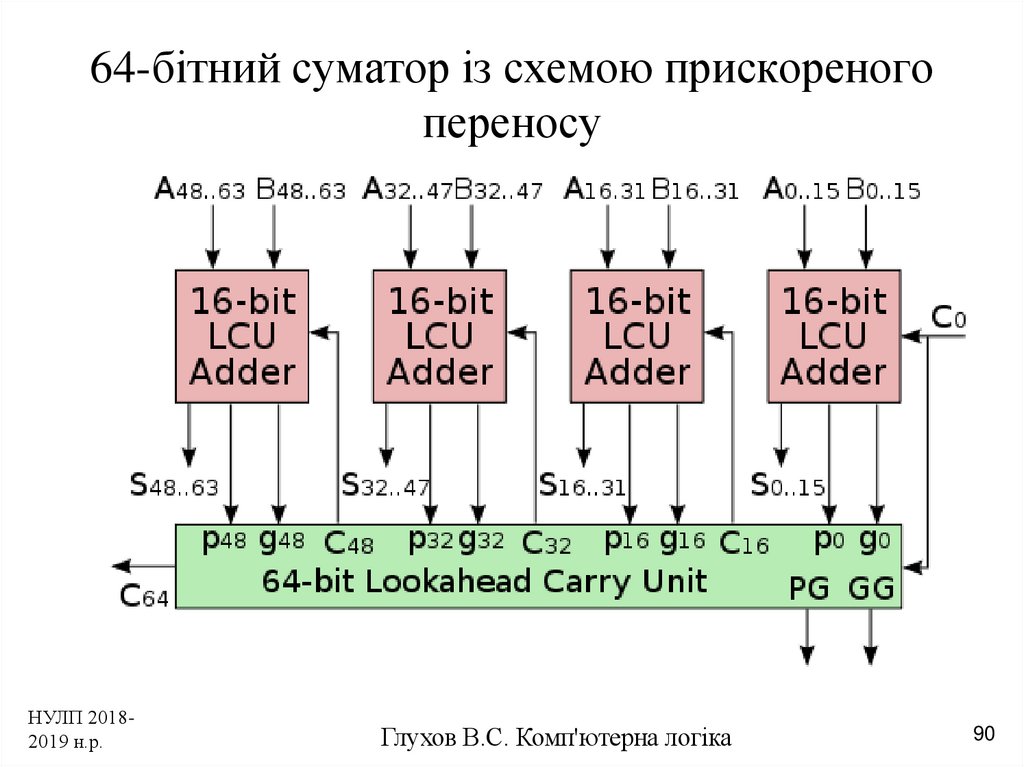

90. 64-бітний суматор із схемою прискореного переносу

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

90

91. Двійкові суматори

• Суматор з паралельним переносом (1 вузолприскорення переносу)

• Суматор з послідовним (наскрізним)

переносом (немає вузлів прискорення

переносу)

• Суматор з груповим переносом (декілька

вузлів прискорення переносу)

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

91

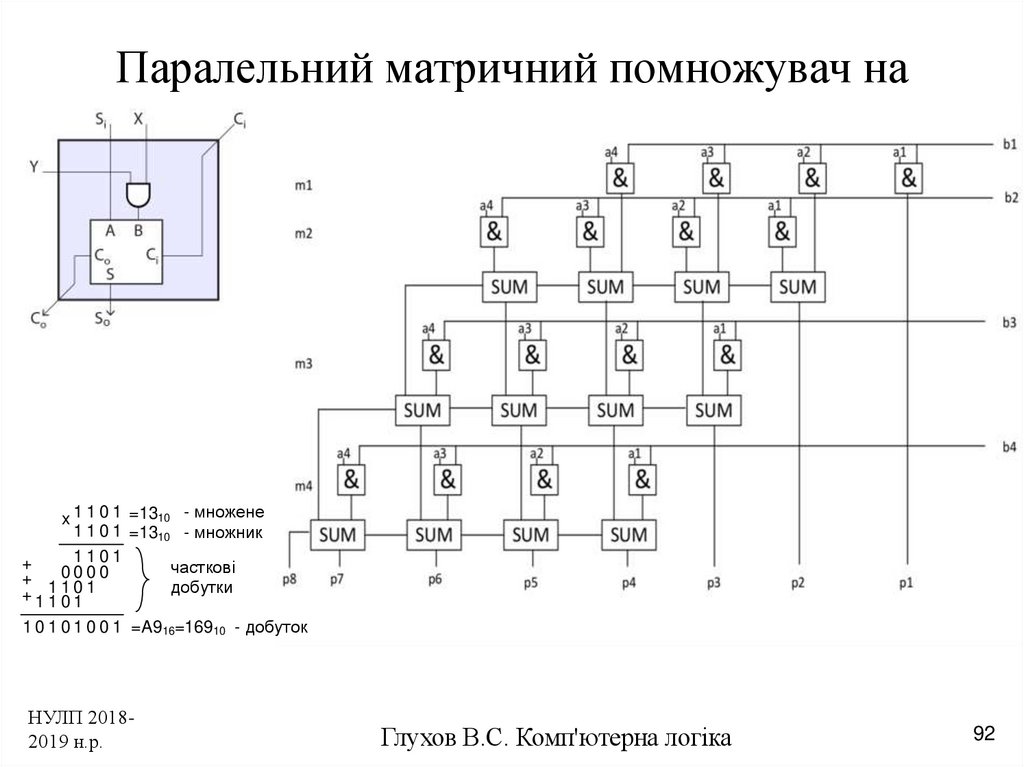

92. Паралельний матричний помножувач на комірках Гілда

x 1 1 0 1 =1310 - множене1 1 0 1 =1310 - множник

1101

+

часткові

0

000

+

101

добутки

+11

101

1 0 1 0 1 0 0 1 =A916=16910 - добуток

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

92

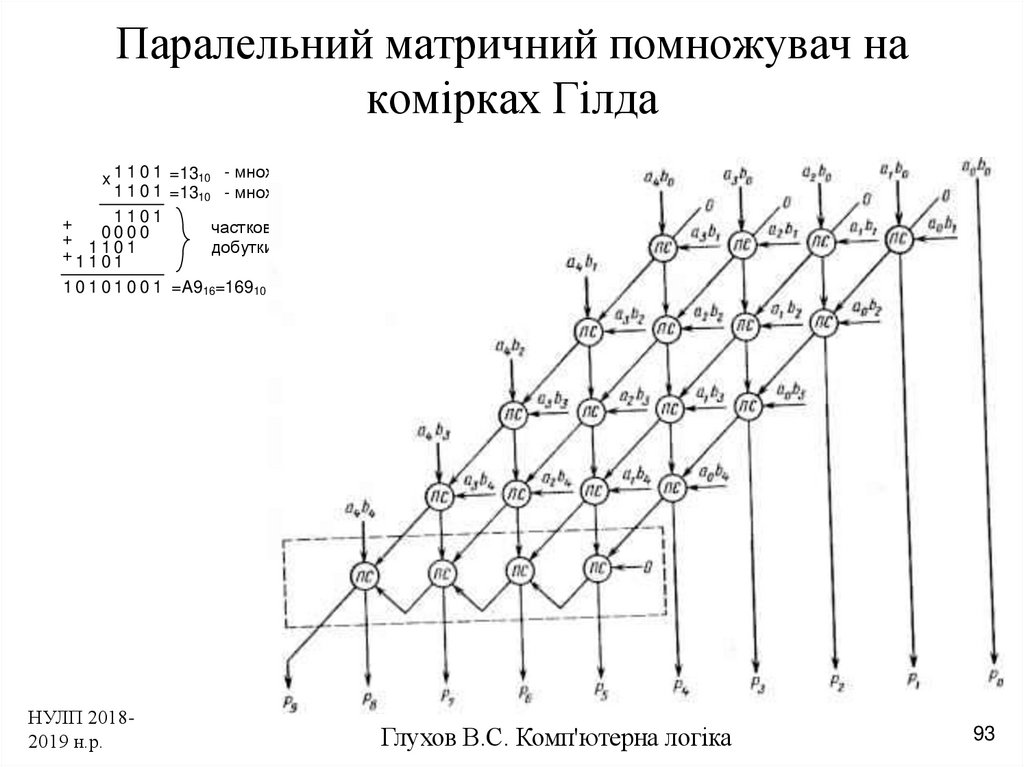

93. Паралельний матричний помножувач на комірках Гілда

x 1 1 0 1 =1310 - множене1 1 0 1 =1310 - множник

1101

+

часткові

0

000

+

1

1

0

1

добутки

+1101

1 0 1 0 1 0 0 1 =A916=16910 - добуток

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

93

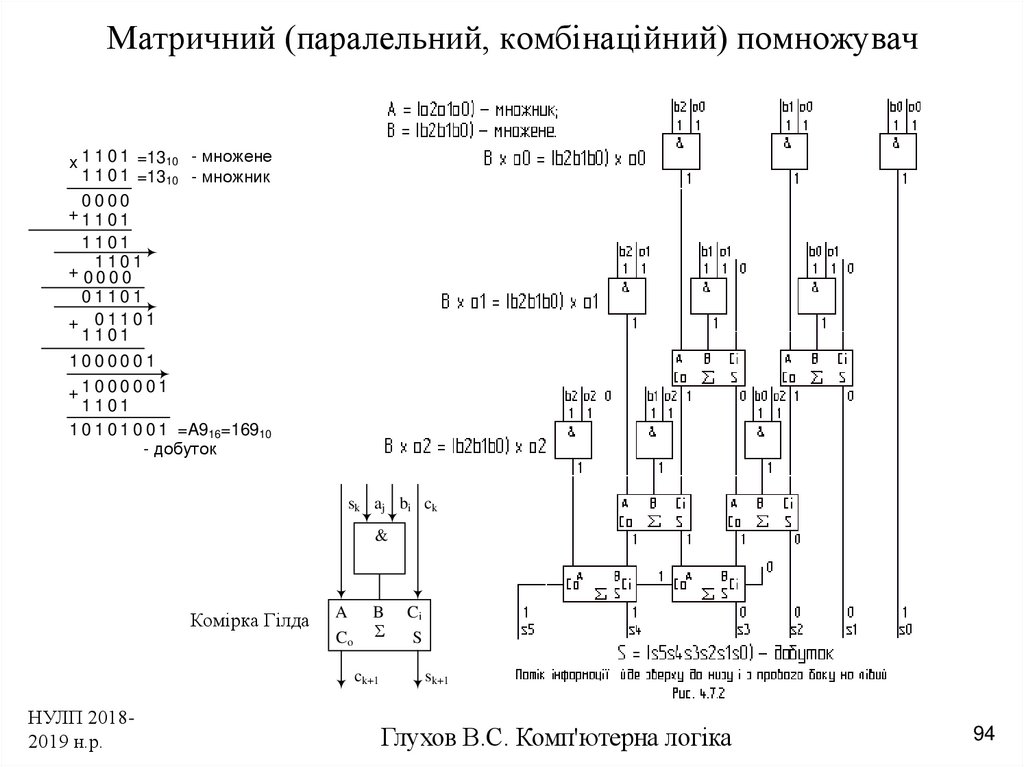

94. Матричний (паралельний, комбінаційний) помножувач

x 1 1 0 1 =1310 - множене1 1 0 1 =1310 - множник

0000

+1101

1101

1101

+ 0000

01101

+ 01101

1101

1000001

+1000001

1101

1 0 1 0 1 0 0 1 =A916=16910

- добуток

sk aj bi ck

&

Комірка Гілда

A

Co

B

Σ

ck+1

НУЛП 20182019 н.р.

Ci

S

sk+1

Глухов В.С. Комп'ютерна логіка

94

95. Арифметико-логічний пристрій

AB

A

B

Fмл

F

MUX

AU

R

LU

A

A

B

R

B

Fмл

F

A

Fмл

A

B

Fмл

Fст

НУЛП 20182019 н.р.

A

Ra

Rл

0

A

B

F

A

B

F

ALU

R

R

1

R

ShU

R

Rз

2

F

Reserve

A

R

B

F

Код операції -КОП

Rр

3

Sel

Fст

00 - арифметичні

01 - логічні

10 - зсуви

11 - резерв

Глухов В.С. Комп'ютерна логіка

Fмл

95

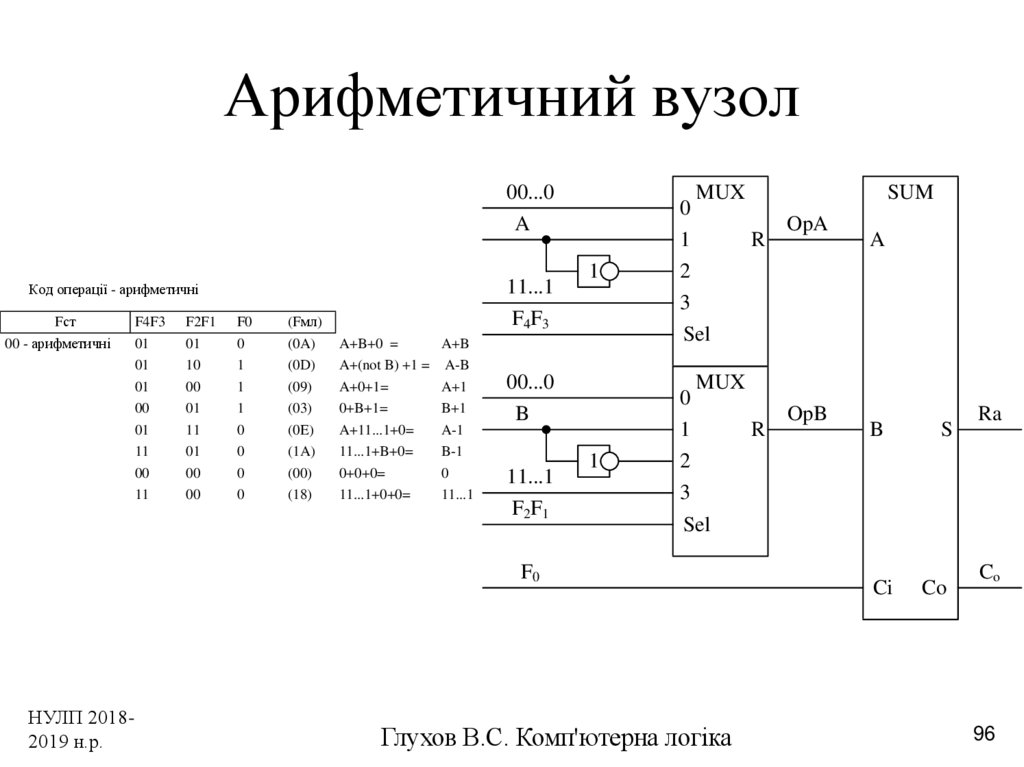

96. Арифметичний вузол

00...0A

11...1

F4F3

Код операції - арифметичні

Fст

00 - арифметичні

F4F3

01

01

01

00

01

11

00

11

F2F1

01

10

00

01

11

01

00

00

F0

0

1

1

1

0

0

0

0

(Fмл)

(0A)

(0D)

(09)

(03)

(0E)

(1A)

(00)

(18)

A+B+0 =

A+(not B) +1 =

A+0+1=

0+B+1=

A+11...1+0=

11...1+B+0=

0+0+0=

11...1+0+0=

A+B

A-B

A+1

B+1

A-1

B-1

0

11...1

1

MUX

0

1

R

2

3

Sel

1

MUX

0

1

R

2

3

Sel

00...0

B

11...1

F2F1

F0

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

SUM

OpA

OpB

A

B

Ci

S

Co

Ra

Co

96

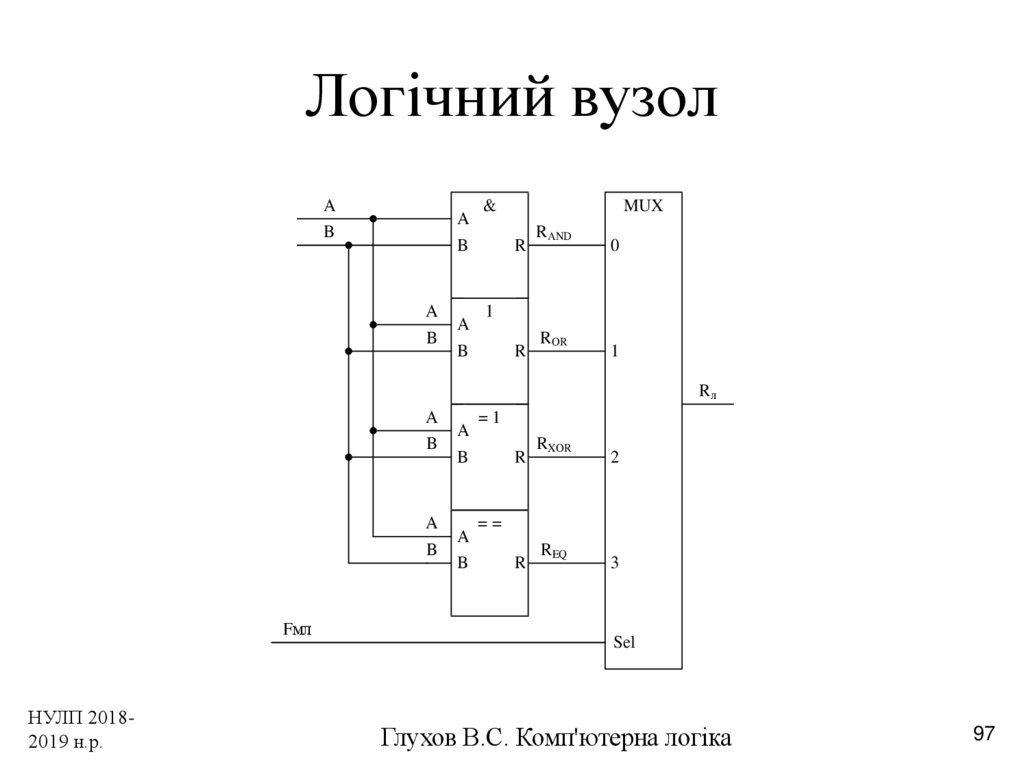

97. Логічний вузол

AB

A

B

A

B

A

B

MUX

&

R

RAND

0

1

R

ROR

1

Rл

A

B

A

B

Fмл

НУЛП 20182019 н.р.

A

B

A

B

=1

R

RXOR

2

==

R

REQ

3

Sel

Глухов В.С. Комп'ютерна логіка

97

98. Вузол зсувів

AA

A

A

A

A

A

LSL

RL

ASL

LSR

RR

ASR

R

0

R

1

R

2

R

3

R

4

R

5

MUX

Rз

6

7

Fмл

НУЛП 20182019 н.р.

Sel

Глухов В.С. Комп'ютерна логіка

98

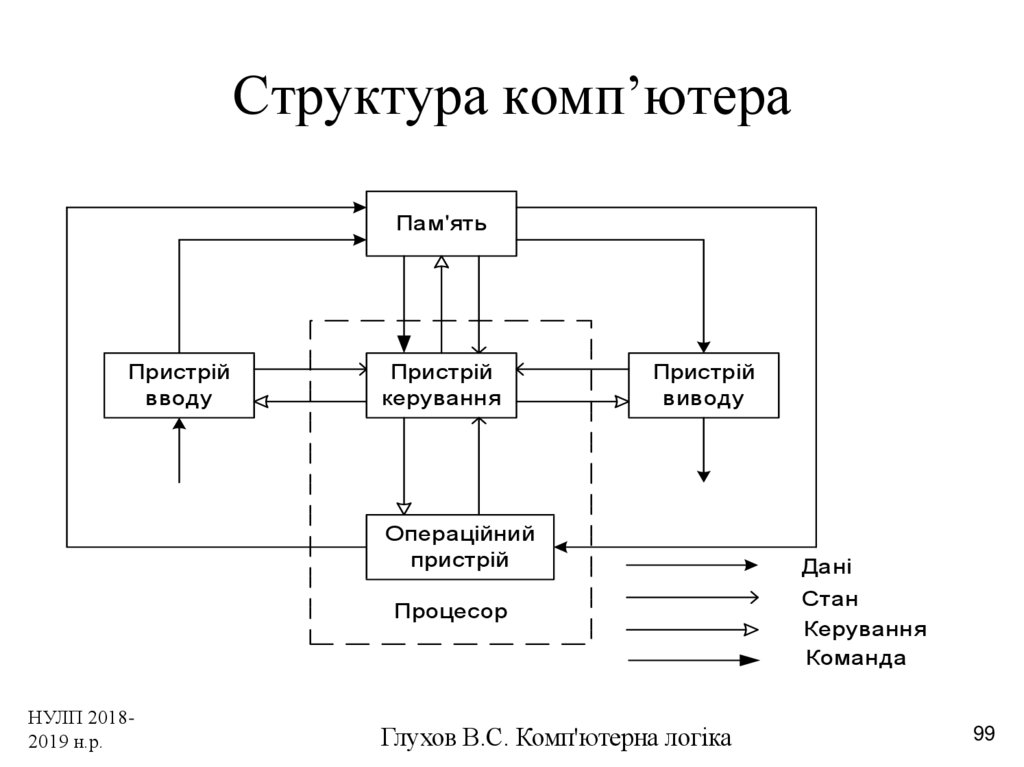

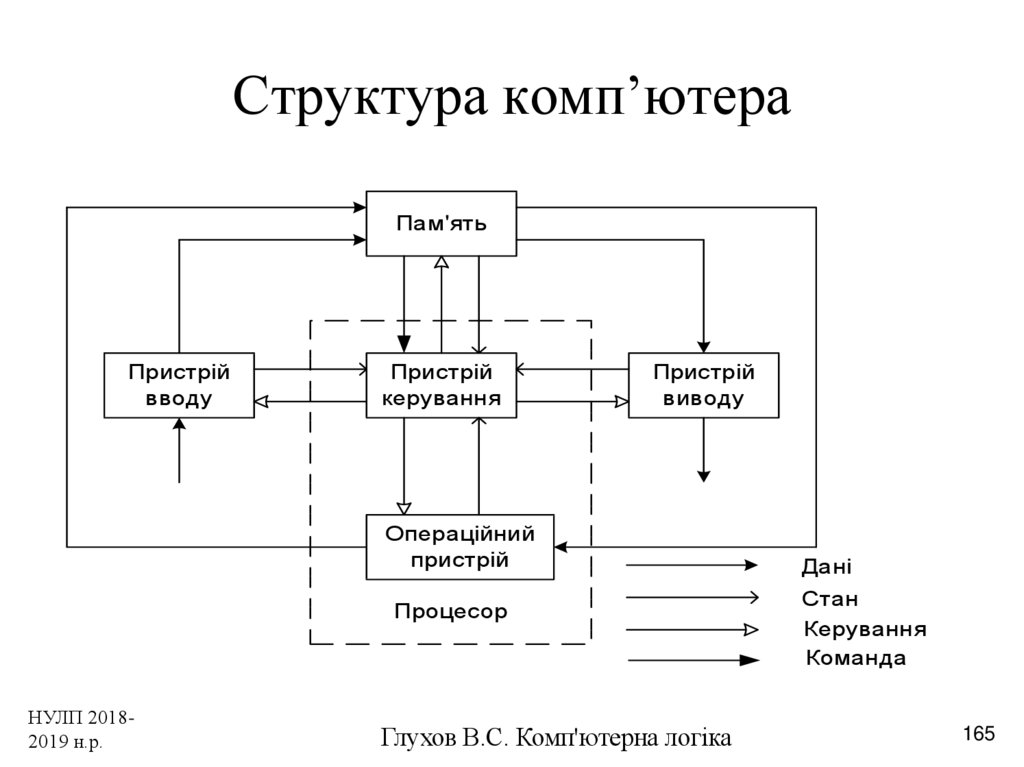

99. Структура комп’ютера

Пам'ятьПристрій

вводу

Пристрій

керування

Пристрій

виводу

Операційний

пристрій

Процесор

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

Дані

Стан

Керування

Команда

99

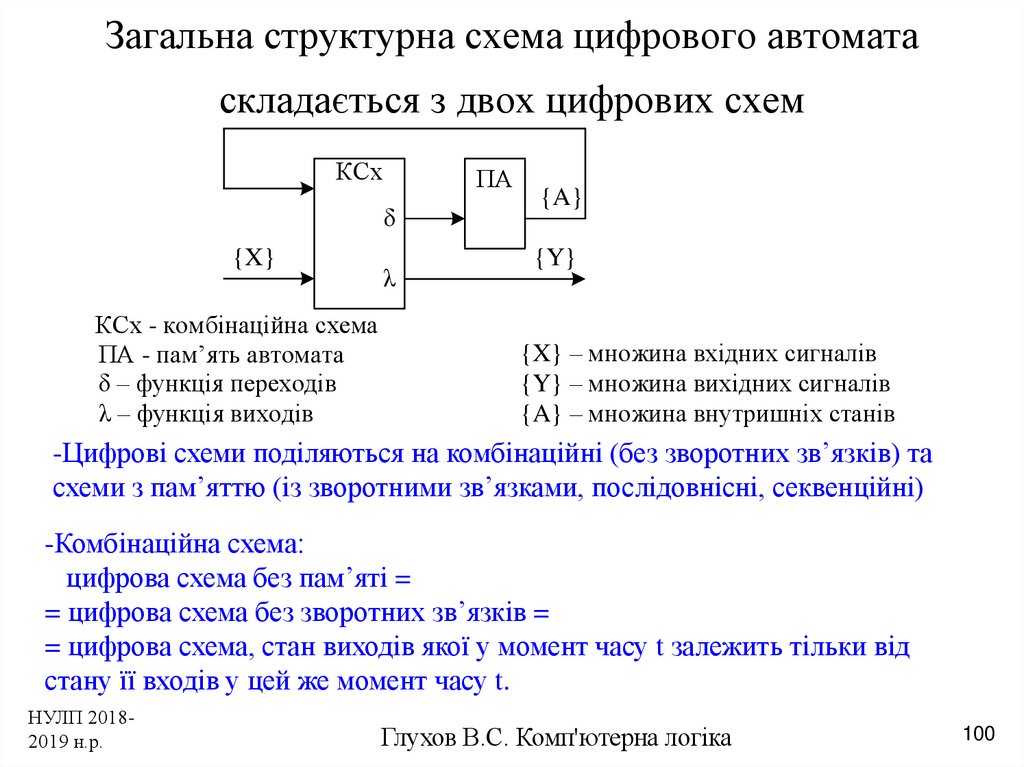

100. Загальна структурна схема цифрового автомата складається з двох цифрових схем

КСхПА

δ

{X}

КСх - комбінаційна схема

ПА - пам’ять автомата

δ – функція переходів

λ – функція виходів

λ

{A}

{Y}

{X} – множина вхідних сигналів

{Y} – множина вихідних сигналів

{A} – множина внутришніх станів

-Цифрові схеми поділяються на комбінаційні (без зворотних зв’язків) та

схеми з пам’яттю (із зворотними зв’язками, послідовнісні, секвенційні)

-Комбінаційна схема:

цифрова схема без пам’яті =

= цифрова схема без зворотних зв’язків =

= цифрова схема, стан виходів якої у момент часу t залежить тільки від

стану її входів у цей же момент часу t.

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

100

101. Структурна схема автомата Мура

iКСх

ПА

δ

{X} j

i

{A}

КСх

λ

1

КСх - комбінаційна схема

ПА - пам’ять автомата

δ – функція переходів

λ – функція виходів

j – кількість вхідних сигналів

k – кількість вихідних сигналів

НУЛП 20182019 н.р.

k

{Y}

2

{X} – множина вхідних сигналів

{Y} – множина вихідних сигналів

{A} – множина внутришніх станів

i – розрядність зворотного зв’язку,

кількість тригерів у пам’яті

автомата

Глухов В.С. Комп'ютерна логіка

101

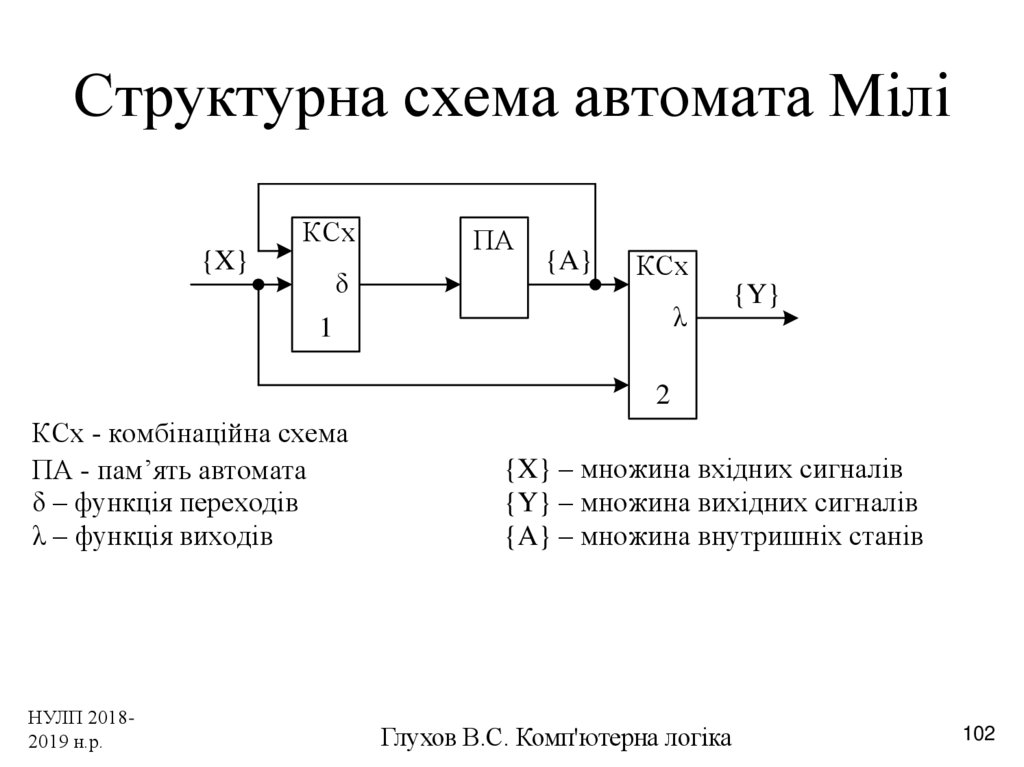

102. Структурна схема автомата Мілі

КСх{X}

δ

ПА

{A}

КСх

λ

1

{Y}

2

КСх - комбінаційна схема

ПА - пам’ять автомата

δ – функція переходів

λ – функція виходів

НУЛП 20182019 н.р.

{X} – множина вхідних сигналів

{Y} – множина вихідних сигналів

{A} – множина внутришніх станів

Глухов В.С. Комп'ютерна логіка

102

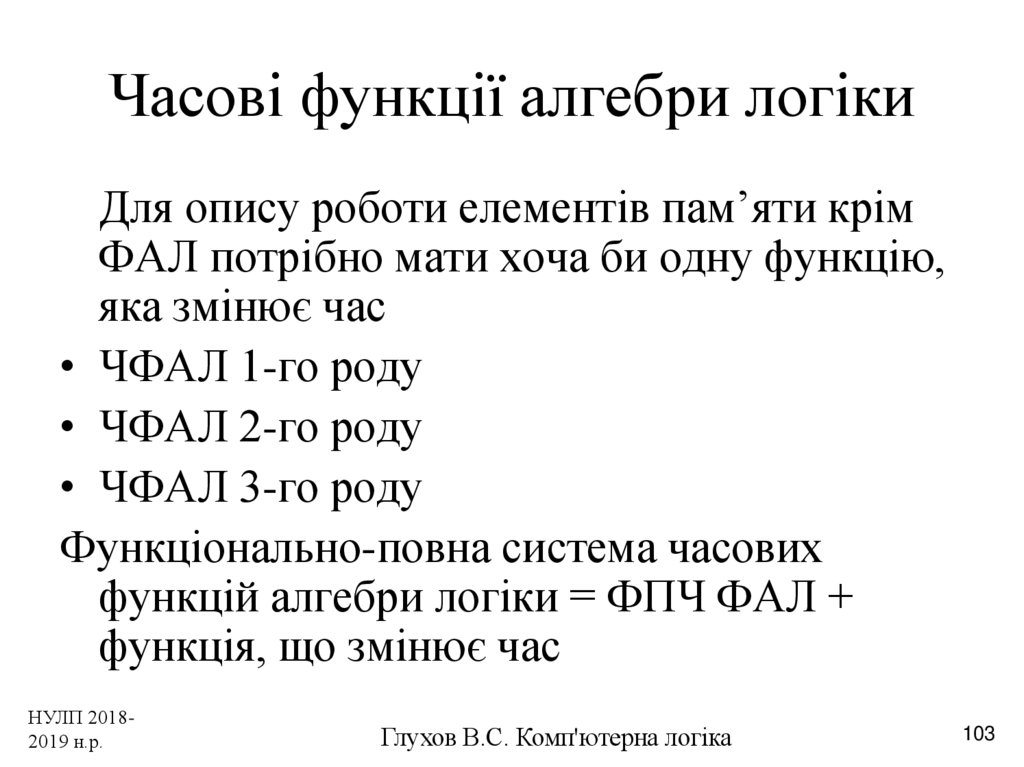

103. Часові функції алгебри логіки

Для опису роботи елементів пам’яти крімФАЛ потрібно мати хоча би одну функцію,

яка змінює час

• ЧФАЛ 1-го роду

• ЧФАЛ 2-го роду

• ЧФАЛ 3-го роду

Функціонально-повна система часових

функцій алгебри логіки = ФПЧ ФАЛ +

функція, що змінює час

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

103

104. Елемент затримки

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

104

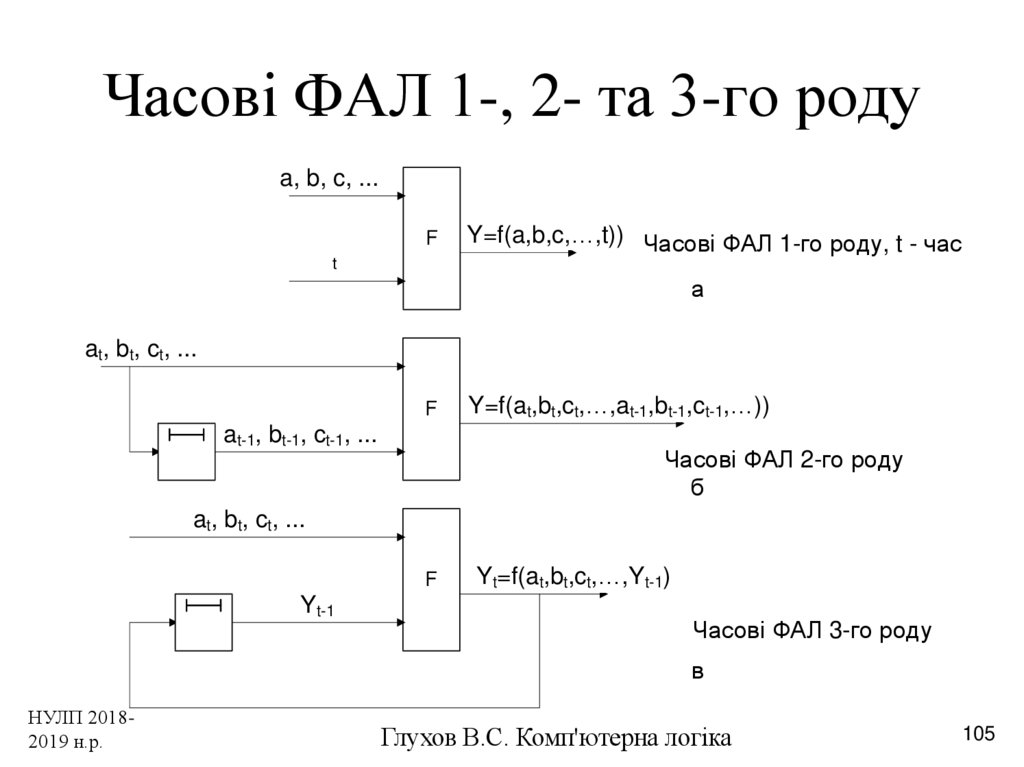

105. Часові ФАЛ 1-, 2- та 3-го роду

a, b, c, ...F

Y=f(a,b,c,…,t)) Часові ФАЛ 1-го роду, t - час

t

а

at, bt, ct, ...

F

at-1, bt-1, ct-1, ...

Y=f(at,bt,ct,…,at-1,bt-1,ct-1,…))

Часові ФАЛ 2-го роду

б

at, bt, ct, ...

F

Yt-1

Yt=f(at,bt,ct,…,Yt-1)

Часові ФАЛ 3-го роду

в

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

105

106. Часова функція 3-го роду Зворотній зв’язок (техн) Змія, що кусає себе за хвіст – Уроборос (філ.)

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

106

107. Загальна схема тригера (trigger, flip-flop, latch)

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

107

108. Тригер та генератор

• Тригер – логічний елемент, що може знаходитися у двох сталихстанах та переходити з одного стану в інший під дією зовнішніх

сигналів = елемент пам’яті для збереження 1 біта.

• Генератор - логічний елемент, що може знаходитися у двох

станах та переходити з одного стану в інший без дії зовнішніх

сигналів

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

108

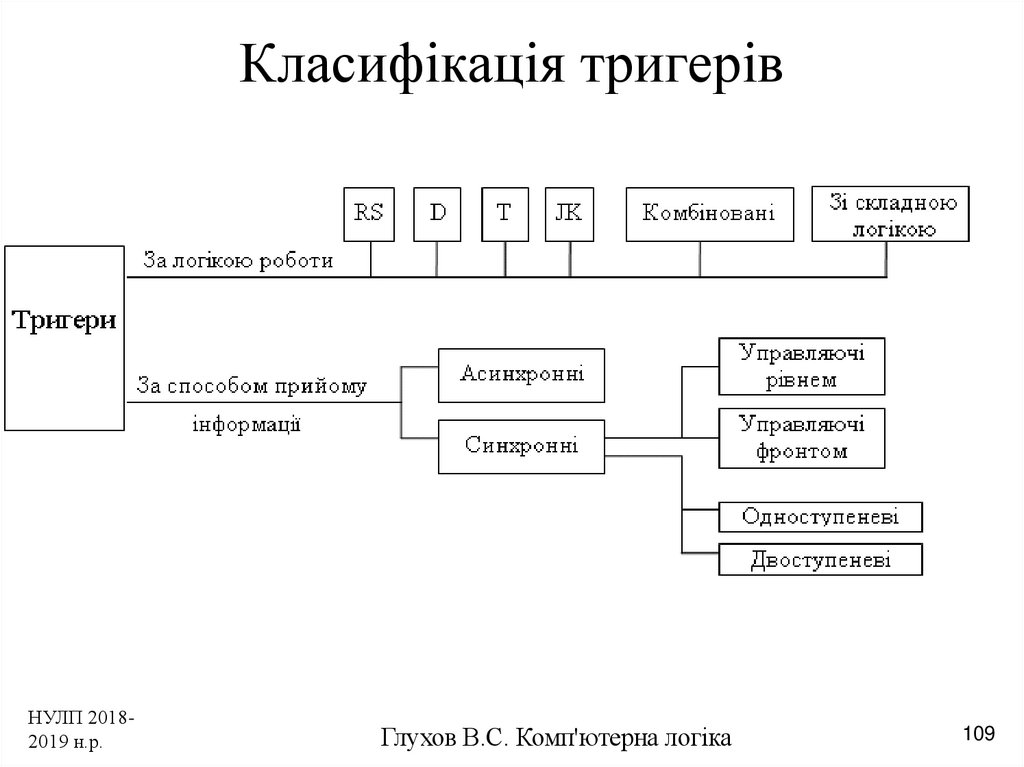

109. Класифікація тригерів

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

109

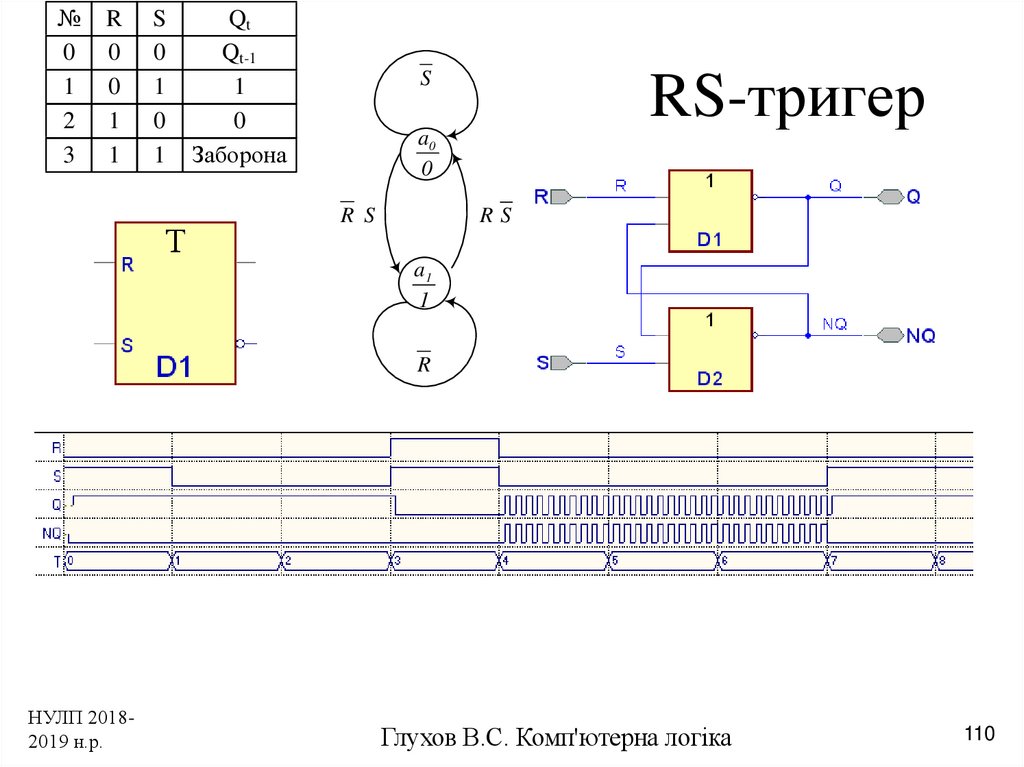

110. RS-тригер

№0

1

2

3

R

0

0

1

1

S

0

1

0

1

Qt

Qt-1

1

0

Заборона

S

RS-тригер

a0

0

R S

RS

a1

1

R

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

110

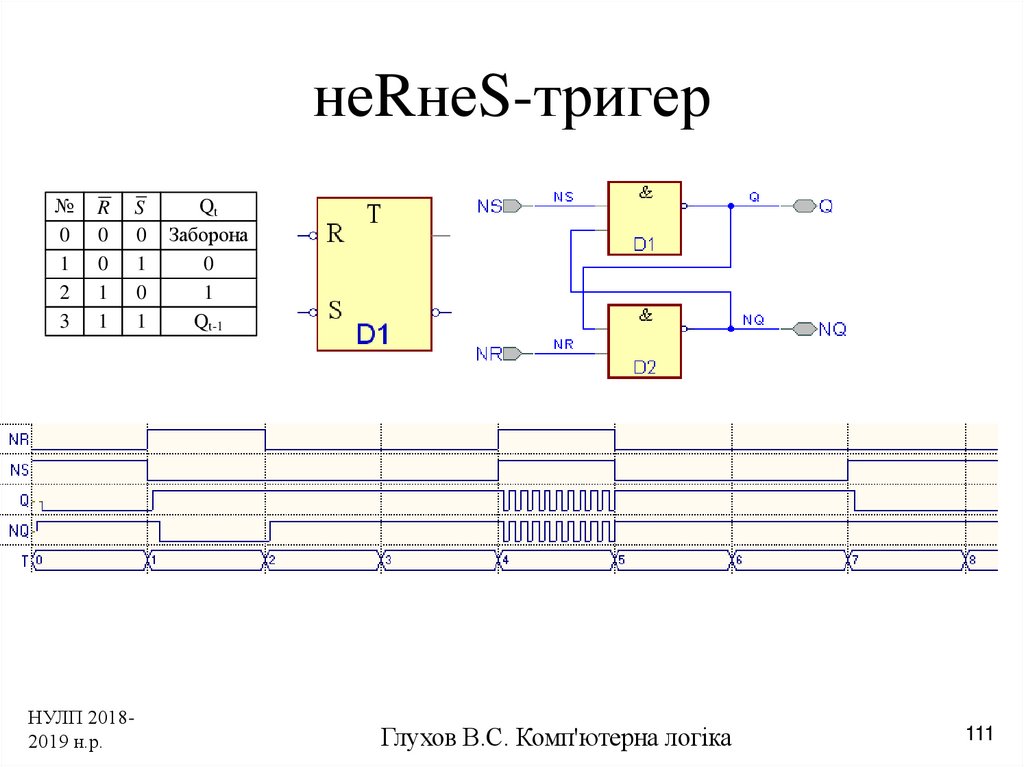

111. неRнеS-тригер

№0

1

2

3

R

0

0

1

1

S

0

1

0

1

НУЛП 20182019 н.р.

Qt

Заборона

0

1

Qt-1

Глухов В.С. Комп'ютерна логіка

111

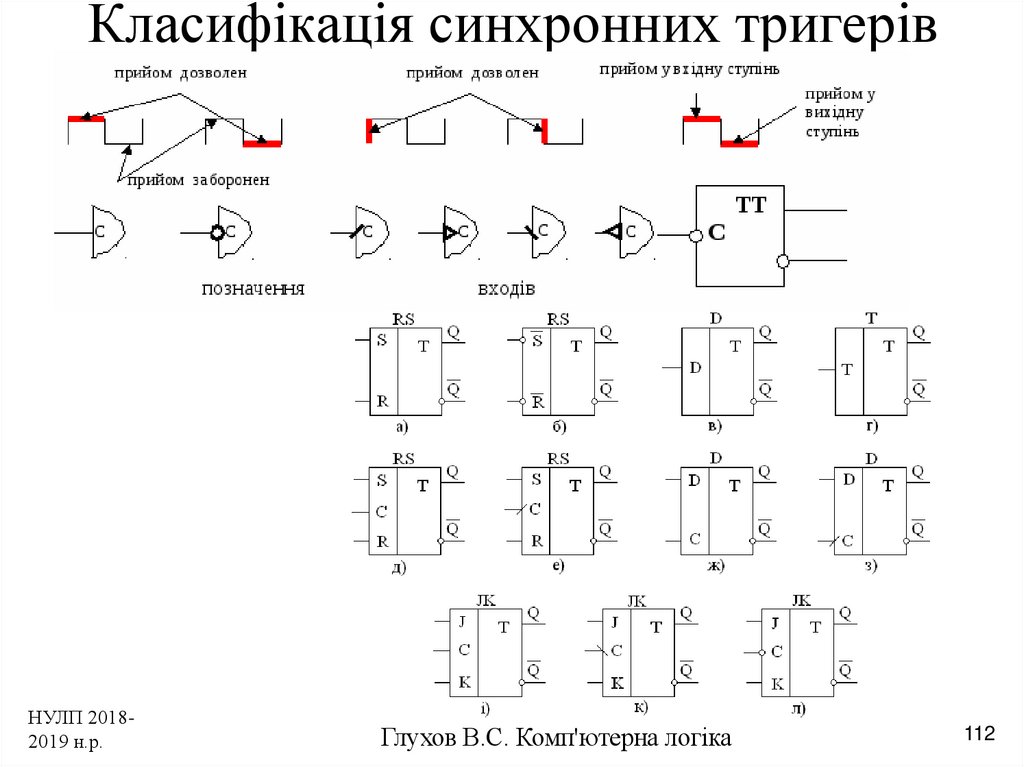

112. Класифікація синхронних тригерів

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

112

113. Синхронний RS-тригер

Sa0

0

R S

RS

a1

1

R

Будь-який перехід на цьому графі

здійснюється при виконанні

додаткової

умови

С=1.

Наприклад, запис

R S

треба розуміти як

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

R SC

113

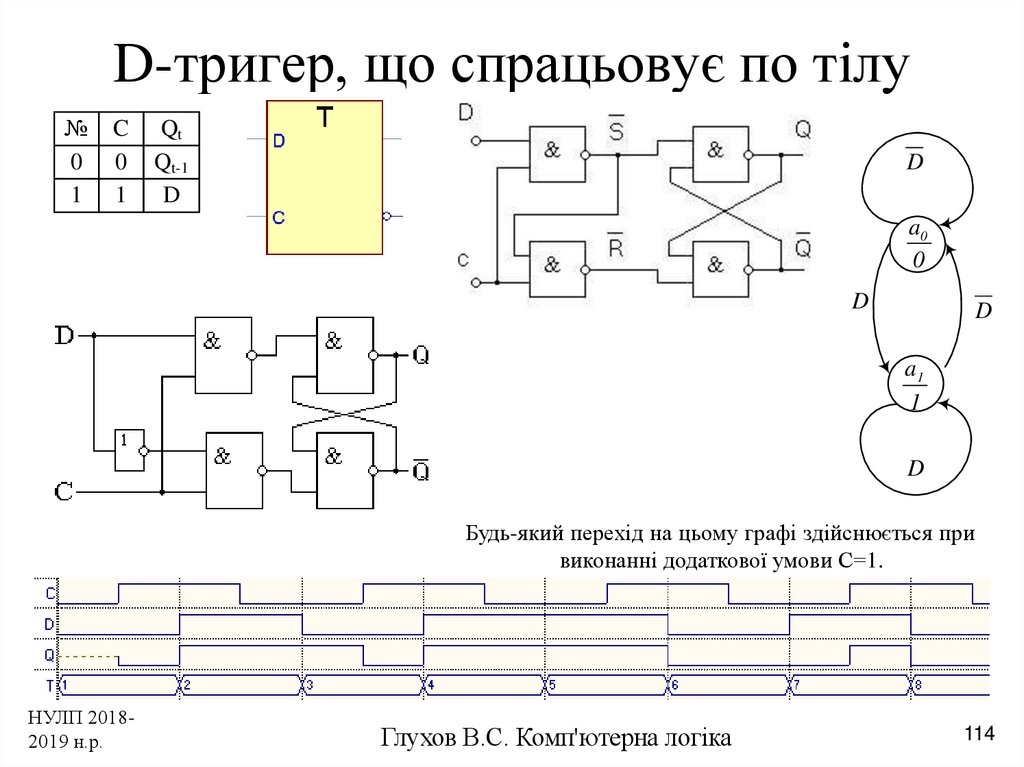

114. D-тригер, що спрацьовує по тілу

№0

1

C

0

1

Qt

Qt-1

D

D

a0

0

D

D

a1

1

D

Будь-який перехід на цьому графі здійснюється при

виконанні додаткової умови С=1.

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

114

115. D-тригер, що спрацьовує по фронту

№0

1

2

3

C

0

1

Qt

Qt-1

Qt-1

Qt-1

D

D

Будь-який перехід на цьому графі

здійснюється при виконанні

додаткової умови “є фронт

зростання на вході С”.

a0

0

D

D

a1

1

D

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

115

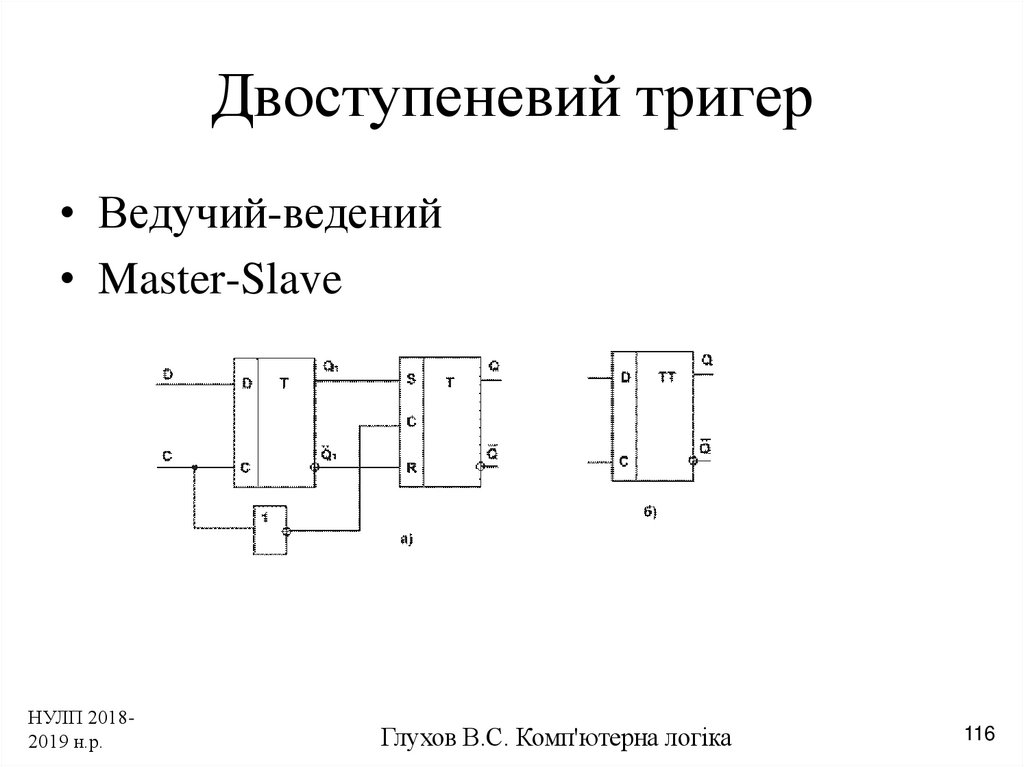

116. Двоступеневий тригер

• Ведучий-ведений• Master-Slave

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

116

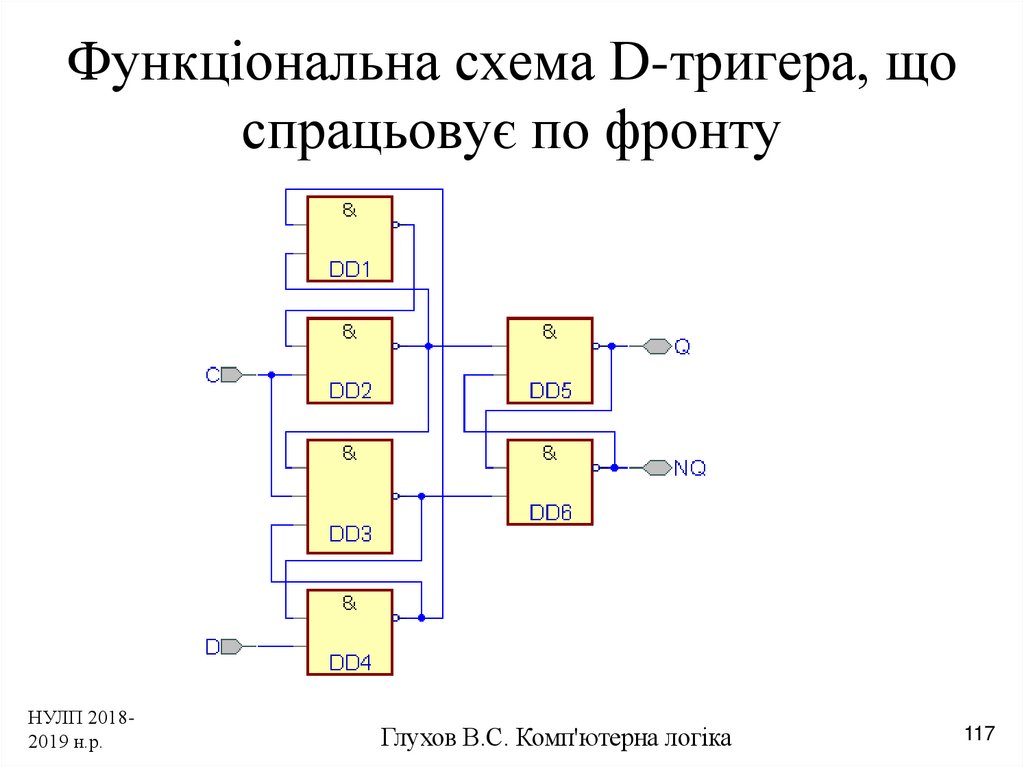

117. Функціональна схема D-тригера, що спрацьовує по фронту

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

117

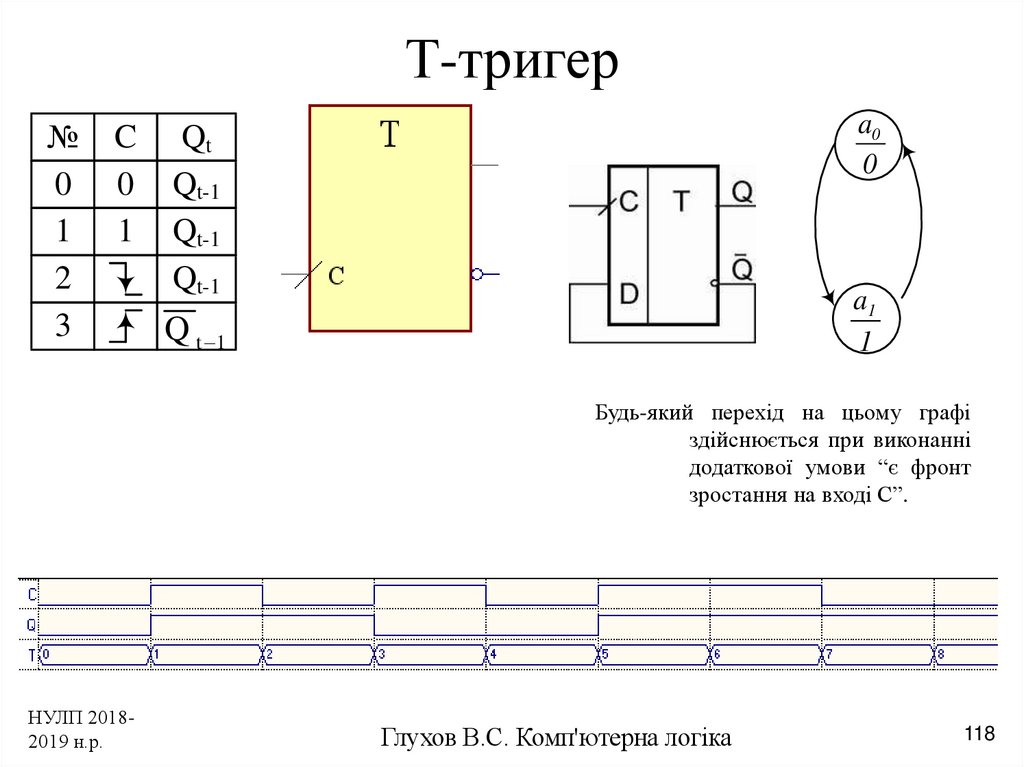

118. Т-тригер

№0

1

2

3

C

0

1

a0

0

Qt

Qt-1

Qt-1

Qt-1

a1

1

Q t 1

Будь-який перехід на цьому графі

здійснюється при виконанні

додаткової умови “є фронт

зростання на вході С”.

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

118

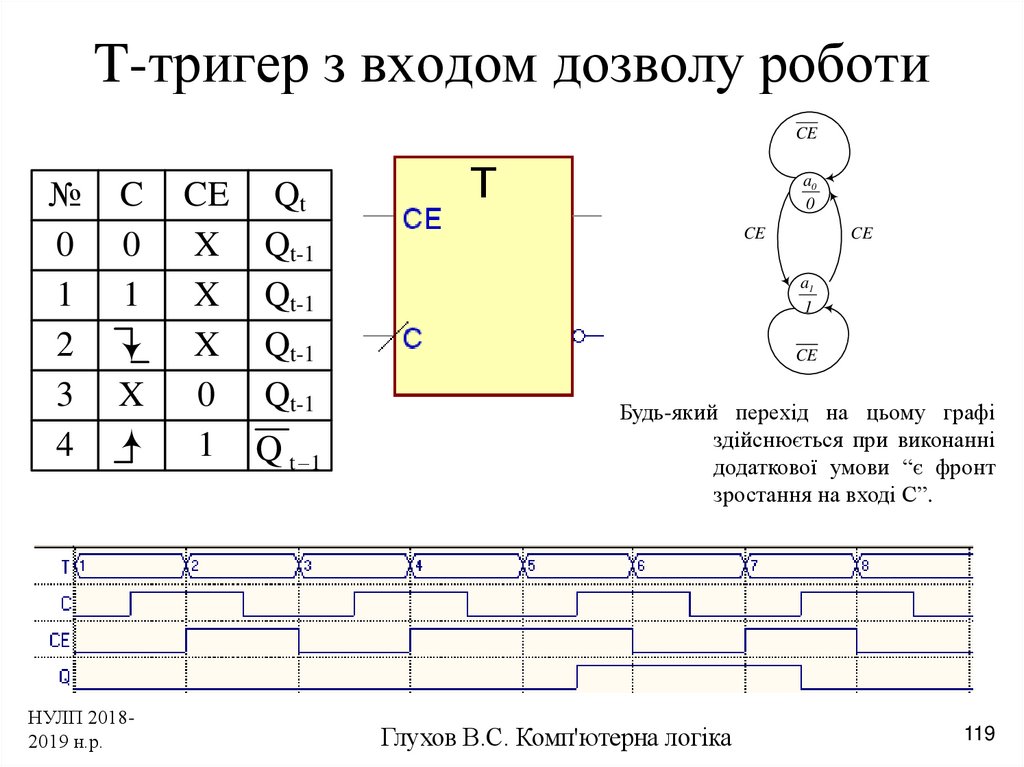

119. T-тригер з входом дозволу роботи

CE№

0

1

2

3

4

C

0

1

X

НУЛП 20182019 н.р.

CE

X

X

X

0

1

Qt

Qt-1

Qt-1

Qt-1

Qt-1

Q t 1

a0

0

CE

CE

a1

1

CE

Будь-який перехід на цьому графі

здійснюється при виконанні

додаткової умови “є фронт

зростання на вході С”.

Глухов В.С. Комп'ютерна логіка

119

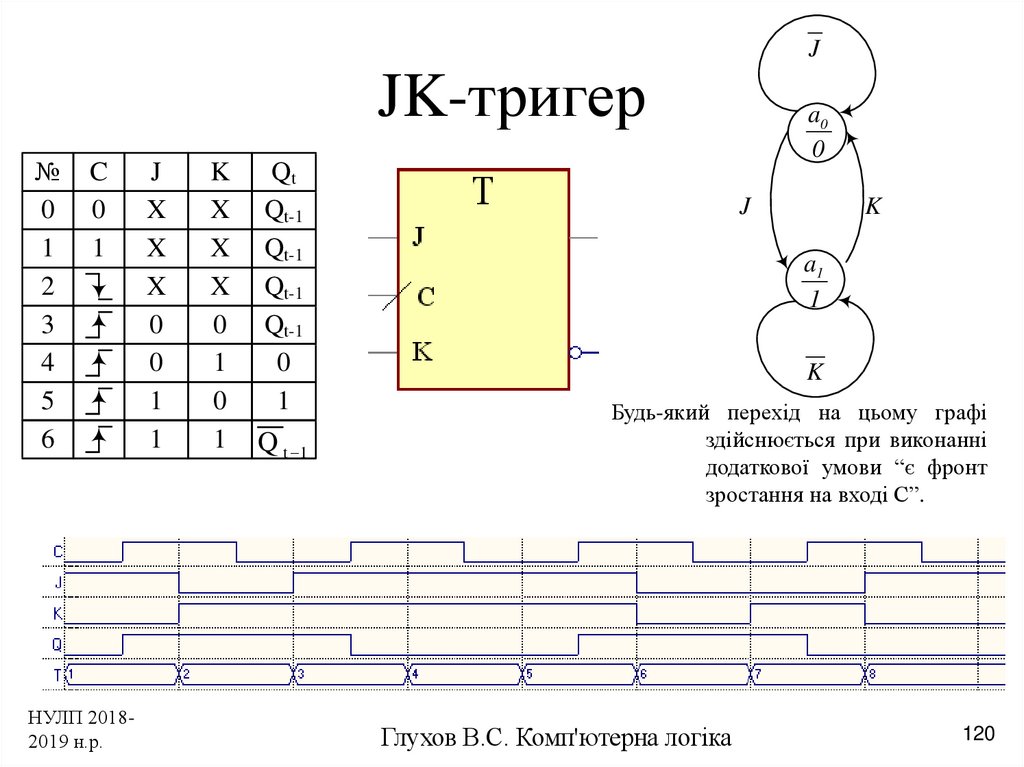

120. JK-тригер

JJK-тригер

№

0

1

2

3

4

5

6

C

0

1

НУЛП 20182019 н.р.

J

X

X

X

0

0

1

1

K

X

X

X

0

1

0

1

Qt

Qt-1

Qt-1

Qt-1

Qt-1

0

1

Q t 1

a0

0

J

K

a1

1

K

Будь-який перехід на цьому графі

здійснюється при виконанні

додаткової умови “є фронт

зростання на вході С”.

Глухов В.С. Комп'ютерна логіка

120

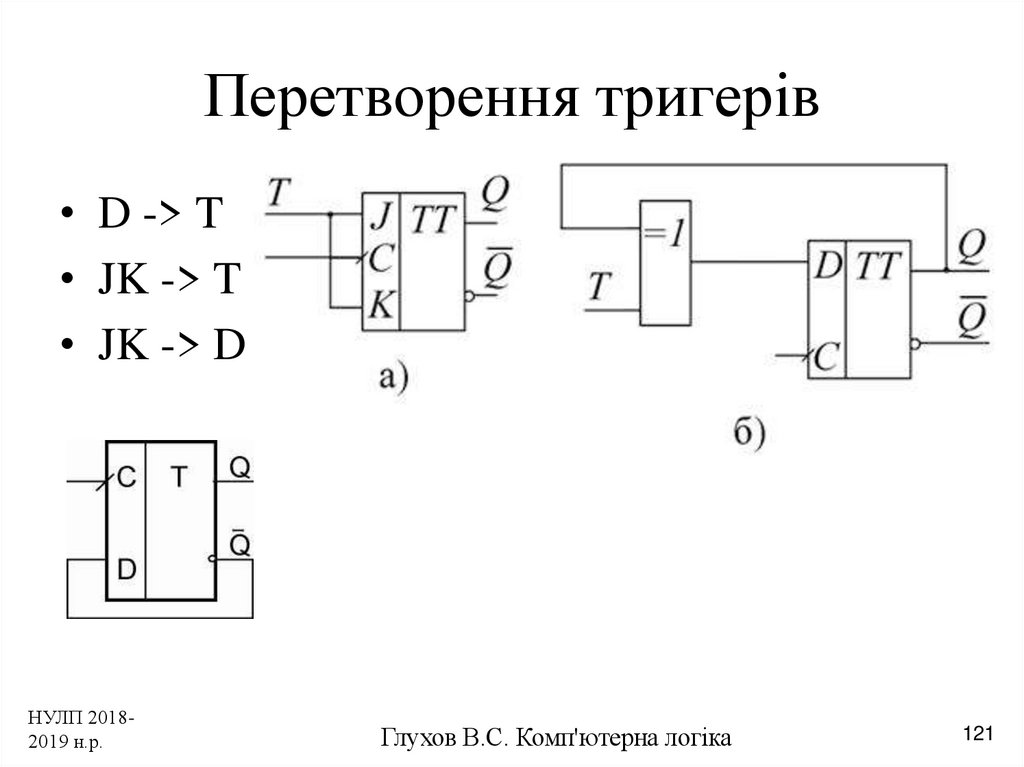

121. Перетворення тригерів

• D -> T• JK -> T

• JK -> D

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

121

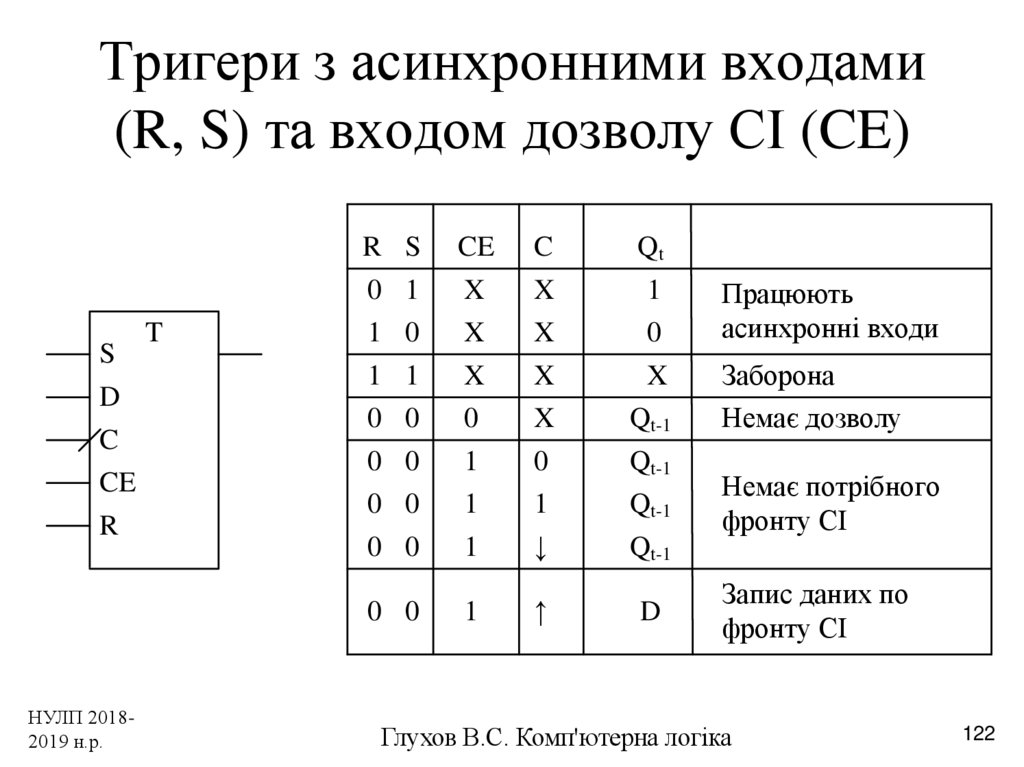

122. Тригери з асинхронними входами (R, S) та входом дозволу СІ (CE)

SD

C

CE

R

T

R

0

1

1

0

0

0

0

S

1

0

1

0

0

0

0

0 0

НУЛП 20182019 н.р.

CE

X

X

X

0

1

1

1

C

X

X

X

X

0

1

↓

Qt

1

0

X

Qt-1

Qt-1

Qt-1

Qt-1

1

↑

D

Працюють

асинхронні входи

Заборона

Немає дозволу

Немає потрібного

фронту СІ

Запис даних по

фронту СІ

Глухов В.С. Комп'ютерна логіка

122

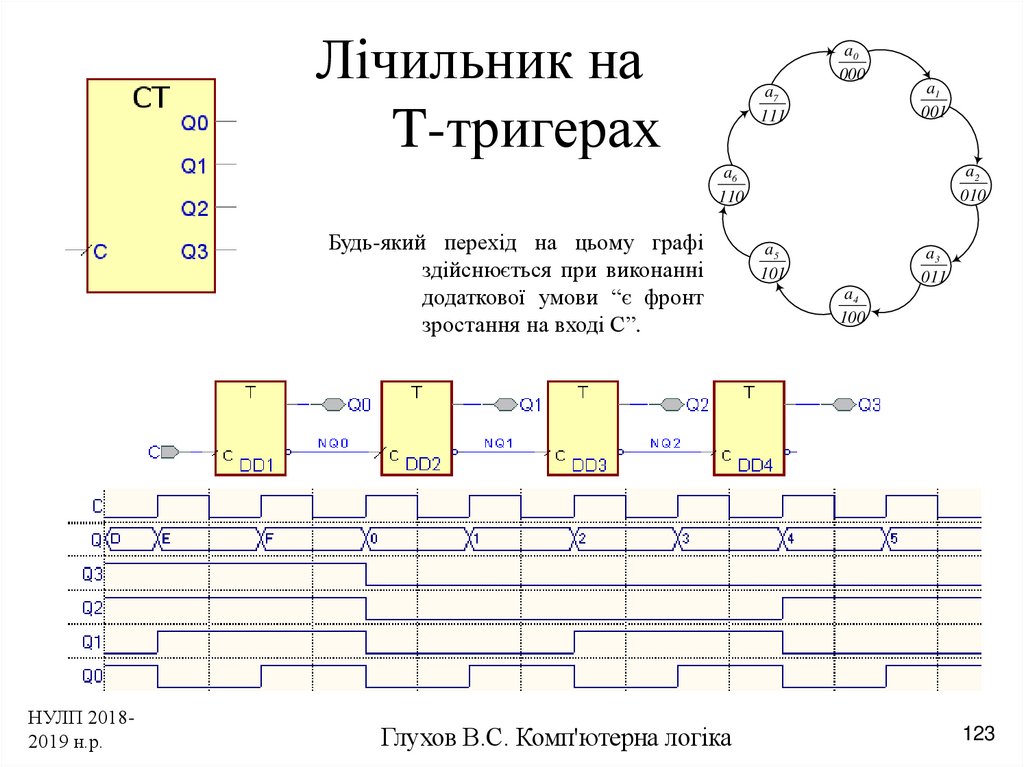

123. Лічильник на T-тригерах

a0000

a7

111

a1

001

a2

010

a6

110

Будь-який перехід на цьому графі

здійснюється при виконанні

додаткової умови “є фронт

зростання на вході С”.

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

a5

101

a3

011

a4

100

123

124. Лічильник на D-тригерах

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

124

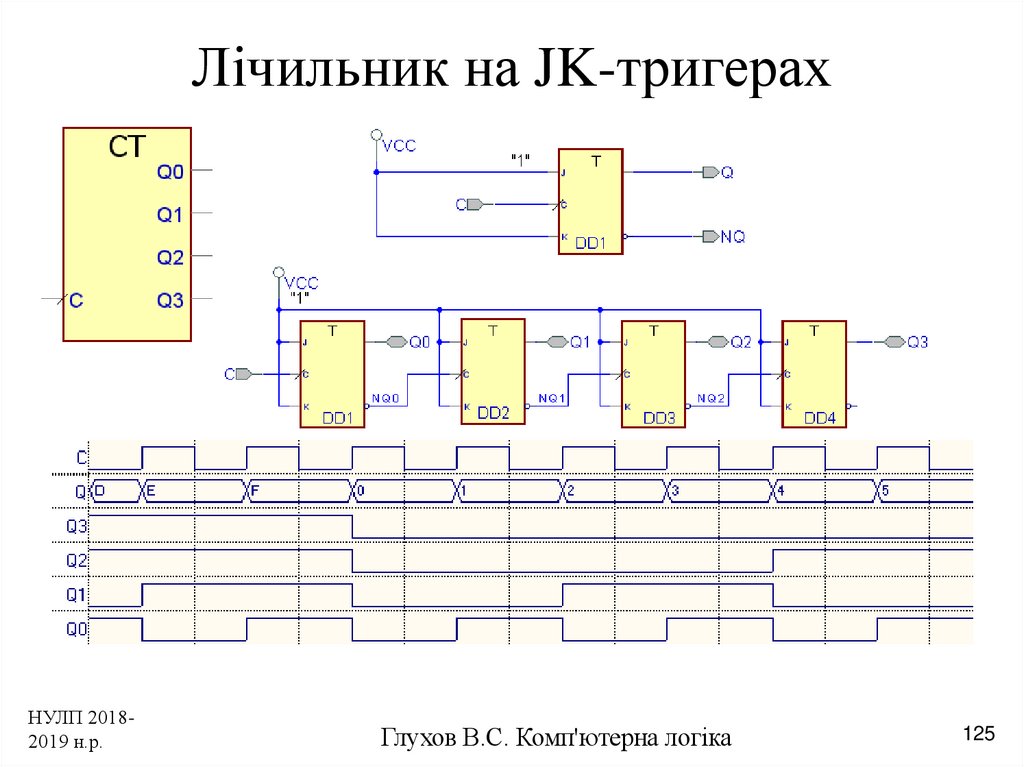

125. Лічильник на JK-тригерах

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

125

126. Класифікація регістрів

• За функціональним призначенням– регістри зсуву

– Регістри для збереження інформації (паралельні)

• За типом тригерів

• За організацією зсуву

– Ліворуч, праворуч, універсальні

• За способом прийому і видачі даних при зсуві (вхід/вихід)

–

–

–

–

НУЛП 20182019 н.р.

Послідовний/послідовний

Послідовний/паралельний

Паралельний/послідовний

Паралельний/паралельний

Глухов В.С. Комп'ютерна логіка

126

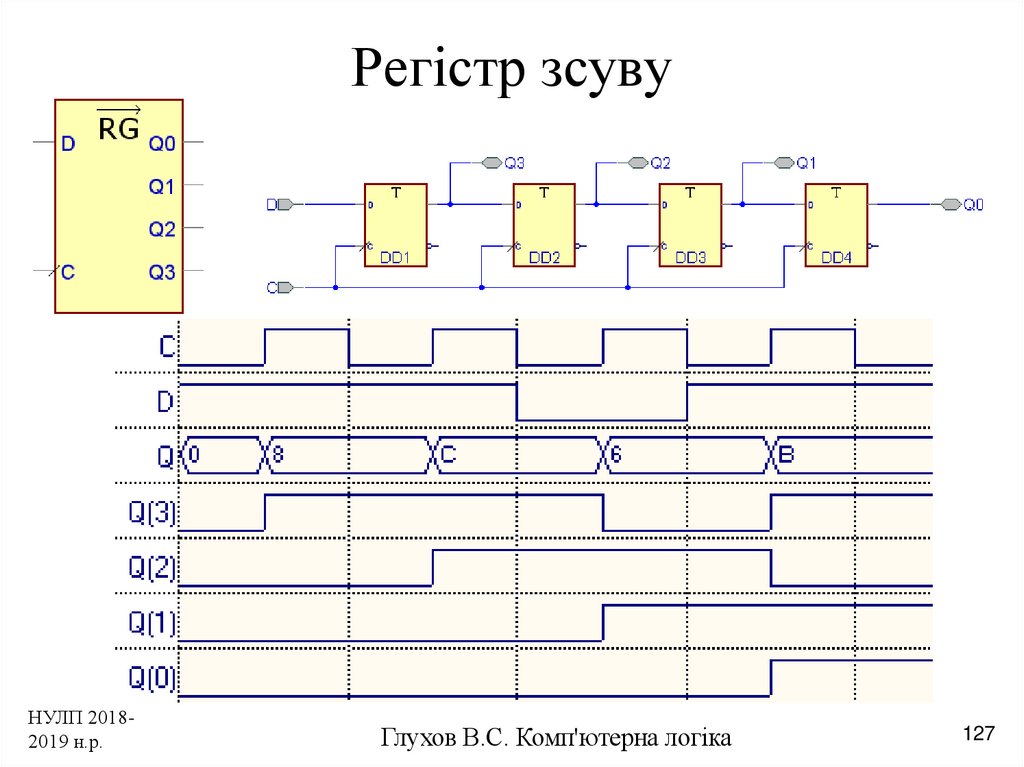

127. Регістр зсуву

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

127

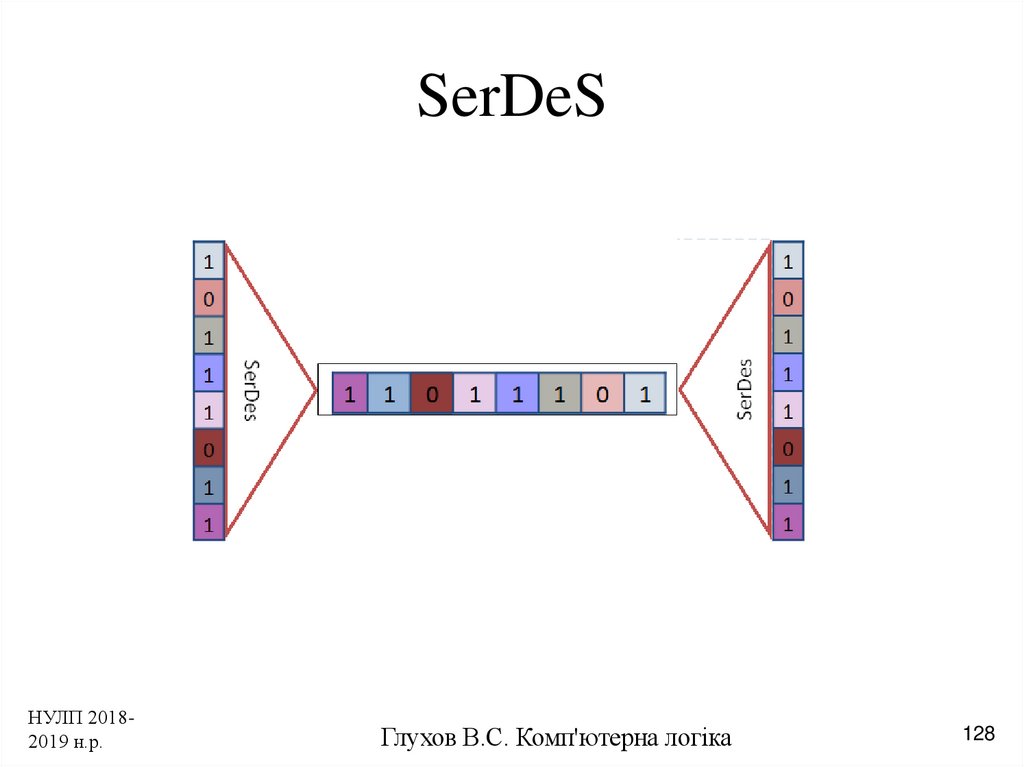

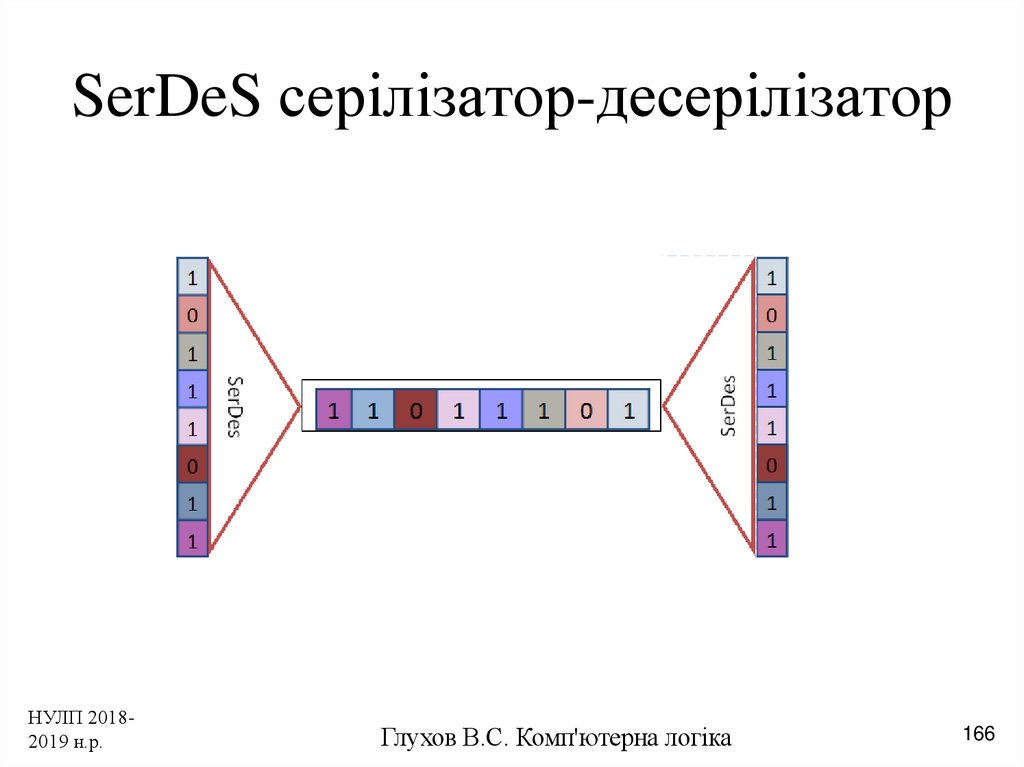

128. SerDeS

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

128

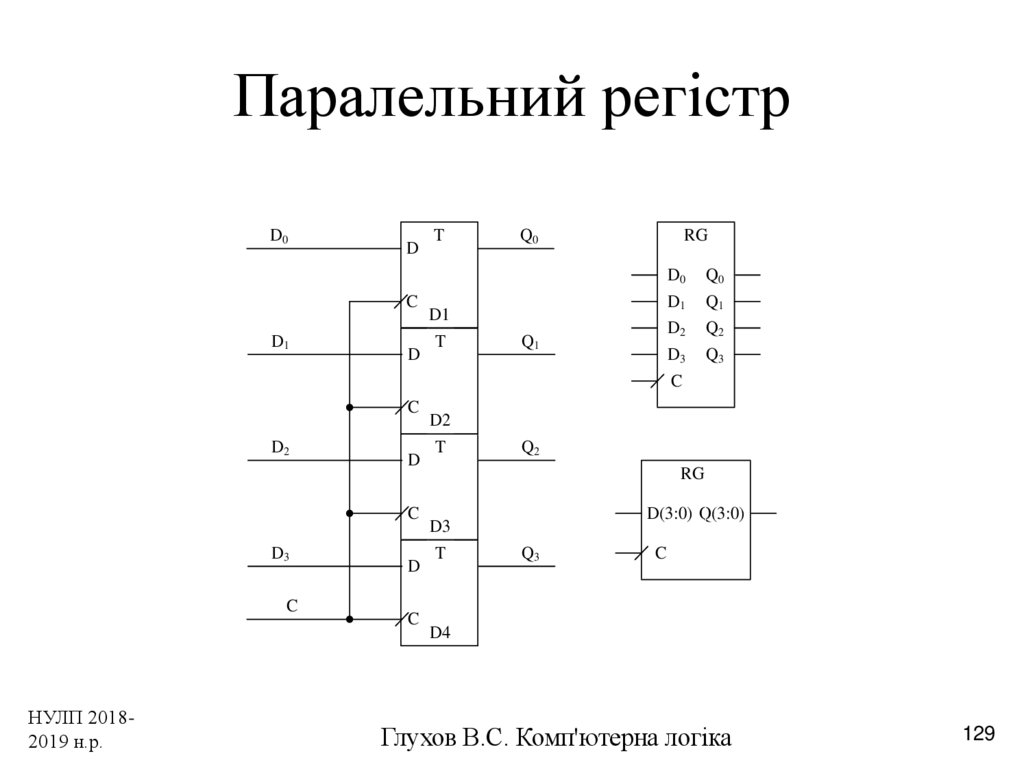

129. Паралельний регістр

D0D

C

D1

D

C

D2

D

C

D3

C

НУЛП 20182019 н.р.

D

C

T

RG

Q0

D1

T

Q1

D2

T

Q2

D0

D1

D2

D3

C

Q0

Q1

Q2

Q3

RG

D3

T

D(3:0) Q(3:0)

Q3

C

D4

Глухов В.С. Комп'ютерна логіка

129

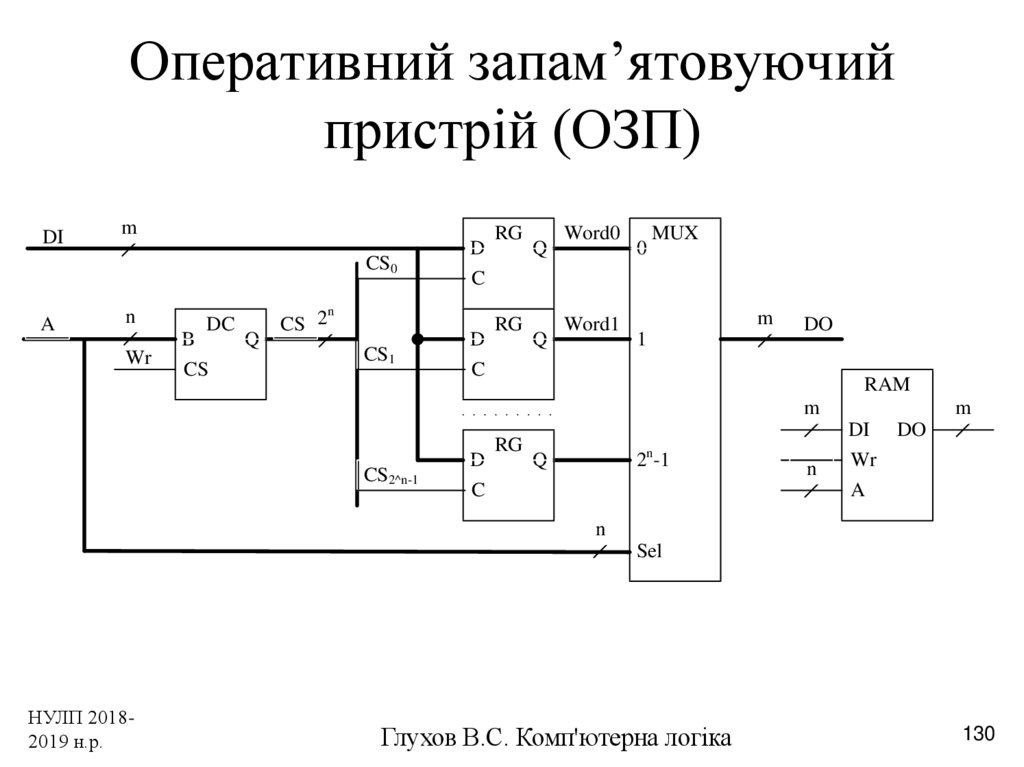

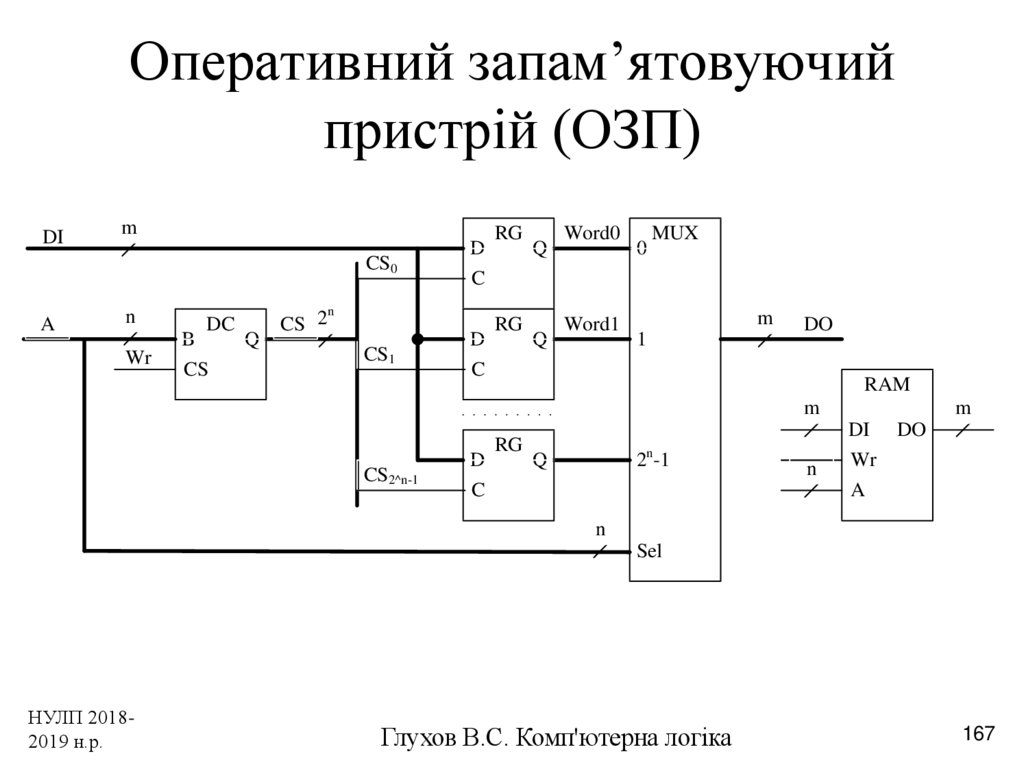

130. Оперативний запам’ятовуючий пристрій (ОЗП)

DIA

m

n

Wr

DC

B

CS

Q

CS0

D

C

CS1

D

C

n

CS 2

RG

RG

Q

Q

Word0

Word1

0

MUX

m

1

DO

RAM

m

CS2^n-1

D

C

RG

2n-1

Q

n

m

DI

Wr

A

DO

n

Sel

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

130

131. Ієрархія пам’яті

nm

A

RAM

m

DI

DO

WR

RD

OE

CS

Основні кількісні характеристики ОЗП:

кількість слів N = 2n;

об’єм пам’яті V = N * m = 2n * m біт.

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

131

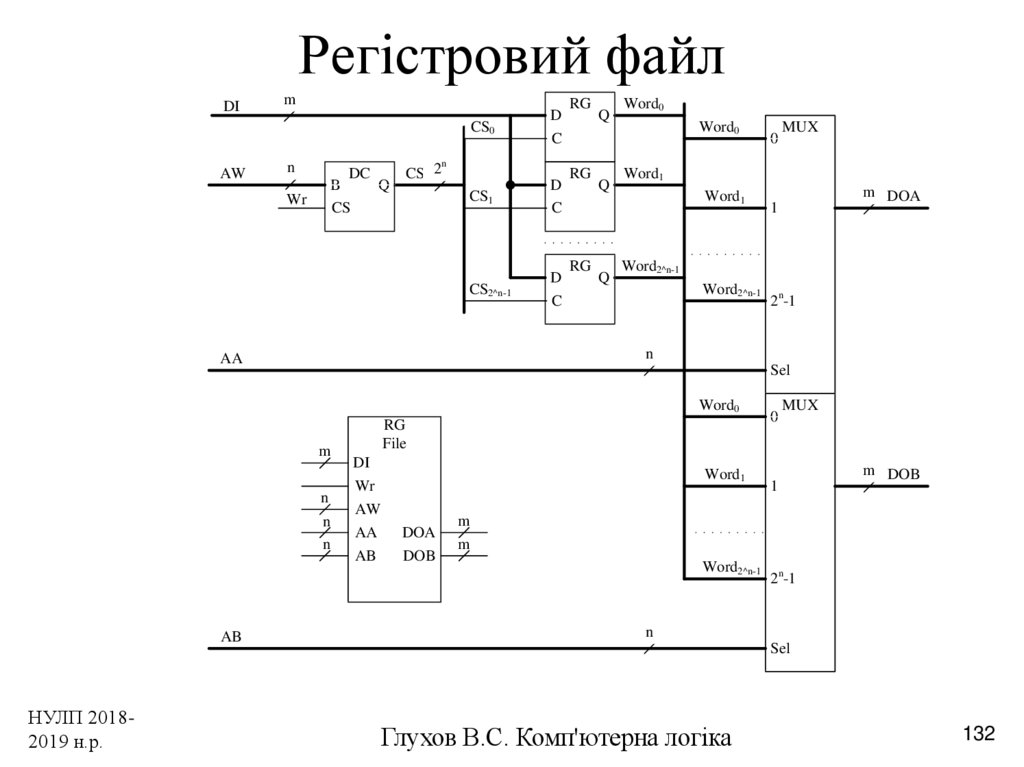

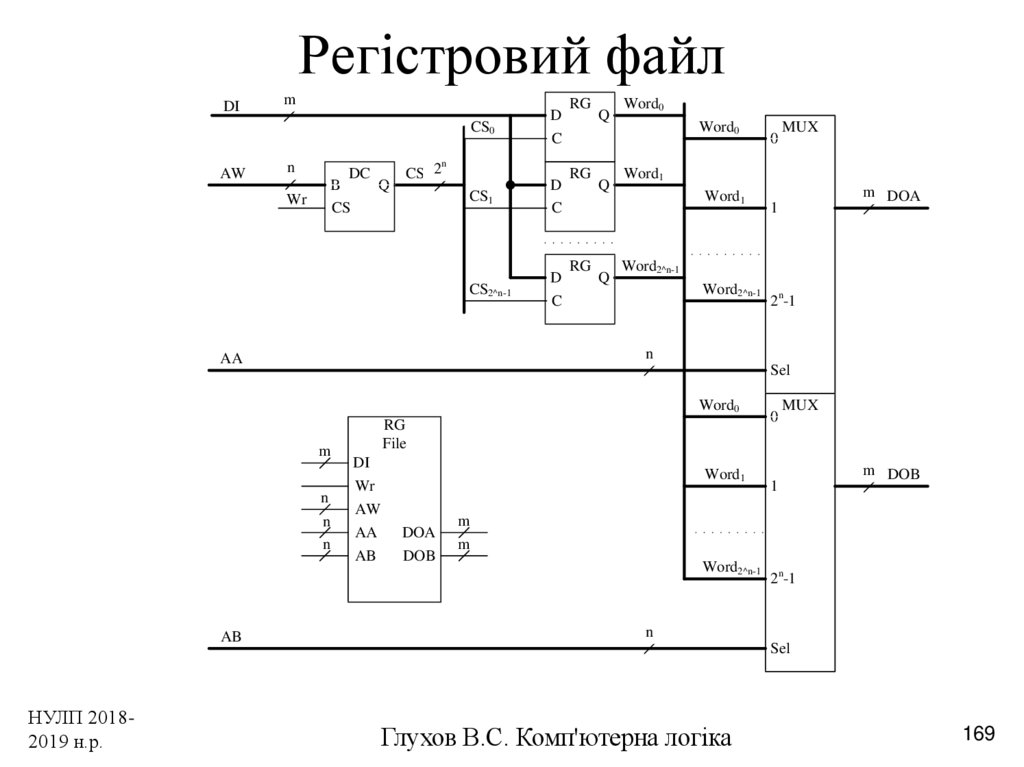

132. Регістровий файл

DIAW

m

n

DC

B

CS

Wr

Q

CS0

D

C

CS1

D

C

CS2^n-1

D

C

n

CS 2

RG

RG

RG

Q

Q

Q

Word0

Word0

Word1

Word1

m DOA

1

Word2^n-1

Word2^n-1

2n-1

Sel

Word0

m

n

n

n

НУЛП 20182019 н.р.

MUX

n

AA

AB

0

RG

File

DI

Wr

AW

AA

DOA

AB

DOB

Word1

0

MUX

1

m DOB

m

m

Word2^n-1

2n-1

n

Sel

Глухов В.С. Комп'ютерна логіка

132

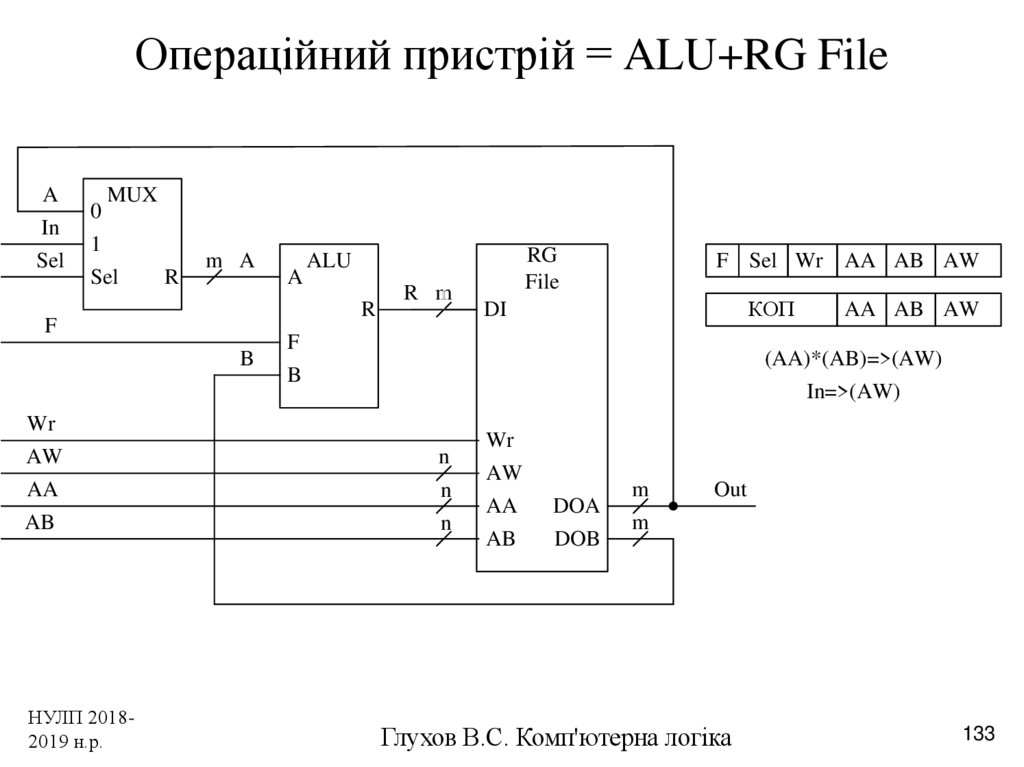

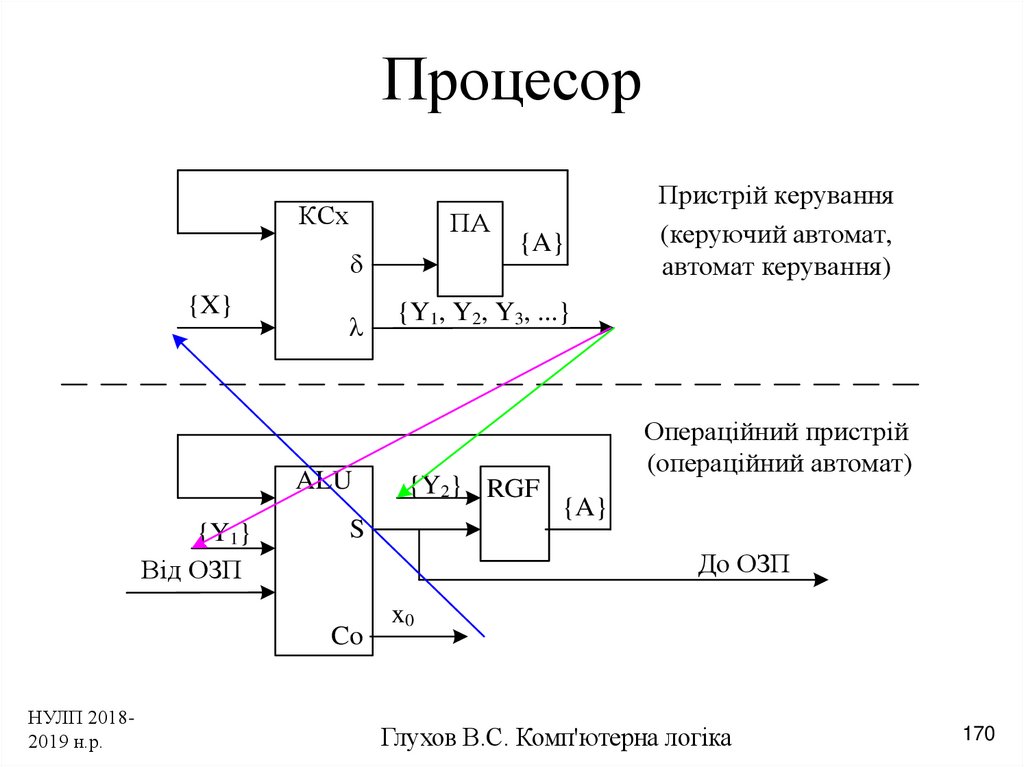

133. Операційний пристрій = ALU+RG File

AIn

Sel

MUX

0

1

Sel

R

m A

B

НУЛП 20182019 н.р.

RG

File

ALU

R

F

Wr

AW

AA

AB

A

R m

F Sel Wr AA AB AW

КОП

DI

F

B

AA AB AW

(AA)*(AB)=>(AW)

In=>(AW)

n

n

n

Wr

AW

AA

AB

DOA

DOB

m

m

Out

Глухов В.С. Комп'ютерна логіка

133

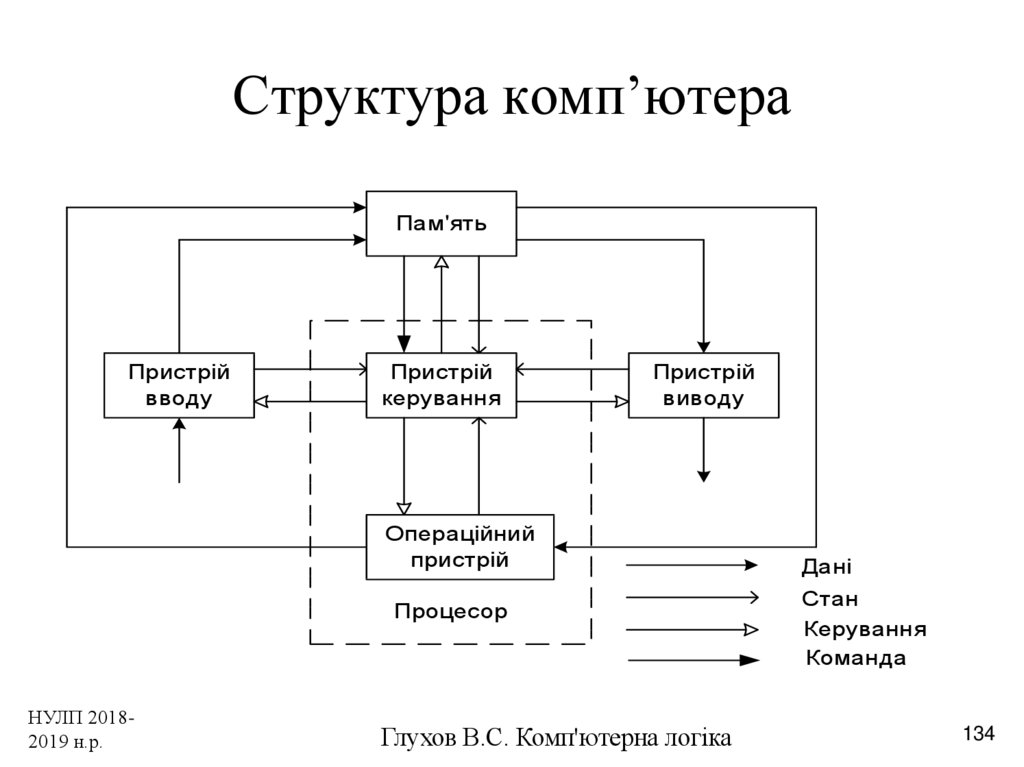

134. Структура комп’ютера

Пам'ятьПристрій

вводу

Пристрій

керування

Пристрій

виводу

Операційний

пристрій

Процесор

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

Дані

Стан

Керування

Команда

134

135. Логічна комірка

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

135

136. Конфігуровна логічна комірка

DconfOКомбінаційних вихід

0

RG

C

D

Cconf

НУЛП 20182019 н.р.

DconfI

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

0 MUX

1

2

3

4

5

6

7

8

9

10

11

MUX

f

Регістровий

вихід

T

C

D

C

Contr

1

1

D2

12

13

14

d

c

b

a

15

1

2

4

8

Глухов В.С. Комп'ютерна логіка

136

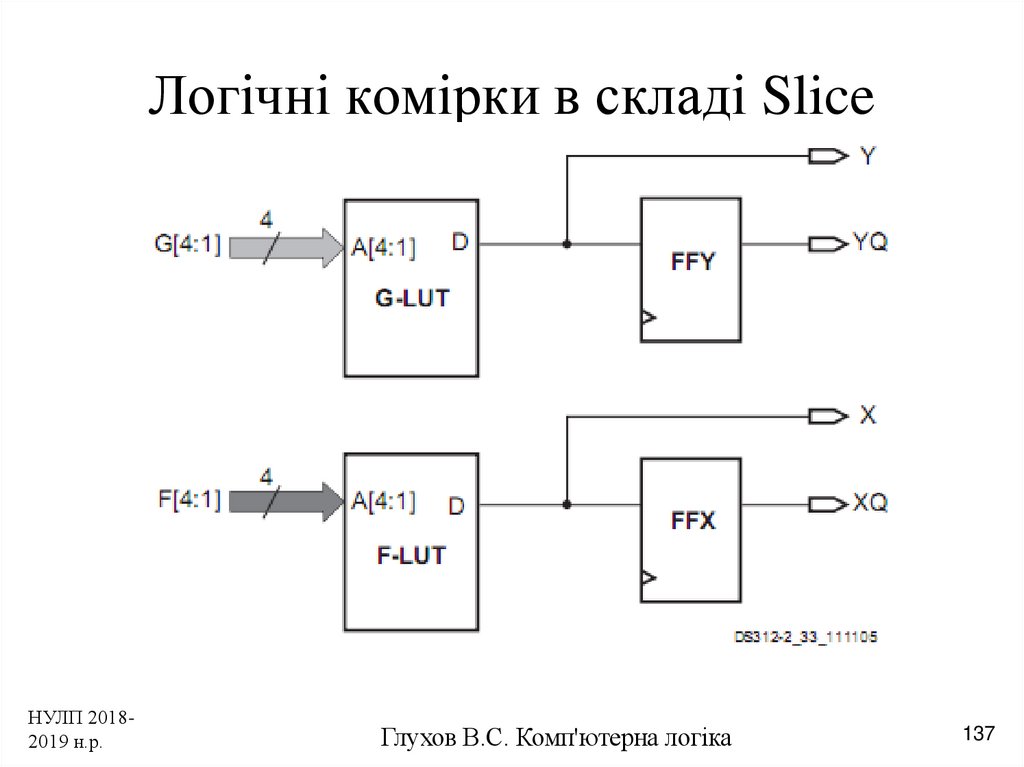

137. Логічні комірки в складі Slice

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

137

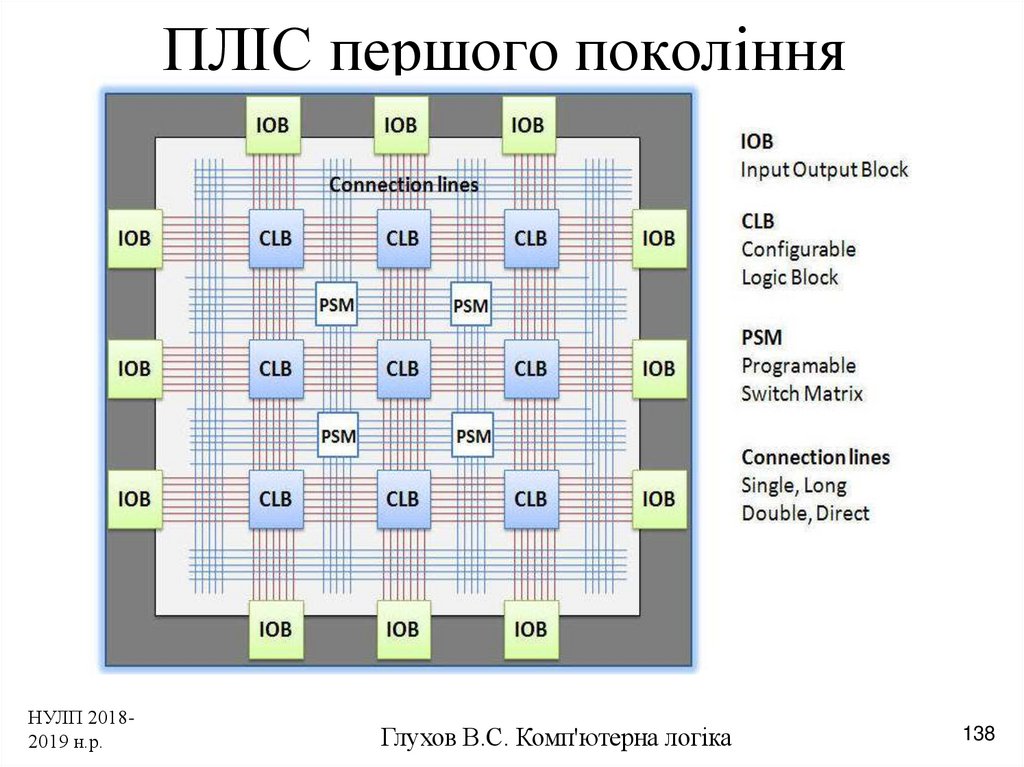

138. ПЛІС першого покоління

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

138

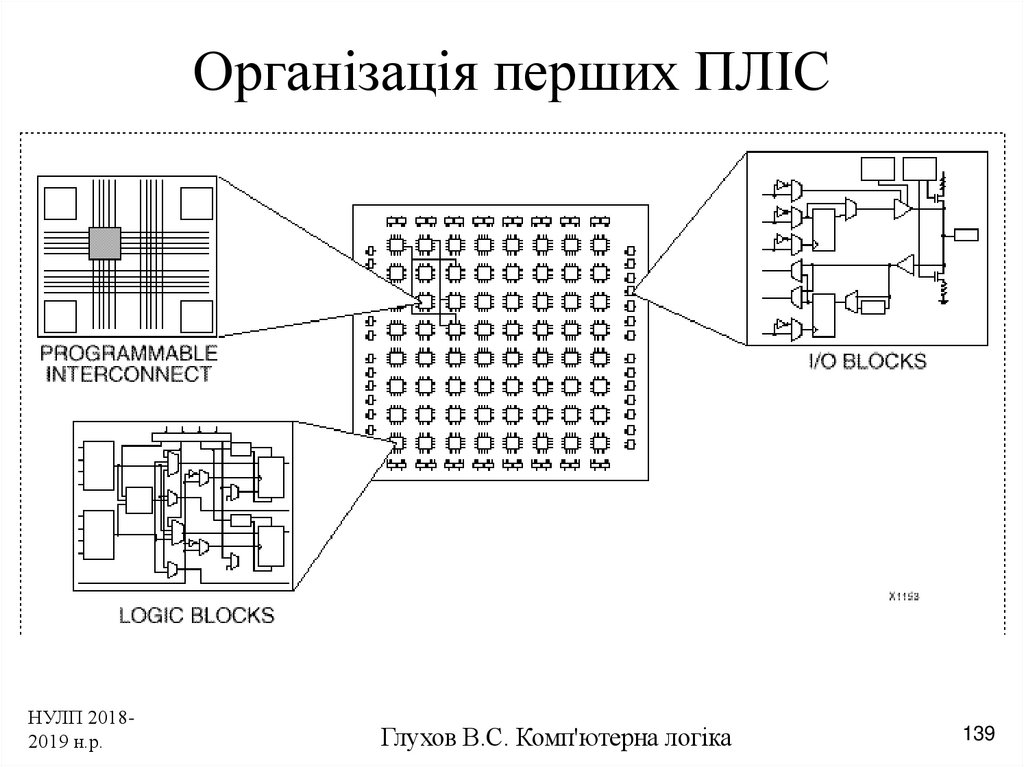

139. Організація перших ПЛІС

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

139

140. Конфігуровані логічні блоки (CLB) та електронні комутатори (PSM -Programmable switch matrix )

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

140

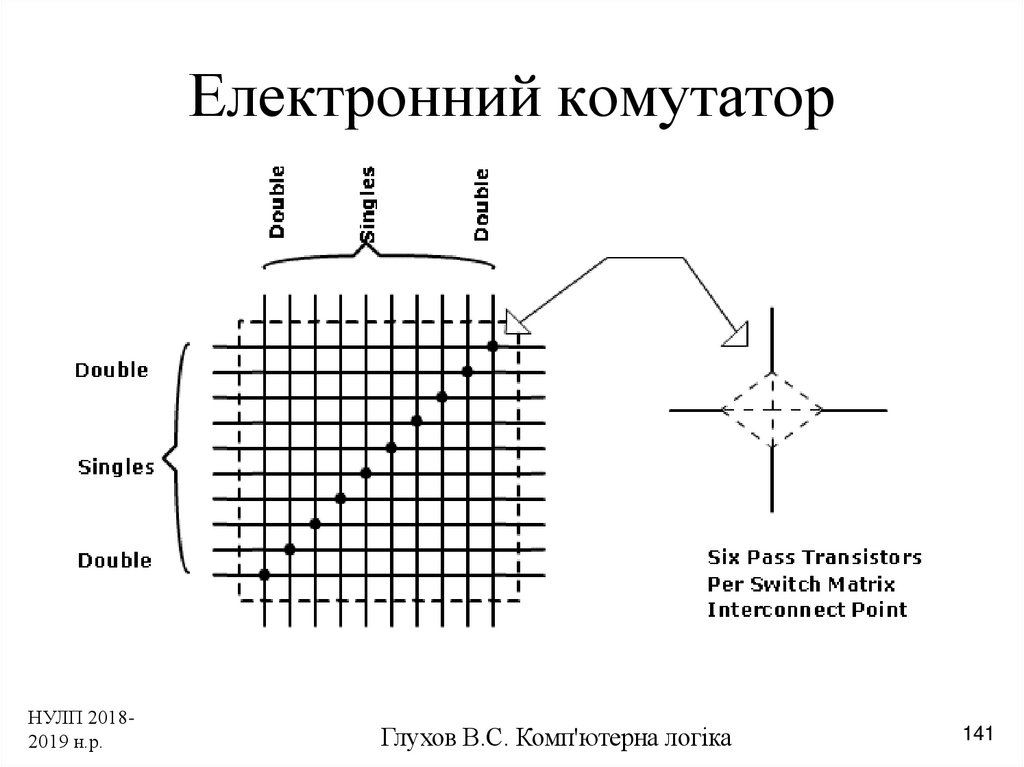

141. Електронний комутатор

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

141

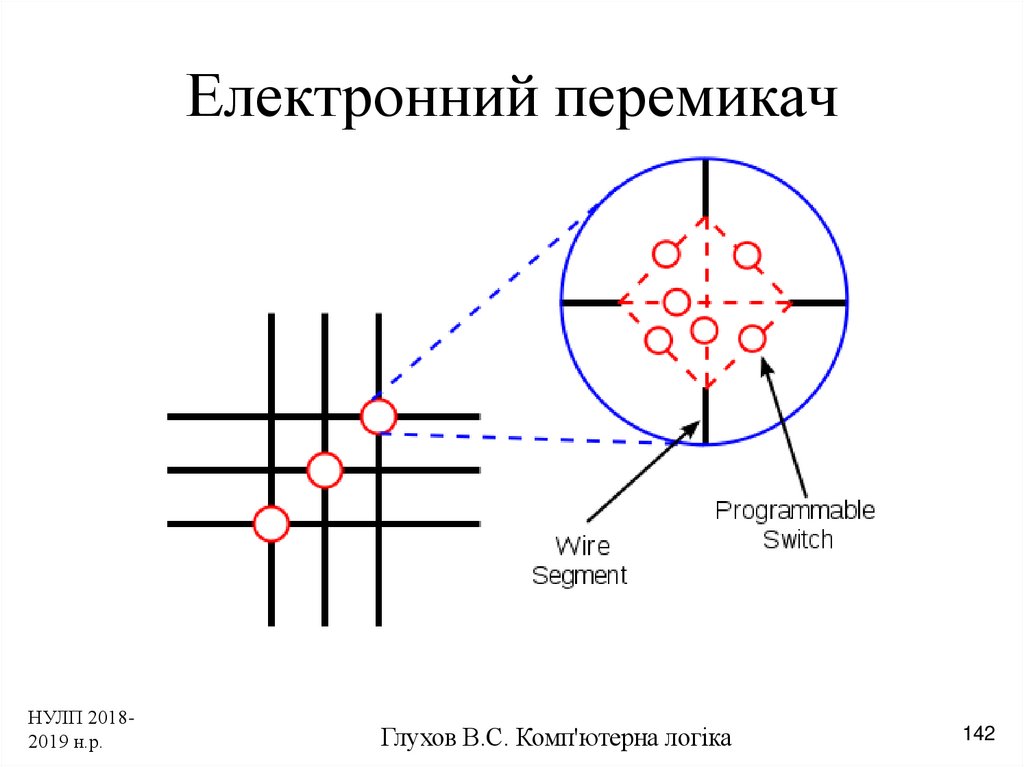

142. Електронний перемикач

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

142

143. Структура комп’ютера

Пам'ятьПристрій

вводу

Пристрій

керування

Пристрій

виводу

Операційний

пристрій

Процесор

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

Дані

Стан

Керування

Команда

143

144. Загальна структурна схема цифрового автомата складається з двох цифрових схем

КСхПА

δ

{X}

КСх - комбінаційна схема

ПА - пам’ять автомата

δ – функція переходів

λ – функція виходів

λ

{A}

{Y}

{X} – множина вхідних сигналів

{Y} – множина вихідних сигналів

{A} – множина внутришніх станів

-Цифрові схеми поділяються на комбінаційні (без зворотних зв’язків) та

схеми з пам’яттю (із зворотними зв’язками, послідовнісні, секвенційні)

-Комбінаційна схема:

цифрова схема без пам’яті =

= цифрова схема без зворотних зв’язків =

= цифрова схема, стан виходів якої у момент часу t залежить тільки від

стану її входів у цей же момент часу t.

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

144

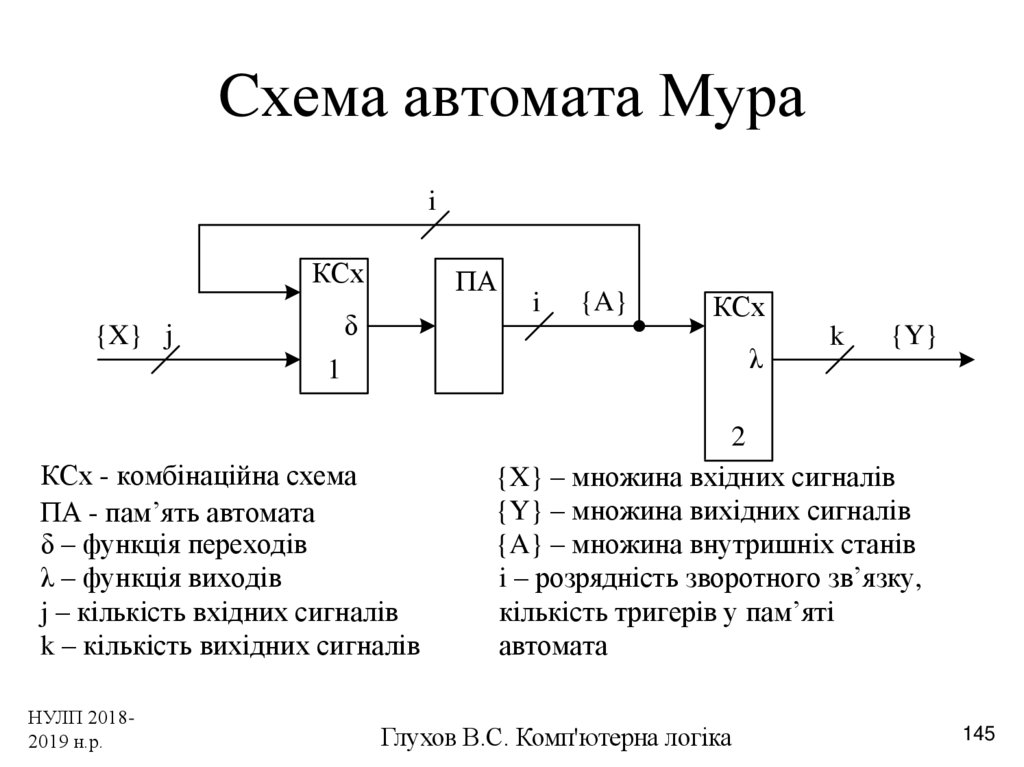

145. Cхема автомата Мура

iКСх

ПА

δ

{X} j

i

{A}

КСх

λ

1

КСх - комбінаційна схема

ПА - пам’ять автомата

δ – функція переходів

λ – функція виходів

j – кількість вхідних сигналів

k – кількість вихідних сигналів

НУЛП 20182019 н.р.

k

{Y}

2

{X} – множина вхідних сигналів

{Y} – множина вихідних сигналів

{A} – множина внутришніх станів

i – розрядність зворотного зв’язку,

кількість тригерів у пам’яті

автомата

Глухов В.С. Комп'ютерна логіка

145

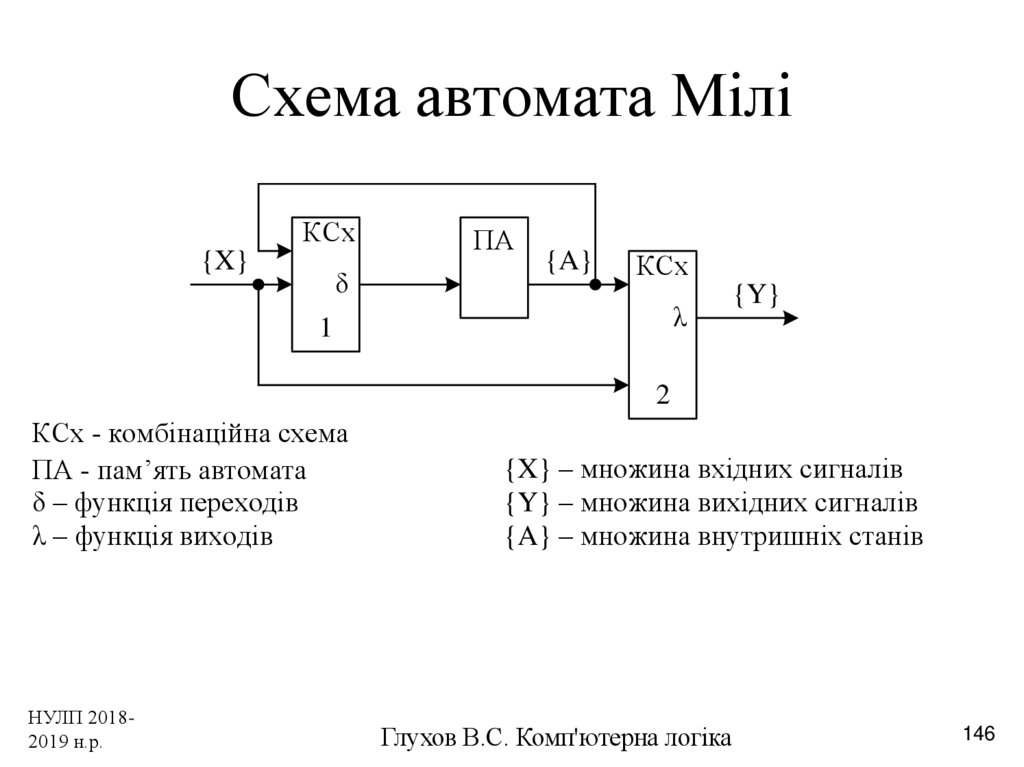

146. Схема автомата Мілі

КСх{X}

δ

ПА

{A}

КСх

λ

1

{Y}

2

КСх - комбінаційна схема

ПА - пам’ять автомата

δ – функція переходів

λ – функція виходів

НУЛП 20182019 н.р.

{X} – множина вхідних сигналів

{Y} – множина вихідних сигналів

{A} – множина внутришніх станів

Глухов В.С. Комп'ютерна логіка

146

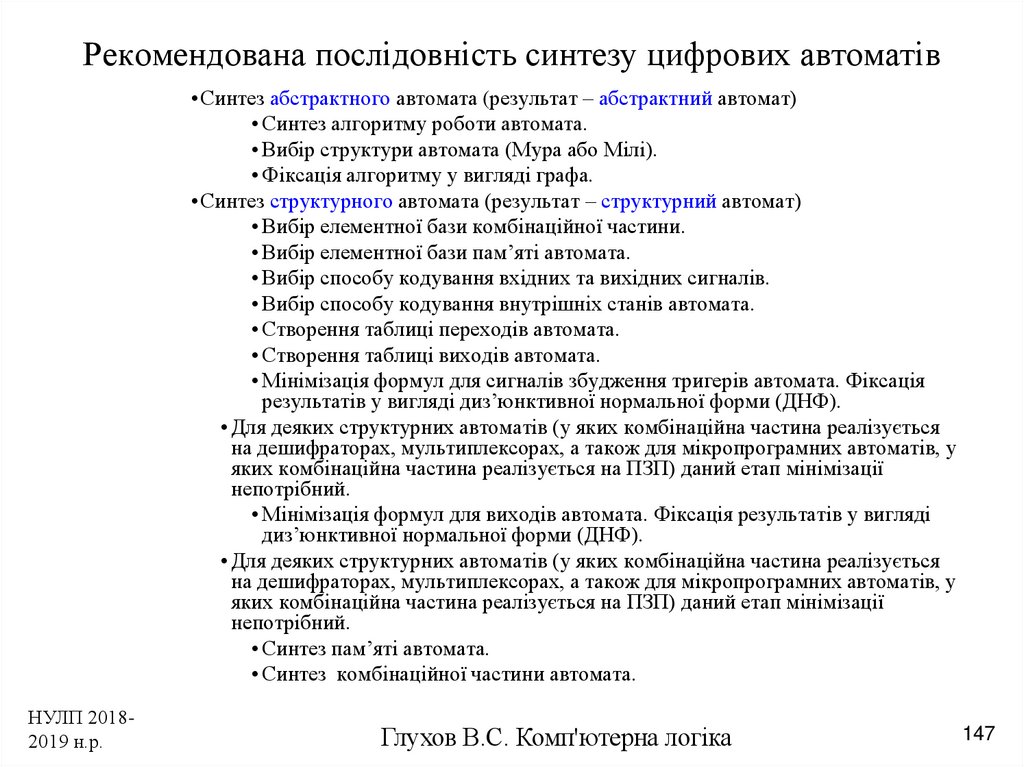

147. Рекомендована послідовність синтезу цифрових автоматів

•Синтез абстрактного автомата (результат – абстрактний автомат)• Синтез алгоритму роботи автомата.

• Вибір структури автомата (Мура або Мілі).

• Фіксація алгоритму у вигляді графа.

•Синтез структурного автомата (результат – структурний автомат)

• Вибір елементної бази комбінаційної частини.

• Вибір елементної бази пам’яті автомата.

• Вибір способу кодування вхідних та вихідних сигналів.

• Вибір способу кодування внутрішніх станів автомата.

• Створення таблиці переходів автомата.

• Створення таблиці виходів автомата.

• Мінімізація формул для сигналів збудження тригерів автомата. Фіксація

результатів у вигляді диз’юнктивної нормальної форми (ДНФ).

• Для деяких структурних автоматів (у яких комбінаційна частина реалізується

на дешифраторах, мультиплексорах, а також для мікропрограмних автоматів, у

яких комбінаційна частина реалізується на ПЗП) даний етап мінімізації

непотрібний.

• Мінімізація формул для виходів автомата. Фіксація результатів у вигляді

диз’юнктивної нормальної форми (ДНФ).

• Для деяких структурних автоматів (у яких комбінаційна частина реалізується

на дешифраторах, мультиплексорах, а також для мікропрограмних автоматів, у

яких комбінаційна частина реалізується на ПЗП) даний етап мінімізації

непотрібний.

• Синтез пам’яті автомата.

• Синтез комбінаційної частини автомата.

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

147

148. Кодуванням станів автомата: двійкове, сусіднє, унітарне

ii

КСх

ПА

δ

{X} j

1

КСх - комбінаційна схема

ПА - пам’ять автомата

δ – функція переходів

λ – функція виходів

j – кількість вхідних сигналів

k – кількість вихідних сигналів

КСх

КСх

i

{A}

λ

{Y}

k

ПА

δ

{X} j

i

КСх

{A}

2

{X} – множина вхідних сигналів

{Y} – множина вихідних сигналів

{A} – множина внутришніх станів

i – розрядність зворотного зв’язку,

кількість тригерів у пам’яті

автомата

k

λ

1

КСх - комбінаційна схема

ПА - пам’ять автомата

δ – функція переходів

λ – функція виходів

j – кількість вхідних сигналів

k – кількість вихідних сигналів

{Y}

2

{X} – множина вхідних сигналів

{Y} – множина вихідних сигналів

{A} – множина внутришніх станів

i – розрядність зворотного зв’язку,

кількість тригерів у пам’яті

автомата

Кількість тригерів залежить тільки від

кількості станів і способу їх кодування

№

0

1

2

...

8

9

Позначення

ai

a0

a1

a2

НУЛП 20182019 н.р.

Стан автомата

Унітарний код

Q9 Q8

Q2 Q1

...

0

0

0

0

...

0

0

0

1

...

0

0

1

0

...

...

...

a8

a9

0

1

...

1

0

...

...

...

...

0

0

...

0

0

№

Q0

1

0

0

...

0

0

0

1

2

...

8

9

Стан автомата

Позначення

Двійковий код

ai

Q3 Q2 Q1 Q0

0

0

0

0

a0

0

0

0

1

a1

a2

0

0

1

0

...

...

a8

a9

1

1

Глухов В.С. Комп'ютерна логіка

...

0

0

...

0

0

...

0

1

148

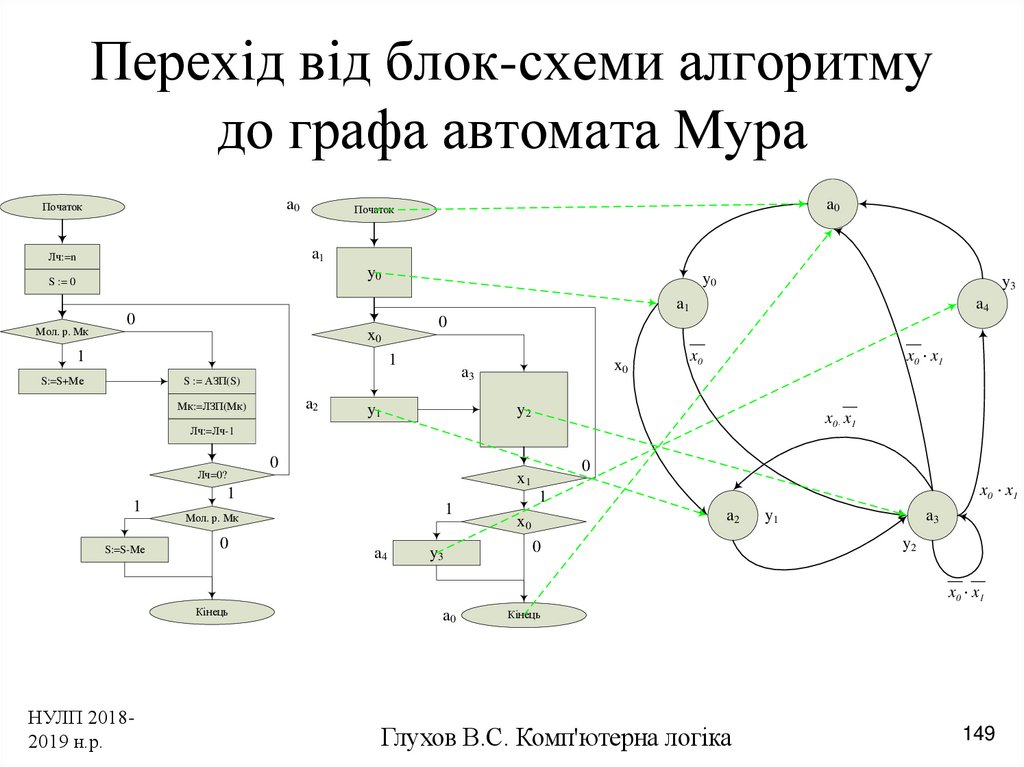

149. Перехід від блок-схеми алгоритму до графа автомата Мура

a0Початок

a0

Початок

a1

Лч:=n

y0

S := 0

Мол. р. Мк

y0

a1

0

1

1

a2

x0

a3

S := АЗП(S)

Мк:=ЛЗП(Мк)

a4

0

x0

S:=S+Ме

y3

y1

x0 x1

x0

y2

x0 x1

Лч:=Лч-1

Лч=0?

1

S:=S-Ме

0

1

1

Мол. р. Мк

0

0

x1

a4

y3

x0 x1

1

a2

x0

0

y1

a3

y2

x0 x1

Кінець

НУЛП 20182019 н.р.

a0

Кінець

Глухов В.С. Комп'ютерна логіка

149

150. Перехід від блок-схеми алгоритму до графа автомата Мілі

Початокy0

Початок

a0

a0

Лч:=n

y0

S := 0

Мол. р. Мк

a1

0

0

x0

1

y1

Мк:=ЛЗП(Мк)

y1

S:=S-Ме

a3

x1

0

1

1

Мол. р. Мк

0

y0

y2

a2

Лч:=Лч-1

1

x0 x1

x0

S := АЗП(S)

Лч=0?

x0

y2

1

S:=S+Ме

a1

x0 x1

y3

0

x0 x1

1

a2

x0

0

y3

a3

y2

y2

x0 x1

a0

Кінець

НУЛП 20182019 н.р.

Кінець

Глухов В.С. Комп'ютерна логіка

150

151. Збудження тригерів

DСигнали збудження тригерів

Щоб змінити

Щоб перевести

Щоб перевести

стан (з 0 до 1 або

тригер до стану 0 тригер до стану 1

з 1 до 0)

D

a0

0

T

D=0

C

J

D

D=1

T

K=1

C

K

D

a1

1

J

D

a0

0

J

J=1

a1

1

CE

CE

C

K

a0

0

T

CE=1

CE

K

CE

a1

1

CE

НУЛП 20182019 н.р.

Глухов В.С. Комп'ютерна логіка

151

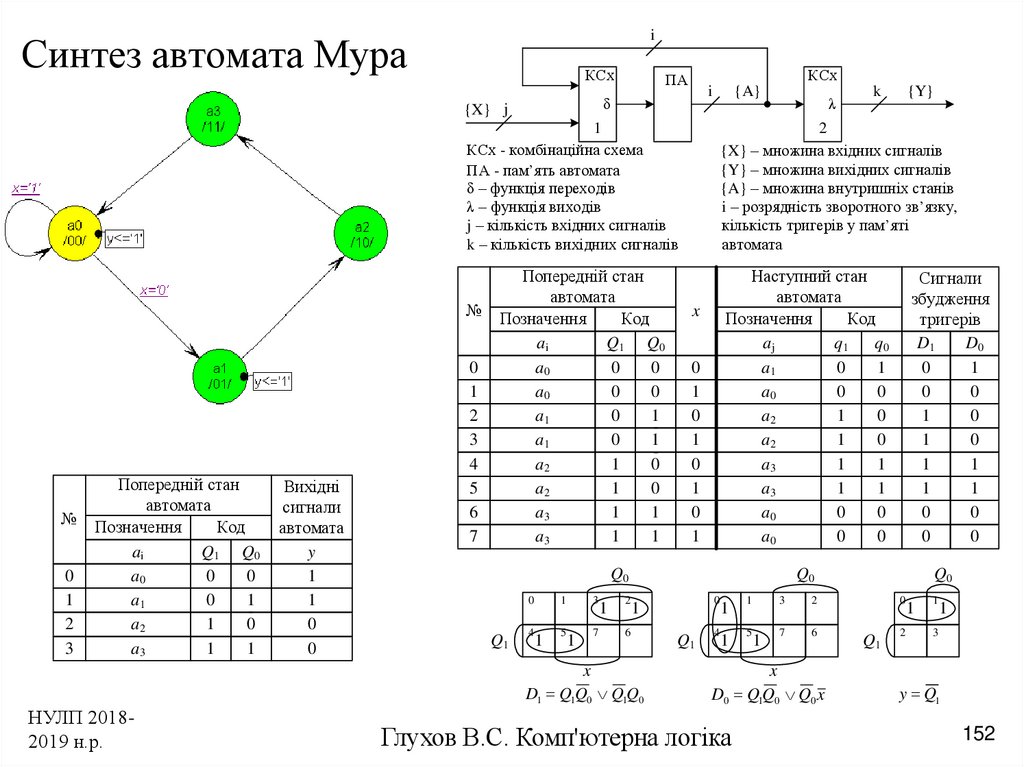

152. Синтез автомата Мура

iСинтез автомата Мура

КСх

КСх

ПА

δ

{X} j

{A}

i

1

КСх - комбінаційна схема

ПА - пам’ять автомата

δ – функція переходів

λ – функція виходів

j – кількість вхідних сигналів

k – кількість вихідних сигналів

№

№

0

1

2

3

Попередній стан

автомата

Позначення

Код

ai

Q1 Q0

0

0

a0

0

1

a1

1

0

a2

1

1

a3

Вихідні

сигнали

автомата

y

1

1

0

0

0

1

2

3

4

5

6

7

Попередній стан

автомата

Позначення

Код

ai

Q1 Q0

a0

0

0

a0

0

0

0

1

a1

0

1

a1

1

0

a2

1

0

a2

a3

1

1

1

1

a3

0

Q1

4

1

1

5

3

1

7

1

2

{Y}

k

2

{X} – множина вхідних сигналів

{Y} – множина вихідних сигналів

{A} – множина внутришніх станів

i – розрядність зворотного зв’язку,

кількість тригерів у пам’яті

автомата

Наступний стан

автомата

Позначення

Код

aj

q1

q0

a1

0

1

a0

0

0

1

0

a2

1

0

a2

1

1

a3

1

1

a3

a0

0

0

0

0

a0

x

0

1

0

1

0

1

0

1

Q0

Сигнали

збудження

тригерів

D1

D0

0

1

0

0

1

0

1

0

1

1

1

1

0

0

0

0

Q0

0

1

6

x

D1 Q1Q0 Q1Q0

НУЛП 20182019 н.р.

λ

Q1

4

1

1

1

5

1

3

2

7

6

x

D0 Q1Q0 Q0 x

Глухов В.С. Комп'ютерна логіка

Q0

0

Q1

2

1

1

1

3

y Q1

152

153. Результат синтезу – схема автомата Мура

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

153

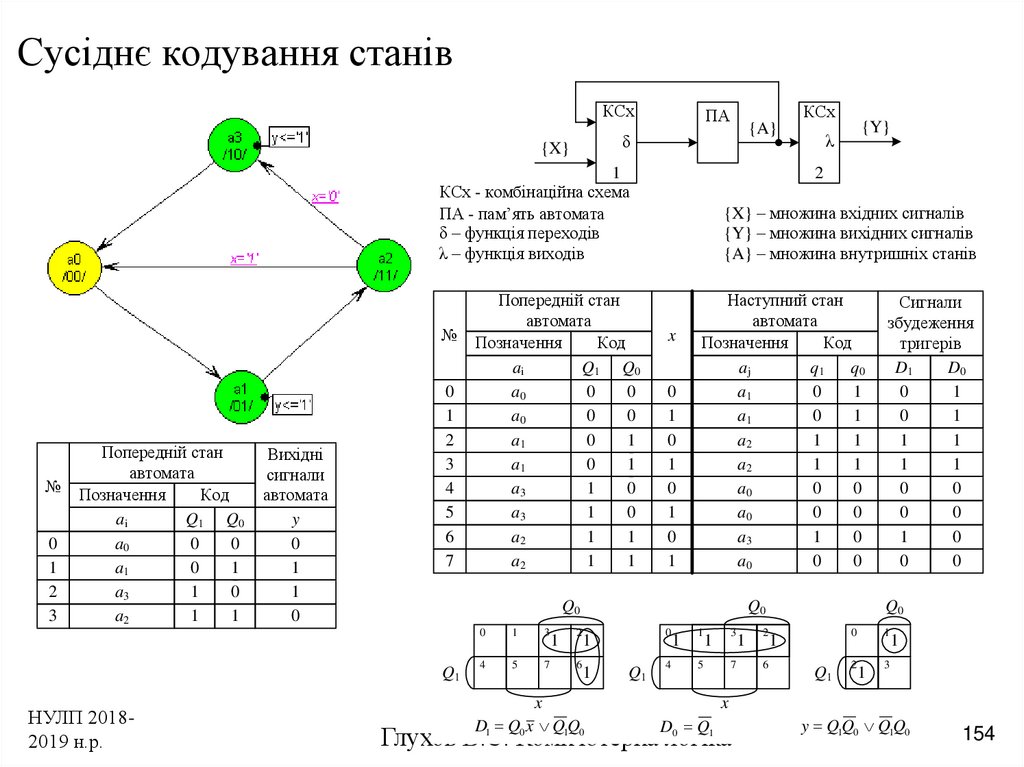

154. Сусіднє кодування станів

КСх1

КСх - комбінаційна схема

ПА - пам’ять автомата

δ – функція переходів

λ – функція виходів

№

0

1

2

3

Попередній стан

автомата

Позначення

Код

ai

Q1 Q0

0

0

a0

0

1

a1

1

0

a3

1

1

a2

Вихідні

сигнали

автомата

y

0

1

1

0

0

1

2

3

4

5

6

7

Попередній стан

автомата

Позначення

Код

ai

Q1 Q0

a0

0

0

a0

0

0

0

1

a1

0

1

a1

1

0

a3

1

0

a3

a2

1

1

1

1

a2

0

1

3

4

5

7

1

2

6

{Y}

λ

2

{X} – множина вхідних сигналів

{Y} – множина вихідних сигналів

{A} – множина внутришніх станів

x

0

1

0

1

0

1

0

1

Наступний стан

автомата

Позначення

Код

aj

q1

q0

a1

0

1

a1

0

1

1

1

a2

1

1

a2

0

0

a0

0

0

a0

a3

1

0

0

0

a0

Q0

Q1

НУЛП 20182019 н.р.

{A}

δ

{X}

№

КСх

ПА

Q0

0

1

1

x

D1 Q0 x Q1Q0

Q1

4

1

1

3

1

5

7

1

2

6

Сигнали

збудеження

тригерів

D1

D0

0

1

0

1

1

1

1

1

0

0

0

0

1

0

0

0

Q0

0

1

Q1

2

1

1

1

3

x

D0 Q1

Глухов В.С. Комп'ютерна логіка

y Q1Q0 Q1Q0

154

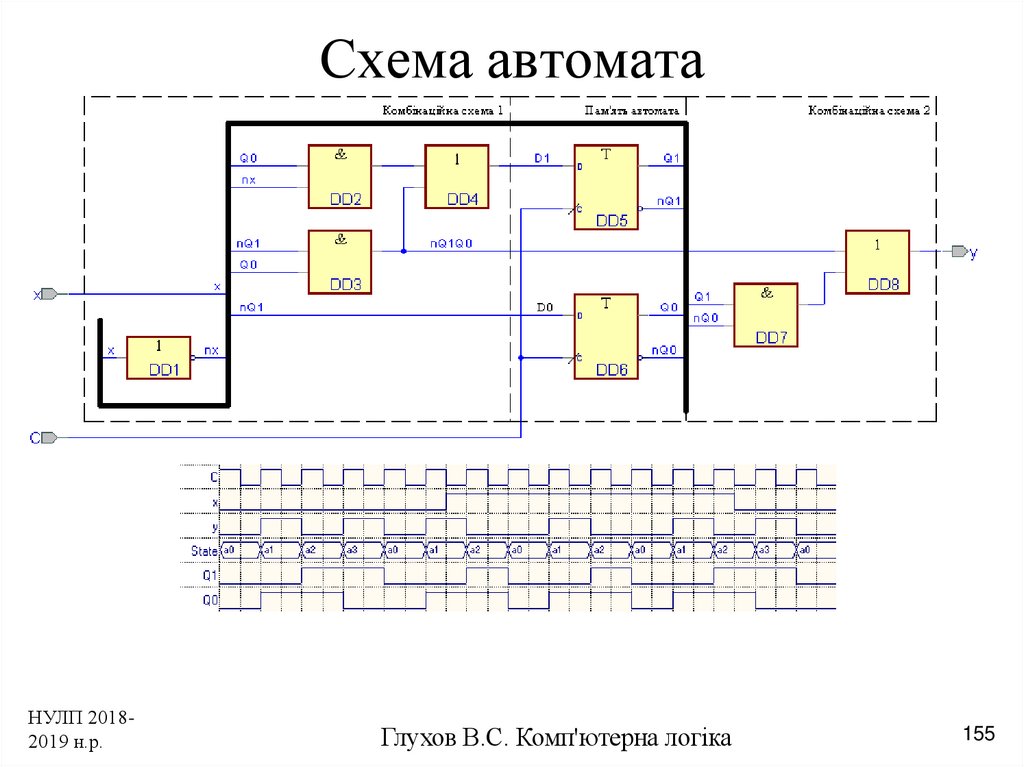

155. Схема автомата

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

155

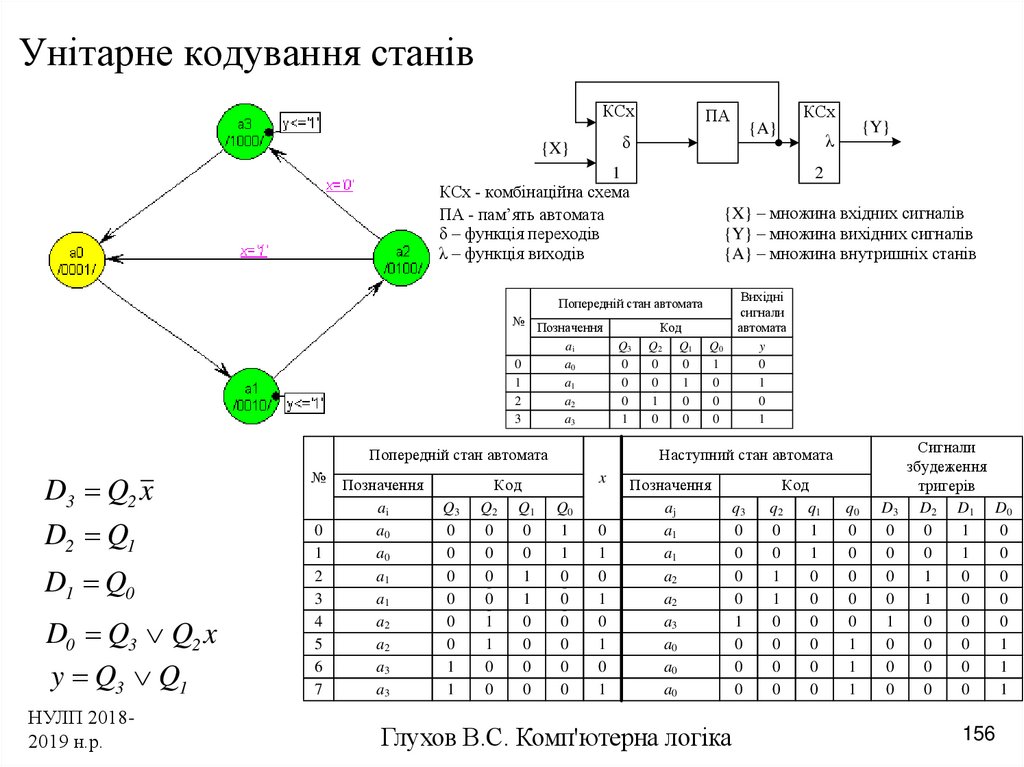

156. Унітарне кодування станів

КСх{X} – множина вхідних сигналів

{Y} – множина вихідних сигналів

{A} – множина внутришніх станів

Попередній стан автомата

Позначення

ai

a0

a1

a2

a3

Попередній стан автомата

D3 Q2 x

D2 Q1

D1 Q0

D0 Q3 Q2 x

y Q3 Q1

НУЛП 20182019 н.р.

№

0

1

2

3

4

5

6

7

Позначення

ai

a0

a0

a1

a1

a2

a2

a3

a3

Q3

0

0

0

0

0

0

1

1

Код

Q2 Q1

0

0

0

0

0

1

0

1

1

0

1

0

0

0

0

0

Q3

0

0

0

1

{Y}

λ

2

1

КСх - комбінаційна схема

ПА - пам’ять автомата

δ – функція переходів

λ – функція виходів

0

1

2

3

{A}

δ

{X}

№

КСх

ПА

Код

Q2 Q1

0

0

0

1

1

0

0

0

Q0

1

0

0

0

Вихідні

сигнали

автомата

y

0

1

0

1

Наступний стан автомата

x

Q0

1

1

0

0

0

0

0

0

0

1

0

1

0

1

0

1

Позначення

aj

a1

a1

a2

a2

a3

a0

a0

a0

Глухов В.С. Комп'ютерна логіка

q3

0

0

0

0

1

0

0

0

Код

q2

q1

0

1

0

1

1

0

1

0

0

0

0

0

0

0

0

0

q0

0

0

0

0

0

1

1

1

D3

0

0

0

0

1

0

0

0

Сигнали

збудеження

тригерів

D2 D1

0

1

0

1

1

0

1

0

0

0

0

0

0

0

0

0

D0

0

0

0

0

0

1

1

1

156

157. Схема автомата

НУЛП 20182019 н.р.Глухов В.С. Комп'ютерна логіка

157

158. Автомат на Т-тригерах

КСхПА

δ

{X}

1

КСх - комбінаційна схема

ПА - пам’ять автомата

δ – функція переходів

λ – функція виходів

№

0

1

2

3

Попередній стан

автомата

Позначення

Код

ai

Q1 Q0

0

0

a0

0

1

a1

1

0

a2

1

1

a3

0

1

2

3

4

5

6

7

Вихідні

сигнали

автомата

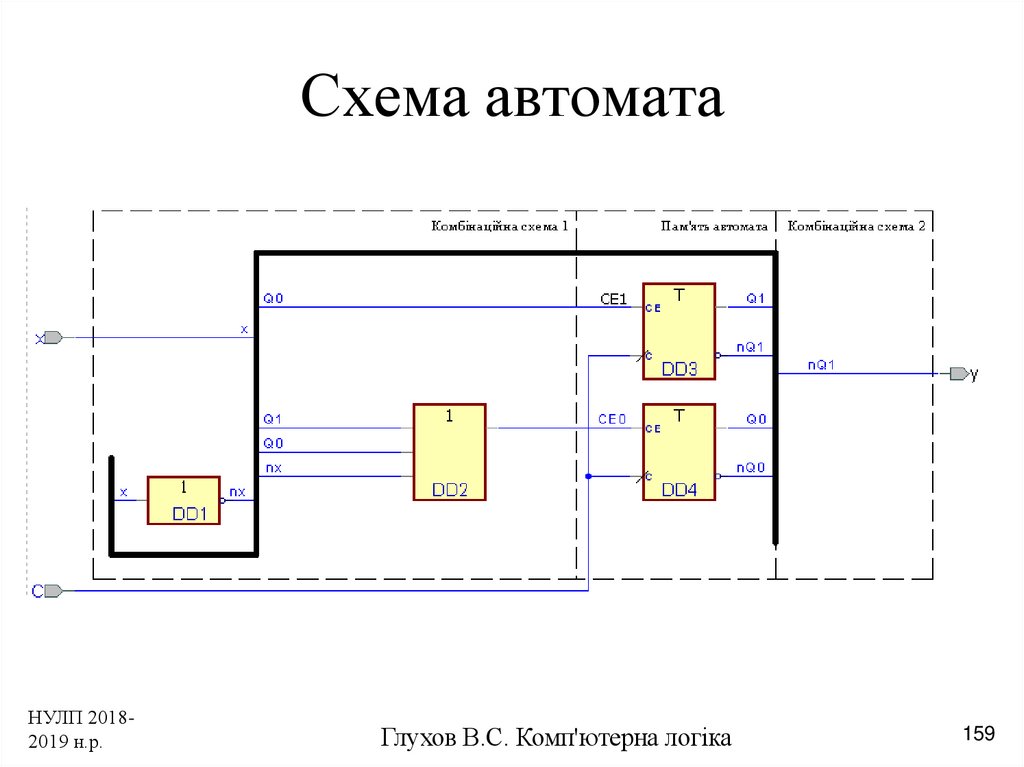

y