Similar presentations:

Программирование специализированных вычислительных устройств. ПЛИС

1.

2.

ИНТЕГРАЛЬНАЯ СХЕМА (ИС, интегральнаямикросхема, микросхема) – функционально

законченное

микроэлектронное

изделие,

представляющее собой совокупность электрически связанных между собой элементов

(транзисторов и др.), сформированных в

полупроводниковой

монокристаллической

пластине.

БОЛЬШАЯ ИНТЕГРАЛЬНАЯ СХЕМА (БИС) –

интегральная схема, содержащая тысячи

компонентов и выполняющая функции целого

узла электронной аппаратуры.

3.

ASIC–

Application-Specific

Integrated

Circuit

–

специализированные заказные интегральные схемы,

предназначенные для выполнения конкретной задачи в

конкретной предметной области

Особенности

все слои масок полностью заказные, могут быть использованы для

производства только этой конкретной СБИС

проектирование топологии каждого вентиля в ручную без

использования стандартных библиотек

критические пути проектируются практически вручную или с

использованием специального инструментария, управляемого

уникальными скриптами разработчика

Преимущества

наиболее высокую производительность и минимальную цену

кремния (меньший размер чипа) для конкретной разработки

Недостатками

длительное время разработки (годы для больших

процессоров), сложность и дороговизна процесса разработки,

а также наиболее высокий риск (ошибки и задержки)

4.

Программируемые логические интегральныесхемы (ПЛИС) – цифровая интегральная схема

состоящая из программируемых логических блоков и

соединений между ними

5.

Общепринятой оценкой логической ёмкостиПЛИС является число эквивалентных вентилей,

определяемое как среднее число вентилей «2И-НЕ»,

необходимых для реализации эквивалентного проекта на

ПЛИС и базовом матричном кристалле (БМК)

Эта оценка весьма условна, поскольку ПЛИС не

содержат вентилей «2И-НЕ» в чистом виде, однако для

проведения

сравнительного

анализа

различных

архитектур она вполне пригодна.

6.

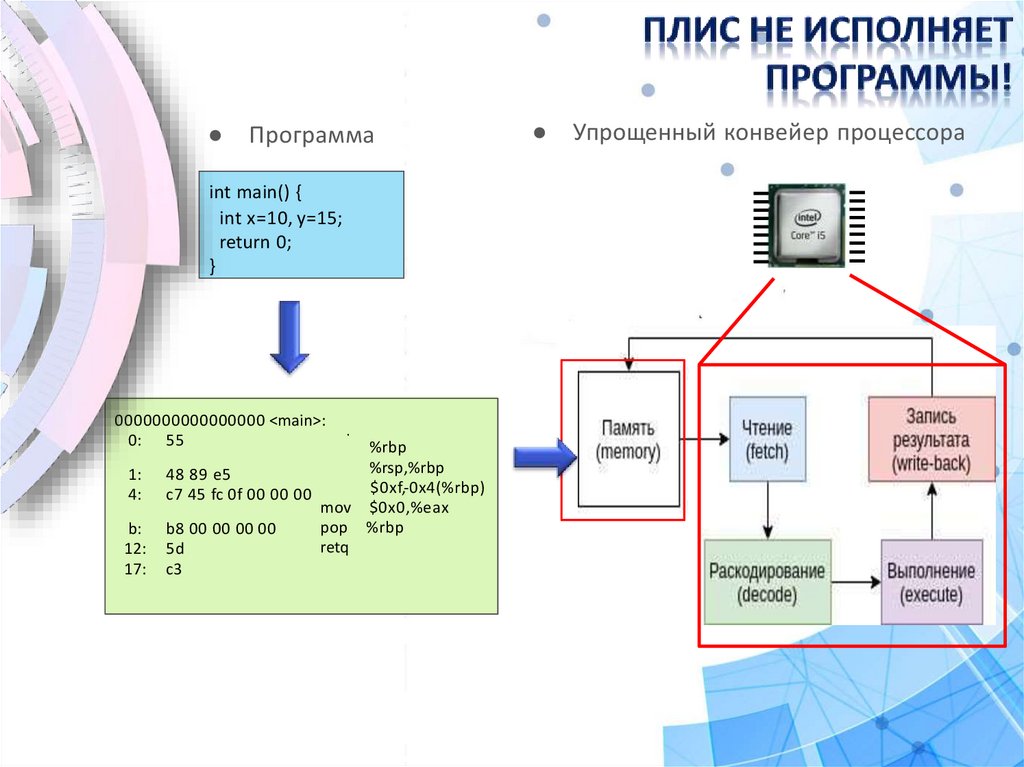

Программа

int main() {

int x=10, y=15;

return 0;

}

0000000000000000 <main>:

0: 55

push %rbp

1: 48 89 e5

mov %rsp,%rbp

4: c7 45 fc 0f 00 00 00 movl $0xf,-0x4(%rbp)

mov $0x0,%eax

pop %rbp

b: b8 00 00 00 00

retq

12: 5d

17: c3

Упрощенный конвейер процессора

7.

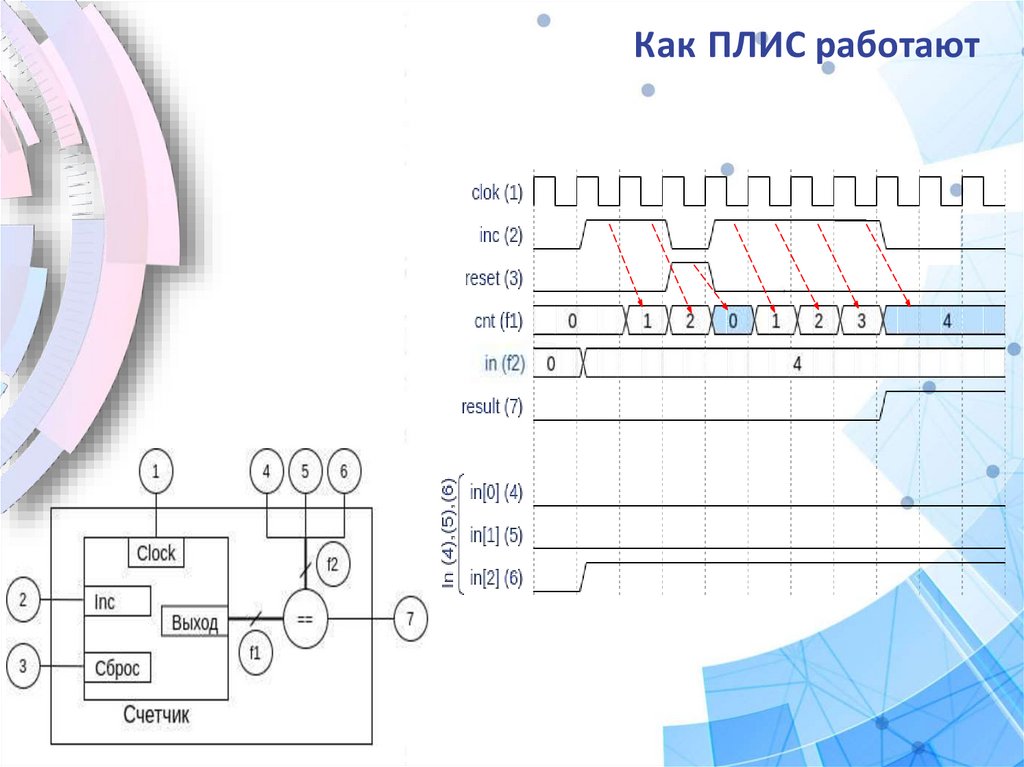

● Блоки внутри работают одновременно (параллельно)● Для работы блоков с памятью (регистров) нужен периодический

сигнал (clock)

● Частота этого сигнала напрямую влияет на производительность

8.

Схемотехника:

Цифровая схемотехника:

-- Компаратор. Сравнение входов.

На выходе “1” если входы

равны. “0” если не равны.

FPGA

-- Счетчик. Считает количество

тактов, когда был “1” на входе

“Inc.

“1” на входе “Сброс” сбрасывает

счетчик.

9.

Как ПЛИС работают10.

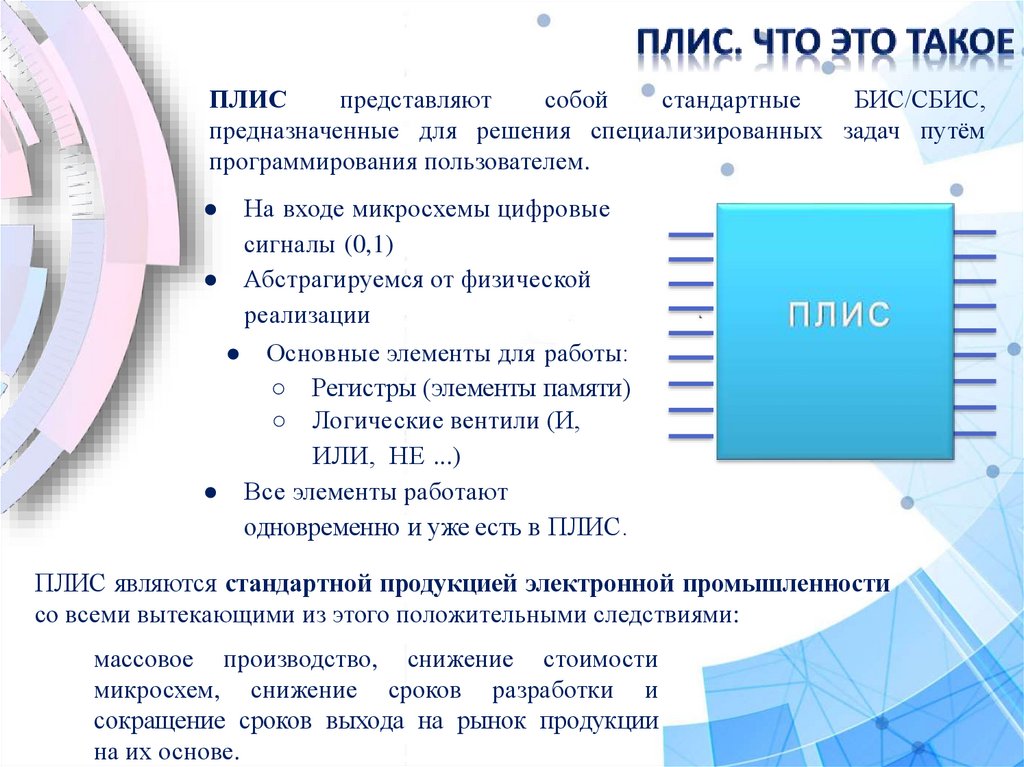

ПЛИСпредставляют

собой

стандартные

БИС/СБИС,

предназначенные для решения специализированных задач путём

программирования пользователем.

На входе микросхемы цифровые

сигналы (0,1)

● Абстрагируемся от физической

реализации

● Основные элементы для работы:

○ Регистры (элементы памяти)

○ Логические вентили (И,

ИЛИ, НЕ ...)

● Все элементы работают

одновременно и уже есть в ПЛИС.

ПЛИС являются стандартной продукцией электронной промышленности

со всеми вытекающими из этого положительными следствиями:

массовое производство, снижение стоимости

микросхем, снижение сроков разработки и

сокращение сроков выхода на рынок продукции

на их основе.

11.

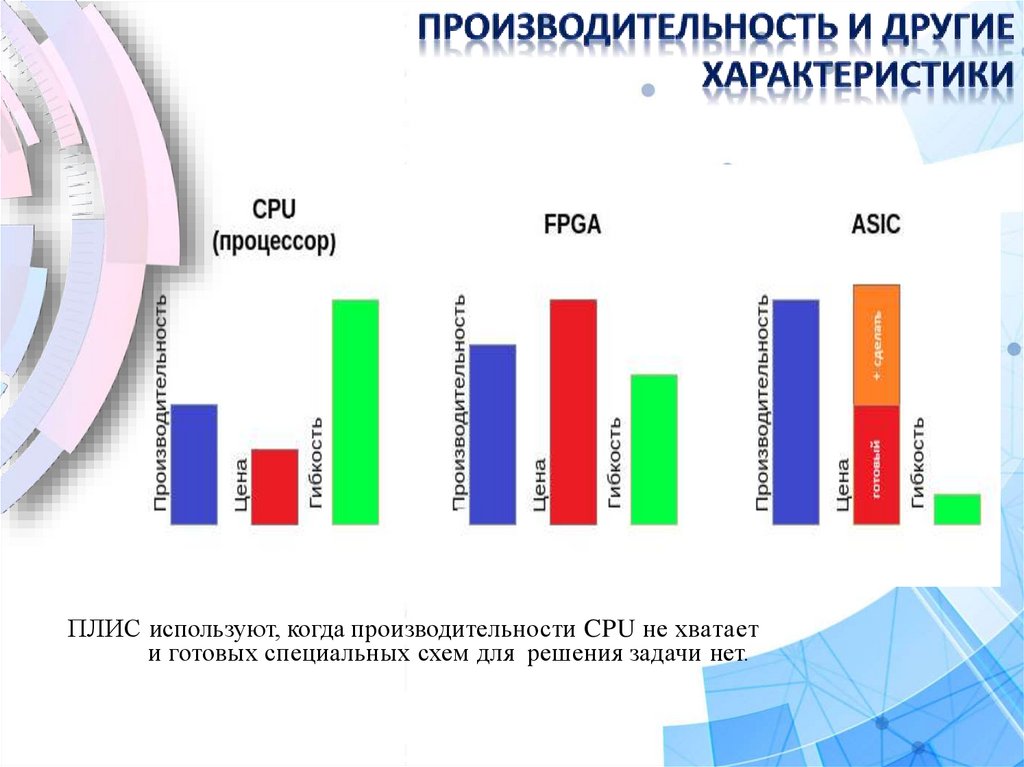

ПЛИС используют, когда производительности CPU не хватаети готовых специальных схем для решения задачи нет.

12.

FPGA реализуются с уровнем интеграции, близкой кмаксимальному. Это является достоинством МС. Это

обеспечивает

их

максимальные

функциональные

возможности.

Области применения FPGA:

- отработка прототипов блоков и систем при их

проектировании, даже если их конечная реализация

рассчитана на другие средства;

-создание конечной продукции для изделий не слишком

большой тиражности быстрыми и эффективными способами.

13.

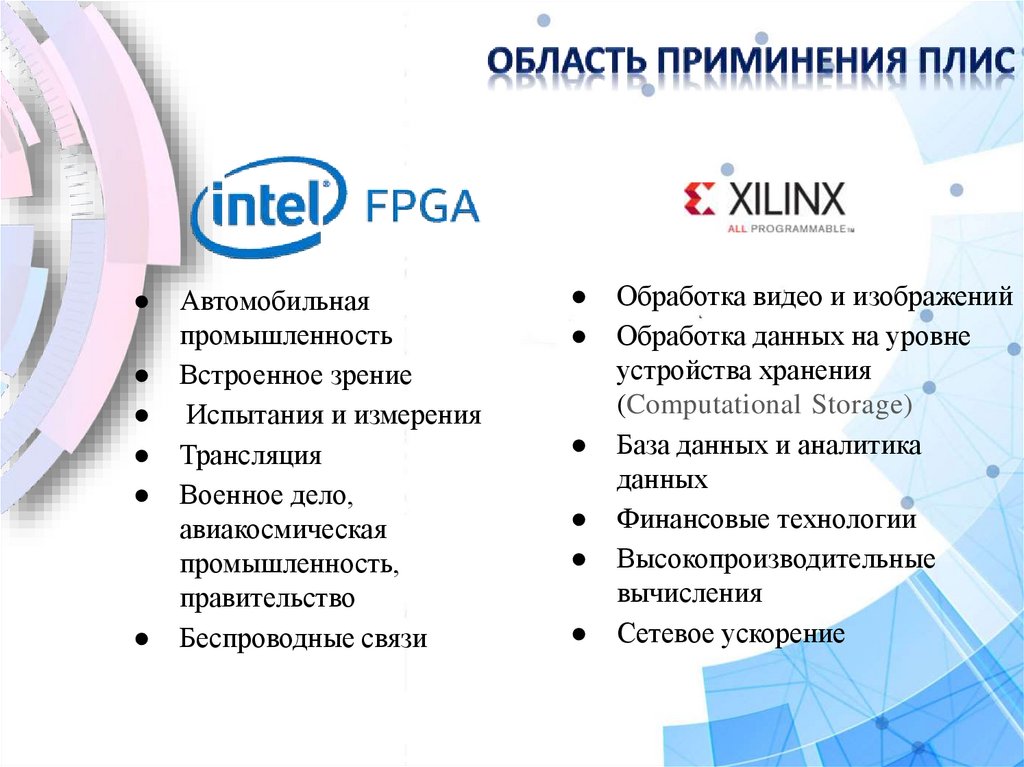

Автомобильная

промышленность

Встроенное зрение

Испытания и измерения

Трансляция

Военное дело,

авиакосмическая

промышленность,

правительство

Беспроводные связи

Обработка видео и изображений

Обработка данных на уровне

устройства хранения

(Computational Storage)

База данных и аналитика

данных

Финансовые технологии

Высокопроизводительные

вычисления

Сетевое ускорение

14.

ВозможностиПостроение реконфигурируемых систем: одна и та же

аппаратная

часть

может

выполнять

различные

преобразования после соответствующей перестройки.

Задачи логической эмуляции: система из микросхем

программируемой логики легко создается и модифицируется,

может работать с реальными сигналами и частотами.

Построение динамически реконфигурируемых систем: в

динамически реконфигурируемых системах уже имеется

(хранится) набор предварительно загруженных настроек,

быстро сменяющих друг друга соответственно требованиям

реализуемого алгоритма.

FPGA-процессоры:

FPGA-процессоры

могут давать хорошие результаты при

параллельной обработке данных, где

большое число переменных преобразуется

сходным образом.

15.

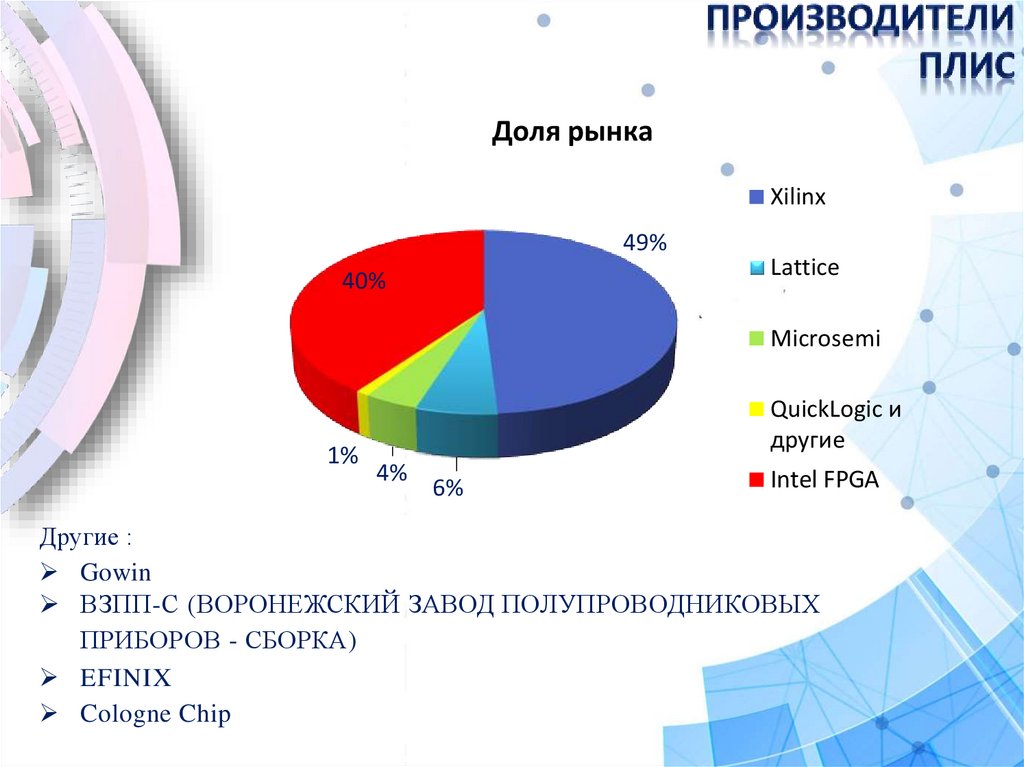

Доля рынкаXilinx

49%

40%

Lattice

Microsemi

1%

QuickLogic и

другие

4%

6%

Intel FPGA

Другие :

Gowin

ВЗПП-С (ВОРОНЕЖСКИЙ ЗАВОД ПОЛУПРОВОДНИКОВЫХ

ПРИБОРОВ - СБОРКА)

EFINIX

Cologne Chip

16.

Основные классификационные признаки ПЛИС:– уровень интеграции и связанная с ним

логическая сложность;

– архитектура (тип функциональных блоков,

характер системы межсоединений);

– число допустимых циклов программирования;

– тип памяти конфигурации («теневой» памяти);

– степень зависимости задержек сигналов от

путей их распространения;

– системные свойства;

– схемотехнология (КМОП, ТТЛШ и др.);

– однородность или гибридность (признак

наличия или отсутствия в микросхеме областей

с различными по методам проектирования

схемами, такими как ПЛИС, БМК, схемы на

стандартных ячейках).

17.

18.

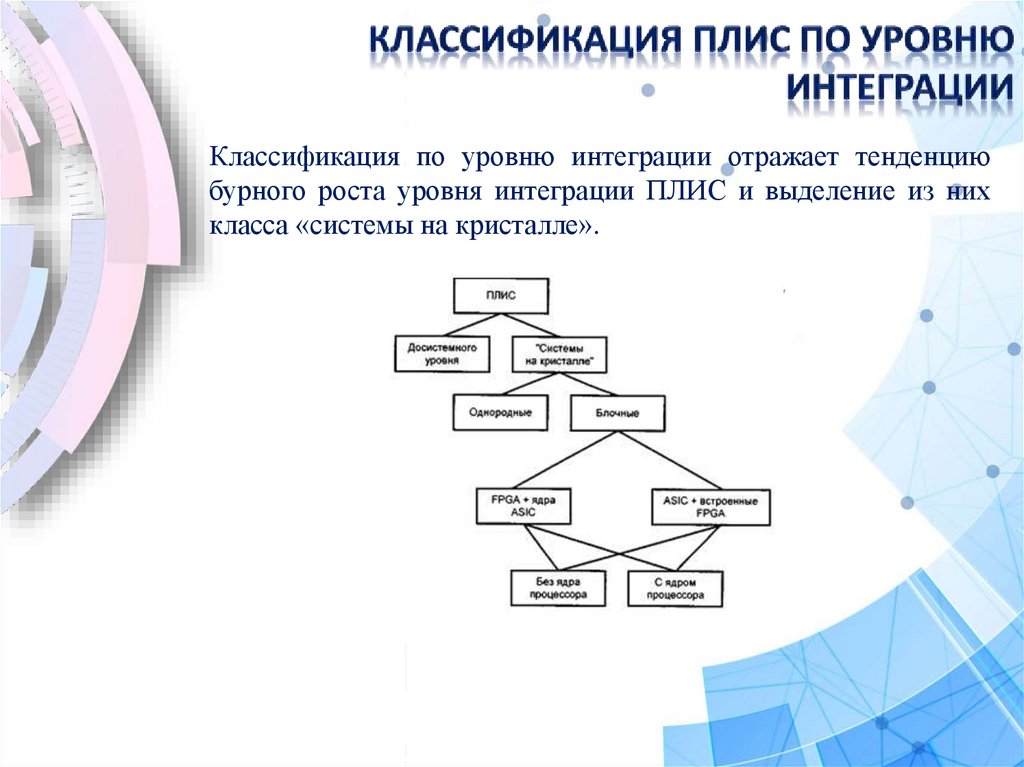

Классификация по уровню интеграции отражает тенденциюбурного роста уровня интеграции ПЛИС и выделение из них

класса «системы на кристалле».

19.

В классификации по архитектуре ПЛИС разделенына 4 основных класса:

20.

SPLD (Simple Programmable Logic Devices) – простыепрограммируемые логические устройства.

По архитектуре эти ПЛИС делятся на 2 подкласса:

– программируемые логические матрицы ПЛМ

(PLA, Programmable Logic Arrays)

– программируемая матричная логика ПМЛ (PAL,

Programmable Arrays Logic, или GAL, Generic Array

Logic).

Оба эти подкласса микросхем реализуют ДНФ

переключательных функций.

Основными блоками SPLD являются две матрицы:

– матрица элементов И;

– матрица элементов ИЛИ,

включённые последовательно.

21.

Во внутренней области FPGA базовой архитектуры построкам и столбцам размещаются идентичные функциональные

блоки ФБ (КЛБ, конфигурируемые логические блоки), между

которыми проходят трассы межсоединений.

В состав функционального

блоки входят:

• функциональный (логический)

преобразователь (ФП);

• триггер (регистр RG);

• мультиплексоры

(MUXs),

играющие

роль

средств

конфигурирования ФБ.

При конфигурировании FPGA функциональные (логические) блоки

настраиваются на выполнение требуемых операций, а система соединений на требуемые связи между элементами и блоками.

22.

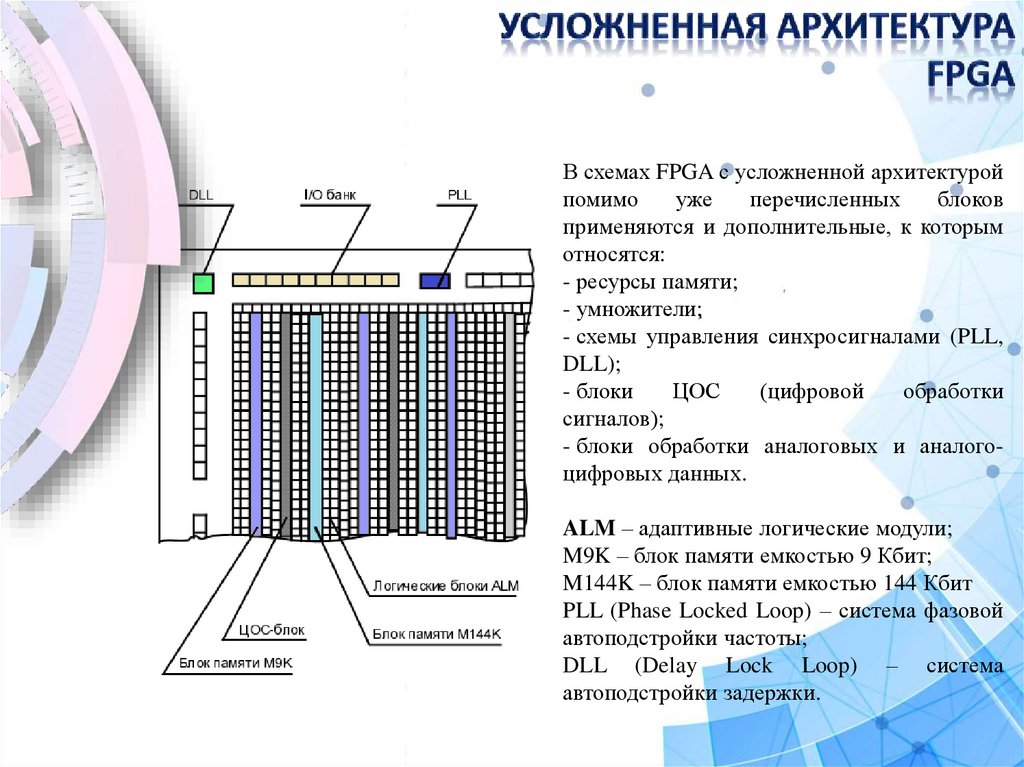

В схемах FPGA с усложненной архитектуройпомимо

уже

перечисленных

блоков

применяются и дополнительные, к которым

относятся:

- ресурсы памяти;

- умножители;

- схемы управления синхросигналами (PLL,

DLL);

- блоки

ЦОС

(цифровой

обработки

сигналов);

- блоки обработки аналоговых и аналогоцифровых данных.

ALM – адаптивные логические модули;

M9K – блок памяти емкостью 9 Кбит;

M144K – блок памяти емкостью 144 Кбит

PLL (Phase Locked Loop) – система фазовой

автоподстройки частоты;

DLL (Delay Lock Loop) – система

автоподстройки задержки.

23.

Решаемые задачи:– определить элементный базис ПЛИС – достаточно

развитый, чтобы реализовать необходимые функции

целевых устройств, и достаточно простой, чтобы

время расчётов на инструментальном компьютере

при синтезе не было чрезмерным;

– разработать математические методы синтеза

устройств

(в выбранном базисе), декомпозиции, компиляции,

межэлементной трассировки, функционального

моделирования и временного анализа;

– создать

интегрированную

систему

проектирования цифровых устройств на ПЛИС.

24.

Программирование ПЛИС первого поколения – микросхемтипа PLA (программируемые логические матрицы – ПЛМ)

осуществлялось в кодах через заполнение таблицы

истинности.

Позже появились микросхемы типа PAL и стали применяться

языки программирования ассемблерного типа, как например

PALASM.

В настоящее время БИС программируемой логики имеют

степень

интеграции

до

нескольких

миллионов

эквивалентных вентилей, быстродействие (ввода-вывода) до

500 МГц и более.

В качестве средств описания проектов применяются:

– языки высокого уровня типа HDL (Hardware

Description Language), например, AlteraHDL (AHDL),

VHDL, Verilog HDL и

– автоматизированные средства схемного ввода.

25.

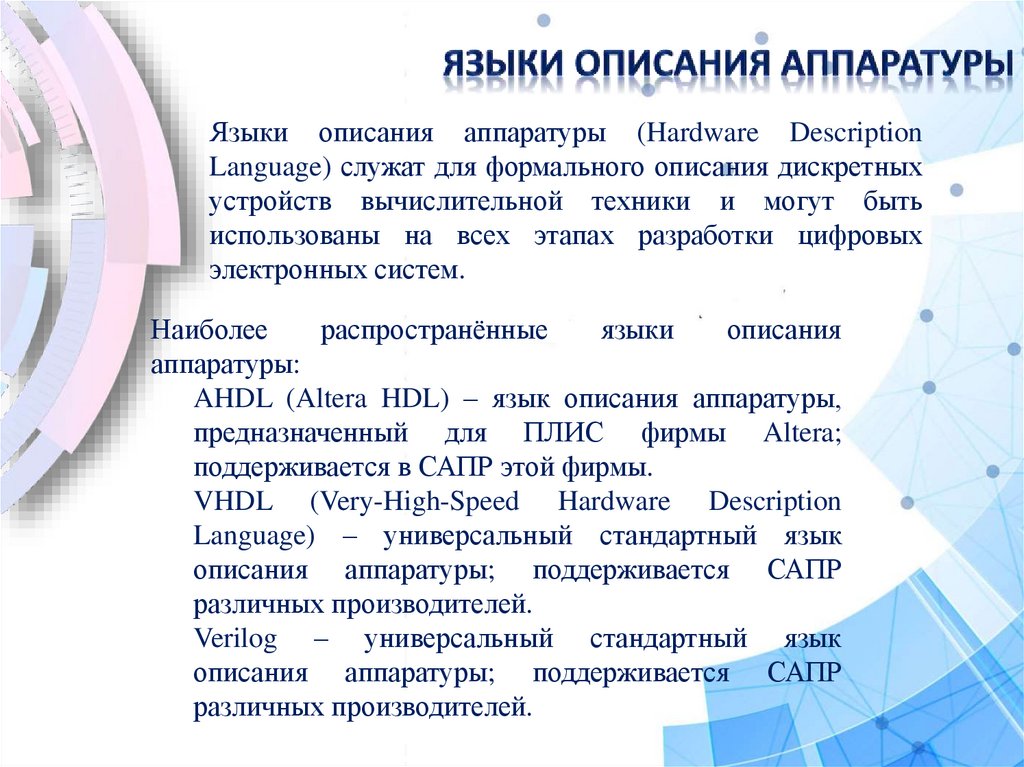

Языки описания аппаратуры (Hardware DescriptionLanguage) служат для формального описания дискретных

устройств вычислительной техники и могут быть

использованы на всех этапах разработки цифровых

электронных систем.

Наиболее

распространённые

языки

описания

аппаратуры:

AHDL (Altera HDL) – язык описания аппаратуры,

предназначенный для ПЛИС фирмы Altera;

поддерживается в САПР этой фирмы.

VHDL (Very-High-Speed Hardware Description

Language) – универсальный стандартный язык

описания аппаратуры; поддерживается САПР

различных производителей.

Verilog – универсальный стандартный язык

описания аппаратуры; поддерживается САПР

различных производителей.

26.

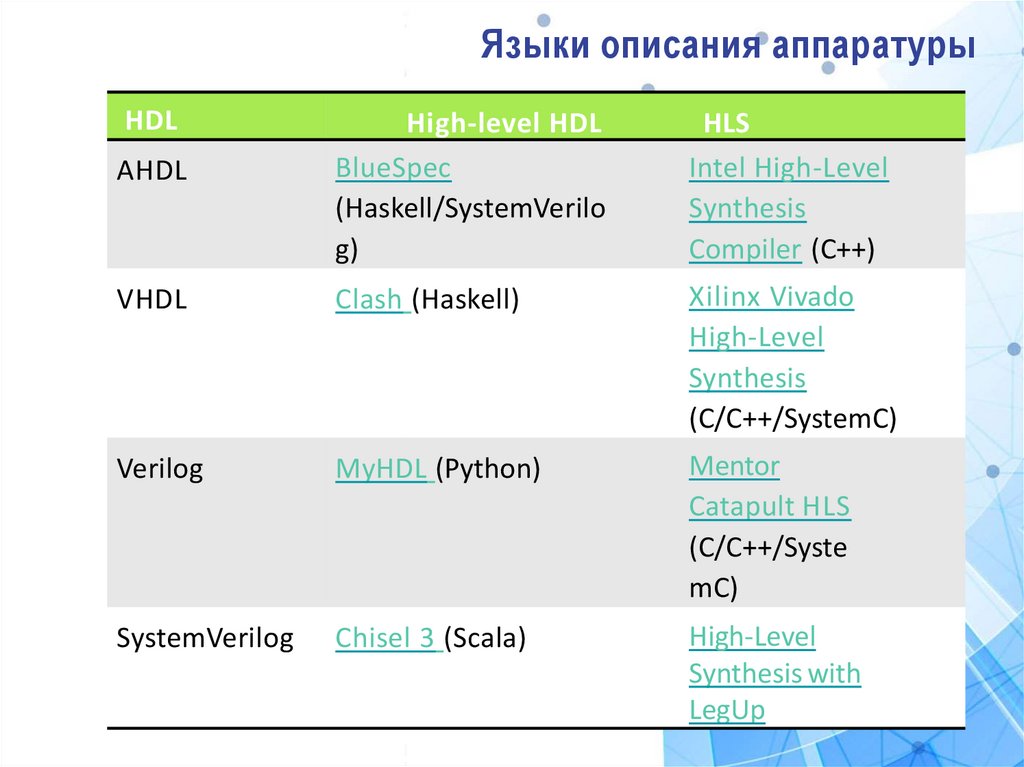

Языки описания аппаратурыHDL - Hardware

Description

Language

Не требует генерации;

cycle accurate.

Не только для FPGA, но и

для описания других

схем и процессов (ASIC);

Чтобы схема работала,

нужно писать

“правильно”. И этой

информации нет в

стандарте языка, зависит

от вендора.

High-level HDL

Генерирует Verilog;

cycle accurate.

Как HDL, но

дополнительные

абстракции;

Дополнительные

проверки и ограничения

помогающие

разработчику;

Очень быстрая

функциональная

симуляция.

HLS - High-level

Synthesis

Генерирует Verilog;

Уровень выше RTL (не

cycle accurate).

Time to market;

Переносимость кода

между платформами;

Абстракция над

интерфейсами (легко

менять интерфейсы);

Очень быстрая

функциональная

симуляция.

27.

Языки описания аппаратурыHDL

High-level HDL

BlueSpec

(Haskell/SystemVerilo

g)

HLS

Intel High-Level

Synthesis

Compiler (C++)

VHDL

Clash (Haskell)

Xilinx Vivado

High-Level

Synthesis

(C/C++/SystemC)

Verilog

MyHDL (Python)

Mentor

Catapult HLS

(C/C++/Syste

mC)

SystemVerilog

Chisel 3 (Scala)

High-Level

Synthesis with

LegUp

AHDL

28.

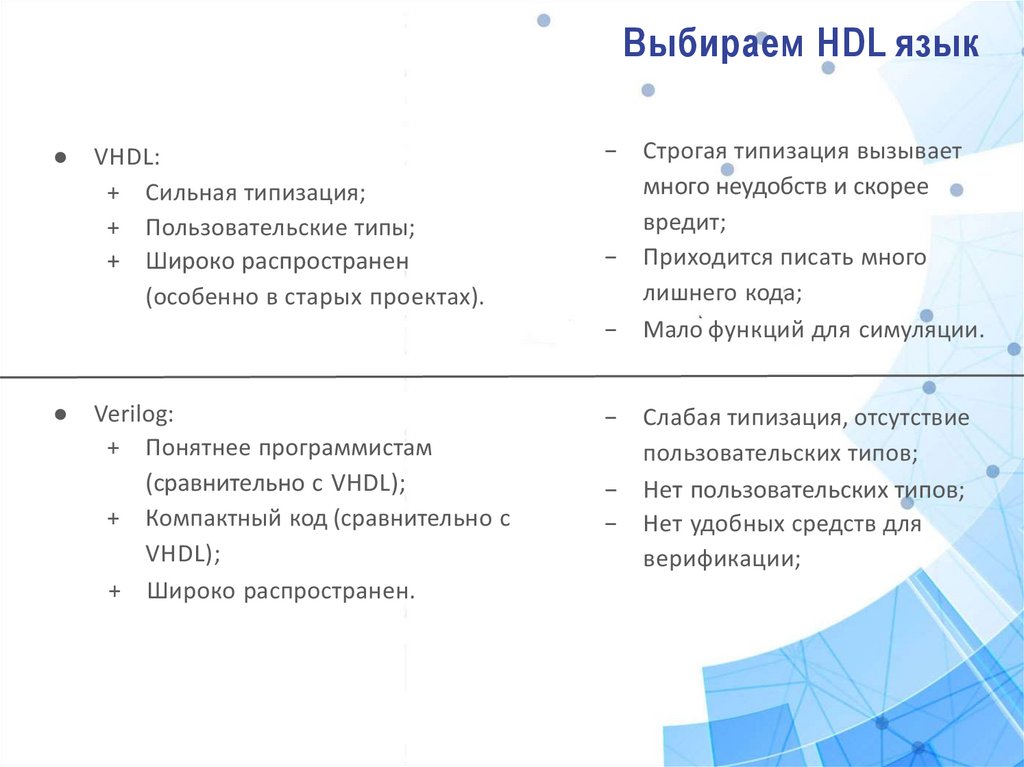

Выбираем HDL языкVHDL:

+ Сильная типизация;

+ Пользовательские типы;

+ Широко распространен

(особенно в старых проектах).

−

−

−

Verilog:

+ Понятнее программистам

(сравнительно с VHDL);

+ Компактный код (сравнительно с

VHDL);

+ Широко распространен.

−

−

−

Строгая типизация вызывает

много неудобств и скорее

вредит;

Приходится писать много

лишнего кода;

Мало функций для симуляции.

Слабая типизация, отсутствие

пользовательских типов;

Нет пользовательских типов;

Нет удобных средств для

верификации;

29.

Выбираем языкSystemVerilog (расширение Verilog):

+ Пользовательские типы

+ Огромное несинтезируемое

подмножество для верификации

+ Удобно писать легко читать

+ Поддержка во многих средствах

проектирования:

−

−

−

Производитель ПЛИС Среда проектирования

ISE (старые семейства)

Xilinx

Vivado

Intel

Quartus

MicroSemi

Libero (Synplify Pro)

Lattice

Diamond (Synplify Pro)

Слабая типизация (легко чтото не туда присвоить);

Сложно получить “скелет” и

начать отлаживать;

Много условностей, как

можно, а как нельзя

использовать конструкции.

Поддержка SV

30.

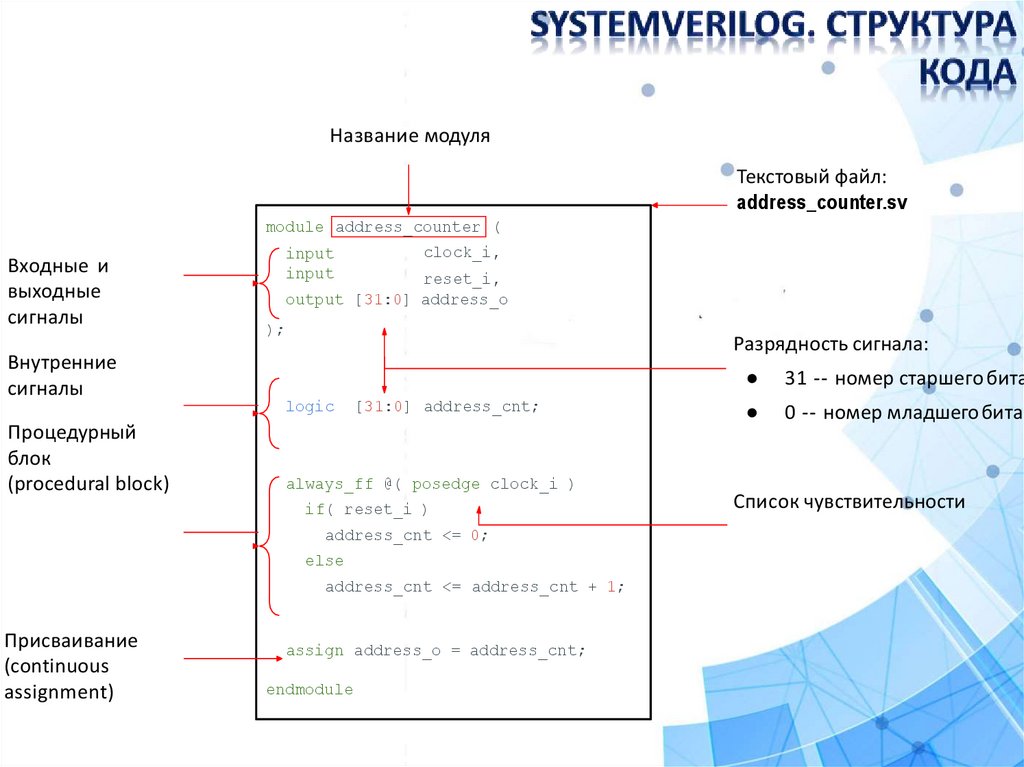

Название модуляТекстовый файл:

address_counter.sv

module address_counter (

Входные и

выходные

сигналы

Внутренние

сигналы

Процедурный

блок

(procedural block)

input

input

clock_i,

reset_i,

output [31:0] address_o

);

Разрядность сигнала:

logic

[31:0] address_cnt;

31 -- номер старшего бита

0 -- номер младшегобита

always_ff @( posedge clock_i )

if( reset_i )

address_cnt <= 0;

else

address_cnt <= address_cnt + 1;

Присваивание

(continuous

assignment)

assign address_o = address_cnt;

endmodule

Список чувствительности

31.

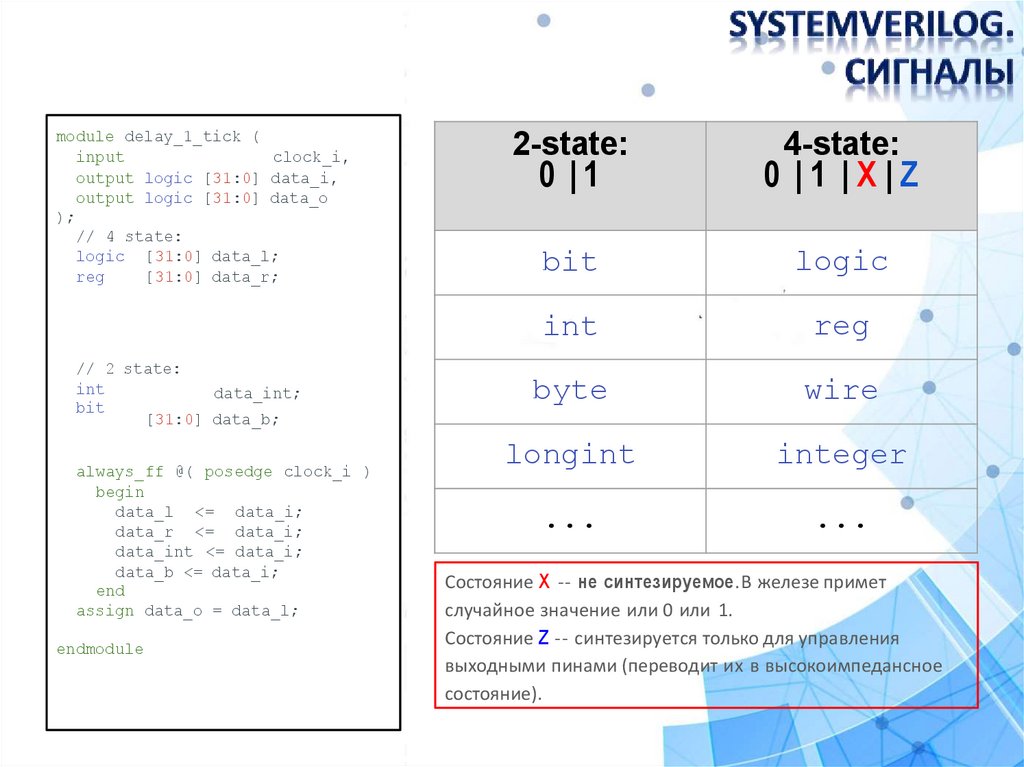

module delay_1_tick (input

clock_i,

output logic [31:0] data_i,

output logic [31:0] data_o

);

// 4 state:

logic [31:0] data_l;

reg

[31:0] data_r;

// 2 state:

int

data_int;

bit

[31:0] data_b;

always_ff @( posedge clock_i )

begin

data_l <= data_i;

data_r <= data_i;

data_int <= data_i;

data_b <= data_i;

end

assign data_o = data_l;

endmodule

2-state:

4-state:

0 |1

0 |1 |X|Z

bit

logic

int

reg

byte

wire

longint

integer

...

...

Состояние X -- не синтезируемое.В железе примет

случайное значение или 0 или 1.

Состояние Z -- синтезируется только для управления

выходными пинами (переводит их в высокоимпедансное

состояние).

32.

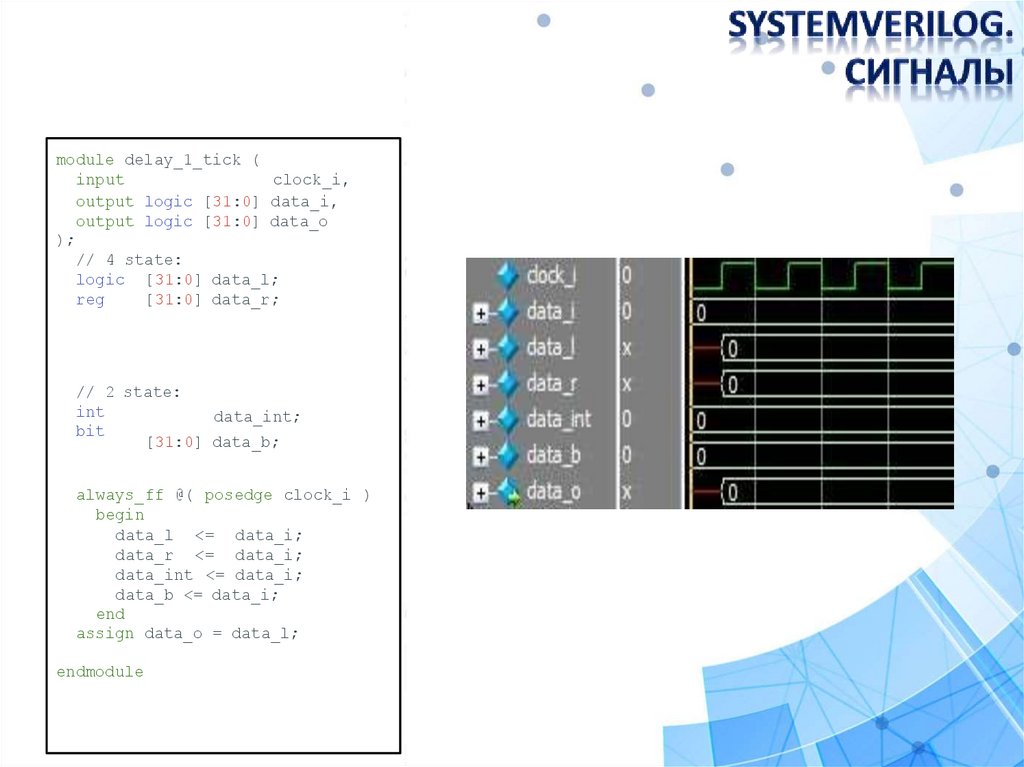

module delay_1_tick (input

clock_i,

output logic [31:0] data_i,

output logic [31:0] data_o

);

// 4 state:

logic [31:0] data_l;

reg

[31:0] data_r;

// 2 state:

int

data_int;

bit

[31:0] data_b;

always_ff @( posedge clock_i )

begin

data_l <= data_i;

data_r <= data_i;

data_int <= data_i;

data_b <= data_i;

end

assign data_o = data_l;

endmodule

33.

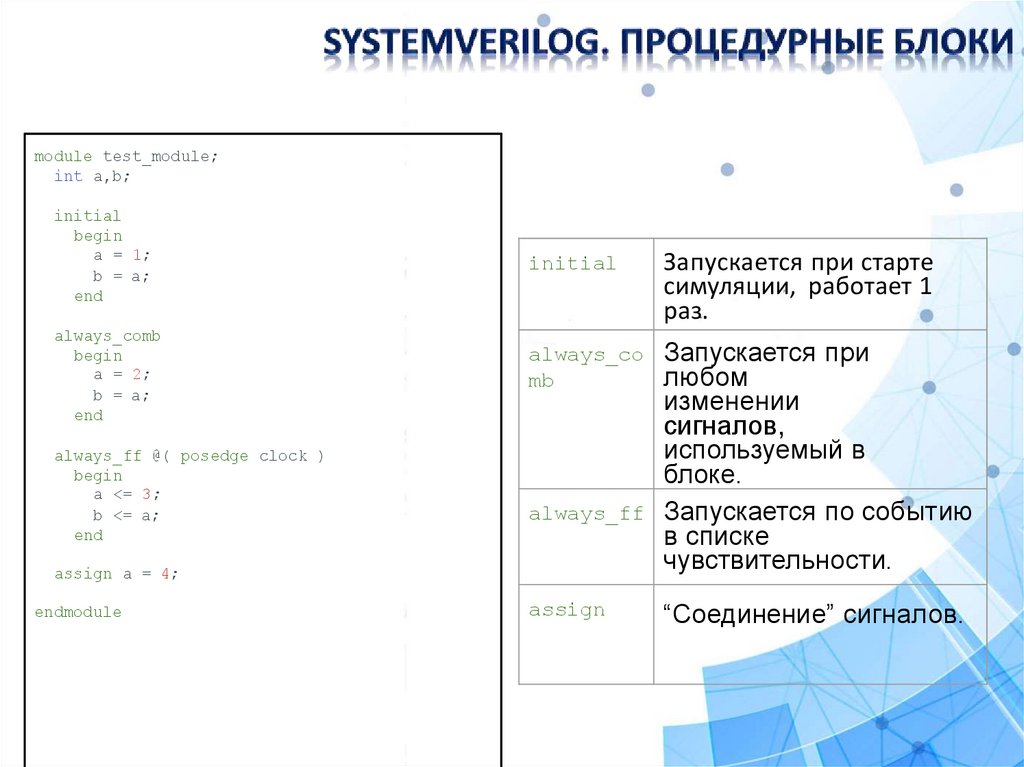

module test_module;int a,b;

initial

begin

a = 1;

b = a;

end

always_comb

begin

a = 2;

b = a;

end

always_ff @( posedge clock )

begin

a <= 3;

b <= a;

end

initial

Запускается при старте

симуляции, работает 1

раз.

always_co

mb

Запускается при

любом

изменении

сигналов,

используемый в

блоке.

Запускается по событию

в списке

чувствительности.

always_ff

assign a = 4;

endmodule

assign

“Соединение” сигналов.

34.

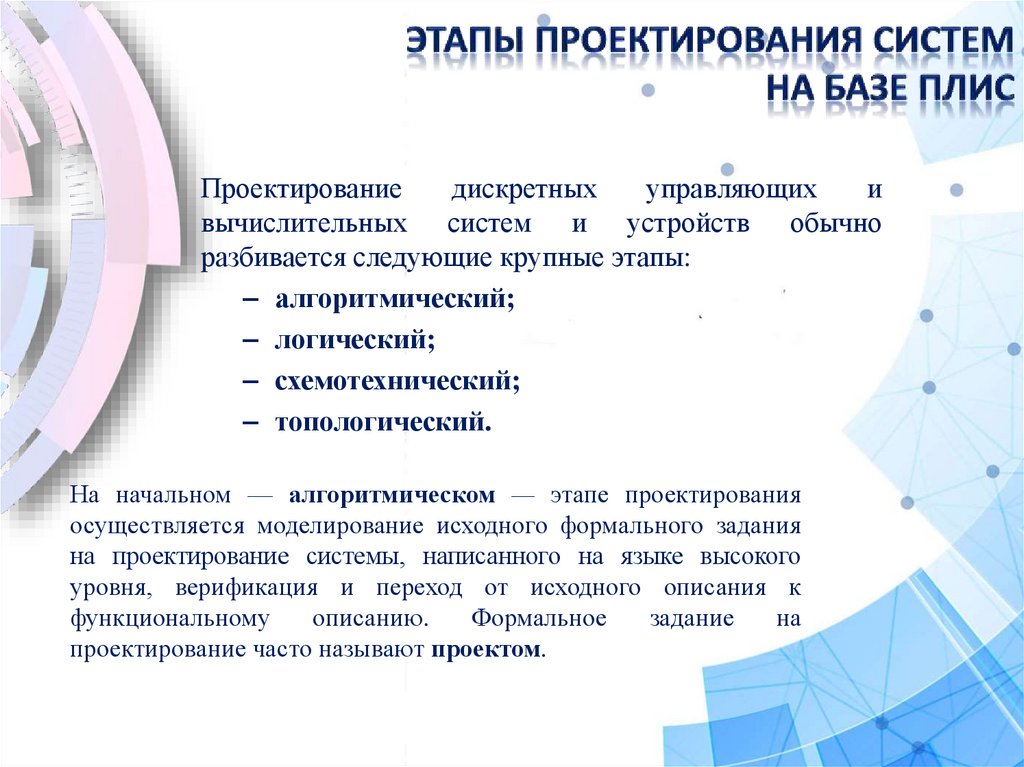

Проектированиедискретных

управляющих

и

вычислительных систем и устройств обычно

разбивается следующие крупные этапы:

– алгоритмический;

– логический;

– схемотехнический;

– топологический.

На начальном — алгоритмическом — этапе проектирования

осуществляется моделирование исходного формального задания

на проектирование системы, написанного на языке высокого

уровня, верификация и переход от исходного описания к

функциональному

описанию.

Формальное

задание

на

проектирование часто называют проектом.

35.

На этапе логического проектирования проект детализируется –решаются задачи синтеза логических схем в заданных

технологических базисах, проводится моделирование схем на

логическом (0, 1) уровне, строятся тесты.

Последующие этапы проектирования определяются

элементным базисом: если устройство реализуется в виде

отдельной БИС (большой интегральной схемы) или СБИС

(сверхбольшой интегральной схемы), то решаются задачи

схемотехнического и топологического проектирования

кристаллов, если же устройство реализуется на

стандартных,

уже

выпускаемых

промышленностью

микросхемах, то дополнительно решаются задачи

проектирования печатных плат и т. д.

36.

Начальныеэтапы

алгоритмического

и

логического

проектирования являются определяющими. Именно на данных

этапах определяются основные характеристики систем и

устройств:

– сложность,

– быстродействие,

– тестопригодность.

Использование ПЛИС, выполненных в виде СБИС, требует

решения специфических задач «трансляции» исходных

алгоритмических описаний (описаний логических схем) в

технологический

формат

файла

программирования

микросхемы либо формат файла описания конфигурации

ПЛИС.

Если цифровая система не может быть реализована на одной

ПЛИС,

то

приходится

решать

задачу

разбиения

(декомпозиции) проекта на сеть взаимосвязанных ПЛИС.

programming

programming