Similar presentations:

Verilog HDL: введение и лексические соглашения

1.

Verilog HDL: введение илексические соглашения

Полное практическое руководство:

синтаксис, числа, строки,

операторы, идентификаторы,

ключевые слова, системные имена

и директивы компилятора

2.

Содержание• 1. Введение в Verilog HDL

• 2. Лексические соглашения

– 2.1 Операторы

– 2.2 Пробелы и комментарии

– 2.3 Числа

– 2.4 Строки

– 2.5 Идентификаторы, ключевые слова,

системные имена

– 2.5.1 Идентификаторы

– 2.5.2 Ключевые слова

3.

Оригинальное содержание (из источника)4.

Что такое Verilog HDL?• Язык описания аппаратуры (HDL)

– Описывает поведение и структуру цифровых

схем

– Используется для моделирования (симуляции)

и синтеза (построения логики)

• Где применяется

– ASIC, FPGA, SoC, IP-ядра, верификация и

тестбенчи

• Стандарты

– IEEE 1364-1995/2001/2005 (Verilog) и

5.

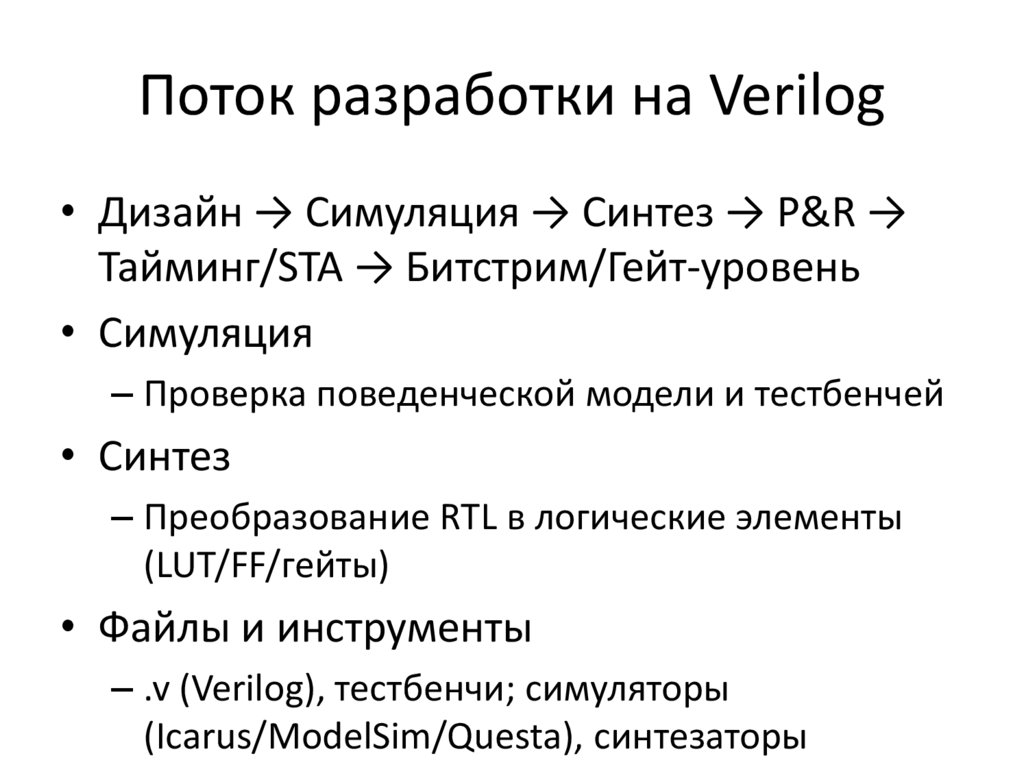

Поток разработки на Verilog• Дизайн → Симуляция → Синтез → P&R →

Тайминг/STA → Битстрим/Гейт-уровень

• Симуляция

– Проверка поведенческой модели и тестбенчей

• Синтез

– Преобразование RTL в логические элементы

(LUT/FF/гейты)

• Файлы и инструменты

– .v (Verilog), тестбенчи; симуляторы

(Icarus/ModelSim/Questa), синтезаторы

6.

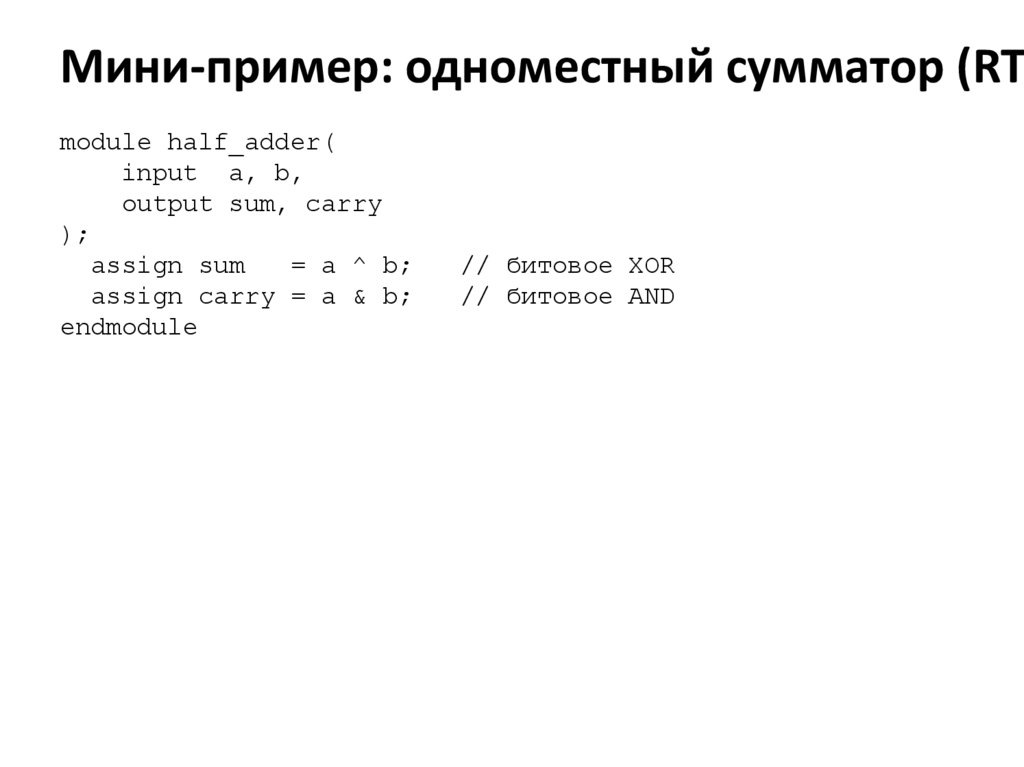

Мини-пример: одноместный сумматор (RTmodule half_adder(

input a, b,

output sum, carry

);

assign sum

= a ^ b;

assign carry = a & b;

endmodule

// битовое XOR

// битовое AND

7.

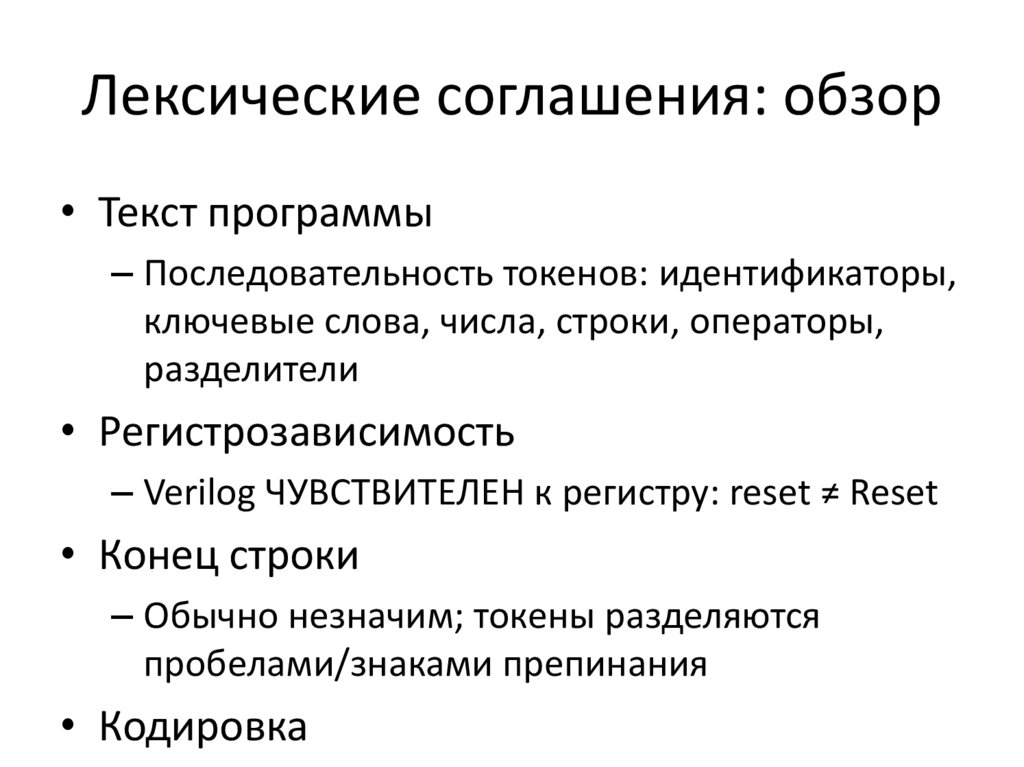

Лексические соглашения: обзор• Текст программы

– Последовательность токенов: идентификаторы,

ключевые слова, числа, строки, операторы,

разделители

• Регистрозависимость

– Verilog ЧУВСТВИТЕЛЕН к регистру: reset ≠ Reset

• Конец строки

– Обычно незначим; токены разделяются

пробелами/знаками препинания

• Кодировка

8.

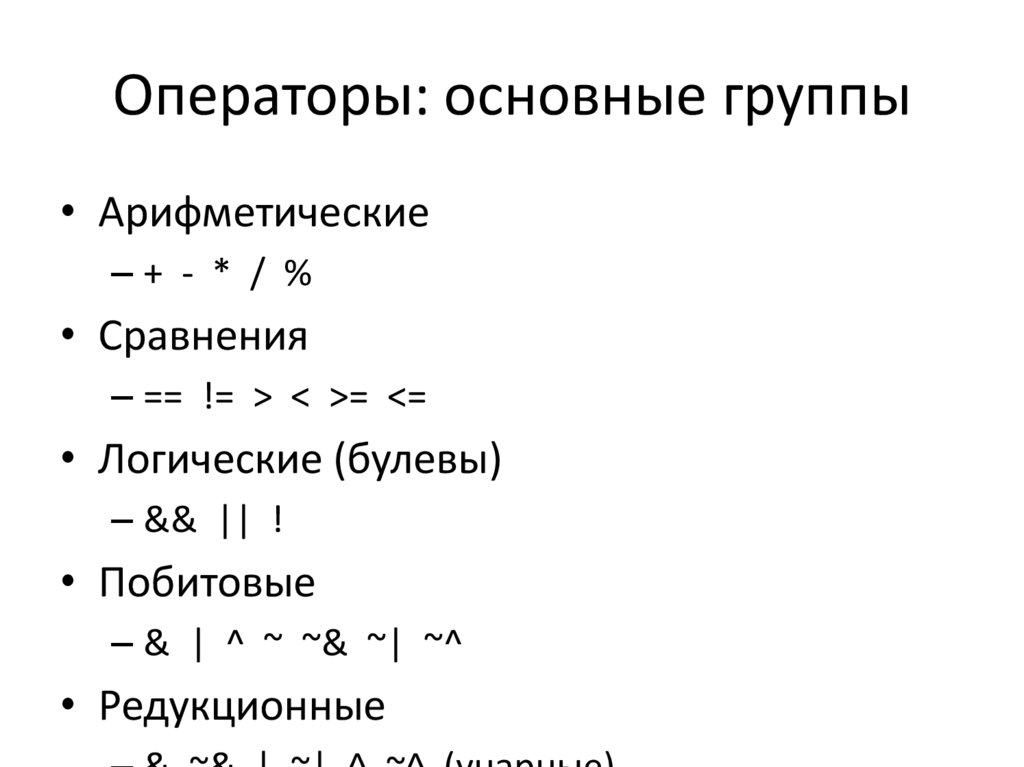

Операторы: основные группы• Арифметические

–+ - * / %

• Сравнения

– == != > < >= <=

• Логические (булевы)

– && || !

• Побитовые

– & | ^ ~ ~& ~| ~^

• Редукционные

9.

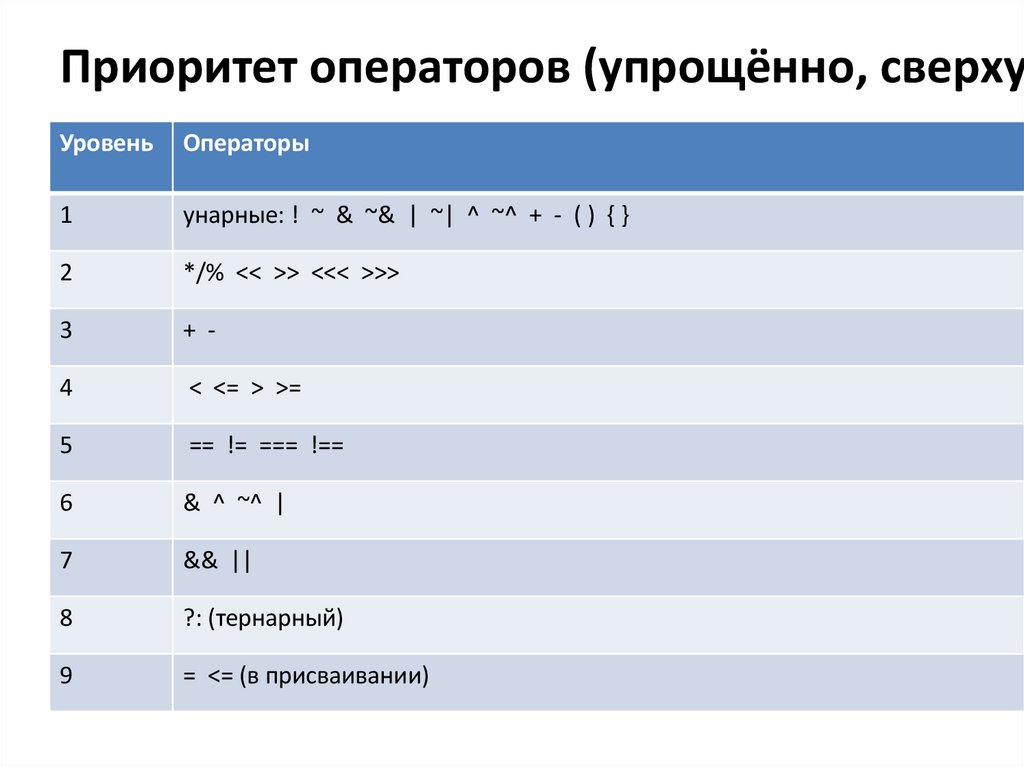

Приоритет операторов (упрощённо, сверхуУровень

Операторы

1

унарные: ! ~ & ~& | ~| ^ ~^ + - ( ) { }

2

*/% << >> <<< >>>

3

+ -

4

< <= > >=

5

== != === !==

6

& ^ ~^ |

7

&& ||

8

?: (тернарный)

9

= <= (в присваивании)

10.

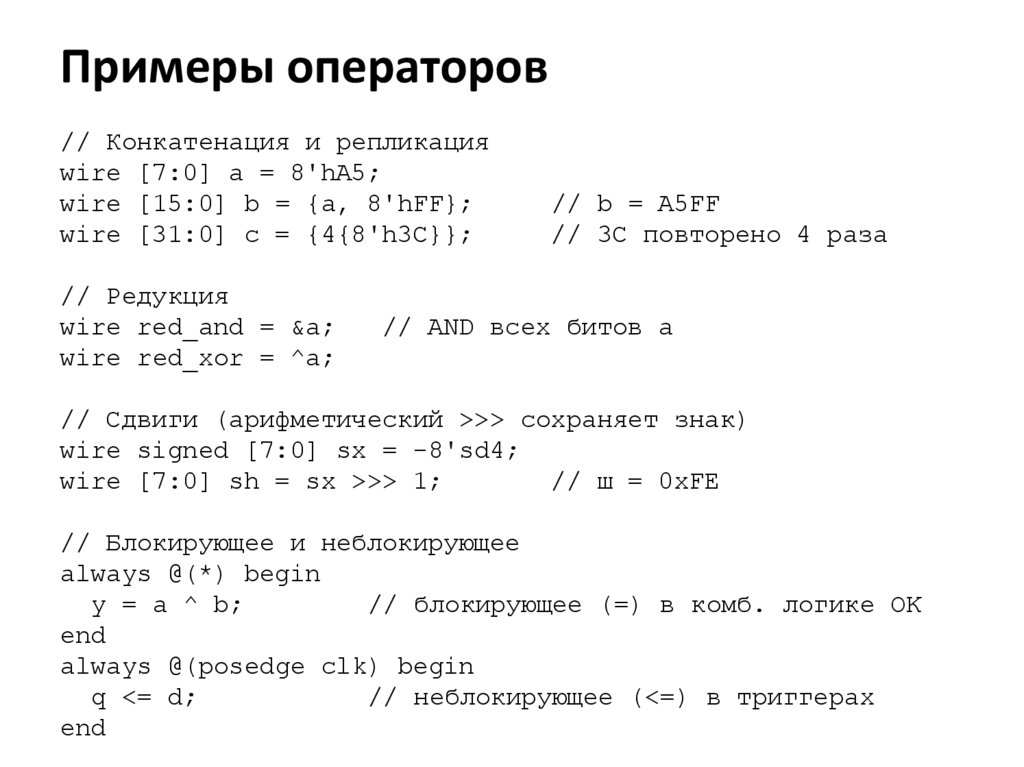

Примеры операторов// Конкатенация и репликация

wire [7:0] a = 8'hA5;

wire [15:0] b = {a, 8'hFF};

wire [31:0] c = {4{8'h3C}};

// Редукция

wire red_and = &a;

wire red_xor = ^a;

// b = A5FF

// 3C повторено 4 раза

// AND всех битов a

// Сдвиги (арифметический >>> сохраняет знак)

wire signed [7:0] sx = -8'sd4;

wire [7:0] sh = sx >>> 1;

// ш = 0xFE

// Блокирующее и неблокирующее

always @(*) begin

y = a ^ b;

// блокирующее (=) в комб. логике OK

end

always @(posedge clk) begin

q <= d;

// неблокирующее (<=) в триггерах

end

11.

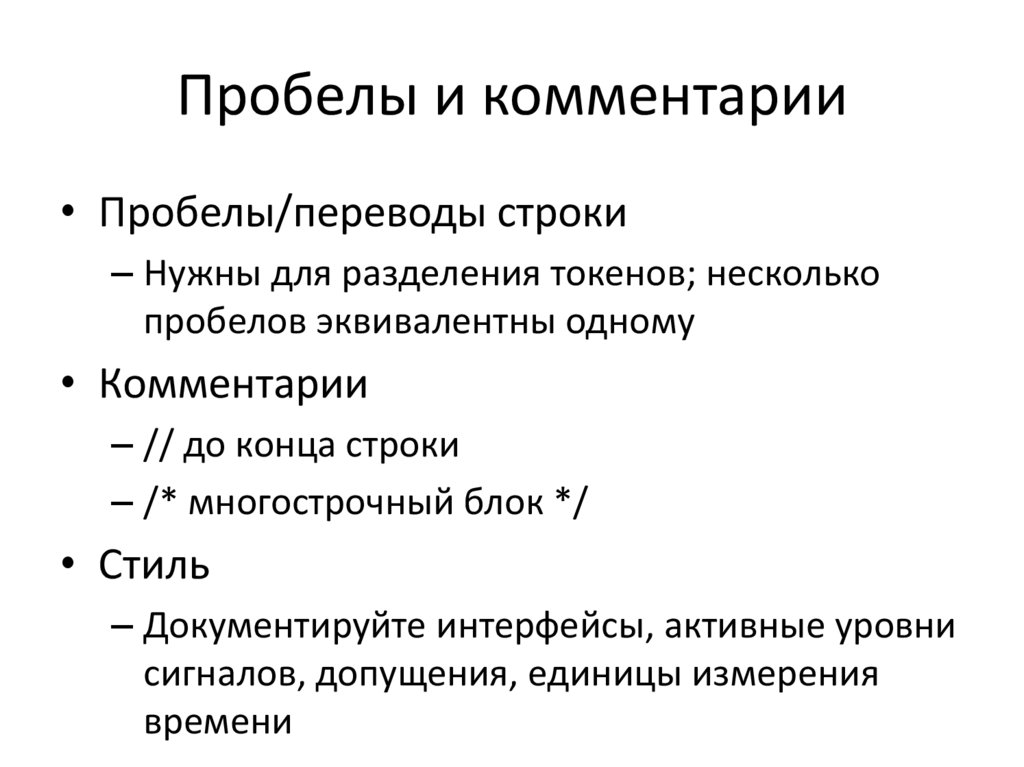

Пробелы и комментарии• Пробелы/переводы строки

– Нужны для разделения токенов; несколько

пробелов эквивалентны одному

• Комментарии

– // до конца строки

– /* многострочный блок */

• Стиль

– Документируйте интерфейсы, активные уровни

сигналов, допущения, единицы измерения

времени

12.

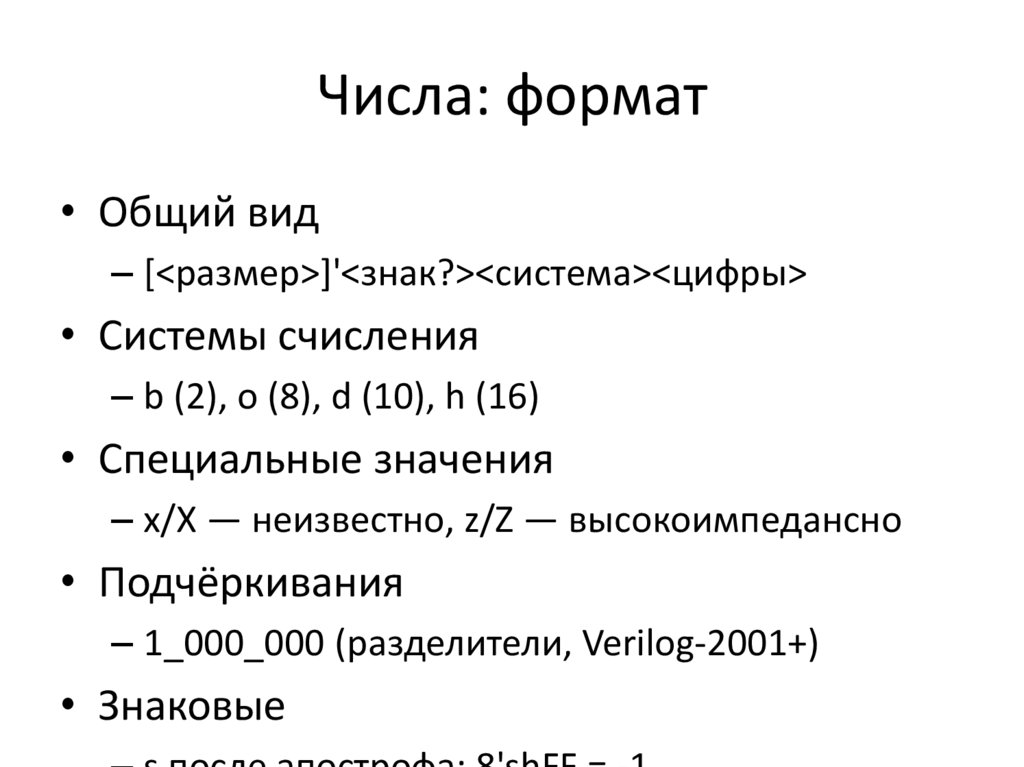

Числа: формат• Общий вид

– [<размер>]'<знак?><система><цифры>

• Системы счисления

– b (2), o (8), d (10), h (16)

• Специальные значения

– x/X — неизвестно, z/Z — высокоимпедансно

• Подчёркивания

– 1_000_000 (разделители, Verilog-2001+)

• Знаковые

13.

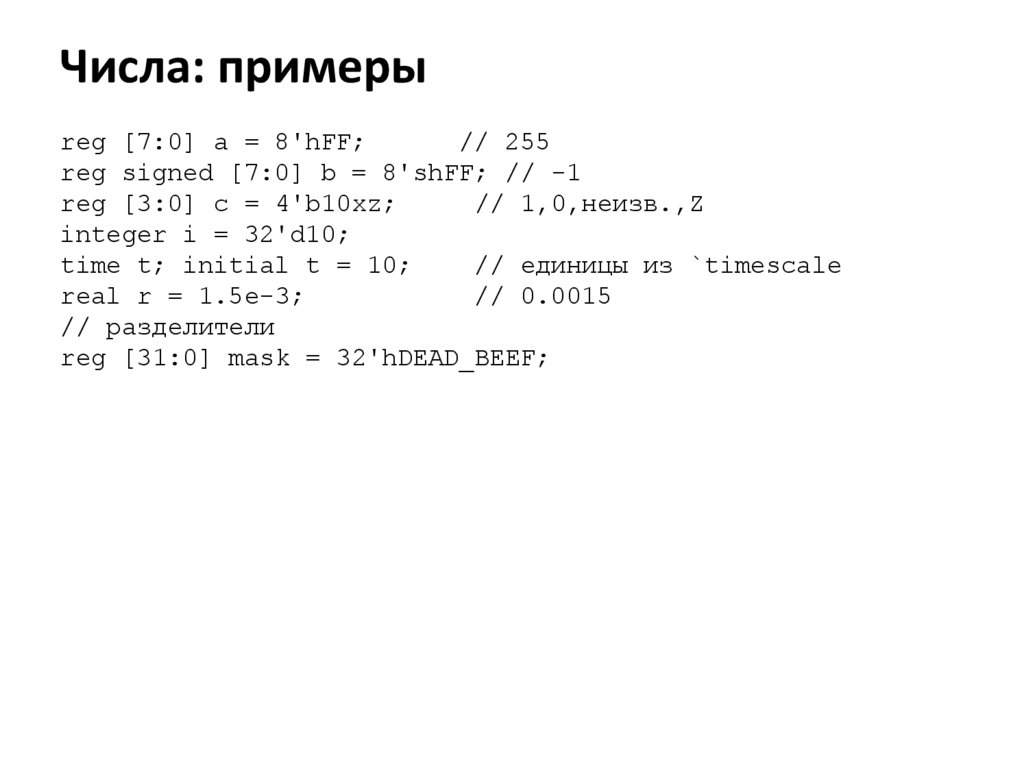

Числа: примерыreg [7:0] a = 8'hFF;

// 255

reg signed [7:0] b = 8'shFF; // -1

reg [3:0] c = 4'b10xz;

// 1,0,неизв.,Z

integer i = 32'd10;

time t; initial t = 10;

// единицы из `timescale

real r = 1.5e-3;

// 0.0015

// разделители

reg [31:0] mask = 32'hDEAD_BEEF;

14.

Строки• Строковые литералы

– "Hello"

– Используются в $display/$fwrite и для

инициализации векторов

• Тип

– В классическом Verilog НЕТ отдельного stringтипа: это массив байт (packed)

• Кодировка

– ASCII 8-бит; каждый символ — 8 бит

• Экранирование

15.

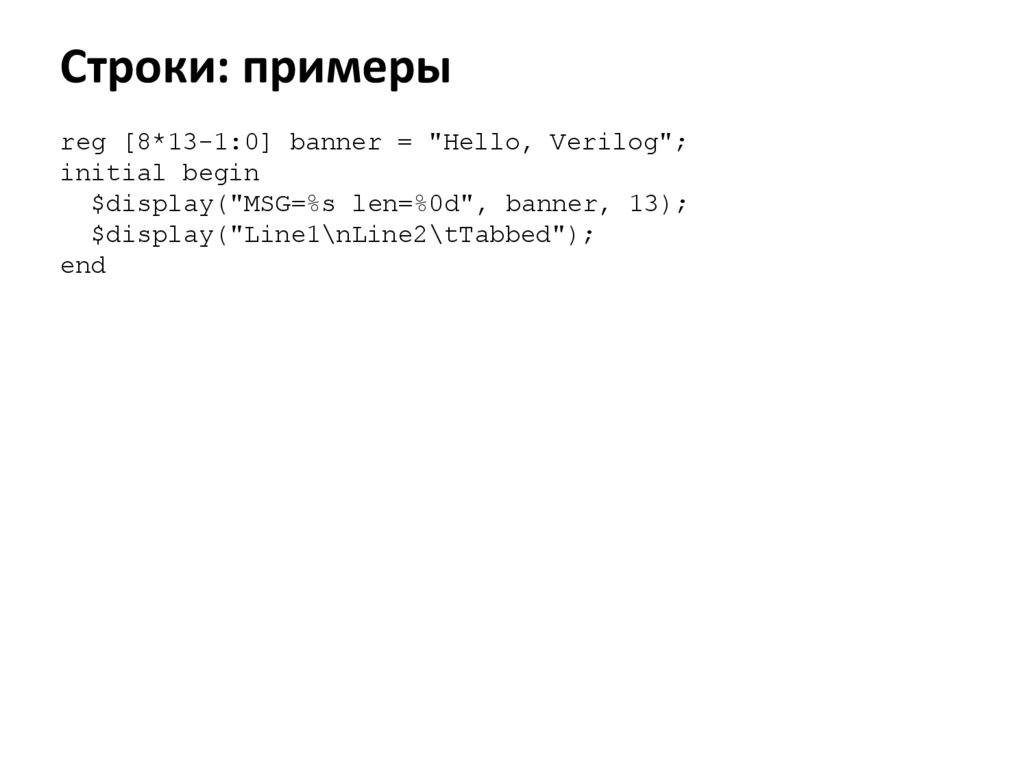

Строки: примерыreg [8*13-1:0] banner = "Hello, Verilog";

initial begin

$display("MSG=%s len=%0d", banner, 13);

$display("Line1\nLine2\tTabbed");

end

16.

Идентификаторы• Правила

– Начинаются с буквы или '_', затем

буквы/цифры/подчёркивание

• Экранированные идентификаторы

– \my-signal[0] <пробел> // завершаются

пробелом

• Чувствительность к регистру

– clk ≠ Clk

• Длина

– Ограничения инструментов; держите < 1024

17.

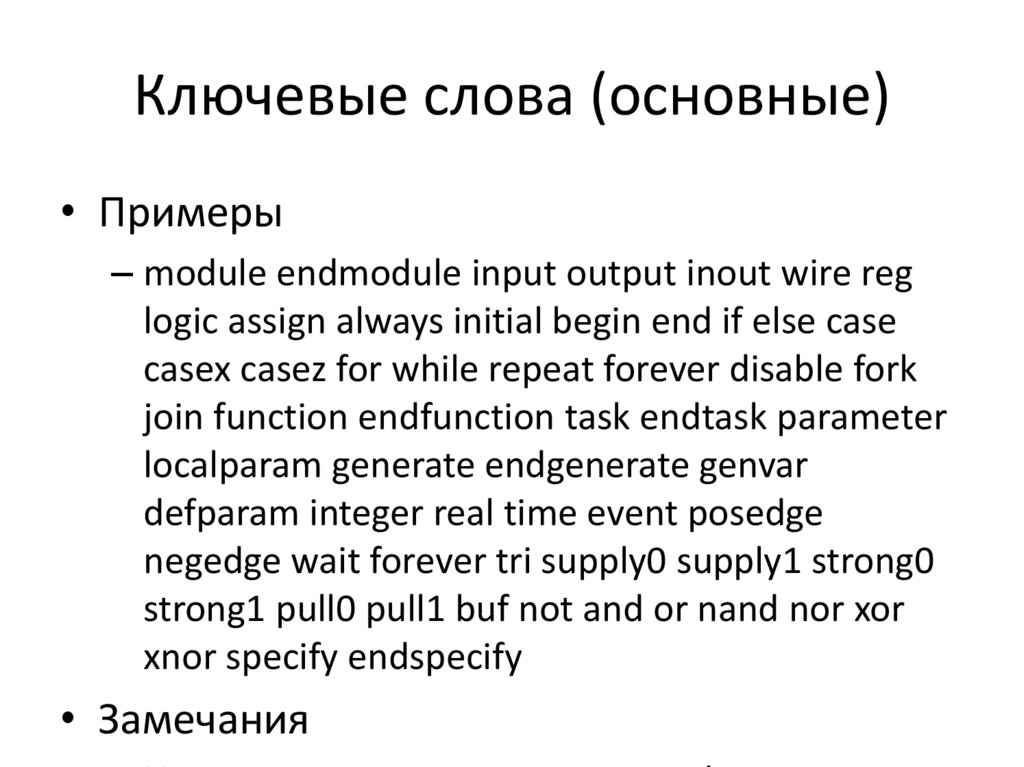

Ключевые слова (основные)• Примеры

– module endmodule input output inout wire reg

logic assign always initial begin end if else case

casex casez for while repeat forever disable fork

join function endfunction task endtask parameter

localparam generate endgenerate genvar

defparam integer real time event posedge

negedge wait forever tri supply0 supply1 strong0

strong1 pull0 pull1 buf not and or nand nor xor

xnor specify endspecify

• Замечания

18.

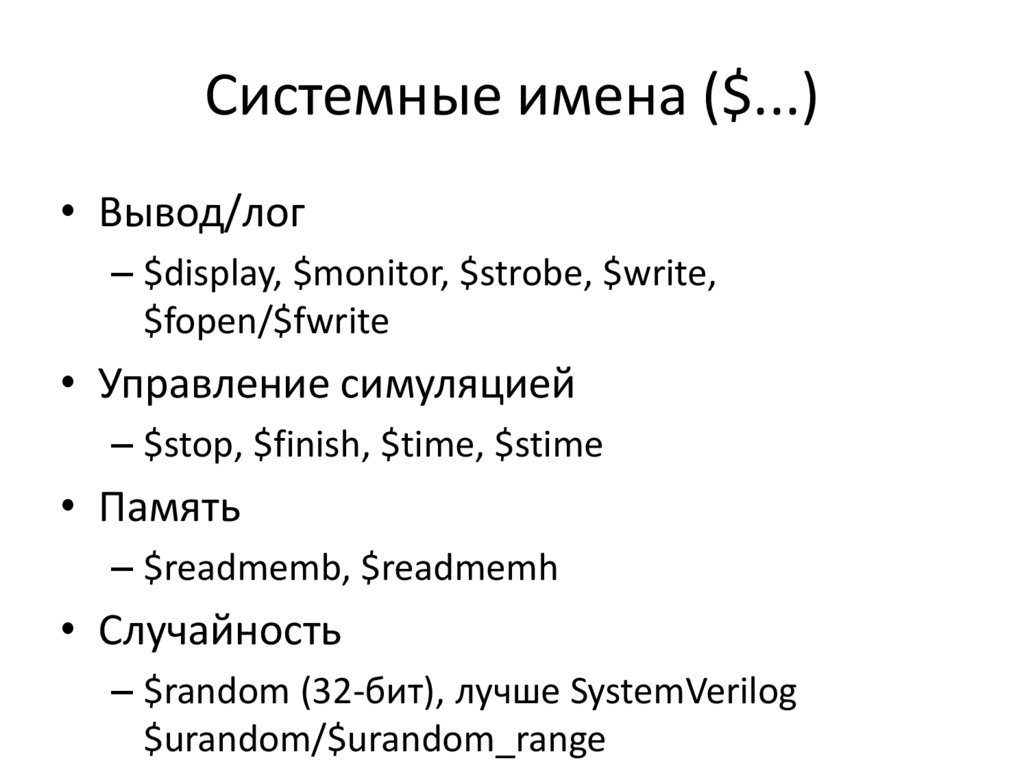

Системные имена ($...)• Вывод/лог

– $display, $monitor, $strobe, $write,

$fopen/$fwrite

• Управление симуляцией

– $stop, $finish, $time, $stime

• Память

– $readmemb, $readmemh

• Случайность

– $random (32-бит), лучше SystemVerilog

$urandom/$urandom_range

19.

Пример: системные задачиinitial begin

$display("t=%0t a=%h b=%h", $time, a, b);

#100 $finish; // завершить симуляцию через 100 единиц времени

end

20.

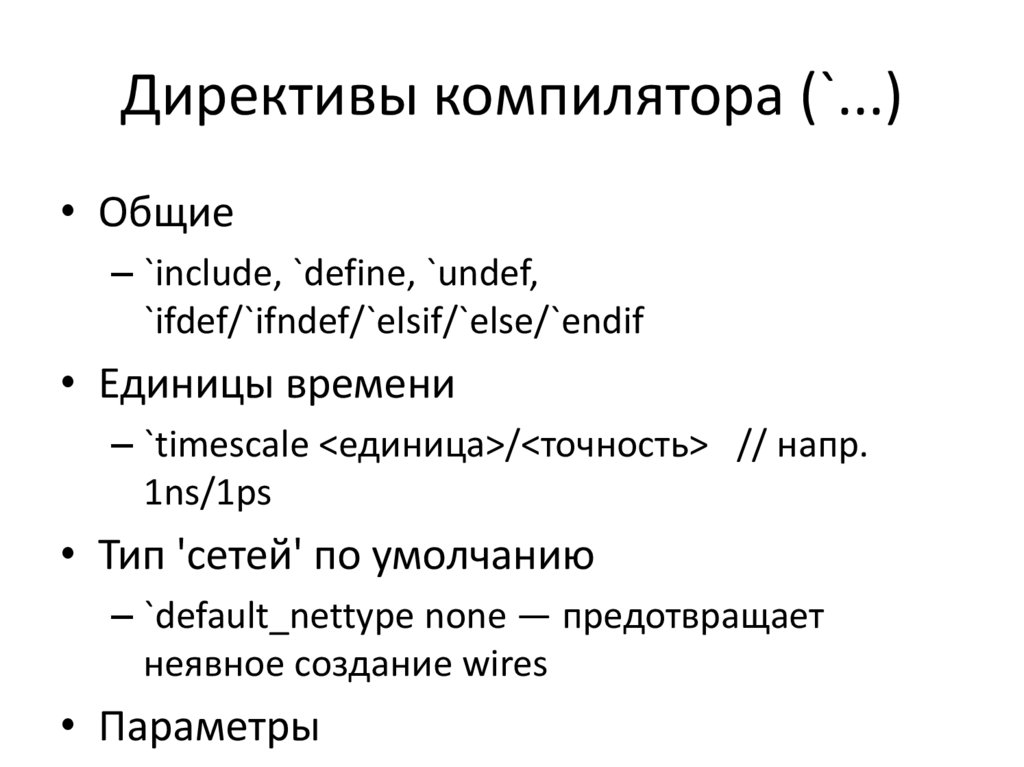

Директивы компилятора (`...)• Общие

– `include, `define, `undef,

`ifdef/`ifndef/`elsif/`else/`endif

• Единицы времени

– `timescale <единица>/<точность> // напр.

1ns/1ps

• Тип 'сетей' по умолчанию

– `default_nettype none — предотвращает

неявное создание wires

• Параметры

21.

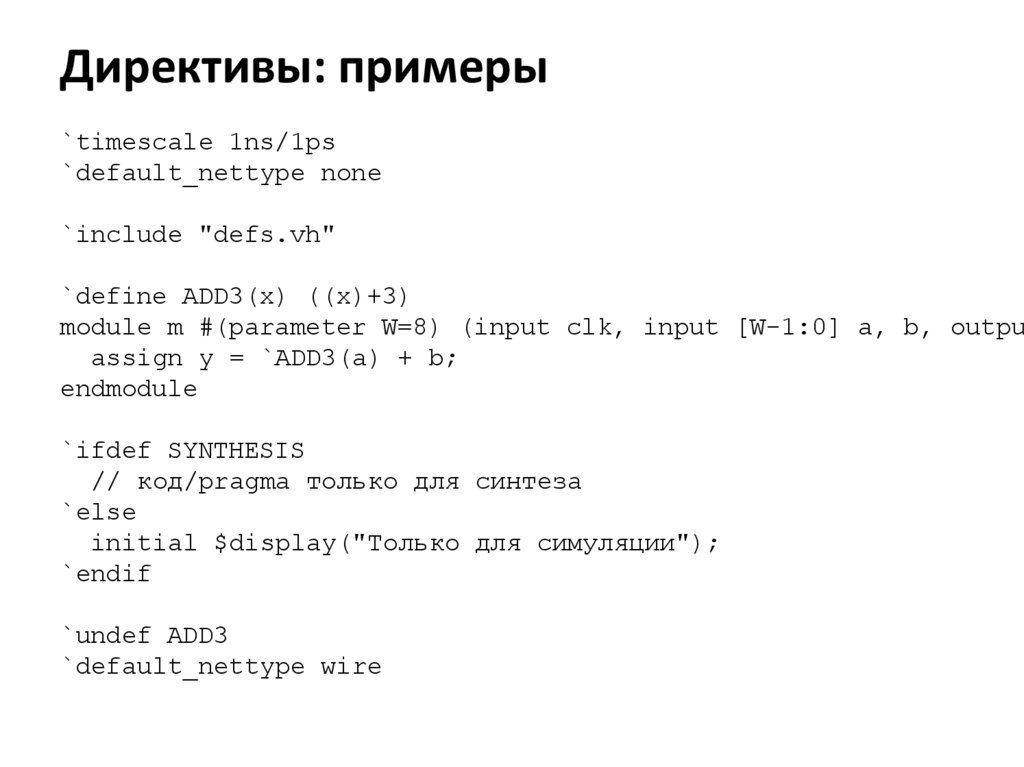

Директивы: примеры`timescale 1ns/1ps

`default_nettype none

`include "defs.vh"

`define ADD3(x) ((x)+3)

module m #(parameter W=8) (input clk, input [W-1:0] a, b, outpu

assign y = `ADD3(a) + b;

endmodule

`ifdef SYNTHESIS

// код/pragma только для синтеза

`else

initial $display("Только для симуляции");

`endif

`undef ADD3

`default_nettype wire

22.

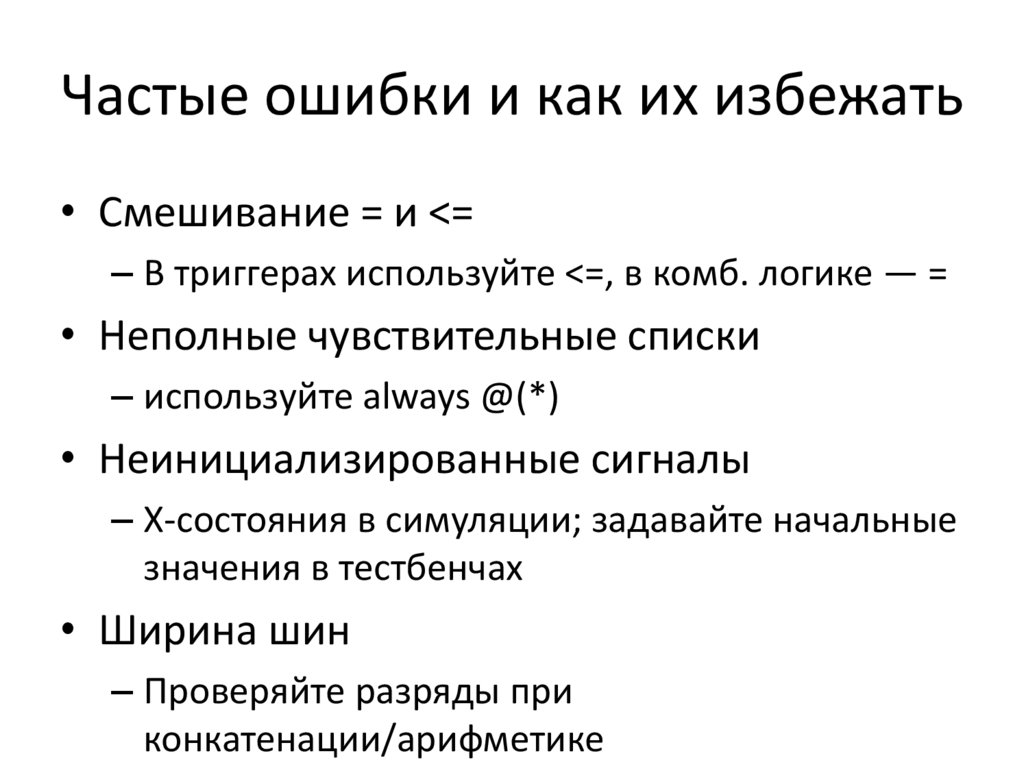

Частые ошибки и как их избежать• Смешивание = и <=

– В триггерах используйте <=, в комб. логике — =

• Неполные чувствительные списки

– используйте always @(*)

• Неинициализированные сигналы

– X-состояния в симуляции; задавайте начальные

значения в тестбенчах

• Ширина шин

– Проверяйте разряды при

конкатенации/арифметике

23.

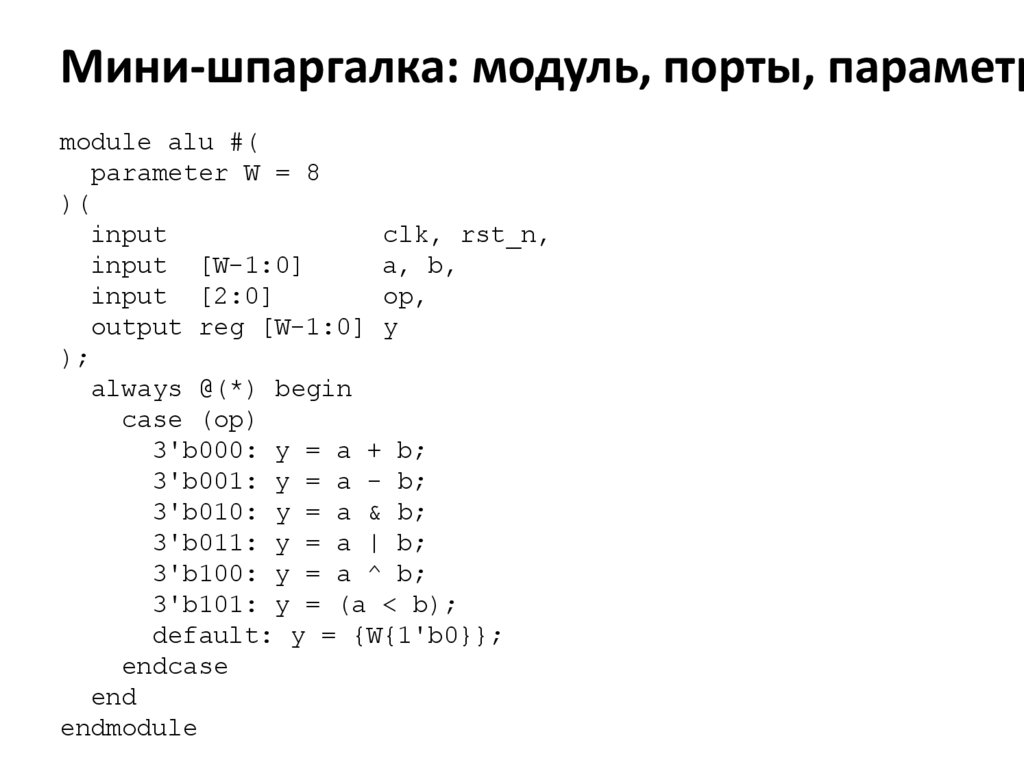

Мини-шпаргалка: модуль, порты, параметрmodule alu #(

parameter W = 8

)(

input

clk, rst_n,

input [W-1:0]

a, b,

input [2:0]

op,

output reg [W-1:0] y

);

always @(*) begin

case (op)

3'b000: y = a + b;

3'b001: y = a - b;

3'b010: y = a & b;

3'b011: y = a | b;

3'b100: y = a ^ b;

3'b101: y = (a < b);

default: y = {W{1'b0}};

endcase

end

endmodule

24.

Где писать тестбенчи и чтопроверять

• Тестбенч = несинтезируемый модуль

– генерация такта, сброса, стимулов, проверки

• Проверка

– $display/$monitor, самопроверка через

assert/сравнение с эталоном

• Покрытие

– Сценарии граничных условий,

знаковые/беззнаковые, X/Z, переполнения

25.

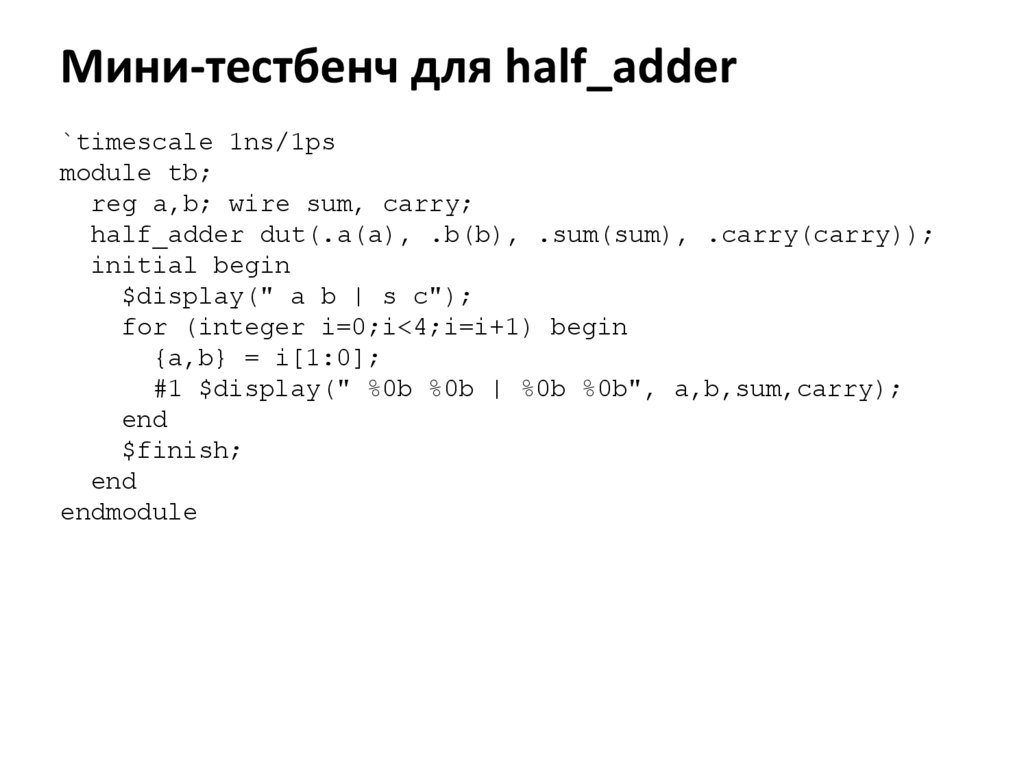

Мини-тестбенч для half_adder`timescale 1ns/1ps

module tb;

reg a,b; wire sum, carry;

half_adder dut(.a(a), .b(b), .sum(sum), .carry(carry));

initial begin

$display(" a b | s c");

for (integer i=0;i<4;i=i+1) begin

{a,b} = i[1:0];

#1 $display(" %0b %0b | %0b %0b", a,b,sum,carry);

end

$finish;

end

endmodule

26.

Практические советы• Стиль кода

– Один модуль — один файл, явные ширины

шин, комментарии к портам

• Параметризация

– parameter/localparam, избегайте defparam

• Именованные соединения портов

– .clk(clk), .rst_n(rst_n)

• Соглашения о сбросе

– rst_n — активный ноль; синхр./асинхр. сброс

• Версионирование

27.

Ресурсы и что дальше• Стандарты

– IEEE 1364-2001/2005, IEEE 1800-2017

(SystemVerilog)

• Книги

– Palnitkar — Verilog HDL; Sutherland —

SystemVerilog for Design

• Практика

– Симулируйте Icarus/Verilator, синтезируйте

Vivado/Quartus

• Шпаргалка

28.

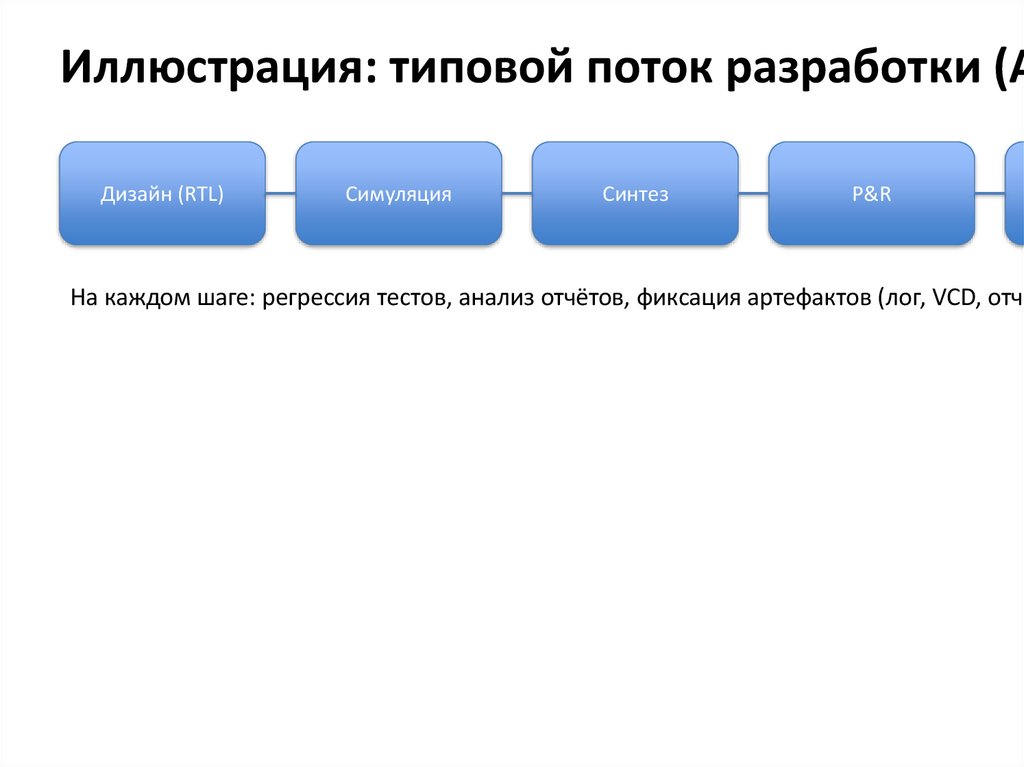

Иллюстрация: типовой поток разработки (AДизайн (RTL)

Симуляция

Синтез

P&R

На каждом шаге: регрессия тестов, анализ отчётов, фиксация артефактов (лог, VCD, отчё

29.

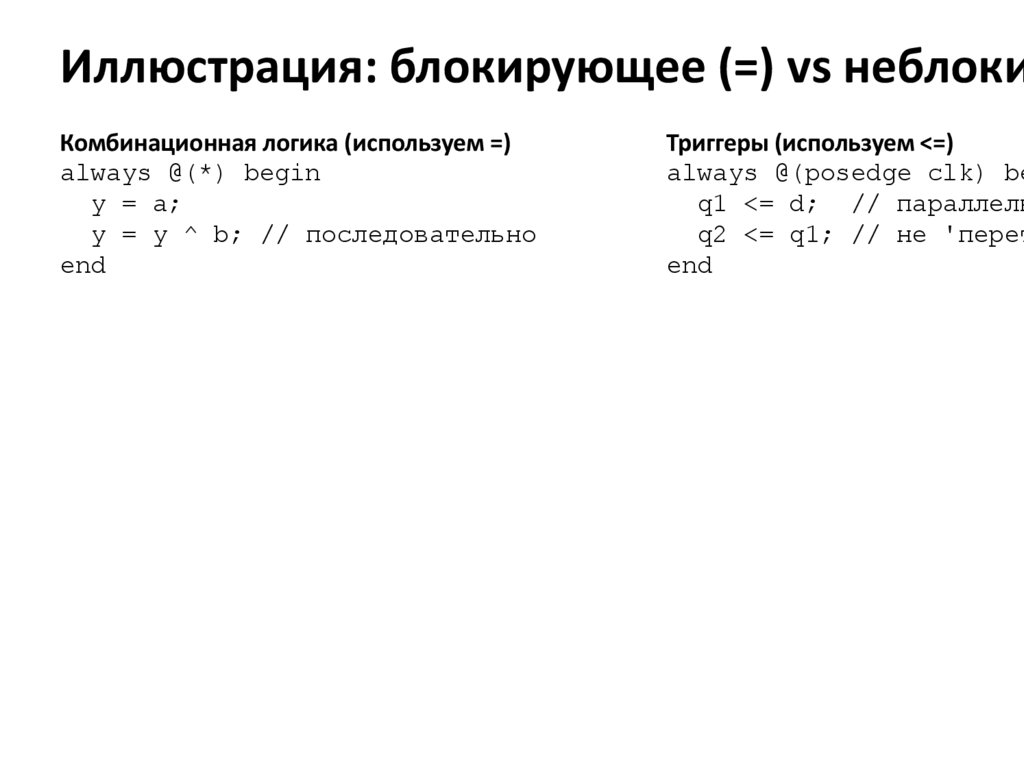

Иллюстрация: блокирующее (=) vs неблокиКомбинационная логика (используем =)

always @(*) begin

y = a;

y = y ^ b; // последовательно

end

Триггеры (используем <=)

always @(posedge clk) be

q1 <= d; // параллель

q2 <= q1; // не 'перет

end

30.

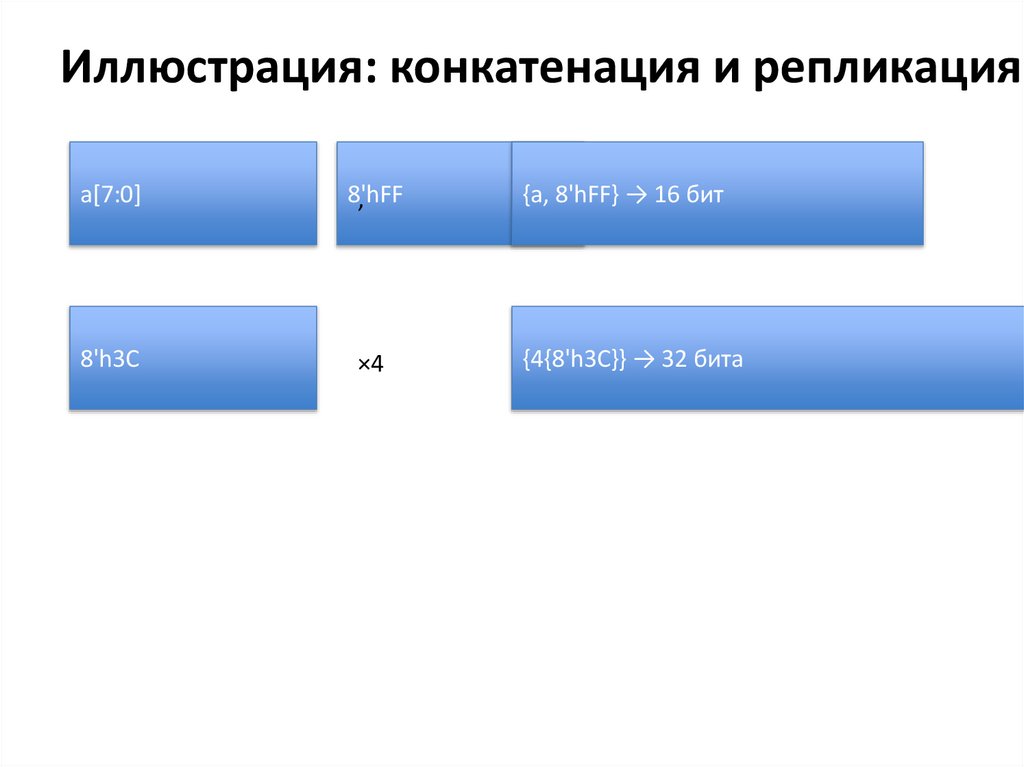

Иллюстрация: конкатенация и репликацияa[7:0]

8'hFF

,

{a, 8'hFF} → 16 бит

8'h3C

×4

{4{8'h3C}} → 32 бита

31.

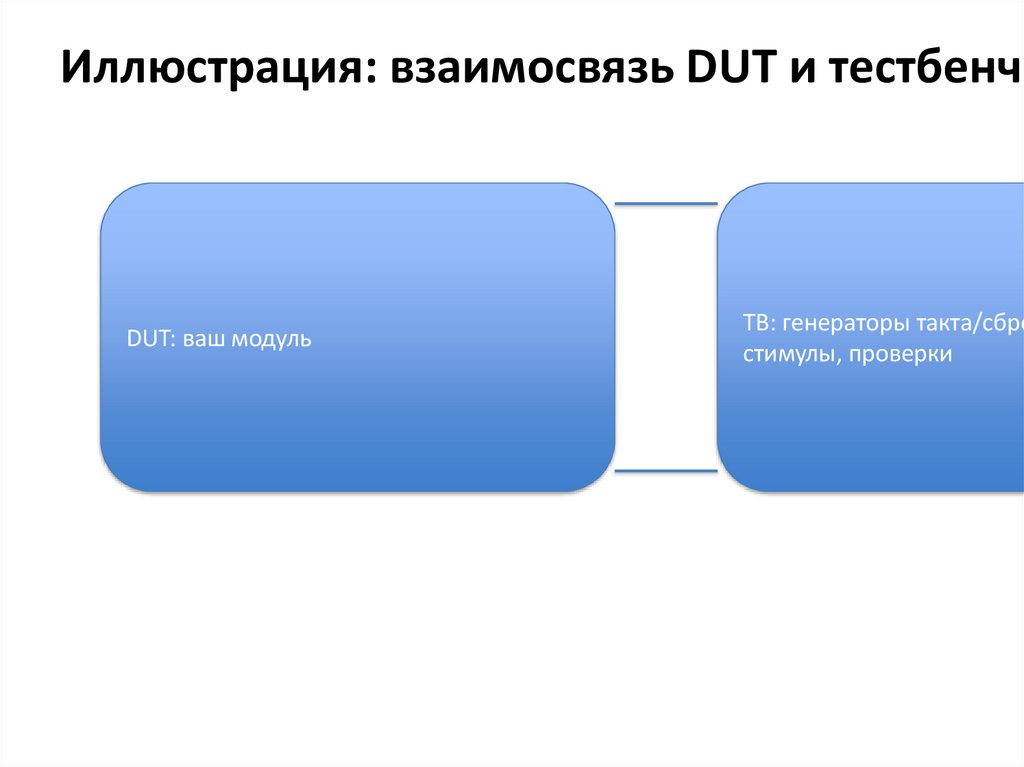

Иллюстрация: взаимосвязь DUT и тестбенчаDUT: ваш модуль

TB: генераторы такта/сбро

стимулы, проверки

programming

programming