Similar presentations:

Архитектура микропроцессоров и ее эволюция

1. Архитектура микропроцессоров

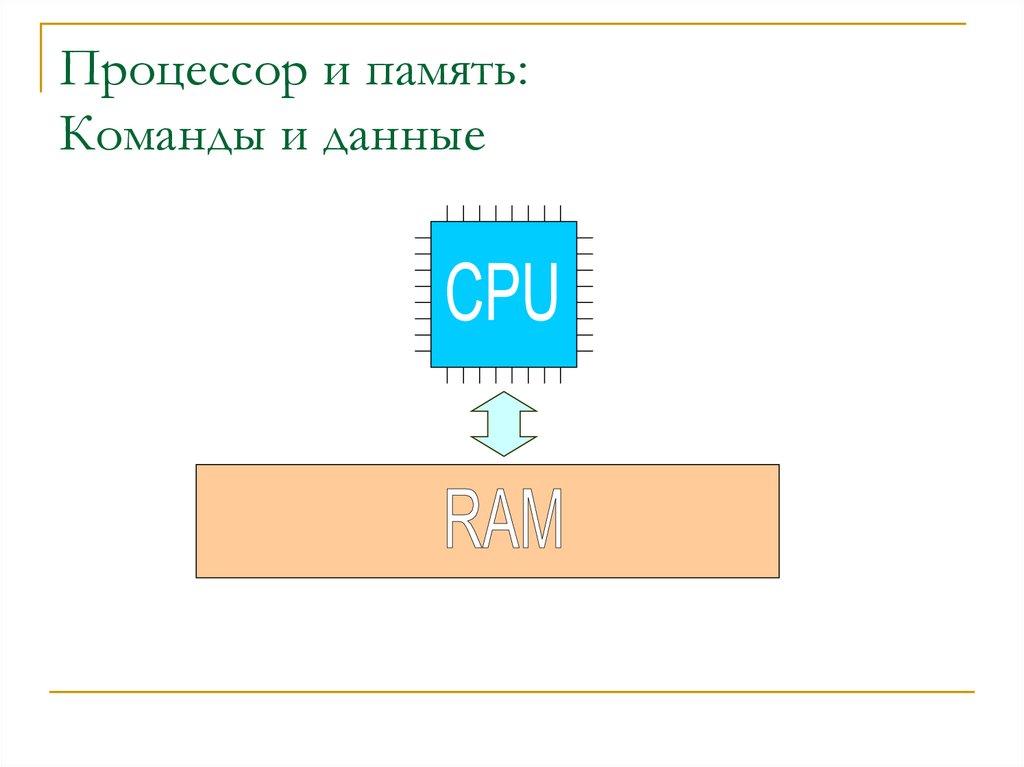

И ее эволюция2. Процессор и память: Команды и данные

3. Пути усовершенствования быстродействия

Улучшение доступа к памятиУвеличение производительности

процессора

4. Процессор и память: Команды и данные

Локальность данныхБыстрая память ближе к процессору

Прозрачность КЭШей

Предвыборка данных

Регистры

КЭШ 1го уровня

КЭШ 2го уровня

Оперативная память

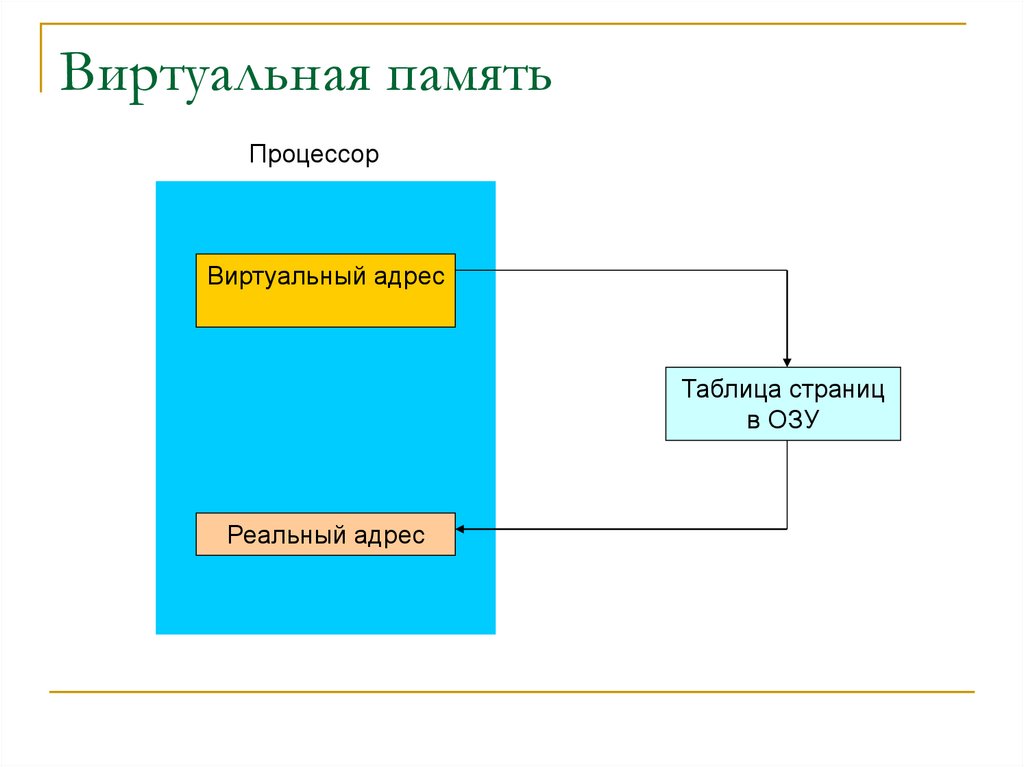

5. Виртуальная память

ПроцессорВиртуальный адрес

Таблица страниц

в ОЗУ

Реальный адрес

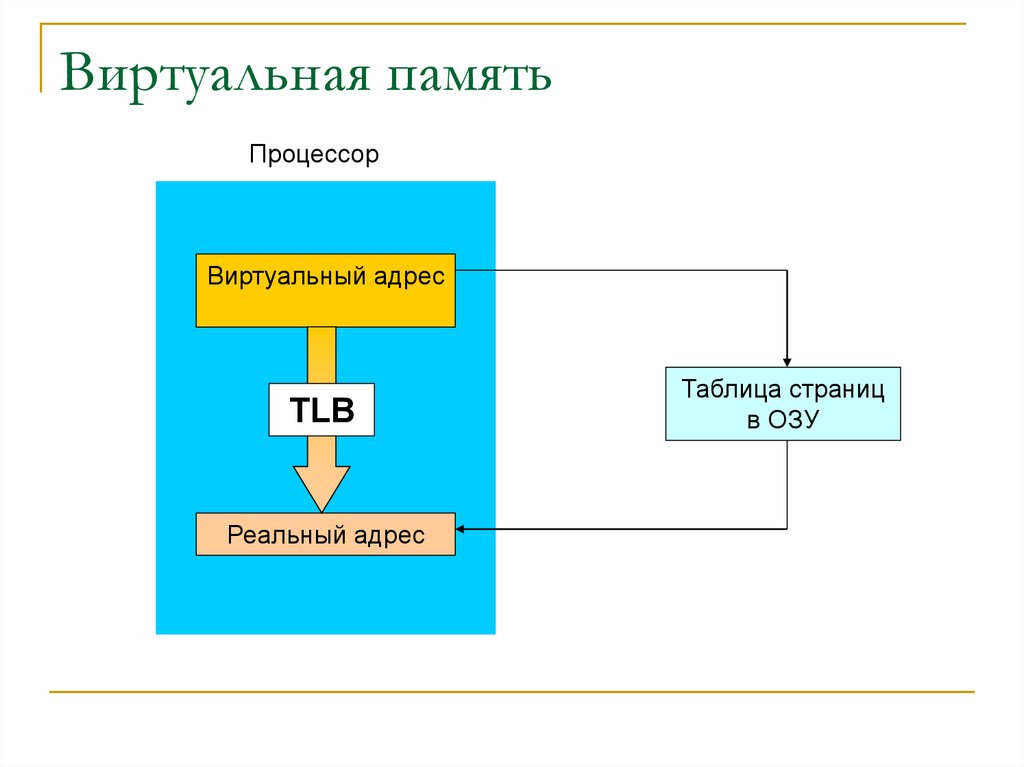

6. Виртуальная память

ПроцессорВиртуальный адрес

TLB

Реальный адрес

Таблица страниц

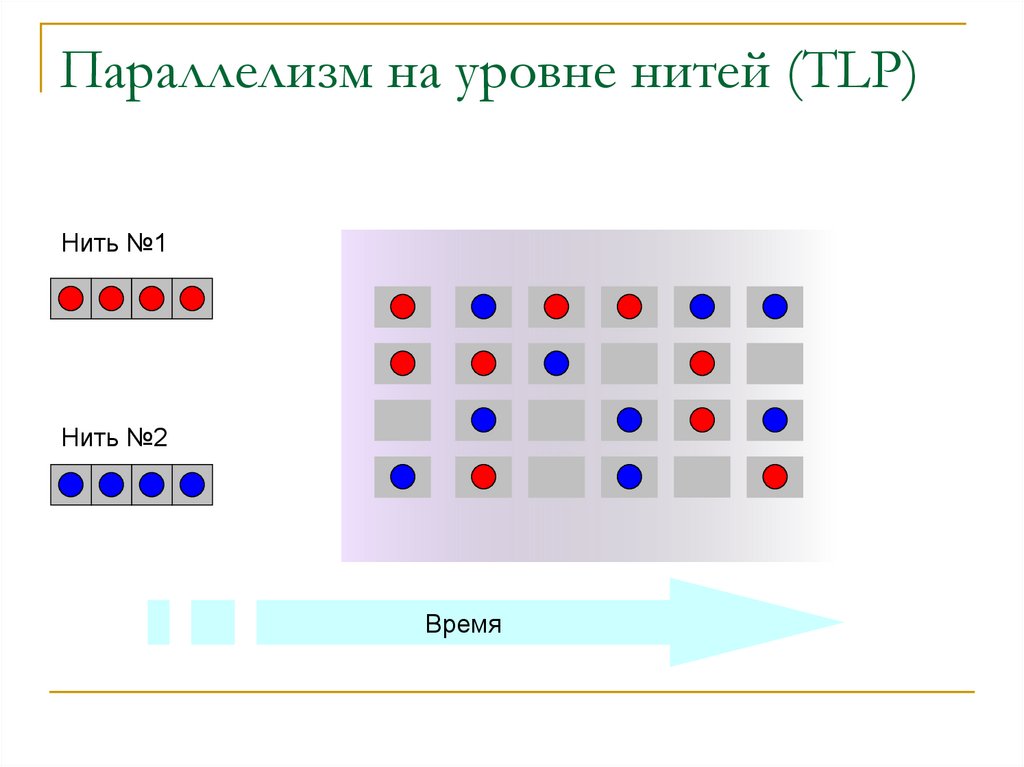

в ОЗУ

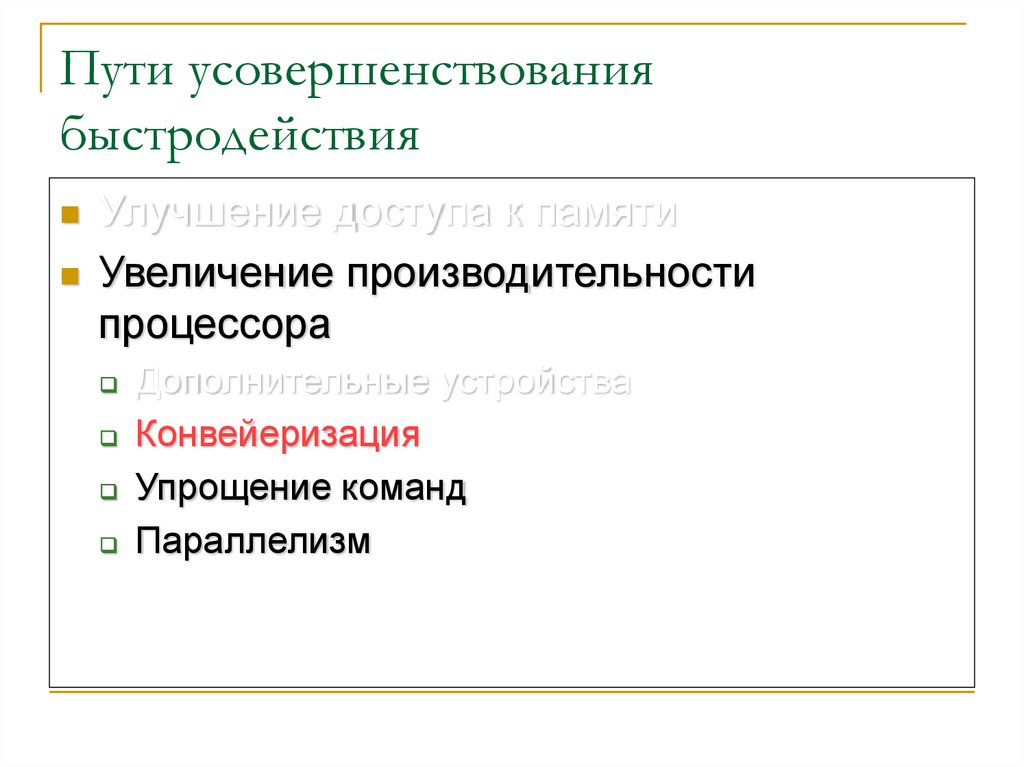

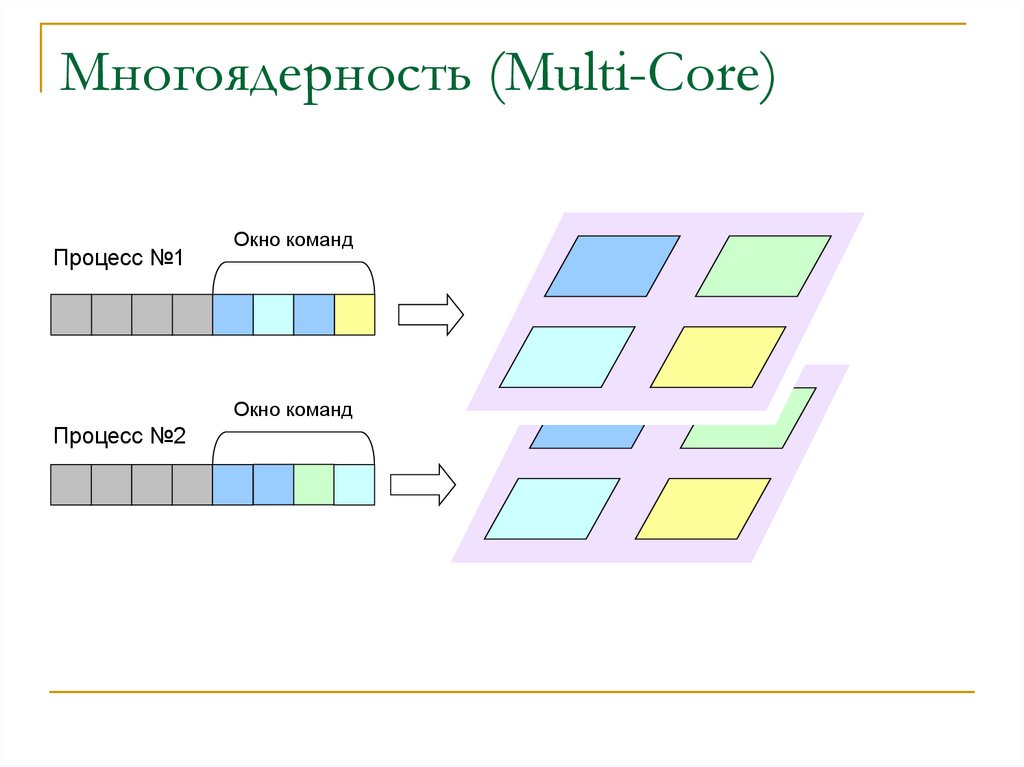

7. Пути усовершенствования быстродействия

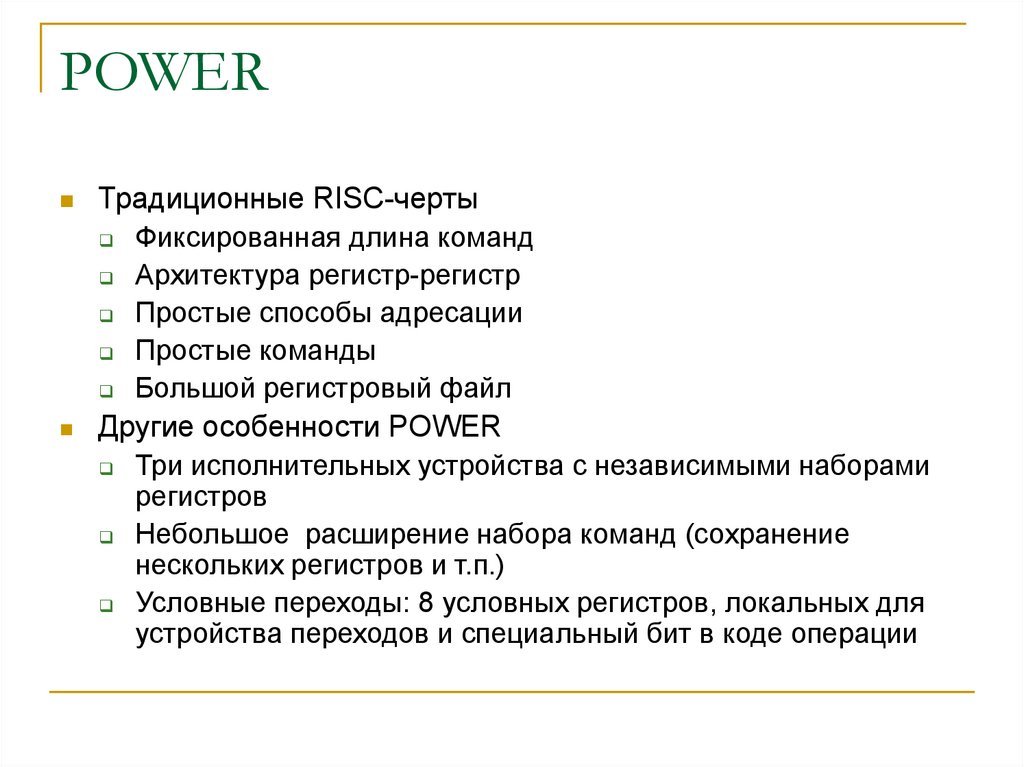

Улучшение доступа к памятиУвеличение производительности

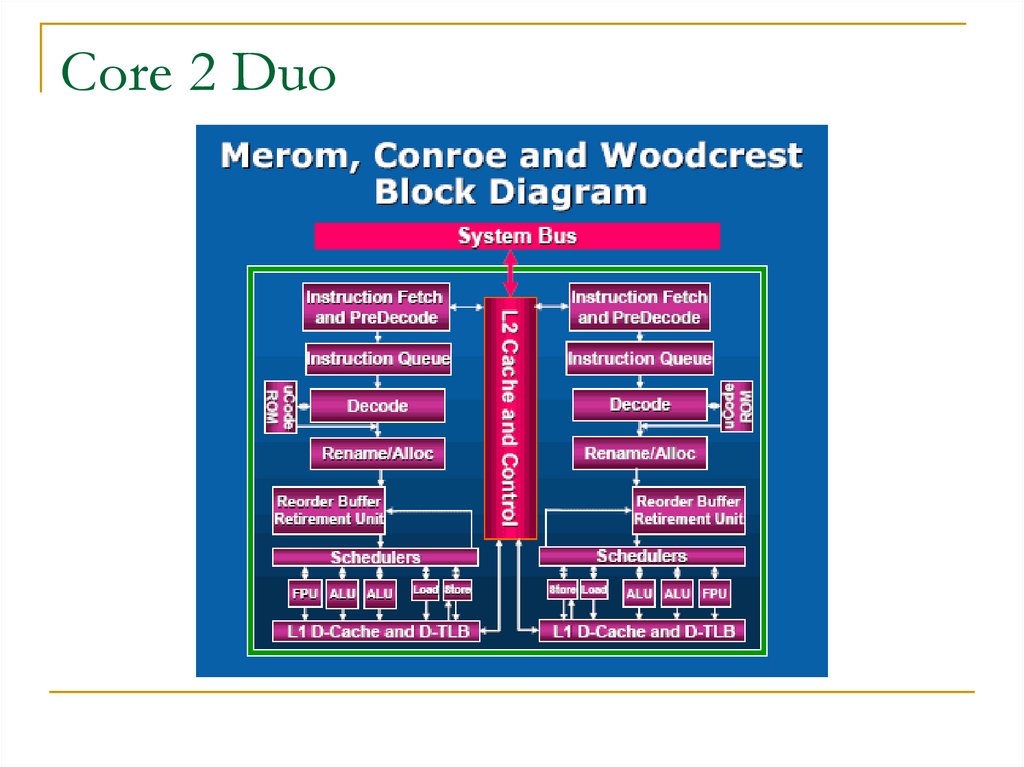

процессора

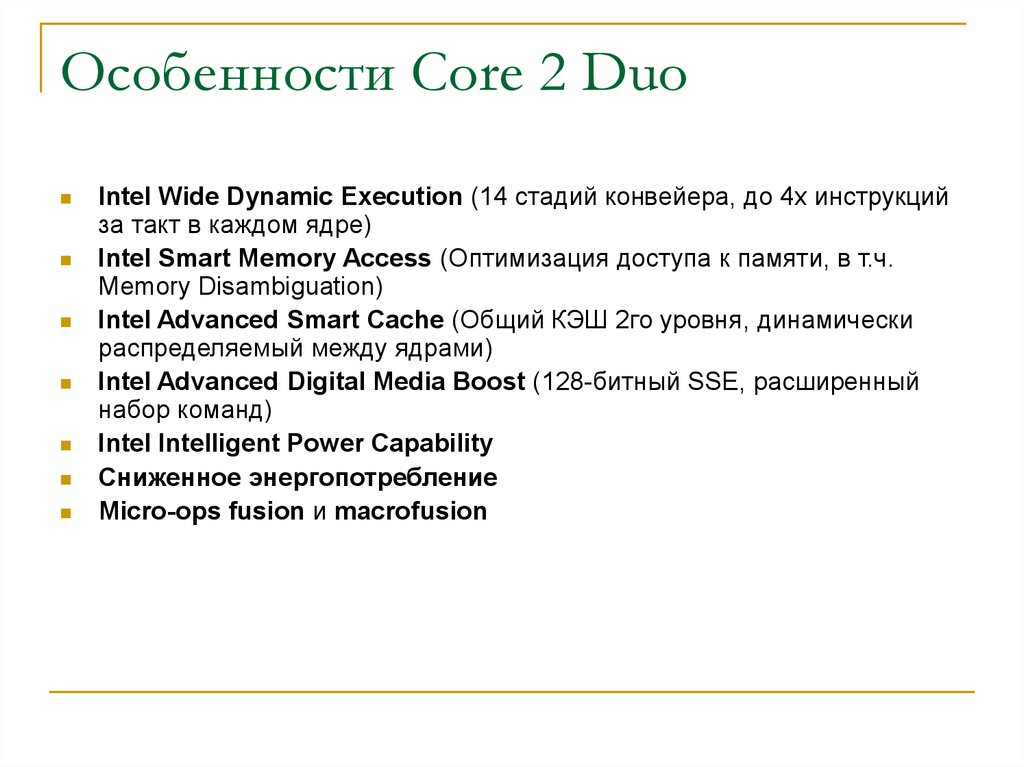

8. Пути усовершенствования быстродействия

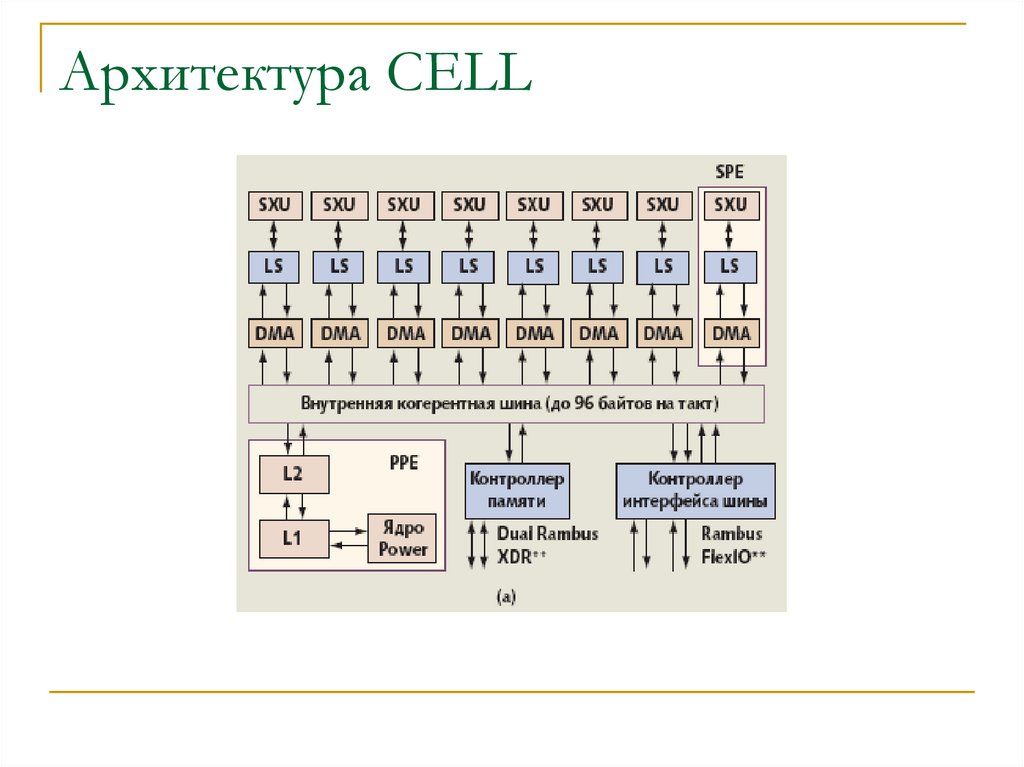

Улучшение доступа к памятиУвеличение производительности

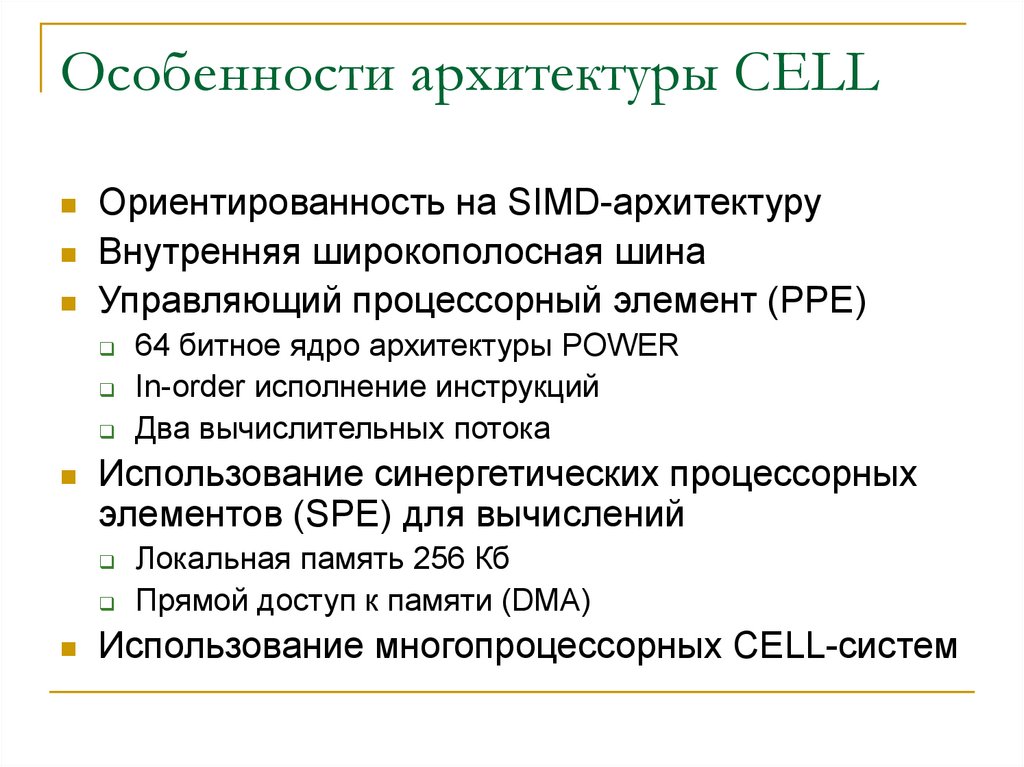

процессора

Дополнительные устройства

Конвейеризация

Упрощение команд

Параллелизм

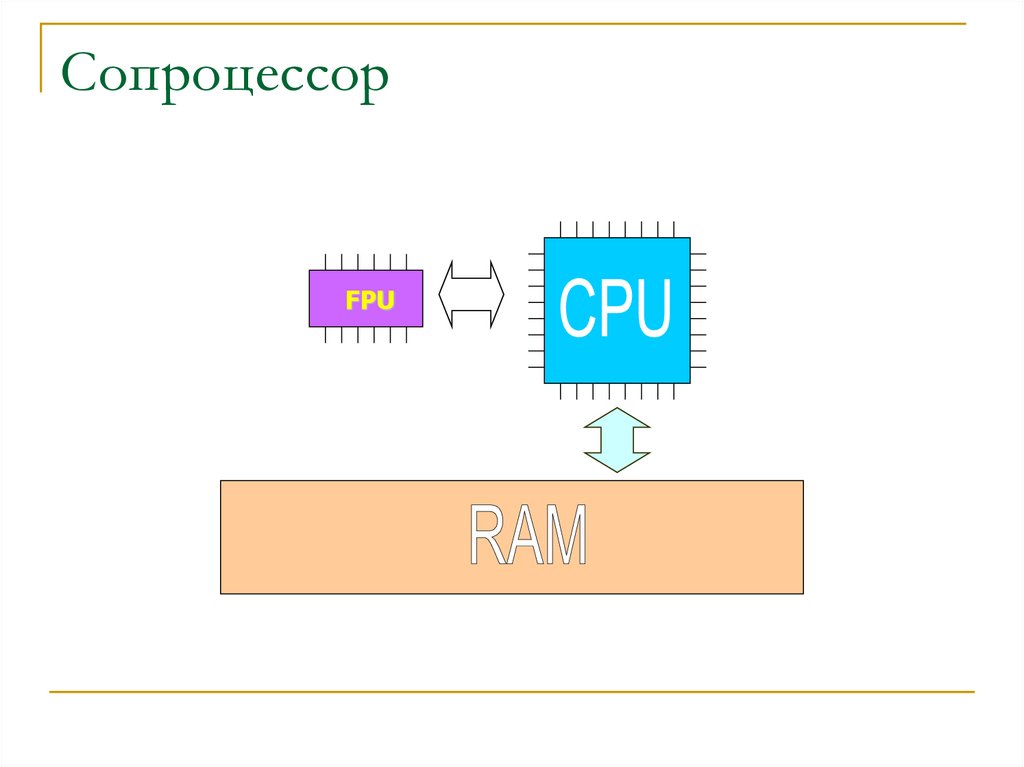

9. Сопроцессор

FPU10. Пути усовершенствования быстродействия

Улучшение доступа к памятиУвеличение производительности

процессора

Дополнительные устройства

Конвейеризация

Упрощение команд

Параллелизм

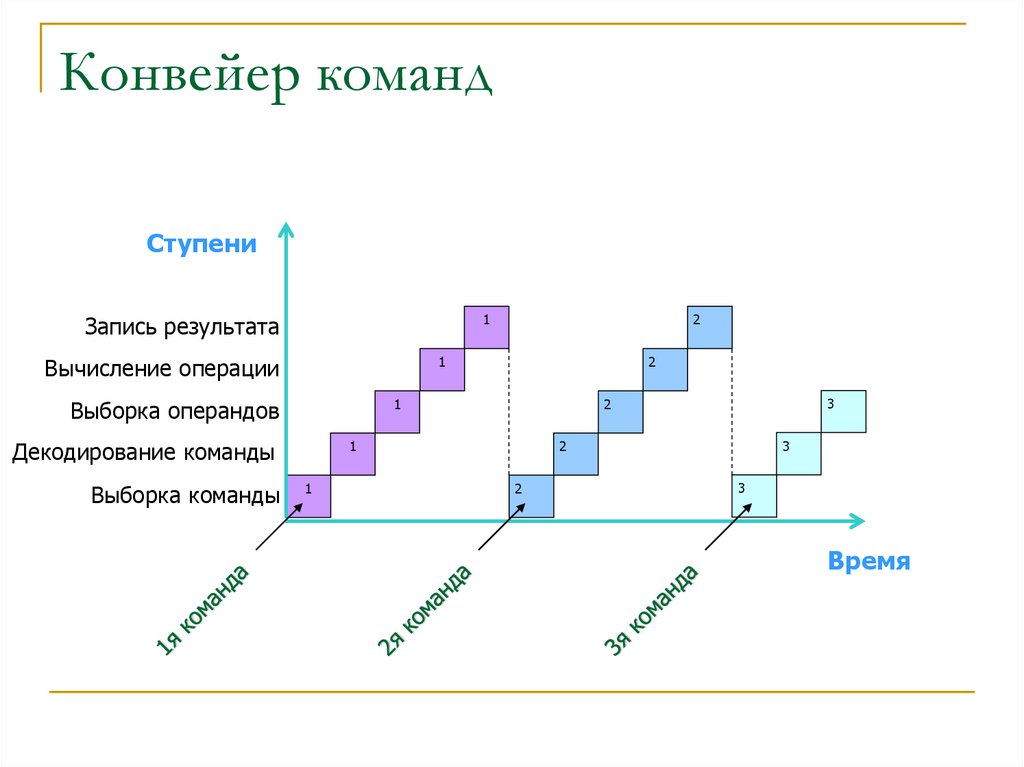

11. Конвейер команд

СтупениЗапись результата

1

Вычисление операции

1

2

1

Выборка операндов

Декодирование команды

Выборка команды

2

1

1

3

2

3

2

2

3

Время

12. Конвейер команд

СтупениВсе ступени конвейера

активны

Латентность конвейера

Запись результата

1

2

3

4

5

2

3

4

5

6

2

3

4

5

6

2

3

4

5

6

3

4

5

6

Вычисление операции

1

1

Выборка операндов

Декодирование команды

Выборка команды

1

1

2

8

8

7

7

7

7

7

6

8

8

8

9

9

9

9

9

Время

13. Конвейер: Условные ветвления

КонвейерПроблема: Условные переходы

?

14. Конвейер: Условные ветвления

Проблема: Условные переходыКонвейер

Решения:

?*

•Спекулятивное исполнение с

предсказанием переходов

•Использование условных команд

•Использование предикатных регистров

15. Конвейер: Условные ветвления

Проблема: Условные переходыКонвейер

Решения:

•Спекулятивное исполнение с

предсказанием переходов

movge

•Использование условных команд

•Использование предикатных регистров

16. Конвейер: Условные ветвления

Проблема: Условные переходыКонвейер

Решения:

•Спекулятивное исполнение с

предсказанием переходов

•Использование условных команд

•Использование предикатных регистров

17. Пути усовершенствования быстродействия

Улучшение доступа к памятиУвеличение производительности

процессора

Дополнительные устройства

Конвейеризация

Упрощение команд

Параллелизм

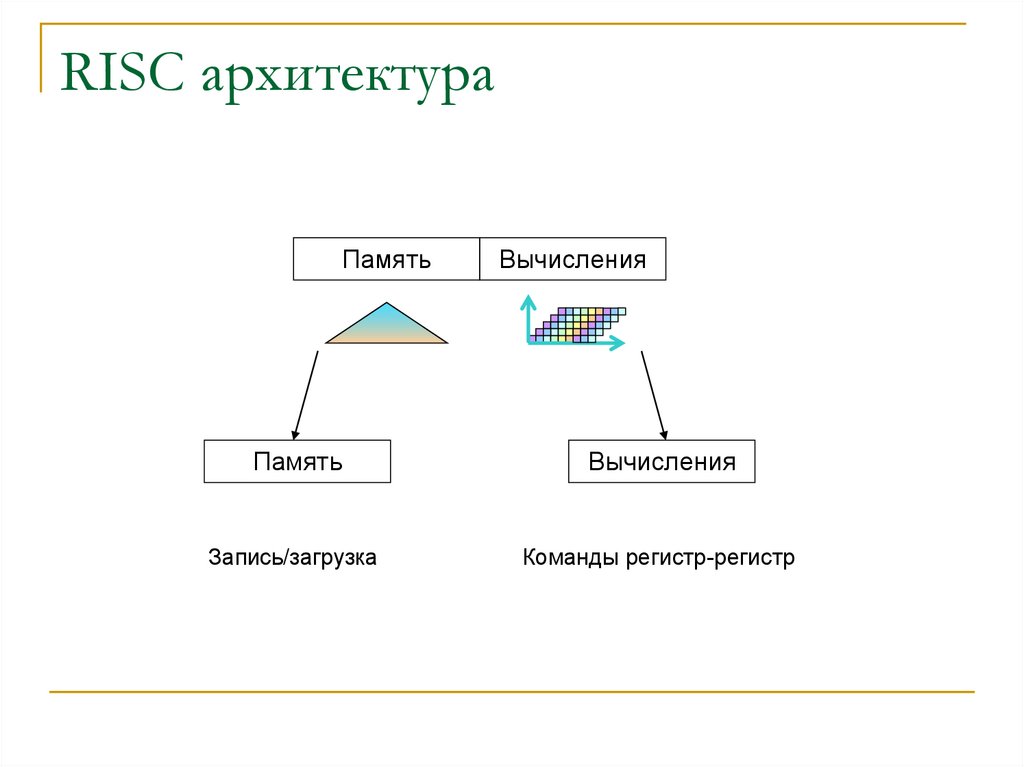

18. RISC архитектура

ПамятьВычисления

Память

Вычисления

Запись/загрузка

Команды регистр-регистр

19. CISC

Большое количествокоманд

Много типов данных

Различная длина

инструкций

Небольшое

количество регистров

Ориентация на

процессор

RISC

Уменьшенное

количество команд

Только основные типы

Фиксированная длина

инструкций

Большой регистровый

файл

Более глубокое

использование

компилятора

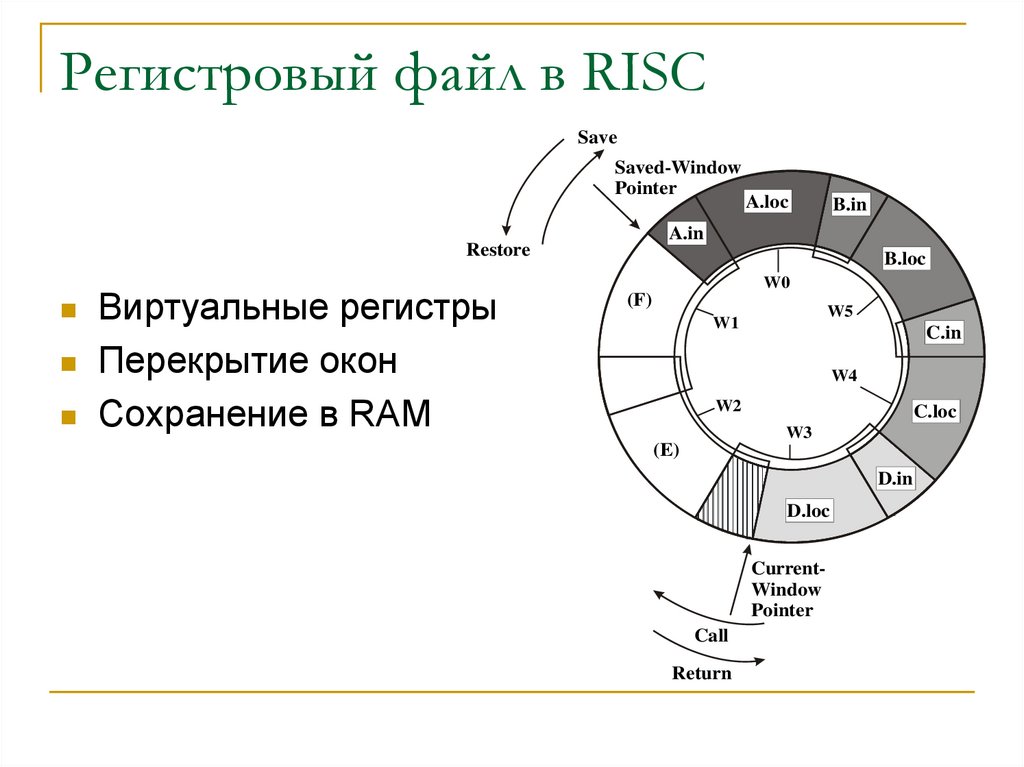

20. Регистровый файл в RISC

SaveSaved-Window

Pointer

Виртуальные регистры

Перекрытие окон

Сохранение в RAM

B.in

A.in

Restore

A.loc

B.loc

W0

(F)

W5

W1

C.in

W4

W2

C.loc

W3

(E)

D.in

D.loc

CurrentWindow

Pointer

Call

Return

21. Пути усовершенствования быстродействия

Улучшение доступа к памятиУвеличение производительности

процессора

Дополнительные устройства

Конвейеризация

Упрощение команд

Параллелизм

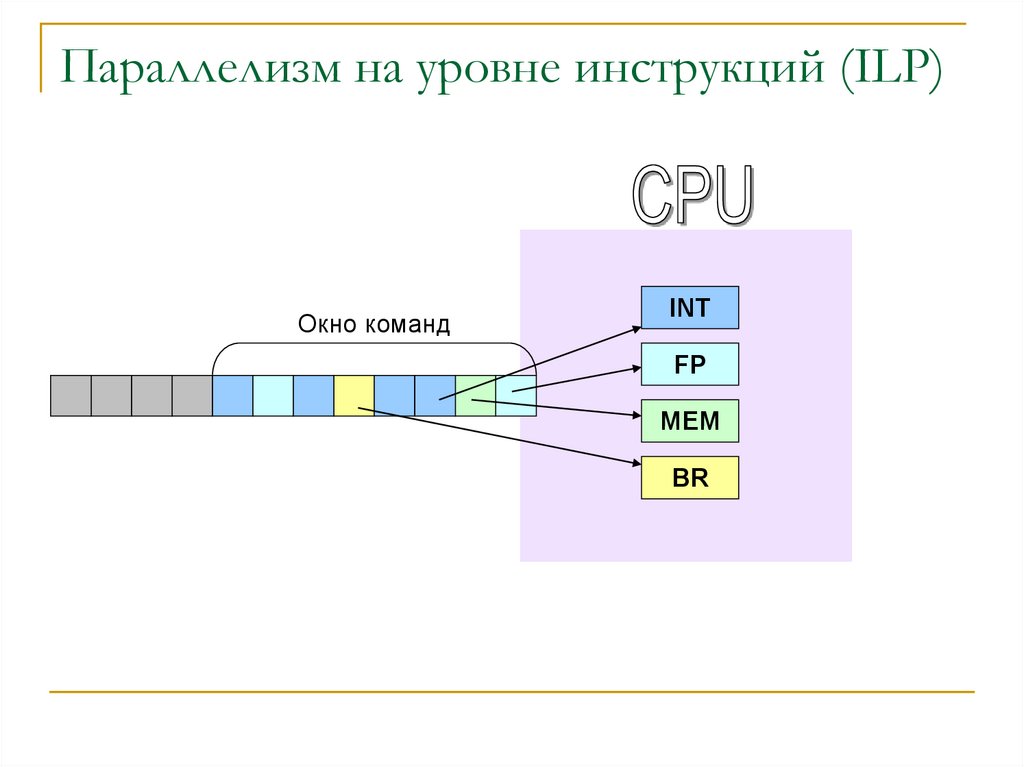

22. Параллелизм на уровне инструкций (ILP)

Окно командINT

FP

MEM

BR

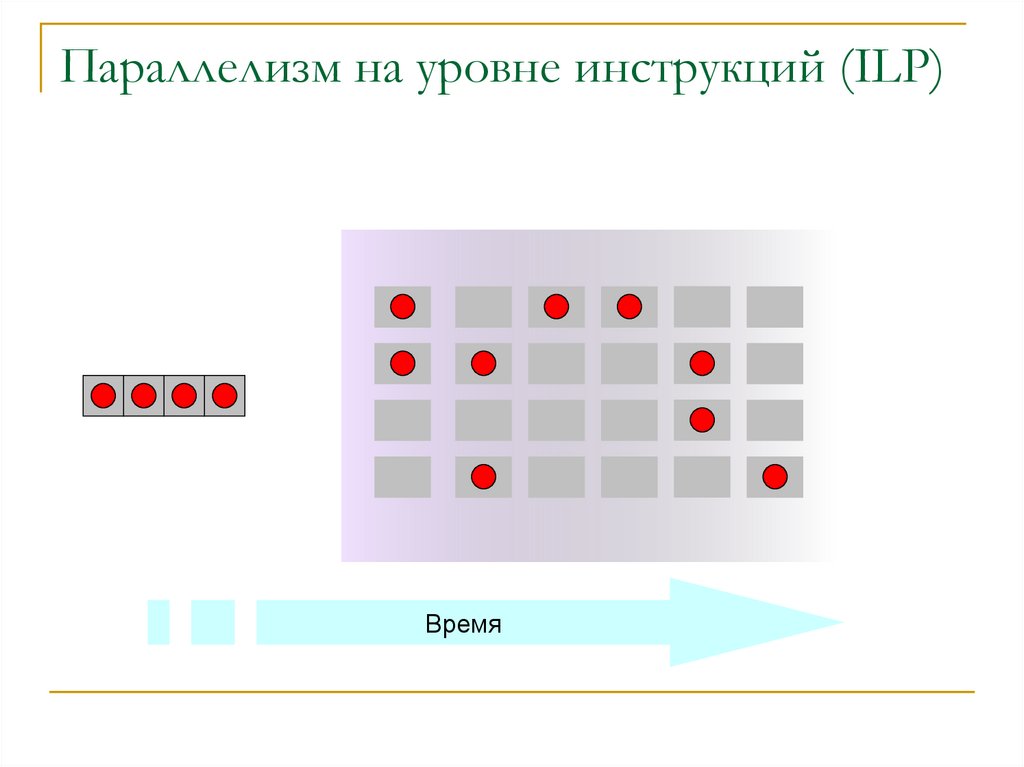

23. Параллелизм на уровне инструкций (ILP)

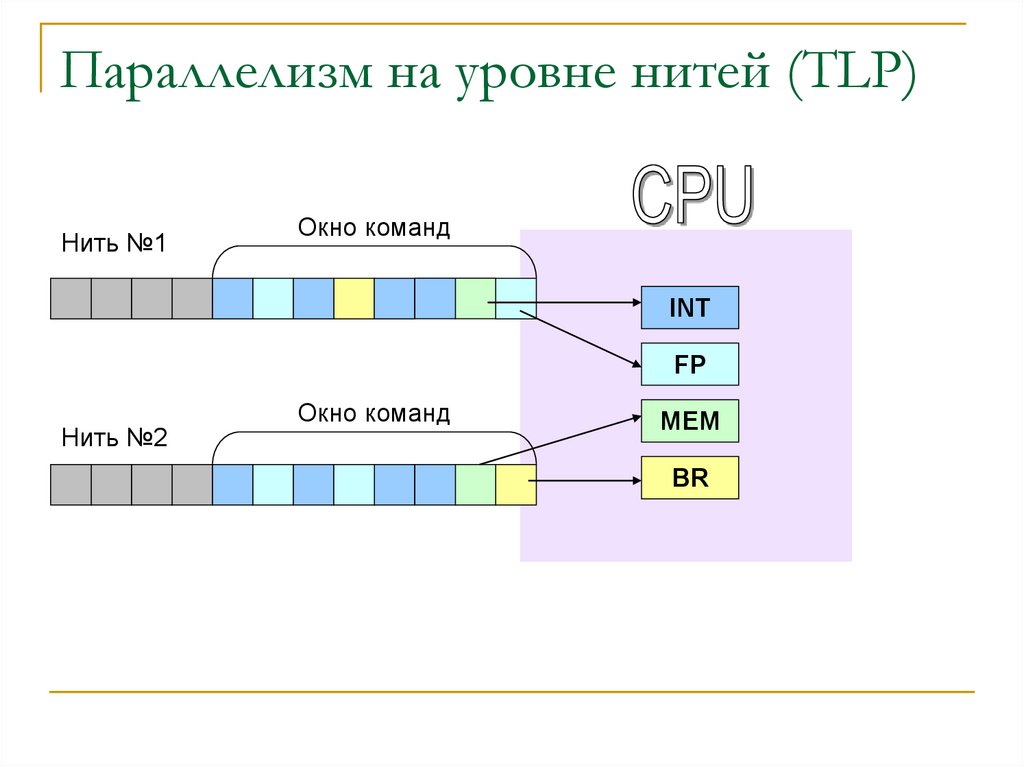

Время24. Параллелизм на уровне нитей (TLP)

Нить №1Окно команд

INT

FP

Нить №2

Окно команд

MEM

BR

25. Параллелизм на уровне нитей (TLP)

Нить №1Нить №2

Время

26. Многоядерность (Multi-Core)

Процесс №1Окно команд

Окно команд

Процесс №2

27. POWER

Традиционные RISC-чертыФиксированная длина команд

Архитектура регистр-регистр

Простые способы адресации

Простые команды

Большой регистровый файл

Другие особенности POWER

Три исполнительных устройства с независимыми наборами

регистров

Небольшое расширение набора команд (сохранение

нескольких регистров и т.п.)

Условные переходы: 8 условных регистров, локальных для

устройства переходов и специальный бит в коде операции

28. Core 2 Duo

29. Особенности Core 2 Duo

Intel Wide Dynamic Execution (14 стадий конвейера, до 4х инструкцийза такт в каждом ядре)

Intel Smart Memory Access (Оптимизация доступа к памяти, в т.ч.

Memory Disambiguation)

Intel Advanced Smart Cache (Общий КЭШ 2го уровня, динамически

распределяемый между ядрами)

Intel Advanced Digital Media Boost (128-битный SSE, расширенный

набор команд)

Intel Intelligent Power Capability

Сниженное энергопотребление

Micro-ops fusion и macrofusion

30. Архитектура CELL

31. Особенности архитектуры CELL

Ориентированность на SIMD-архитектуруВнутренняя широкополосная шина

Управляющий процессорный элемент (PPE)

Использование синергетических процессорных

элементов (SPE) для вычислений

64 битное ядро архитектуры POWER

In-order исполнение инструкций

Два вычислительных потока

Локальная память 256 Кб

Прямой доступ к памяти (DMA)

Использование многопроцессорных CELL-систем

electronics

electronics