Similar presentations:

Лекция2 Вычислительные машины, сети и системы

1. Лекция 2

Эволюция технологийизготовления процессора

Электромеханическое реле

Вакуумные лампы и ячейки на

лампах

Транзисторы

2. Эволюция технологий изготовления процессора

Эволюция технологийизготовления процессора:

микросхемы

Микропроцессор Intel

4004

• 1971 год

• первый в мире коммерчески

доступный однокристальный

микропроцессор

• стоимость 200 долларов

• на одном кристалле все

функции процессора

большой ЭВМ

• 60 000 (в среднем,

максимально до 93 000)

инструкций в секунду

• Количество транзисторов:

2250

3. Эволюция технологий изготовления процессора: микросхемы

В «настоящее» времяIntel Core i3 2010

2011 год

995 000 000 транзисторов

~145 000 000 000 операций с

плавающей точкой в секунду

Частота процессора 3.8 ГГц

Количество ядер 4

Техпроцесс 32 нм

2013 год: Ivy Bridge 1,4 млрд.

транзисторов на площади

кристалла 160 мм².

4. В «настоящее» время

Intel Core i7 Частота процессора: 2.8 ГГцТехпроцесс:

22 nm

Количество ядер:

8

Поддержка Hyper-Threading: Есть

Поддержка технологии Turbo Boost: Есть

Частота процессора в режиме Turbo

Boost: 3.6 ГГц

TDP:

140 W (Thermal Design Power)

Тип памяти:

DDR4-1333/1600/2133

2,2 млрд транзисторов

~ 1000 долларов

QPI с северным мостом

Контроллер памяти на ЦП

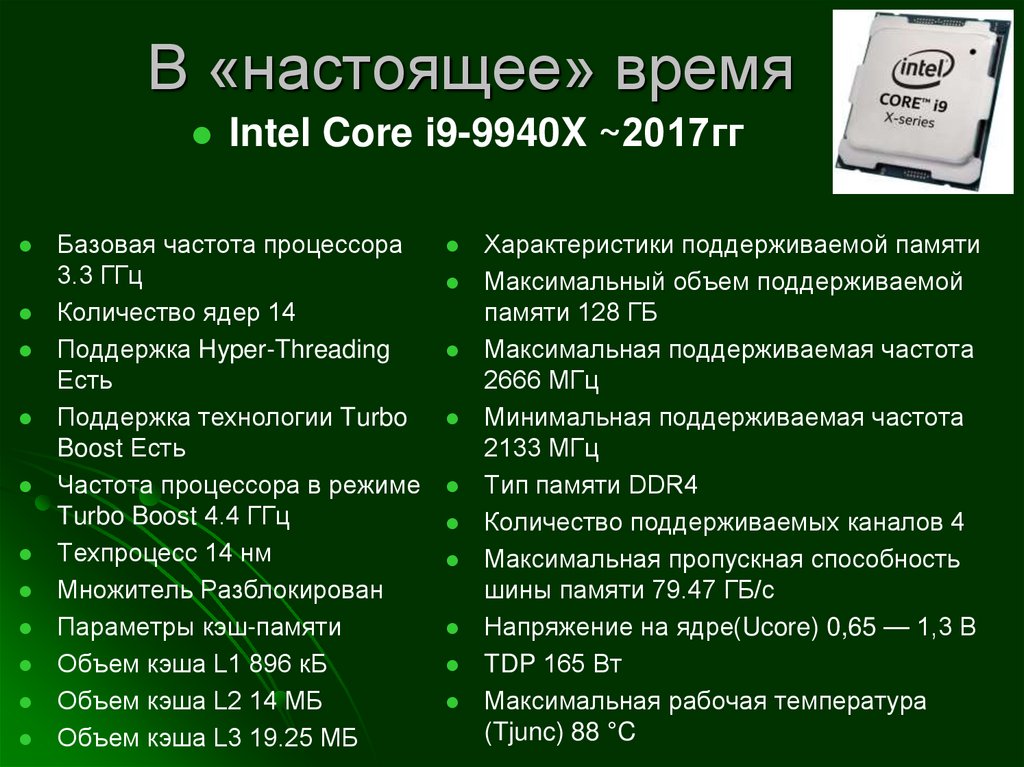

5. В «настоящее» время

Intel Core i9-9940X ~2017ггБазовая частота процессора

3.3 ГГц

Количество ядер 14

Поддержка Hyper-Threading

Есть

Поддержка технологии Turbo

Boost Есть

Частота процессора в режиме

Turbo Boost 4.4 ГГц

Техпроцесс 14 нм

Множитель Разблокирован

Параметры кэш-памяти

Объем кэша L1 896 кБ

Объем кэша L2 14 МБ

Объем кэша L3 19.25 МБ

Характеристики поддерживаемой памяти

Максимальный объем поддерживаемой

памяти 128 ГБ

Максимальная поддерживаемая частота

2666 МГц

Минимальная поддерживаемая частота

2133 МГц

Тип памяти DDR4

Количество поддерживаемых каналов 4

Максимальная пропускная способность

шины памяти 79.47 ГБ/с

Напряжение на ядре(Ucore) 0,65 — 1,3 В

TDP 165 Вт

Максимальная рабочая температура

(Tjunc) 88 °C

6. В «настоящее» время

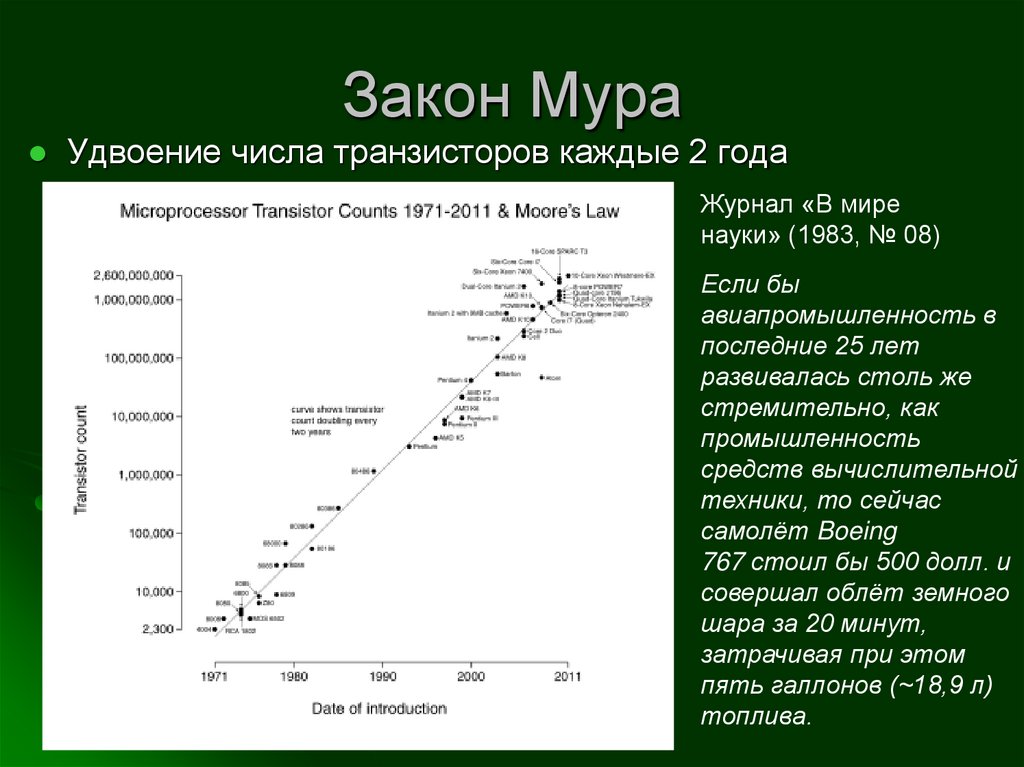

Закон МураУдвоение числа транзисторов каждые 2 года

Журнал «В мире

науки» (1983, № 08)

Если бы

авиапромышленность в

последние 25 лет

развивалась столь же

стремительно, как

промышленность

средств вычислительной

техники, то сейчас

самолёт Boeing

767 стоил бы 500 долл. и

совершал облёт земного

шара за 20 минут,

затрачивая при этом

пять галлонов (~18,9 л)

топлива.

7. Закон Мура

О транзисторахЧто это?

Для чего нужны?

Где используются?

8. О транзисторах

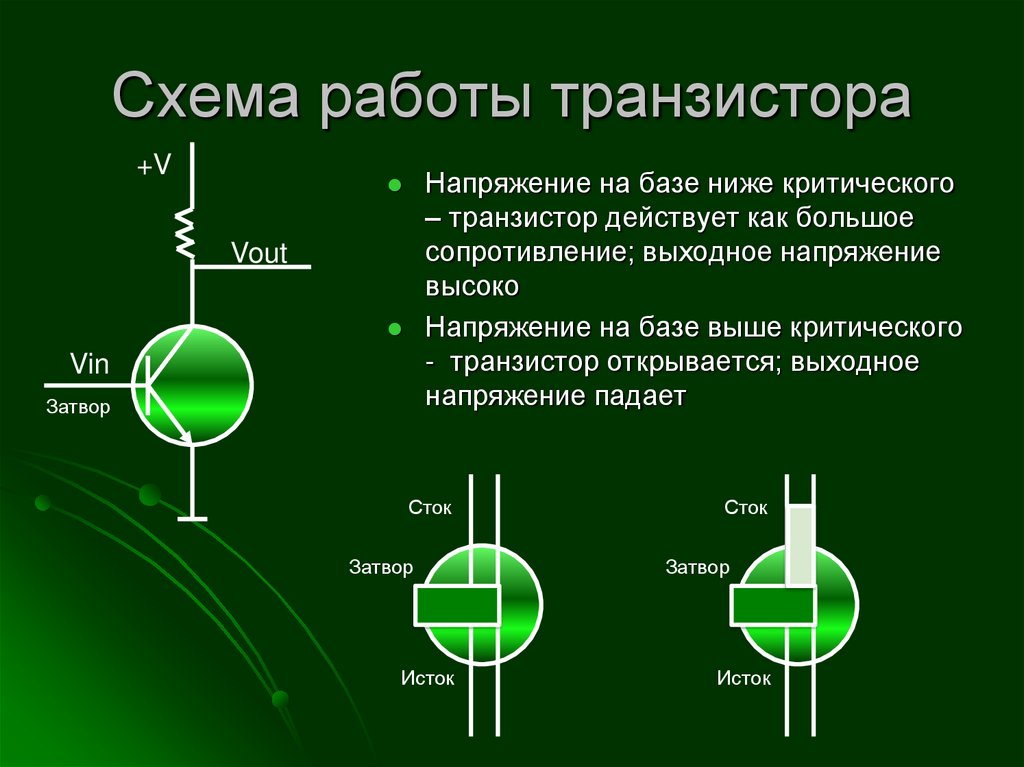

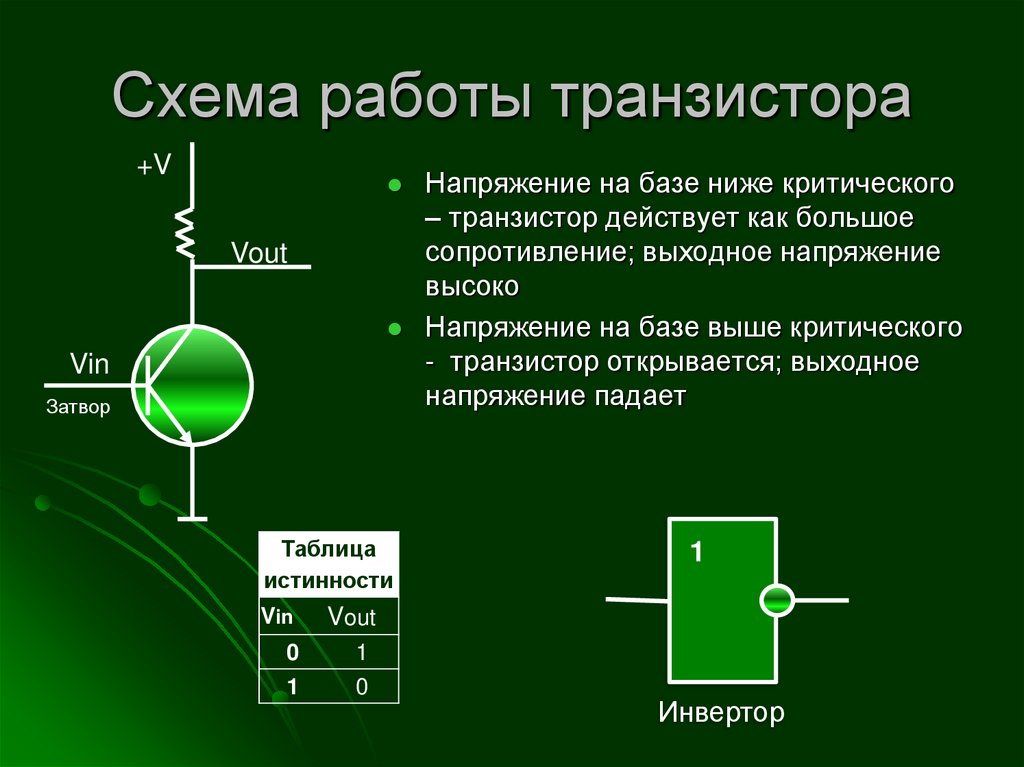

Схема работы транзистора+V

Напряжение на базе ниже критического

– транзистор действует как большое

сопротивление; выходное напряжение

высоко

Напряжение на базе выше критического

- транзистор открывается; выходное

напряжение падает

Vout

Vin

Затвор

Сток

Затвор

Исток

Сток

Затвор

Исток

9. Схема работы транзистора

+VVout

Vin

Затвор

Таблица

истинности

Vin

Vout

0

1

1

0

Напряжение на базе ниже критического

– транзистор действует как большое

сопротивление; выходное напряжение

высоко

Напряжение на базе выше критического

- транзистор открывается; выходное

напряжение падает

1

Инвертор

10. Схема работы транзистора

Построение логическихэлементов на транзисторах

11. Построение логических элементов на транзисторах

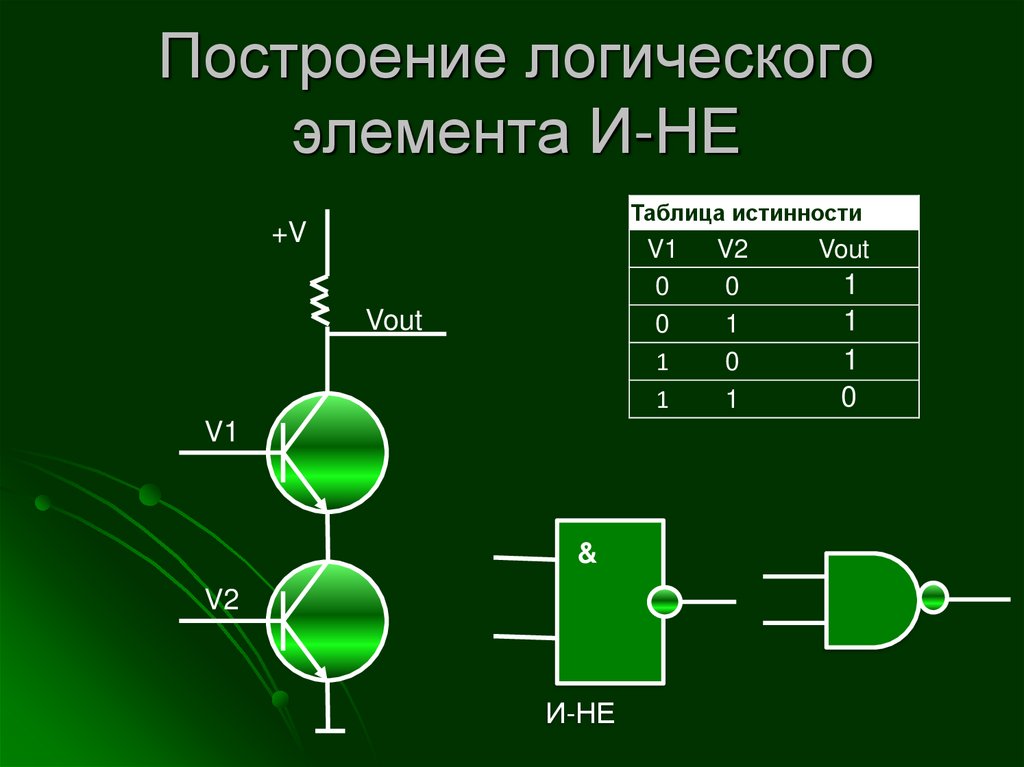

Построение логическогоэлемента И-НЕ

Таблица истинности

+V

V1

0

0

1

1

Vout

V1

&

V2

И-НЕ

V2

0

1

0

1

Vout

1

1

1

0

12. Построение логического элемента И-НЕ

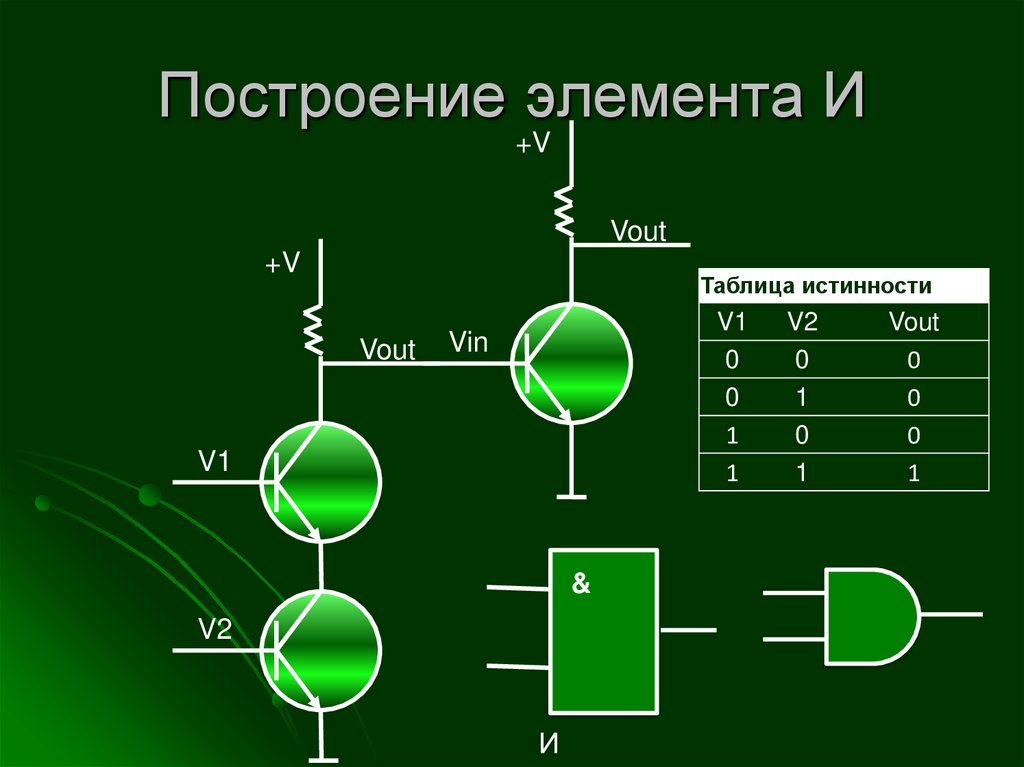

Построение элемента И+V

Vout

+V

Таблица истинности

Vout

V1

0

0

1

1

Vin

V1

&

V2

И

V2

0

1

0

1

Vout

0

0

0

1

13. Построение элемента И

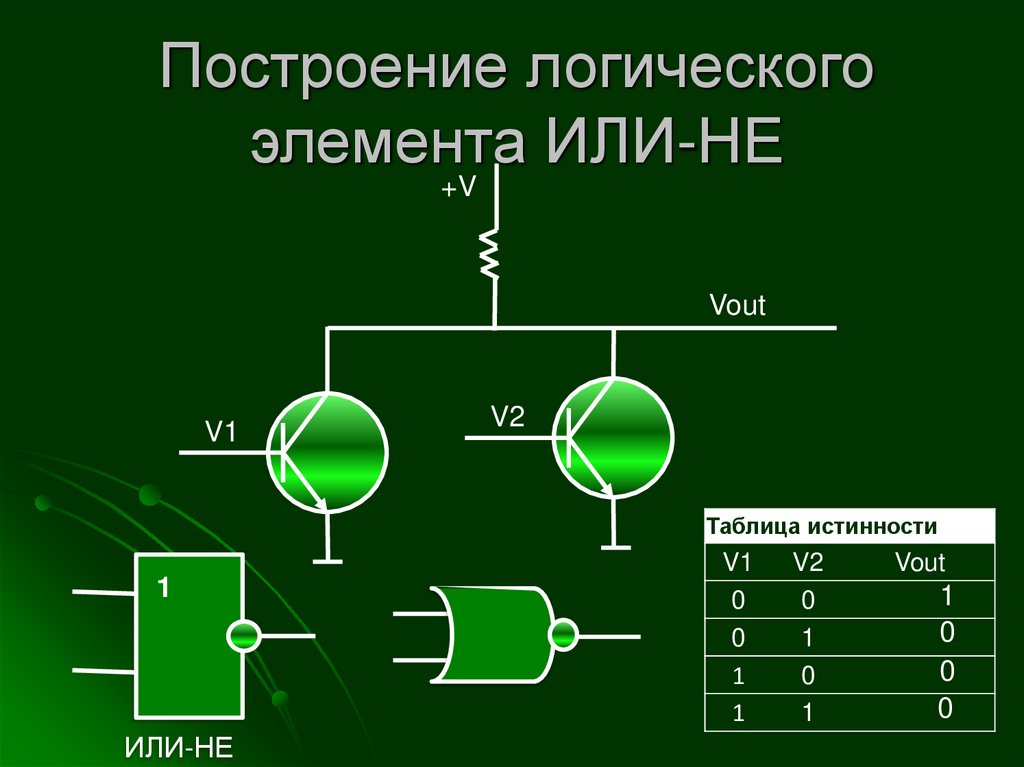

Построение логическогоэлемента ИЛИ-НЕ

+V

Vout

V1

V2

Таблица истинности

1

ИЛИ-НЕ

V1

0

0

1

1

V2

0

1

0

1

Vout

1

0

0

0

14.

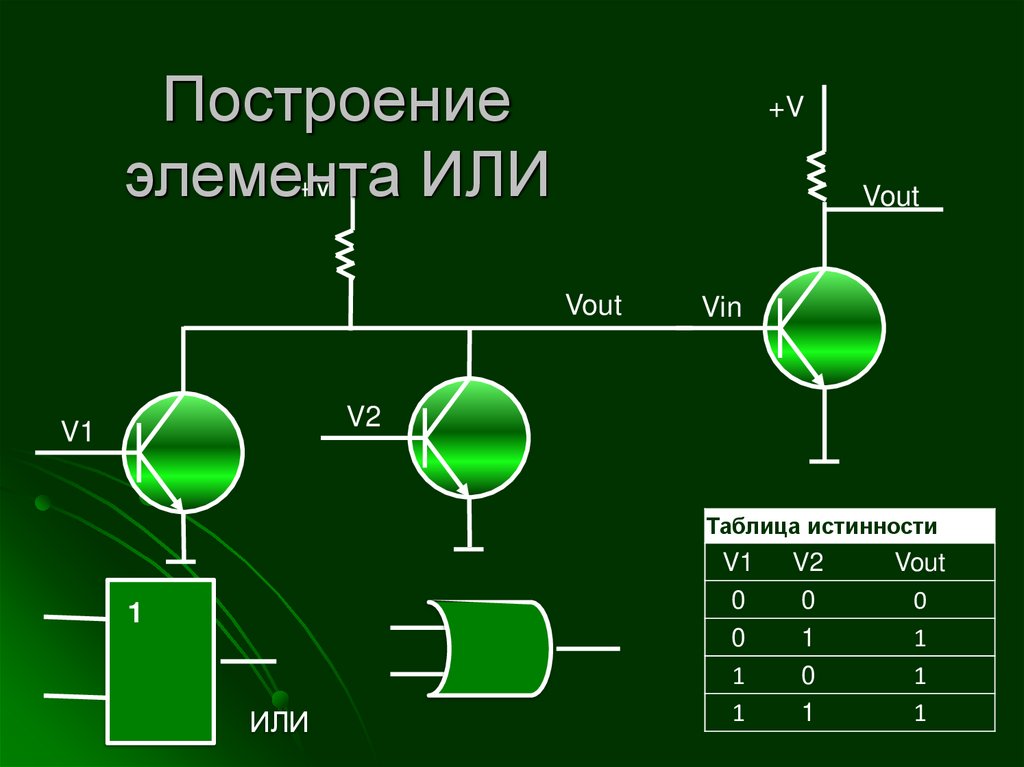

Построениеэлемента

ИЛИ

+V

+V

Vout

Vout

Vin

V2

V1

Таблица истинности

1

ИЛИ

V1

0

0

1

1

V2

0

1

0

1

Vout

0

1

1

1

15.

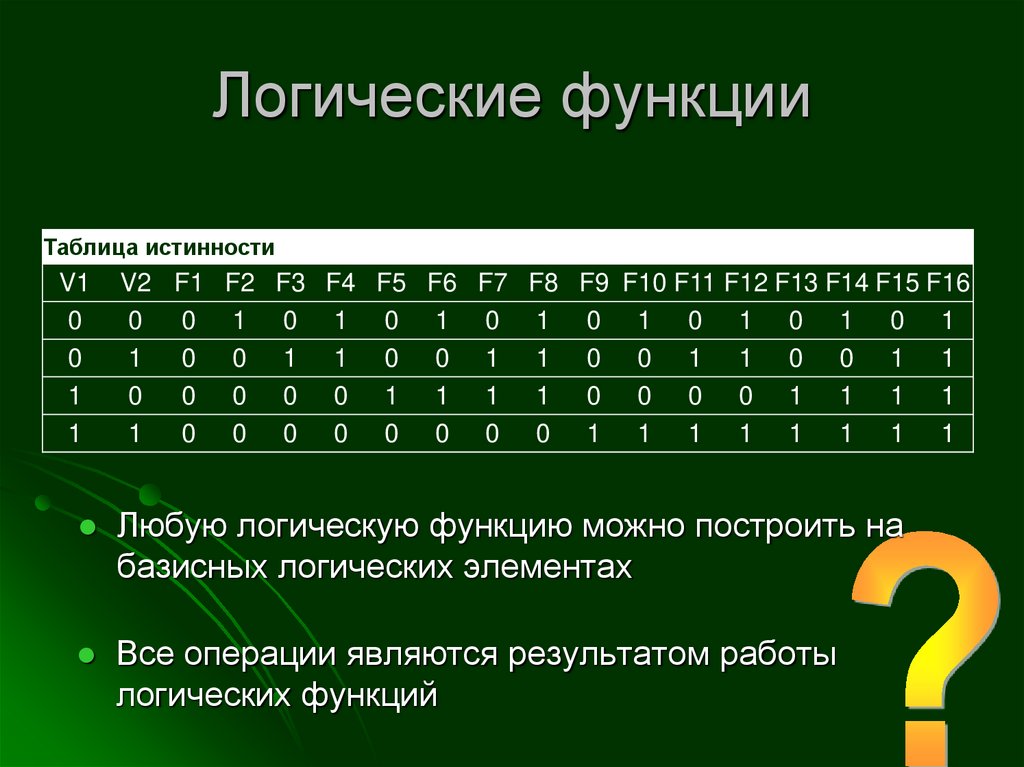

Логические функцииТаблица истинности

V1

0

0

1

1

V2 F1 F2 F3 F4 F5 F6 F7 F8 F9 F10 F11 F12 F13 F14 F15 F16

0

0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

1

0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

0

0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

1

0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

Любую логическую функцию можно построить на

базисных логических элементах

Все операции являются результатом работы

логических функций

16. Логические функции

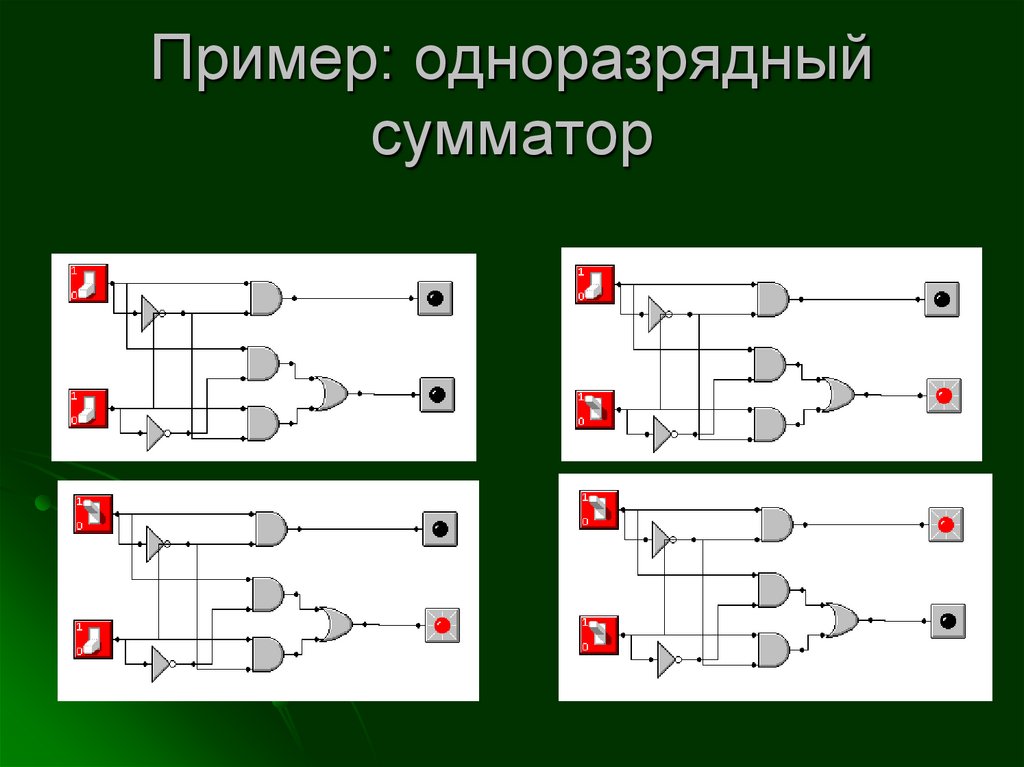

Пример: одноразрядныйсумматор

17. Пример: одноразрядный сумматор

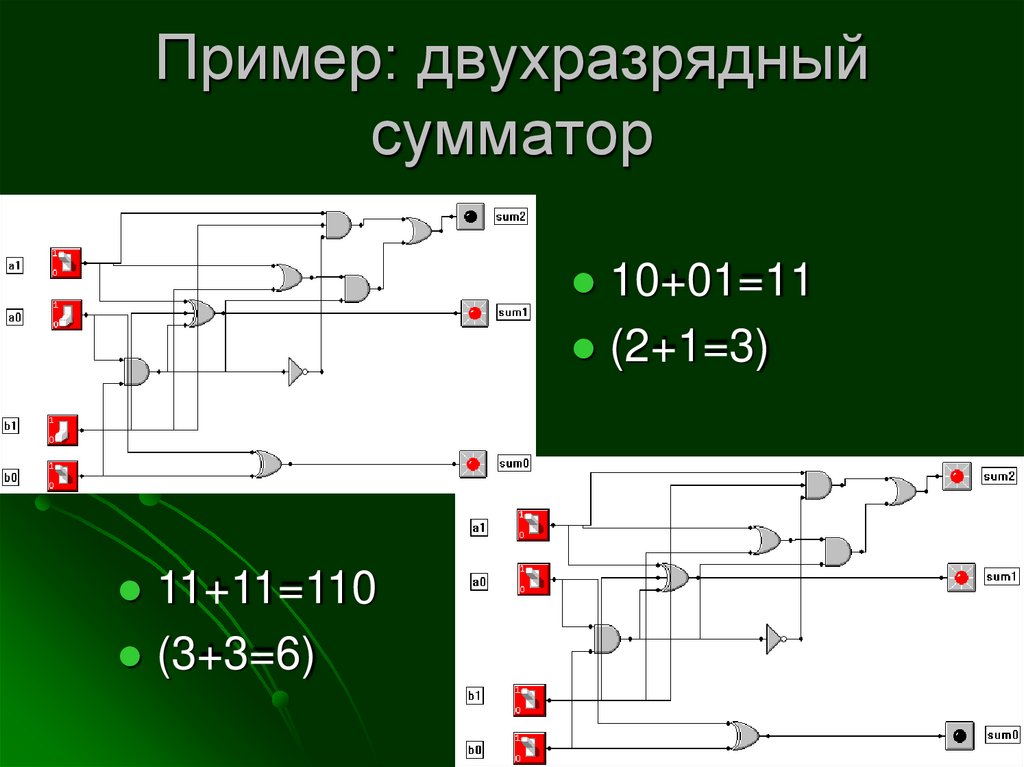

Пример: двухразрядныйсумматор

10+01=11

(2+1=3)

11+11=110

(3+3=6)

18. Пример: двухразрядный сумматор

Логика построения сумматораТаблица истинности для

младшего разряда

V1

0

0

1

1

V2

0

1

0

1

Сумма Перенос

0

1

1

0

0

0

0

1

Таблица истинности для следующих

разрядов

V1

0

0

1

1

0

0

1

1

V2

0

1

0

1

0

1

0

1

Перенос1 Сумма Перенос2

0

0

0

0

1

0

0

1

0

0

0

1

1

1

0

0

1

1

1

0

1

1

1

1

19. Логика построения сумматора

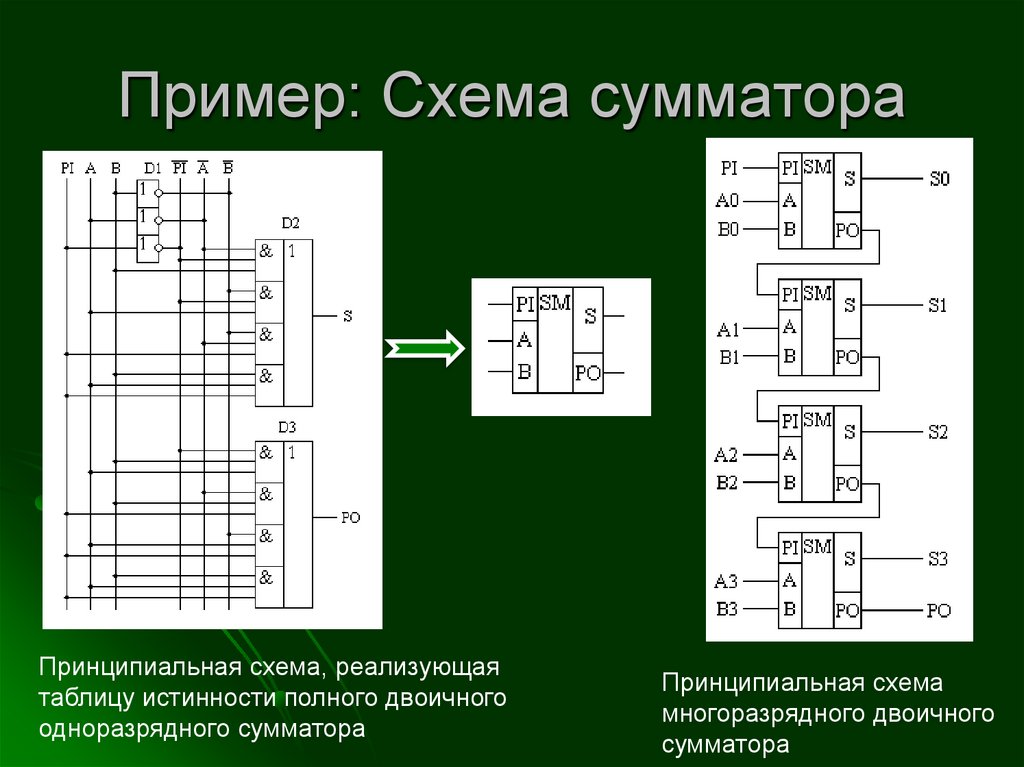

Пример: Схема сумматораПринципиальная схема, реализующая

таблицу истинности полного двоичного

одноразрядного сумматора

Принципиальная схема

многоразрядного двоичного

сумматора

20. Пример: Схема сумматора

Построение запоминающихэлементов на транзисторах

Триггер – устройство для хранения бита

информации

R

1

Q

1

S

Q

21. Построение запоминающих элементов на транзисторах

Устройство триггера0

R

1

Q

0

1

Q

S

1

0

Таблица истинности ИЛИ-НЕ

V1

0

0

1

1

V2

0

1

0

1

Vout

1

0

0

0

R=0

S=0

Не

изменяет

состояние

триггера

22. Устройство триггера

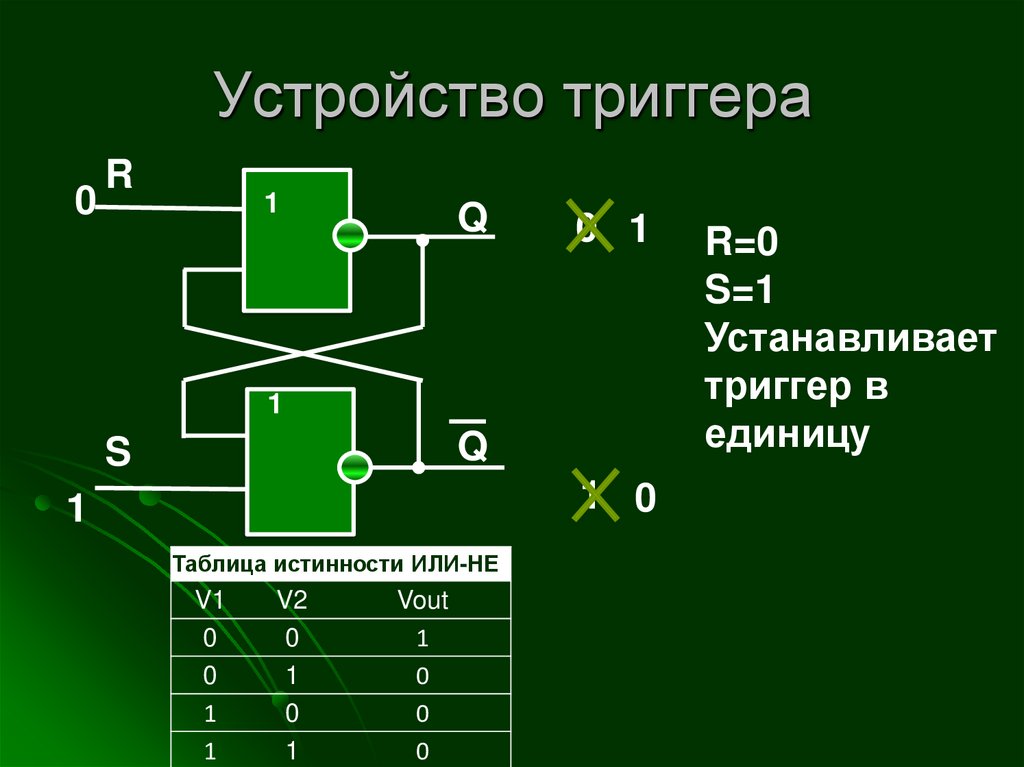

0R

1

Q

0 1

1

Q

S

1 0

1

Таблица истинности ИЛИ-НЕ

V1

0

0

1

1

V2

0

1

0

1

Vout

1

0

0

0

R=0

S=1

Устанавливает

триггер в

единицу

23. Устройство триггера

1R

1

Q

1 0

1

Q

S

0 1

0

Таблица истинности ИЛИ-НЕ

V1

0

0

1

1

V2

0

1

0

1

Vout

1

0

0

0

R=1

S=0

Устанавливает

триггер в ноль

24. Устройство триггера

1R

1

Q

1

Q

S

1

Таблица истинности ИЛИ-НЕ

V1

0

0

1

1

V2

0

1

0

1

Vout

1

0

0

0

R=1

S=1

Запрещенная

комбинация

25. Устройство триггера

Триггер – устройство для хранения битаинформации

R

1

Q

1

S

Q

26. Устройство триггера

Схема синхронного RSтриггера на элементах 2И-НЕОдин элемент И-НЕ

Один триггер

Условное графическое

обозначение синхронного RSтриггера

27. Схема синхронного RS-триггера на элементах 2И-НЕ

Для чего применяются триггерыРегистр –

1 1 0

упорядоченная

последовательность

триггеров

Один 8-ми

разрядный регистр

В настоящее время применяются

64-разрядные регистры

1 0 1 1 0

28. Для чего применяются триггеры

Вывод: на транзисторахможно реализовать логику

любого уровня сложности как

для преобразования данных,

так и для хранения данных

29. Вывод: на транзисторах можно реализовать логику любого уровня сложности как для преобразования данных, так и для хранения

Алгоритм работы процессора30. Алгоритм работы процессора

Алгоритм работы процессора:обращение в память за командой

31. Алгоритм работы процессора: обращение в память за командой

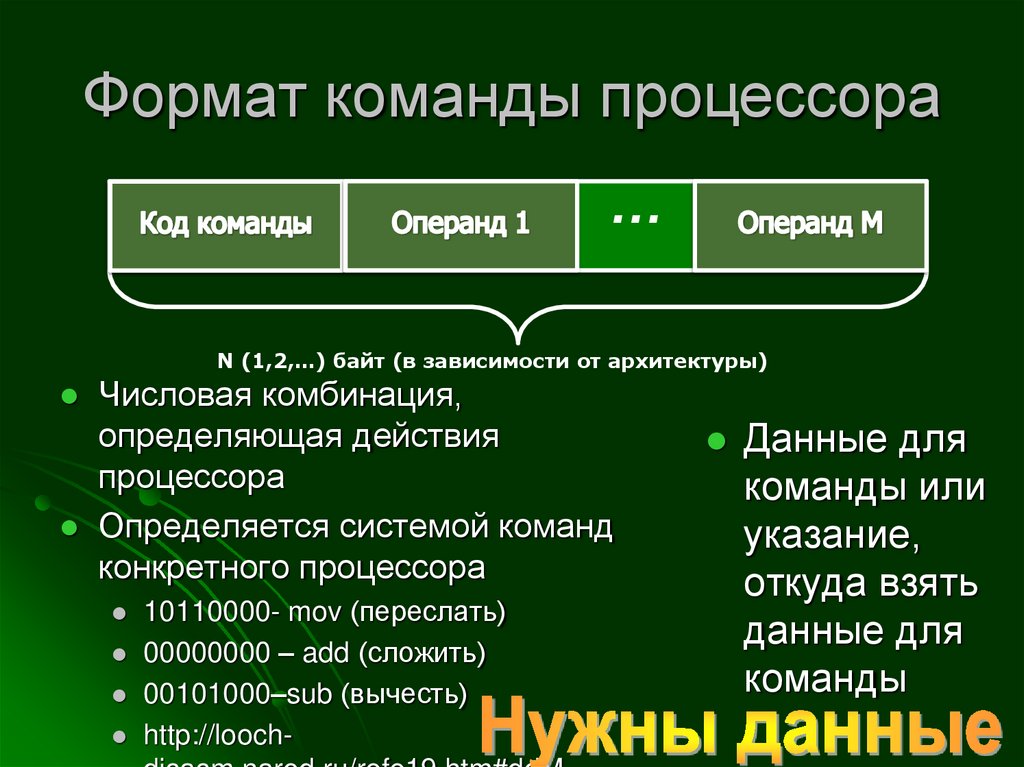

Формат команды процессора…

N (1,2,…) байт (в зависимости от архитектуры)

Числовая комбинация,

определяющая действия

процессора

Определяется системой команд

конкретного процессора

10110000- mov (переслать)

00000000 – add (сложить)

00101000–sub (вычесть)

http://looch

Данные для

команды или

указание,

откуда взять

данные для

команды

32. Формат команды процессора

Алгоритм работы процессора:обращение в память за командой

33. Алгоритм работы процессора: обращение в память за командой

34. Алгоритм работы процессора: обращение в память за командой

35. Алгоритм работы процессора: обращение в память за командой

36. Алгоритм работы процессора: обращение в память за командой

Алгоритм работы процессораВыбор команды

Дешифрация

Запрос операндов

Выполнение команды

с получением

результата и/или

формированием

признаков

Запись результата

Увеличение

(изменение) счетчика

команд

37. Алгоритм работы процессора

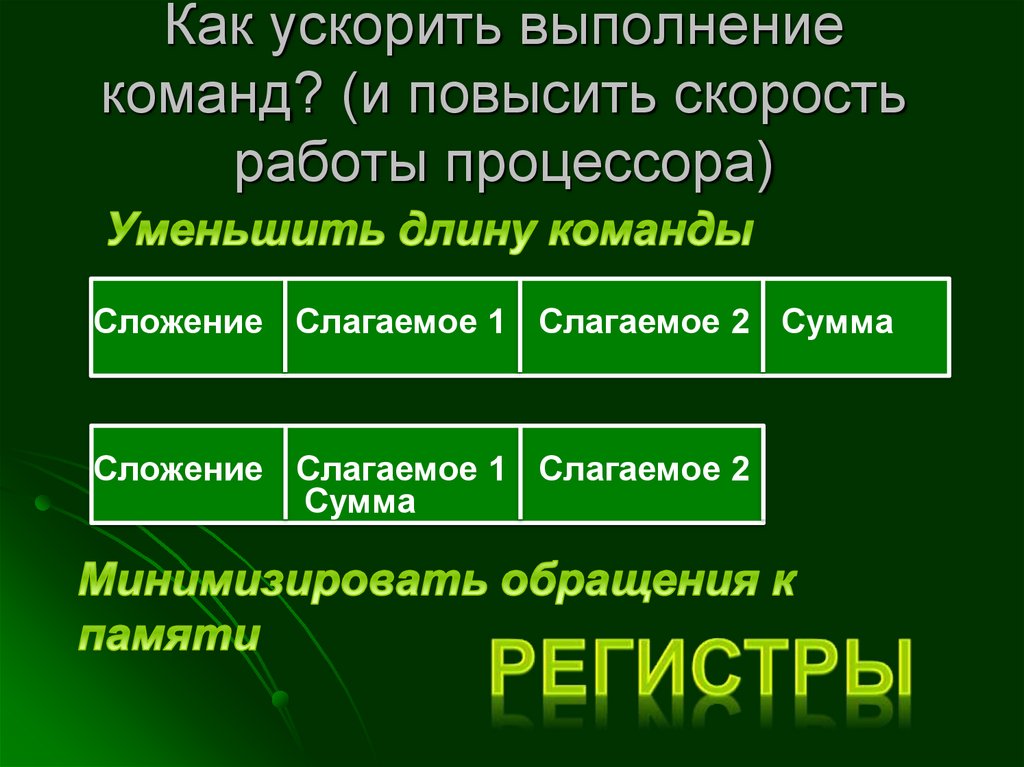

Как ускорить выполнениекоманд? (и повысить скорость

работы процессора)

Сложение Слагаемое 1 Слагаемое 2 Сумма

Сложение Слагаемое 1 Слагаемое 2

Сумма

38. Как ускорить выполнение команд? (и повысить скорость работы процессора)

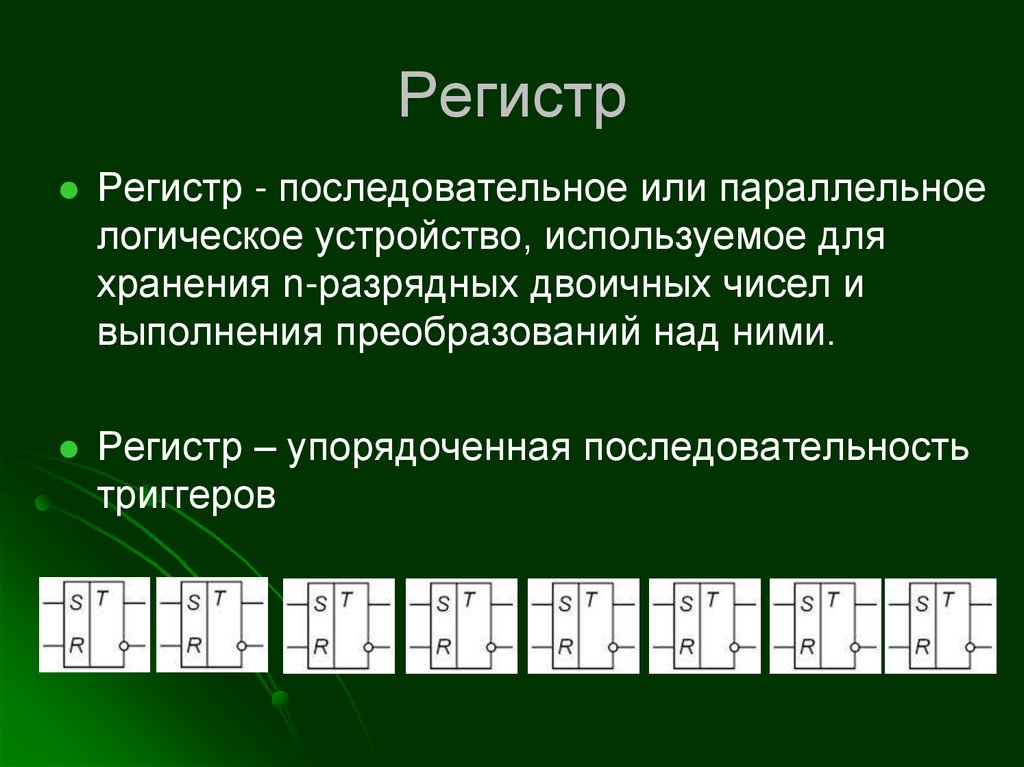

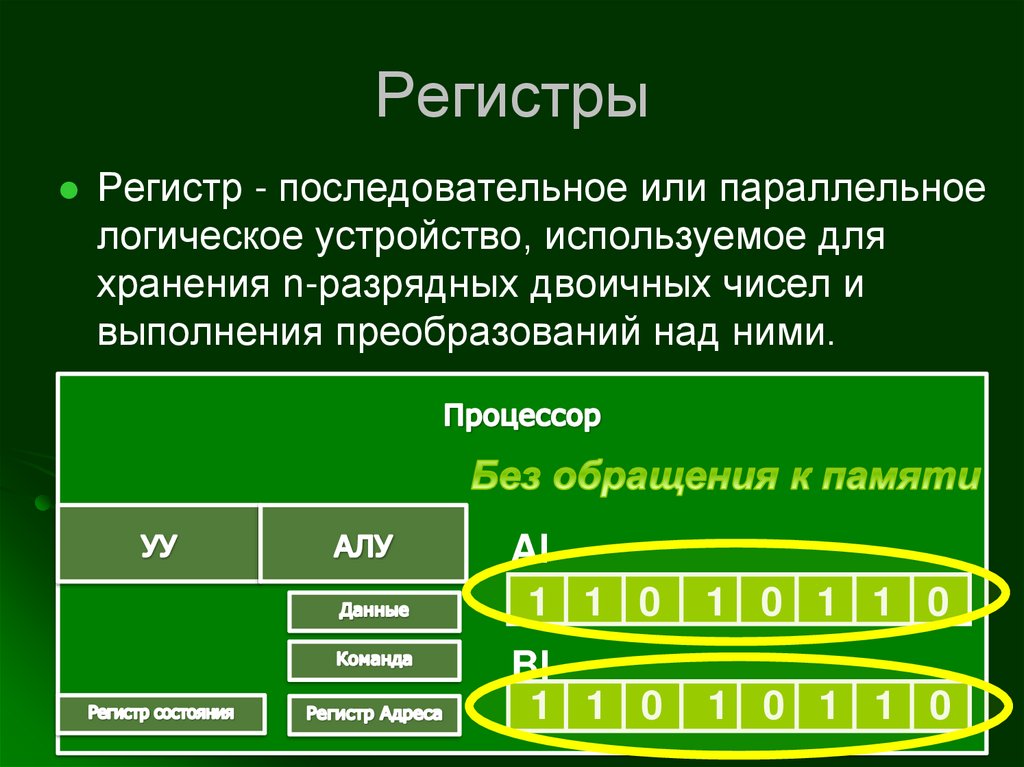

РегистрРегистр - последовательное или параллельное

логическое устройство, используемое для

хранения n-разрядных двоичных чисел и

выполнения преобразований над ними.

Регистр – упорядоченная последовательность

триггеров

39. Регистр

Основные регистрыпроцессора

40. Основные регистры процессора

РегистрыРегистр - последовательное или параллельное

логическое устройство, используемое для

хранения n-разрядных двоичных чисел и

выполнения преобразований над ними.

Al

1 1 0

1 0 1 1 0

Bl

1 1 0

1 0 1 1 0

41. Регистры

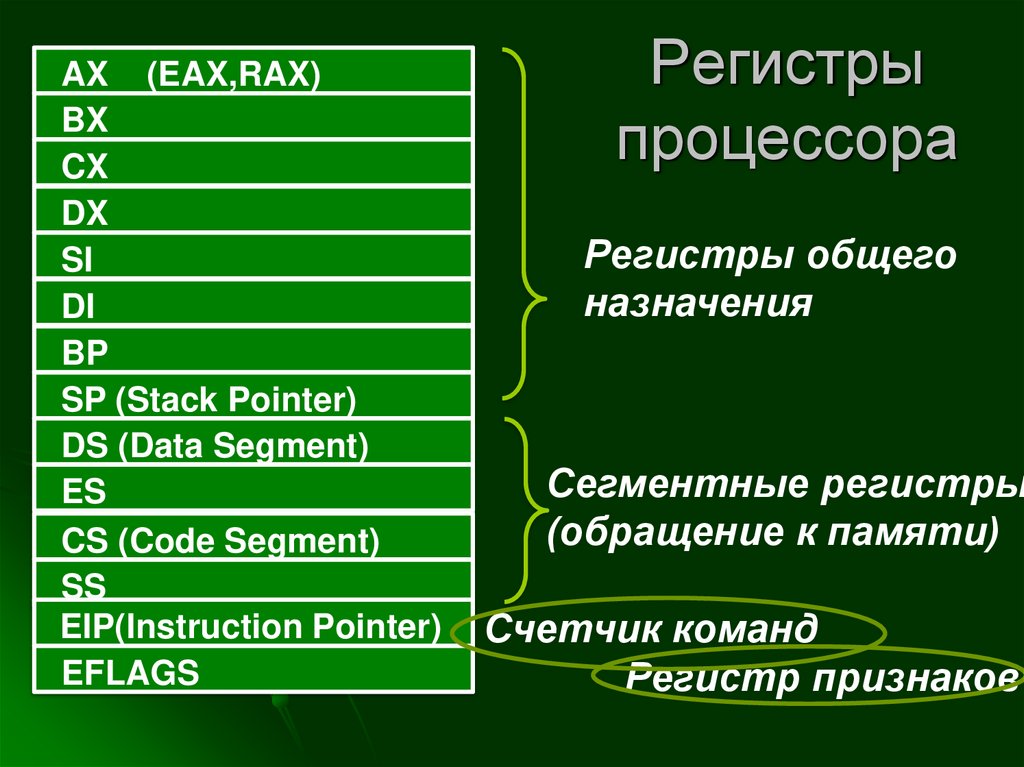

AX (EAX,RAX)BX

CX

DX

SI

DI

BP

SP (Stack Pointer)

DS (Data Segment)

ES

CS (Code Segment)

SS

EIP(Instruction Pointer)

register)

EFLAGS ()

Регистры

процессора

Регистры общего

назначения

Сегментные регистры

(обращение к памяти)

Счетчик команд

Регистр признаков

42. Регистры процессора

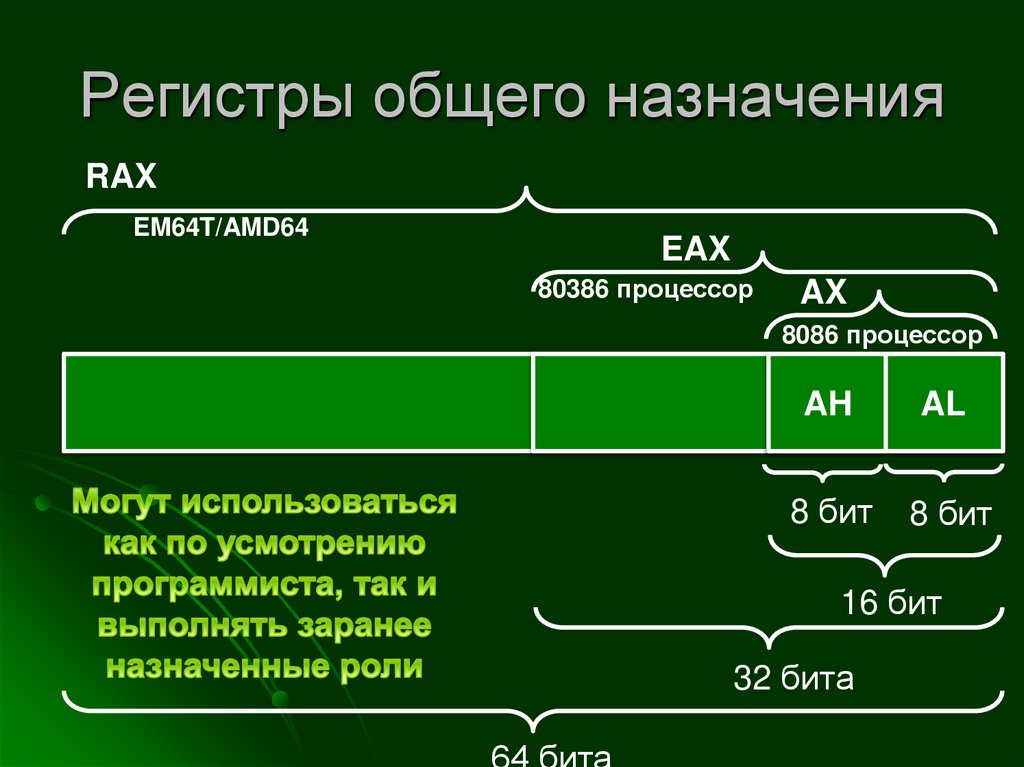

Регистры общего назначенияRAX

EM64T/AMD64

EAX

80386 процессор

AX

8086 процессор

AH

AL

8 бит

8 бит

16 бит

32 бита

43. Регистры общего назначения

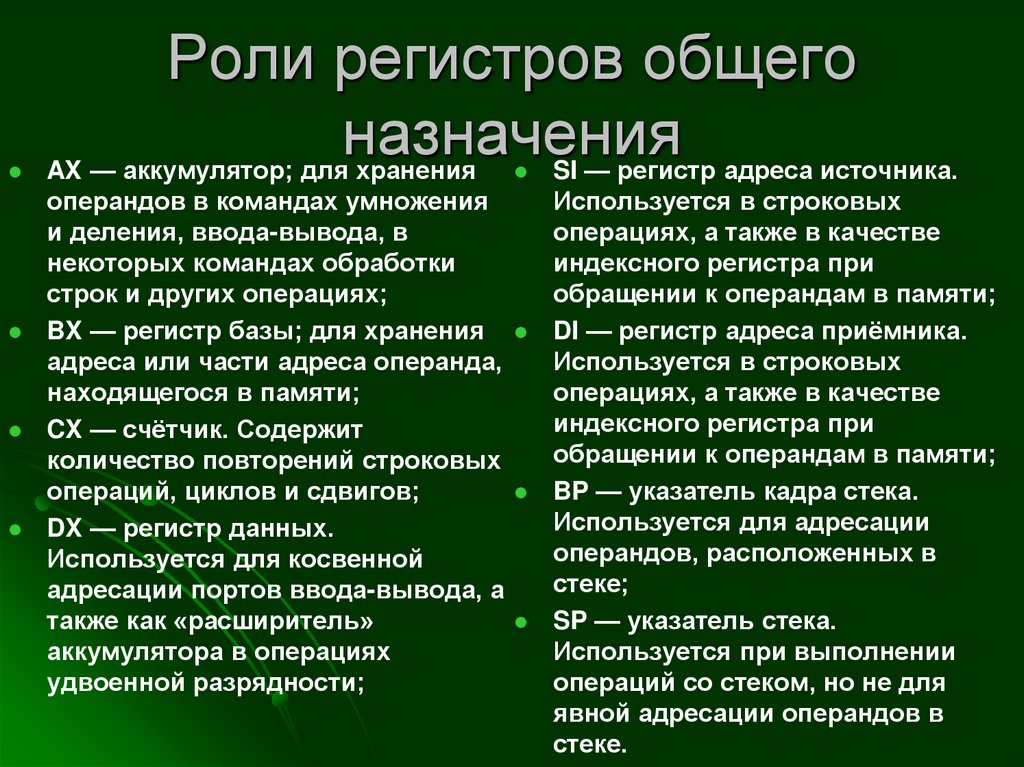

Роли регистров общегоназначения

AX — аккумулятор; для хранения

SI — регистр адреса источника.

операндов в командах умножения

и деления, ввода-вывода, в

некоторых командах обработки

строк и других операциях;

BX — регистр базы; для хранения

адреса или части адреса операнда,

находящегося в памяти;

CX — счётчик. Содержит

количество повторений строковых

операций, циклов и сдвигов;

DX — регистр данных.

Используется для косвенной

адресации портов ввода-вывода, а

также как «расширитель»

аккумулятора в операциях

удвоенной разрядности;

Используется в строковых

операциях, а также в качестве

индексного регистра при

обращении к операндам в памяти;

DI — регистр адреса приёмника.

Используется в строковых

операциях, а также в качестве

индексного регистра при

обращении к операндам в памяти;

BP — указатель кадра стека.

Используется для адресации

операндов, расположенных в

стеке;

SP — указатель стека.

Используется при выполнении

операций со стеком, но не для

явной адресации операндов в

стеке.

44. Роли регистров общего назначения

Сегментные регистрыСегмент – выделенная

область пространства

памяти

CS сегмента кода - в

каком месте памяти

находится программа

DS сегмента данных локализует

используемые

программой данные.

ES дополняет сегмент

данных.

SS сегмента стека стек компьютера.

45. Сегментные регистры

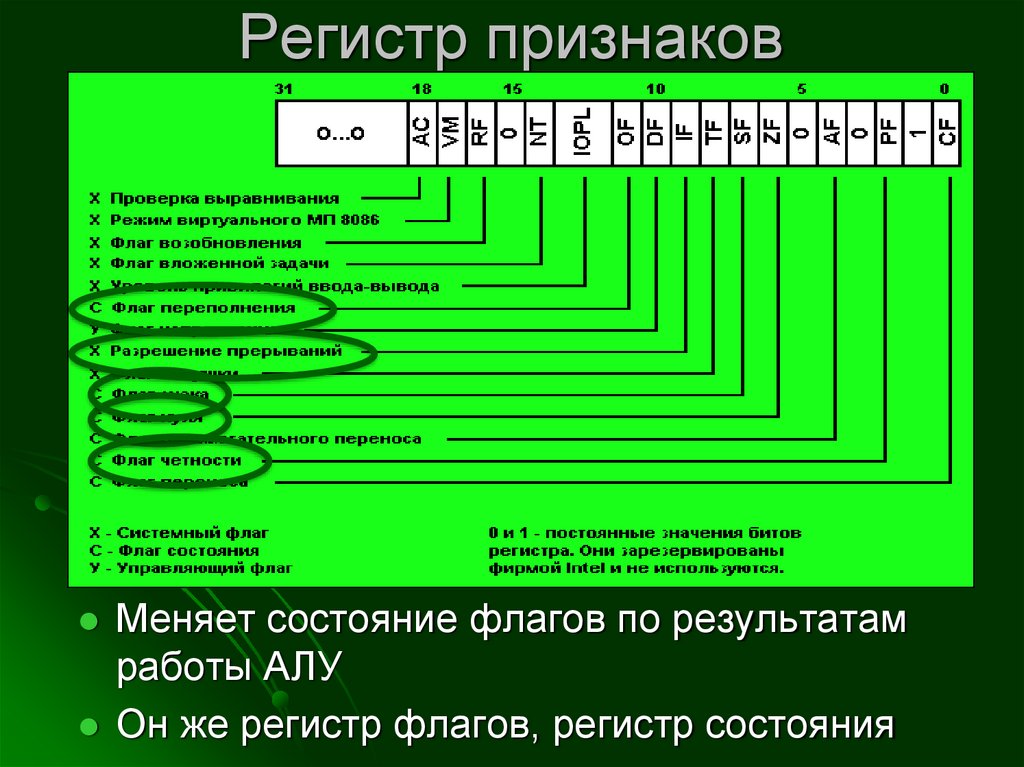

Регистр признаковМеняет состояние флагов по результатам

работы АЛУ

Он же регистр флагов, регистр состояния

46. Регистр признаков

Выводы:БОльшая часть команд процессора

выполняется с использованием регистров

Регистры позволяют сократить время за счет

минимизации обращений к оперативной памяти

В регистре Счетчик Команд хранится адрес

выполняемой инструкции

Регистр состояния процессора отображает

результаты выполнения последней команды

47. Выводы: БОльшая часть команд процессора выполняется с использованием регистров Регистры позволяют сократить время за счет

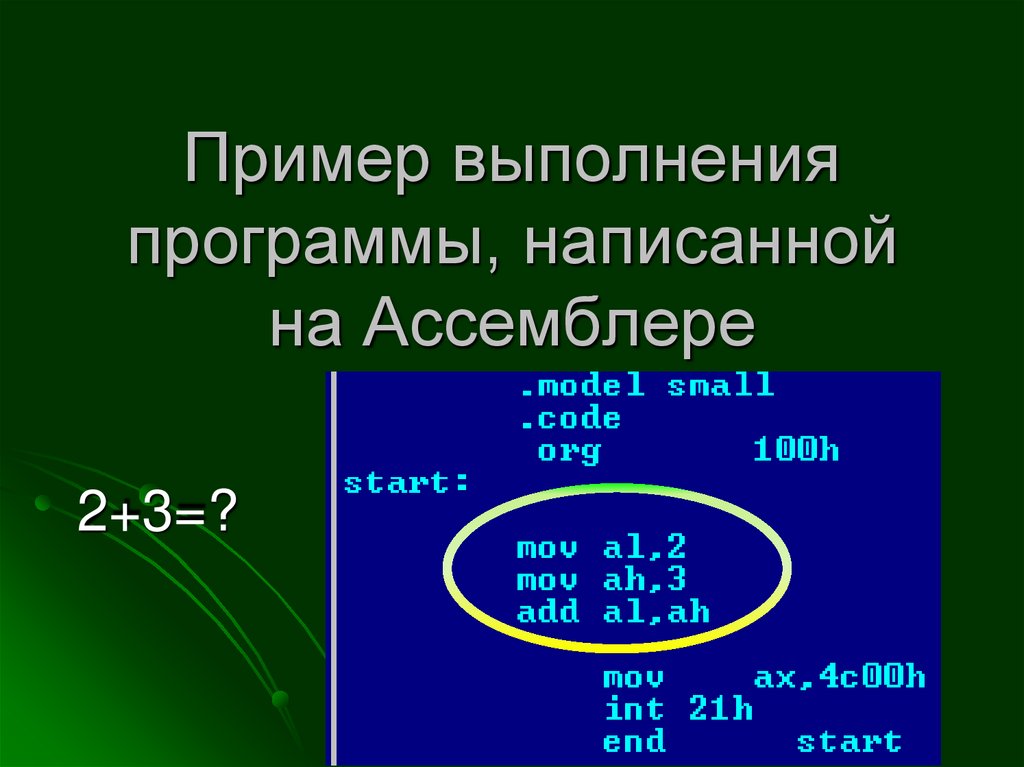

Пример выполненияпрограммы, написанной

на Ассемблере

2+3=?

48. Пример выполнения программы, написанной на Ассемблере

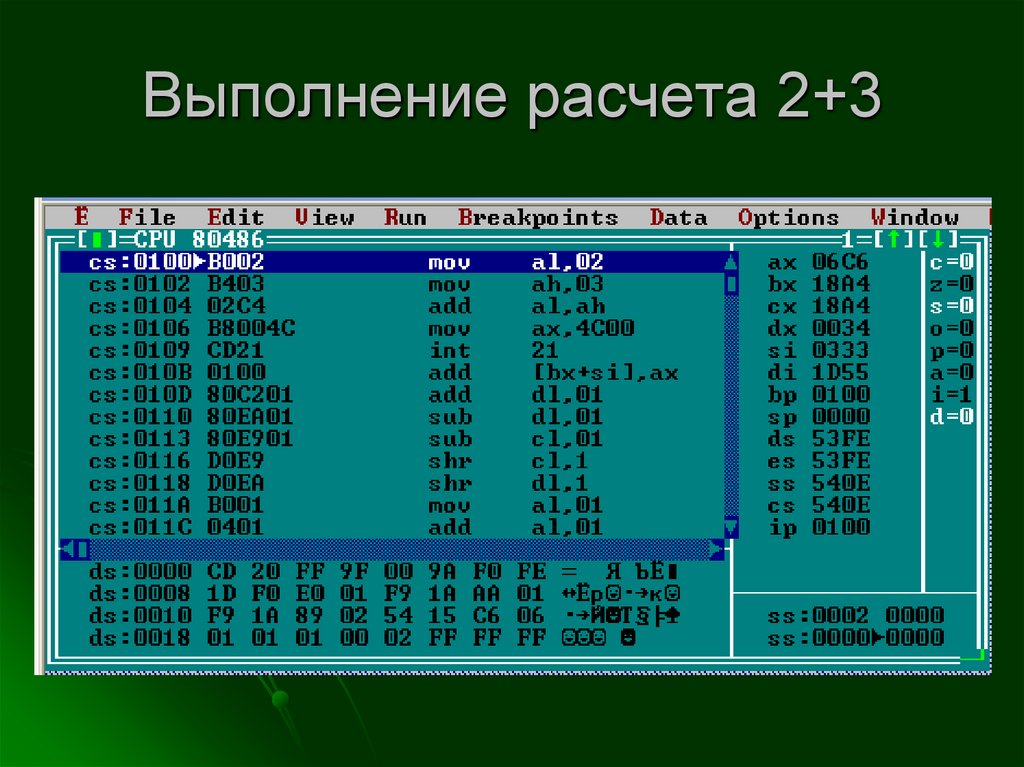

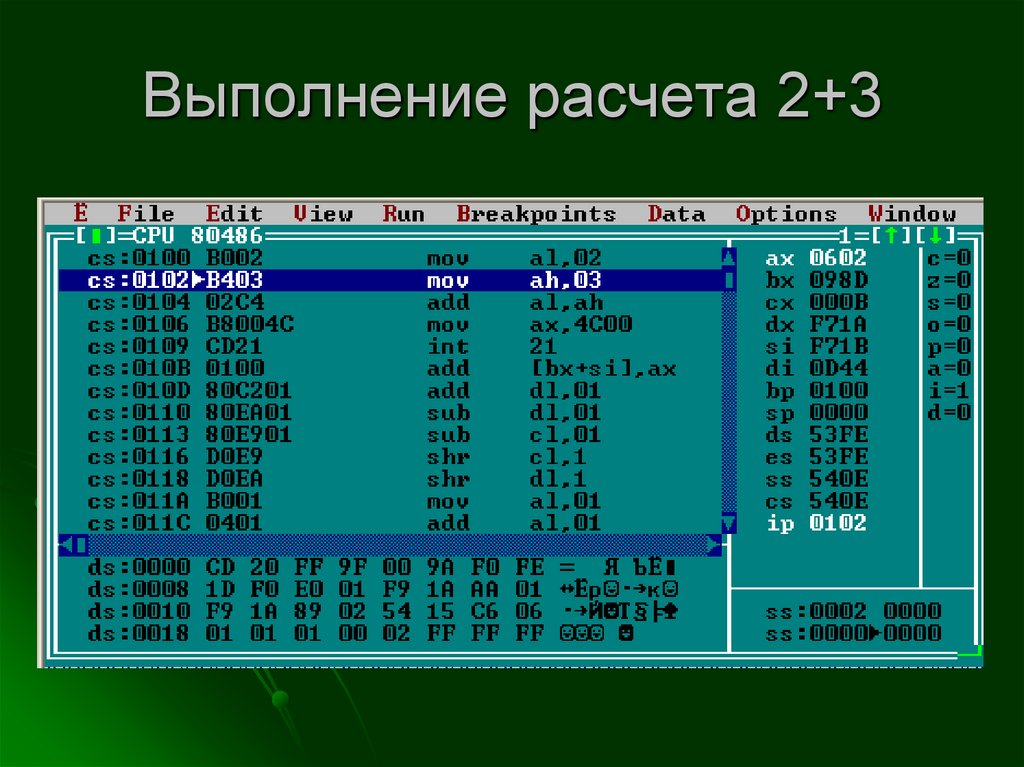

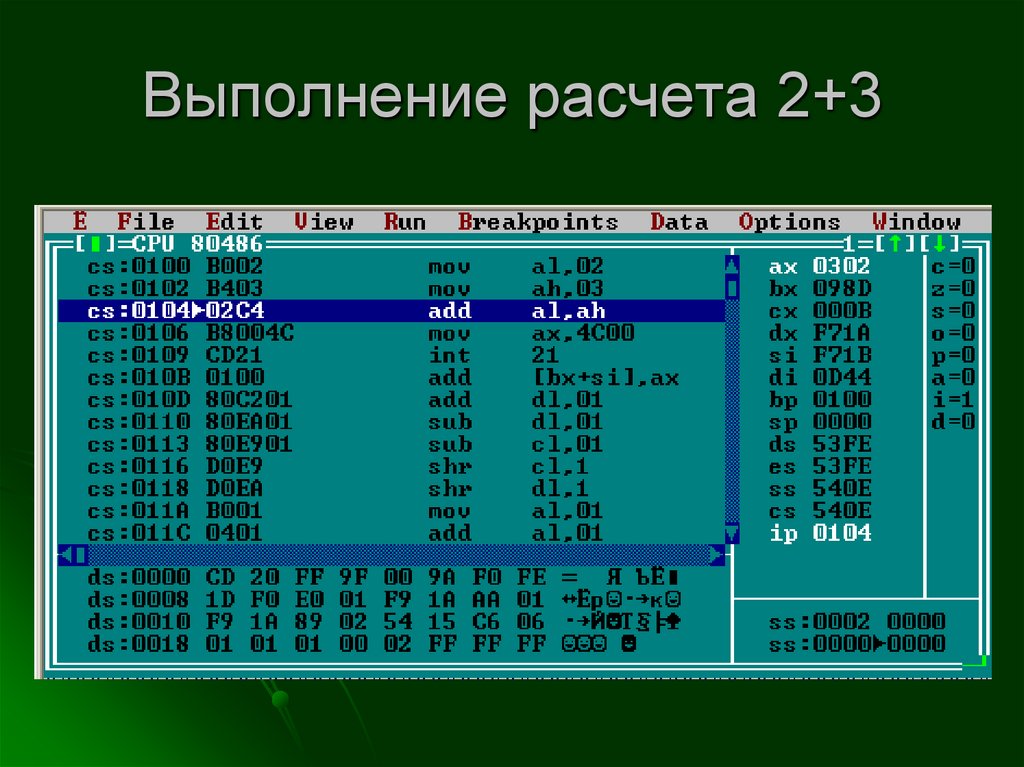

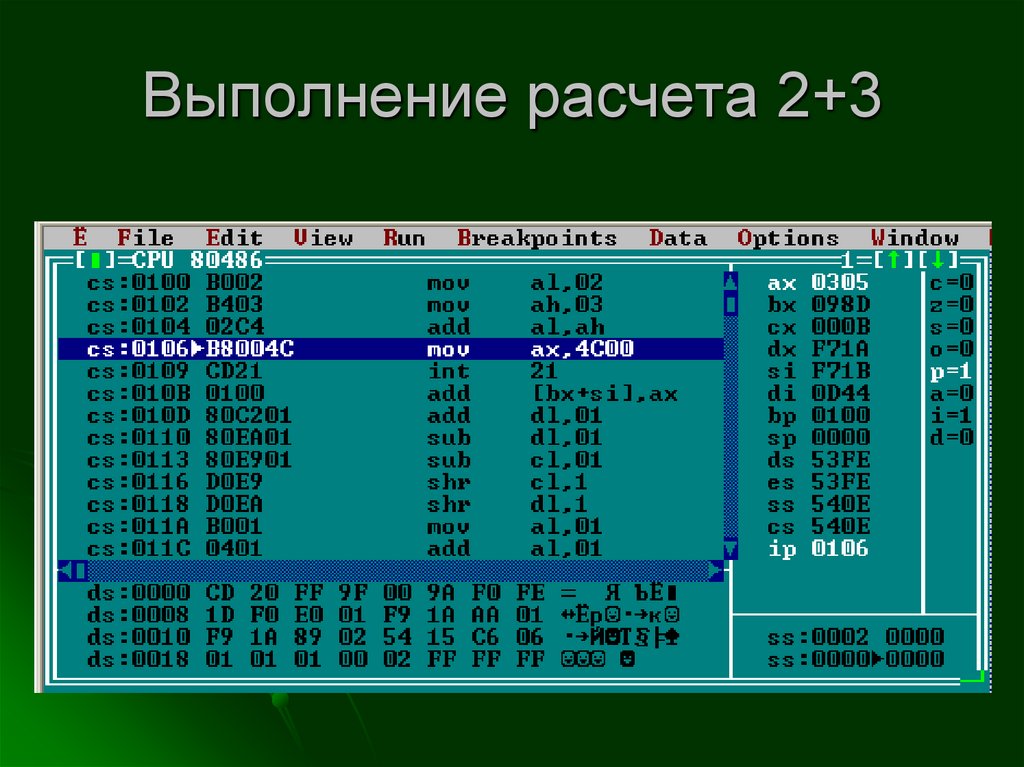

Выполнение расчета 2+349. Выполнение расчета 2+3

50. Выполнение расчета 2+3

51. Выполнение расчета 2+3

52. Выполнение расчета 2+3

ТЕСТПримеры команд процессора

и демонстрация работы

процессора при выполнении

некоторых команд

53. Примеры команд процессора и демонстрация работы процессора при выполнении некоторых команд

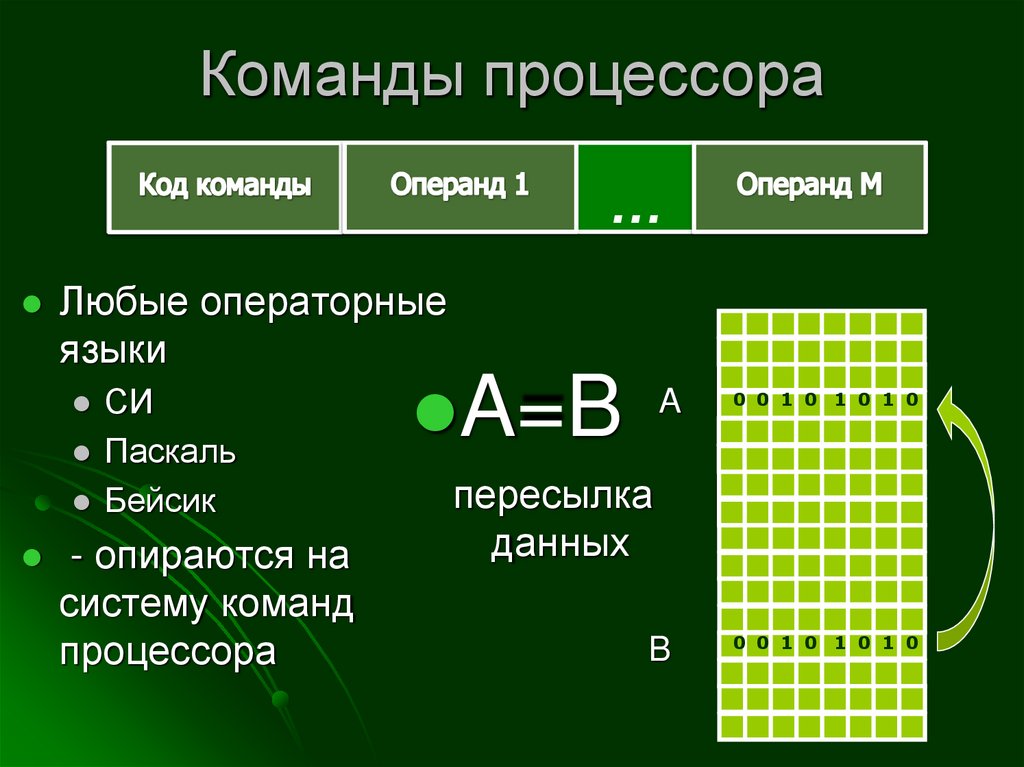

Команды процессора…

Любые операторные

языки

СИ

Паскаль

Бейсик

- опираются на

систему команд

процессора

A=B

A

0 0 1 0

1 0 1 0

B

0 0 1 0

1 0 1 0

пересылка

данных

54.

Система командКоманды пересылки

Команды обработки данных:

Арифметические

Логические команды

Команды сдвига

Команды ветвления или управления

Команды обращения к процедурам

Системные команды

55. Система команд

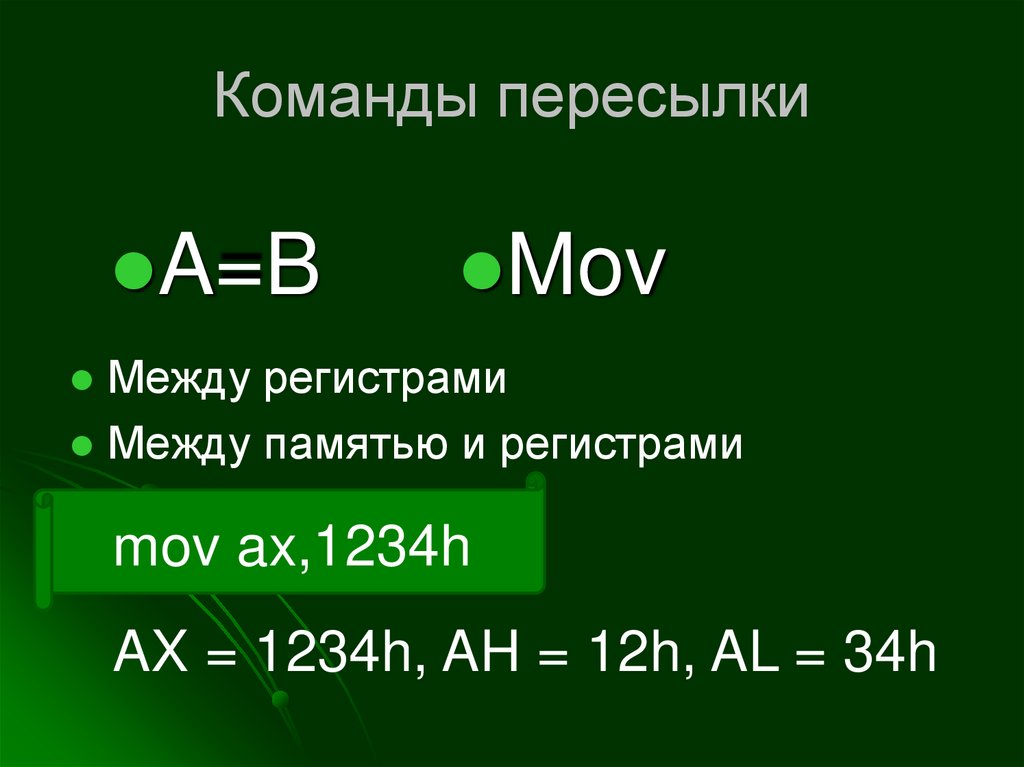

Команды пересылкиA=B

Mov

Между регистрами

Между памятью и регистрами

mov ax,1234h

AX = 1234h, AH = 12h, AL = 34h

56. Команды пересылки

Al0 0 0

1 0 0 1 0

1 1 0

0 0 0 1 1

Бит знака

Al 12h

Бит нуля

MOV

Бит четности

Выполнение команды пересылки

57. Выполнение команды пересылки

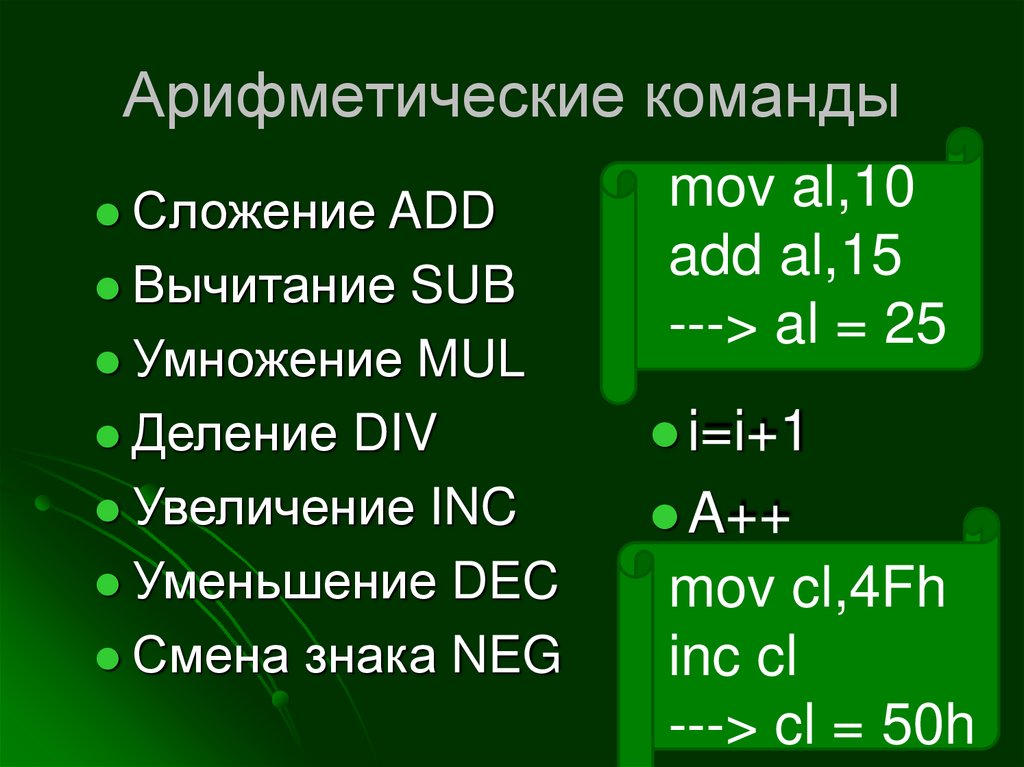

Арифметические командыСложение ADD

Вычитание SUB

Умножение MUL

mov al,10

add al,15

---> al = 25

Деление DIV

i=i+1

Увеличение INC

A++

Уменьшение DEC

mov cl,4Fh

inc cl

---> cl = 50h

Смена знака NEG

58. Арифметические команды

Выполнение команды сложениеAl

0 0 0

1 0 0 1 0

Bl

0 0 0

0 0 1 1 0

0 0 0

1 1 0 0 0

Бит знака

Bl

Бит четности

Al

0 1

0

Бит нуля

Сложение

59. Выполнение команды сложение

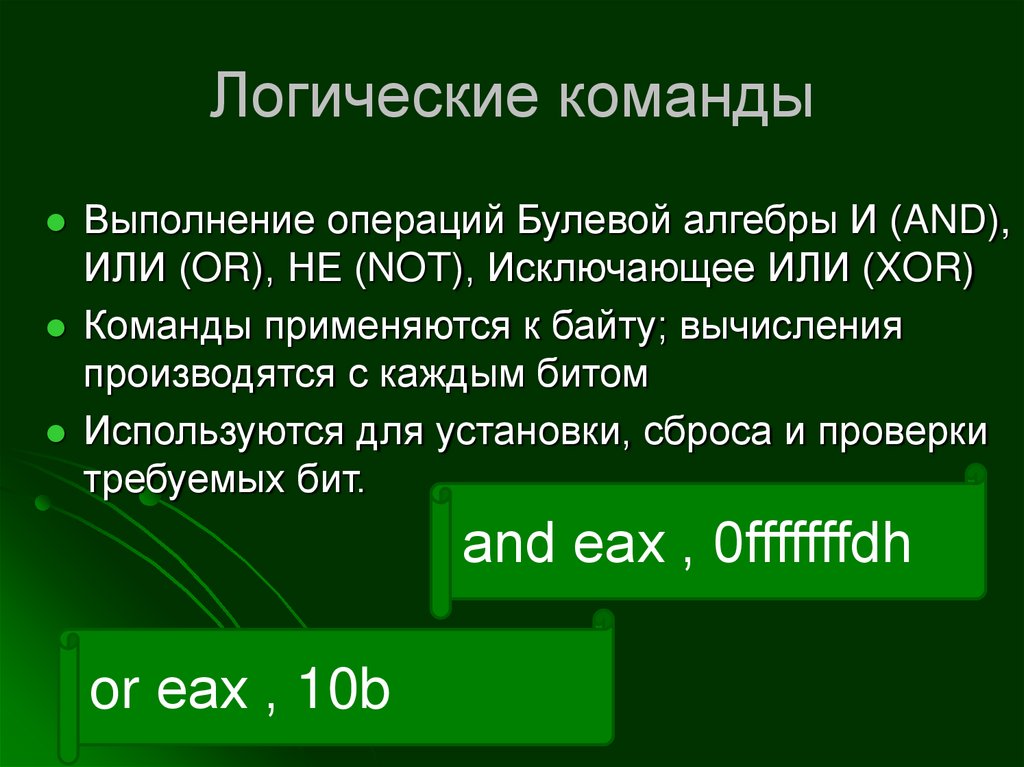

Логические командыВыполнение операций Булевой алгебры И (AND),

ИЛИ (OR), НЕ (NOT), Исключающее ИЛИ (XOR)

Команды применяются к байту; вычисления

производятся с каждым битом

Используются для установки, сброса и проверки

требуемых бит.

and еах , 0fffffffdh

or еах , 10b

60. Логические команды

Выполнение команды логическоеумножение

0 0 0

0 0 0

1 0 0 1 0

0 1 1 1 1

0 0 0 1 0

Бит знака

0 0 0

0F

Бит четности

Al

Al

0 0

0

Бит нуля

AND

61. Выполнение команды логическое умножение

Команды сдвигаЛогический сдвиг

shr al,1

Циклический сдвиг

rol al,1

62. Команды сдвига

Выполнение команды сдвига0 0 0

0 0 0

1 0 0 1 0

0 0 0 0 1

0 1 0 0 1

Бит знака

0 0 0

1

Бит четности

Al

Al

0 1

0

Бит нуля

SHR

63. Выполнение команды сдвига

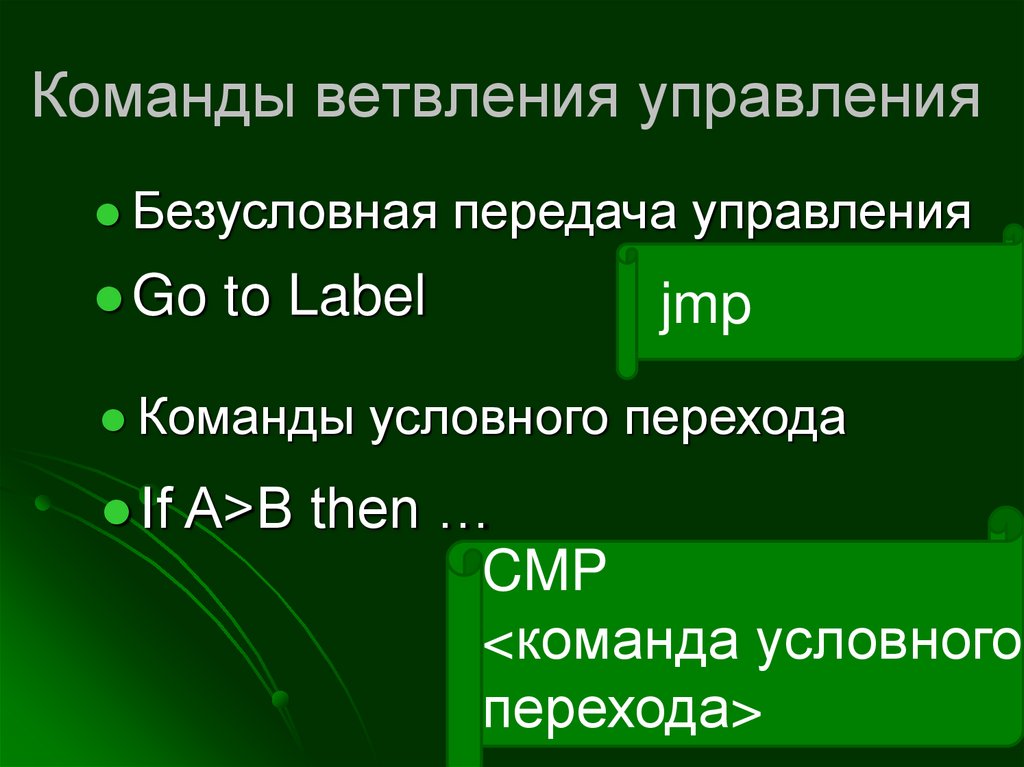

Команды ветвления управленияБезусловная передача управления

Go to Label

jmp

Команды условного перехода

If A>B then …

CMP

<команда условного

перехода>

64. Команды ветвления управления

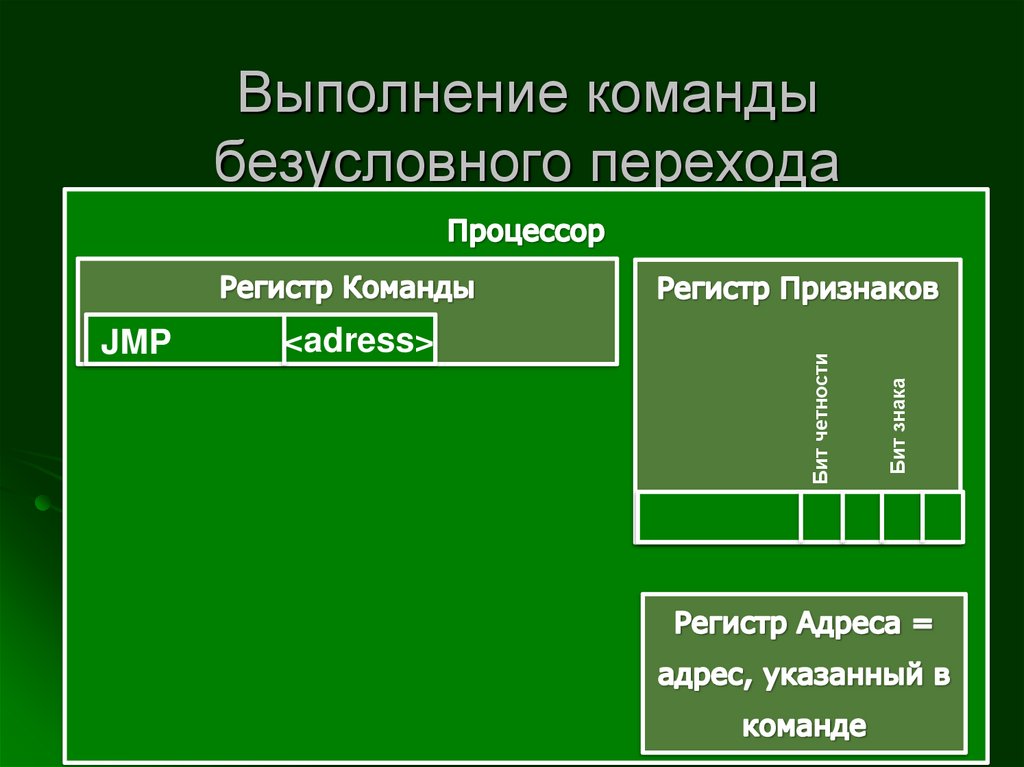

<adress>Бит знака

JMP

Бит четности

Выполнение команды

безусловного перехода

65. Выполнение команды безусловного перехода

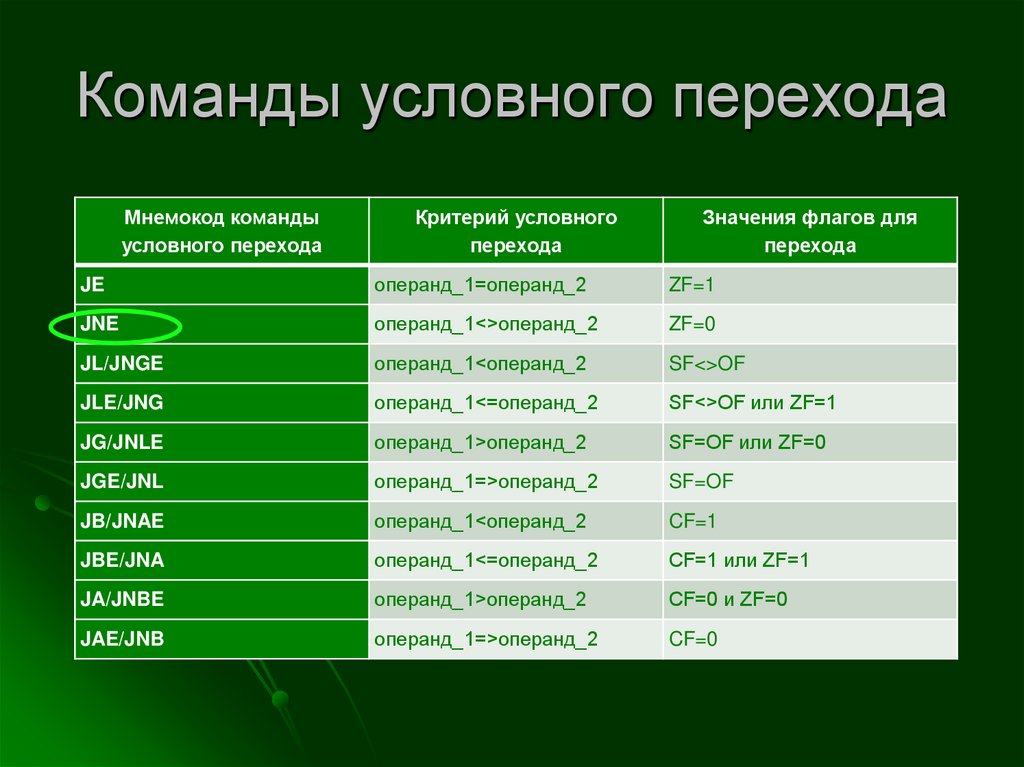

Команды условного переходаМнемокод команды

условного перехода

Критерий условного

перехода

Значения флагов для

перехода

JE

операнд_1=операнд_2

ZF=1

JNE

операнд_1<>операнд_2

ZF=0

JL/JNGE

операнд_1<операнд_2

SF<>OF

JLE/JNG

операнд_1<=операнд_2

SF<>OF или ZF=1

JG/JNLE

операнд_1>операнд_2

SF=OF или ZF=0

JGE/JNL

операнд_1=>операнд_2

SF=OF

JB/JNAE

операнд_1<операнд_2

CF=1

JBE/JNA

операнд_1<=операнд_2

CF=1 или ZF=1

JA/JNBE

операнд_1>операнд_2

CF=0 и ZF=0

JAE/JNB

операнд_1=>операнд_2

CF=0

66. Команды условного перехода

Выполнение условного переходаAl

0 0 0

1 0 0 1 0

Bl

0 0 0

0 0 1 1 0

0 0 0

0 1 1 0 0

Бит знака

Bl

Бит четности

Al

0 1

0

Бит нуля

CMP

67. Выполнение условного перехода

0 0 01 0 0 1 0

Bl

0 0 0

0 0 1 1 0

Бит знака

Al

Бит четности

<address>

0 1

0

Бит нуля

JNE

68. Выполнение условного перехода

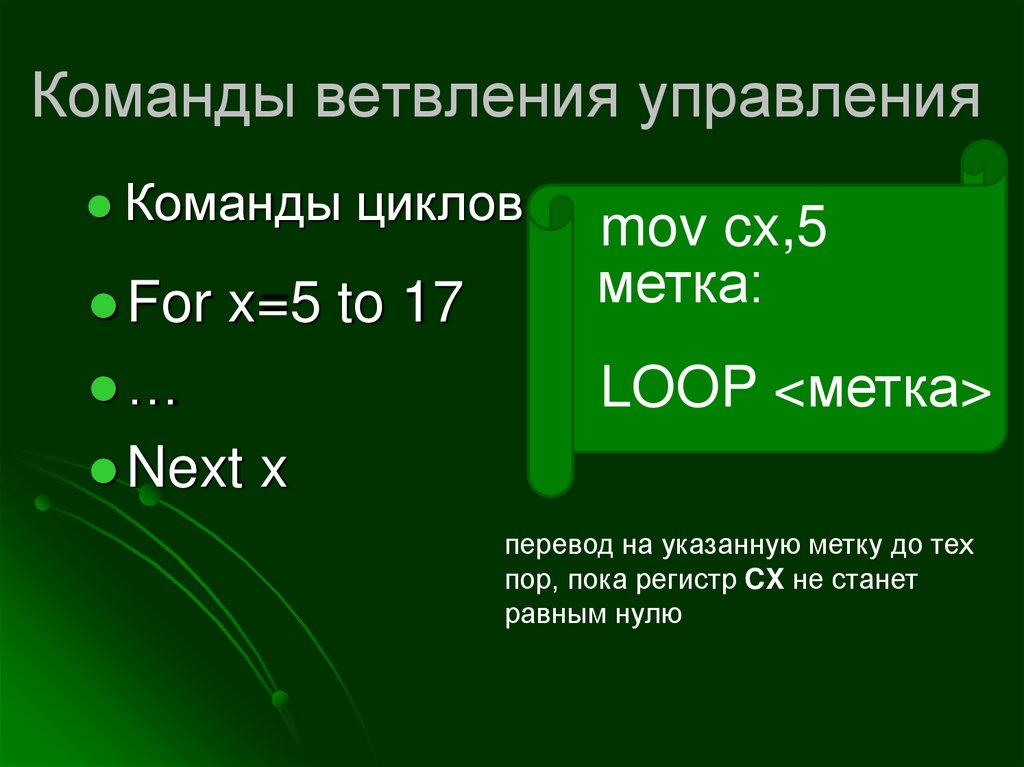

Команды ветвления управленияКоманды циклов

For x=5 to 17

mov cx,5

метка:

…

LOOP <метка>

Next x

перевод на указанную метку до тех

пор, пока регистр CX не станет

равным нулю

69. Команды ветвления управления

0 0 05

0 0 1 0 1

Бит знака

CX

CX

Бит нуля

MOV

Бит четности

Реализация цикла

70. Реализация цикла

0 0 00 0 0

0 0 1 0 1

0 0 0 0 1

0 0 1 0 0

Бит знака

0 0 0

Бит четности

CX

<adress>

0 0

0

Бит нуля

LOOP

71. Реализация цикла

0 0 00 0 0

0 0 0 0 1

0 0 0 0 1

0 0 0 0 0

Бит знака

0 0 0

Бит четности

CX

<adress>

1 1

0

Бит нуля

LOOP

72. Реализация цикла

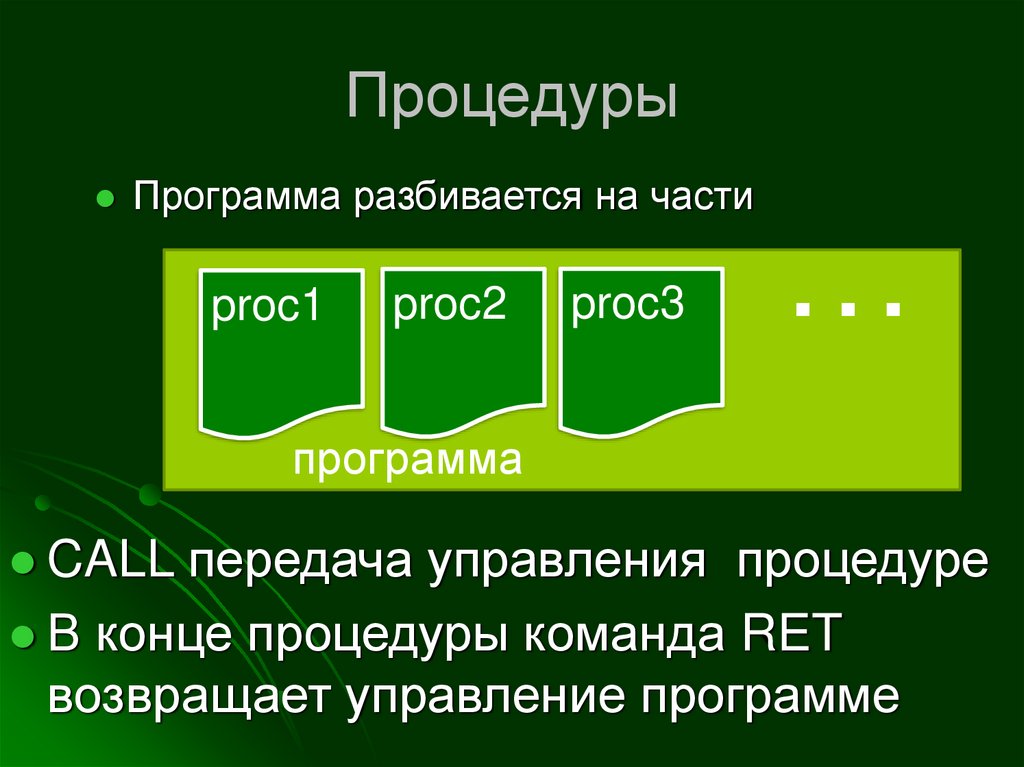

ПроцедурыПрограмма разбивается на части

proc1

proc2

proc3

…

программа

CALL передача управления

процедуре

В конце процедуры команда RET

возвращает управление программе

73. Процедуры

Использование процедурпрограмма

…

…

CALL proc1

CALL proc2

CALL proc1

CALL proc3

proc1

proc2

proc3

74. Использование процедур

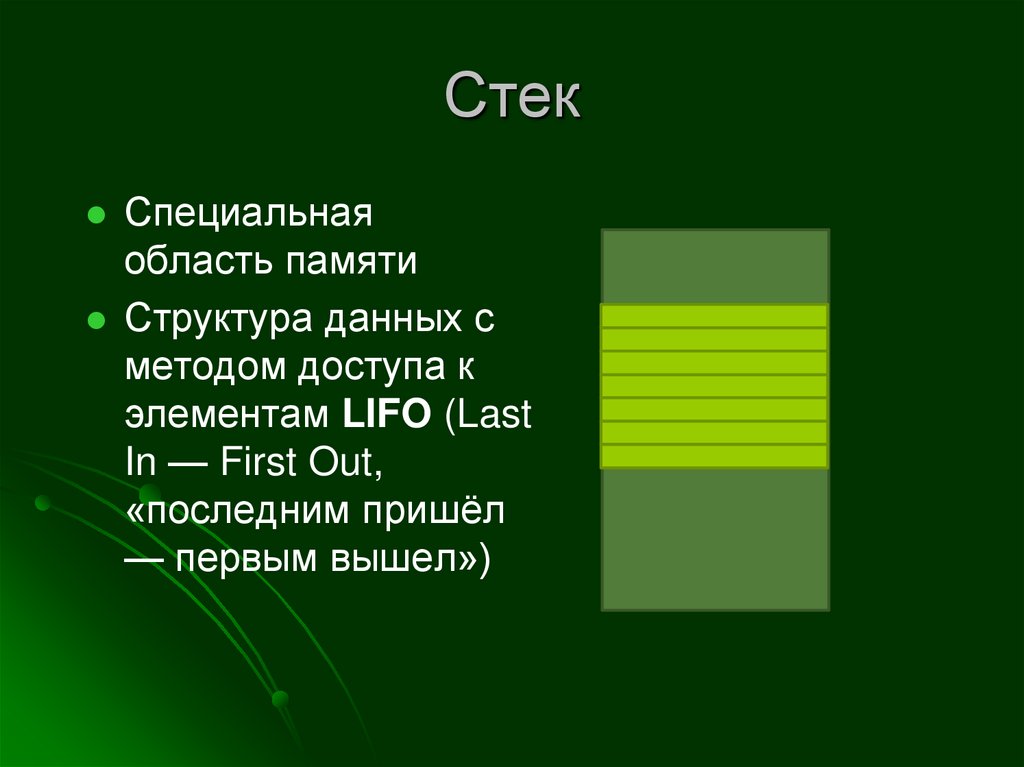

СтекСпециальная

область памяти

Структура данных с

методом доступа к

элементам LIFO (Last

In — First Out,

«последним пришёл

— первым вышел»)

75. Стек

Размещение и извлечениезначений в стеке

1202

mov ax, 4560h

push ax

mov cx, FFFFh

push cx

pop edx

ESP

1203 FF

ESP

1204 FF

1205 60

ESP

1206 45

1207

1208

1209

120A

edx: 4560FFFFh

76. Размещение и извлечение значений в стеке

Обращения к процедурам0002

0056

0003

0057

По завершении процедуры

процессор должен уметь

вернуть управление

программе

0091

0058

0005

0092

1024

0059

1025

0006 Call

0093 Call

0060

0094

1026

0007

0061

0001

0004

0008

0009

0010

0011

0012

Call

0062

1027

0095

1028 Ret

0096

0063

0064 Ret

0097

Ret

Адрес возврата

записывается в стек

0094

0062

0007

77. Обращения к процедурам

Адресация…

N (1,2,…) байт (в зависимости от архитектуры)

Прямая

Косвенная (адрес

адреса операнда)

78. Адресация

Прямая адресацияmov ax,1234h

add bx,ax

79. Прямая адресация

Косвенная адресацияОперанд указывает на

адрес требуемых данных

mov ax,[cx]

add ax,[bx+2]

80. Косвенная адресация

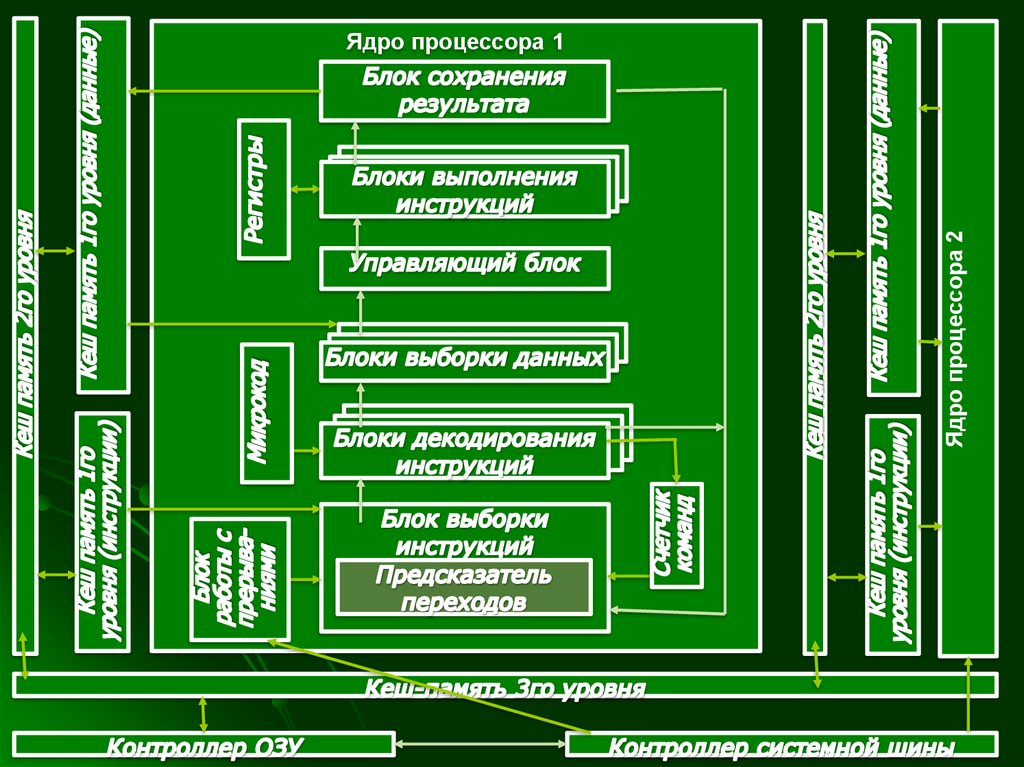

Упрощенная структурнаясхема процессора

(следующий слайд)

81. Упрощенная структурная схема процессора

Ядро процессора 2Ядро процессора 1

82.

Способы увеличенияпроизводительности процессора

83. Способы увеличения производительности процессора

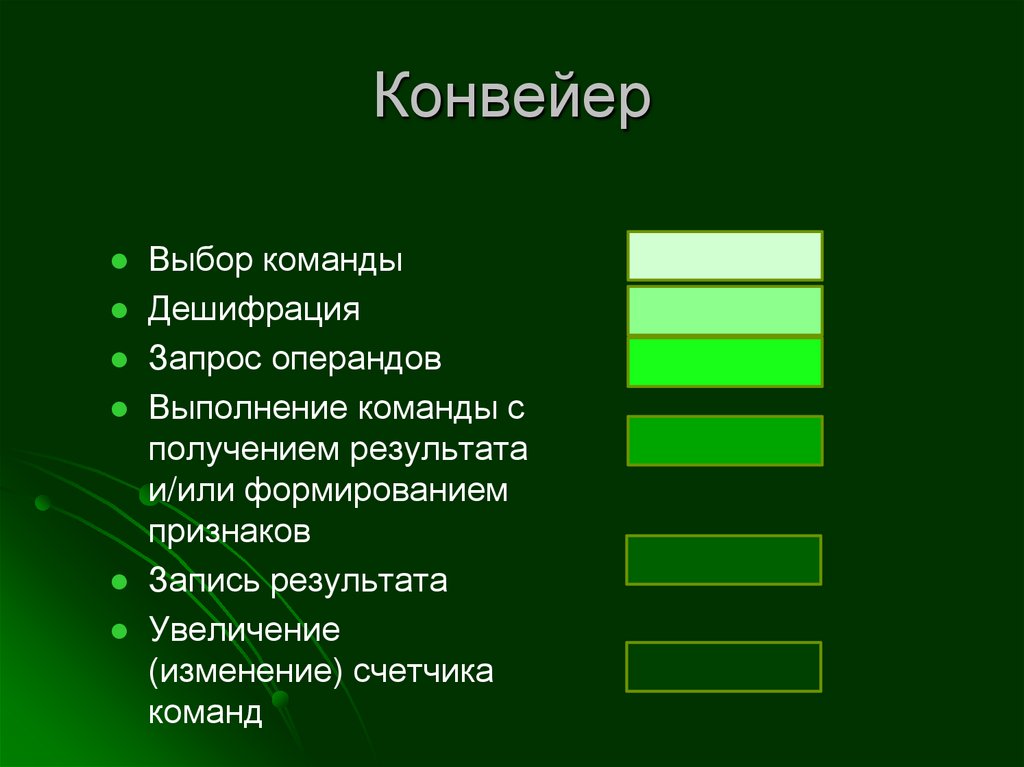

КонвейерВыбор команды

Дешифрация

Запрос операндов

Выполнение команды с

получением результата

и/или формированием

признаков

Запись результата

Увеличение

(изменение) счетчика

команд

84. Конвейер

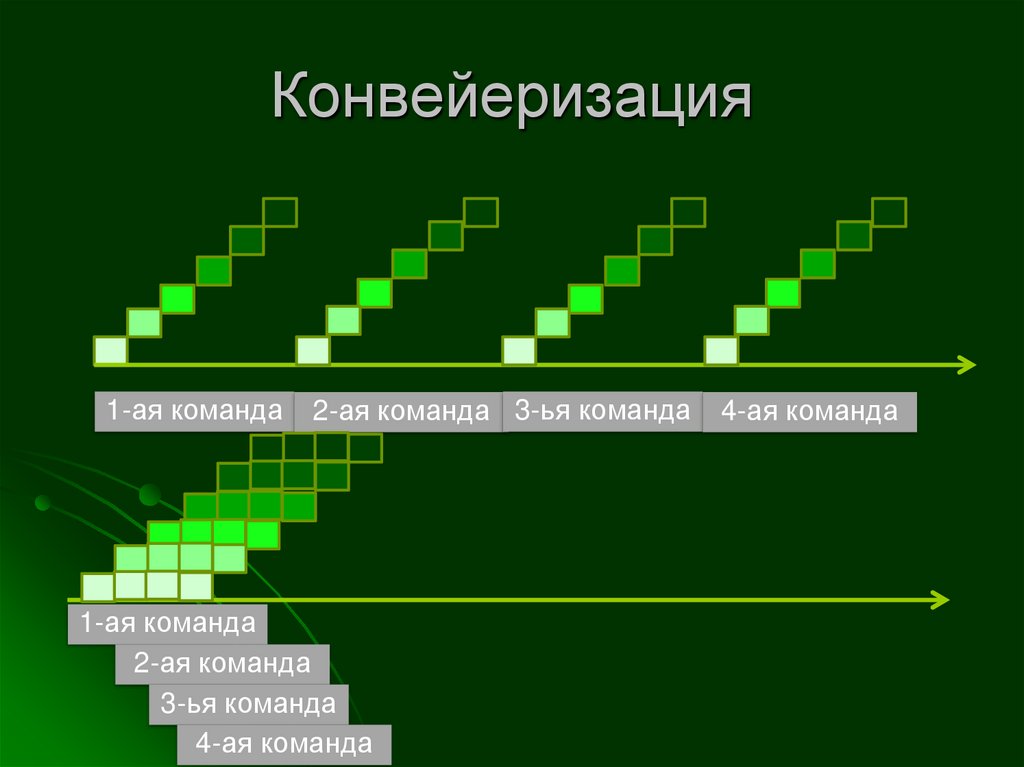

Конвейеризация1-ая команда

2-ая команда 3-ья команда

1-ая команда

2-ая команда

3-ья команда

4-ая команда

4-ая команда

85. Конвейеризация

СуперскалярностьНаиболее

нагруженные блоки

присутствуют в

нескольких

экземплярах

Несколько

декодеров команд

Параллельное

выполнение

возможно при

независимости

инструкций

86. Суперскалярность

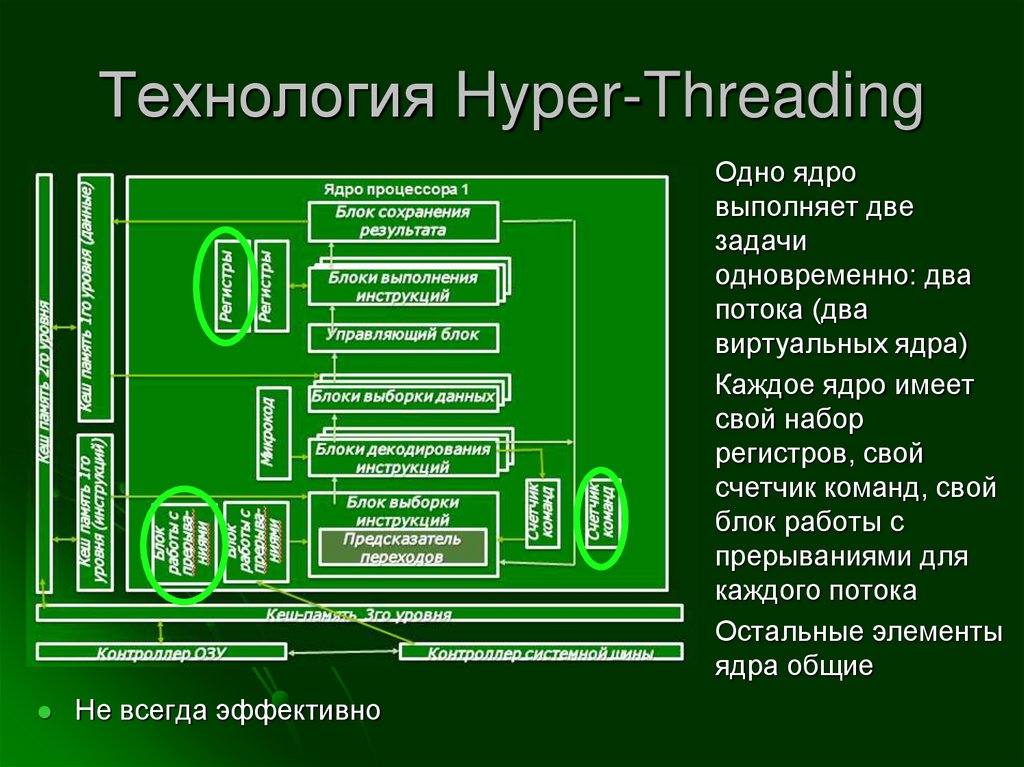

Технология Hyper-ThreadingНе всегда эффективно

Одно ядро

выполняет две

задачи

одновременно: два

потока (два

виртуальных ядра)

Каждое ядро имеет

свой набор

регистров, свой

счетчик команд, свой

блок работы с

прерываниями для

каждого потока

Остальные элементы

ядра общие

87. Технология Hyper-Threading

Параллельная обработкаданных - многоядерность

Не все программы

могут работать на

нескольких ядрах

Одна программа –

одно ядро: а если

программе надо

более одного ядра?

Сложный механизм

доступа к ОП и

проч. Ресурсам.

Увеличение

энергопотребления

Стоимость

88. Параллельная обработка данных - многоядерность

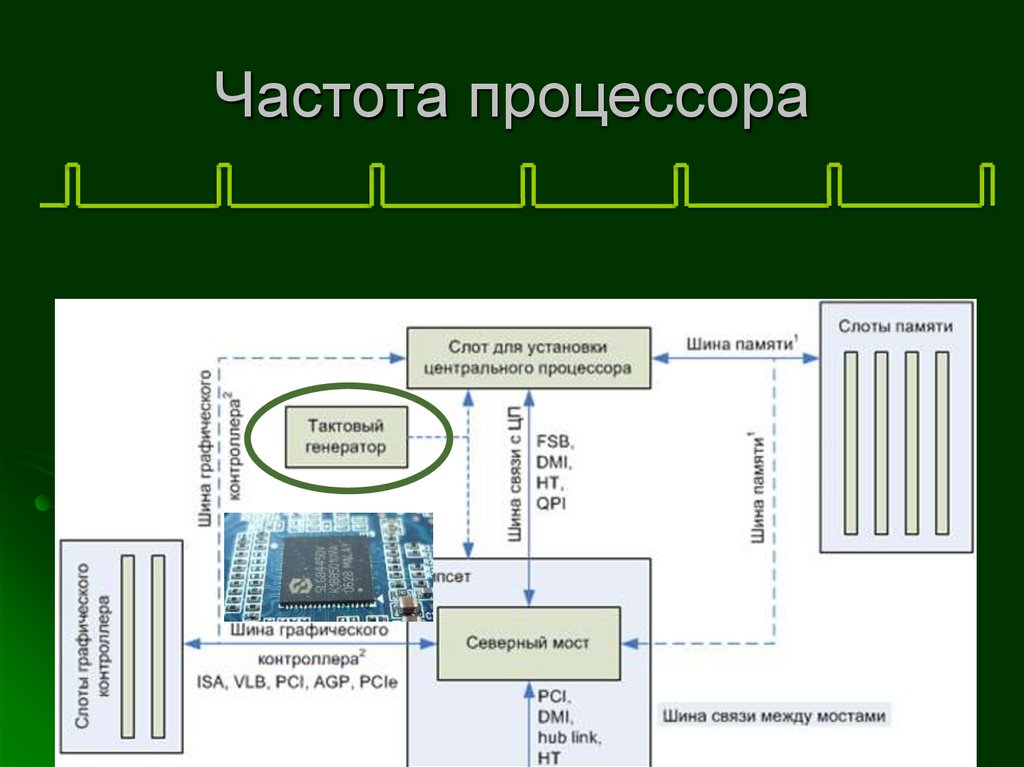

Частота процессора89. Частота процессора

90. Частота процессора

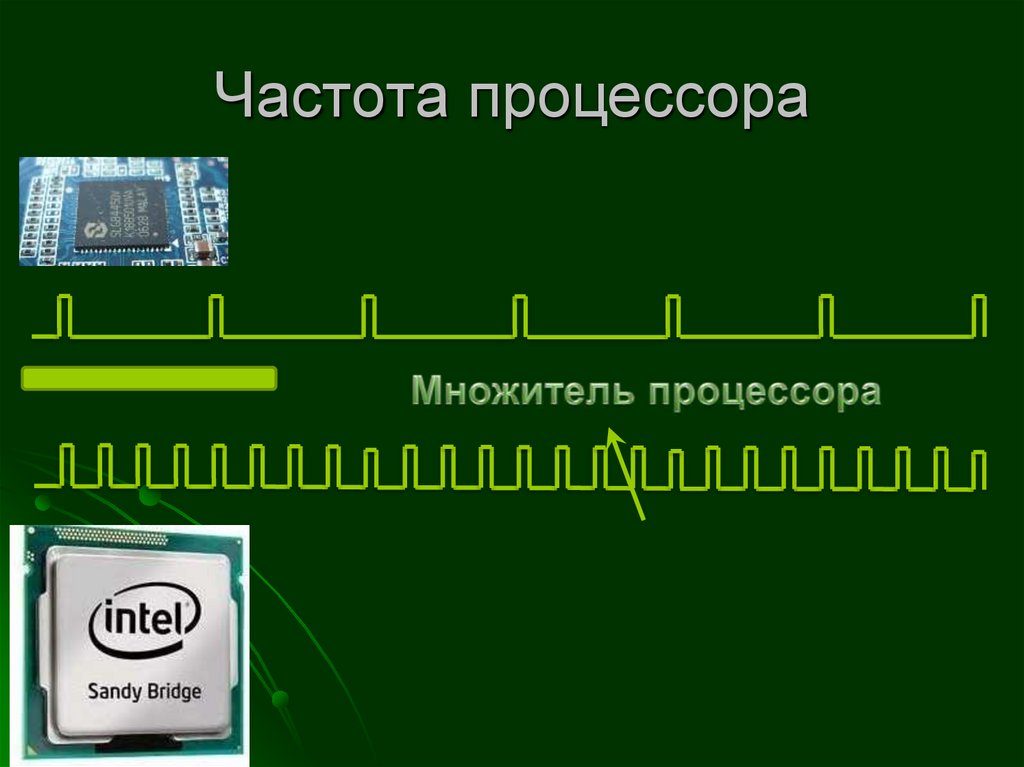

Множитель процессораЧастота системной шины * множитель процессора =

Частота процессора

~100 МГц * 24 = 2400МГц

Частота системной

шины ~100 МГц

200МГц

91. Множитель процессора

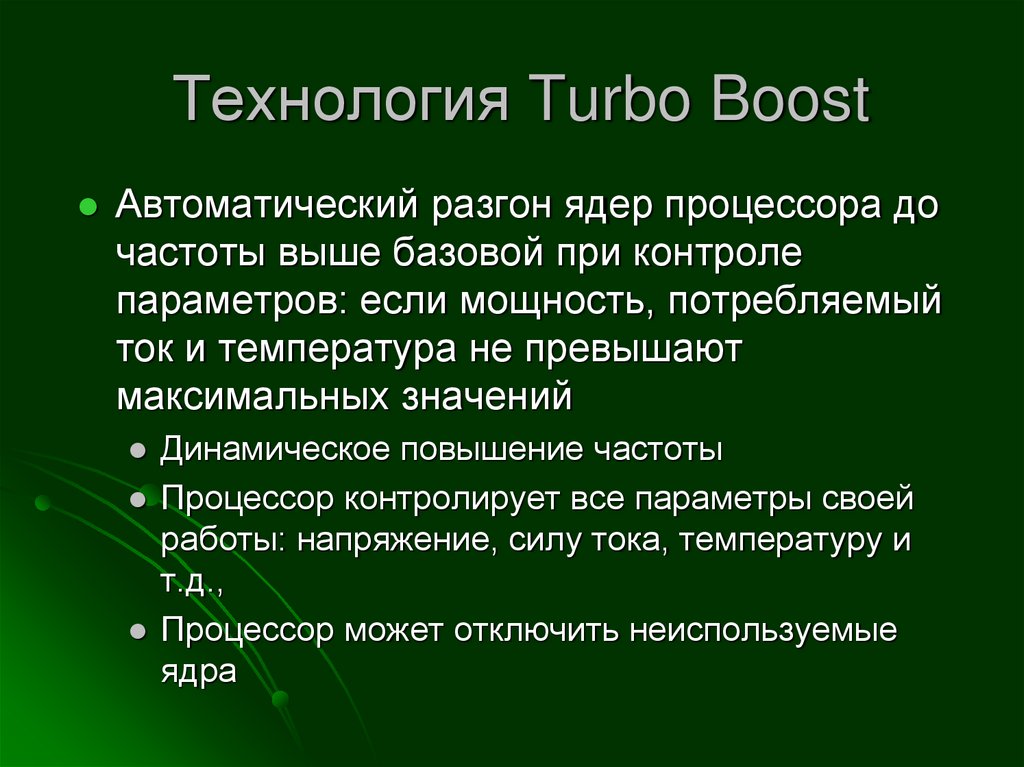

Технология Turbo BoostАвтоматический разгон ядер процессора до

частоты выше базовой при контроле

параметров: если мощность, потребляемый

ток и температура не превышают

максимальных значений

Динамическое повышение частоты

Процессор контролирует все параметры своей

работы: напряжение, силу тока, температуру и

т.д.,

Процессор может отключить неиспользуемые

ядра

92. Технология Turbo Boost

Эффективность выполнениякоманд: различные архитектуры

93. Эффективность выполнения команд: различные архитектуры

CISC (Complex Instruction SetComputing)

Исторически первые процессоры реализовывались

на архитектуре CISC

Базовые особенности:

арифметические действия выполняются одной

командой;

длина команды может быть любой;

каждый регистр выполняет строго свою функцию и

их количество ограничено;

94. CISC (Complex Instruction Set Computing)

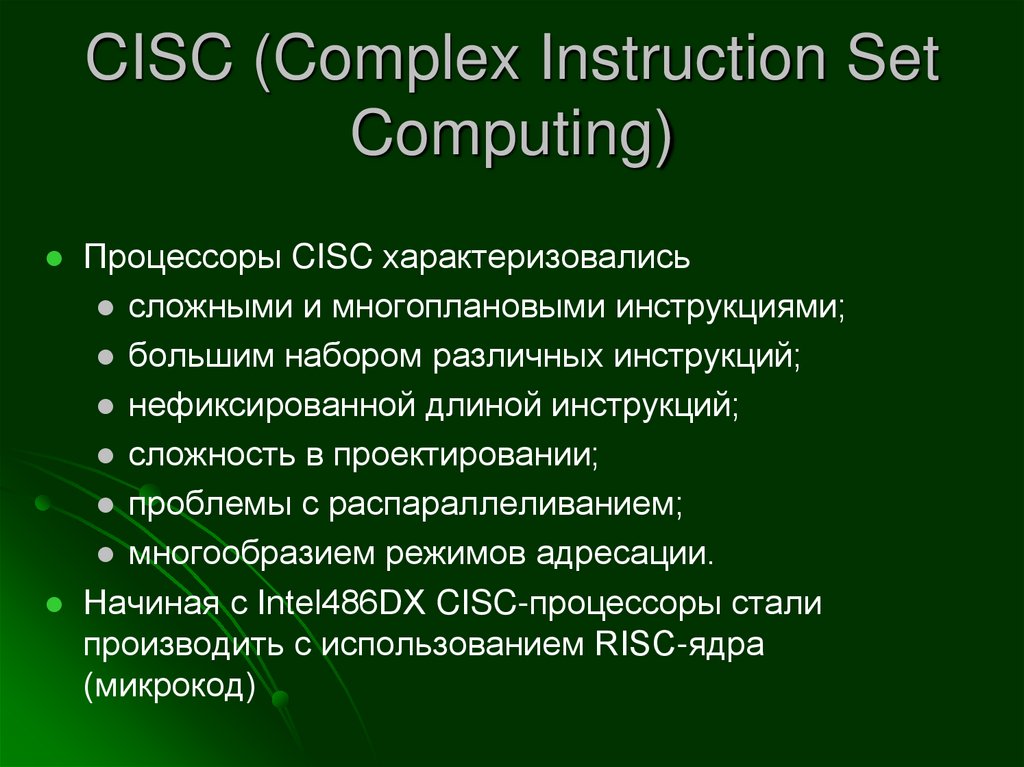

Процессоры CISC характеризовалисьсложными и многоплановыми инструкциями;

большим набором различных инструкций;

нефиксированной длиной инструкций;

сложность в проектировании;

проблемы с распараллеливанием;

многообразием режимов адресации.

Начиная с Intel486DX CISC-процессоры стали

производить с использованием RISC-ядра

(микрокод)

95. CISC (Complex Instruction Set Computing)

RISC (Reduced Instruction SetComputer)

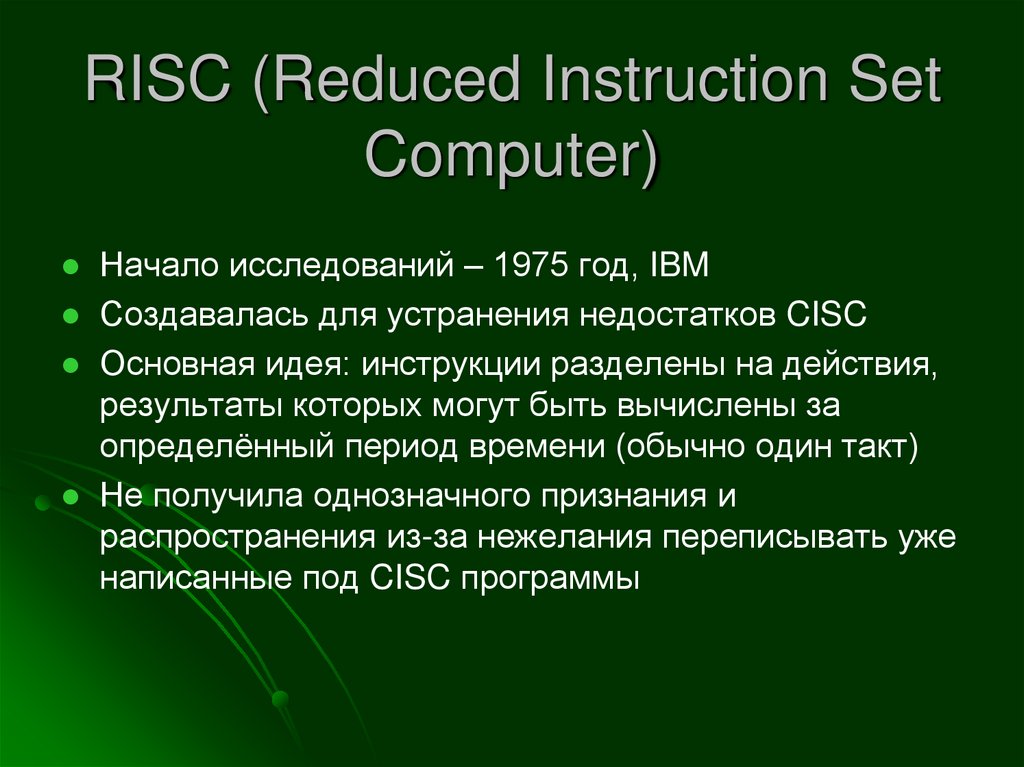

Начало исследований – 1975 год, IBM

Создавалась для устранения недостатков CISC

Основная идея: инструкции разделены на действия,

результаты которых могут быть вычислены за

определённый период времени (обычно один такт)

Не получила однозначного признания и

распространения из-за нежелания переписывать уже

написанные под CISC программы

96. RISC (Reduced Instruction Set Computer)

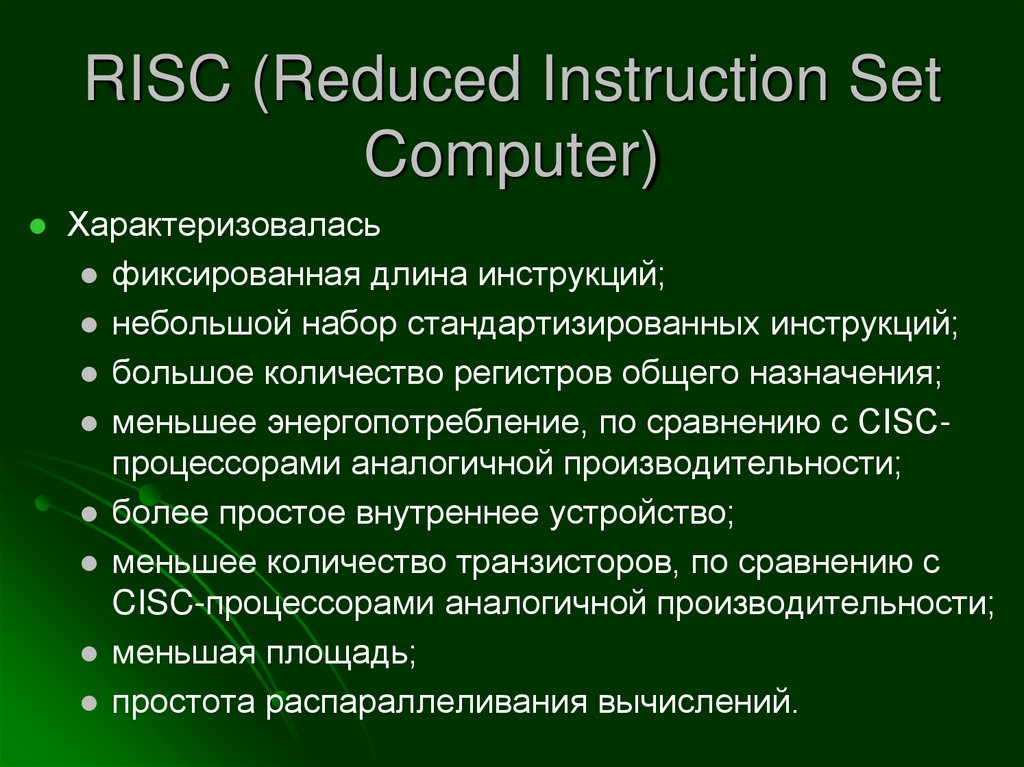

Характеризоваласьфиксированная длина инструкций;

небольшой набор стандартизированных инструкций;

большое количество регистров общего назначения;

меньшее энергопотребление, по сравнению с CISCпроцессорами аналогичной производительности;

более простое внутреннее устройство;

меньшее количество транзисторов, по сравнению с

CISC-процессорами аналогичной производительности;

меньшая площадь;

простота распараллеливания вычислений.

97. RISC (Reduced Instruction Set Computer)

MISC (Minimal Instruction SetComputer)

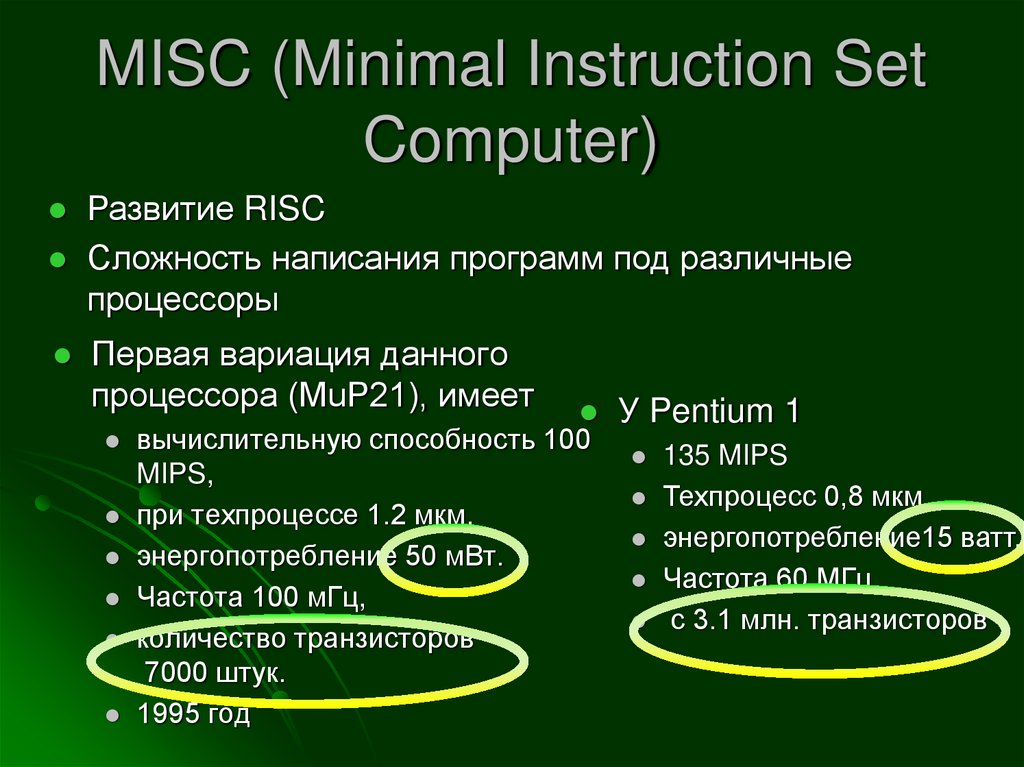

Развитие RISC

Сложность написания программ под различные

процессоры

Первая вариация данного

процессора (MuP21), имеет

вычислительную способность 100

MIPS,

при техпроцессе 1.2 мкм,

энергопотребление 50 мВт.

Частота 100 мГц,

количество транзисторов

7000 штук.

1995 год

У Pentium 1

135 MIPS

Техпроцесс 0,8 мкм

энергопотребление15 ватт,

Частота 60 МГц

с 3.1 млн. транзисторов

98. MISC (Minimal Instruction Set Computer)

ARM (Advanced Risc Machine)32—x битная архитектура, основанная на RISC

(упрощённый набор команд) архитектуре,

разработанная компанией ARM Holdings

низкие потребления энергии и тепловыделение.

применяются в мобильных игровых приставках,

музыкальных и видео плеерах, сетевом оборудовании,

планшетах.

95% смартфонов имеют процессор ARM

99. ARM (Advanced Risc Machine)

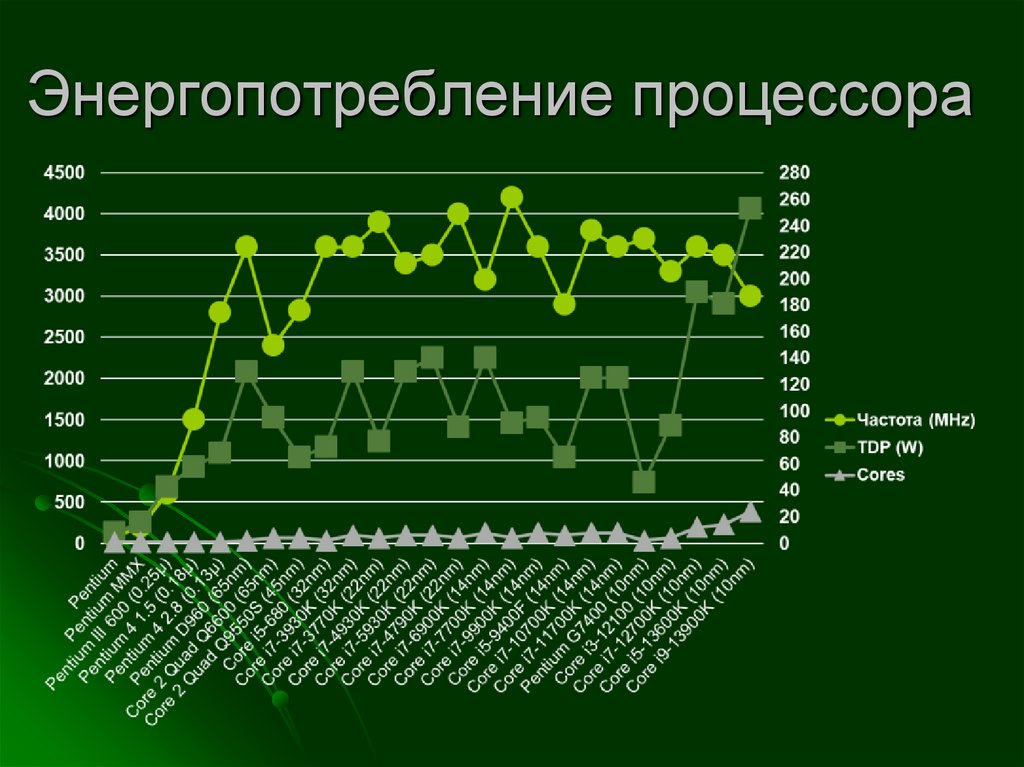

Энергопотребление процессораМодель

Pentium

Pentium MMX

Pentium III 600 (0.25μ)

Pentium 4 1.5 (0.18μ)

Pentium 4 2.8 (0.13μ)

Pentium D960 (65nm)

Core 2 Quad Q6600 (65nm)

Частота (MHz)

TDP (W)

75

8

Частота (MHz)

200

15,7

600

43

1500

58

2800

68

3600

130

2400

95

Модель

Pentium

Pentium MMX

Pentium II 300 (0.35µ)

Pentium III 600 (0.25µ)

Core 2 Quad

Pentium

III Q9550S

1000(45nm)

(0.18µ) 2830

3600

Core i5-680 (32nm)

Pentium

III

1333

(0.13µ)

3600

Core i7-3930K (32nm)

Pentium

4 1.5 (22nm)

(0.18µ)

3900

Core i7-3770K

3400

Core i7-4930K

Pentium

4 2.8 (22nm)

(0.13µ)

3500

Core i7-5930K (22nm)

Pentium

4

HT

672

(90nm)

4000

Core i7-4790K (22nm)

3200

Pentium

D 960(14nm)

(65nm)

Core i7-6900K

i7-7700K (14nm)

CoreCore

2 Duo

E6850 (65nm) 4200

3600

Core i7-9900K (14nm)

CoreCore

2 Quad

Q6600

(65nm)

2900

i5-9400F (14nm)

3800

i7-10700KQ9550S

(14nm)

CoreCore

2 Quad

3600

Core i7-11700K (14nm)

(45nm)

3700

Pentium G7400 (10nm)

CoreCore

i5-680

(32nm)

3300

i3-12100 (10nm)

3600

i7-12700K (10nm)

CoreCore

i7-3930K

(32nm)

3500

i5-13600K (10nm)

CoreCore

i7-3770K

(22nm)

3000

Core i9-13900K (10nm)

65

73

130

77

130

140

88

140

91

95

65

125

125

46

89

190

181

253

Cores

Год выпуска

1

1993

cores

1 TDP (W) 1997

1

1999

75

8

1

1

2000

200

15,7

1

1

2002

300

18,6

1

2

2006

4

2007

600

43

1

4

1000

2

1330

6

1500

4

6

2800

6

3800

4

8

3600

4

3000

8

2400

6

8

2008

35,5

2010

34

2011

58

2012

2013

68

2014

115

2015

2016

130

2017

65

2018

95

2019

1

1

1

1

1

2

2

4

2020

2830

8

65

2021

2

3600

4

12

3600

14

3900

24

2022

73

2022

2022

130

2022

77

2022

4

2

6

4

100. Энергопотребление процессора

101. Энергопотребление процессора

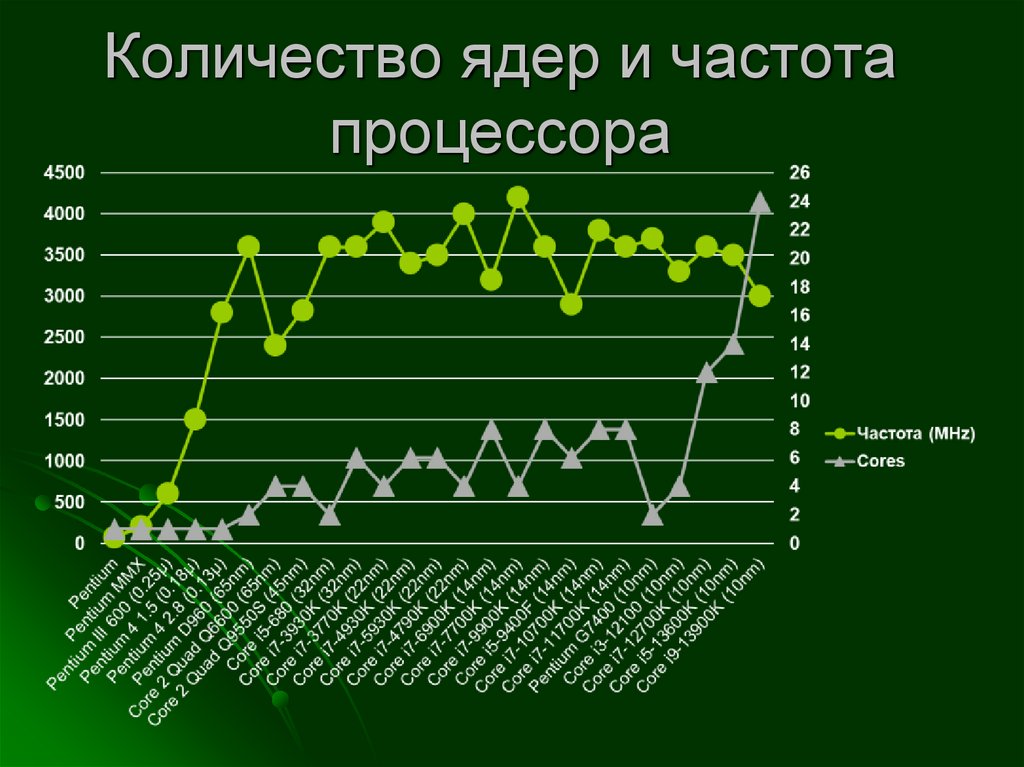

Количество ядер и частотапроцессора

102. Количество ядер и частота процессора

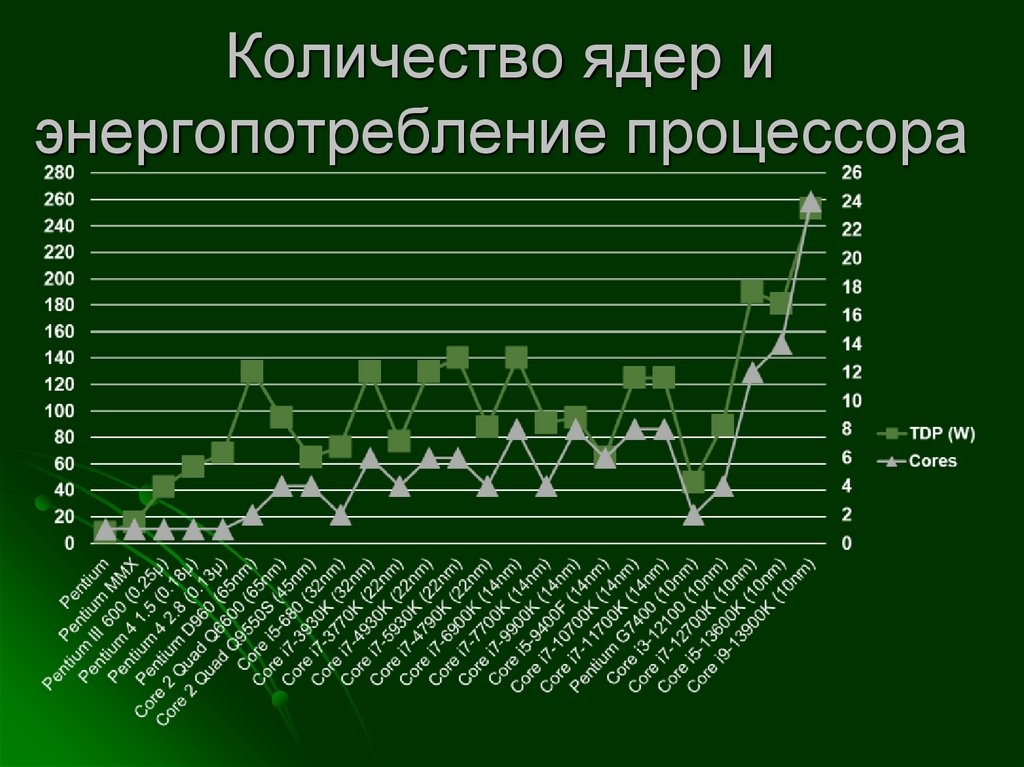

Количество ядер иэнергопотребление процессора

103. Количество ядер и энергопотребление процессора

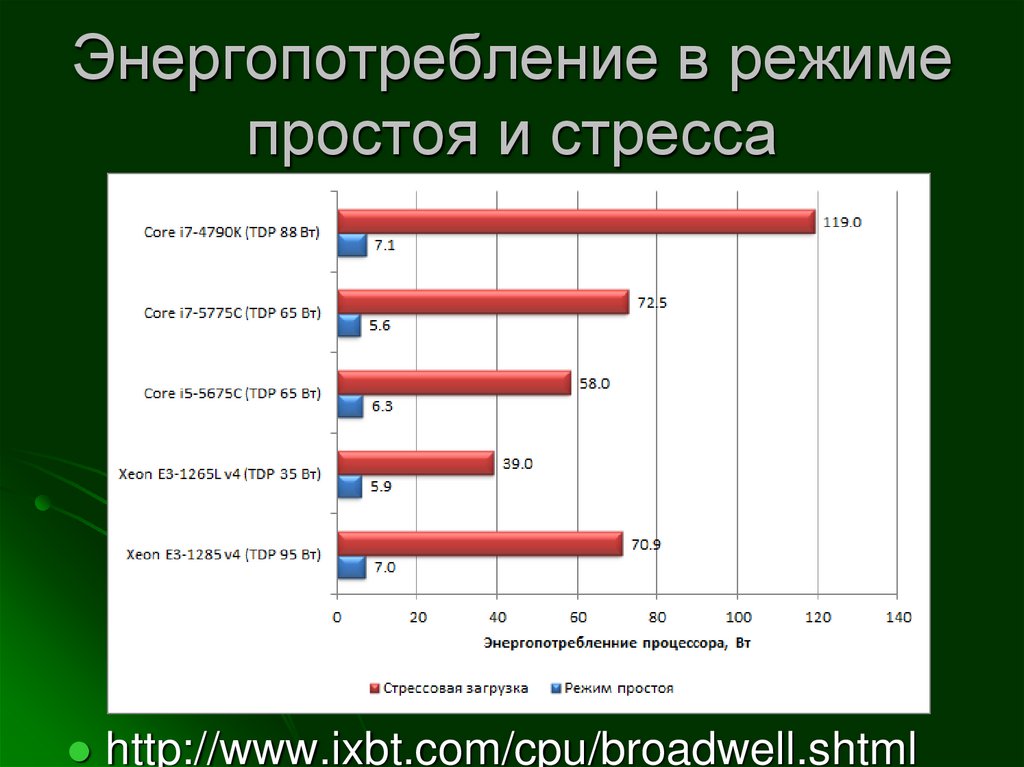

Энергопотребление в режимепростоя и стресса

http://www.ixbt.com/cpu/broadwell.shtml

104. Энергопотребление в режиме простоя и стресса

Способы сниженияэнергопотребления процессора

Портативные устройства

Снижение частоты – потеря производительности…

позволяет динамически изменять энергопотребление

процессора, за счет изменения тактовой частоты

процессора и напряжения: если процессор используется

не полностью, тактовую частоту можно снизить

105. Способы снижения энергопотребления процессора

Характеристики процессораКоличество ядер

Частота процессора как количество

элементарных операций, которые

процессор может выполнить в секунду (ГГц)

Техпроцесс

Энергопотребление

Системная шина (FSB)

Разрядность

Кеш-память

electronics

electronics