Similar presentations:

Архитектура ЭВМ и систем. Лекция 8

1. Архитектура ЭВМ и систем

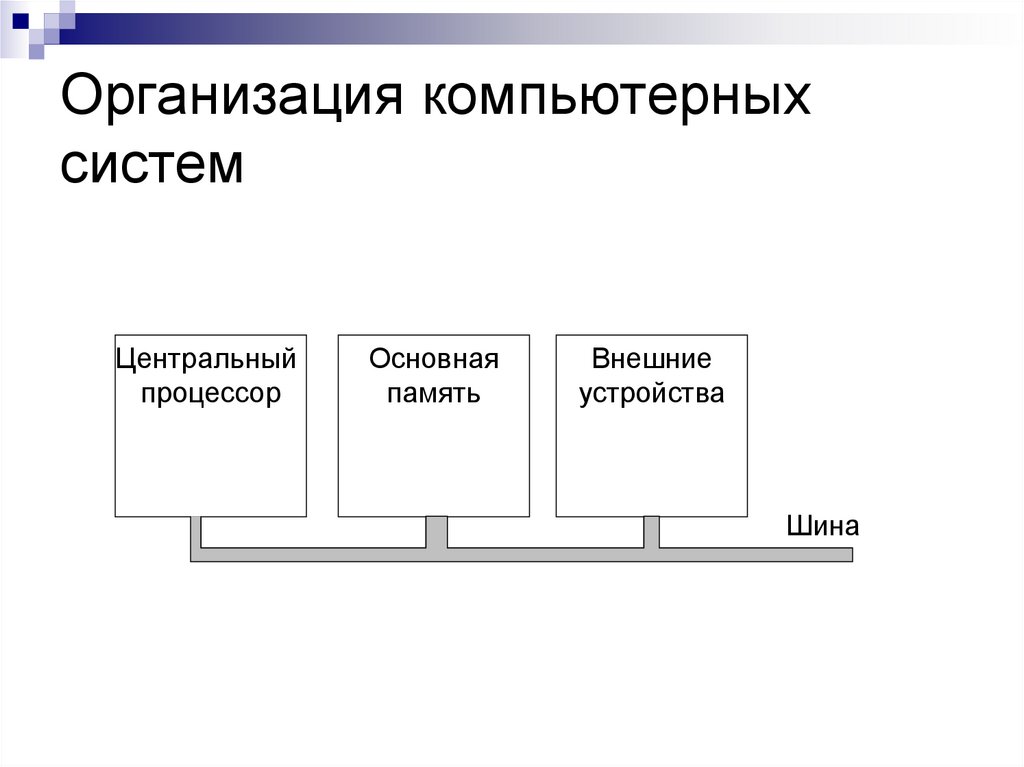

Лекция 82. Организация компьютерных систем

Центральныйпроцессор

Основная

память

Внешние

устройства

Шина

3. Процессор

CPU – Central Processing UnitЗадачи

Интерпретация команд

Выполнение команд

Рассылка управляющих сигналов другим

устройствам

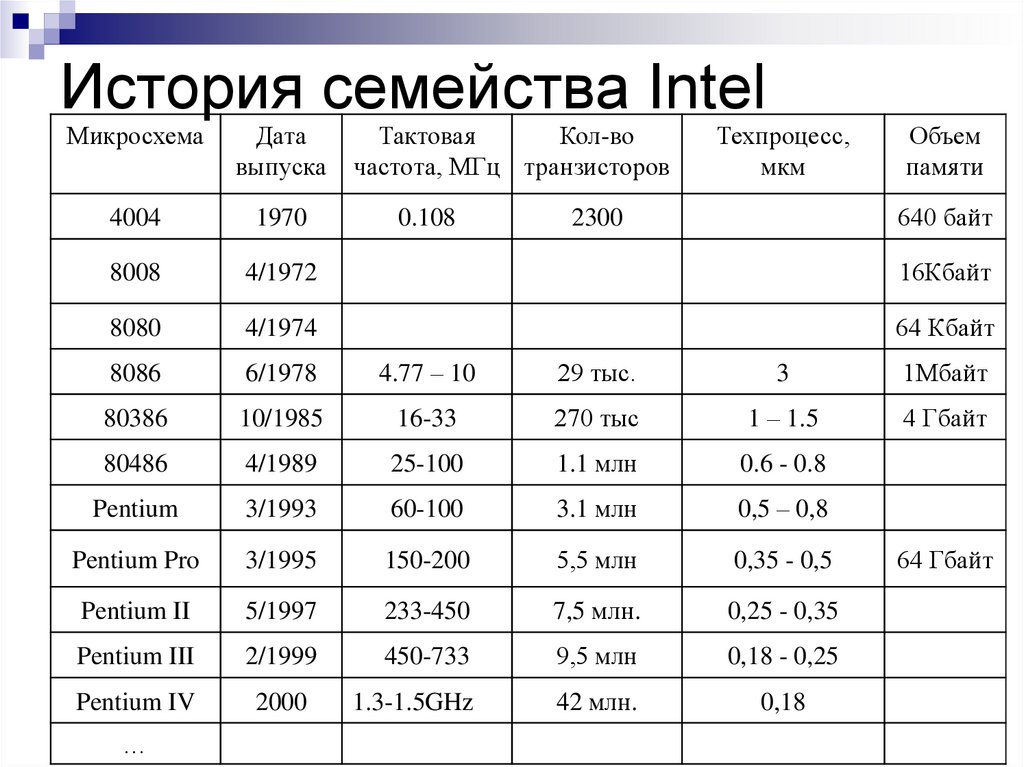

4. История семейства Intel

МикросхемаДата

выпуска

4004

1970

8008

4/1972

16Кбайт

8080

4/1974

64 Кбайт

8086

6/1978

4.77 – 10

29 тыс.

3

1Мбайт

80386

10/1985

16-33

270 тыс

1 – 1.5

4 Гбайт

80486

4/1989

25-100

1.1 млн

0.6 - 0.8

Pentium

3/1993

60-100

3.1 млн

0,5 – 0,8

Pentium Pro

3/1995

150-200

5,5 млн

0,35 - 0,5

Pentium II

5/1997

233-450

7,5 млн.

0,25 - 0,35

Pentium III

2/1999

450-733

9,5 млн

0,18 - 0,25

Pentium IV

2000

1.3-1.5GHz

42 млн.

0,18

…

Тактовая

Кол-во

частота, МГц транзисторов

0.108

Техпроцесс,

мкм

Объем

памяти

640 байт

2300

64 Гбайт

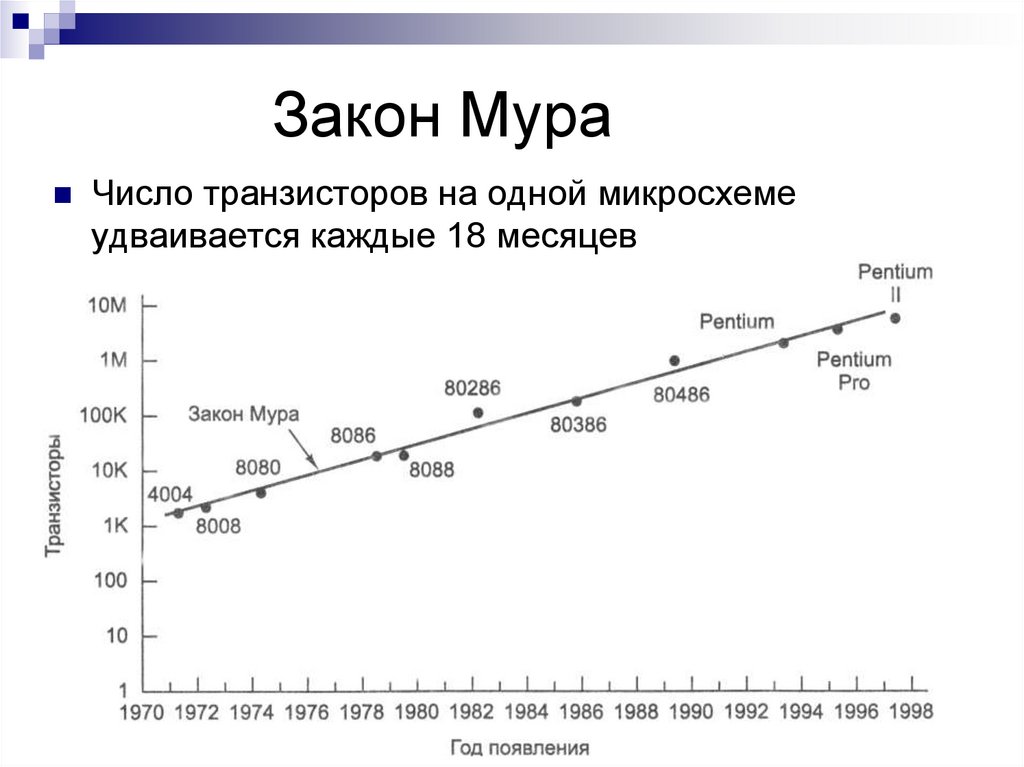

5. Закон Мура

Число транзисторов на одной микросхемеудваивается каждые 18 месяцев

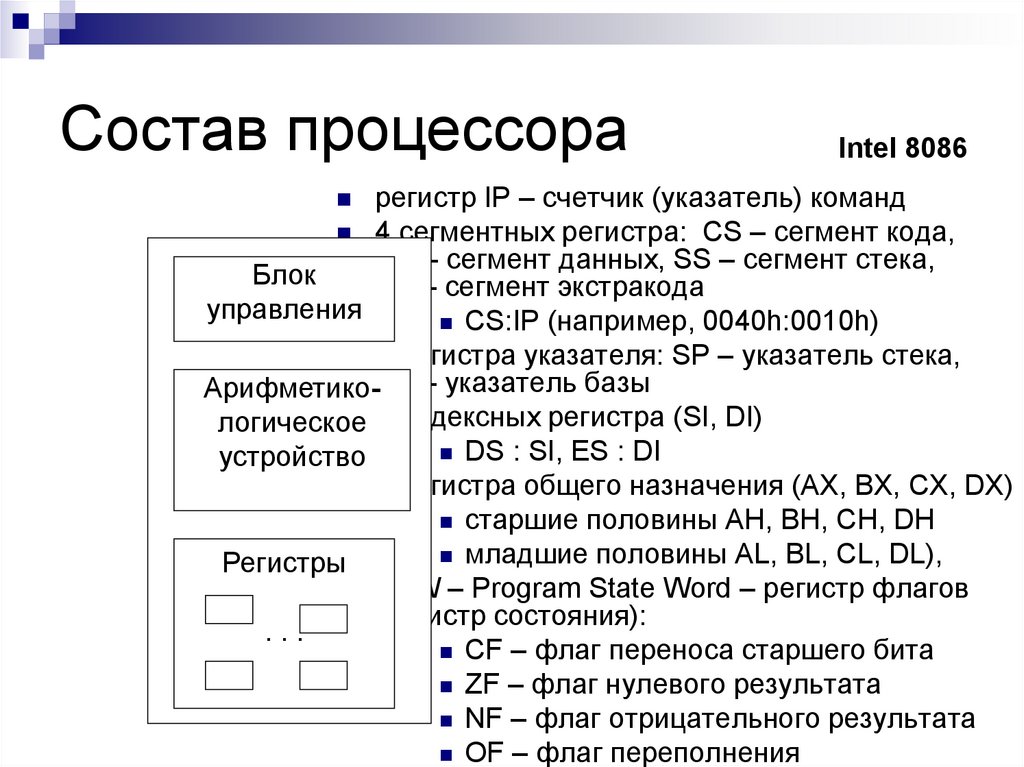

6. Состав процессора

Intel 8086регистр IP – счетчик (указатель) команд

4 сегментных регистра: CS – сегмент кода,

DS – сегмент данных, SS – сегмент стека,

Блок

ES – сегмент экстракода

управления

CS:IP (например, 0040h:0010h)

2 регистра указателя: SP – указатель стека,

Арифметико-BP – указатель базы

2 индексных регистра (SI, DI)

логическое

DS : SI, ES : DI

устройство

4 регистра общего назначения (AX, BX, CX, DX)

старшие половины AH, BH, CH, DH

младшие половины AL, BL, CL, DL),

Регистры

PSW – Program State Word – регистр флагов

(регистр состояния):

...

CF – флаг переноса старшего бита

ZF – флаг нулевого результата

NF – флаг отрицательного результата

OF – флаг переполнения

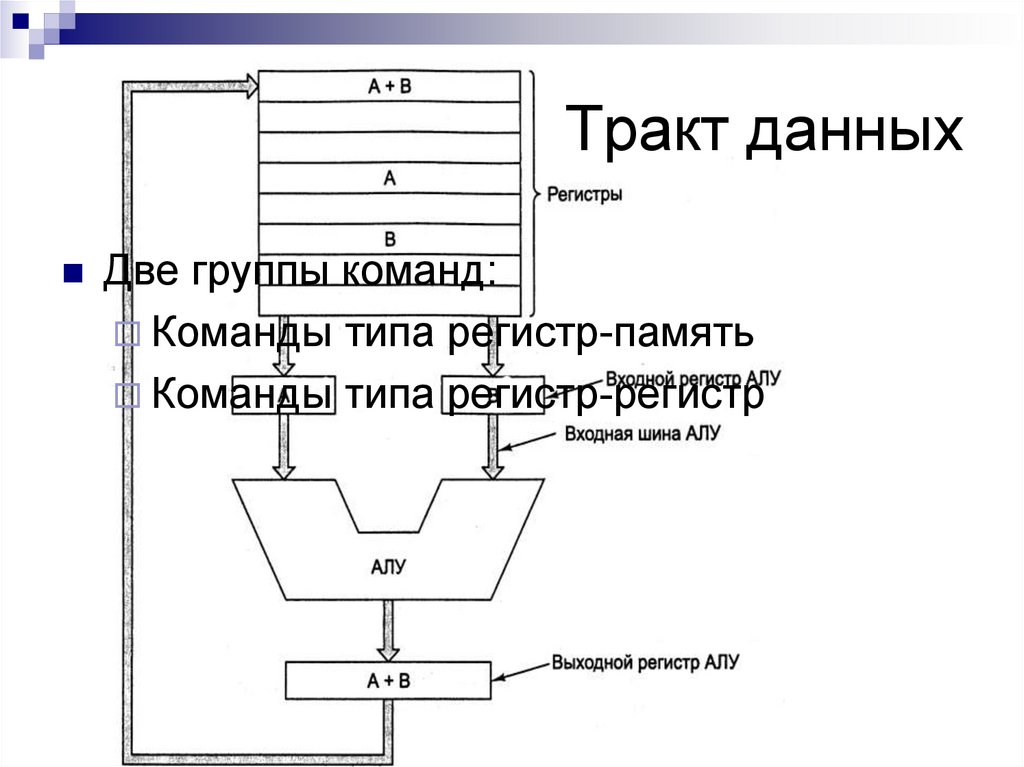

7. Тракт данных

Две группы команд:Команды типа регистр-память

Команды типа регистр-регистр

8. Выполнение команд

ЦП выполняет каждую команду за несколько шагов:вызывает очередную команду из памяти и переносит ее в

регистр команд

2. определяет тип вызванной команды

3. меняет IP, который теперь должен указывать на следующую

команду

4. если команда использует слово из памяти, определяет, где

находится это слово

5. переносит слово, если это необходимо, в регистр ЦП

6. выполняет команду

7. переходит к шагу 1

1.

(выборка–декодирование–исполнение)

9. Основные характеристики процессора

Тактовая частотачисло элементарных операций – тактов,

выполняемых в течение одной секунды

Разрядность (длина слова)

максимальное количество разрядов двоичного

кода, которые могут передаваться или

обрабатываться одновременно за один такт.

Архитектура

10. Архитектура процессора

Система и форматы командСпособ реализации команд

Способ организации вычислительного процесса

Поддержка мультипроцессорности

Состав, имена и назначение программно доступных

регистров

Режимы адресации памяти

Способы машинного представления данных разного типа

Способы адресации периферийных устройств и средства

выполнения операций ввода/вывода

Классы прерываний, особенности инициирования и

обработки прерывания

и т.д.

11. Форматы команд

Машинная команда – это элементарнаяинструкция машине, выполняемая ею

автоматически без каких-либо

дополнительных указаний и пояснений.

Код операции Поле операндов

По количеству операндов

Безадресные

Одноадресные

Двухадресные (н-р, Pentium II)

Трехадресные (н-р, Ultra SPARC II)

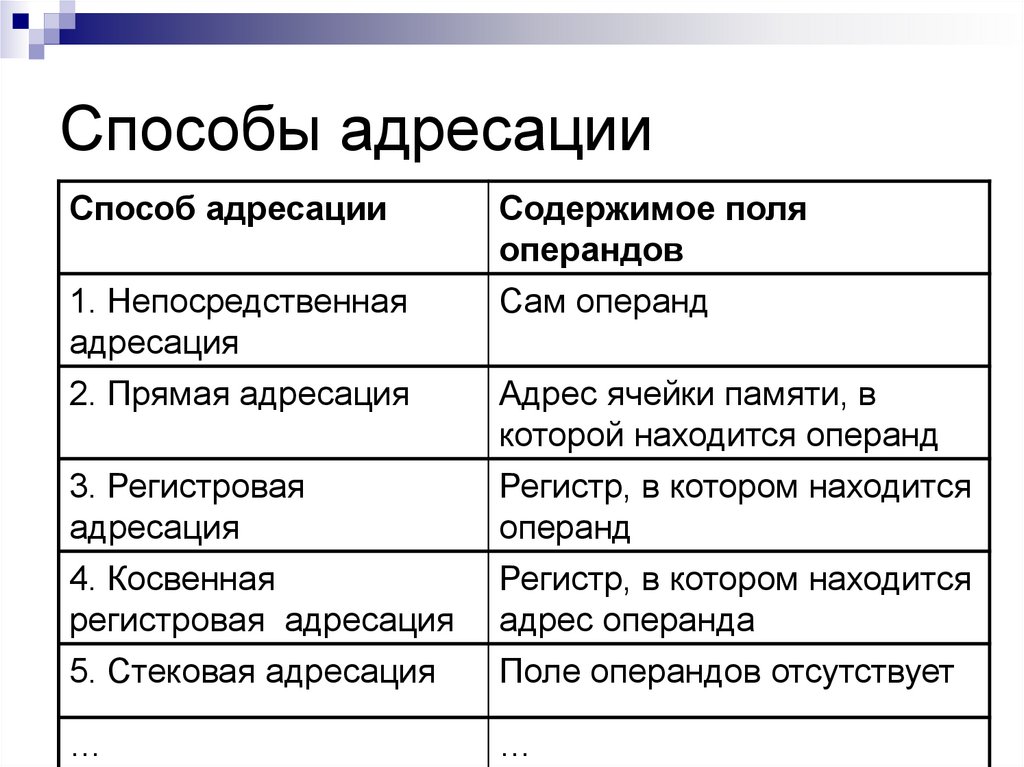

12. Способы адресации

Способ адресации1. Непосредственная

адресация

2. Прямая адресация

Содержимое поля

операндов

Сам операнд

4. Косвенная

регистровая адресация

5. Стековая адресация

Адрес ячейки памяти, в

которой находится операнд

Регистр, в котором находится

операнд

Регистр, в котором находится

адрес операнда

Поле операндов отсутствует

…

…

3. Регистровая

адресация

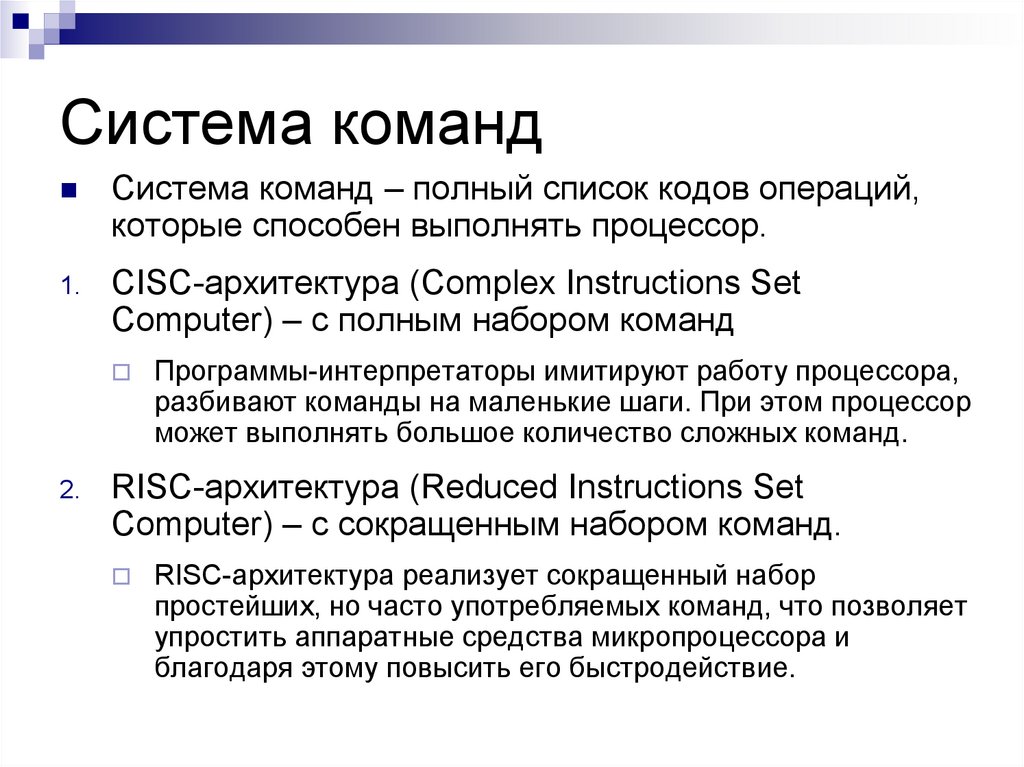

13. Система команд

Система команд – полный список кодов операций,которые способен выполнять процессор.

1.

CISC-архитектура (Complex Instructions Set

Computer) – с полным набором команд

2.

Программы-интерпретаторы имитируют работу процессора,

разбивают команды на маленькие шаги. При этом процессор

может выполнять большое количество сложных команд.

RISC-архитектура (Reduced Instructions Set

Computer) – с сокращенным набором команд.

RISС-архитектура реализует сокращенный набор

простейших, но часто употребляемых команд, что позволяет

упростить аппаратные средства микропроцессора и

благодаря этому повысить его быстродействие.

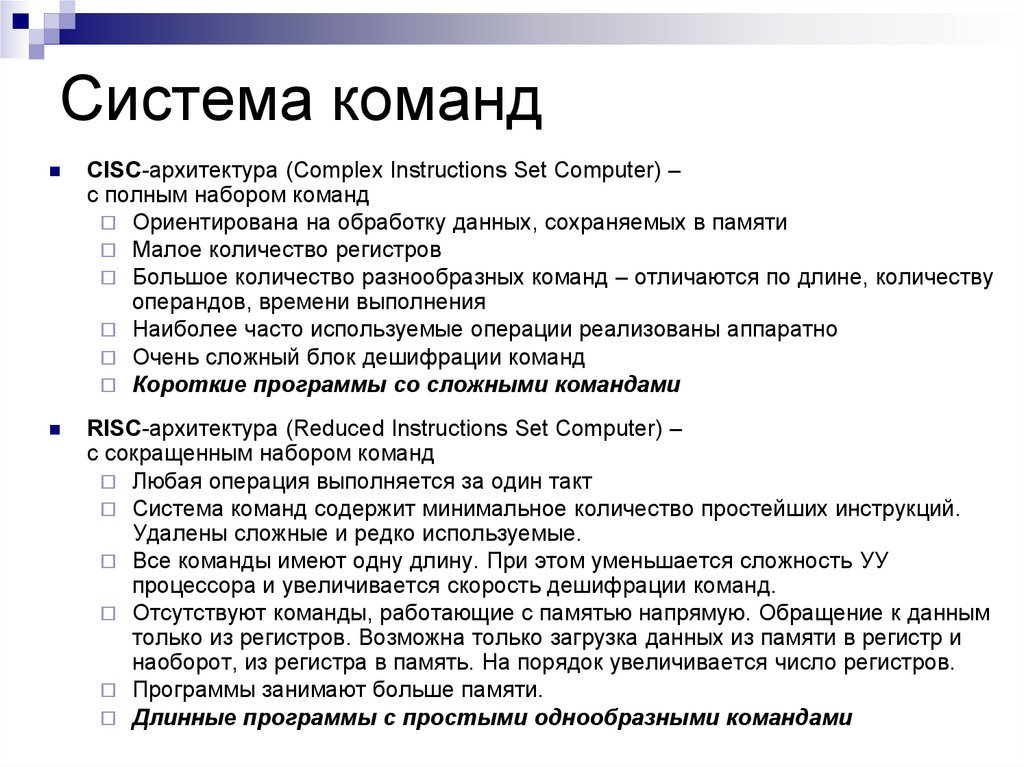

14. Система команд

CISC-архитектура (Complex Instructions Set Computer) –с полным набором команд

Ориентирована на обработку данных, сохраняемых в памяти

Малое количество регистров

Большое количество разнообразных команд – отличаются по длине, количеству

операндов, времени выполнения

Наиболее часто используемые операции реализованы аппаратно

Очень сложный блок дешифрации команд

Короткие программы со сложными командами

RISC-архитектура (Reduced Instructions Set Computer) –

с сокращенным набором команд

Любая операция выполняется за один такт

Система команд содержит минимальное количество простейших инструкций.

Удалены сложные и редко используемые.

Все команды имеют одну длину. При этом уменьшается сложность УУ

процессора и увеличивается скорость дешифрации команд.

Отсутствуют команды, работающие с памятью напрямую. Обращение к данным

только из регистров. Возможна только загрузка данных из памяти в регистр и

наоборот, из регистра в память. На порядок увеличивается число регистров.

Программы занимают больше памяти.

Длинные программы с простыми однообразными командами

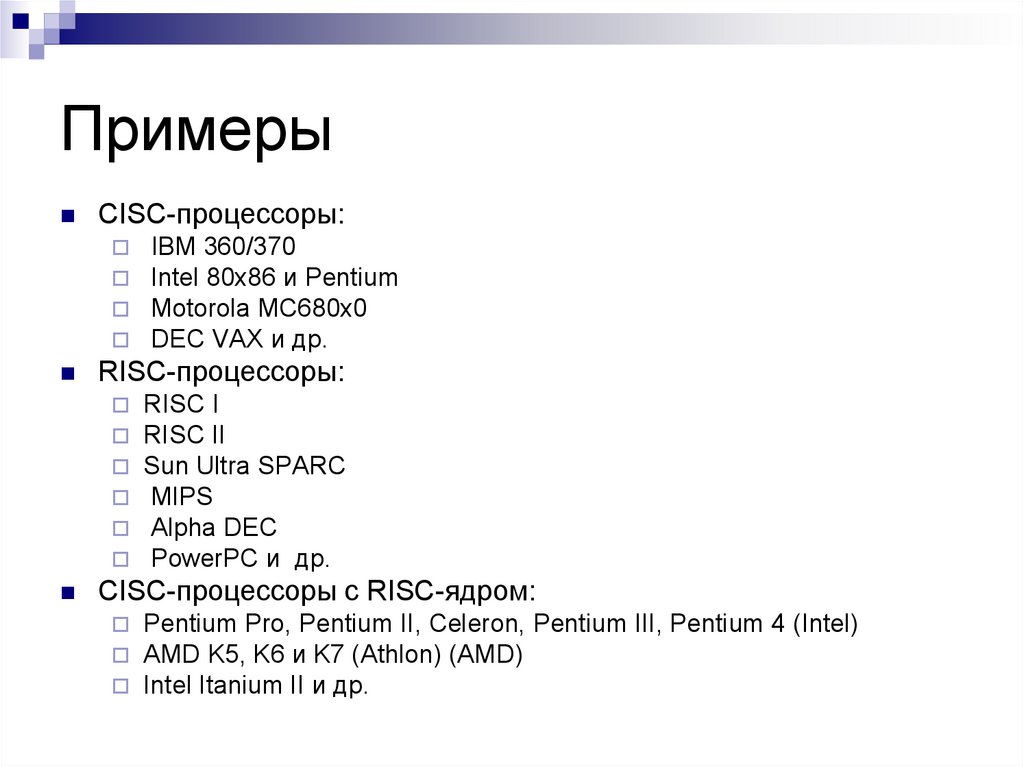

15. Примеры

CISC-процессоры:IBM 360/370

Intel 80x86 и Pentium

Motorola MC680x0

DEC VAX и др.

RISC-процессоры:

RISC I

RISC II

Sun Ultra SPARC

MIPS

Alpha DEC

PowerPC и др.

CISC-процессоры с RISC-ядром:

Pentium Pro, Pentium II, Celeron, Pentium III, Pentium 4 (Intel)

AMD K5, K6 и K7 (Athlon) (AMD)

Intel Itanium II и др.

16. Принципы разработки современных компьютеров (принципы RISC)

Все команды непосредственно выполняютсяаппаратным обеспечением.

Компьютер должен начинать выполнение

большого числа команд в секунду.

Команды должны легко декодироваться.

К памяти должны обращаться только

команды загрузки и сохранения.

Должно быть большое количество регистров.

17. Параллелизм

Используется для достижения лучшейпроизводительности при данной

скорости работы процессора.

Существует две основные формы:

на уровне команд

на уровне процессоров

18. Параллелизм на уровне команд

1. Выборка с упреждением(1959 г. IBM Stretch)

Выполнение команды =

вызов команды

выполнение

2. Конвейер

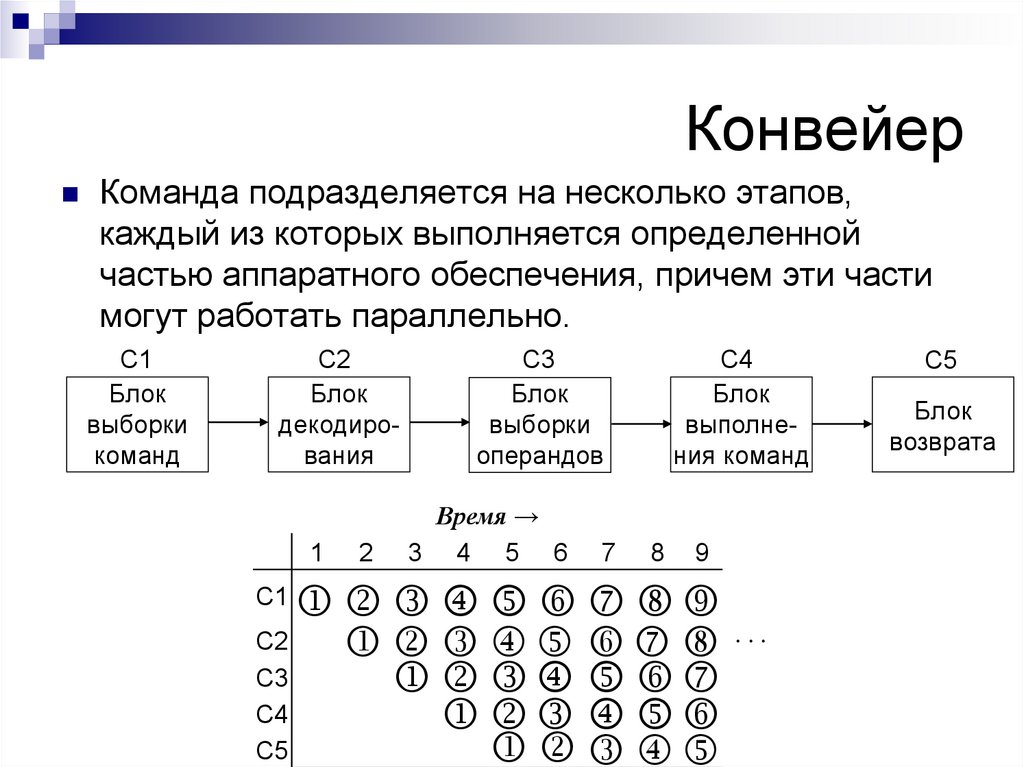

19. Конвейер

Команда подразделяется на несколько этапов,каждый из которых выполняется определенной

частью аппаратного обеспечения, причем эти части

могут работать параллельно.

С1

Блок

выборки

команд

С2

Блок

декодирования

1

2

С3

Блок

выборки

операндов

Время →

3 4 5 6

7

С4

Блок

выполнения команд

8

9

С2

...

С3

С4

С5

С1

С5

Блок

возврата

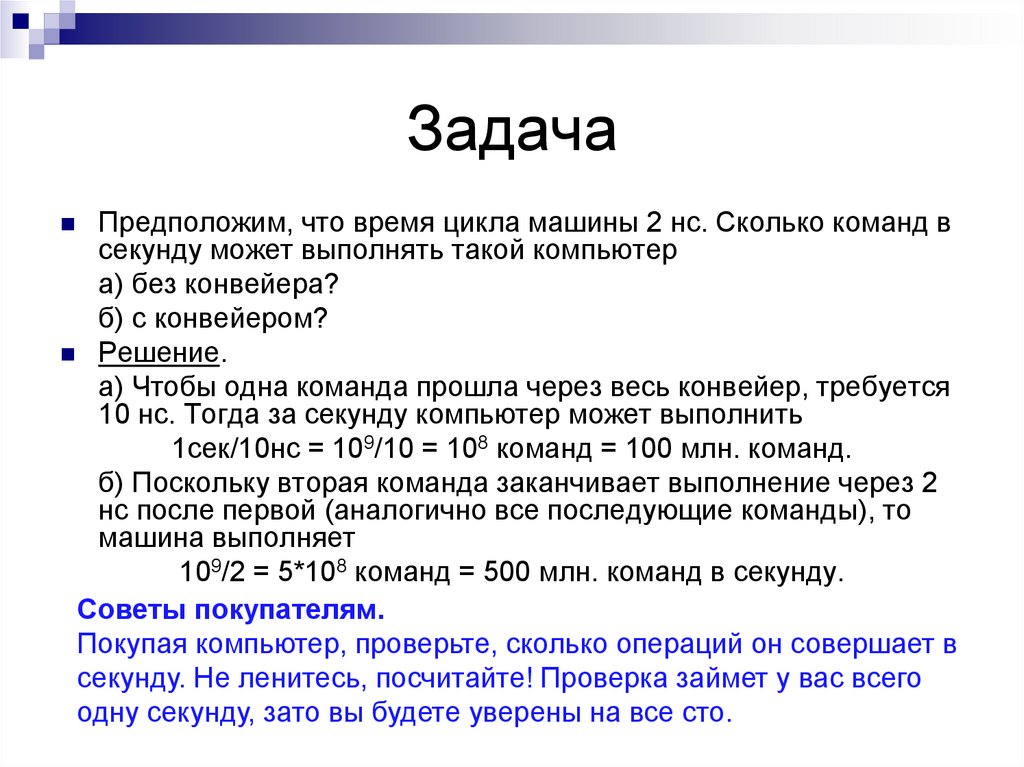

20. Задача

Предположим, что время цикла машины 2 нс. Сколько команд всекунду может выполнять такой компьютер

а) без конвейера?

б) с конвейером?

Решение.

а) Чтобы одна команда прошла через весь конвейер, требуется

10 нс. Тогда за секунду компьютер может выполнить

1сек/10нс = 109/10 = 108 команд = 100 млн. команд.

б) Поскольку вторая команда заканчивает выполнение через 2

нс после первой (аналогично все последующие команды), то

машина выполняет

109/2 = 5*108 команд = 500 млн. команд в секунду.

Советы покупателям.

Покупая компьютер, проверьте, сколько операций он совершает в

секунду. Не ленитесь, посчитайте! Проверка займет у вас всего

одну секунду, зато вы будете уверены на все сто.

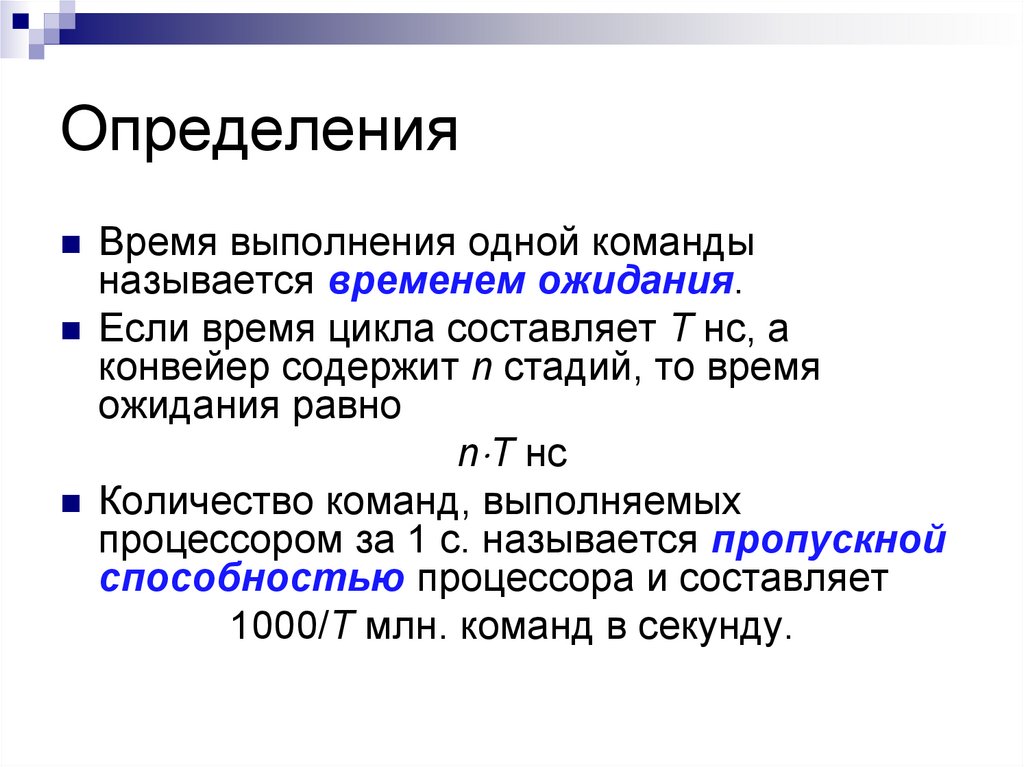

21. Определения

Время выполнения одной командыназывается временем ожидания.

Если время цикла составляет T нс, а

конвейер содержит n стадий, то время

ожидания равно

n T нс

Количество команд, выполняемых

процессором за 1 с. называется пропускной

способностью процессора и составляет

1000/T млн. команд в секунду.

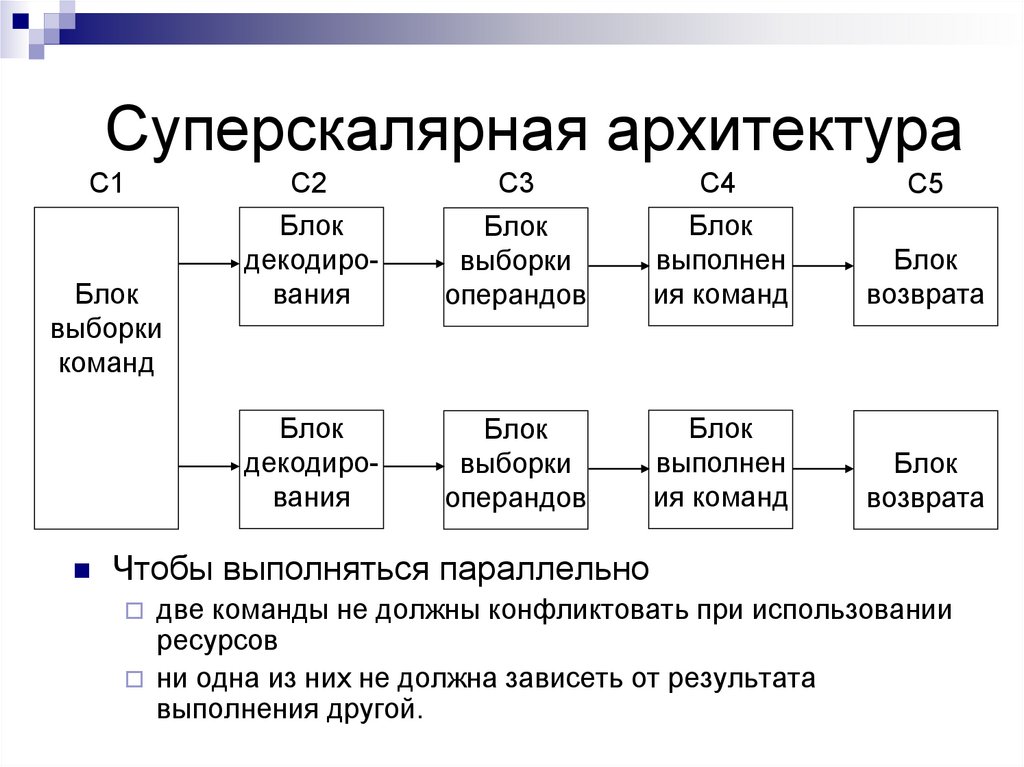

22. Суперскалярная архитектура

С1Блок

выборки

команд

С2

Блок

декодирования

Блок

декодирования

С3

Блок

выборки

операндов

С4

Блок

выполнен

ия команд

Блок

возврата

Блок

выборки

операндов

Блок

выполнен

ия команд

Блок

возврата

С5

Чтобы выполняться параллельно

две команды не должны конфликтовать при использовании

ресурсов

ни одна из них не должна зависеть от результата

выполнения другой.

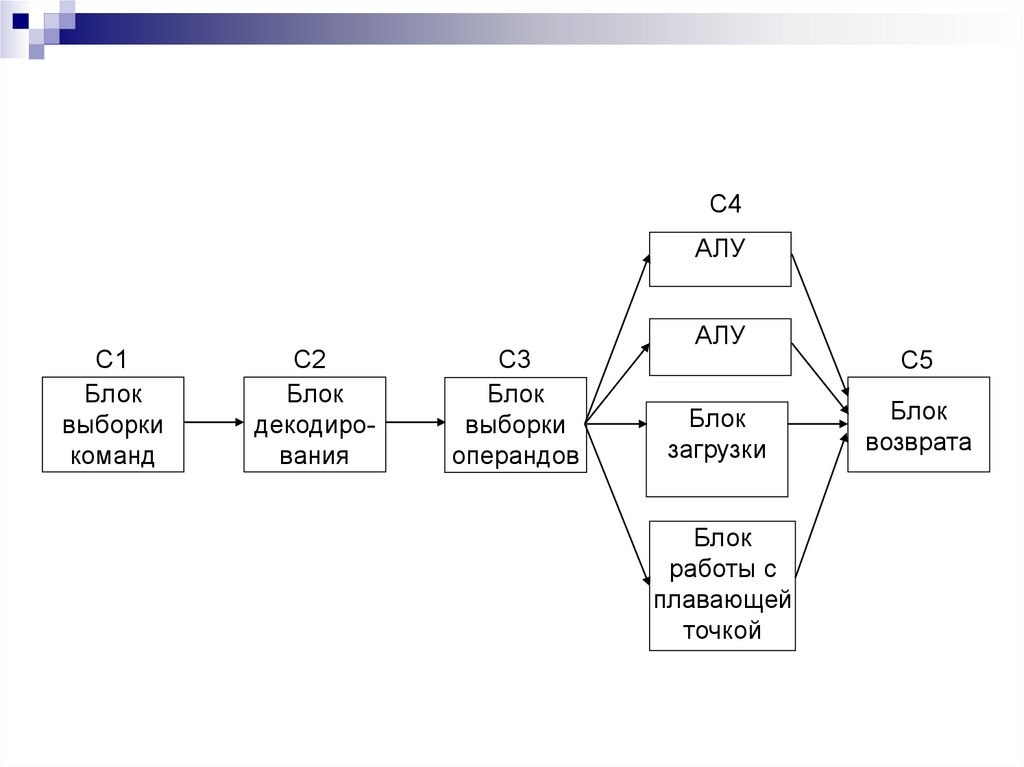

23.

С4АЛУ

С1

Блок

выборки

команд

С2

Блок

декодирования

С3

Блок

выборки

операндов

АЛУ

Блок

загрузки

Блок

работы с

плавающей

точкой

С5

Блок

возврата

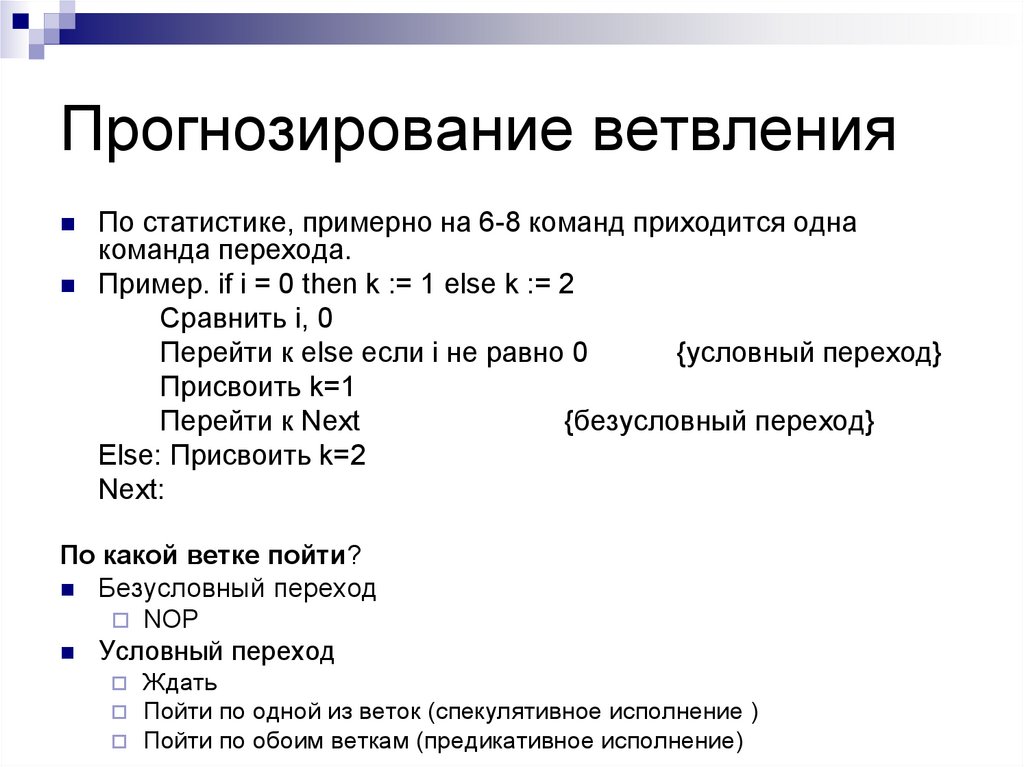

24. Прогнозирование ветвления

По статистике, примерно на 6-8 команд приходится однакоманда перехода.

Пример. if i = 0 then k := 1 else k := 2

Сравнить i, 0

Перейти к else если i не равно 0

{условный переход}

Присвоить k=1

Перейти к Next

{безусловный переход}

Else: Присвоить k=2

Next:

По какой ветке пойти?

Безусловный переход

NOP

Условный переход

Ждать

Пойти по одной из веток (спекулятивное исполнение )

Пойти по обоим веткам (предикативное исполнение)

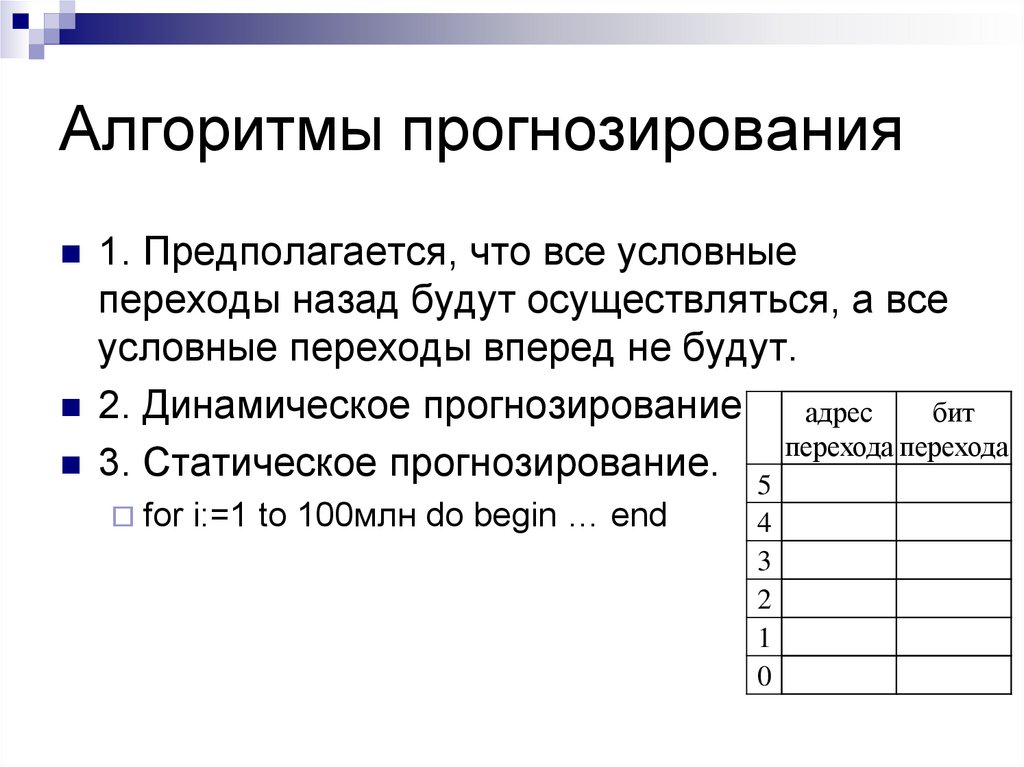

25. Алгоритмы прогнозирования

1. Предполагается, что все условныепереходы назад будут осуществляться, а все

условные переходы вперед не будут.

2. Динамическое прогнозирование

адрес

бит

перехода перехода

3. Статическое прогнозирование.

5

for i:=1 to 100млн do begin … end

4

3

2

1

0

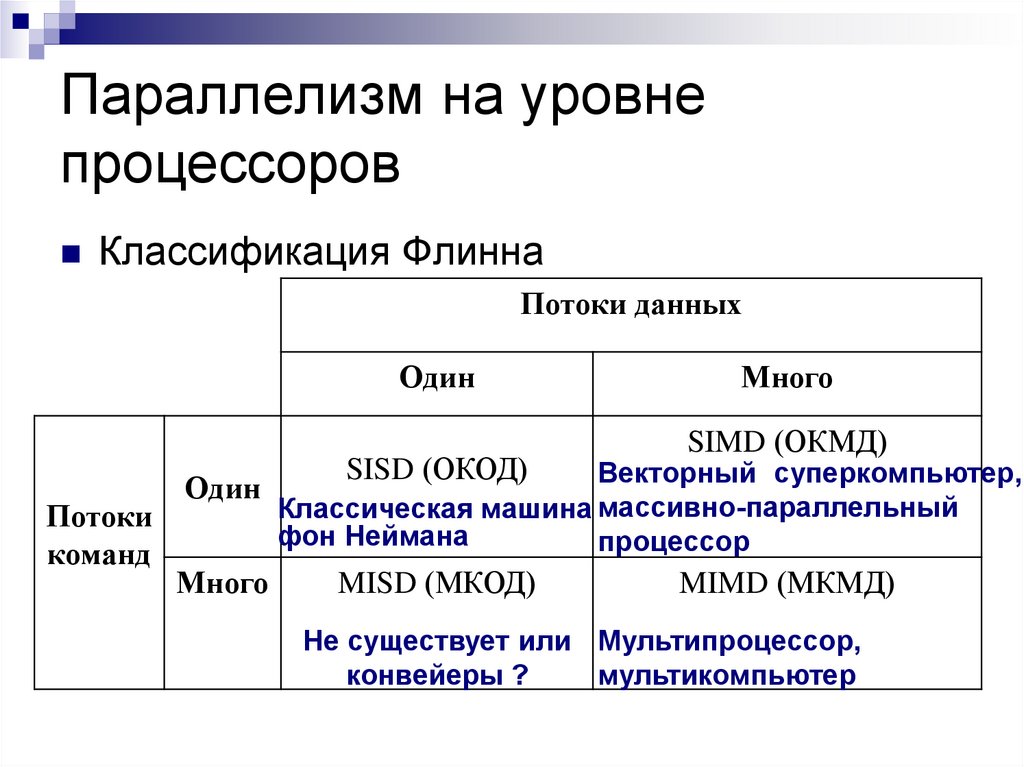

26. Параллелизм на уровне процессоров

Классификация ФлиннаПотоки данных

Один

Потоки

команд

Один

Много

SISD (ОКОД)

Много

SIMD (ОКМД)

Векторный суперкомпьютер,

Классическая машина массивно-параллельный

фон Неймана

процессор

MISD (МКОД)

MIMD (МКМД)

Не существует или Мультипроцессор,

конвейеры ?

мультикомпьютер

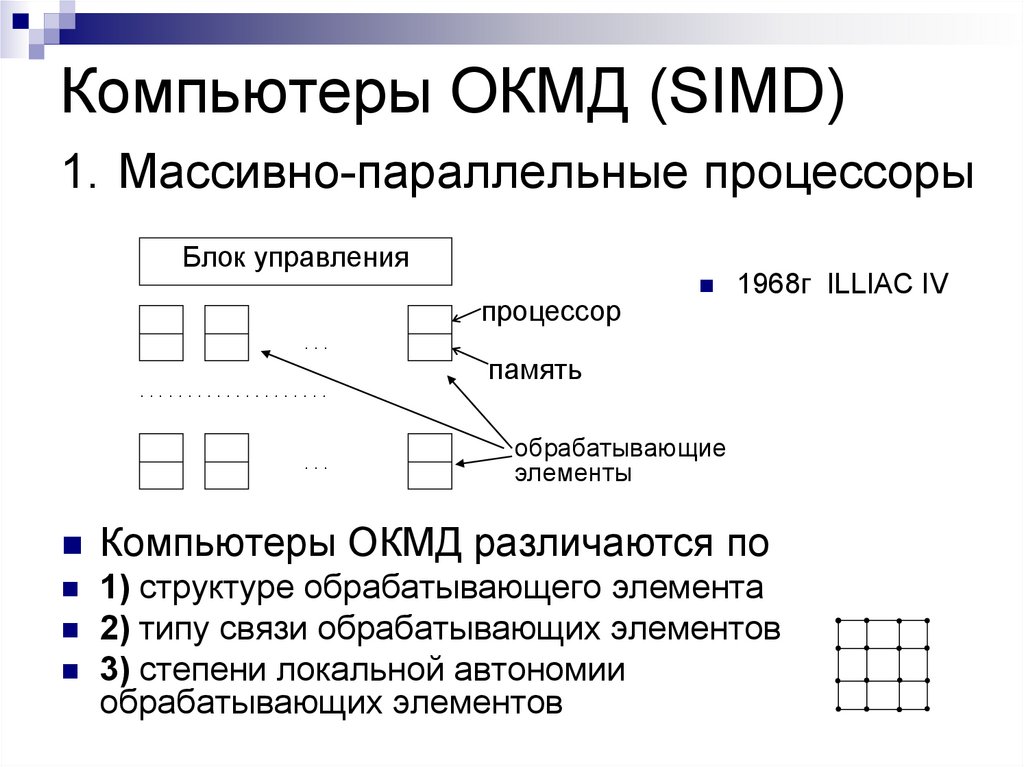

27. Компьютеры ОКМД (SIMD) 1. Массивно-параллельные процессоры

Блок управленияпроцессор

1968г ILLIAC IV

...

....................

...

память

обрабатывающие

элементы

Компьютеры ОКМД различаются по

1) структуре обрабатывающего элемента

2) типу связи обрабатывающих элементов

3) степени локальной автономии

обрабатывающих элементов

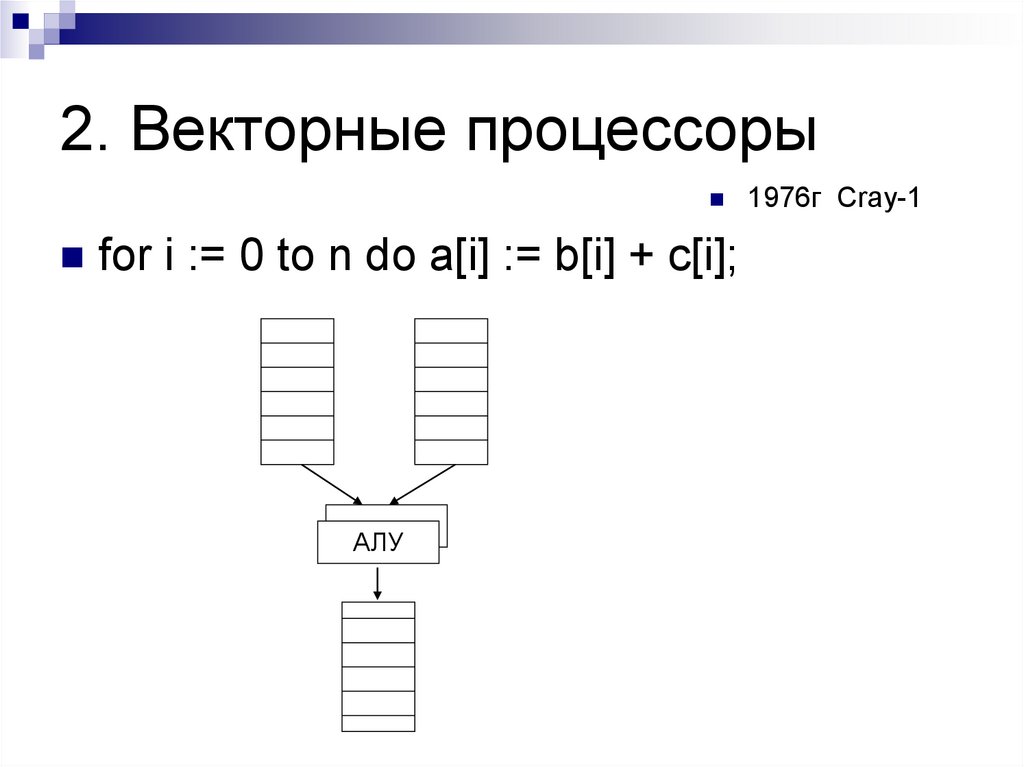

28. 2. Векторные процессоры

for i := 0 to n do a[i] := b[i] + c[i];АЛУ

1976г Cray-1

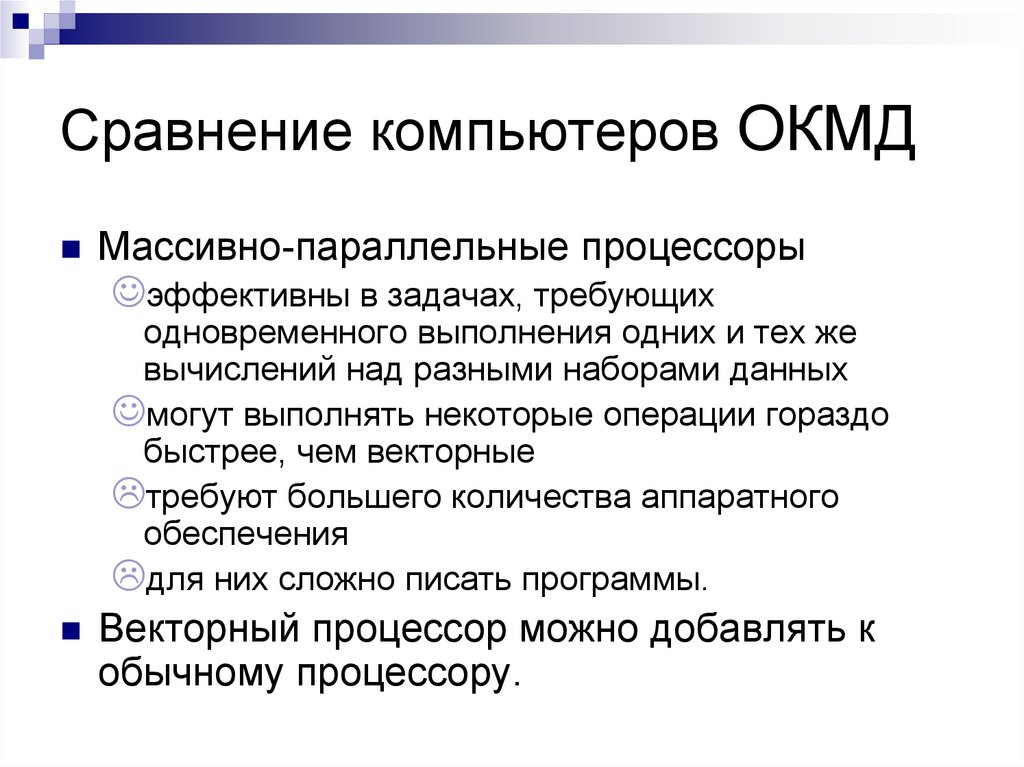

29. Сравнение компьютеров ОКМД

Массивно-параллельные процессорыэффективны в задачах, требующих

одновременного выполнения одних и тех же

вычислений над разными наборами данных

могут выполнять некоторые операции гораздо

быстрее, чем векторные

требуют большего количества аппаратного

обеспечения

для них сложно писать программы.

Векторный процессор можно добавлять к

обычному процессору.

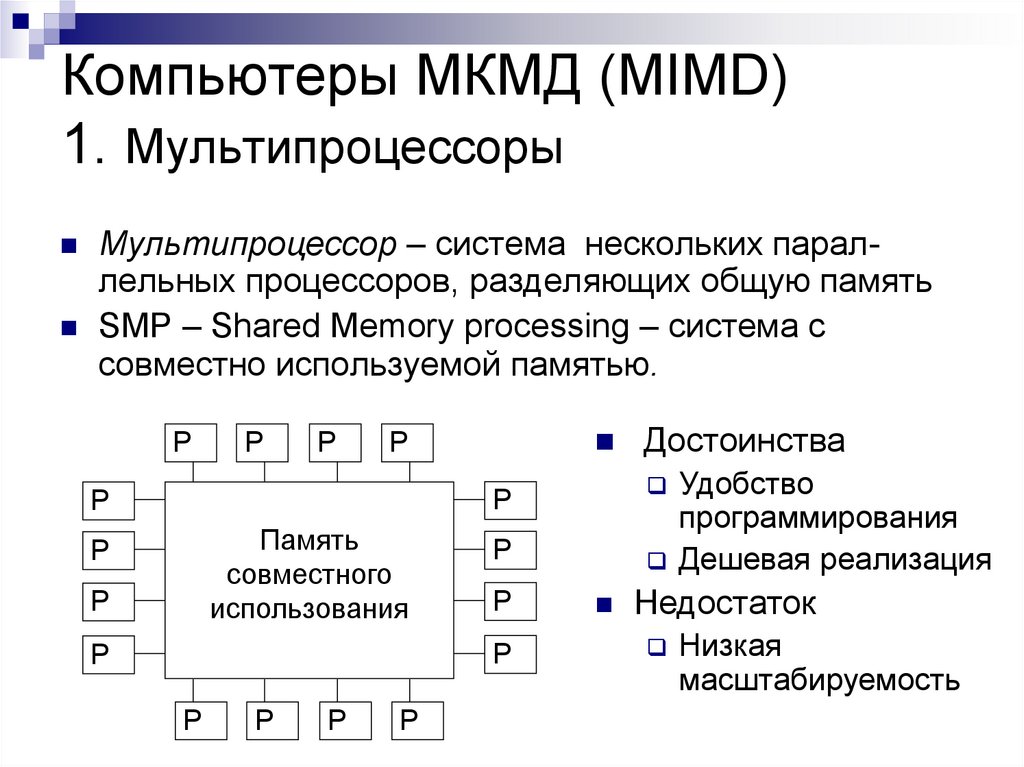

30. Компьютеры МКМД (МIMD) 1. Мультипроцессоры

Мультипроцессор – система нескольких параллельных процессоров, разделяющих общую памятьSMP – Shared Memory processing – система с

совместно используемой памятью.

Р

Р

Р

Р

Удобство

Р

Р

Память

совместного

использования

Р

Р

Р

Р

Р

Р

Р

Р

программирования

Дешевая реализация

Р

Р

Достоинства

Недостаток

Низкая

масштабируемость

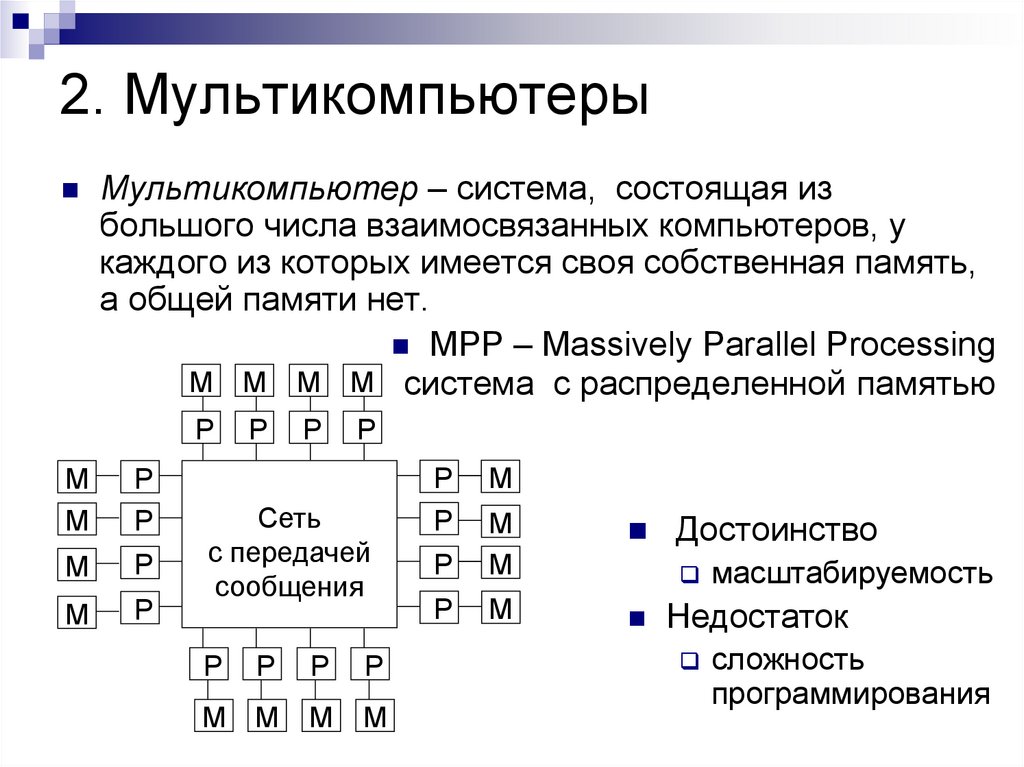

31. 2. Мультикомпьютеры

Мультикомпьютер – система, состоящая избольшого числа взаимосвязанных компьютеров, у

каждого из которых имеется своя собственная память,

а общей памяти нет.

MPP – Massively Parallel Processing

M M M M система с распределенной памятью

Р

M

M

Р

Р

M

Р

M

Р

Р

Р

Р

Сеть

с передачей

сообщения

Р

Р

Р

Р

M

M

M

M

Р

Р

M

Р

M

M

Р

M

Достоинство

масштабируемость

Недостаток

сложность

программирования

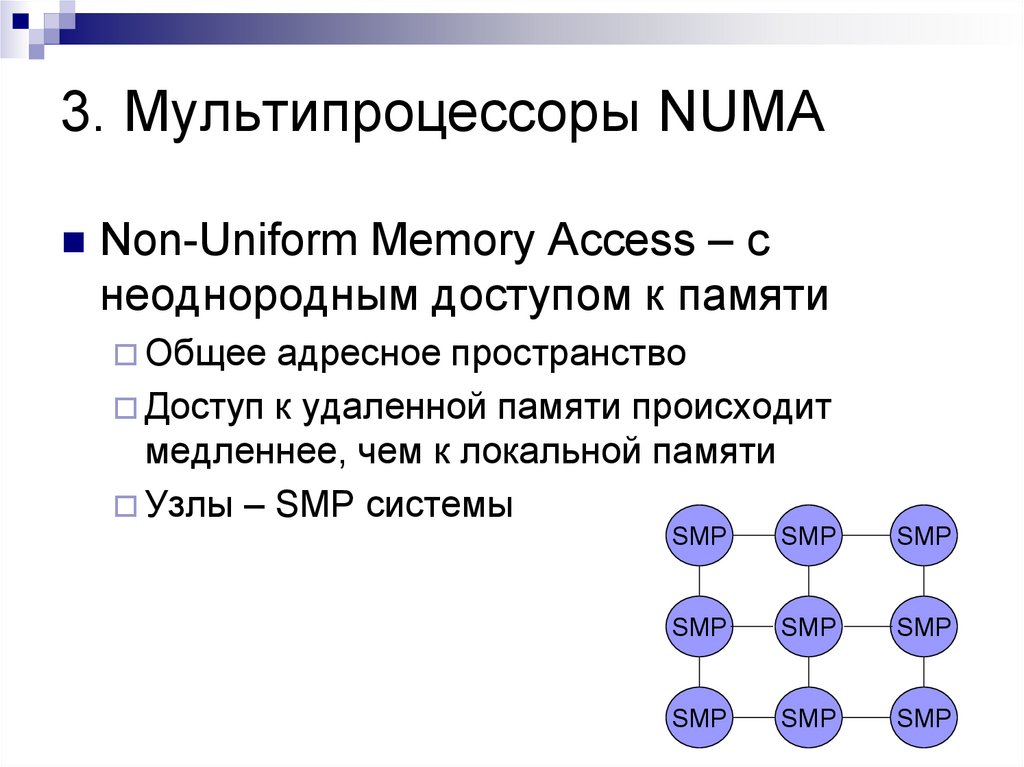

32. 3. Мультипроцессоры NUMA

Non-Uniform Memory Access – снеоднородным доступом к памяти

Общее адресное пространство

Доступ к удаленной памяти происходит

медленнее, чем к локальной памяти

Узлы – SMP системы

SMP

SMP

SMP

SMP

SMP

SMP

SMP

SMP

SMP

electronics

electronics