Similar presentations:

Ассемблер Atmel AVR. Занятие №1: Архитектура AVR, схемотехника ЭВМ

1.

АссемблерAtmel AVR

Занятие №1: Архитектура AVR,

схемотехника ЭВМ.

2.

Уровни абстракцииApplications

Kernel

Assembler

Firmware

Hardware

3.

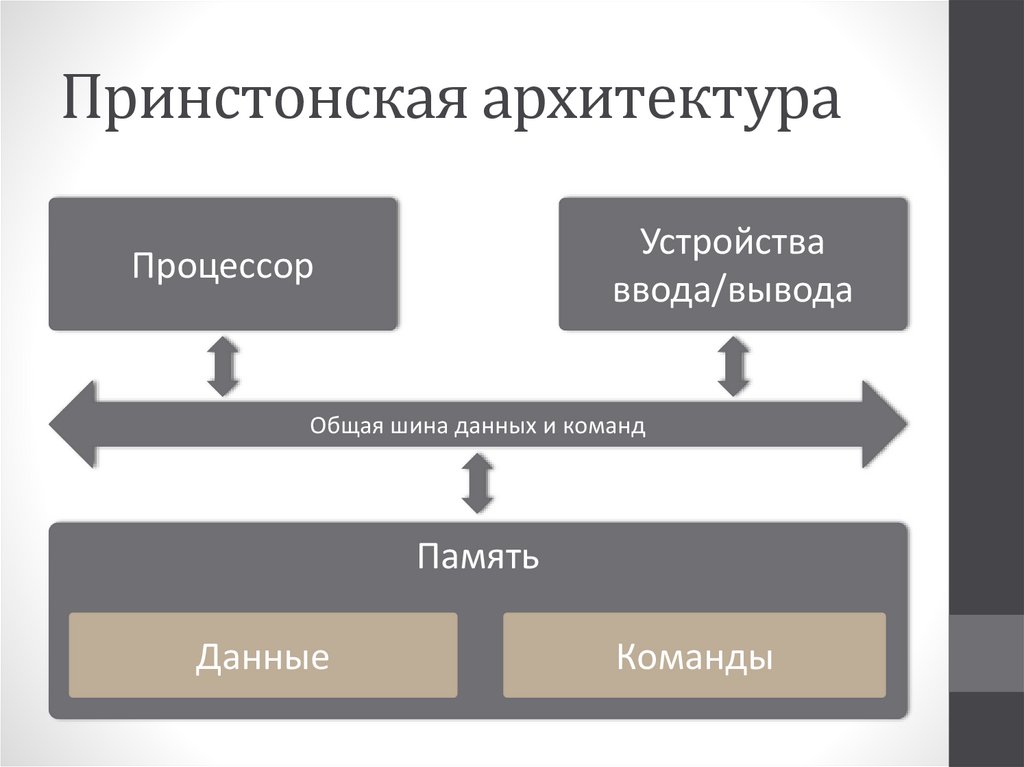

Принстонская архитектураУстройства

ввода/вывода

Процессор

Общая шина данных и команд

Память

Данные

Команды

4.

Гарвардская архитектураШина команд

Память

команд

Процессор

Память

данных

Шина данных

Устройства

ввода/вывода

5.

Архитектуры CISC и RISCCISC

RISC

Машинные

инструкции

Машинные

инструкции

Преобразование

микрокода

Обработка

инструкций

Микроинструкции

Обработка

микроинструкций

6.

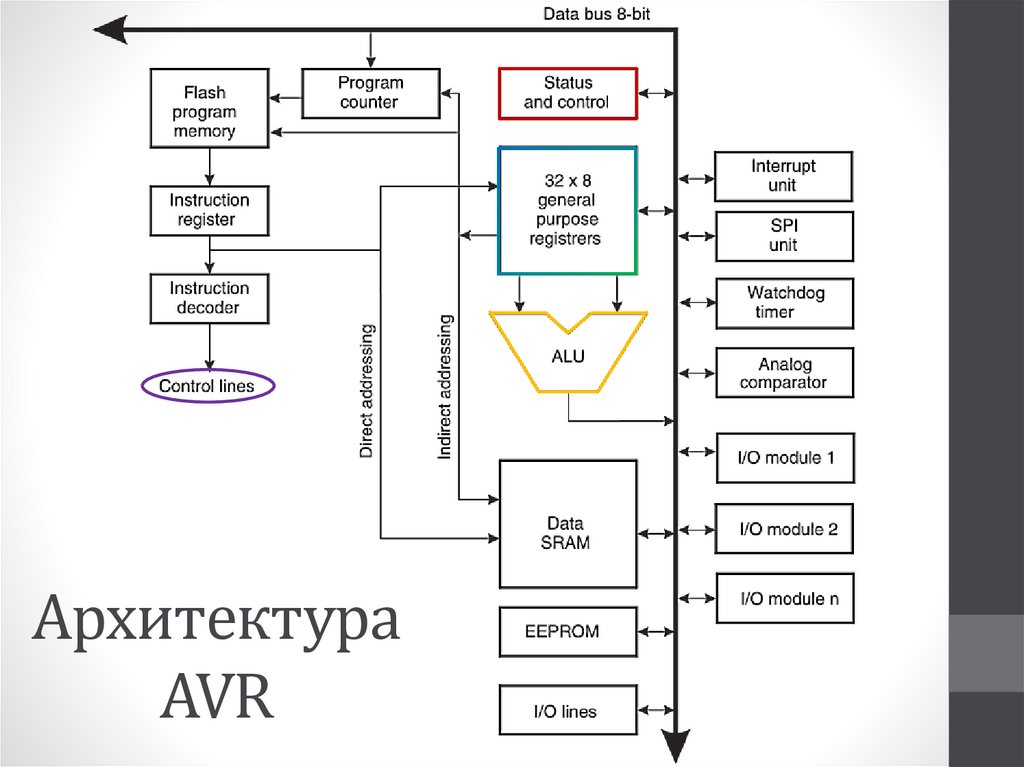

АрхитектураAVR

7.

Транзистор – всему головаБаза

Эмиттер

Коллектор

Транзистор – это кнопка, которая нажимается не

пальцем, а подачей напряжения на Базу, после чего ток

начинает протекать между Коллектором и Эмиттером.

8.

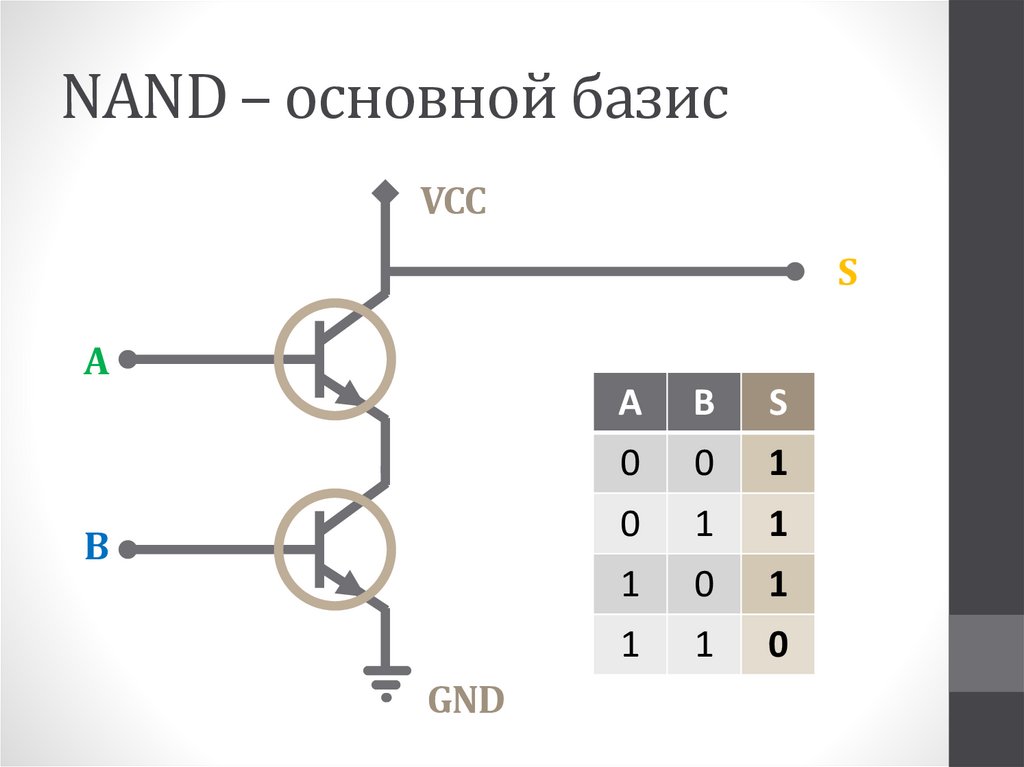

NAND – основной базисVCC

S

A

B

GND

A

B

S

0

0

1

0

1

1

1

0

1

1

1

0

9.

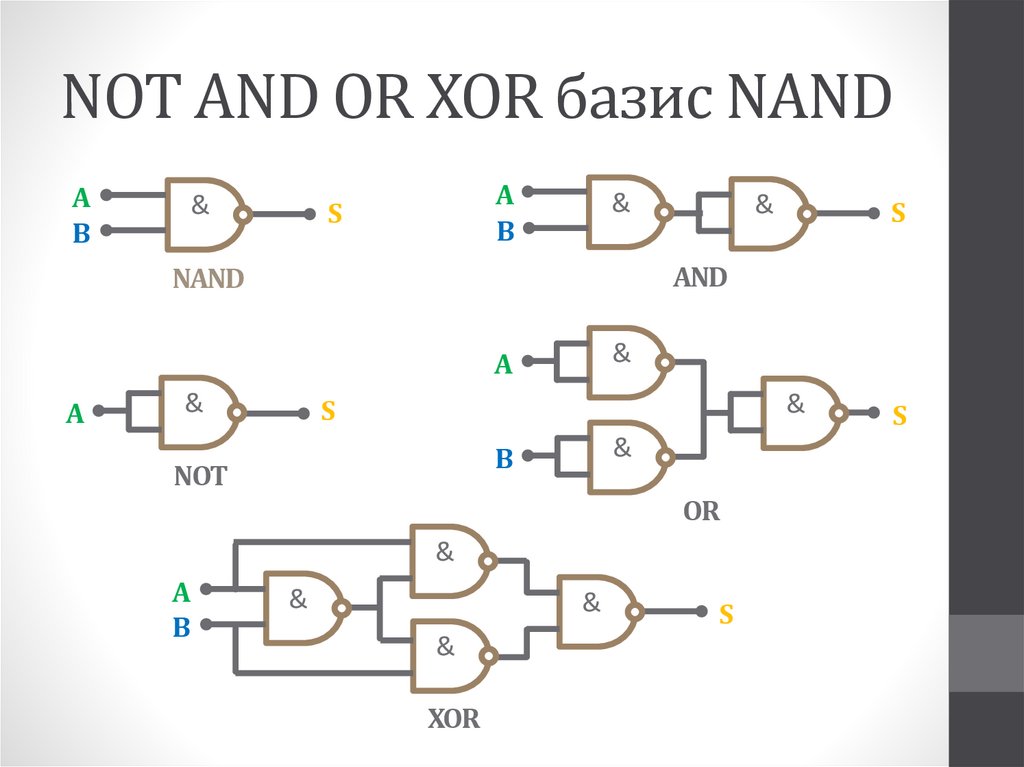

NOT AND OR XOR базис NANDA

B

&

A

B

S

&

&

A

&

&

S

&

B

NOT

OR

&

A

B

S

AND

NAND

A

&

&

&

&

XOR

S

S

10.

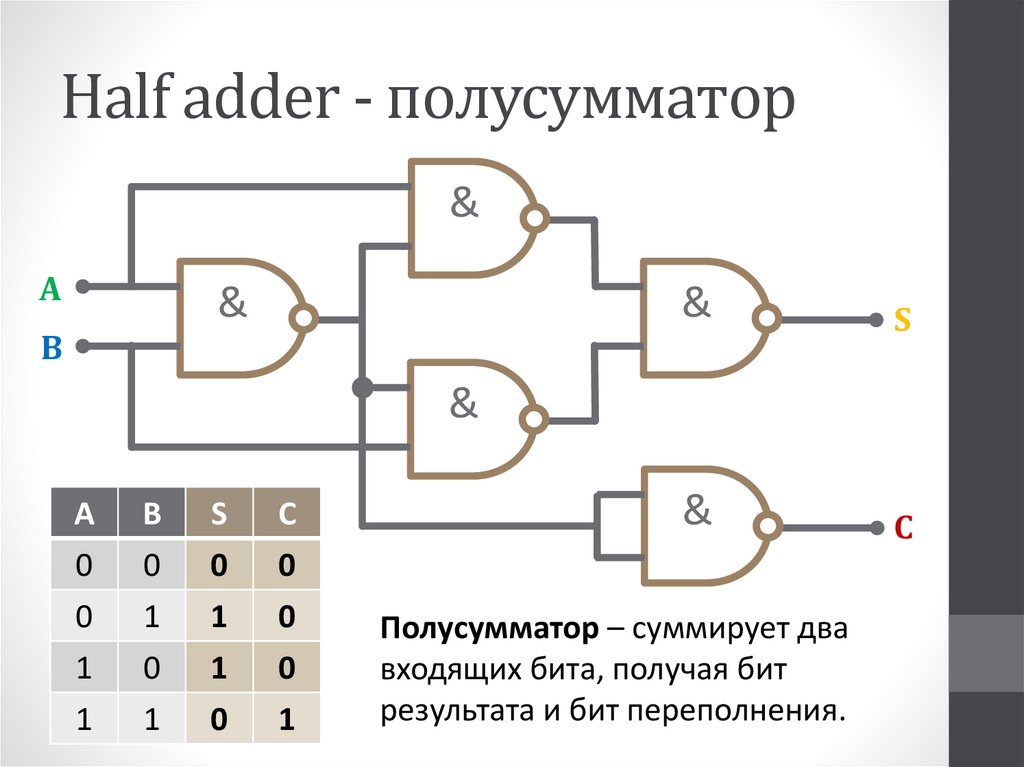

Half adder - полусумматор&

A

&

B

&

S

&

C

&

A

0

B

0

S

0

C

0

0

1

1

1

0

1

1

1

0

0

0

1

Полусумматор – суммирует два

входящих бита, получая бит

результата и бит переполнения.

11.

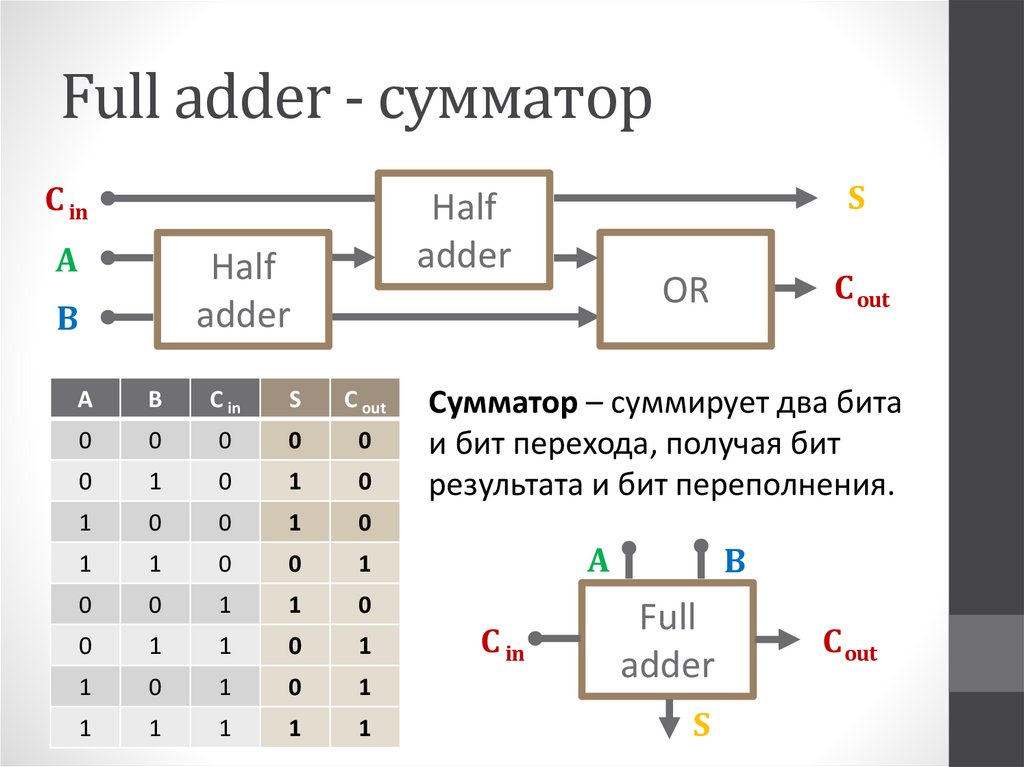

Full adder - сумматорC in

A

Half

adder

B

S

Half

adderS

A

B

С in

S

C out

0

0

0

0

0

0

1

0

1

0

1

0

0

1

0

1

1

0

0

1

0

0

1

1

0

0

1

1

0

1

1

0

1

0

1

1

1

1

1

1

C out

OR

Сумматор – суммирует два бита

и бит перехода, получая бит

результата и бит переполнения.

A

C in

B

Full

adder

S

C out

12.

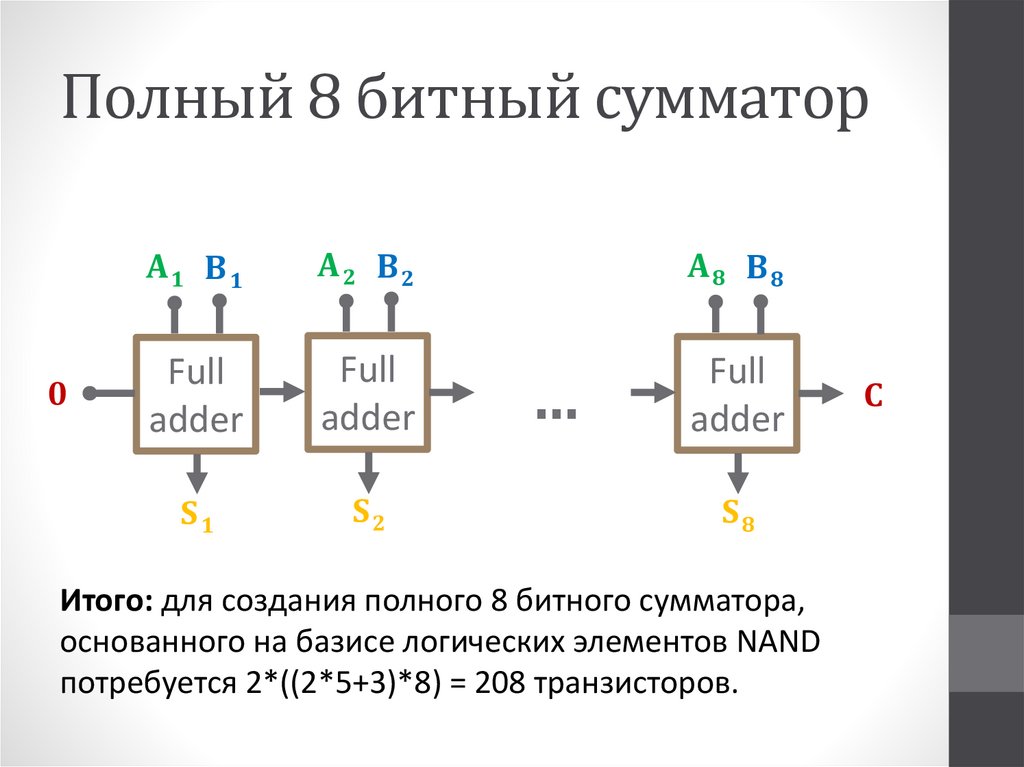

Полный 8 битный сумматор0

A1 B1

A2 B2

A8 B8

Full

adder

Full

adder

Full

adder

S1

S2

…

S8

Итого: для создания полного 8 битного сумматора,

основанного на базисе логических элементов NAND

потребуется 2*((2*5+3)*8) = 208 транзисторов.

C

13.

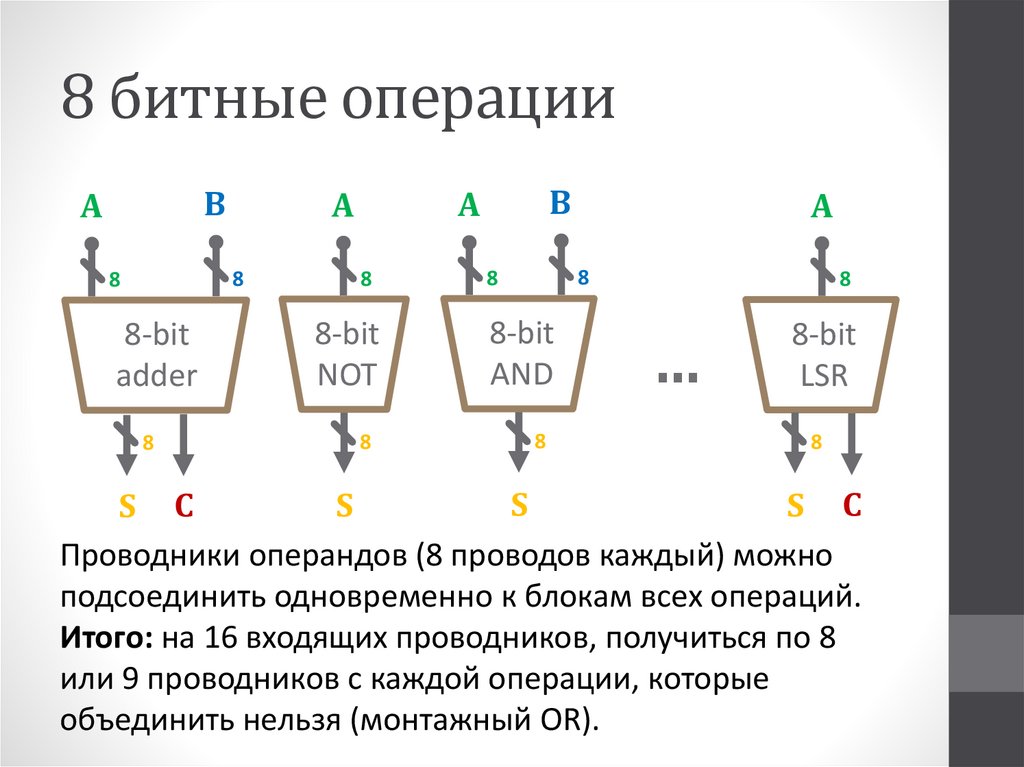

8 битные операцииB

A

8

8

8-bit

adder

8

B

A

A

8

8-bit

NOT

8

A

8

8

8-bit

AND

8

8

…

8-bit

LSR

8

S

S

S С

S С

Проводники операндов (8 проводов каждый) можно

подсоединить одновременно к блокам всех операций.

Итого: на 16 входящих проводников, получиться по 8

или 9 проводников с каждой операции, которые

объединить нельзя (монтажный OR).

14.

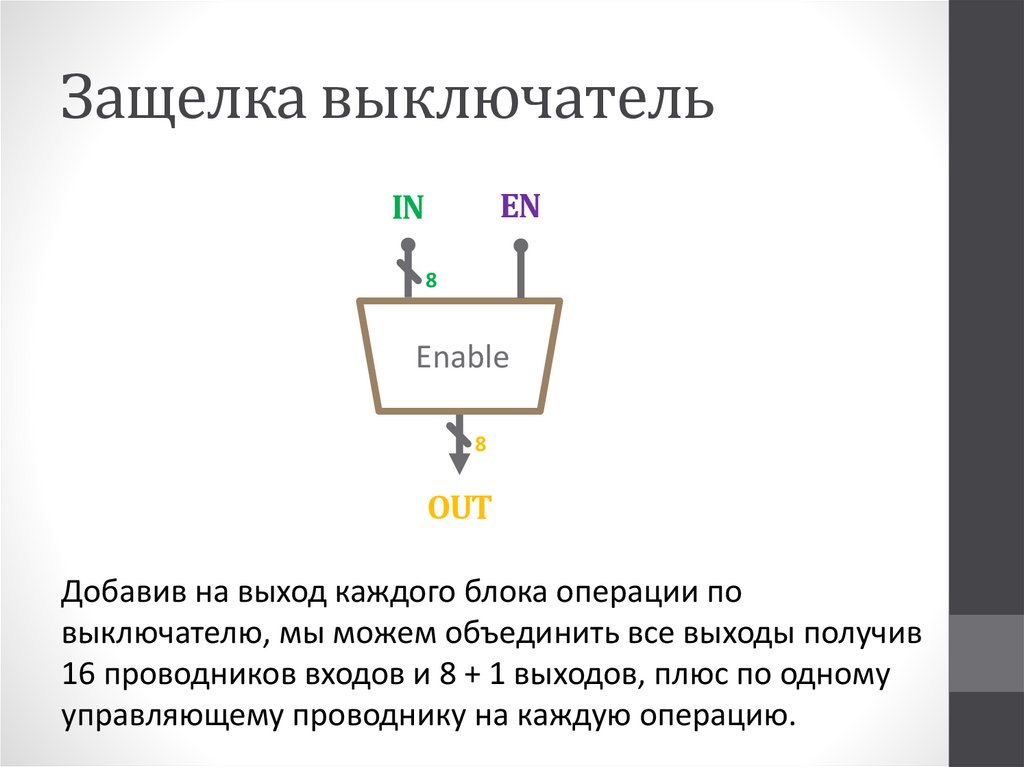

Защелка выключательEN

IN

8

Enable

8

OUT

Добавив на выход каждого блока операции по

выключателю, мы можем объединить все выходы получив

16 проводников входов и 8 + 1 выходов, плюс по одному

управляющему проводнику на каждую операцию.

15.

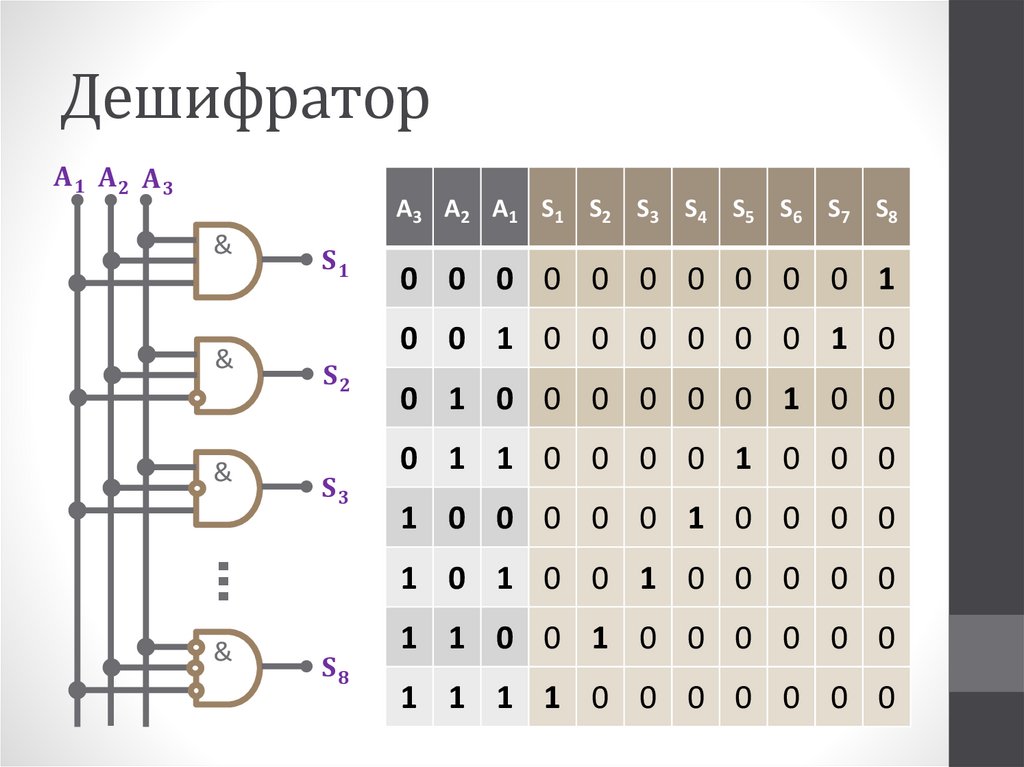

ДешифраторA1 A2 A3

A3 A 2 A1 S1 S2 S3 S4 S5 S6 S7 S8

&

&

&

S1

S2

S3

0 0 0 0 0 0 0 0 0 0 1

0 0 1 0 0 0 0 0 0 1 0

0 1 0 0 0 0 0 0 1 0 0

0 1 1 0 0 0 0 1 0 0 0

1 0 0 0 0 0 1 0 0 0 0

…

1 0 1 0 0 1 0 0 0 0 0

&

1 1 0 0 1 0 0 0 0 0 0

S8

1 1 1 1 0 0 0 0 0 0 0

16.

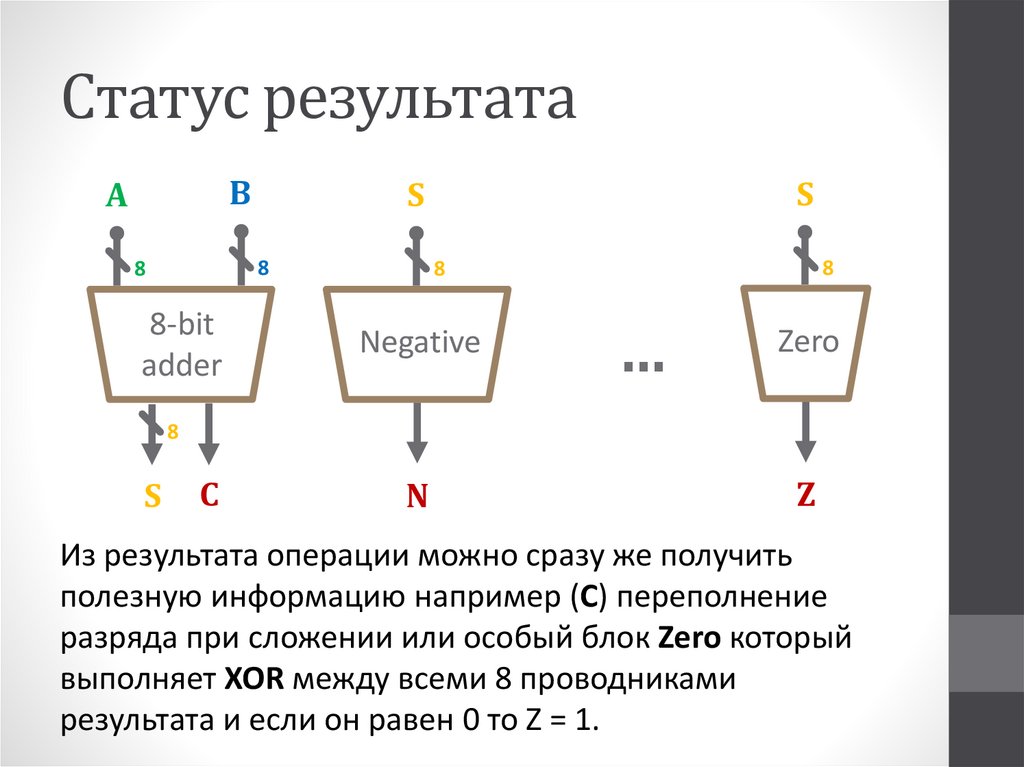

Статус результатаB

A

8

8

8-bit

adder

S

S

8

8

Negative

…

Zero

8

S

С

N

Z

Из результата операции можно сразу же получить

полезную информацию например (C) переполнение

разряда при сложении или особый блок Zero который

выполняет XOR между всеми 8 проводниками

результата и если он равен 0 то Z = 1.

17.

Арифметико-логическоеустройство

Операнд

Операнд

Статус

Сигналы

управления

АЛУ

Результат

Статус

18.

АрхитектураAVR

19.

Регистры процессора AVRR0

R1

0x00

0x01

Адрес 5 бит

…

R15

R16

R17

0x0F

0x10

0x11

Адрес 4 бита

…

R24

R25

R26

R27

R28

R29

R30

R31

X

Y

Z

0x18

0x19

0x1A

0x1B

0x1C

0x1D

0x1E

0x1F

Адрес 2 бита

20.

Память AVRFlash 16-bits

SRAM 8-bits

EEPROM 8-bits

0x0000

0x0000 РОН 0x001F

0x0000

0x0020 I/O 0x005F

0x0060

Внутренняя SRAM

Память программ

RAMEND

Память EEPROM

RAMEND+1

Внешняя SRAM

FLASHEND – 0xFFFF

0xFFFF

EEPROMEND – 0xFFFF

21.

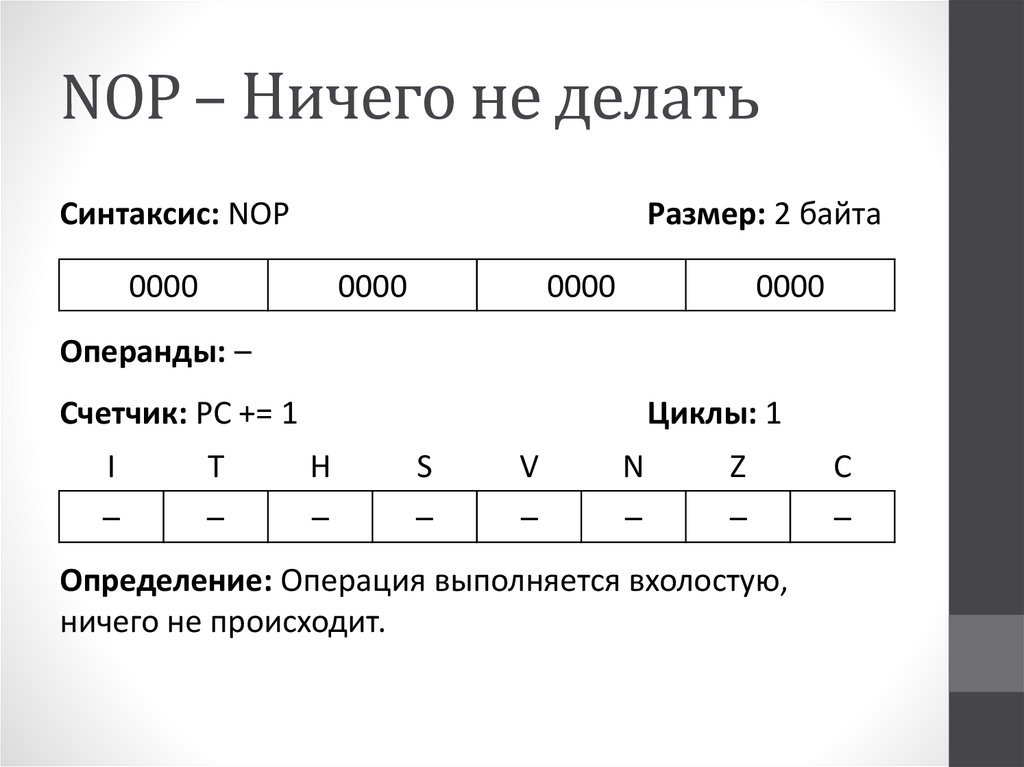

NOP – Ничего не делатьСинтаксис: NOP

Размер: 2 байта

0000

0000

0000

0000

Операнды: –

Счетчик: PC += 1

I

–

T

–

Циклы: 1

H

–

S

–

V

–

N

–

Z

–

Определение: Операция выполняется вхолостую,

ничего не происходит.

C

–

22.

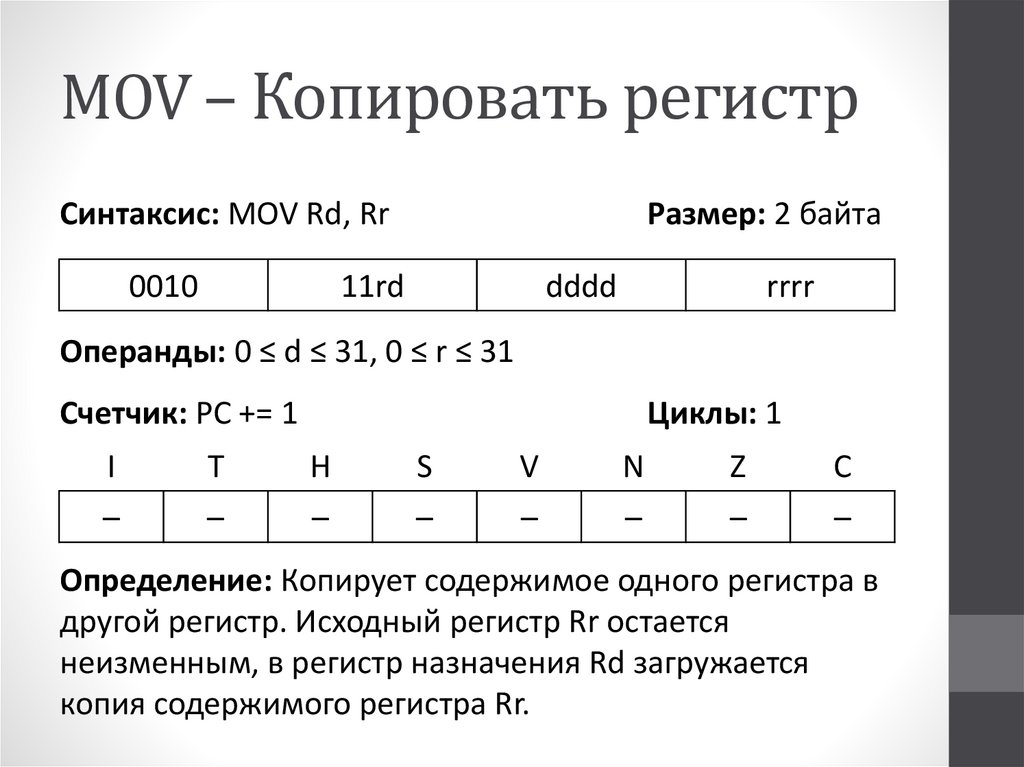

MOV – Копировать регистрСинтаксис: MOV Rd, Rr

0010

Размер: 2 байта

11rd

dddd

rrrr

Операнды: 0 ≤ d ≤ 31, 0 ≤ r ≤ 31

Счетчик: PC += 1

I

–

T

–

Циклы: 1

H

–

S

–

V

–

N

–

Z

–

C

–

Определение: Копирует содержимое одного регистра в

другой регистр. Исходный регистр Rr остается

неизменным, в регистр назначения Rd загружается

копия содержимого регистра Rr.

23.

LDI – Загрузитьзначение в регистр

Синтаксис: LDI Rd, K

1110

Размер: 2 байта

KKKK

dddd

KKKK

Операнды: 16 ≤ d ≤ 31, 0 ≤ K ≤ 255

Счетчик: PC += 1

I

–

T

–

Циклы: 1

H

–

S

–

V

–

N

–

Z

–

C

–

Определение: Загрузить непосредственное значение из

кода операции в регистр Rd.

24.

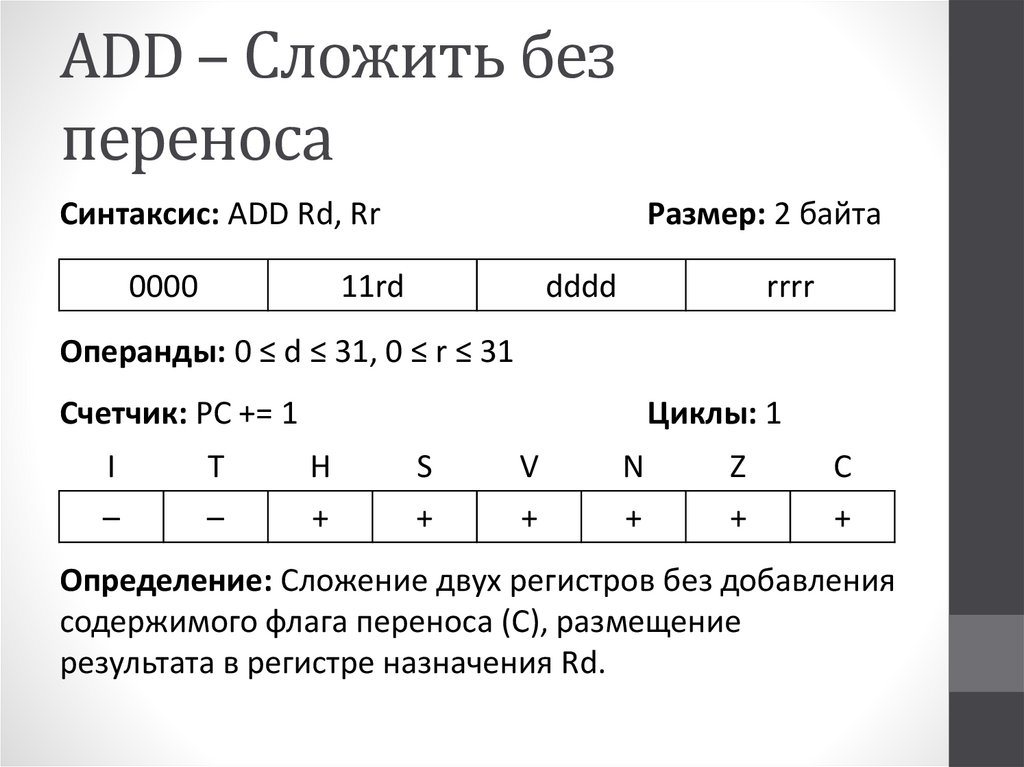

ADD – Сложить безпереноса

Синтаксис: ADD Rd, Rr

0000

Размер: 2 байта

11rd

dddd

rrrr

Операнды: 0 ≤ d ≤ 31, 0 ≤ r ≤ 31

Счетчик: PC += 1

I

–

T

–

Циклы: 1

H

+

S

+

V

+

N

+

Z

+

C

+

Определение: Сложение двух регистров без добавления

содержимого флага переноса (С), размещение

результата в регистре назначения Rd.

25.

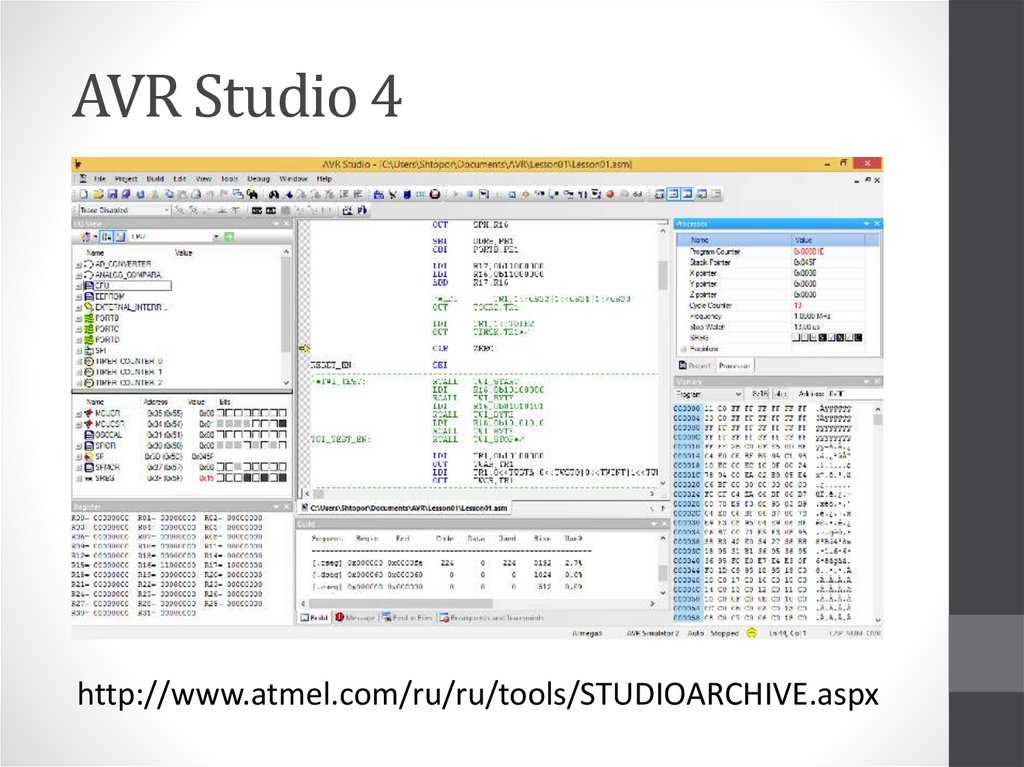

AVR Studio 4http://www.atmel.com/ru/ru/tools/STUDIOARCHIVE.aspx

programming

programming