Similar presentations:

Ассемблер Atmel AVR. Занятие №2: Арифметические и логические операции

1.

АссемблерAtmel AVR

Занятие №2: Арифметические и

логические операции

2.

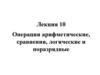

INC – ИнкрементироватьСинтаксис: INC Rd

1001

Размер: 2 байта

010d

dddd

0011

Операнды: 0 ≤ d ≤ 31

Счетчик: PC += 1

I

–

T

–

Циклы: 1

H

–

S

+

V

+

N

+

Z

+

C

–

Определение: Добавление единицы к содержимому

регистра Rd и размещение результата в регистре

назначения Rd.

3.

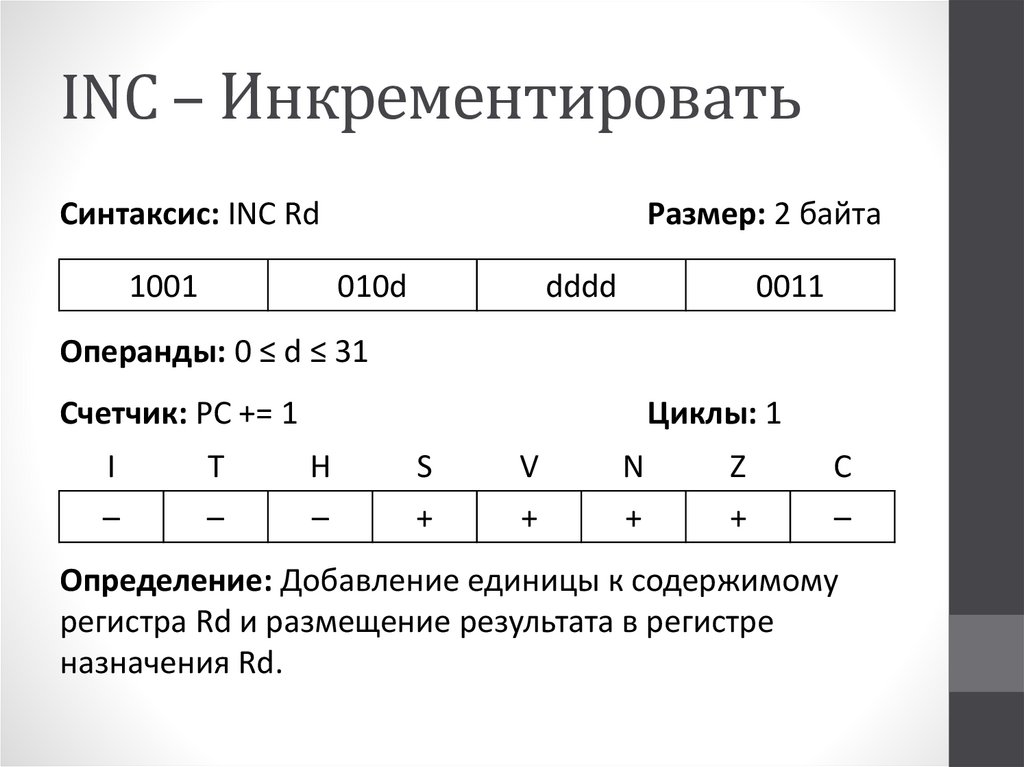

DEC – ДекрементироватьСинтаксис: DEC Rd

1001

Размер: 2 байта

010d

dddd

1010

Операнды: 0 ≤ d ≤ 31

Счетчик: PC += 1

I

–

T

–

Циклы: 1

H

–

S

+

V

+

N

+

Z

+

Определение: Вычитание единицы из содержимого

регистра Rd и размещение результата в регистре

назначения Rd.

C

–

4.

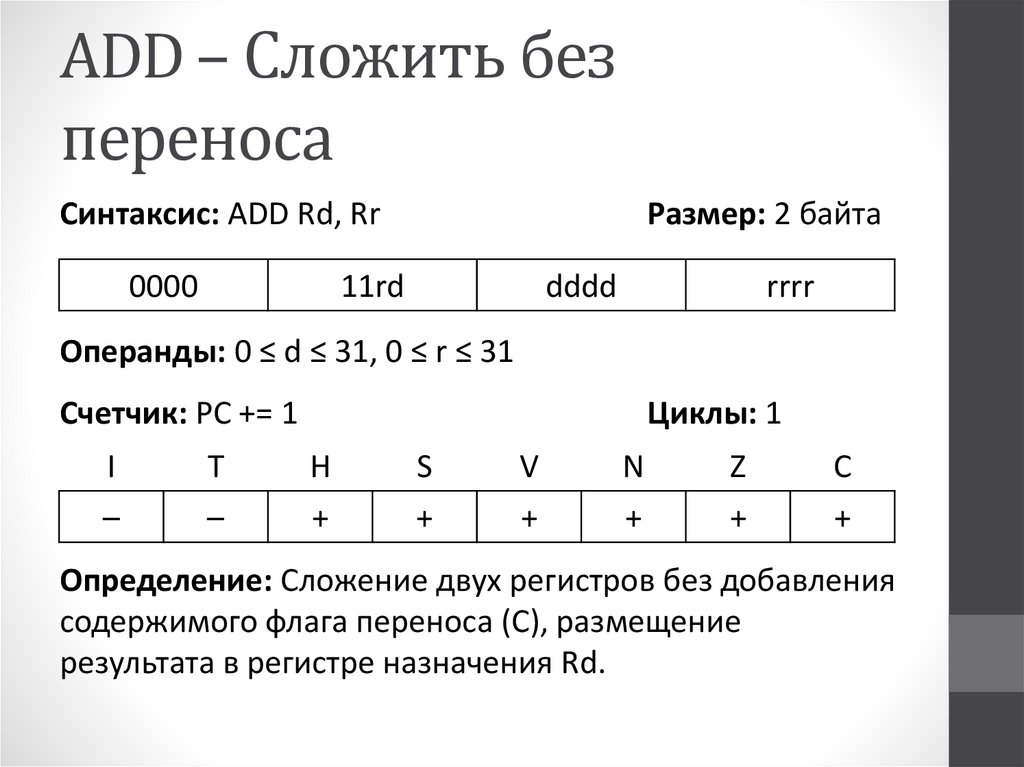

ADD – Сложить безпереноса

Синтаксис: ADD Rd, Rr

0000

Размер: 2 байта

11rd

dddd

rrrr

Операнды: 0 ≤ d ≤ 31, 0 ≤ r ≤ 31

Счетчик: PC += 1

I

–

T

–

Циклы: 1

H

+

S

+

V

+

N

+

Z

+

C

+

Определение: Сложение двух регистров без добавления

содержимого флага переноса (С), размещение

результата в регистре назначения Rd.

5.

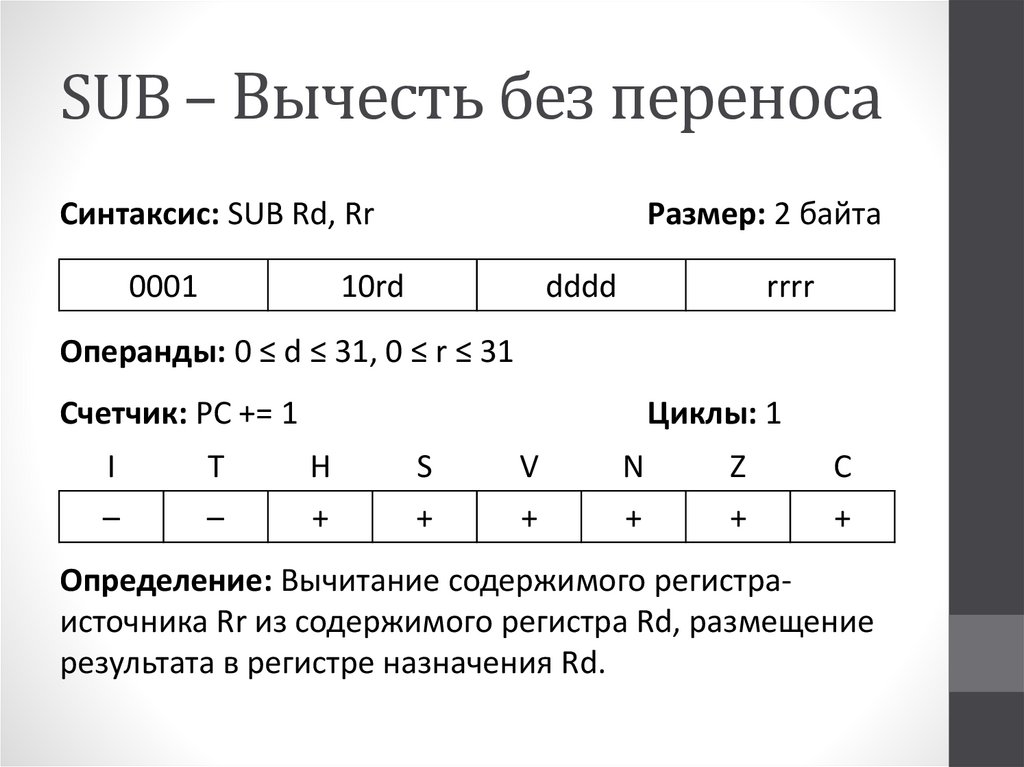

SUB – Вычесть без переносаСинтаксис: SUB Rd, Rr

0001

Размер: 2 байта

10rd

dddd

rrrr

Операнды: 0 ≤ d ≤ 31, 0 ≤ r ≤ 31

Счетчик: PC += 1

I

–

T

–

Циклы: 1

H

+

S

+

V

+

N

+

Z

+

C

+

Определение: Вычитание содержимого регистраисточника Rr из содержимого регистра Rd, размещение

результата в регистре назначения Rd.

6.

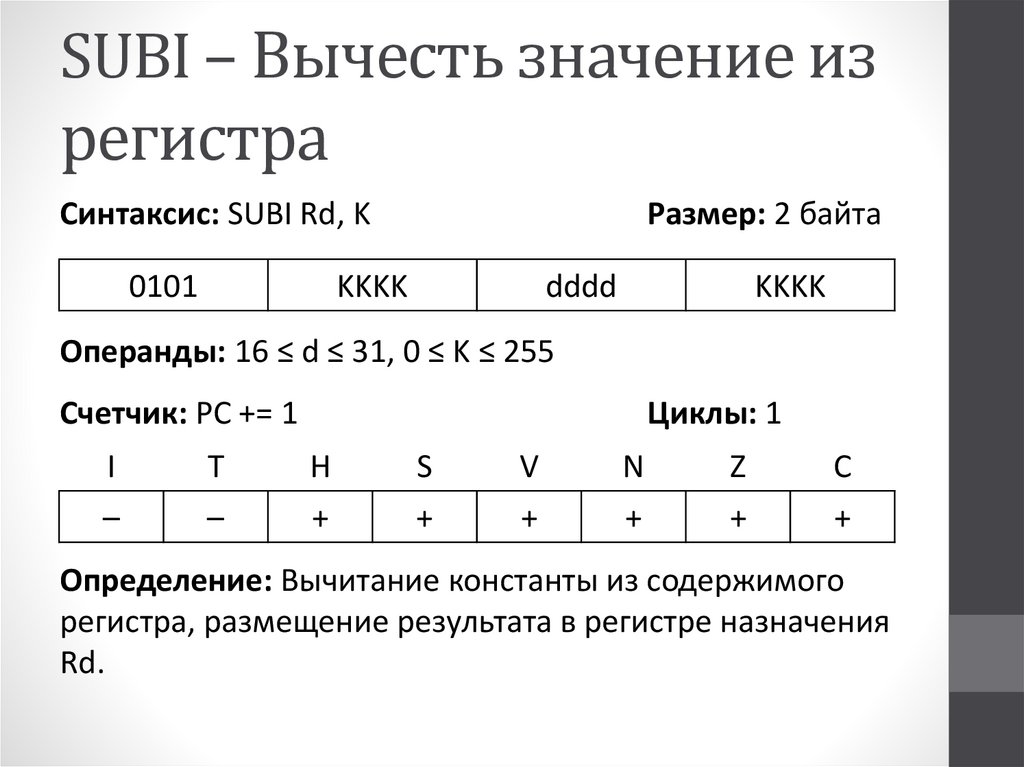

SUBI – Вычесть значение изрегистра

Синтаксис: SUBI Rd, K

0101

Размер: 2 байта

KKKK

dddd

KKKK

Операнды: 16 ≤ d ≤ 31, 0 ≤ K ≤ 255

Счетчик: PC += 1

I

–

T

–

Циклы: 1

H

+

S

+

V

+

N

+

Z

+

C

+

Определение: Вычитание константы из содержимого

регистра, размещение результата в регистре назначения

Rd.

7.

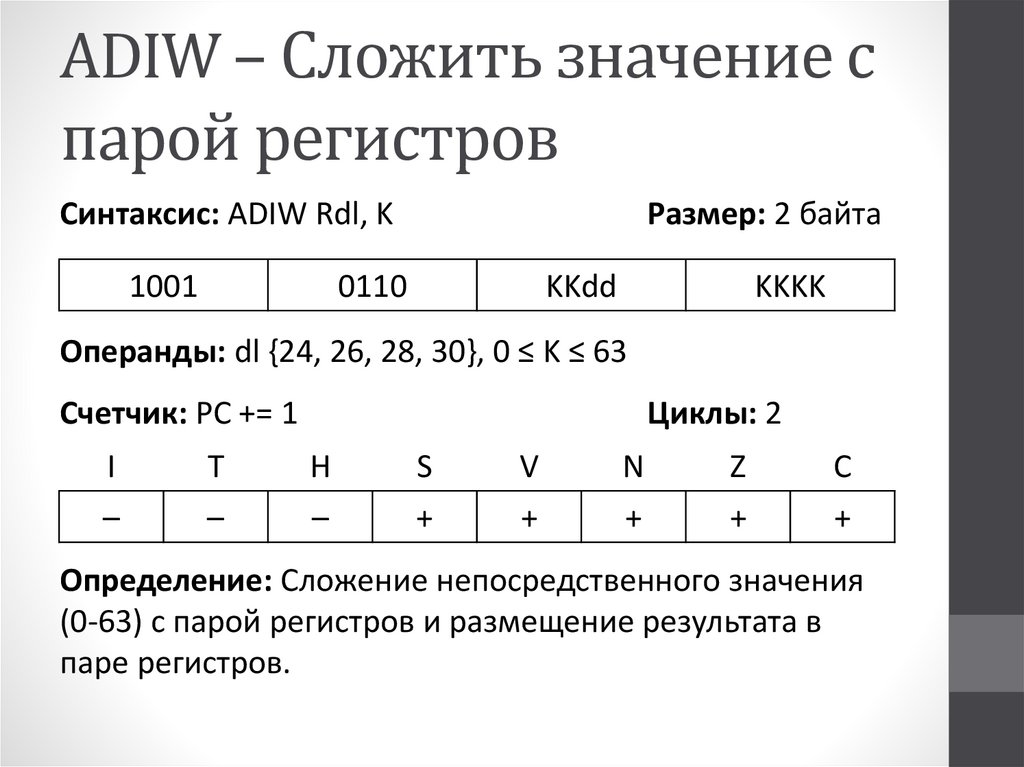

ADIW – Сложить значение спарой регистров

Синтаксис: ADIW Rdl, K

1001

Размер: 2 байта

0110

KKdd

KKKK

Операнды: dl {24, 26, 28, 30}, 0 ≤ K ≤ 63

Счетчик: PC += 1

I

–

T

–

Циклы: 2

H

–

S

+

V

+

N

+

Z

+

C

+

Определение: Сложение непосредственного значения

(0-63) с парой регистров и размещение результата в

паре регистров.

8.

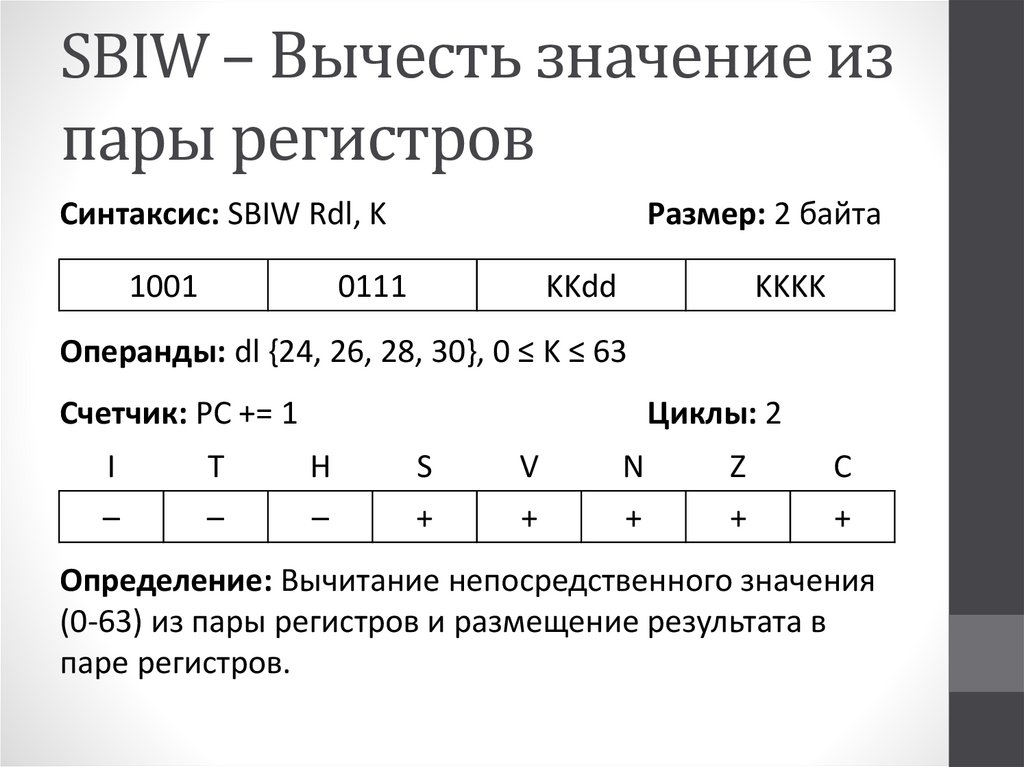

SBIW – Вычесть значение изпары регистров

Синтаксис: SBIW Rdl, K

1001

Размер: 2 байта

0111

KKdd

KKKK

Операнды: dl {24, 26, 28, 30}, 0 ≤ K ≤ 63

Счетчик: PC += 1

I

–

T

–

Циклы: 2

H

–

S

+

V

+

N

+

Z

+

C

+

Определение: Вычитание непосредственного значения

(0-63) из пары регистров и размещение результата в

паре регистров.

9.

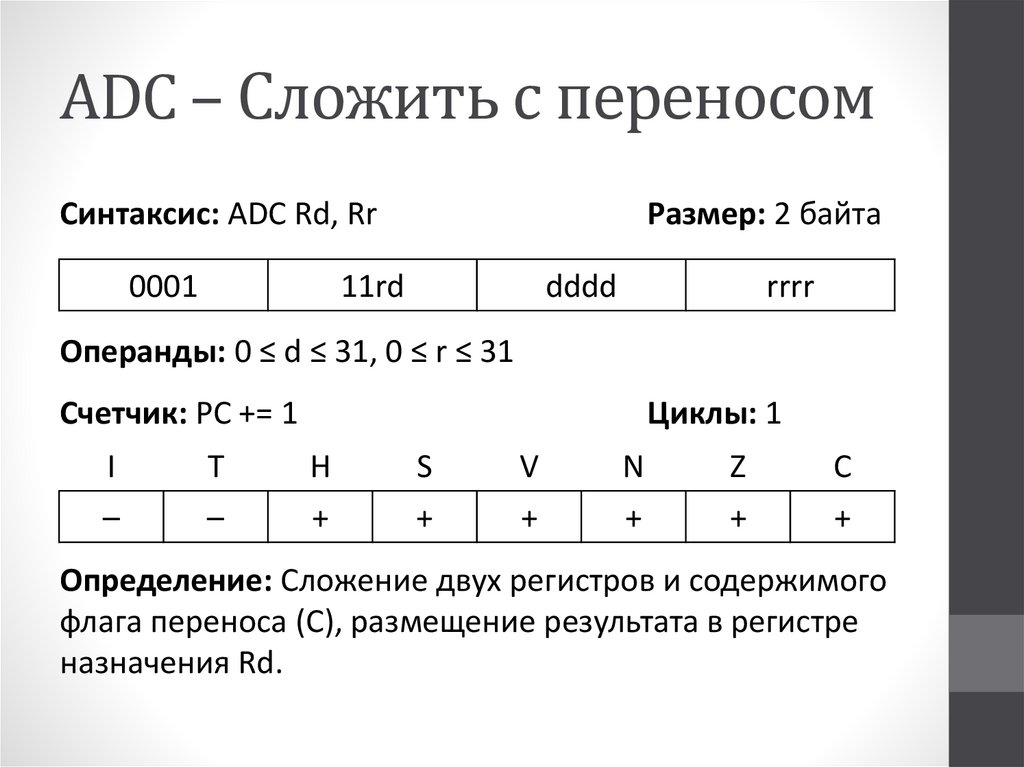

ADC – Сложить с переносомСинтаксис: ADC Rd, Rr

0001

Размер: 2 байта

11rd

dddd

rrrr

Операнды: 0 ≤ d ≤ 31, 0 ≤ r ≤ 31

Счетчик: PC += 1

I

–

T

–

Циклы: 1

H

+

S

+

V

+

N

+

Z

+

C

+

Определение: Сложение двух регистров и содержимого

флага переноса (С), размещение результата в регистре

назначения Rd.

10.

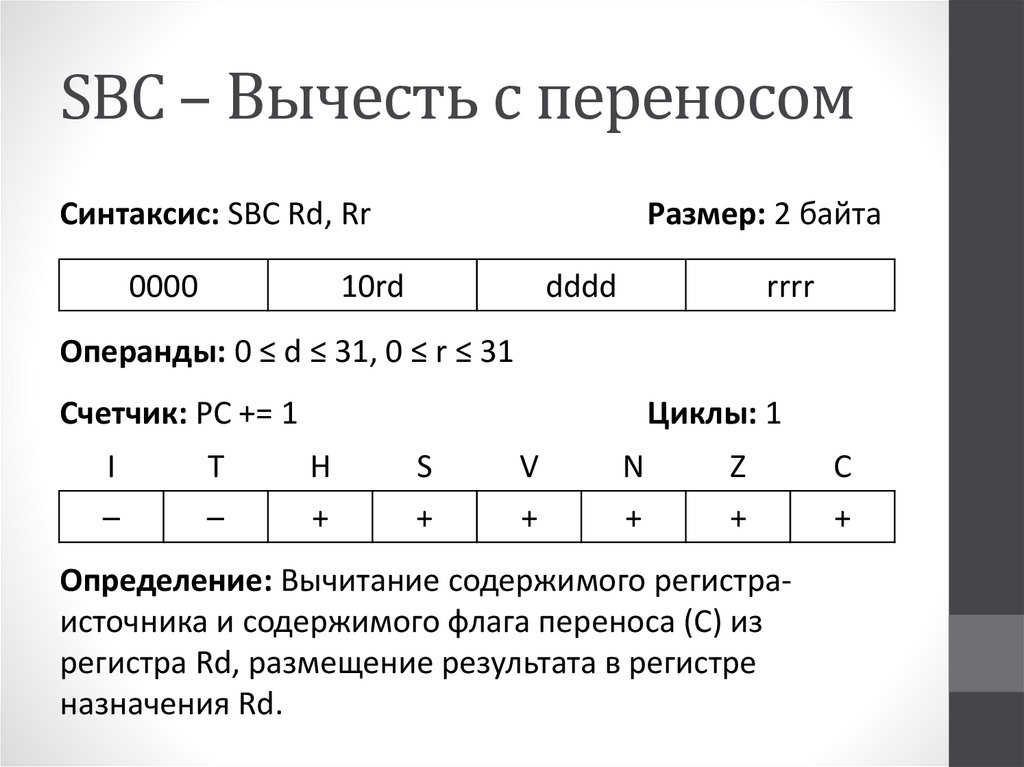

SBC – Вычесть с переносомСинтаксис: SBC Rd, Rr

0000

Размер: 2 байта

10rd

dddd

rrrr

Операнды: 0 ≤ d ≤ 31, 0 ≤ r ≤ 31

Счетчик: PC += 1

I

–

T

–

Циклы: 1

H

+

S

+

V

+

N

+

Z

+

Определение: Вычитание содержимого регистраисточника и содержимого флага переноса (С) из

регистра Rd, размещение результата в регистре

назначения Rd.

C

+

11.

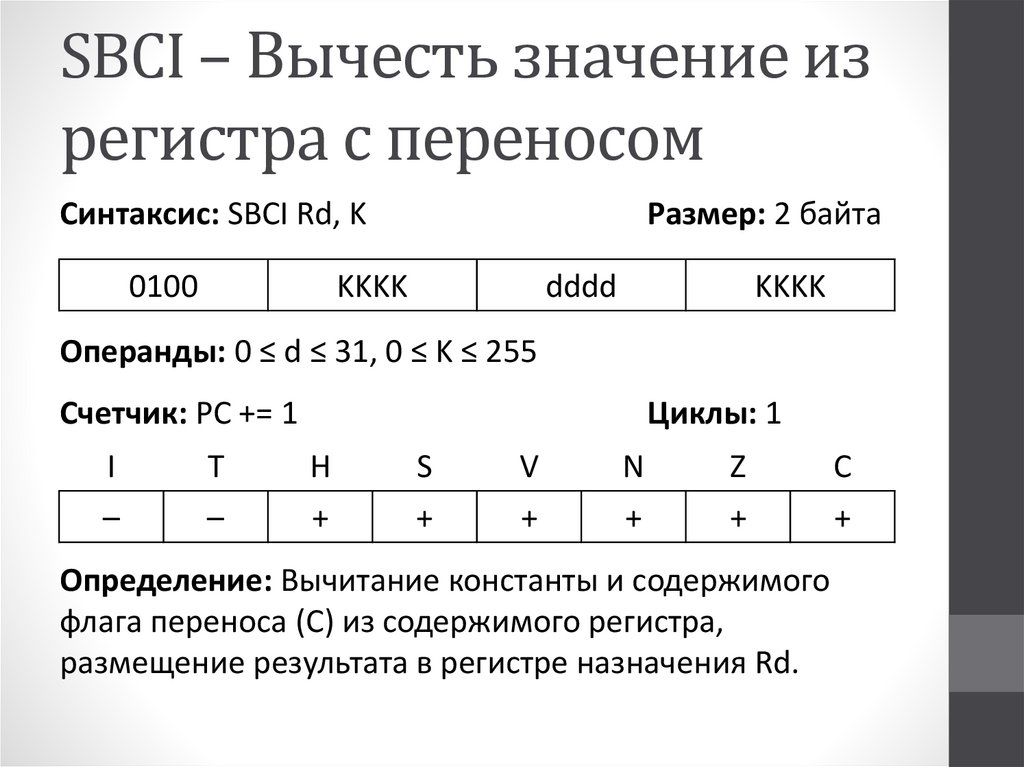

SBCI – Вычесть значение изрегистра с переносом

Синтаксис: SBCI Rd, K

0100

Размер: 2 байта

KKKK

dddd

KKKK

Операнды: 0 ≤ d ≤ 31, 0 ≤ K ≤ 255

Счетчик: PC += 1

I

–

T

–

Циклы: 1

H

+

S

+

V

+

N

+

Z

+

Определение: Вычитание константы и содержимого

флага переноса (С) из содержимого регистра,

размещение результата в регистре назначения Rd.

C

+

programming

programming