Similar presentations:

Программные средства моделирования логических БИС (поддерживающие языки Verilog, VHDL)

1.

Кафедра промышленной электроники (ПрЭ)Программные средства моделирования логических БИС

(поддерживающие языки Verilog, VHDL)

Выполнил:

Студент гр. 368-М1

Лункин Дмитрий Сергеевич

Томск 2019

2.

Определение СБИССверхбольшая интегральная схема

изготовленная

на

(СБИС) – электронная схема,

полупроводниковом

кристалле,

помещенная

в

неразборный корпус.

Малая интегральная схема (МИС) — до 100 элементов

Средняя интегральная схема (СИС) — до 1000

Большая интегральная схема (БИС) — до 10000

Сверхбольшая интегральная схема(СБИС)— до 1 млн.

Ультрабольшая интегральная схема (УБИС) — до 1 млрд

Гигабольшая интегральная схема(ГБИС) — более 1 млрд

2

3.

Определение ПЛИСПрограммируемая логическая интегральная схема (ПЛИС) - электронный

компонент

(интегральная

микросхема),

используемый

для

создания

конфигурируемых цифровых электронных схем.

Высокая надежность

Низкое энергопотребление

Интеграция встроенного CPU

Жесткое реальное время

Параллелизм вычислений и работы блоков

3

4.

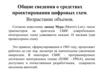

Языки описания аппаратуры Verilog и VHDLVerilog , VHDL -

языки описания моделей аппаратуры, пригодных для

дальнейшего автоматического синтеза спецификаций, с целью производства

реальных чипов.

Verilog

VHDL

Простота конструкций;

Более сложные конструкции;

параллелизм;

параллелизм;

Схожесть с Си;

большая

Слабо типизирован

цифровых схем и других моделей) ;

Нет разделения интерфейса и

строго типизирован

реализации

Разделение интерфейса и реализации

универсальность

(описание

4

5.

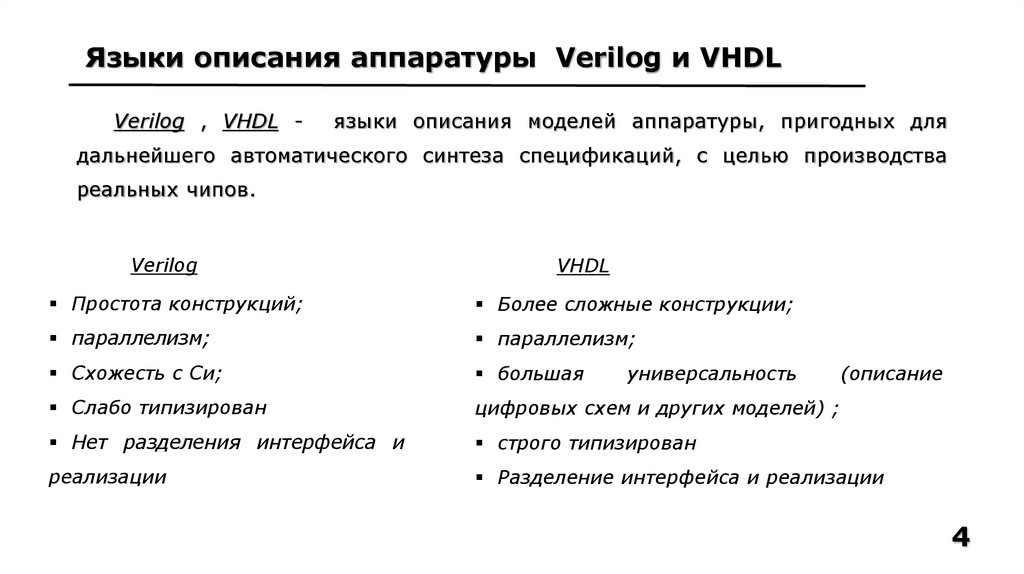

Языки описания аппаратуры Verilog и VHDLПример реализации простого мультиплексора с применением Verilog и VHDL

VHDL

Verilog

5

6.

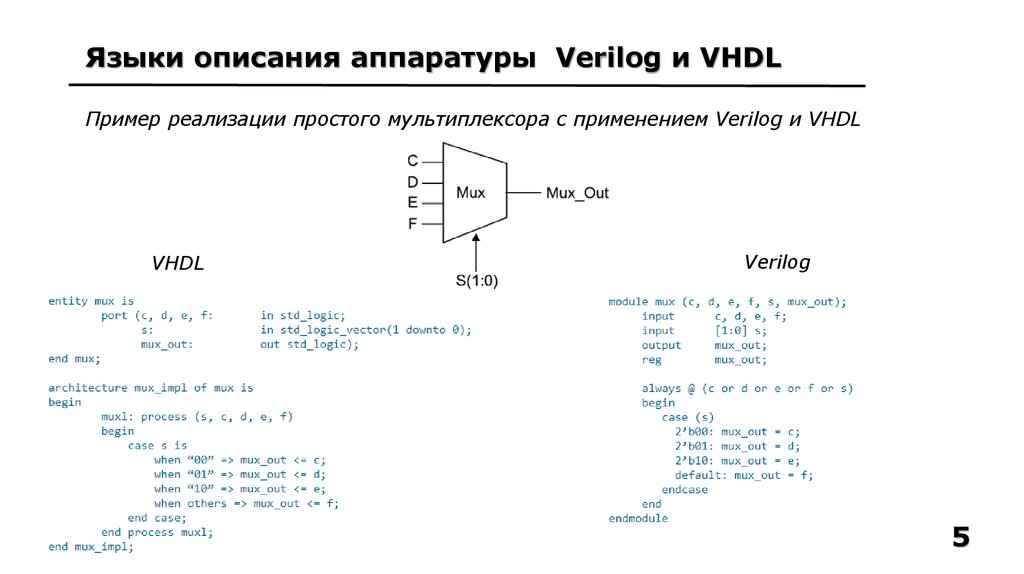

Средства разработки и моделирования для ПЛИС6

7.

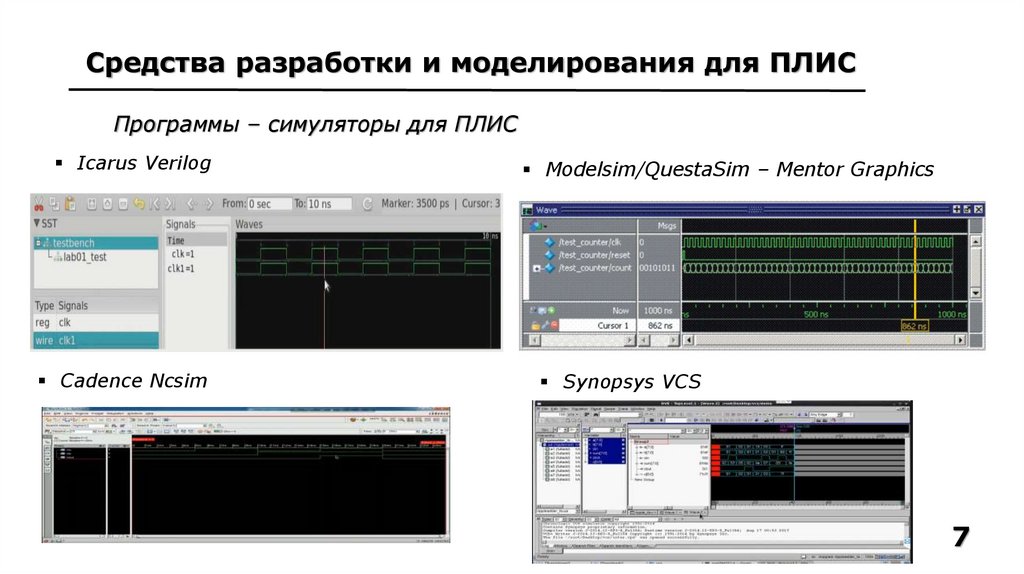

Средства разработки и моделирования для ПЛИСПрограммы – симуляторы для ПЛИС

Icarus Verilog

Cadence Ncsim

Modelsim/QuestaSim – Mentor Graphics

Synopsys VCS

7

8.

Средства разработки и моделирования для ПЛИСIntel Quartus Prime - для разработки дизайна систем на базе Intel FPGA, SoC

и Complex Programmable Logic Device (CPLD), начиная с самых основ и включая

далее отладку взаимодействия, оптимизацию, верификацию и моделирование.

Возможности Quartus

Создание схемы графическим способом (Shematic)

Описание на HDL – языках (Verilog, VHDL)

Моделирование работы синтезируемой схемы (ModelSim)

Компиляция проекта, взаимодействие с реальным железом

8

9.

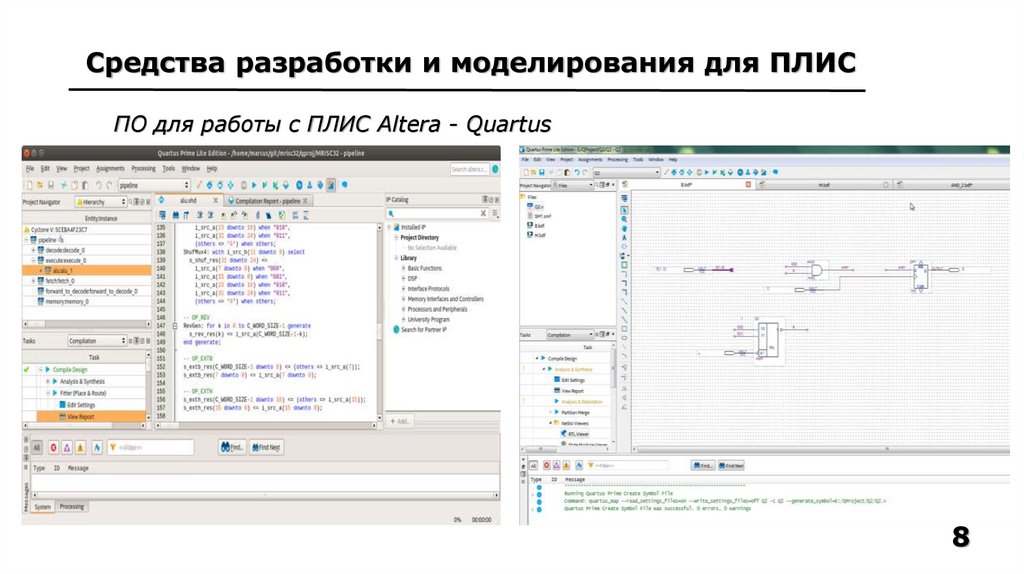

Средства разработки и моделирования для ПЛИСПО для работы с ПЛИС Altera - Quartus

8

10.

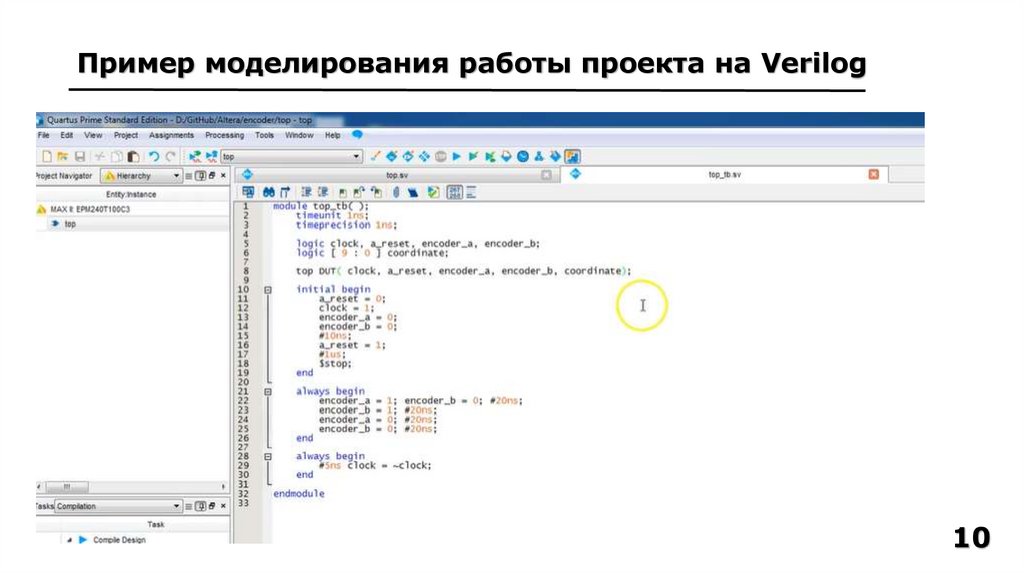

Пример моделирования работы проекта на Verilog10

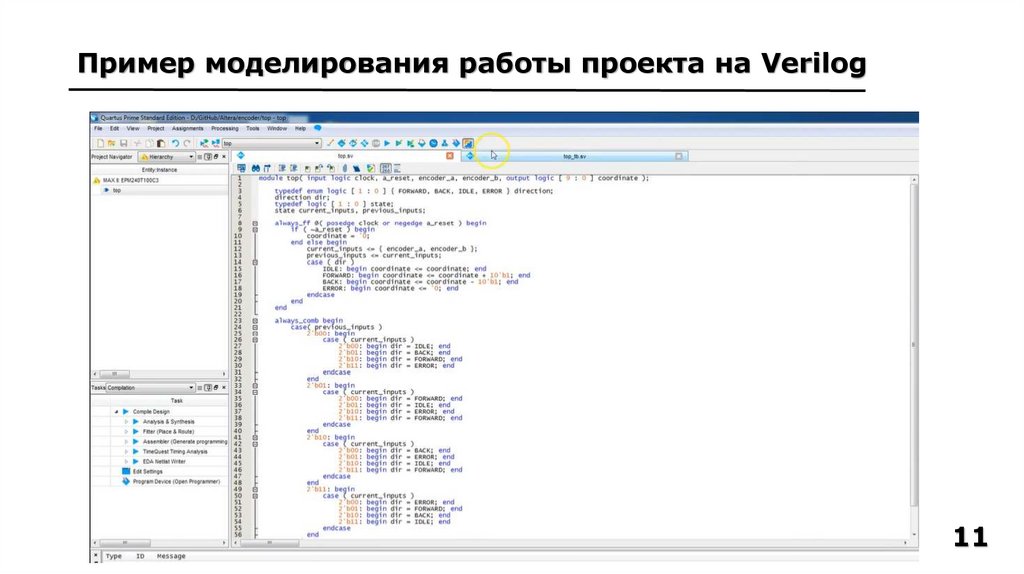

11.

Пример моделирования работы проекта на Verilog11

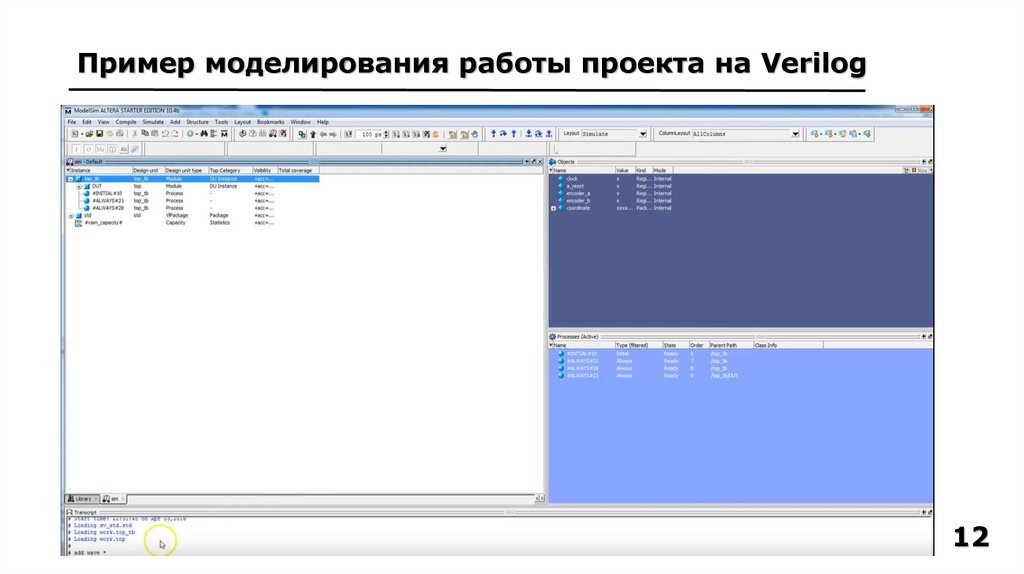

12.

Пример моделирования работы проекта на Verilog12

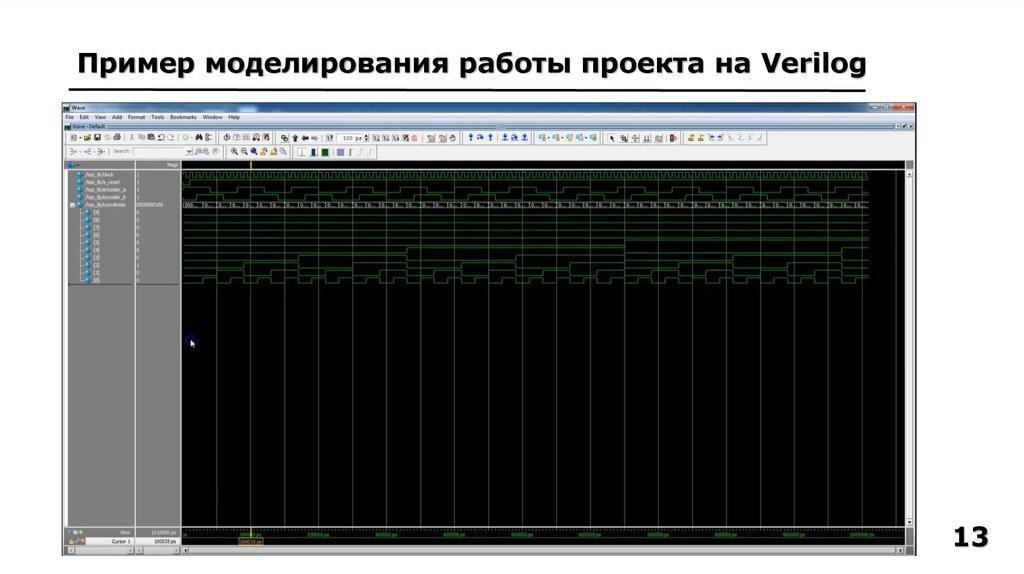

13.

Пример моделирования работы проекта на Verilog13

14.

Пример моделирования работы проекта на Verilog13

15.

Спасибо за внимание!Выполнил:

Студент гр. 368-М1

Лункин Дмитрий Сергеевич

electronics

electronics