Similar presentations:

Общие сведения о средствах проектирования цифровых схем. Возрастание объемов

1. Общие сведения о средствах проектирования цифровых схем. Возрастание объемов.

Согласно известному закону Мура (Мооге's Law), числотранзисторов на кристалле СБИС (сверхбольших

интегральных схем) удваивается каждые 18 месяцев (дця

процессорных схем).

Это правило, сформулированное в 1965 году, продолжает

работать до сих пор, несмотря на значительное увеличение

микросхем. В некоторых СБИС - программируемых

логических интегральных схемах (ПЛИС - FРGА), вполне

доступных и отечественным разработчикам, содержатся

миллионы вентилей.

2. Общие сведения о средствах проектирования цифровых схем (2). Возрастание объемов и сложности

Возрастание сложности СБИС позволяет иметь ваппаратуре все большее число компонентов, и, как

следствие, создавать все более сложные схемы. Для

эффективного использования этих возможностей необходим

переход на новые технологии проектирования.

Типичная логическая схема в графическом представлении содержит на странице фрагмент, эквивалентный 200

вентилям. Таким образом, схема объемом 10 000 вентилей

будет представлена на 50 страницах. Легко представить

себе, во что выльется (по времени) составление и ввод в

графической нотации схем СБИС сложностью 50 тыс., 100

тыс., 500 тыс. вентилей и более.

3. Общие сведения о средствах проектирования цифровых схем (3). Применение языков описания схем

Альтернативой графического представления схемявляются языки описания аппаратуры. Их называют

языками HDL (Нагdwаге Descгiption Language). Они

обеспечивают компактную запись проектируемой схемы,

дают значительное сокращение трудоемкости и сроков

разработки схем, а также упрощают перенос проекта на

разные варианты технологий, реализацию их в СБИС с

учетом специфики технологий различных производителей.

Разработчик получает возможность оценить варианты

реализации проектируемого устройства в СБИС при

различных вариантах проектных ограничений, на

различных технологиях, у различных производителей.

4. Общие сведения о средствах проектирования цифровых схем (4).

Проблема не ограничивается только количественнымихарактеристиками

описания

проектируемых

схем.

Описание работы схем разных уровней (структyрные,

функциональные,

принципиальные),

дается

с

использованием привычных, но не стандартизированных и

не всегда однозначных в понимании дополнительных

графических форм (временных диаграмм и др.).

Традиционные методы описания схем - таблицы

истинности, конечные автоматы, сети Петри и другие оказываются пригодными лишь для очень небольших, по

современным меркам, фрагментов аппаратуры.

5. Общие сведения о средствах проектирования цифровых схем (5). Применение aлгopитмического подхода

Возрастающая алгоритмическая сложность аппаратнореализованных устройств приводит к тому, что, как

проблемы разработки, описания и применения аппаратуры

(hаrdwаrе), так и подходы к их решению, становятся подобны

проблемам и методам решения для современных

программных систем (sоftwаrе).

Перспективное направление решения этих проблем применение

aлгopитмического

подхода,

создание

алгоритмического языка для описания аппаратуpы и

функционирования

аппаратных

средств

обработки

информации.

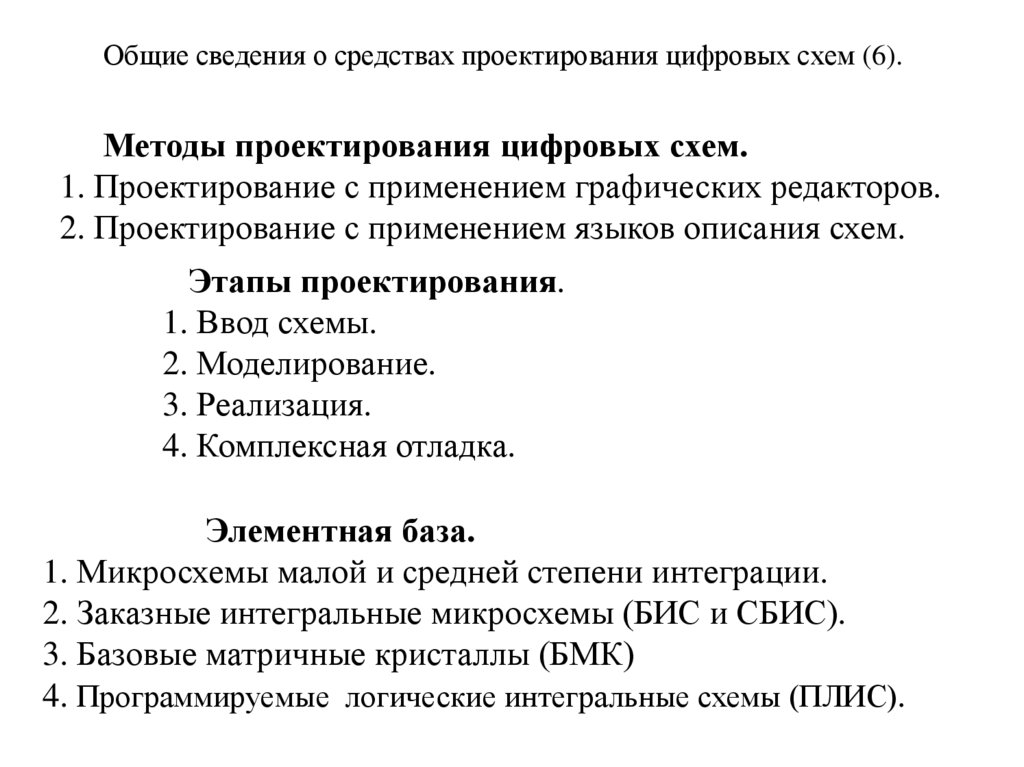

6. Общие сведения о средствах проектирования цифровых схем (6).

Методы проектирования цифровых схем.1. Проектирование с применением графических редакторов.

2. Проектирование с применением языков описания схем.

Этапы проектирования.

1. Ввод схемы.

2. Моделирование.

3. Реализация.

4. Комплексная отладка.

Элементная база.

1. Микросхемы малой и средней степени интеграции.

2. Заказные интегральные микросхемы (БИС и СБИС).

3. Базовые матричные кристаллы (БМК)

4. Программируемые логические интегральные схемы (ПЛИС).

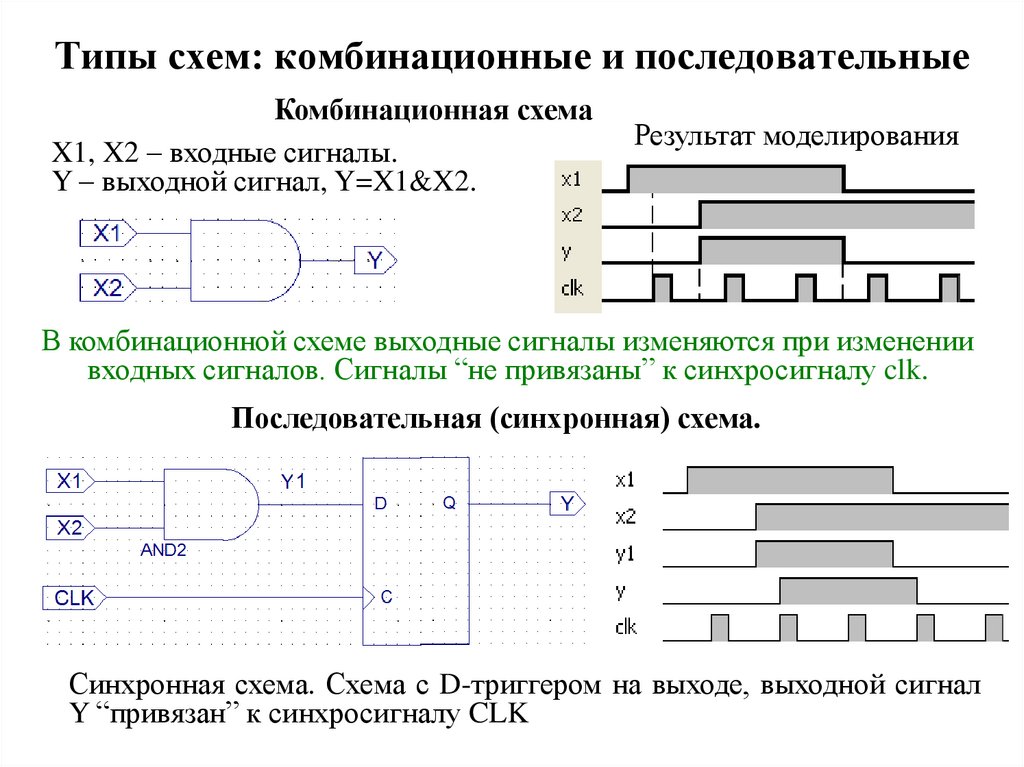

7. Типы схем: комбинационные и последовательные

Комбинационная схемаX1, X2 – входные сигналы.

Y – выходной сигнал, Y=X1&X2.

Результат моделирования

В комбинационной схеме выходные сигналы изменяются при изменении

входных сигналов. Сигналы “не привязаны” к синхросигналу clk.

Последовательная (синхронная) схема.

Синхронная схема. Схема с D-триггером на выходе, выходной сигнал

Y “привязан” к синхросигналу CLK

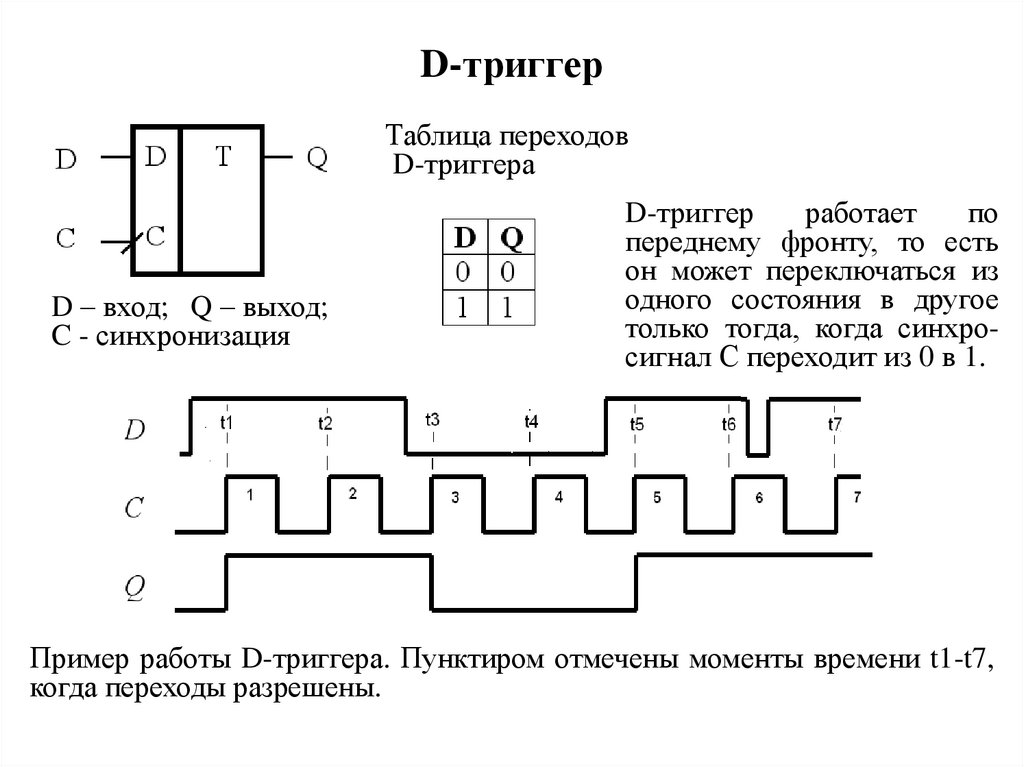

8. D-триггер

Таблица переходовD-триггера

D – вход; Q – выход;

C - синхронизация

D-триггер

работает

по

переднему фронту, то есть

он может переключаться из

одного состояния в другое

только тогда, когда синхросигнал С переходит из 0 в 1.

Пример работы D-триггера. Пунктиром отмечены моменты времени t1-t7,

когда переходы разрешены.

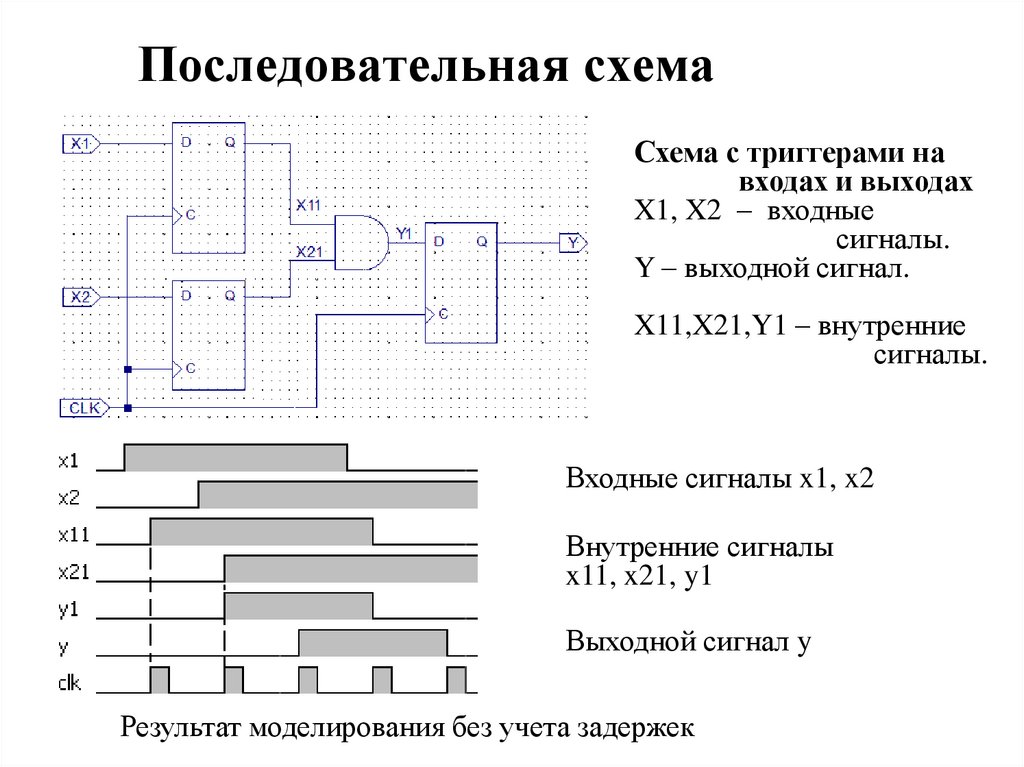

9. Последовательная схема

Схема с триггерами навходах и выходах

X1, X2 – входные

сигналы.

Y – выходной сигнал.

X11,X21,Y1 – внутренние

сигналы.

Входные сигналы x1, x2

Внутренние сигналы

x11, x21, y1

Выходной сигнал y

Результат моделирования без учета задержек

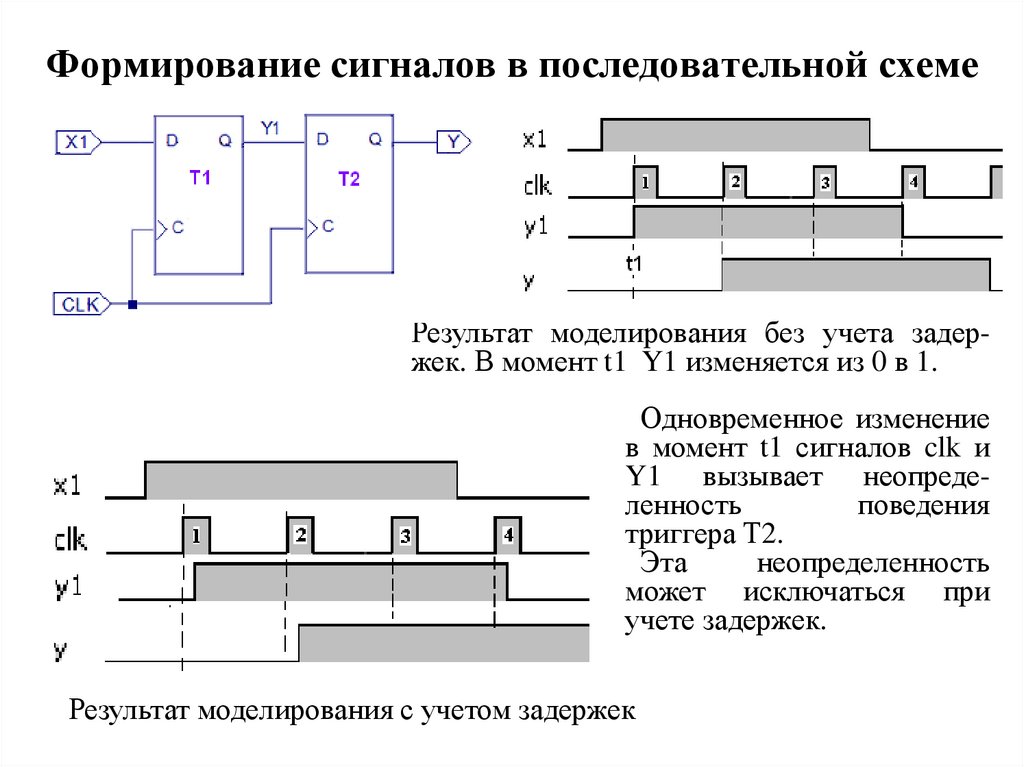

10. Формирование сигналов в последовательной схеме

Результат моделирования без учета задержек. В момент t1 Y1 изменяется из 0 в 1.Одновременное изменение

в момент t1 сигналов clk и

Y1 вызывает неопределенность

поведения

триггера Т2.

Эта

неопределенность

может исключаться при

учете задержек.

Результат моделирования с учетом задержек

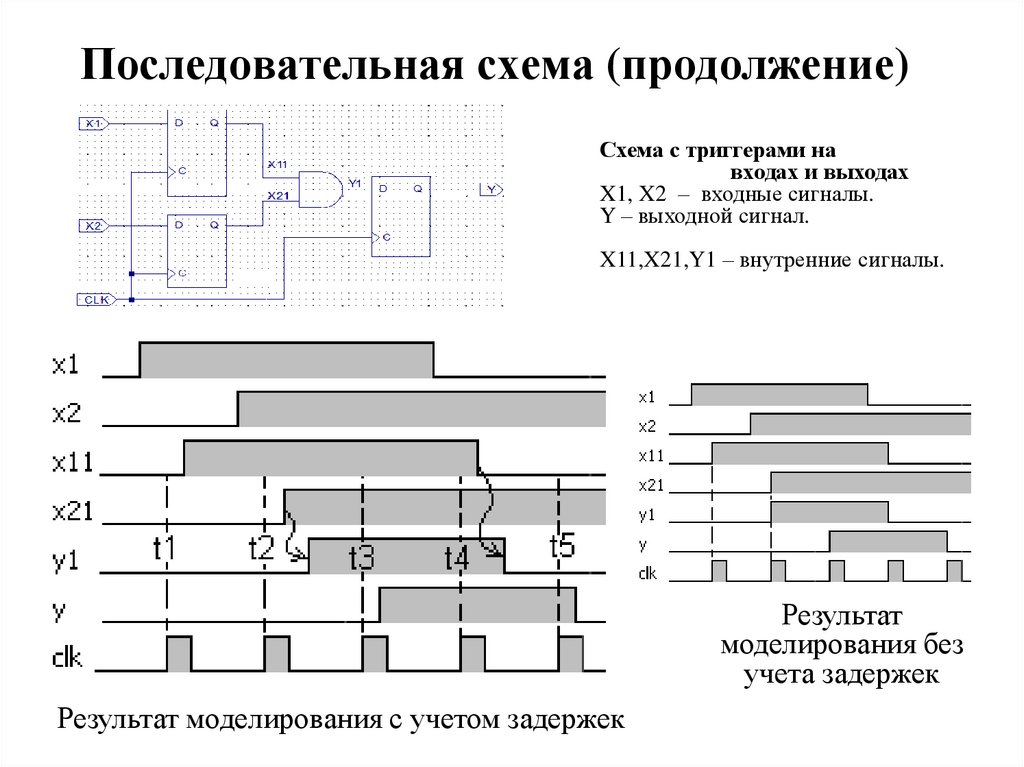

11. Последовательная схема (продолжение)

Схема с триггерами навходах и выходах

X1, X2 – входные сигналы.

Y – выходной сигнал.

X11,X21,Y1 – внутренние сигналы.

Результат

моделирования без

учета задержек

Результат моделирования с учетом задержек

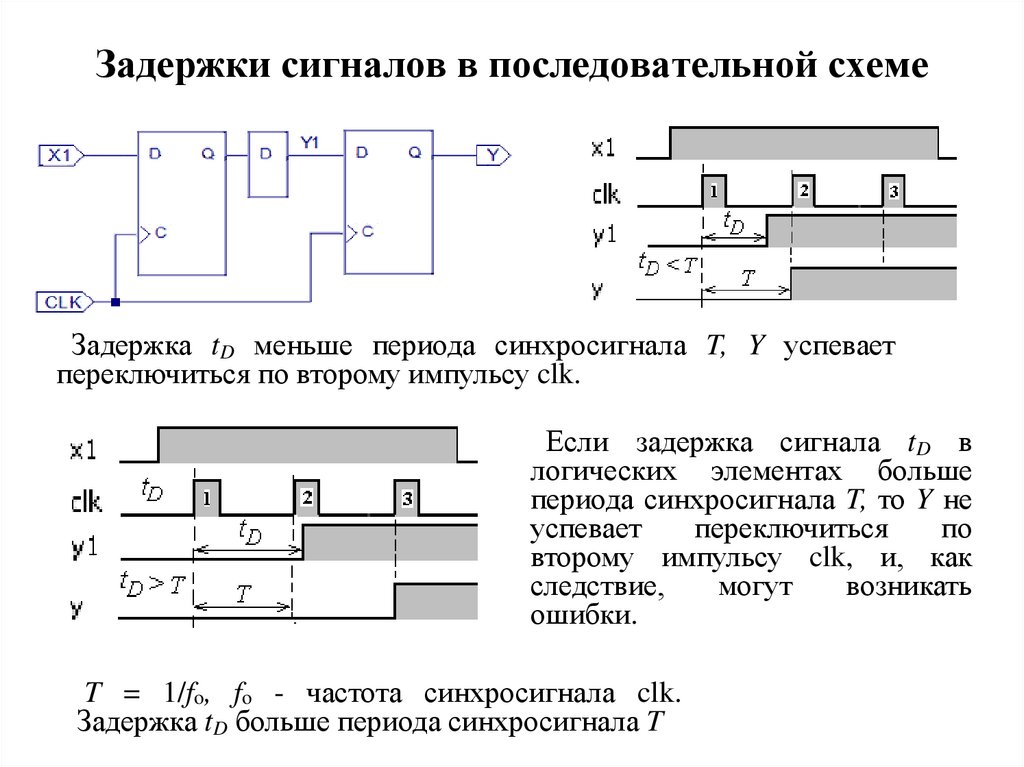

12. Задержки сигналов в последовательной схеме

Задержка tD меньше периода синхросигнала T, Y успеваетпереключиться по второму импульсу clk.

Если задержка сигнала tD в

логических элементах больше

периода синхросигнала T, то Y не

успевает

переключиться

по

второму импульсу clk, и, как

следствие,

могут

возникать

ошибки.

T = 1/fo, fo - частота синхросигнала clk.

Задержка tD больше периода синхросигнала T

13. Проектирование цифровых схем с применением языков описания схем.

Языки описания схем (Hardware Description Language)используются:

- при проектировании устройств на программируемых

логических интегральных схемах (ПЛИС), базовых

матричных кристаллов (БМК), заказных интегральных

микросхем,

- для моделирования цифровых схем.

Наиболее распространенные языки описания схем:

VHDL,

Verilog.

14. Преимущества использования языков HDL

1. Проектировщики могут выполнить описание на уровнеRTL, не выбирая определенную технологию изготовления.

Проекты могут быть выполнены на абстрактном уровне при

помощи HDL. Логические инструментальные средства синтеза

могут автоматически преобразовать проект в любую технологию

изготовления. Если появляется новая технология, то

специалисты не должны перепроектировать всю схему целиком.

·

· 2. Функциональная проверка проекта может быть сделана

непосредственно в цикле проекта, на ранней стадии.

Большинство ошибок в проектах устраняется именно на этом

этапе. Это значительно сокращает время проектирования,

потому что при устранении ошибок нет необходимости

многократно выполнять достаточно большой объем работ по

размещению проекта на кристалле на уровне вентилей.·

15. Преимущества использования языков HDL (продолжение)

3. Текстовое описание с комментариями — это болеепростой

способ

разработки

и

отладки

схемы.

Проектирование на языке HDL очень похоже на

программирование. Текстовое описание выглядит более

компактным, по сравнению со схемными решениями,

представленными на уровне примитивов — триггеров и

вентилей. Даже для проектов средней сложности, схемы,

выполненные на уровне триггеров и вентилей, довольно

трудны в сопровождении и дальнейшей модернизации.

·

16. Способы настройки цифровых схем

Этапы проектирования.1. Разработка и ввод схемы.

2. Моделирование.

3. Реализация.

4. Комплексная отладка

Основные способы настройки.

1. Моделирование.

2. Комплексная отладка.

U1 - настраиваемая схема

G - генератор тестовых сигналов

R - регистратор (дисплей)

x1…xn - тестовые сигналы

y1…ym - выходы U1

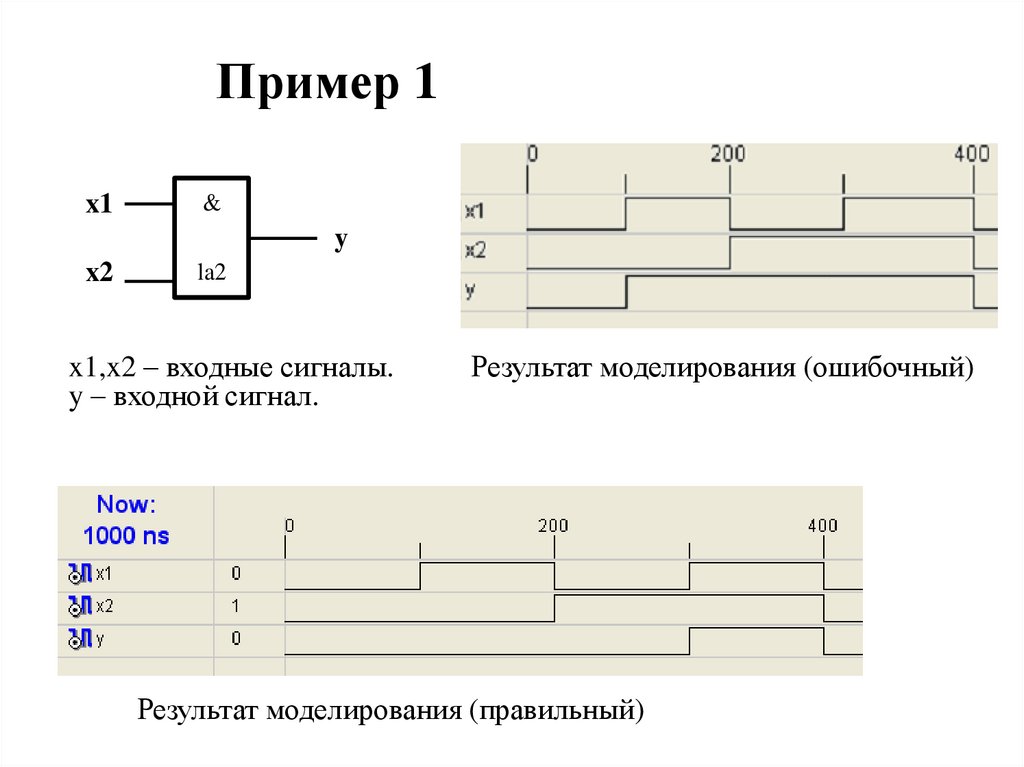

17. Пример 1

x1&

y

x2

la2

x1,x2 – входные сигналы.

y – входной сигнал.

Результат моделирования (ошибочный)

Результат моделирования (правильный)

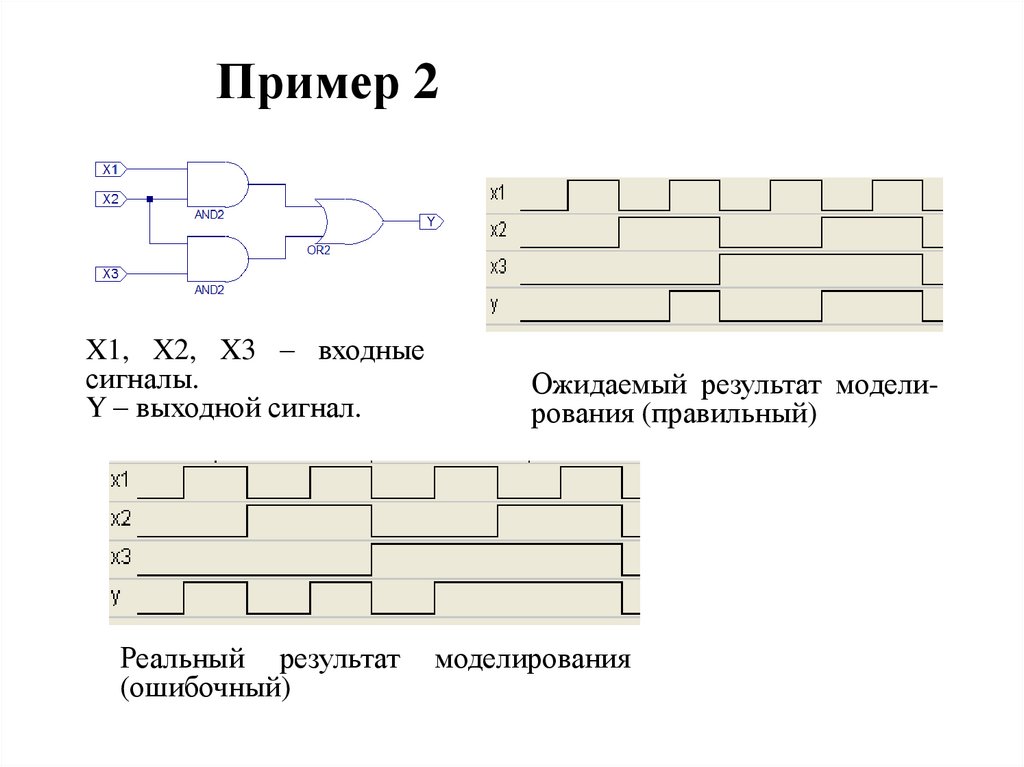

18. Пример 2

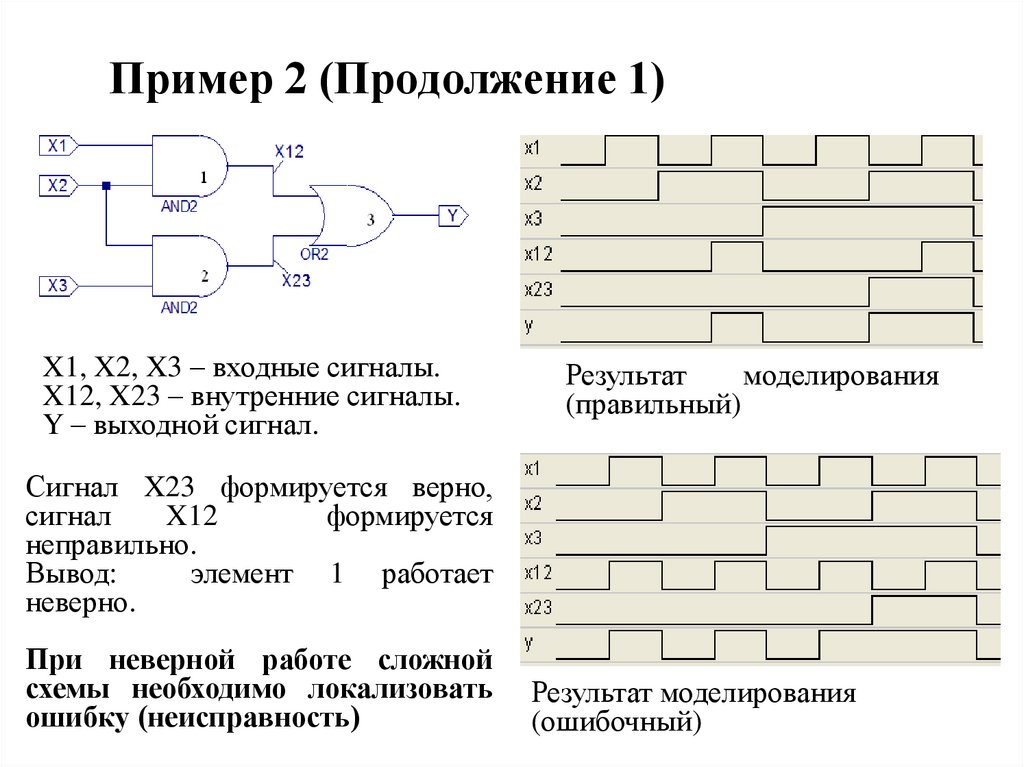

X1, X2, X3 – входныесигналы.

Y – выходной сигнал.

Реальный результат

(ошибочный)

Ожидаемый результат моделирования (правильный)

моделирования

19. Пример 2 (Продолжение 1)

X1, X2, X3 – входные сигналы.X12, X23 – внутренние сигналы.

Y – выходной сигнал.

Результат

моделирования

(правильный)

Сигнал X23 формируется верно,

сигнал

X12

формируется

неправильно.

Вывод:

элемент 1 работает

неверно.

При неверной работе сложной

схемы необходимо локализовать

ошибку (неисправность)

Результат моделирования

(ошибочный)

electronics

electronics