Similar presentations:

Генератор, задающий 16-битную последовательность

1. Дипломная работа

Национальный исследовательский Институт «МосковскийЭнергетический Институт»

ДИПЛОМНАЯ РАБОТА

ТЕМА: «ГЕНЕРАТОР, ЗАДАЮЩИЙ 16-БИТНУЮ ПОСЛЕДОВАТЕЛЬНОСТЬ

Студент гр.Э-05-12 Сипарова Анна Павловна

Научный руководитель: ст.пр. Ануфриев Ю.В.

2016 год

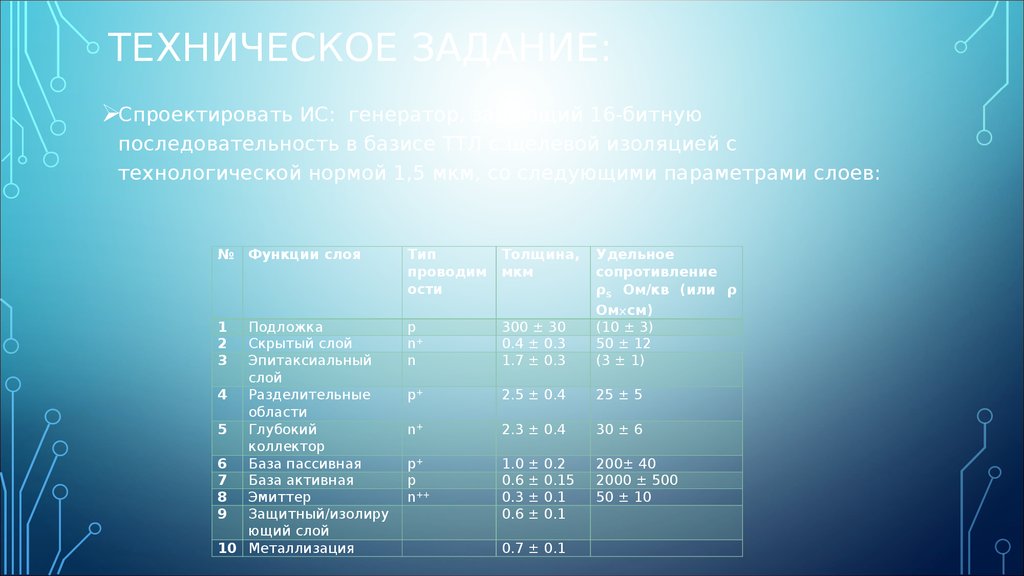

2. Техническое задание:

ТЕХНИЧЕСКОЕ ЗАДАНИЕ:Спроектировать ИС: генератор, задающий 16-битную

последовательность в базисе ТТЛ с щелевой изоляцией с

технологической нормой 1,5 мкм, со следующими параметрами слоев:

№

1

2

3

Функции слоя

Подложка

Скрытый слой

Эпитаксиальный

слой

4

Разделительные

области

5

Глубокий

коллектор

6

База пассивная

7

База активная

8

Эмиттер

9

Защитный/изолиру

ющий слой

10 Металлизация

Тип

проводим

ости

Толщина,

мкм

p

n+

n

300 ± 30

0.4 ± 0.3

1.7 ± 0.3

Удельное

сопротивление

ρS Ом/кв (или ρ

Ом см)

(10 ± 3)

50 ± 12

(3 ± 1)

p+

2.5 ± 0.4

25 ± 5

n+

2.3 ± 0.4

30 ± 6

p+

p

n++

1.0

0.6

0.3

0.6

200± 40

2000 ± 500

50 ± 10

0.7 ± 0.1

±

±

±

±

0.2

0.15

0.1

0.1

3. Краткое содержание:

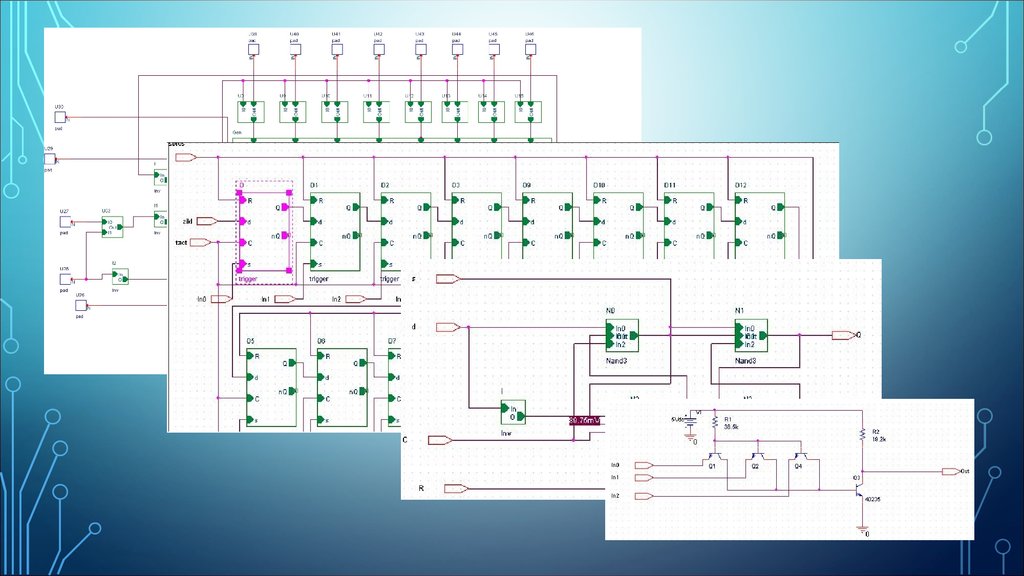

КРАТКОЕ СОДЕРЖАНИЕ:Разработка логической структуры

Технологическое проектирование

Физико-топологическое проектирование

Проектирование электрической схемы и топологии

базовой ячейки

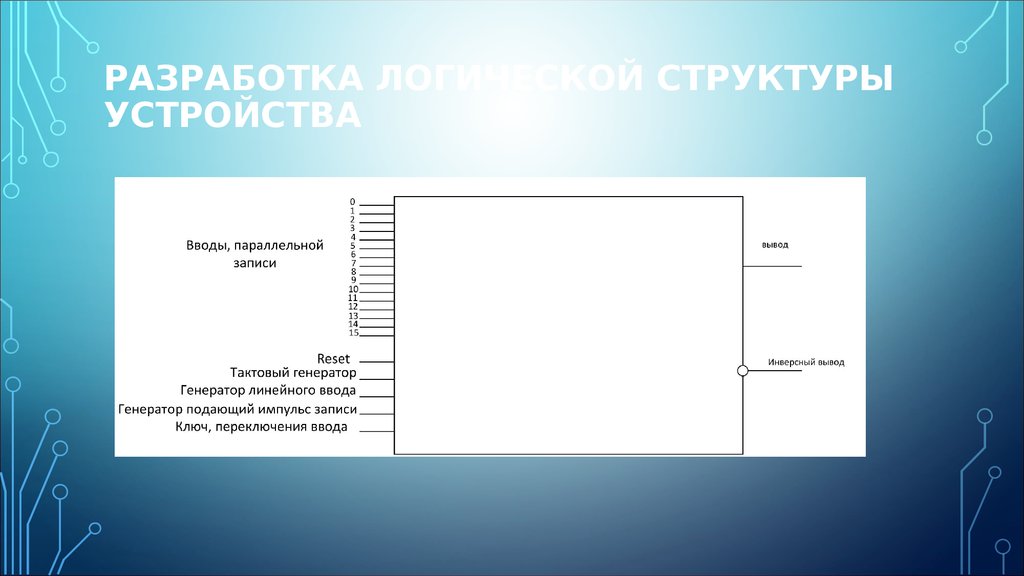

4. Разработка логической структуры устройства

РАЗРАБОТКА ЛОГИЧЕСКОЙ СТРУКТУРЫУСТРОЙСТВА

5.

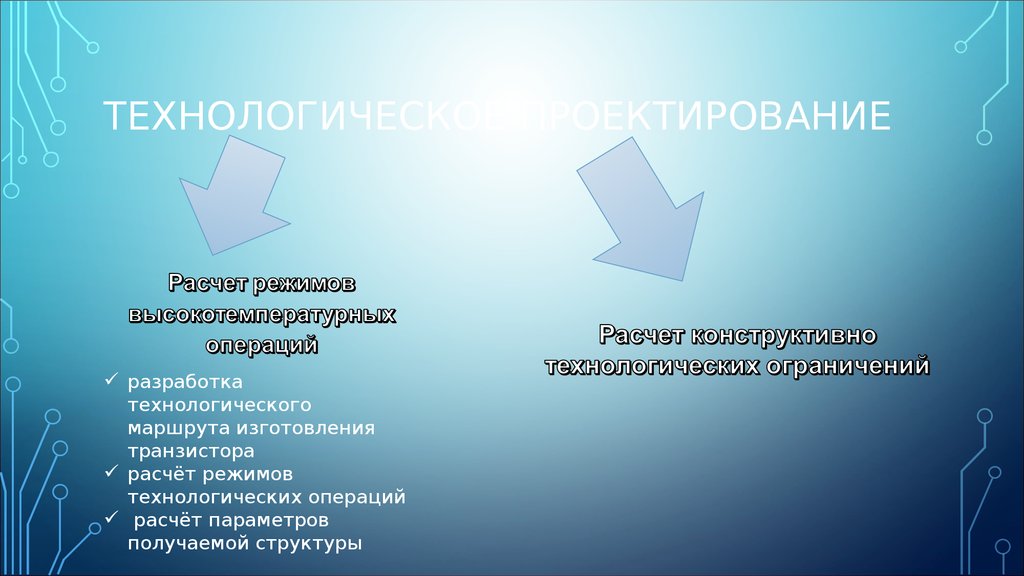

6. Технологическое проектирование

ТЕХНОЛОГИЧЕСКОЕ ПРОЕКТИРОВАНИЕразработка

технологического

маршрута изготовления

транзистора

расчёт режимов

технологических операций

расчёт параметров

получаемой структуры

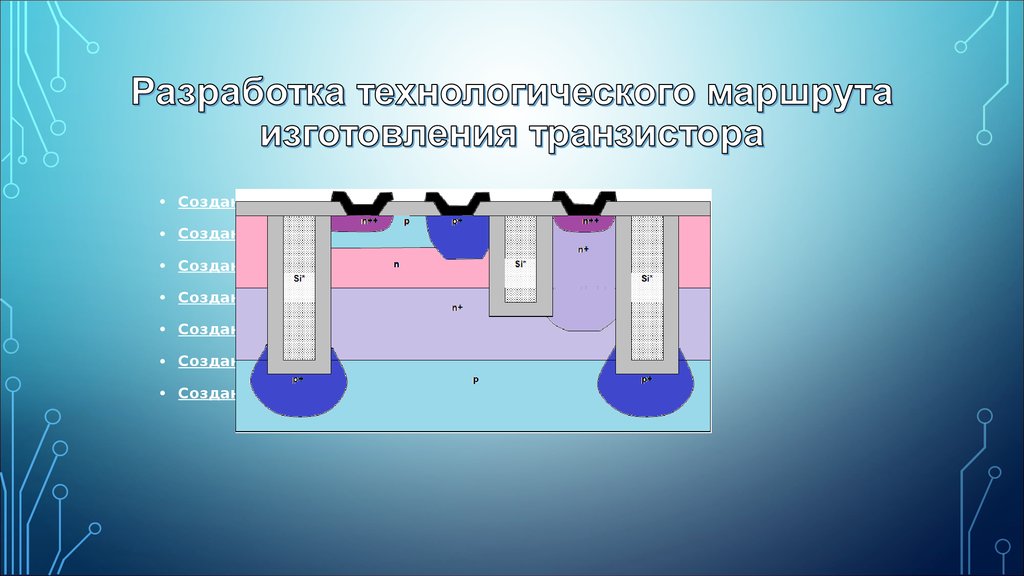

7. Разработка технологического маршрута изготовления транзистора

Создание скрытого коллекторного слоя

Создание изолирующих областей

Создание глубокого коллектора

Создание пассивной базы

Создание активной базы

Создание эмиттера

Создание металлизации

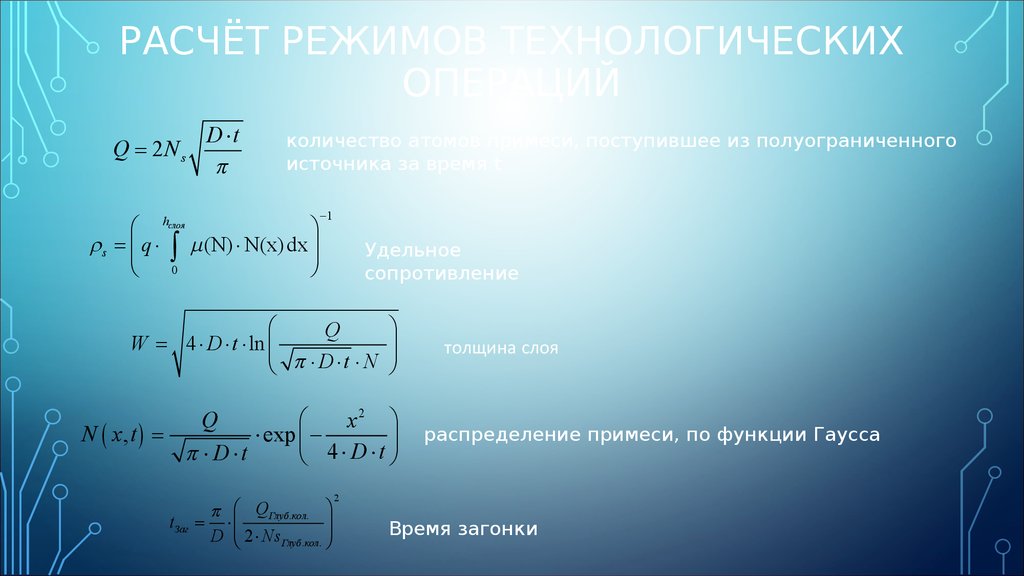

8. расчёт режимов технологических операций

РАСЧЁТ РЕЖИМОВ ТЕХНОЛОГИЧЕСКИХОПЕРАЦИЙ

Q = 2Ns

D ×t

p

количество атомов примеси, поступившее из полуограниченного

источника за время t

æ hслоя

ö

r s = ç q × ò m (N) × N(x) dx ÷

ç

÷

0

è

ø

-1

Удельное

сопротивление

æ

Q

W = 4 × D × t × ln çç

è p × D ×t × N

ö

÷÷

ø

æ

Q

x2 ö

N ( x, t ) =

× exp ç ÷

4

×

D

×

t

p × D×t

è

ø

tЗаг

p æ QГлуб .кол. ö

= ×ç

÷

D çè 2 × Ns Глуб .кол. ÷ø

распределение примеси, по функции Гаусса

2

Время загонки

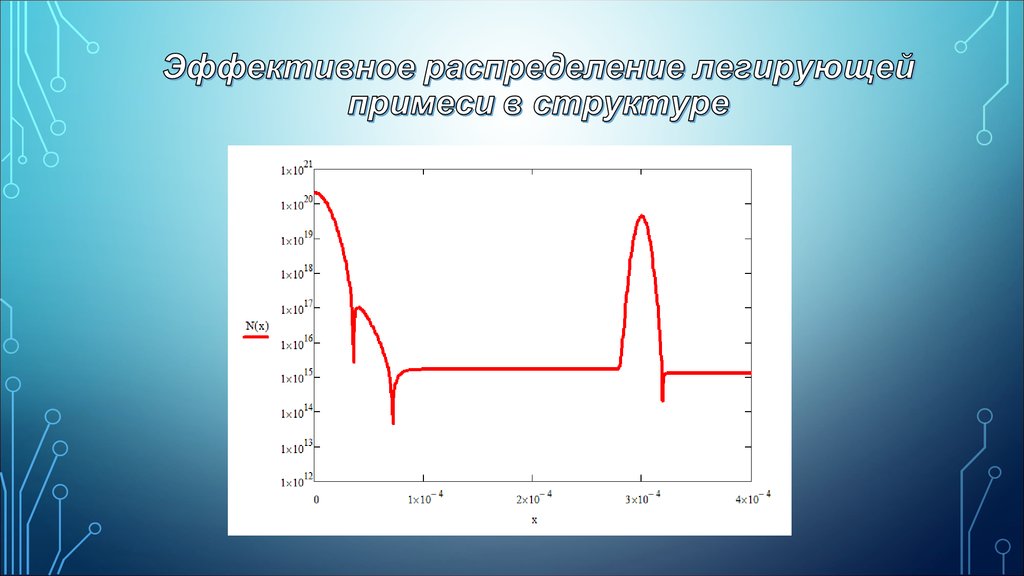

9. Эффективное распределение легирующей примеси в структуре

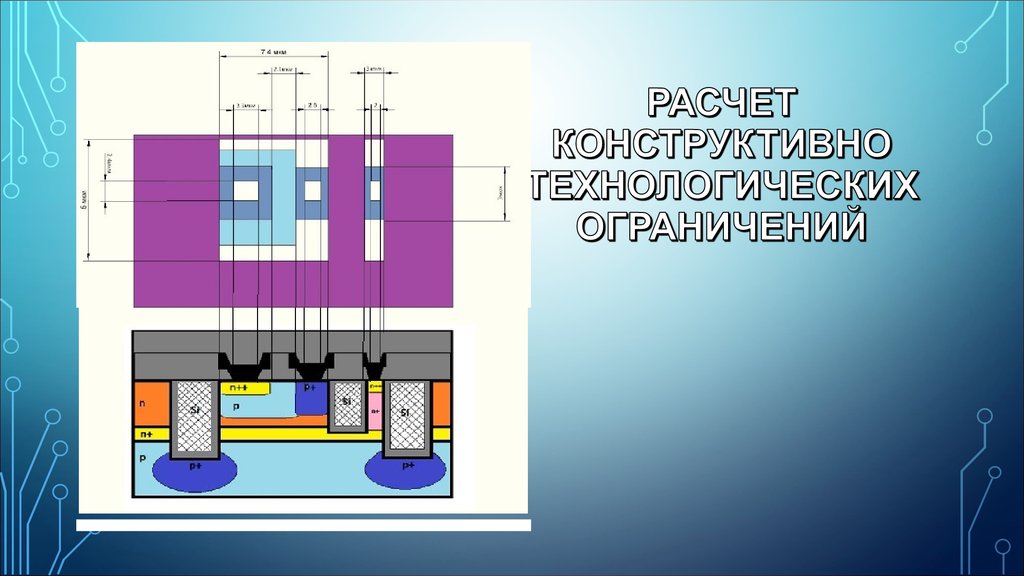

10. Расчет конструктивно технологических ограничений

рис. 1 структура и размеры транзистора11. Физико-топологическое проектирование

ФИЗИКО-ТОПОЛОГИЧЕСКОЕПРОЕКТИРОВАНИЕ

Моделирование с пакете ISE T-Cad

Теоретический расчет

Экстрагирование

н ие

е

н

в

а

ср

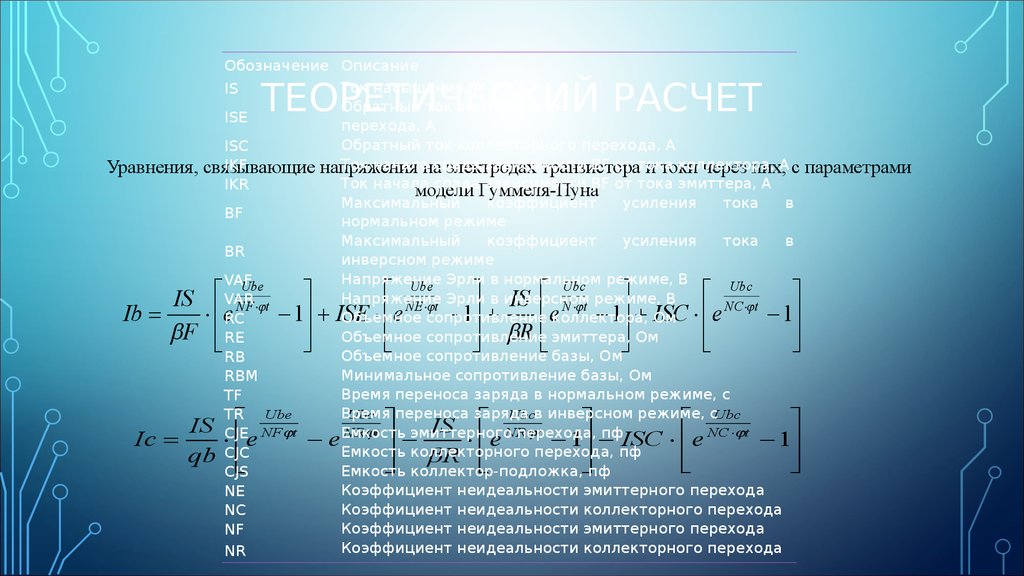

12. Теоретический расчет

Обозначение ОписаниеТок насыщения, А

IS

Обратный ток эмиттерного

ISE

перехода, А

Обратный ток коллекторного перехода, А

ISC

Ток началана

спада

зависимости

BF от тока

коллектора,

IKF

Уравнения, связывающие

напряжения

электродах

транзистора

и токи

через них,А с параметрами

Ток начала спада зависимости BF от тока эмиттера, А

IKR

модели Гуммеля-Пуна

Максимальный

коэффициент

усиления

тока

в

BF

нормальном режиме

Максимальный

коэффициент

усиления

тока

в

BR

инверсном режиме

Напряжение

VAF

Ube

Ube Эрли в нормальном

Ubc режиме, В

Ubc

Напряжение

Эрли

в

инверсном

режиме,

В

IS VAR

IS

NF × t

NE × t

N × t

NC × t

Ib =

× eRC - 1 ISE

× e сопротивление

- 1

- 1 Ом

ISC × e

- 1

Объемное

eколлектора,

F RE

R эмиттера, Ом

Объемное

сопротивление

Объемное сопротивление базы, Ом

RB

Минимальное сопротивление базы, Ом

RBM

Время переноса заряда в нормальном режиме, с

TF

Время

переноса заряда

Ubc

Ubcв инверсном режиме, сUbc

TR Ube

NF t

пф

NC × t

IS CJE

IS

NR t

t

Емкость

эмиттерногоNR

перехода,

Ic =

× e

-e

× e

- 1 - ISC × e

- 1

-коллекторного

Емкость

перехода,

пф

CJC

qb

R

коллектор-подложка,

пф

Емкость

CJS

Коэффициент неидеальности эмиттерного перехода

NE

Коэффициент неидеальности коллекторного перехода

NC

Коэффициент неидеальности эмиттерного перехода

NF

Коэффициент неидеальности коллекторного перехода

NR

ТЕОРЕТИЧЕСКИЙ РАСЧЕТ

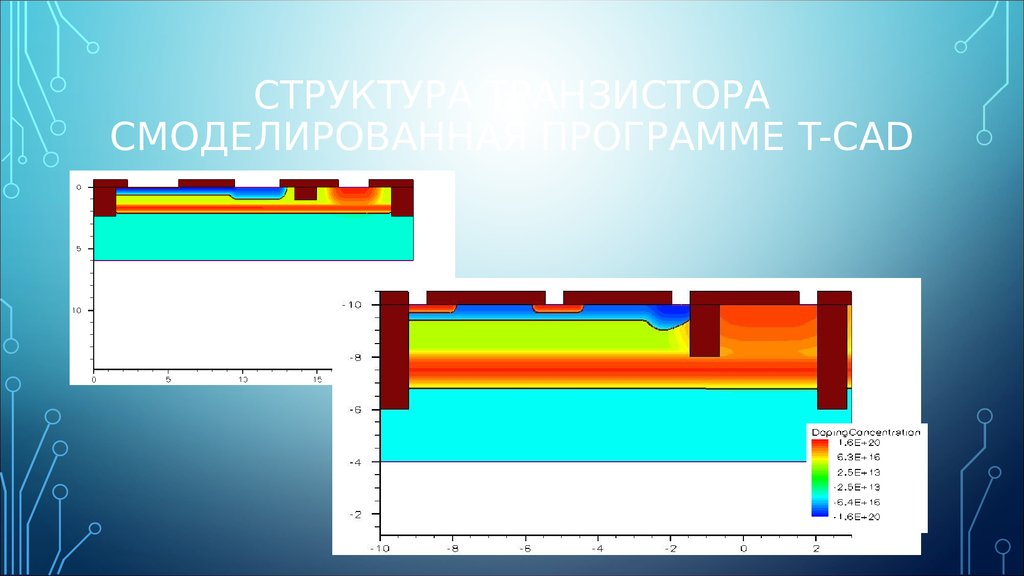

13. Структура транзистора смоделированная программе T-CAD

СТРУКТУРА ТРАНЗИСТОРАСМОДЕЛИРОВАННАЯ ПРОГРАММЕ T-CAD

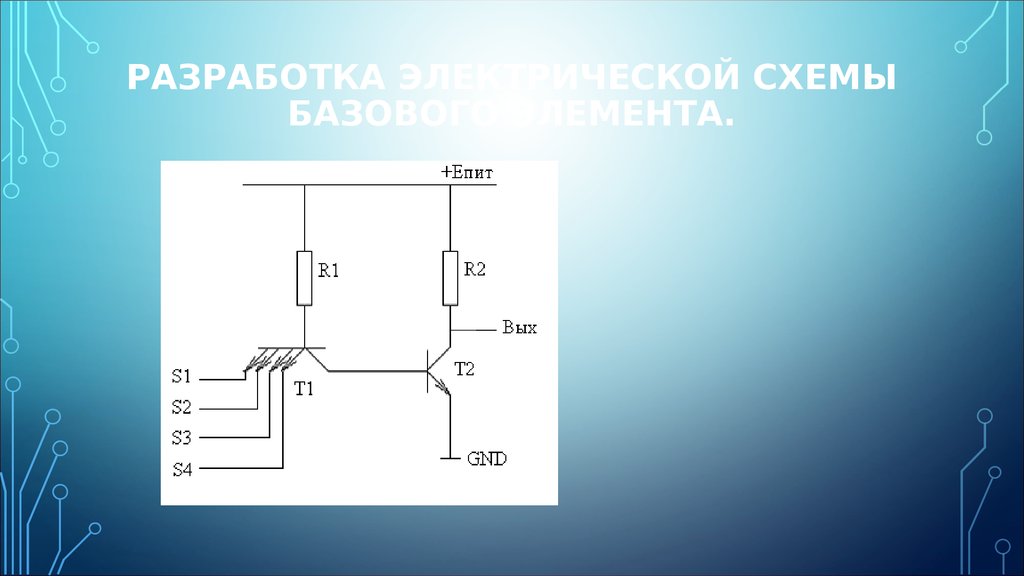

14. Разработка электрической схемы базового элемента.

РАЗРАБОТКА ЭЛЕКТРИЧЕСКОЙ СХЕМЫБАЗОВОГО ЭЛЕМЕНТА.

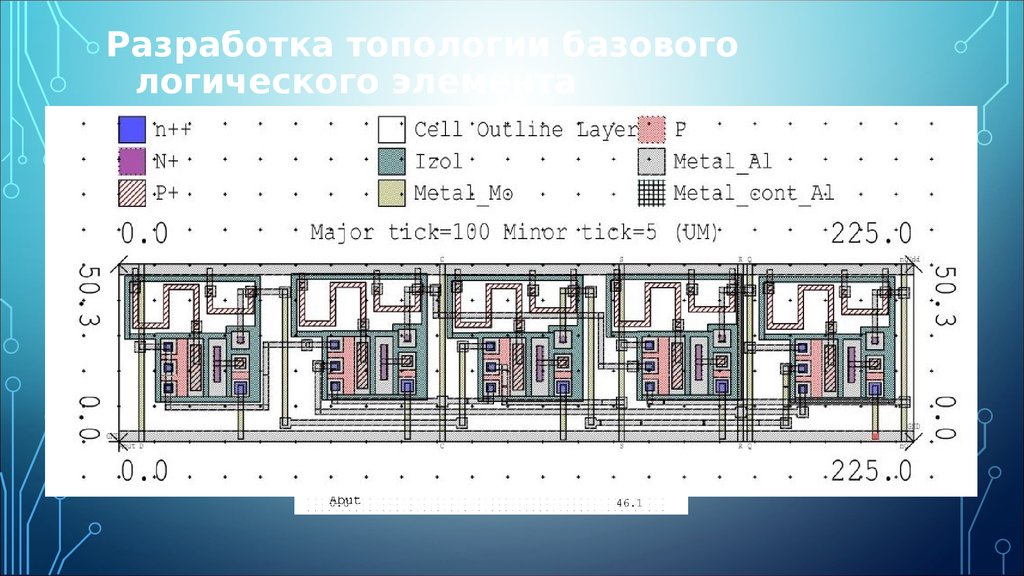

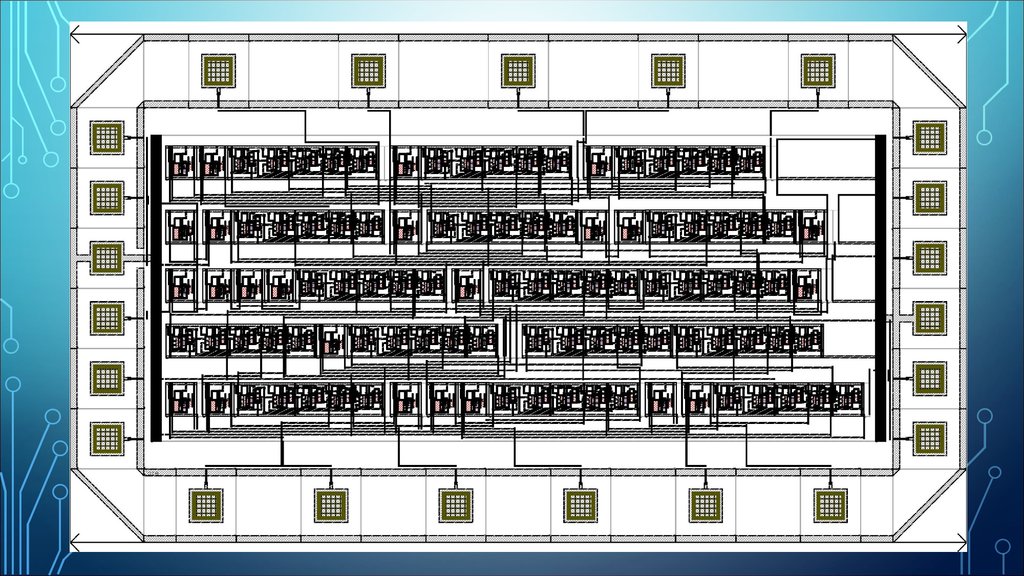

15. Разработка топологии базового логического элемента

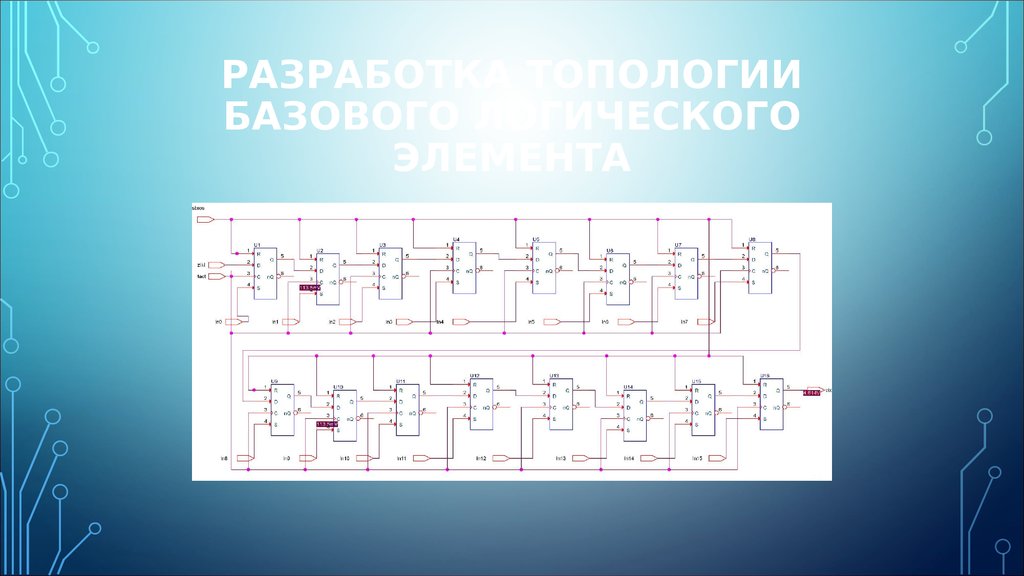

16. Разработка топологии базового логического элемента

РАЗРАБОТКА ТОПОЛОГИИБАЗОВОГО ЛОГИЧЕСКОГО

ЭЛЕМЕНТА

17.

18. Спасибо за внимание !!!

СПАСИБО ЗА ВНИМАНИЕ !!!27.06.2016, Москва

electronics

electronics