Similar presentations:

Электроника и информационно-измерительная техника. Двоичный и шестнадцатеричный коды. (Тема 18)

1.

Электроника и информационно-измерительная техника2.

Тема 18Двоичный и шестнадцатеричный коды

3.

Логические уровни при напряжении питания 5 ВU, В

5

Логическая единица

2,4

Неопределённость

0,8

0

Логический ноль

t

4.

Соотношение между десятичным кодом и двоичным кодомN DEC

n 1

Zi 2

i

i 0

Z i {0;1}

n – разрядность двоичного кода

i – номер разряда двоичного кода

5.

Пример двоичного кода7 6

5

4 3

2 1

2 2 2 2 2 2 2 2

0

0 0 1 0 0 1 1 1

Старший бит

Младший бит

N DEC 1 2 0 1 21 1 2 2 0 23 0 2 4 1 25 0 2 6 0 2 7

1 2 4 32 39

1 байт = 8 бит

1К байт =210 бит = 1024 бит

1M байт =220 бит = 1048576 бит

1Г байт =230 бит = 1073741824 бит

1Т байт =240 бит = 1099511627760 бит

6.

Перевод десятичного числа 39 в двоичный код111001

39

2

19,5

19

2

9,5

9

2

4,5

4

2

2,0

2

2

1,0

1

2

0,5

Ответ: 100111

7.

Шестнадцатеричный кодDEC 0 1 2 3 4 5 6

HEX 0 1 2 3 4 5 6

7 8 9

7 8 9

10 11 12 13 14 15

A B C D E F

Пример

BIN

10011101011100101100

DEC

9

13

7

2

12

HEX

9

D

7

2

C

Ответ: 0x9D72C

0х - признак записи в шестнадцатеричном коде

8.

Тема 19Простейшие арифметические операции с двоичными числами

9.

Правила арифметического сложения двоичных чисел0 BIN 0 BIN 0 BIN ;

0 BIN 1BIN 1BIN ;

1BIN 0 BIN 1BIN ;

1BIN 1BIN 10 BIN ;

1BIN 1BIN 1BIN 11BIN .

10.

Пример арифметического сложения двоичных чисел1 1 1 1 1

0 1 1 1 0

+0 1 1 1 1

1 0

1 1

1

0

1 1 1 1 0

0 1

1

11.

Правила арифметического вычитания двоичных чиселABIN BBIN ABIN BBIN .доп ABIN BBIN 1

где: BBIN .доп - число BBIN в дополнительном коде; BBIN проинвертированное число BBIN .

Если A B , то результат получается в прямом коде. При этом в старшем

разряде появляется единица (перенос), которую в результате учитывать

не нужно. Если A B , то результат получается в дополнительном коде.

Для перехода в прямой код его нужно проинвертировать, а затем

прибавить единицу.

12.

Пример вычитания №1:ABIN 1111 ; BBIN 0110 .

BBIN 1001.

BBIN .доп 1001 0001 1010 .

ABIN BBIN ABIN BBIN .доп 1111 1010 11001

Ответ: 1001BIN . (15-6=9).

13.

Пример вычитания №2:ABIN 0110 ; B BIN 1111 .

BBIN 0000 .

BBIN .доп 0000 0001 0001 .

ABIN B BIN ABIN BBIN .доп 0110 0001 0111 .

0111 1000 .

1000 0001 1001 .

Ответ: 0111BIN .доп 1001BIN . (6-15=-9).

14.

Тема 20Логические операции в цифровой электронике

15.

Логические операции в цифровой электроникеИнверсия

(логическое отрицание)

Конъюнкция

(логическое умножение)

Дизъюнкция

(логическое сложение)

16.

ИнверсияY X

Y {0;1} X {0;1}

Таблица истинности

X

0

1

Y

1

0

Логический элемент «НЕ» («NOT»)

X

1

Y

17.

ДизъюнкцияY X1 X 2

Таблица истинности

X1

0

0

1

1

X2

0

1

0

1

Y

0

1

1

1

Логический элемент «ИЛИ» («OR»)

X1

1

Y

X2

Анимация

18.

КонъюнкцияY X1 X 2

Таблица истинности

X1

0

0

1

1

X2

0

1

0

1

Y

0

0

0

1

Логический элемент «И» («AND»)

X1

&

Y

X2

Анимация

19.

Дизъюнкция с инверсиейY X1 X 2

Таблица истинности

X1

0

0

1

1

X2

0

1

0

1

Y

1

0

0

0

Логический элемент «ИЛИ-НЕ»

X1

1

Y

X2

Анимация

20.

Конъюнкция с инверсиейY X1 X 2

Таблица истинности

X1

0

0

1

1

X2

0

1

0

1

Y

1

1

1

0

Логический элемент «И-НЕ»

X1

&

Y

X2

Анимация

21.

Микросхема КP1533ЛА3 (IN74HC00)22.

Тема 21Цифровые триггеры и двоичные счётчики

23.

Цифровые триггерыRS-триггер

Т-триггер

D-триггер

24.

RS - триггерR

S

&

&

Q

Режим хранения

Таблица истинности

R

1

1

1

0

1

0

S

1

0

1

1

1

0

Qn

0

1

1

0

0

?

Qn 1

0

0

1

1

0

?

Режим установки

Режим сброса

Режим неопределённости

25.

D - триггерD T

C

Q

Q

D

t

C

t

Q

t

26.

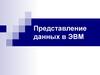

T - триггерD T

Q

Q

T

T

Q

C

T

t

Q

t

27.

Четырёхразрядный двоичный счётчикCT

Счётный вход

С

Q3

Старший бит выхода

Q2

Q1

Вход сброса

R

Q0

Младший бит выхода

Таблица истинности четырехразрядного двоичного счетчика

N имп 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0

Q0

0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0

Q1

0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0

Q2

0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0

Q3

28.

Тема 22Цифровые регистры и мультиплексоры

29.

Четырёхразрядный регистрВходы данных

D3 RG Q 3

D2

D1

D0

C

Вход записи

Q2

Q1

Q0

Выходы

30.

Двухразрядный мультиплексорВходы данных

1

D3

D2

D1

D0

А1

А0

Входы адреса

Выход

M U X

Q

31.

Тема 23Цифро-аналоговые преобразователи (ЦАП)

32.

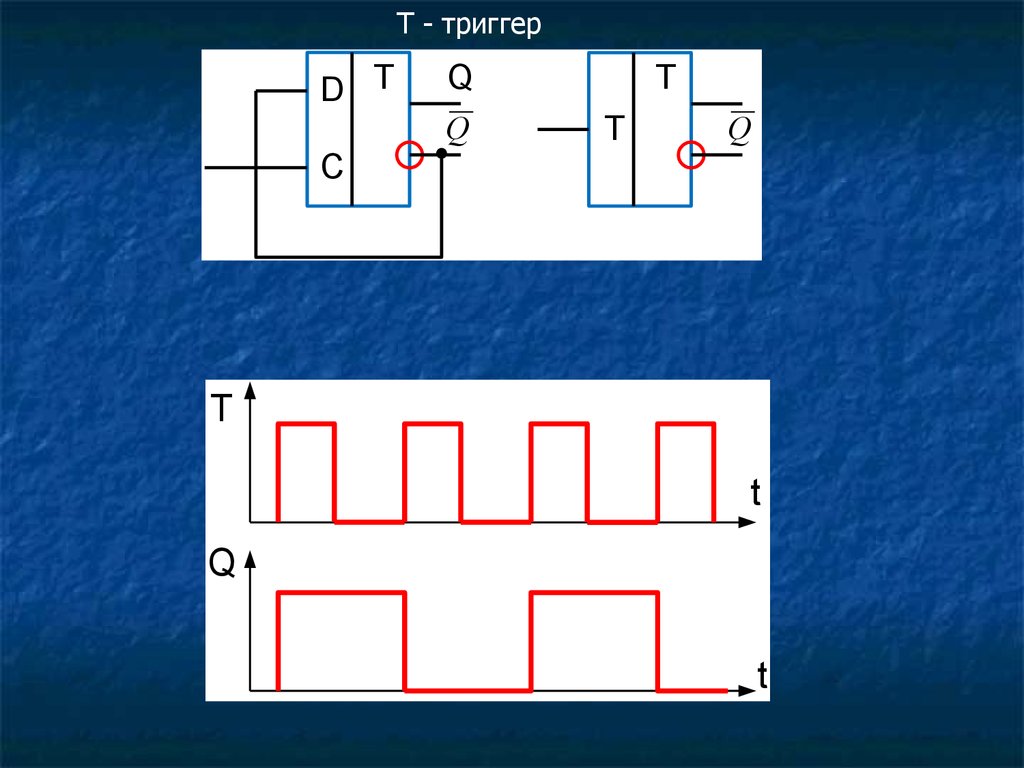

Четырёхразрядный цифро-аналоговый преобразователь (ЦАП)D3 DAC

D2

U вых

D1

D0

Цифровые

входы

Аналоговый

выход

U оп

Опорное напряжение

U вых

U оп N вх

2n 1

n 1

где:

N вх Di 2 i

i 0

Di {0;1}

33.

Передаточная характеристика четырёхразрядного ЦАПU вых

U оп

U

N вх

1 2 3

15

34.

Тема 24Аналого-цифровые преобразователи (АЦП)

35.

Четырёхразрядный аналого-цифровой преобразователь (АЦП)Входное

напряжение

Опорное

напряжение

Q3

Q2

Q1

Q0

ADC

U вх

U оп

N вых

Цифровые

выходы

U вх 2 n 1

U оп

n 1

N вых Qi 2

i 0

Qi {0;1}

i

36.

Передаточная характеристика четырёхразрядного АЦПN вых

15

U вх

1

U

U оп

37.

Тема 25Микропроцессоры

38.

Обобщённая структурная схема микропроцессораÒ àêòî âû å è ì ï ó ë üñû

Ø èí à

óï ðàâëåí è ÿ

Ðåãè ñòð

êî ì àí ä

Ä åø è ô ðàòî ð

êî ì àí ä

Áëî ê

óï ðàâëåí èÿ

Ñ ÷åò÷è ê

êî ì àí ä

Ô î ðì è ðî âàòåë ü

àä ðåñî â

Ðåãè ñòðû

î á ù åãî

í àçí à÷ åí è ÿ

Ðåãè ñòðàê êó ì ó ë ÿòî ð

Ø èí à

äàí í û õ

Ø èí à

àäðåñî â

À Ë Ó

39.

Тема 26Микропроцессорная система

40.

Обобщённая структурная схема микропроцессорной системыот ВУ

ГТИ

Память

ОЗУ

ПЗУ

к ВУ

Порты

Порты

ввода

вывода

Порты ввода-вывода

Шина

управления

МП

Шина

данных

Шина

адресов

41.

Структура памяти восьмиразрядной микропроцессорной системыАдрес

Данные

0000000000000000 01010011

0000000000000001 11110011

0000000000000010 00010000

1111111111111111 11010001

Ячейки

памяти

42.

Тема 27Память в микропроцессорных системах

informatics

informatics