Similar presentations:

Цифровые устройства и микропроцессоры. Лекция №4. Математическое описание последовательностных цифровых устройств

1.

ВОЕННАЯ АКАДЕМИЯ ВОЗДУШНО-КОСМИЧЕСКОЙ ОБОРОНЫИМЕНИ МАРШАЛА СОВЕТСКОГО СОЮЗА Г.К. ЖУКОВА

Кафедра № 13

основ построения радиоэлектронных средств и систем

Учебная дисциплина Д-1321

«ЦИФРОВЫЕ УСТРОЙСТВА И

МИКРОПРОЦЕССОРЫ»

Тверь 2018

2.

СТРУКТУРА УЧЕБНОЙ ДИСЦИПЛИНЫ ДС-1321Номера и наименование

разделов и тем

Всего

часов

Из них по видам занятий

Лекции Лаб.раб. Пр.зан.

Зачет

5 семестр

Введение

2

2

Тема 1. Основы схемотехники и элементная база

комбинационных цифровых электронных

устройств

14

6

4

4

Тема 2. Основы схемотехники и элементная база

последовательностных цифровых электронных

устройств

24

10

8

6

Тема 3. Аналого-цифровые и цифро-аналоговые 10

преобразователи

4

4

2

Тема 4. Запоминающие устройства ЭВМ и МПС

8

4

2

2

Тема 5. Микропроцессоры и микропроцессорные

системы

26

16

Заключение

2

2

Зачет с оценкой в конце 5-го семестра

4

Всего по дисциплине

90

10

4

44

18

24

4

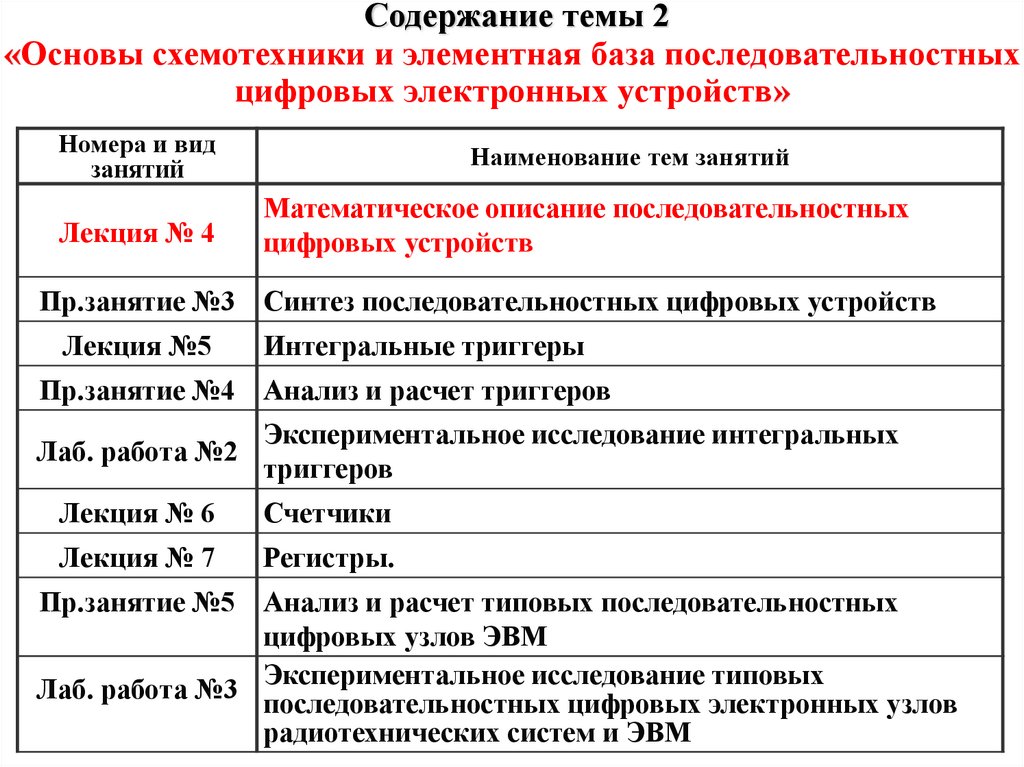

3.

Содержание темы 2«Основы схемотехники и элементная база последовательностных

цифровых электронных устройств»

Номера и вид

занятий

Лекция № 4

Наименование тем занятий

Математическое описание последовательностных

цифровых устройств

Пр.занятие №3 Синтез последовательностных цифровых устройств

Лекция №5

Интегральные триггеры

Пр.занятие №4 Анализ и расчет триггеров

Лаб. работа №2

Экспериментальное исследование интегральных

триггеров

Лекция № 6

Счетчики

Лекция № 7

Регистры.

Пр.занятие №5 Анализ и расчет типовых последовательностных

цифровых узлов ЭВМ

исследование типовых

Лаб. работа №3 Экспериментальное

последовательностных цифровых электронных узлов

радиотехнических систем и ЭВМ

4.

ЛЕКЦИЯ №4Математическое описание

последовательностных цифровых

устройств

5.

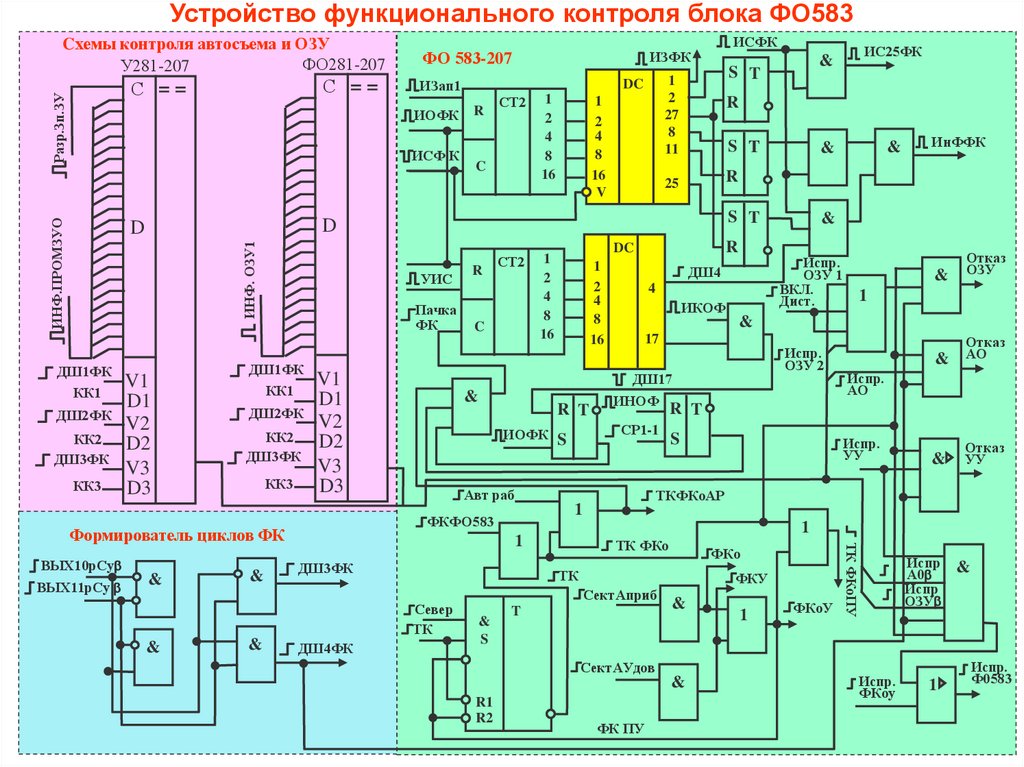

Устройство функционального контроля блока ФО583Cхемы контроля автосъема и ОЗУ

ФО281-207

У281-207

С ==

Разр.Зп.ЗУ

С ==

ФО 583-207

ИЗап1

ИОФК

ИНФ.ПРОМЗУО

ИСФ К

ИНФ. ОЗУ1

ДШ2ФК

КК2

ДШ3ФК

КК3

S T

V1

D1

V2

D2

V3

D3

Пачка

ФК

ДШ1ФК

КК1

ДШ2ФК

КК2

ДШ3ФК

КК3

V1

D1

V2

D2

V3

D3

&

&

&

C

1

2

4

8

16

ИОФК

4

ИКОФ

СР1-1

S

Испр.

ОЗУ 2

Отказ

& АО

Испр.

АО

R T

S

ТК ФКо

Испр.

УУ

ФКо

ТК

ФКУ

СектАприб

T

&

СектАУдов

&

R1

R2

1

&

Отказ

УУ

1

1

&

S

Отказ

ОЗУ

ТКФКоАР

1

ДШ3ФК

&

&

17

ИНОФ

&

Испр.

ОЗУ 1

ВКЛ.

Дист.

ДШ4

Авт раб

ФКФО583

ДШ4ФК

R

ДШ17

R T

ИнФФК

R

25

DC

1

2

4

8

16

&

Север

ТК

&

R

СТ2

&

&

ФК ПУ

1

ФКоУ

ТК ФКоПУ

ВЫХ11рСу

R

S T

УИС

Формирователь циклов ФК

ВЫХ10рСу

C

1

2

4

8

16

V

D

D

ДШ1ФК

КК1

СТ2

1

2

4

8

16

ИС25ФК

&

S T

1

2

27

8

11

DC

R

ИСФК

ИЗФК

Испр.

ФКоу

Испр

А0

Испр

ОЗУ

1

&

Испр.

Ф0583

6.

ФОРМИРУЕМАЯ КОМПЕТЕНЦИЯСпособность учитывать в профессиональной деятельности

современные

тенденции

развития

электроники,

измерительной и вычислительной техники (ОПК-6).

ПЛАНИРУЕМЫЕ РЕЗУЛЬТАТЫ ОБУЧЕНИЯ

ЗНАТЬ:

основы схемотехники и элементную базу цифровых

электронных устройств, архитектуру, условия и способы

использования микропроцессоров и микропроцессорных

систем в электронных устройствах.

УЧЕБНАЯ ЦЕЛЬ ЛЕКЦИИ

Систематизировать основы научных знаний по методам

математического описания последовательностных цифровых

устройств

7.

УЧЕБНЫЕ ВОПРОСЫ ЛЕКЦИИ1. Общие сведения о последовательностных

цифровых устройствах.

2. Методика синтеза последовательностных

цифровых устройств.

8.

ЛИТЕРАТУРА1. Цифровые устройства и микропроцессоры [Электронный

ресурс]: Учебное пособие / Е. Н. Жидков и [др.]. – Тверь:

ВА ВКО,2016. URL: http://ibook.akademy.org/book/46.

(ЭЛ.1/о м. 3.1.)

2. Цифровые устройства и микропроцессоры. Учебнометодическое пособие./ Е.Н.Жидков, [ и др.]. Тверь: ВА

ВКО., 2019 168с.

(Л.1/д с.45-58)

9.

1. Общие сведения опоследовательностных цифровых

устройствах

10.

Понятие цифрового автомата с памятью и егоматематическая модель

Способы задания цифровых автоматов с памятью

Элементарные цифровые автоматы с памятью

11.

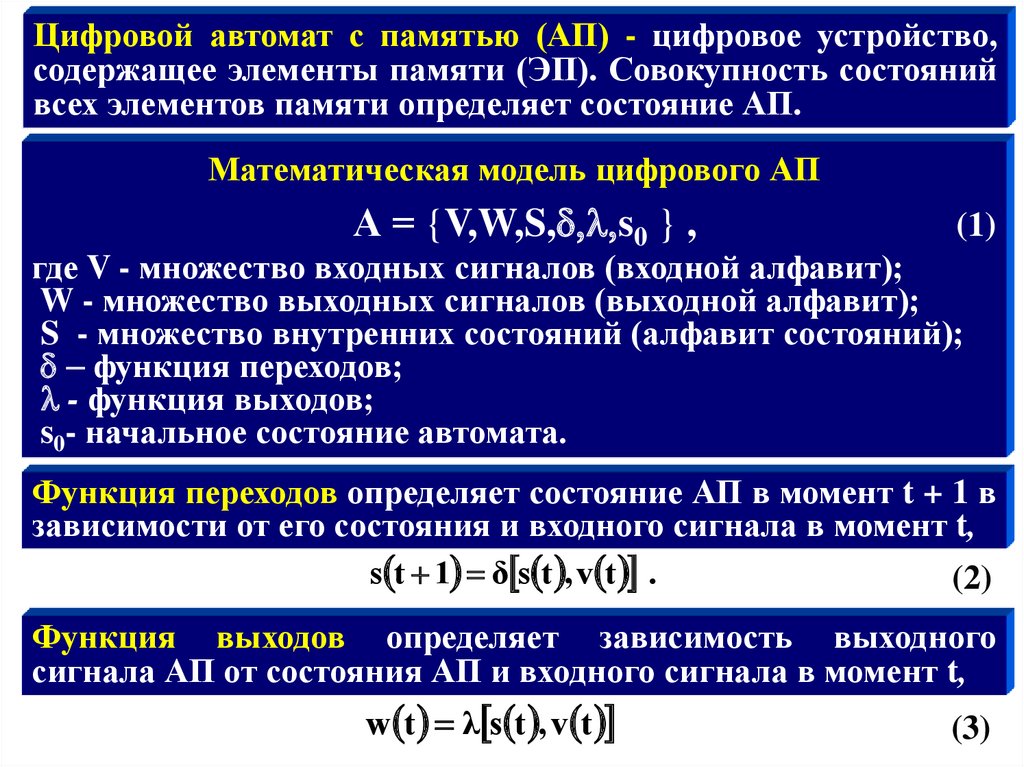

Цифровой автомат с памятью (АП) - цифровое устройство,содержащее элементы памяти (ЭП). Совокупность состояний

всех элементов памяти определяет состояние АП.

Математическая модель цифрового АП

А = {V,W,S,d,l,s0 } ,

(1)

где V - множество входных сигналов (входной алфавит);

W - множество выходных сигналов (выходной алфавит);

S - множество внутренних состояний (алфавит состояний);

d функция переходов;

l - функция выходов;

s0- начальное состояние автомата.

Функция переходов определяет состояние АП в момент t + 1 в

зависимости от его состояния и входного сигнала в момент t,

s t 1 δ s t , v t .

(2)

Функция выходов определяет зависимость выходного

сигнала АП от состояния АП и входного сигнала в момент t,

w t λ s t , v t

(3)

12.

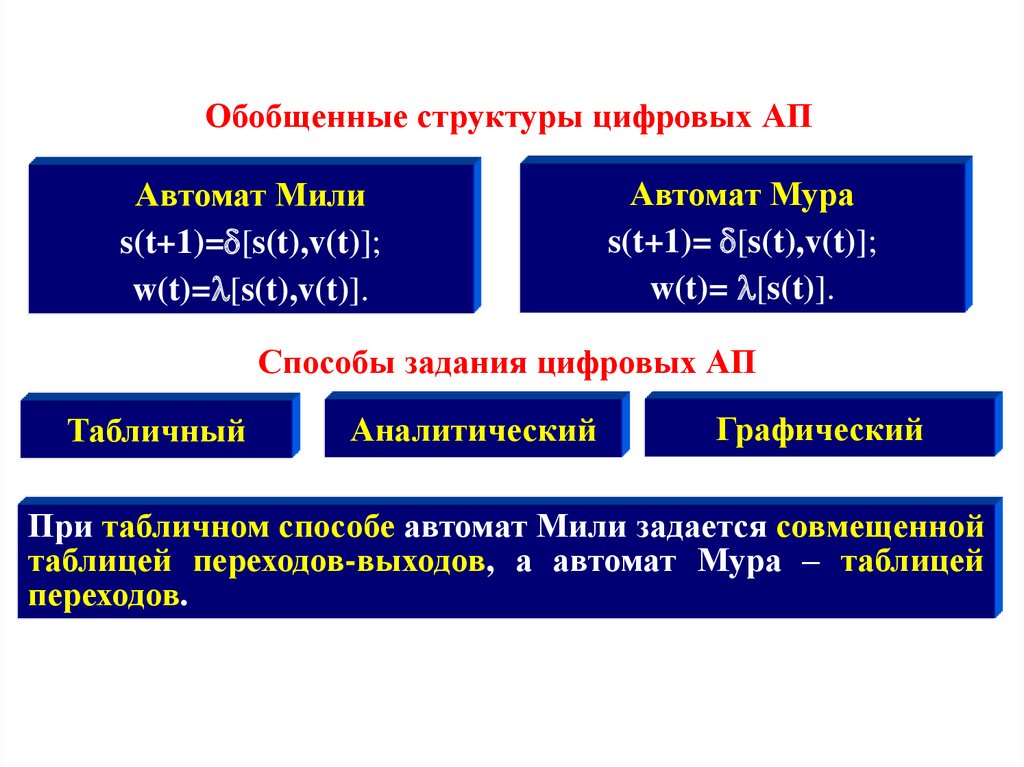

Обобщенные структуры цифровых АПАвтомат Мили

s(t+1)=d[s(t),v(t)];

w(t)=l[s(t),v(t)].

Автомат Мура

s(t+1)= d[s(t),v(t)];

w(t)= l[s(t)].

Способы задания цифровых АП

Табличный

Аналитический

Графический

При табличном способе автомат Мили задается совмещенной

таблицей переходов-выходов, а автомат Мура – таблицей

переходов.

13.

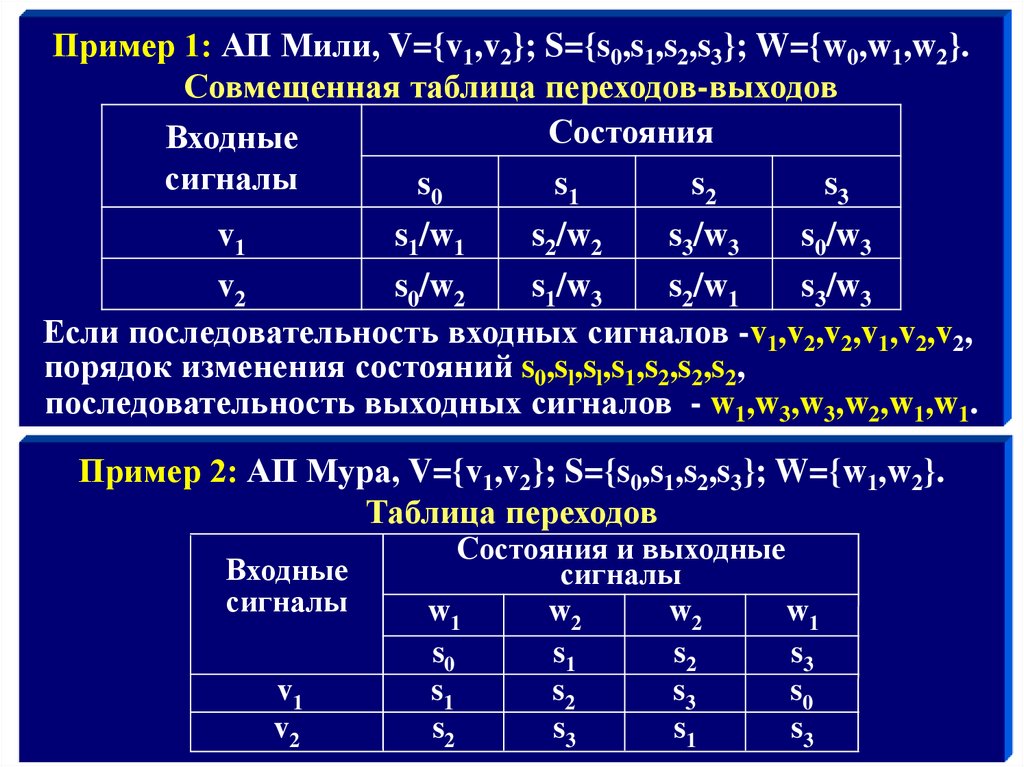

Пример 1: АП Мили, V={v1,v2}; S={s0,s1,s2,s3}; W={w0,w1,w2}.Совмещенная таблица переходов-выходов

Состояния

Входные

сигналы

s0

s1

s2

s3

v1

s1/w1

s2/w2

s3/w3

s0/w3

v2

s0/w2

s1/w3

s2/w1

s3/w3

Если последовательность входных сигналов -v1,v2,v2,v1,v2,v2,

порядок изменения состояний s0,sl,sl,s1,s2,s2,s2,

последовательность выходных сигналов - w1,w3,w3,w2,w1,w1.

Пример 2: АП Мура, V={v1,v2}; S={s0,s1,s2,s3}; W={w1,w2}.

Таблица переходов

Входные

сигналы

v1

v2

Состояния и выходные

сигналы

w1

w2

w2

w1

s0

s1

s2

s3

s1

s2

s3

s0

s2

s3

s1

s3

14.

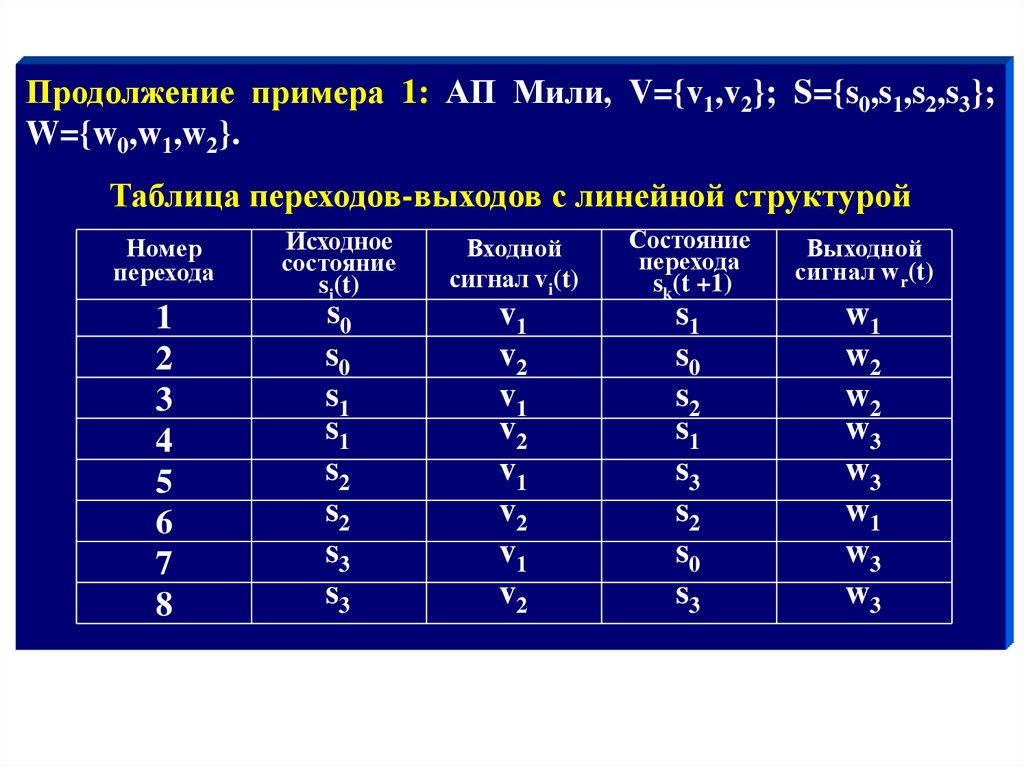

Продолжение примера 1: АП Мили, V={v1,v2}; S={s0,s1,s2,s3};W={w0,w1,w2}.

Таблица переходов-выходов с линейной структурой

Номер

перехода

1

2

3

4

5

6

7

8

Исходное

состояние

si(t)

s0

s0

s1

s1

s2

s2

s3

s3

Входной

сигнал vi(t)

v1

v2

v1

v2

v1

v2

v1

v2

Состояние

перехода

sk(t +1)

s1

s0

s2

s1

s3

s2

s0

s3

Выходной

сигнал wr(t)

w1

w2

w2

w3

w3

w1

w3

w3

15.

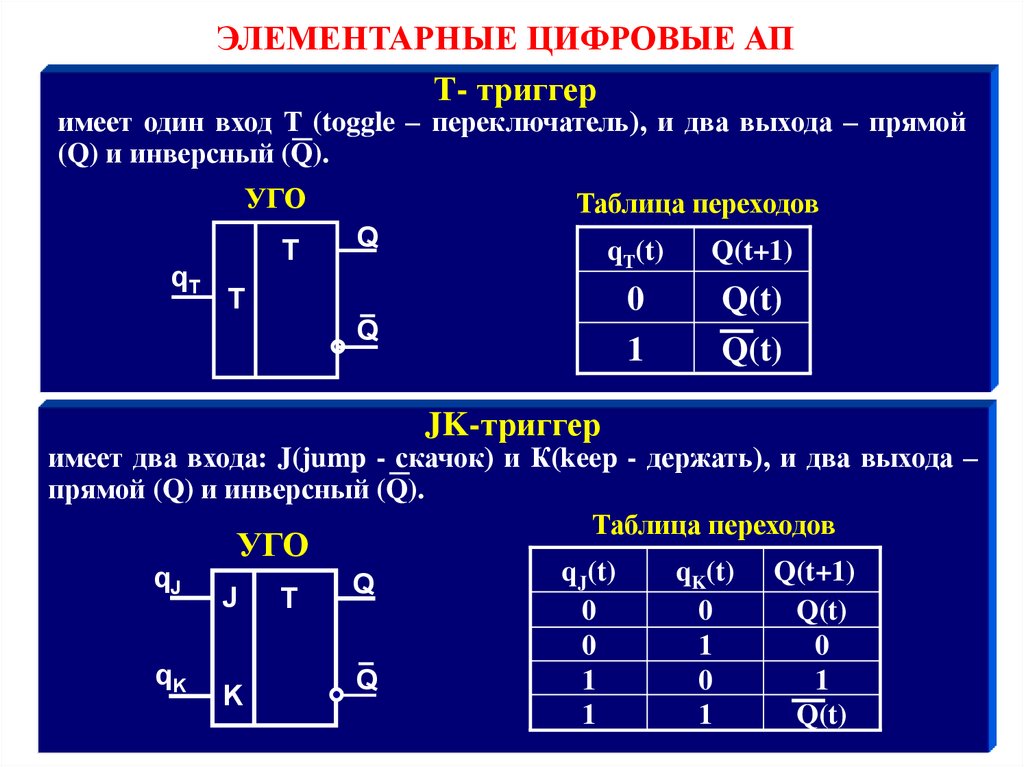

ЭЛЕМЕНТАРНЫЕ ЦИФРОВЫЕ АПТ- триггер

имеет один вход Т (toggle – переключатель), и два выхода – прямой

(Q) и инверсный (Q).

УГО

qT

T

Таблица переходов

Q

qТ(t)

Q(t+1)

0

1

Q(t)

Q(t)

T

Q

JK-триггер

имеет два входа: J(jump - скачок) и К(keep - держать), и два выхода –

прямой (Q) и инверсный (Q).

Таблица переходов

УГО

qJ

qK

J

K

T

Q

Q

qJ(t)

0

0

1

1

qK(t)

0

1

0

1

Q(t+1)

Q(t)

0

1

Q(t)

16.

2. Методика синтезапоследовательностных цифровых

устройств

17.

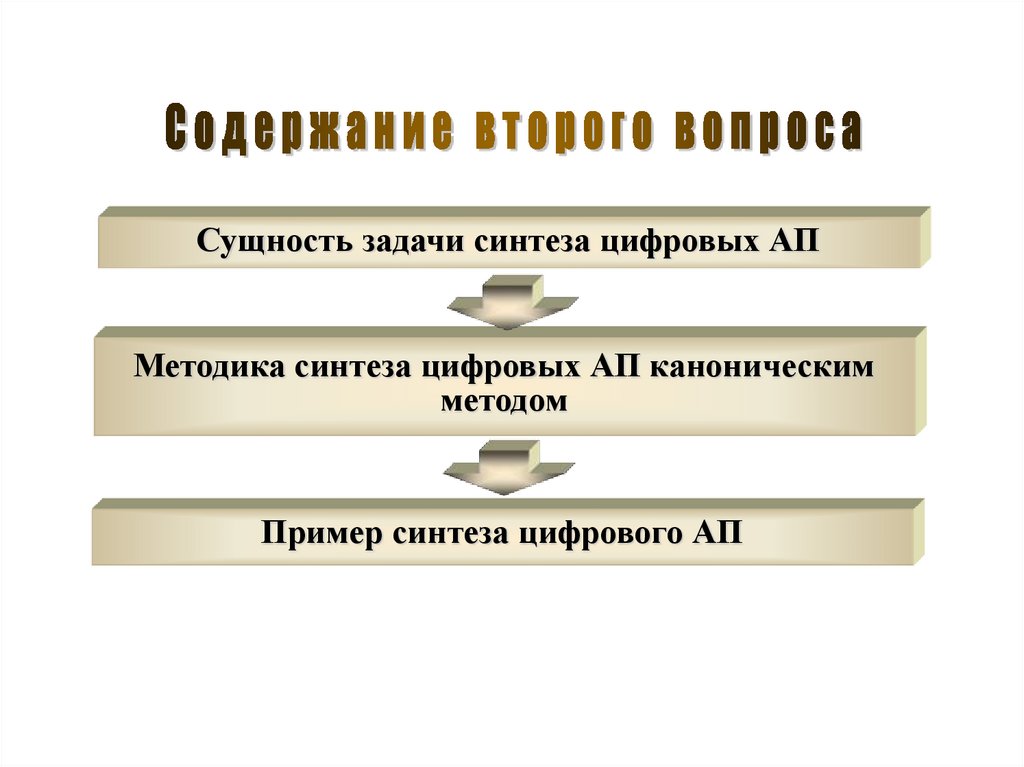

Сущность задачи синтеза цифровых АПМетодика синтеза цифровых АП каноническим

методом

Пример синтеза цифрового АП

18.

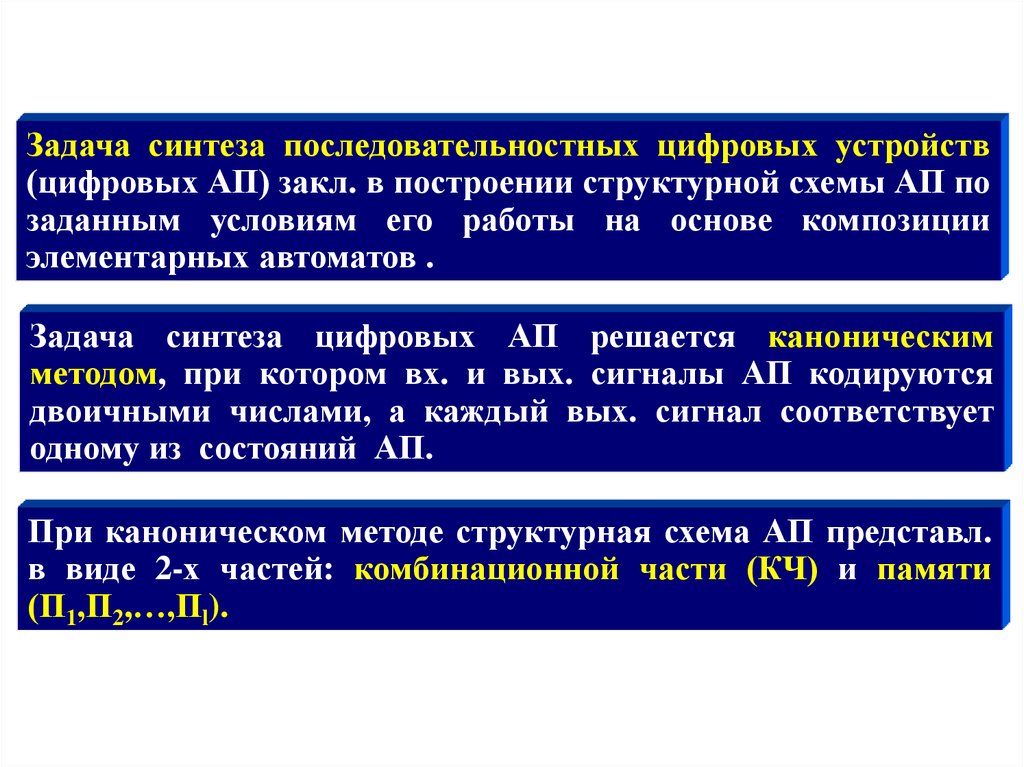

Задача синтеза последовательностных цифровых устройств(цифровых АП) закл. в построении структурной схемы АП по

заданным условиям его работы на основе композиции

элементарных автоматов .

Задача синтеза цифровых АП решается каноническим

методом, при котором вх. и вых. сигналы АП кодируются

двоичными числами, а каждый вых. сигнал соответствует

одному из состояний АП.

При каноническом методе структурная схема АП представл.

в виде 2-х частей: комбинационной части (КЧ) и памяти

(П1,П2,…,Пl).

19.

Обобщенная структурная схема цифрового АПx1

x2

.

.

.

хn

y1

y2

.

.

.

ym

КЧ

q1

q2

.

.

.

ql

П1

Q1

П2

.

.

.

Q2

Пl

Ql

20.

Если элементы памяти предварительно выбраны, синтез АПсводится к синтезу его КЧ, которая должна реализовывать

следующую систему БФ (канонических уравнений):

Канонические уравнения

y 1 (t ) f1 x1 t , x 2 t ,..., x n t , Q1 t , Q 2 t ,...,Q l t ;

y (t ) f x t , x t ,..., x t , Q t , Q t ,...,Q t ;

2

2

1

2

n

1

2

l

.

..........

..........

..........

..........

..........

..........

..........

..........

..

y m (t ) f m x1 t , x 2 t ,..., x n t , Q1 t , Q 2 t ,...,Q l t

(4)

q1 (t ) f1 x1 t , x 2 t ,..., x n t , Q1 t , Q 2 t ,...,Q l t ;

q (t ) f x t , x t ,..., x t , Q t , Q t ,...,Q t ;

2

2

1

2

n

1

2

l

.

..................................................................................

q l (t ) f l x1 t , x 2 t ,..., x n t , Q1 t , Q 2 t ,...,Q l t

(5)

21.

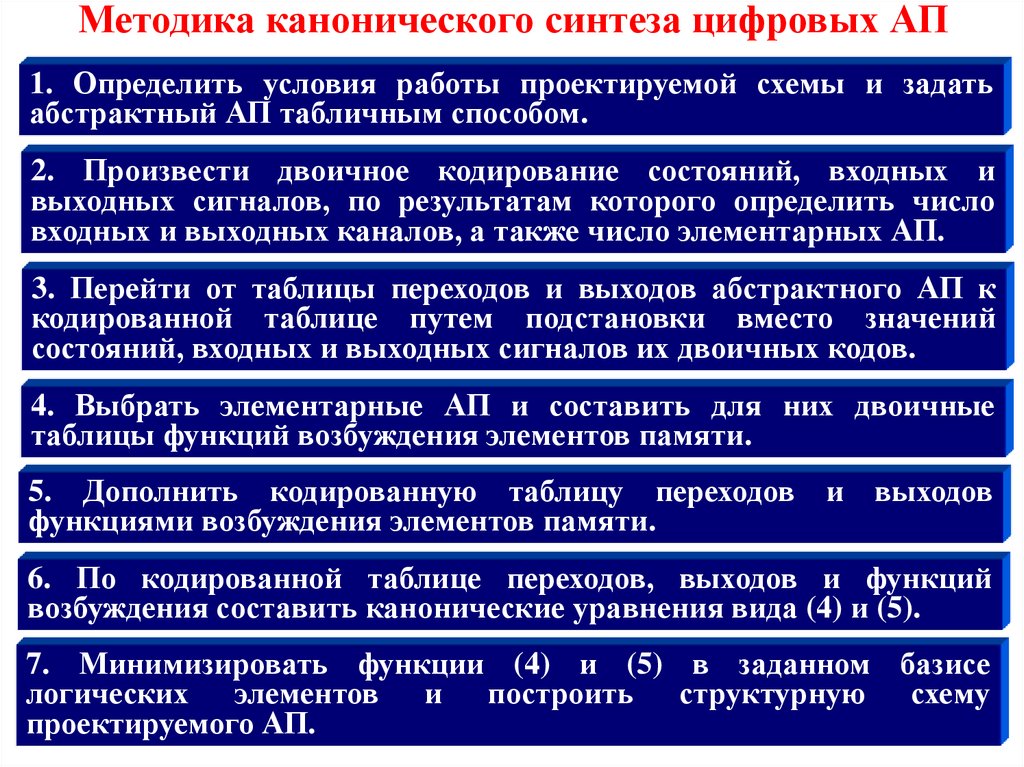

Методика канонического синтеза цифровых АП1. Определить условия работы проектируемой схемы и задать

абстрактный АП табличным способом.

2. Произвести двоичное кодирование состояний, входных и

выходных сигналов, по результатам которого определить число

входных и выходных каналов, а также число элементарных АП.

3. Перейти от таблицы переходов и выходов абстрактного АП к

кодированной таблице путем подстановки вместо значений

состояний, входных и выходных сигналов их двоичных кодов.

4. Выбрать элементарные АП и составить для них двоичные

таблицы функций возбуждения элементов памяти.

5. Дополнить кодированную таблицу переходов и выходов

функциями возбуждения элементов памяти.

6. По кодированной таблице переходов, выходов и функций

возбуждения составить канонические уравнения вида (4) и (5).

7. Минимизировать функции (4) и (5) в заданном базисе

логических элементов и построить структурную схему

проектируемого АП.

22.

Пример 1. Синтезировать делитель частоты на 3. Автомат суммирует 1-езначения входного сигнала и запоминает их сумму. При поступлении на

вход автомата 3-го сигнала с 1-м значением он выдаёт вых. сигнал,

равный 1, и переходит в исходное состояние.

-1Входной алфавит: v1 – отсутствие 1-го сигнала на вх.; v2 – наличие 1-го

сигнала на вх.

Алфавит состояний: s0- исходное состояние АП; s1 – состояние АП,

соответствующее хранению 1; s2 – состояние АП, соответствующее

хранению 2.

Выходной алфавит: w1 – отсутствие 1-го сигнала на вых.; w2 – наличие

1-го сигнала на вых.

Совмещённая таблица переходов и выходов

Входные

Состояния (si)

сигналы

s0

s1

s2

(vi)

v1

v2

s0/w1

s1/w1

s1/w1

s2/w1

s2/w1

s0/w2

23.

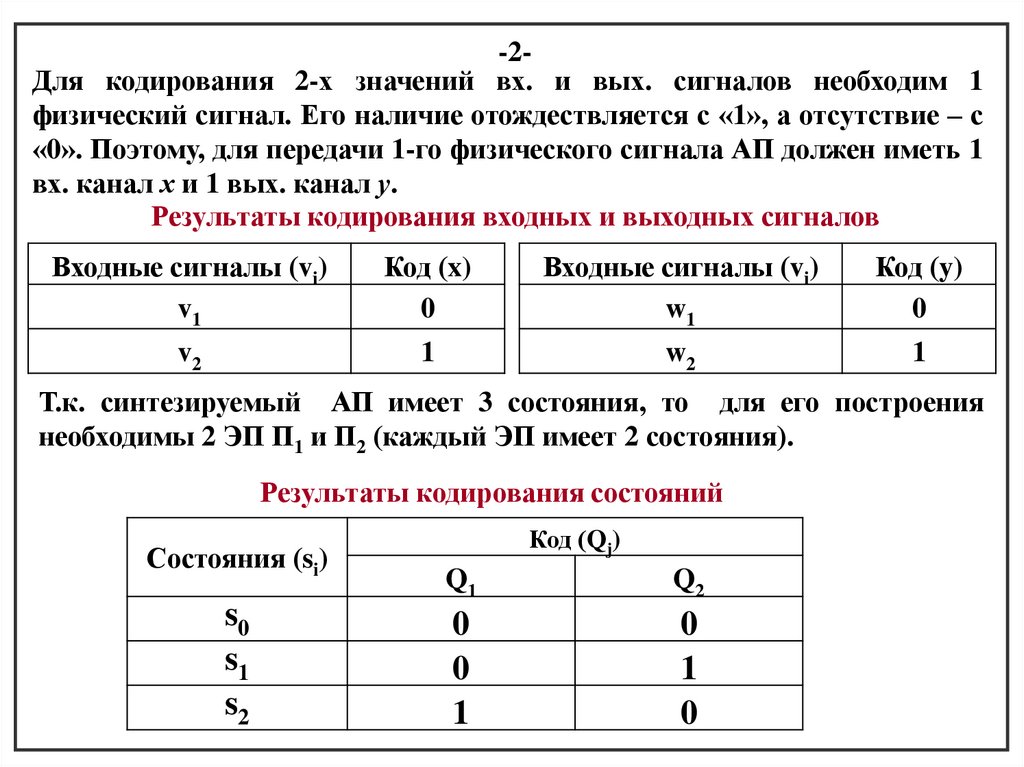

-2Для кодирования 2-х значений вх. и вых. сигналов необходим 1физический сигнал. Его наличие отождествляется с «1», а отсутствие – с

«0». Поэтому, для передачи 1-го физического сигнала АП должен иметь 1

вх. канал х и 1 вых. канал у.

Результаты кодирования входных и выходных сигналов

Входные сигналы (vi)

v1

Код (x)

0

Входные сигналы (vi)

w1

Код (y)

0

v2

1

w2

1

Т.к. синтезируемый АП имеет 3 состояния, то для его построения

необходимы 2 ЭП П1 и П2 (каждый ЭП имеет 2 состояния).

Результаты кодирования состояний

Состояния (si)

s0

s1

s2

Код (Qj)

Q1

Q2

0

0

1

0

1

0

24.

-3Совмещённая кодированная таблица переходов и выходовСостояния (Q1,Q2)

Входные сигналы

(xi)

s0

s1

s2

0

00/0

01/0

10/0

1

01/0

10/0

00/1

Совмещённая линейная кодированная таблица переходов и выходов

х(t)

Q1(t)

Q2(t)

Q1(t+1)

Q2(t+1)

y(t)

0

0

0

0

0

0

0

0

1

0

1

0

0

1

0

1

0

0

1

0

0

0

1

0

1

0

1

1

0

0

1

1

0

0

0

1

25.

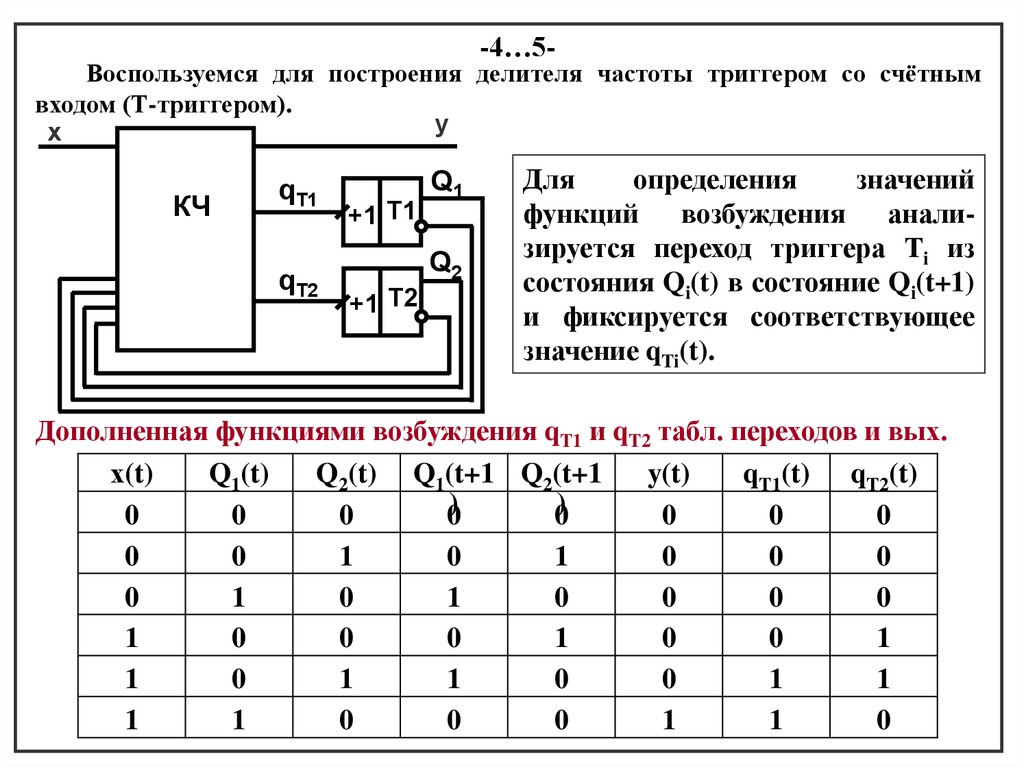

-4…5-Воспользуемся для построения делителя частоты триггером со счётным

входом (Т-триггером).

y

x

КЧ

qT1

qT2

+1 Т1

Q1

Q2

+1 Т2

Для

определения

значений

функций возбуждения анализируется переход триггера Тi из

состояния Qi(t) в состояние Qi(t+1)

и фиксируется соответствующее

значение qTi(t).

Дополненная функциями возбуждения qT1 и qT2 табл. переходов и вых.

х(t)

Q1(t)

Q2(t) Q1(t+1 Q2(t+1

y(t)

qT1(t) qT2(t)

0

0

0

0)

0)

0

0

0

0

0

1

0

1

0

0

0

0

1

0

1

0

0

0

0

1

0

0

0

1

0

0

1

1

0

1

1

0

0

1

1

1

1

0

0

0

1

1

0

26.

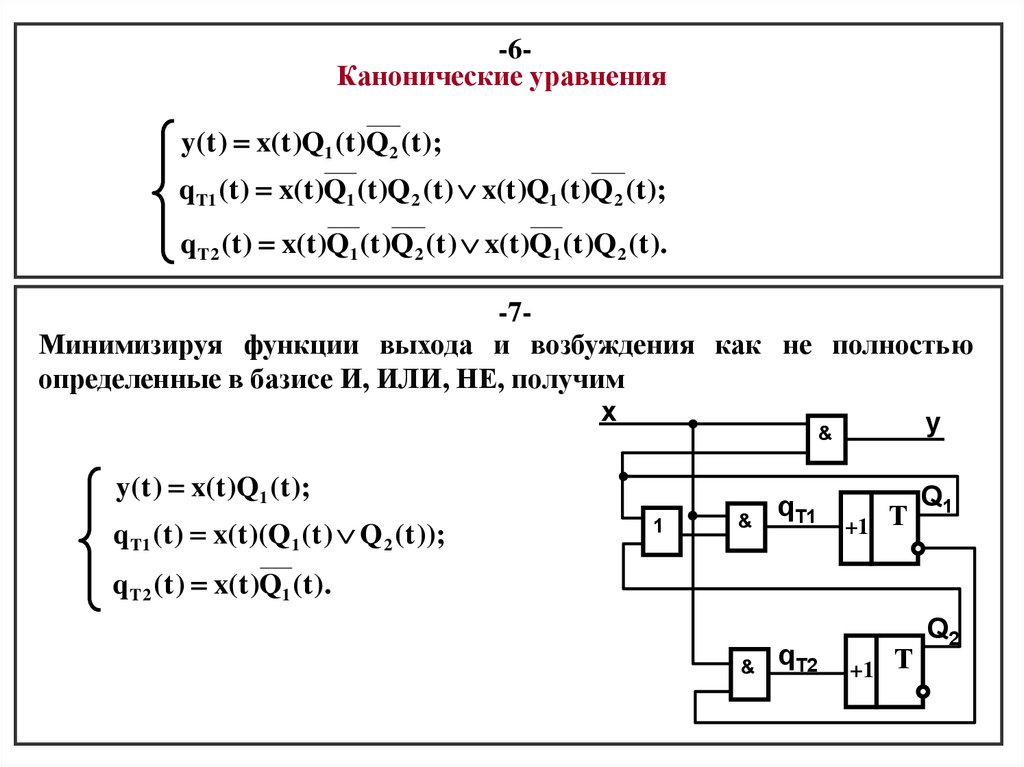

-6Канонические уравненияy(t ) x(t )Q1 (t )Q 2 (t );

q T1 (t ) x(t )Q1 (t )Q 2 (t ) x(t )Q1 (t )Q 2 (t );

q T 2 (t ) x(t )Q1 (t )Q 2 (t ) x(t )Q1 (t )Q 2 (t ).

-7Минимизируя функции выхода и возбуждения как не полностью

определенные в базисе И, ИЛИ, НЕ, получим

x

y

&

y(t ) x(t )Q1 (t );

q T1 (t ) x(t )(Q1 (t ) Q 2 (t ));

1

&

qT1

+1

Т

Q1

q T 2 (t ) x(t )Q1 (t ).

&

qT2

+1

Т

Q2

27.

Таким образом, на этапе структурногосинтеза выполняются: кодирование состояний АП; составление таблицы переходов

АП; определение функций возбуждения

элементов памяти; переход к базису

выбранной для реализации схемотехнологии; составление логической схемы АП.

28.

Отработать лекцию, используя:(ЭЛ.1/о м. 3.1.);

(Л.1/д с.45-58).

Подготовиться к пр. зан. №3 «Синтез

последовательностных

цифровых

устройств».

informatics

informatics