Similar presentations:

Введение в ПОР. Основные теоретические вопросы проектирования ПОР

1.

Московский Авиационный Институт(Национальный Исследовательский Университет)

«Программно-Определяемые

Радиосистемы»

Серкин Фёдор Борисович

Кафедра 408 – «Инфокоммуникации»

2.

Литература:1. Скляр Б., «Цифровая связь. Теоретические основы и практическое

применение», «Вильямс», Москва, Санкт-Петербург, Киев, 2003.

2. Гольденберг Л.М., Матюшкин Б.Д., Поляк М.Н., «Цифровая обработка

сигналов», «Радио и связь», Москва, 1990.

3. Максфилд К., «Проектирование на ПЛИС. Архитектура, средства и

методы», «Додэка-ХХI», Москва, 2007.

4. «IEEE 1012 Standard for Software Verification and Validation», IEEE, New

York, 2005.

5. Tuttlebee W., «software defined radio. Enabling technology», WILEY, New

York, 2002.

1

3.

Содержание курса:I.

Введение в ПОР.

II.

Основные теоретические вопросы проектирования ПОР.

III.

Реализация на жесткой и программируемой логике.

IV. Программируемое радио.

2

4.

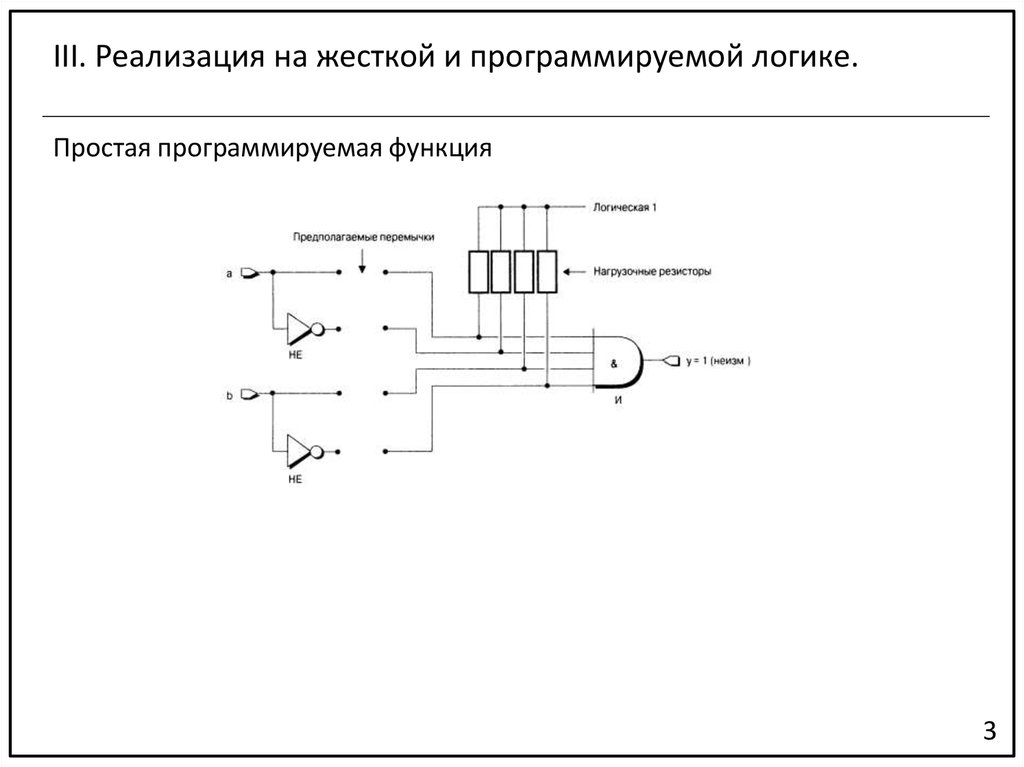

III. Реализация на жесткой и программируемой логике.Простая программируемая функция

3

5.

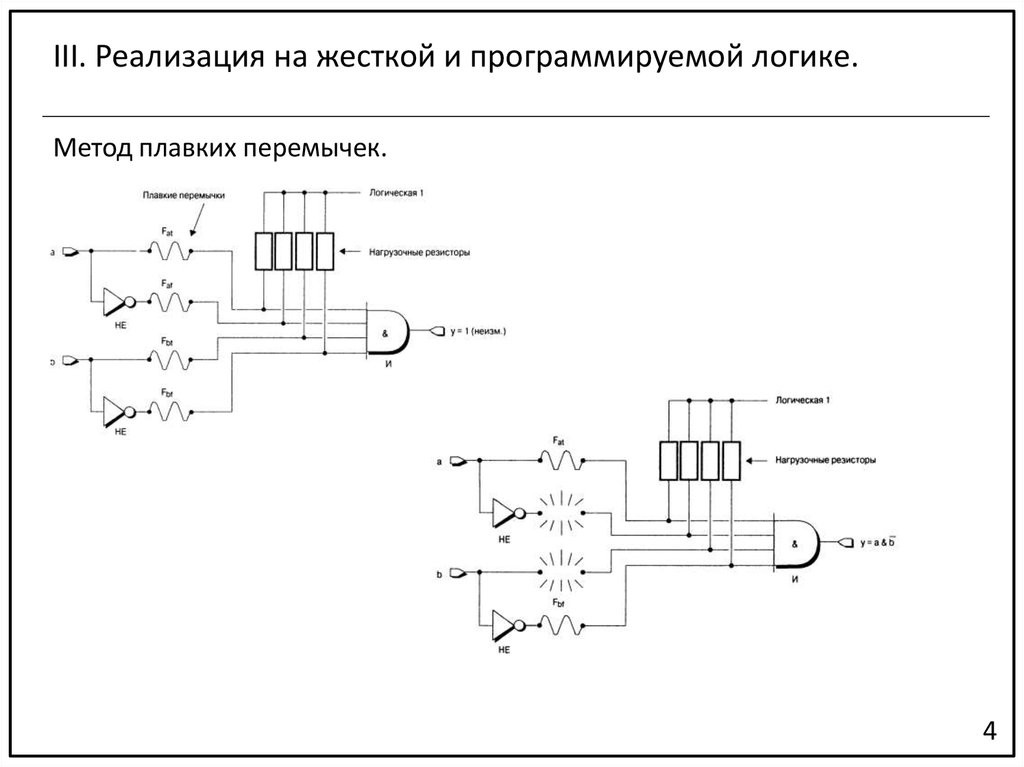

III. Реализация на жесткой и программируемой логике.Метод плавких перемычек.

4

6.

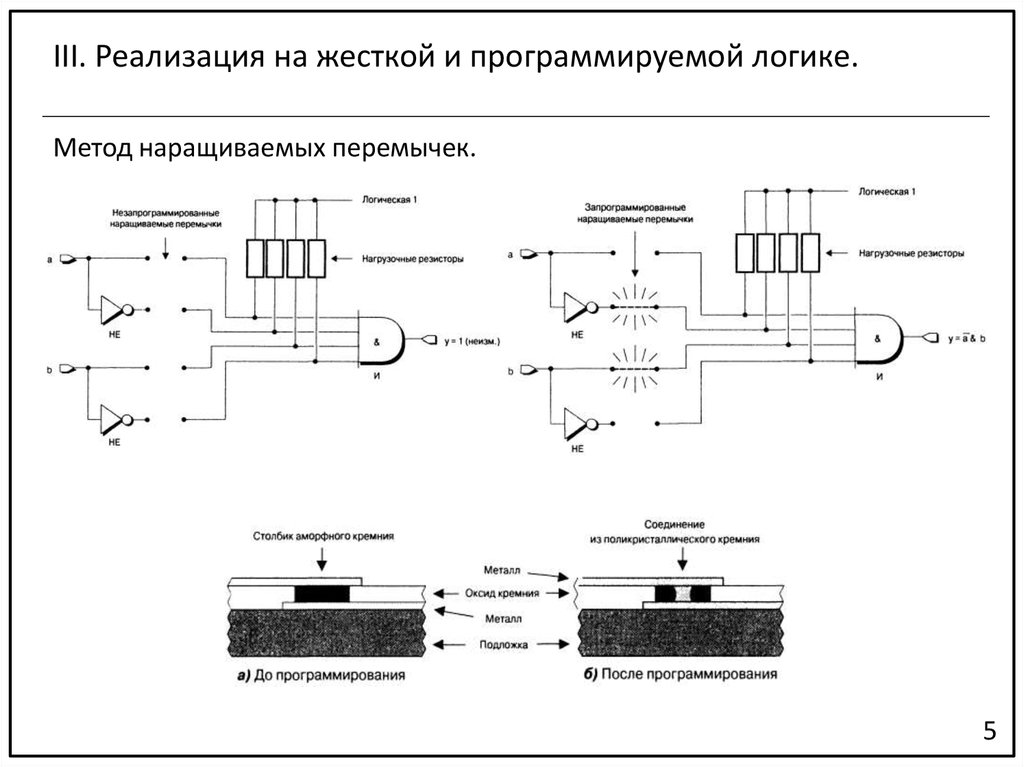

III. Реализация на жесткой и программируемой логике.Метод наращиваемых перемычек.

5

7.

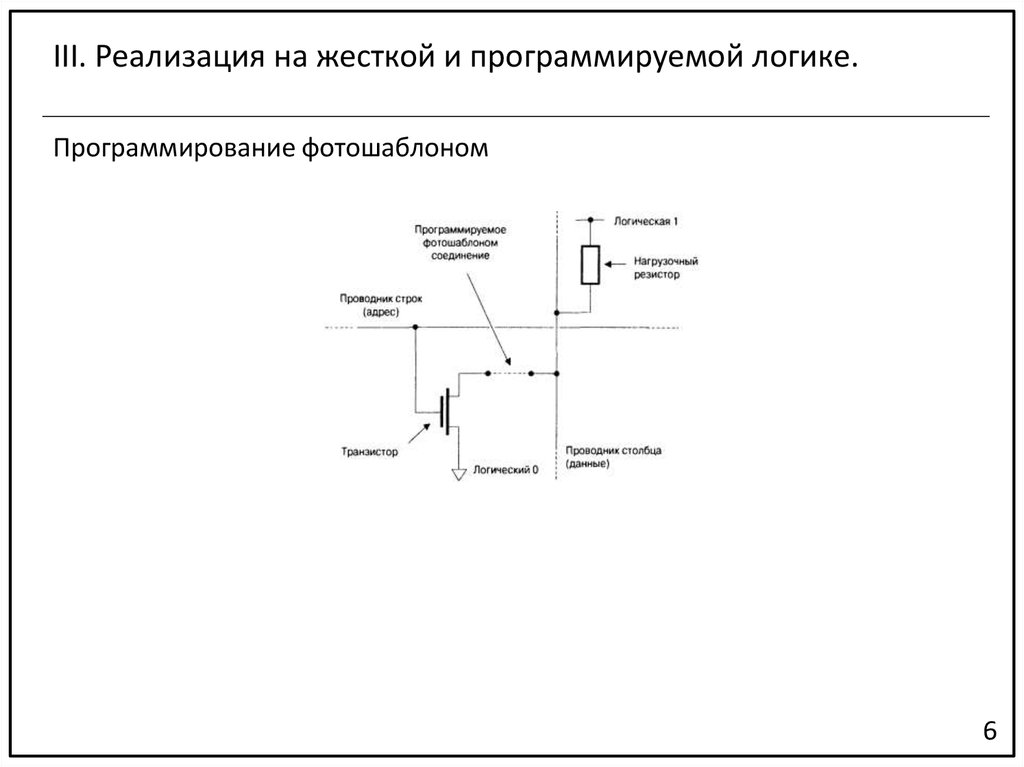

III. Реализация на жесткой и программируемой логике.Программирование фотошаблоном

6

8.

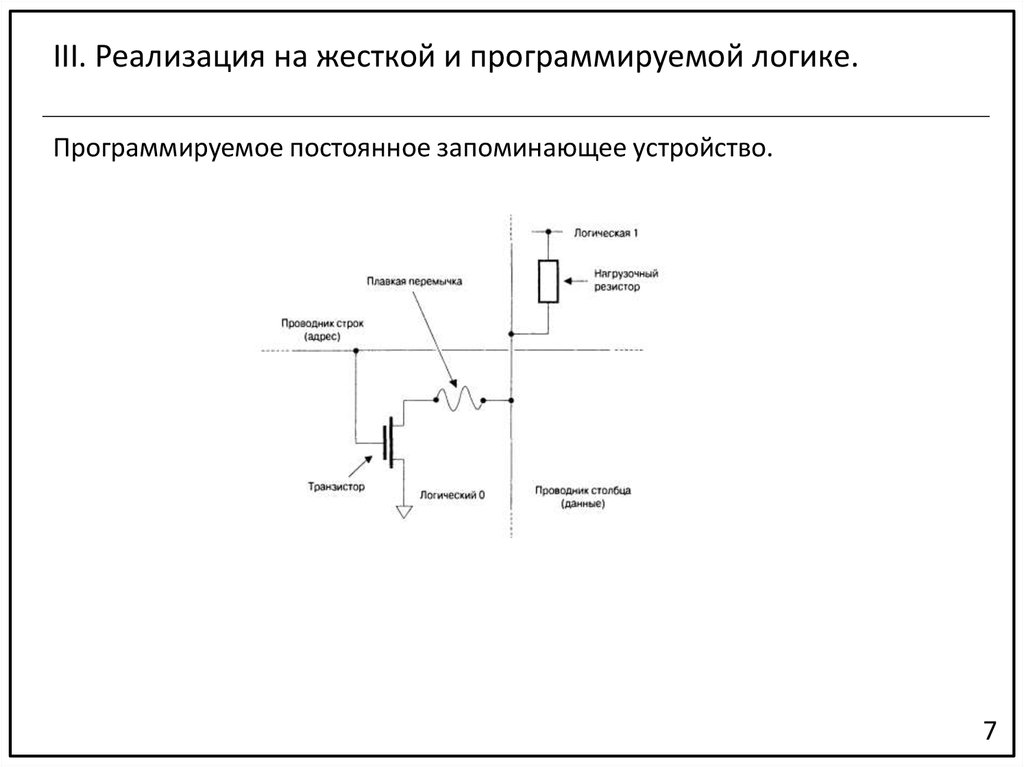

III. Реализация на жесткой и программируемой логике.Программируемое постоянное запоминающее устройство.

7

9.

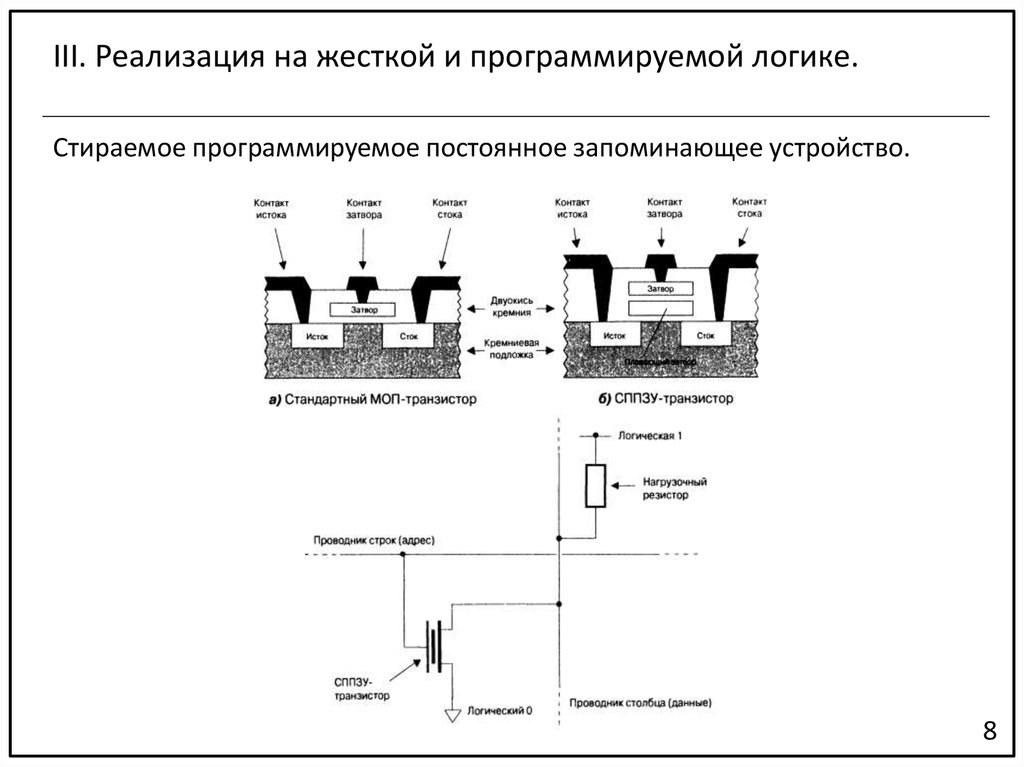

III. Реализация на жесткой и программируемой логике.Стираемое программируемое постоянное запоминающее устройство.

8

10.

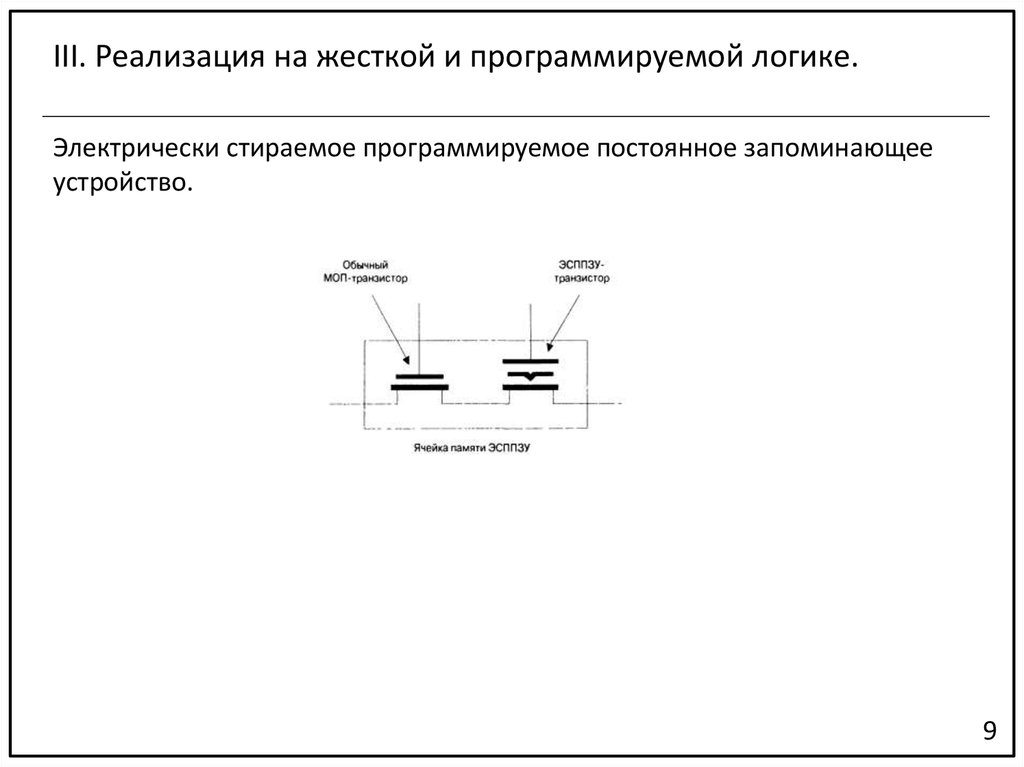

III. Реализация на жесткой и программируемой логике.Электрически стираемое программируемое постоянное запоминающее

устройство.

9

11.

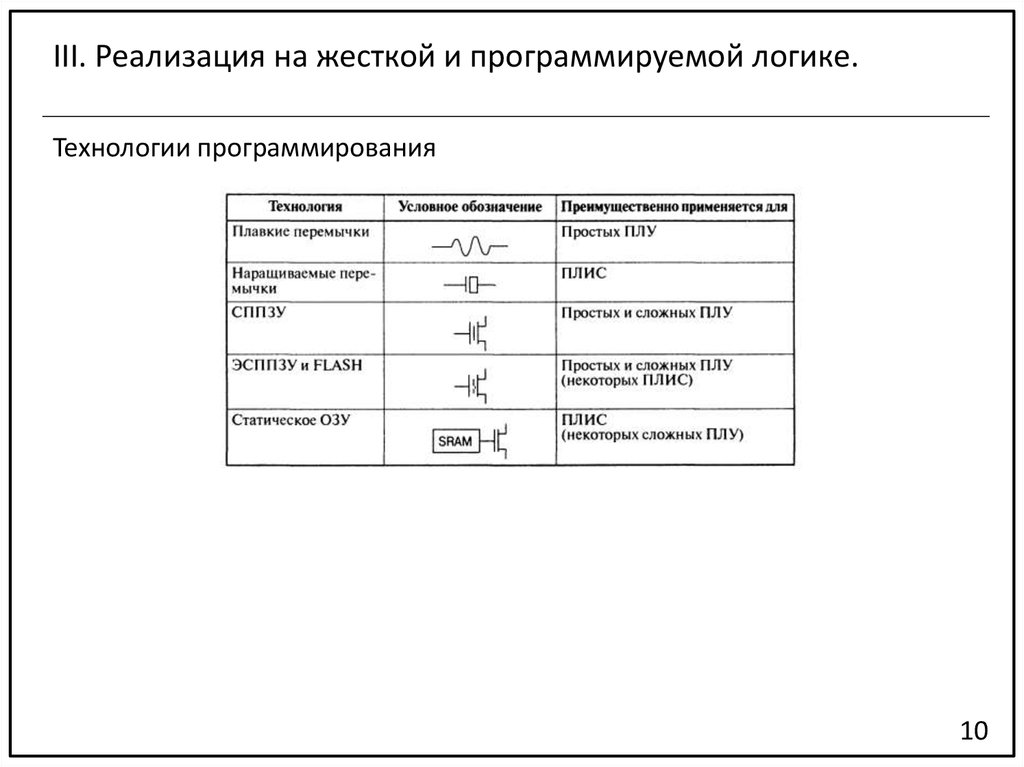

III. Реализация на жесткой и программируемой логике.Технологии программирования

10

12.

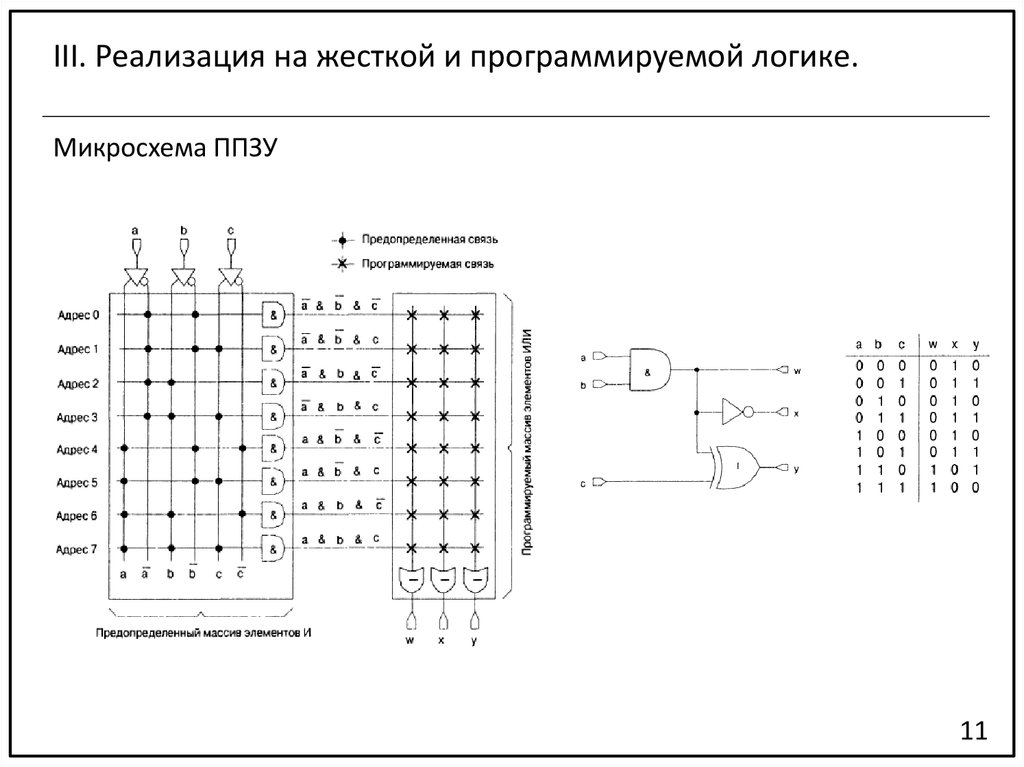

III. Реализация на жесткой и программируемой логике.Микросхема ППЗУ

11

13.

III. Реализация на жесткой и программируемой логике.Микросхема ППЗУ

12

14.

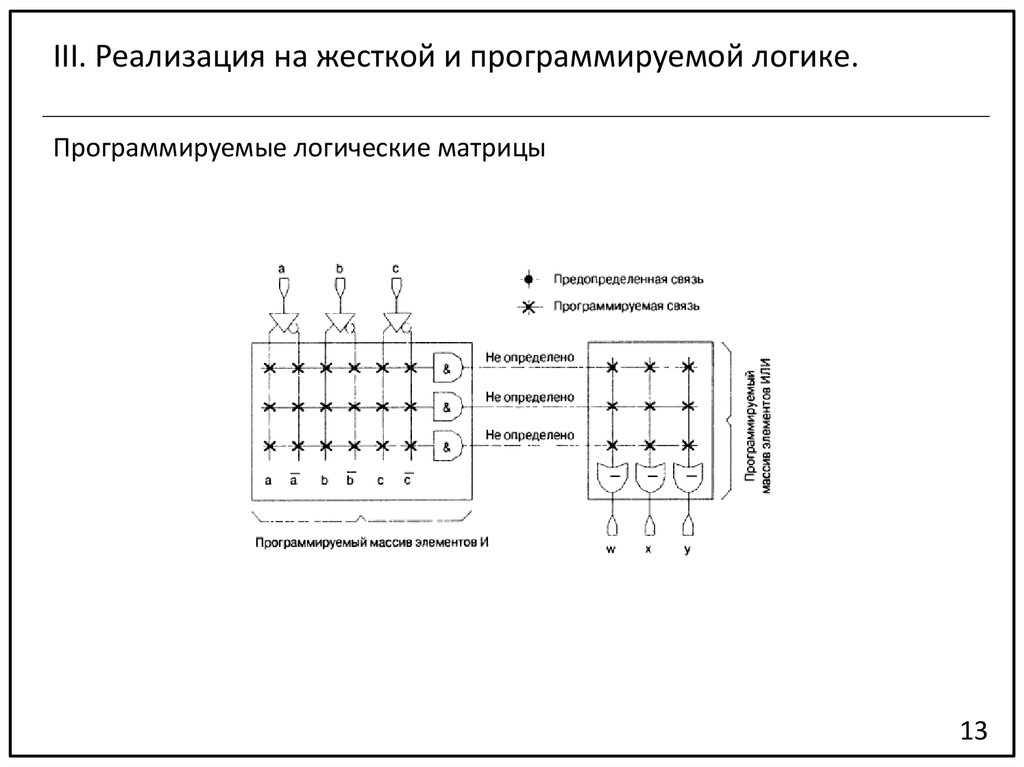

III. Реализация на жесткой и программируемой логике.Программируемые логические матрицы

13

15.

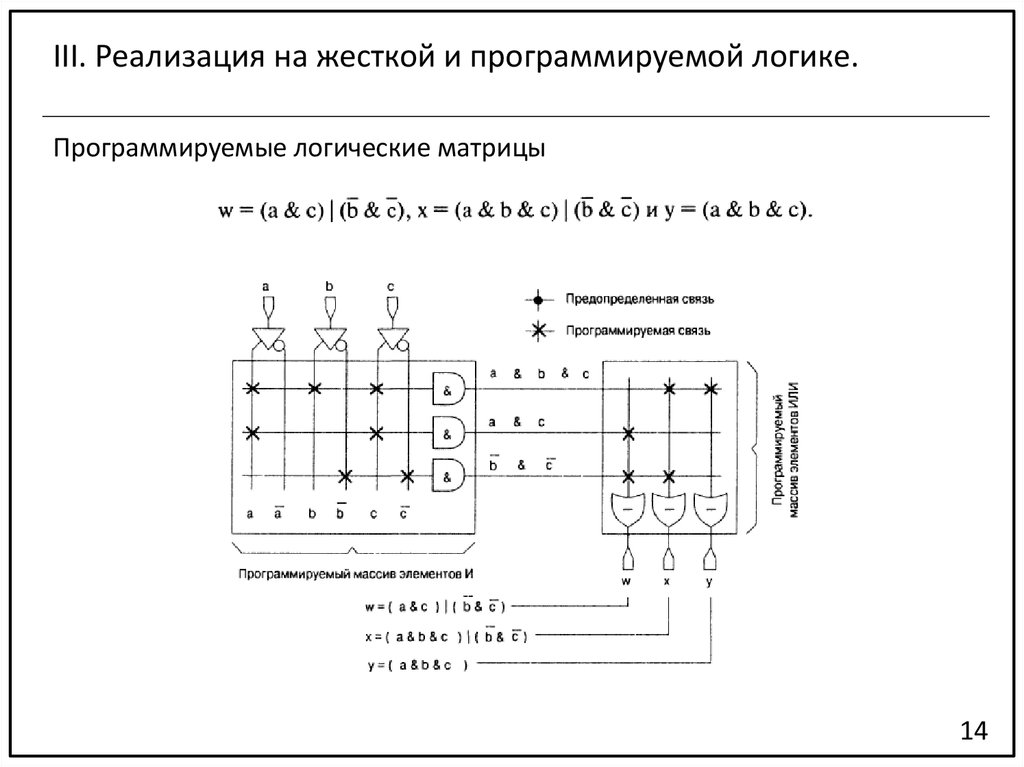

III. Реализация на жесткой и программируемой логике.Программируемые логические матрицы

14

16.

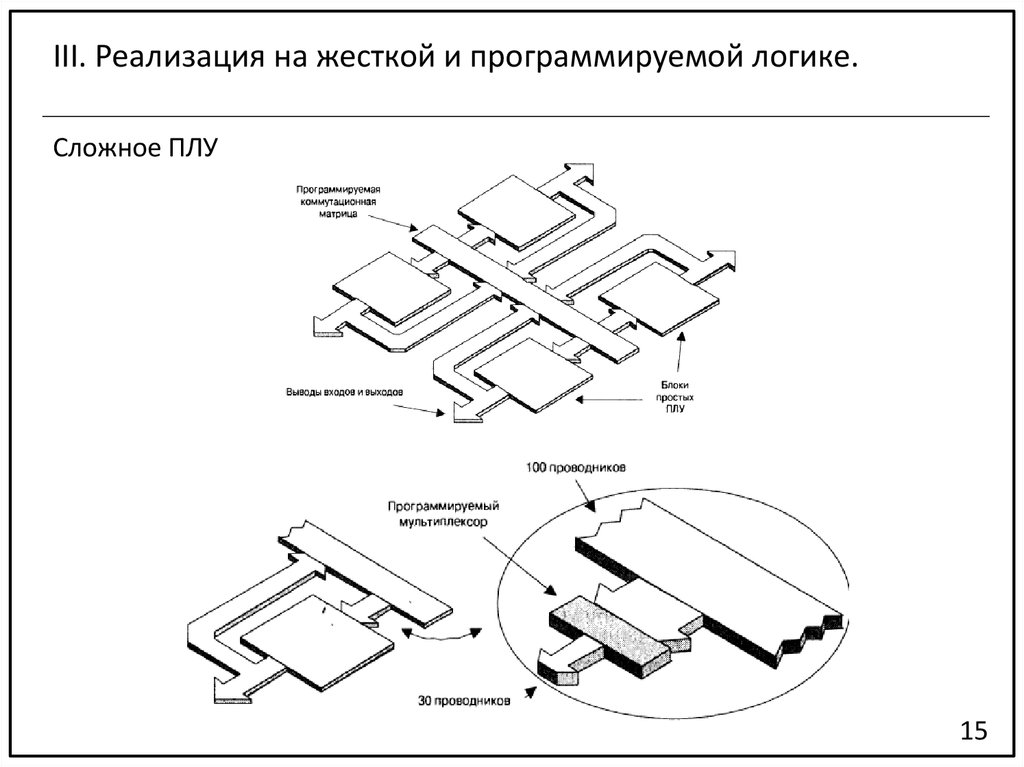

III. Реализация на жесткой и программируемой логике.Сложное ПЛУ

15

17.

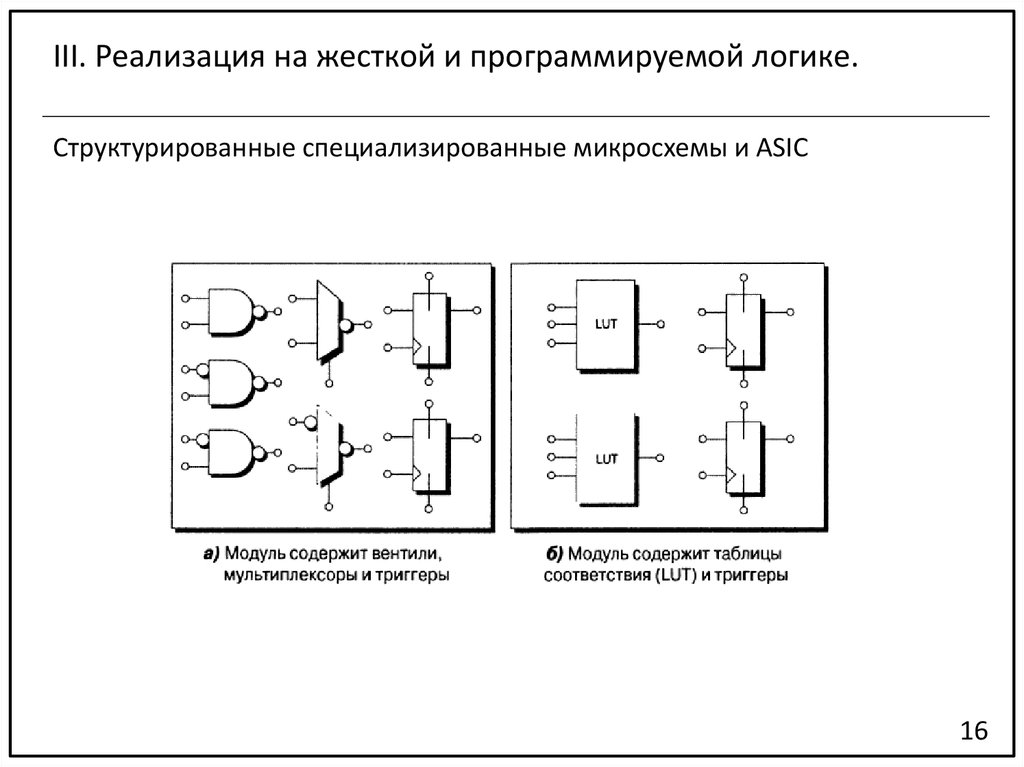

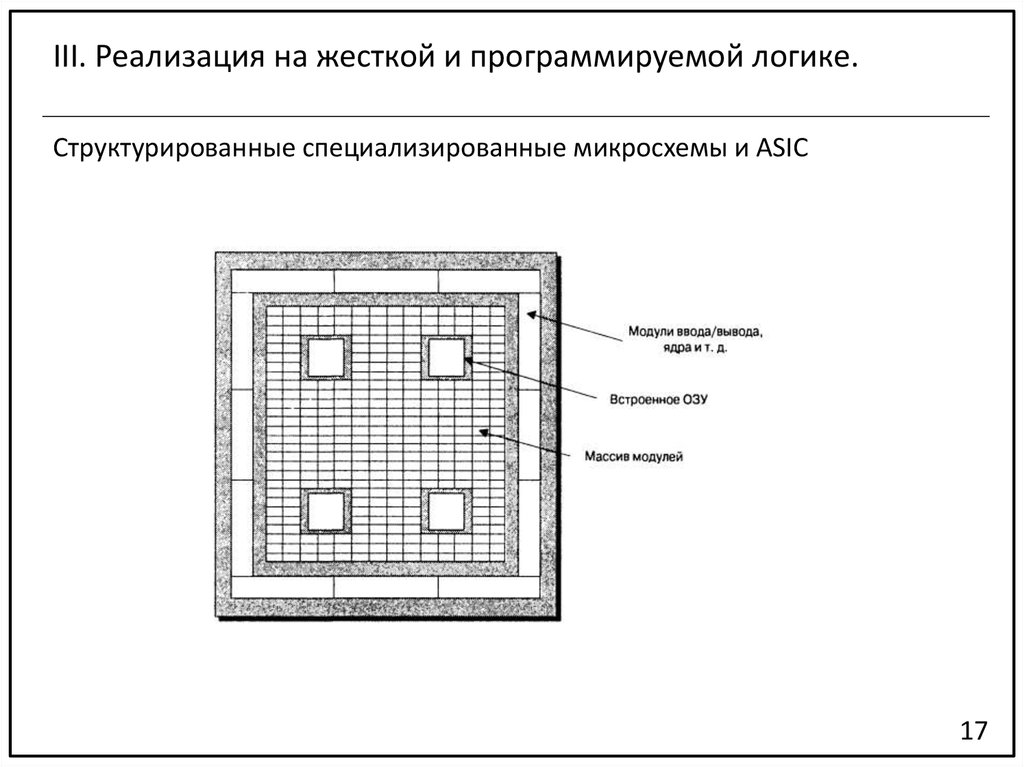

III. Реализация на жесткой и программируемой логике.Структурированные специализированные микросхемы и ASIC

16

18.

III. Реализация на жесткой и программируемой логике.Структурированные специализированные микросхемы и ASIC

17

19.

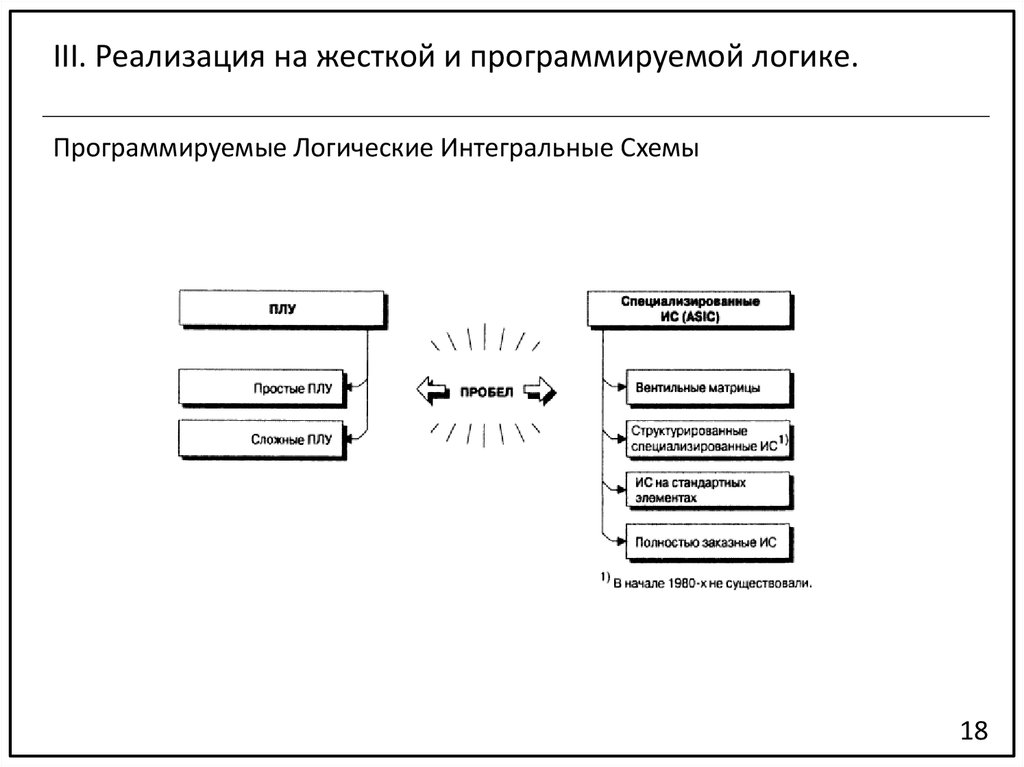

III. Реализация на жесткой и программируемой логике.Программируемые Логические Интегральные Схемы

18

20.

III. Реализация на жесткой и программируемой логике.Программируемые Логические Интегральные Схемы

19

21.

III. Реализация на жесткой и программируемой логике.Программируемые Логические Интегральные Схемы

20

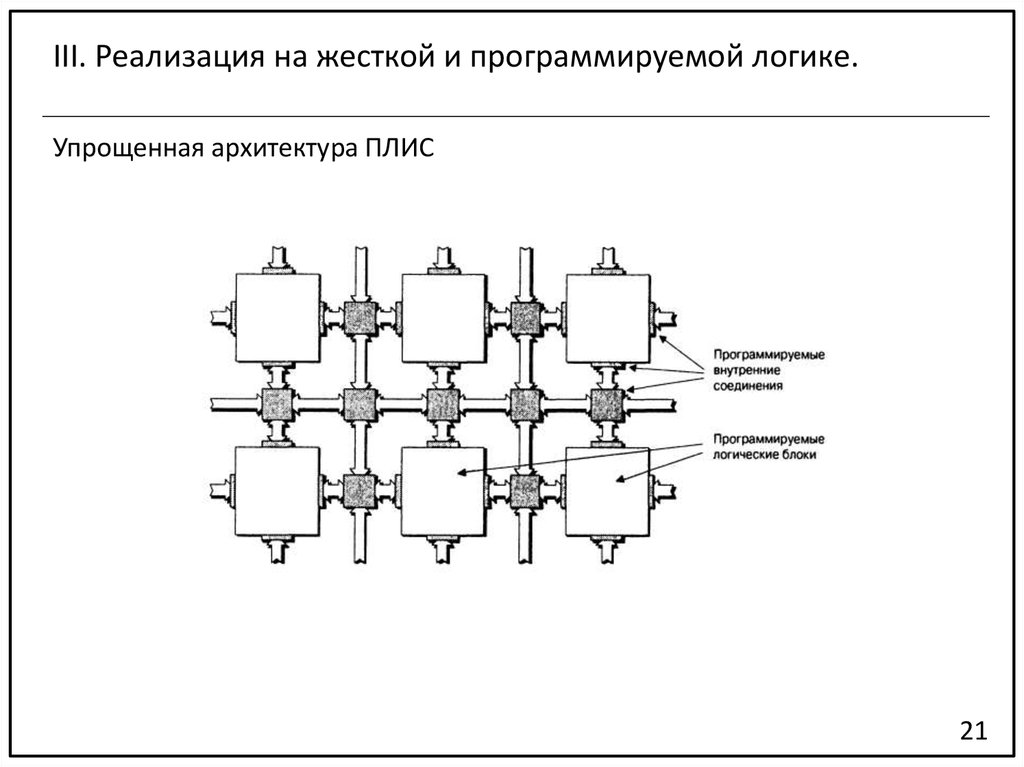

22.

III. Реализация на жесткой и программируемой логике.Упрощенная архитектура ПЛИС

21

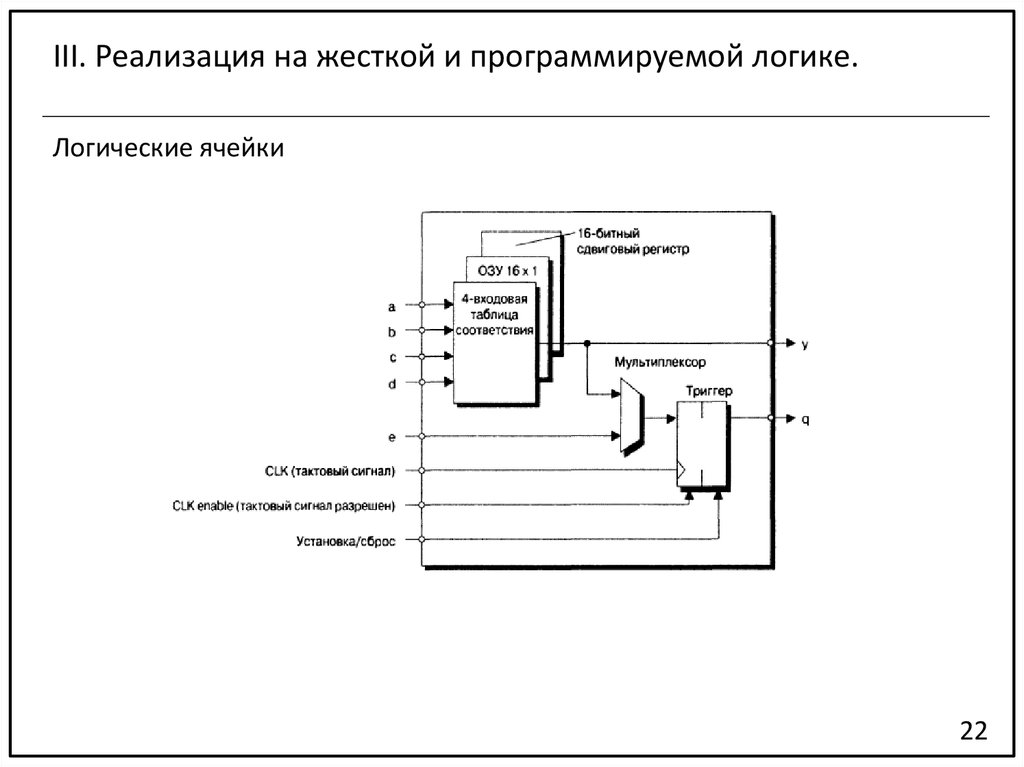

23.

III. Реализация на жесткой и программируемой логике.Логические ячейки

22

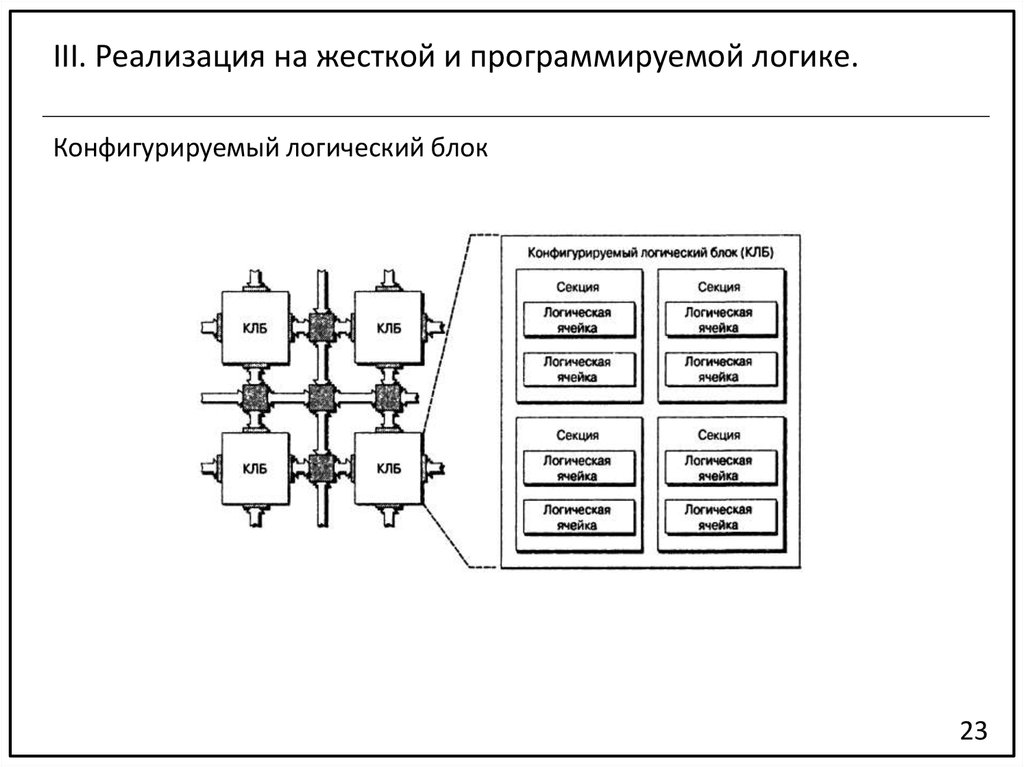

24.

III. Реализация на жесткой и программируемой логике.Конфигурируемый логический блок

23

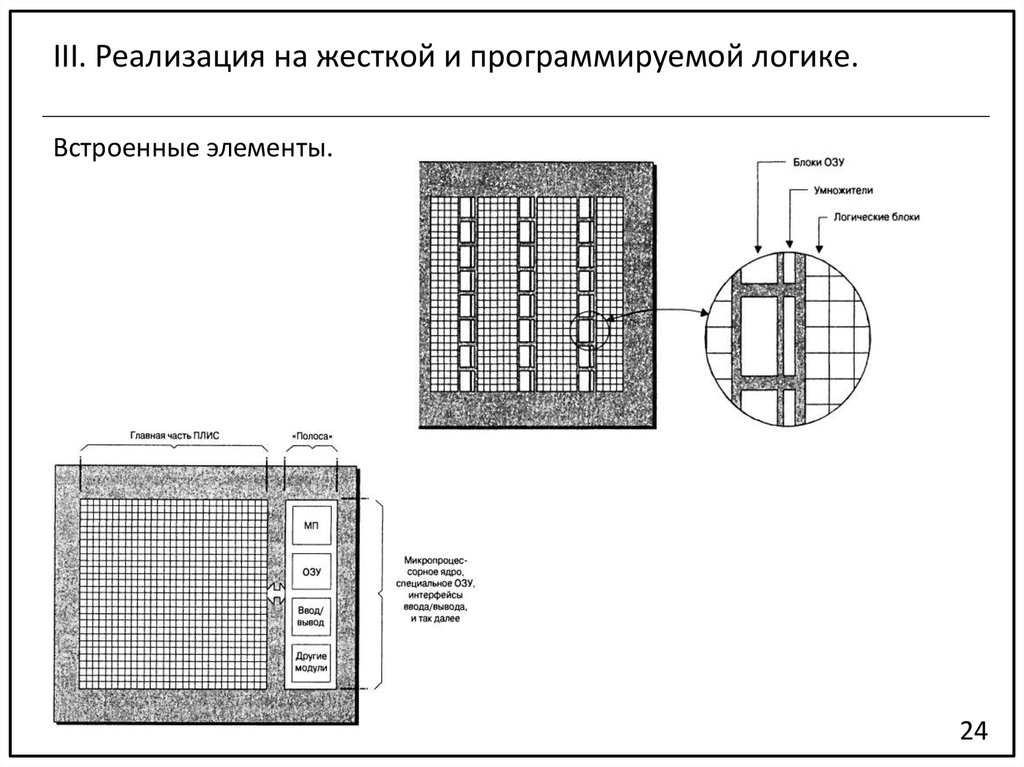

25.

III. Реализация на жесткой и программируемой логике.Встроенные элементы.

24

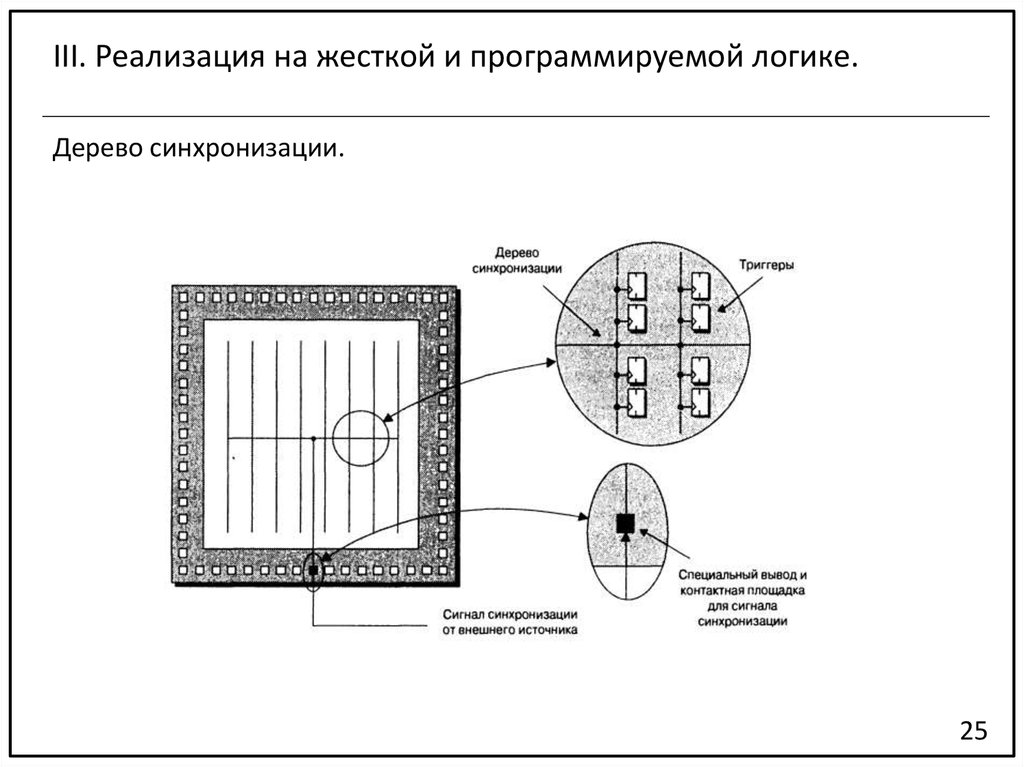

26.

III. Реализация на жесткой и программируемой логике.Дерево синхронизации.

25

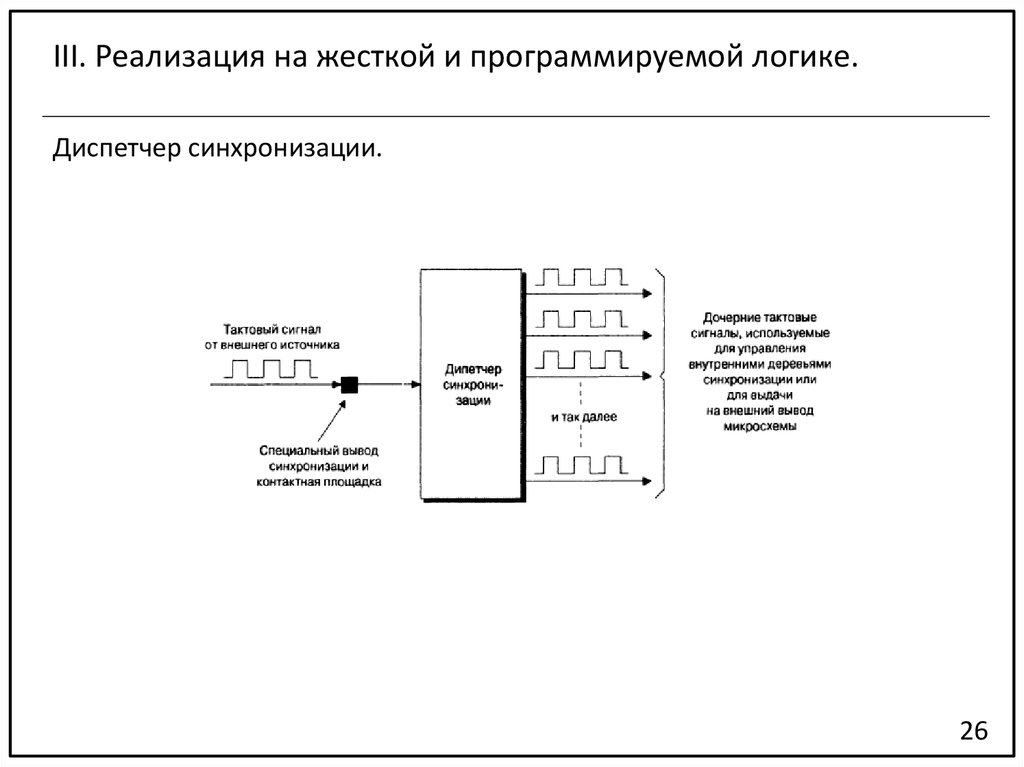

27.

III. Реализация на жесткой и программируемой логике.Диспетчер синхронизации.

26

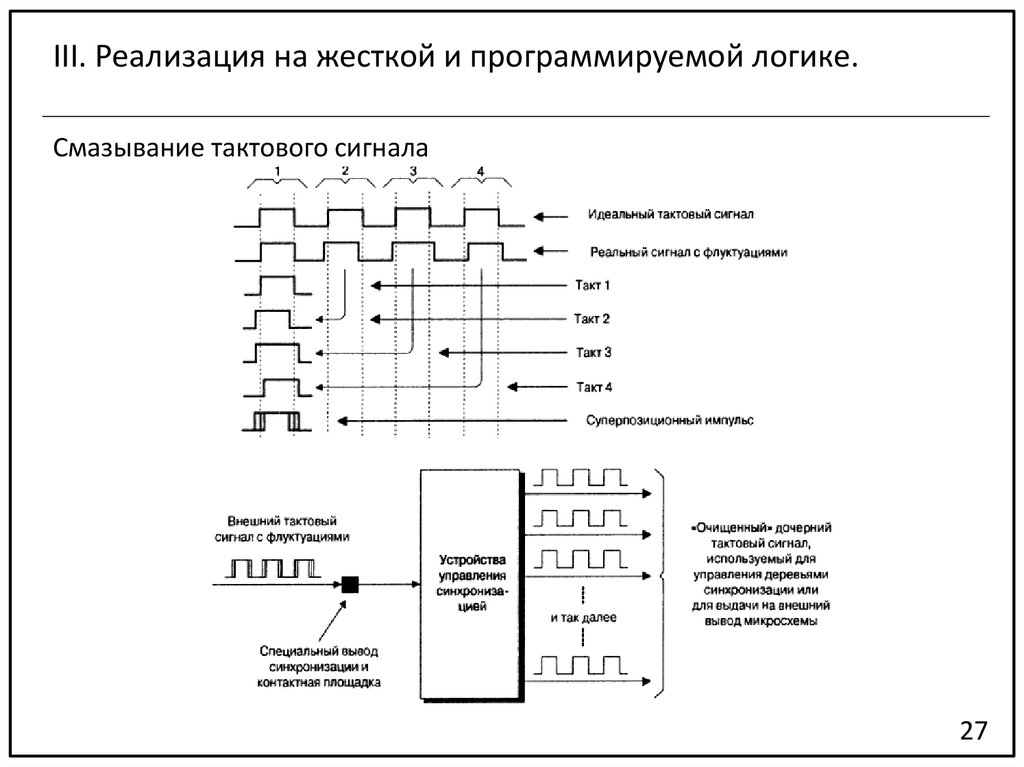

28.

III. Реализация на жесткой и программируемой логике.Смазывание тактового сигнала

27

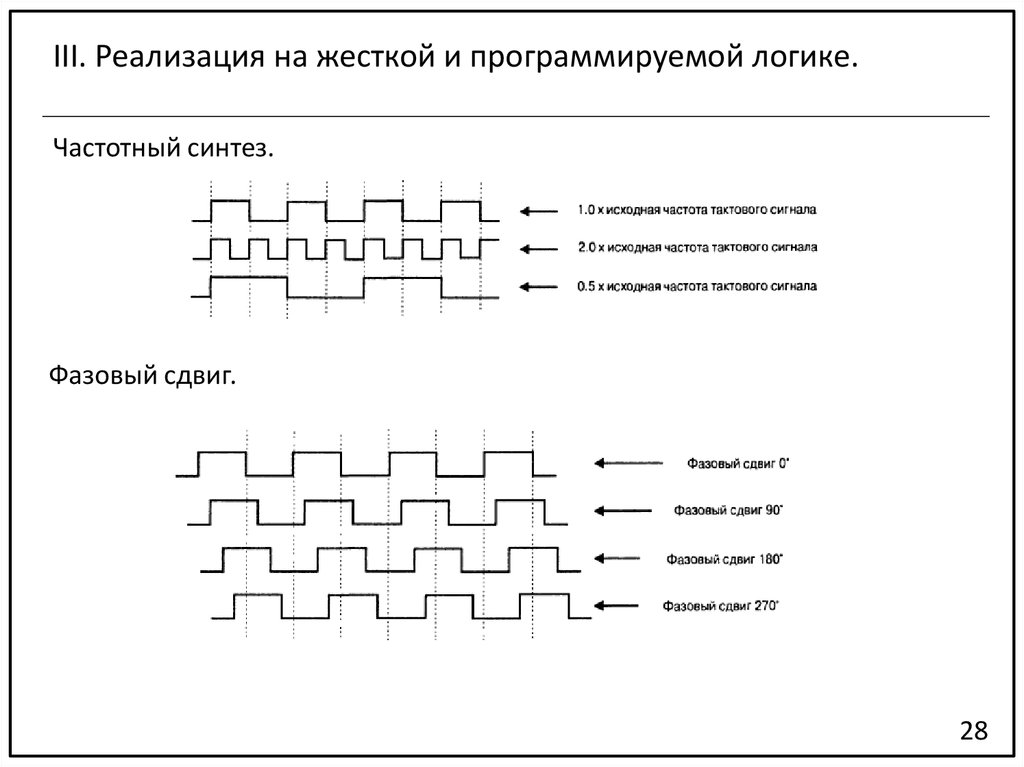

29.

III. Реализация на жесткой и программируемой логике.Частотный синтез.

Фазовый сдвиг.

28

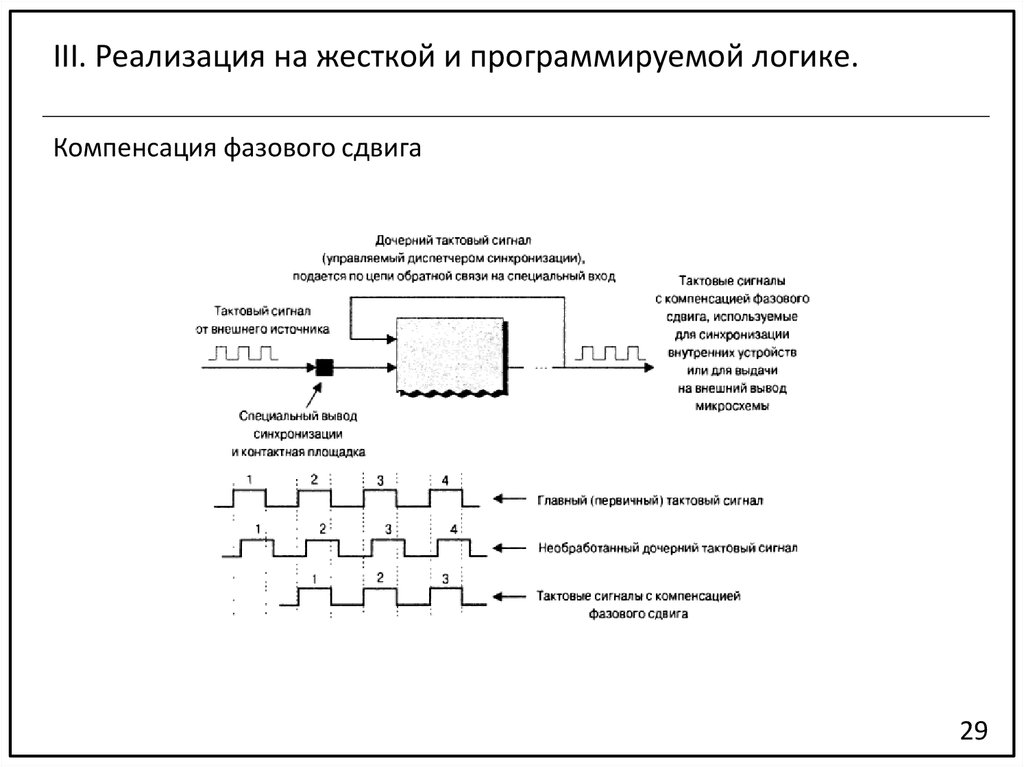

30.

III. Реализация на жесткой и программируемой логике.Компенсация фазового сдвига

29

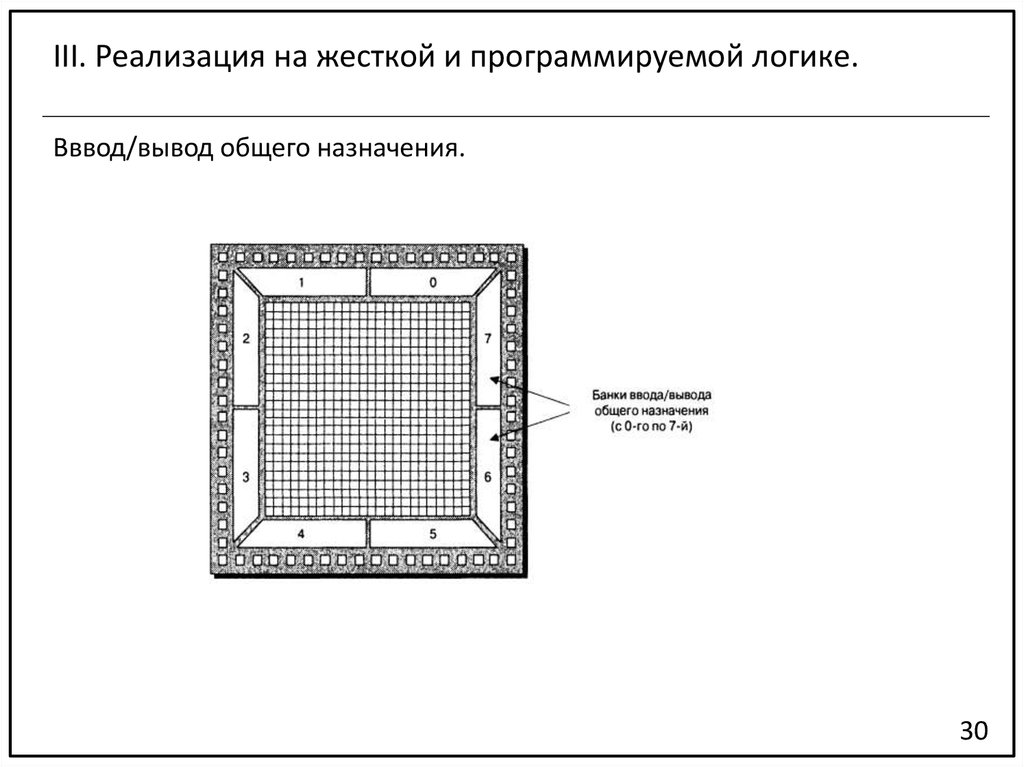

31.

III. Реализация на жесткой и программируемой логике.Вввод/вывод общего назначения.

30

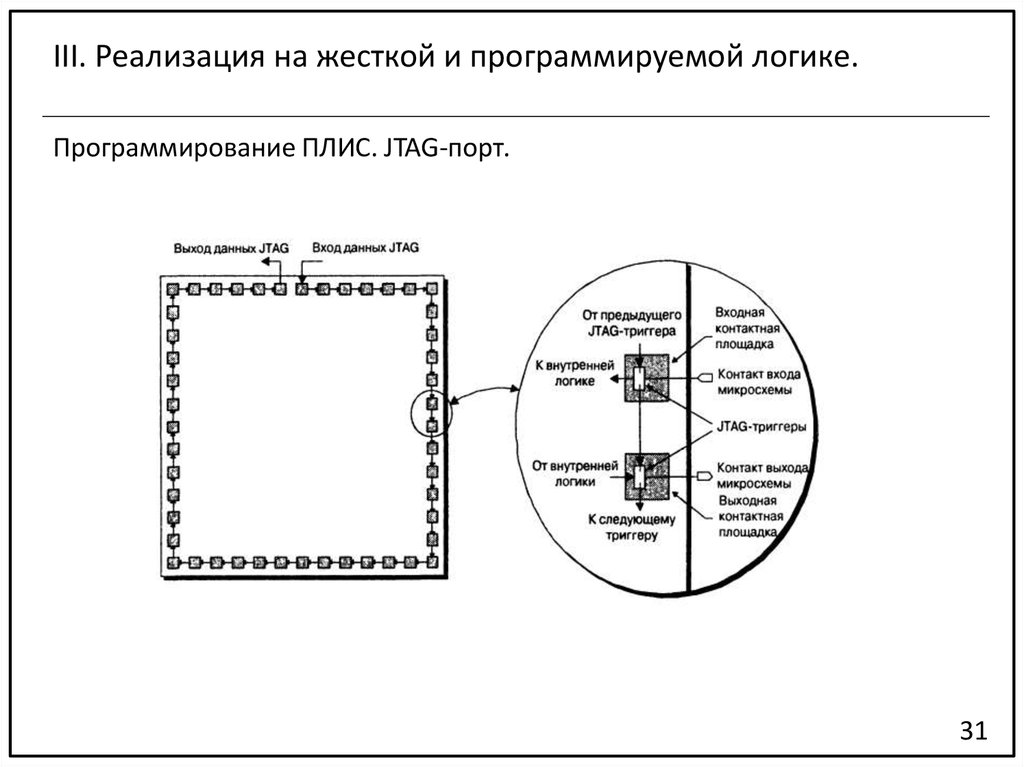

32.

III. Реализация на жесткой и программируемой логике.Программирование ПЛИС. JTAG-порт.

31

33.

III. Реализация на жесткой и программируемой логике.Программирование ПЛИС. JTAG-порт.

32

34.

Московский Авиационный Институт(Национальный Исследовательский Университет)

31

programming

programming