Similar presentations:

Обзор программируемых логических интегральных схем и интегральных схем гибкой логики

1. Обзор программируемых логических интегральных схем и интегральных схем гибкой логики

Программируемая памятьИнтерфейс

программирования

Входные

сигналы

Управляющие

сигналы

Матрица

вентилей

“И”

Элементы

“ИЛИ”

Выходные

макроячейки

Выходные

сигналы

Рис. 1.1

При этом учитывается тот

факт, что любое

логическое выражение

может быть преобразовано

в эквивалентную форму

логической суммы

произведений

(минимальной

дизьюнктивной нормальной

формы МДНФ) [5] и таким

образом реализовано на

основе архитектуры матриц

элементов "И" и "ИЛИ".

2. Интерфейс программирования и тестирования JTAG/IEEE 1149.1

TDITDO

TDI

TDO

TCK TMS

TCK TMS

TCK TMS

TCK TMS

TDO TDI

TDO TDI

TDO

TCK

TMS

TDI

Рис. 1.2 Соединение 4 БИС интерфейсом тестирования.

При этом регистры интерфейса в БИС образуют соединяющими их

информационными сигналами TDI и TDO единый последовательный

однонаправленный сдвиговый регистр, а управляющий и сигнал

синхронизации являются обычными параллельно подсоединяемыми к БИС

сигналами.

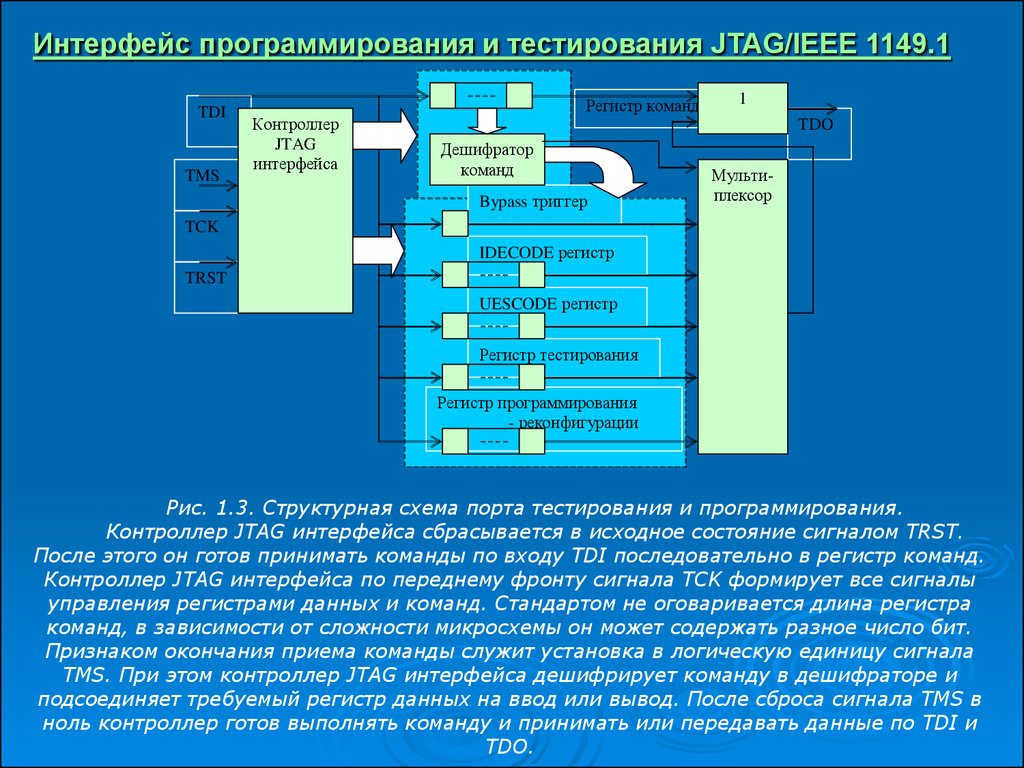

Порт тестирования и программирования в каждой БИС управляется

контроллером JTAG интерфейса. Структурная схема порта тестирования и

программирования показана на рис. 1.3.

3. Интерфейс программирования и тестирования JTAG/IEEE 1149.1

TDITMS

Контроллер

JTAG

интерфейса

Регистр команд

1

TDO

Дешифратор

команд

Bypass триггер

Мультиплексор

TCK

IDECODE регистр

TRST

UESCODE регистр

Регистр тестирования

Регистр программирования

- реконфигурации

Рис. 1.3. Структурная схема порта тестирования и программирования.

Контроллер JTAG интерфейса сбрасывается в исходное состояние сигналом TRST.

После этого он готов принимать команды по входу TDI последовательно в регистр команд.

Контроллер JTAG интерфейса по переднему фронту сигнала TCK формирует все сигналы

управления регистрами данных и команд. Стандартом не оговаривается длина регистра

команд, в зависимости от сложности микросхемы он может содержать разное число бит.

Признаком окончания приема команды служит установка в логическую единицу сигнала

TMS. При этом контроллер JTAG интерфейса дешифрирует команду в дешифраторе и

подсоединяет требуемый регистр данных на ввод или вывод. После сброса сигнала TMS в

ноль контроллер готов выполнять команду и принимать или передавать данные по TDI и

TDO.

4. Интерфейс программирования и тестирования JTAG/IEEE 1149.1

Ячейкитестирования

Внутренняя

логика

Входные –

выходные

данные с

выводов

БИС

Контроллер JTAG интерфейса

TDI

TMS

TCK

TRST

TDO

Рис. 1.4. Ячейки периферийного тестирования.

С точки зрения контроллера JTAG интерфейса они образуют один

сдвиговый регистр для передачи данных от TDI к TDO. Для информационных

данных с выводов БИС они являются запоминающими ячейками, причем

запоминая данные, они их в то же время пропускают насквозь во (из)

внутреннюю логику и регистры БИС, не влияя на общий алгоритм работы

микросхемы.

5.

КЛАССИФИКАЦИЯ ВЫСОКОПРОИЗВОДИТЕЛЬНЫХ ЦИФРОВЫХВЫЧИСЛИТЕЛЕЙ

ОКОД

ОКМД

К

ОЗУк

УУ

ОЗУк

К

ОЗУд

УУ

Д1

ЦП

ЦП1

ОЗУд

Д

ЦПn

Дn

МКМД

К1

УУ

ОЗУк

Кn

ОЗУд

УУ

ЦП1

Д1

ЦП1

Дn

Рис. 2.1. Классификация

параллельных

архитектур

6. Векторные команды и матричная вычислительная система

ОЗУфайлов

Параллельное

устройство

управления

Скалярный

процессор

ОЗУ

1

ОЗУ

n

Коммутационная

сеть

МП

1

МП

n

Локальное

ОЗУ

Рис. 3.1

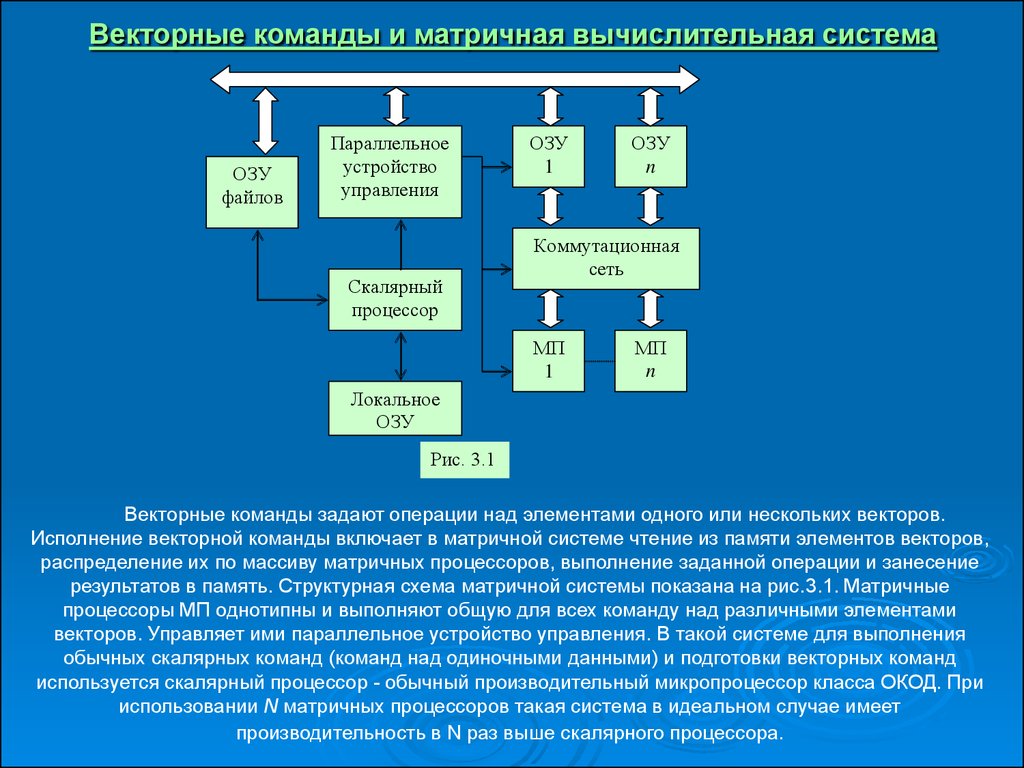

Векторные команды задают операции над элементами одного или нескольких векторов.

Исполнение векторной команды включает в матричной системе чтение из памяти элементов векторов,

распределение их по массиву матричных процессоров, выполнение заданной операции и занесение

результатов в память. Структурная схема матричной системы показана на рис.3.1. Матричные

процессоры МП однотипны и выполняют общую для всех команду над различными элементами

векторов. Управляет ими параллельное устройство управления. В такой системе для выполнения

обычных скалярных команд (команд над одиночными данными) и подготовки векторных команд

используется скалярный процессор - обычный производительный микропроцессор класса ОКОД. При

использовании N матричных процессоров такая система в идеальном случае имеет

производительность в N раз выше скалярного процессора.

7. Конвейеризация вычислений и организация векторных вычислителей класса ОКМД

таблица занятости конвейераCT1

D1

D2

D3

D4

D5

CT2

-

D1

D2

D3

D4

CT3

-

-

D1

D2

D3

CT4

-

-

-

D1

D2

t1

t2

t3

t4

t5

8. Основы проектирования аппаратных средств конвейерных вычислителей

T вычS

S

W

Рис. 3.2

Фиксатор

Логика

Фиксатор

Логика

Фиксатор

При проектировании конвейерных устройств, следует обратить внимание на

логическое проектирование логики и фиксаторов ступеней, учесть проблемы

синхронизации быстродействующих конвейеров [3].

Особенности проектирования логики ступени конвейера проиллюстрированы на

рис. 3.2.

9. Основы проектирования аппаратных средств конвейерных вычислителей

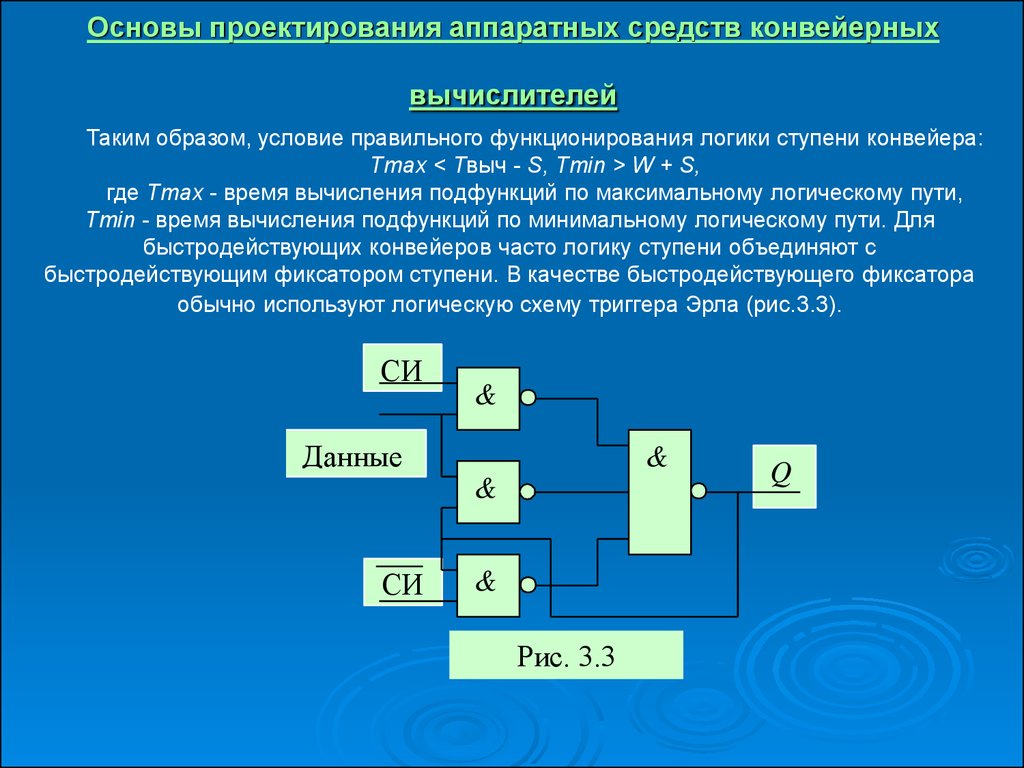

Таким образом, условие правильного функционирования логики ступени конвейера:Tmax < Tвыч - S, Tmin > W + S,

где Tmax - время вычисления подфункций по максимальному логическому пути,

Tmin - время вычисления подфункций по минимальному логическому пути. Для

быстродействующих конвейеров часто логику ступени объединяют с

быстродействующим фиксатором ступени. В качестве быстродействующего фиксатора

обычно используют логическую схему триггера Эрла (рис.3.3).

СИ

&

Данные

&

&

СИ

&

Рис. 3.3

Q

10. Основы проектирования аппаратных средств конвейерных вычислителей

Схема 1Схема 2

Схема N

Источник СИ

Рис. 3.4

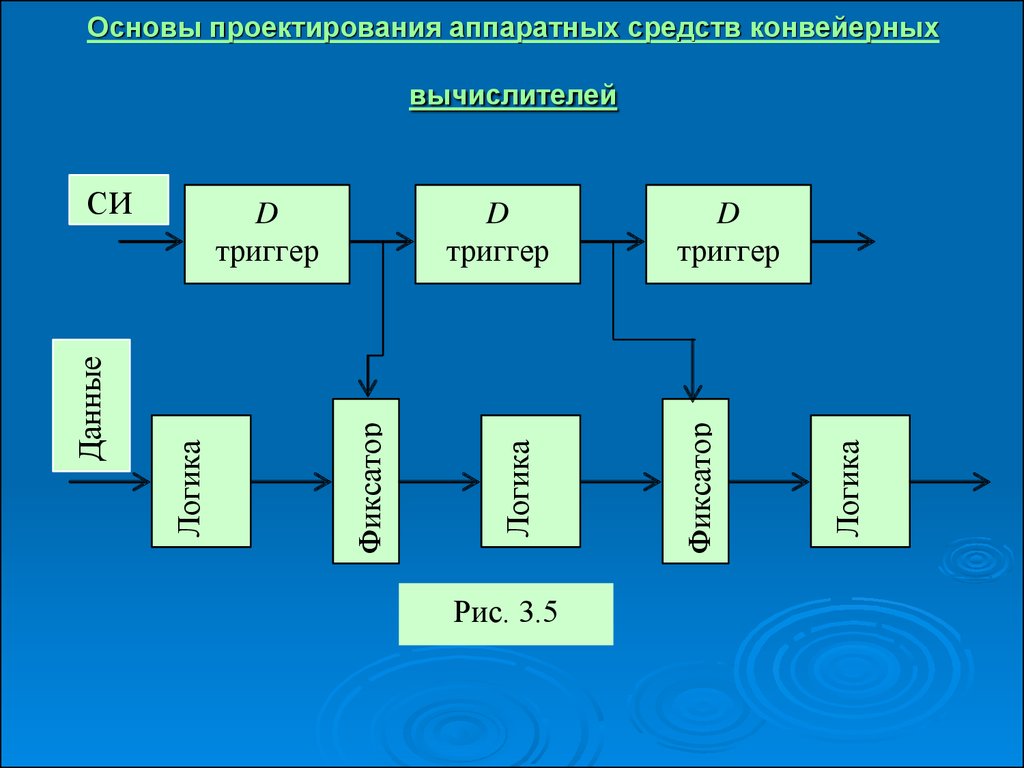

Второй метод пакетирования СИ использует временную цепь передачи, которая

включает в свой состав формирующие триггерные каскады передачи, устраняющие

перекосы при распространении СИ (рис.3.5).

Описанные выше особенности логического проектирования специализированных

конвейерных вычислителей необходимо знать разработчикам радиоэлектронной

аппаратуры, поскольку развитие высокоскоростных ПЛИС позволяет реализовать их

максимальное быстродействие только на основе таких параллельных архитектур.

11. Основы проектирования аппаратных средств конвейерных вычислителей

Рис. 3.5Логика

D

триггер

Фиксатор

Логика

D

триггер

Фиксатор

D

триггер

Логика

Данные

СИ

12. Многопроцессорные комплексы

Вычислительные алгоритмы на основе ряда слабосвязанных потоков команд иданных реализуются в многопроцессорных комплексах класса МКМД. Основное

внимание в таких комплексах уделяется синхронизации и взаимосвязи между

параллельно функционирующими вычислительными процессами на ряде МП.

Применяются в основном два механизма взаимодействия процессов:

- использование общей многопортовой оперативной памяти для организации

синхронизации и взаимодействия;

- работа по принципу обмена сообщениями процессов друг с другом через

высокоскоростные линии связи. Структурные схемы двух таких параллельных

архитектур показаны на рис. 4.1.

Общее

ОЗУ

Коммутационная сеть

Коммутационная сеть

ЦП

ЦП

ЦП

ОЗУ

ОЗУ

ЦП

Рис. 4.1

13. Многопроцессорные комплексы

Общее ОЗУКоммутационная сеть

Для снижения требований по

быстродействию к общему ОЗУ при

реализации первого механизма,

помимо общей, каждому процессору

выделяется локальная память (рис.

4.2,а). Для уменьшения сложности

коммутационной сети при реализации

второго механизма несколько МП

объединяются в группы - кластеры со

своими локальными коммутационными

сетями, переключение же таких групп

осуществляется глобальной

коммутационной сетью (рис. 4.2,б).

Локальное

ОЗУ

Локальное

ОЗУ

МП

МП

а

Глобальная

коммутационная сеть

Кластер

m

Кластер 1

Локальная

коммутационная

сеть

МП1

МПn

б

Рис. 4.2

14. Многопроцессорные комплексы

МП1Два фактора ограничивают

производительность таких комплексов:

- организация связей между

элементами комплекса, практически

каждый элемент комплекса должен

быть связан с другими, что часто не

удается реализовать в полном объеме;

- сложность организации

вычислительного процесса в

многопроцессорном комплексе при

параллельной работе нескольких

процессоров.

Существуют три основных

способа организации связей МП в

многопроцессорных вычислительных

комплексах:

- с общей разделяемой во

времени шиной (рис. 4.3,а);

- с перекрестной коммутацией

скоростных последовательных линий

связи (рис. 4.3,б);

- с многопортовым общим ОЗУ

(рис. 4.3,в).

ОЗУ1

МП2

ОЗУm

МП3

УВВ1

УВВm

а

МП1

УВВ1

МПn

УВВk

Коммутационная

матрица

ОЗУ1

ОЗУm

б

МП1

МПn

ОЗУ1

ОЗУm

Общее

ОЗУ

в

Рис. 4.3

УВВ1

УВВm

15. Вычислители, управляемые потоками данных

К архитектуре МКМД вычислителей относятся потоковые параллельныевычислители, или устройства, управляемые потоками данных. Для организации

процесса вычислений в таких архитектурах алгоритм вычислений строится в виде

графа потоков данных (рис. 4.4).

x

a

y

b

u

T слияние F

w

Рис. 4.4

p

z

16. ОРГАНИЗАЦИЯ СИСТЕМ ПАМЯТИ ВЫСОКОПРОИЗВОДИТЕЛЬНЫХ ВЫЧИСЛИТЕЛЕЙ

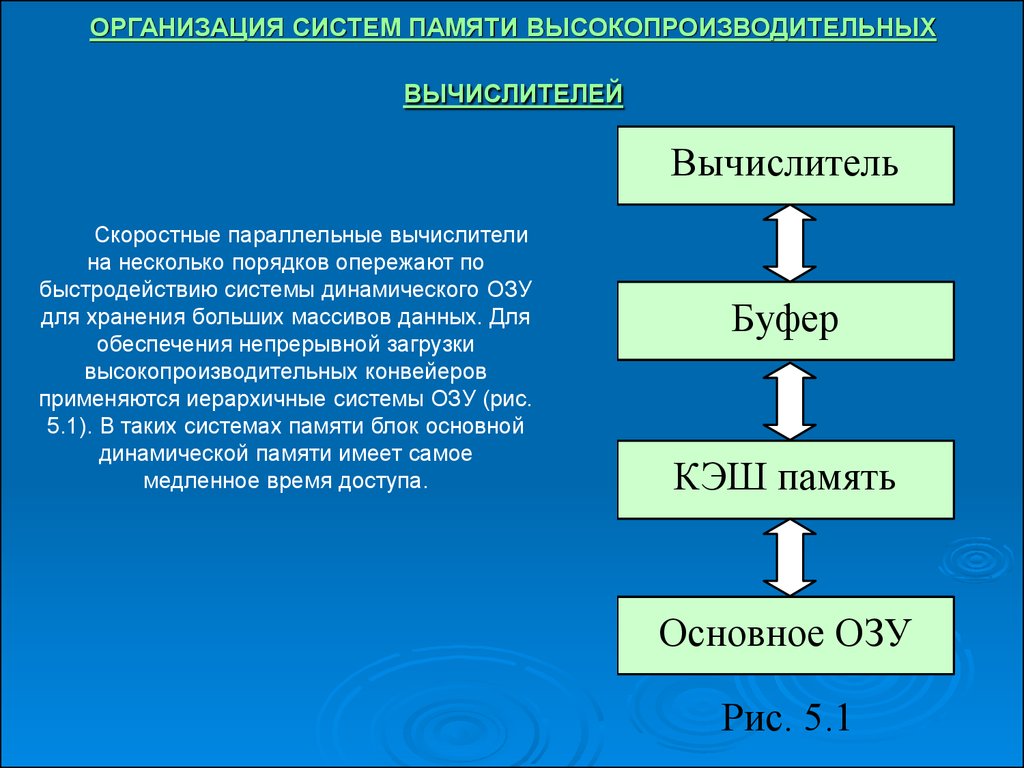

ВычислительСкоростные параллельные вычислители

на несколько порядков опережают по

быстродействию системы динамического ОЗУ

для хранения больших массивов данных. Для

обеспечения непрерывной загрузки

высокопроизводительных конвейеров

применяются иерархичные системы ОЗУ (рис.

5.1). В таких системах памяти блок основной

динамической памяти имеет самое

медленное время доступа.

Буфер

КЭШ память

Основное ОЗУ

Рис. 5.1

17. ОРГАНИЗАЦИЯ СИСТЕМ ПАМЯТИ ВЫСОКОПРОИЗВОДИТЕЛЬНЫХ ВЫЧИСЛИТЕЛЕЙ

ОРГАНИЗАЦИЯ СИСТЕМ ПАМЯТИ ВЫСОКОПРОИЗВОДИТЕЛЬНЫХДругая причина усложнения ВЫЧИСЛИТЕЛЕЙ

систем ОЗУ в

Регистр базы

высокопроизводительных

вычислителях - повышенные

Виртуальный

требования к защите данных при

адрес

многозадачном режиме работы

программы

вычислителя. Последняя

причина обусловила наличие

виртуальной адресации памяти и

Физический

адрес

соответствующей аппаратуры

преобразования виртуальных

адресов программы в

физические адреса ОЗУ, как

Схема

показано на рис. 5.2.

сравнения

Виртуальный адрес программы

всегда начинается с нулевого

Прерывание по

адреса. Он суммируется с

Адрес ОЗУ

ошибке

содержимым регистра базы,

адресации

базовый адрес которого

указывает, в какое место

Рис. 5.2

поместить программу в

физической памяти, то есть

операционная система

управляет памятью.

Регистр

границы и

защиты доступа

18. ОРГАНИЗАЦИЯ СИСТЕМ ПАМЯТИ ВЫСОКОПРОИЗВОДИТЕЛЬНЫХ ВЫЧИСЛИТЕЛЕЙ

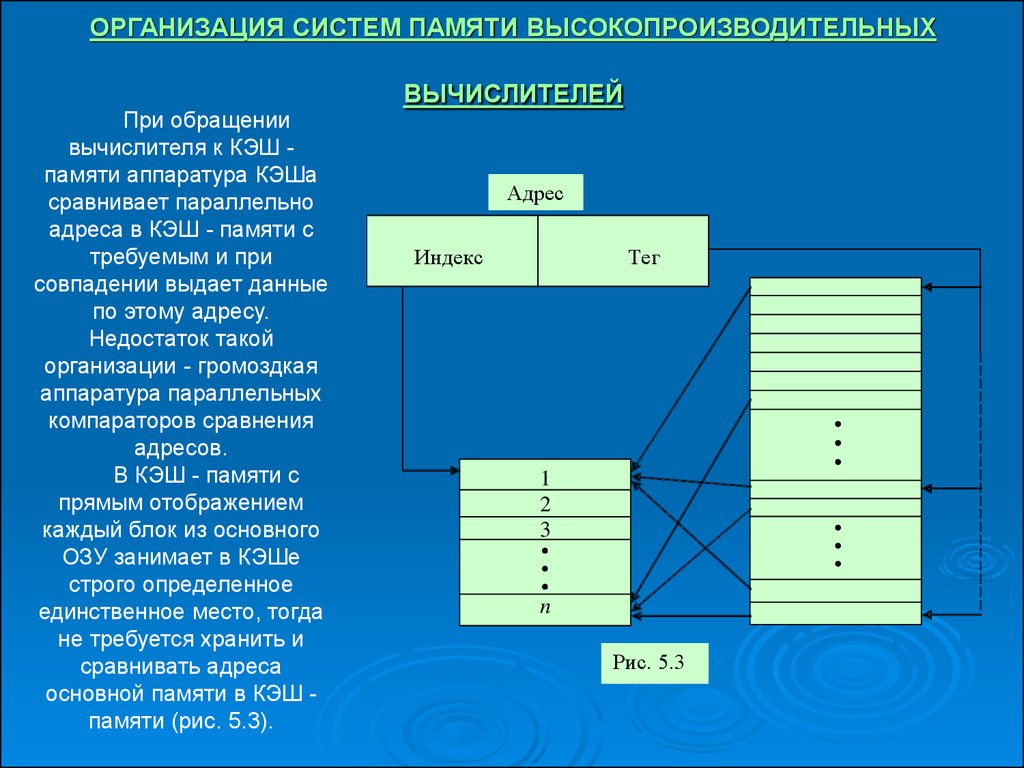

ОРГАНИЗАЦИЯ СИСТЕМ ПАМЯТИ ВЫСОКОПРОИЗВОДИТЕЛЬНЫХПри обращении

вычислителя к КЭШ памяти аппаратура КЭШа

сравнивает параллельно

адреса в КЭШ - памяти с

требуемым и при

совпадении выдает данные

по этому адресу.

Недостаток такой

организации - громоздкая

аппаратура параллельных

компараторов сравнения

адресов.

В КЭШ - памяти с

прямым отображением

каждый блок из основного

ОЗУ занимает в КЭШе

строго определенное

единственное место, тогда

не требуется хранить и

сравнивать адреса

основной памяти в КЭШ памяти (рис. 5.3).

ВЫЧИСЛИТЕЛЕЙ

Адрес

Индекс

Тег

1

2

3

n

Рис. 5.3

19. ОРГАНИЗАЦИЯ СИСТЕМ ПАМЯТИ ВЫСОКОПРОИЗВОДИТЕЛЬНЫХ ВЫЧИСЛИТЕЛЕЙ

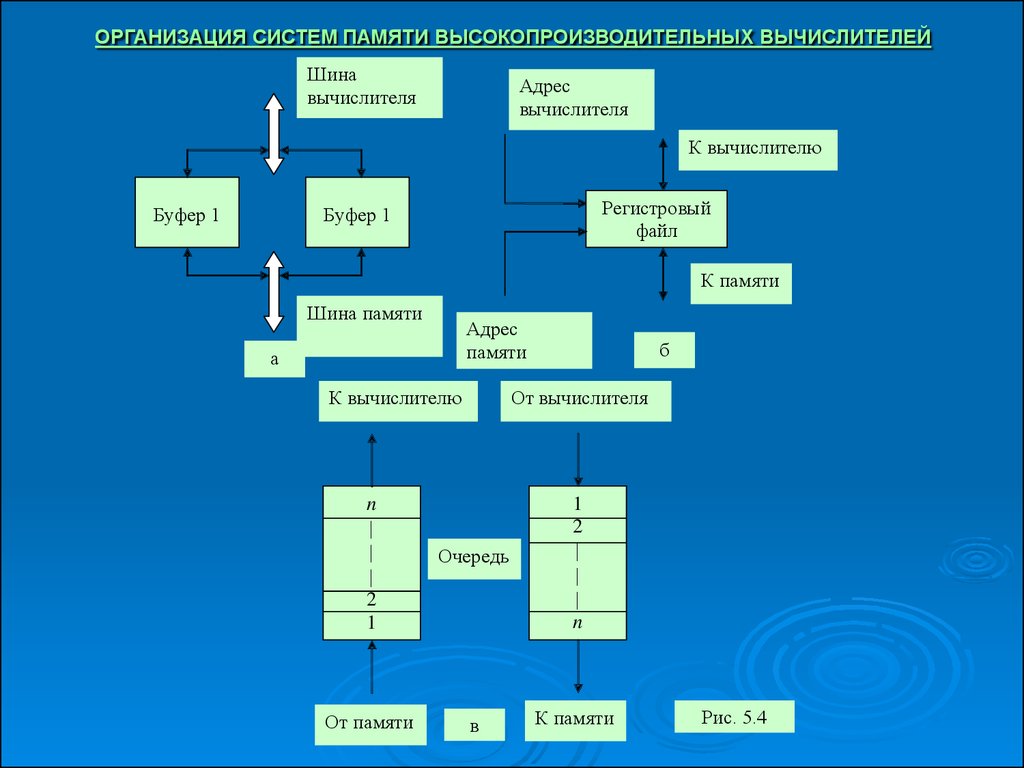

Шинавычислителя

Адрес

вычислителя

К вычислителю

Буфер 1

Регистровый

файл

Буфер 1

К памяти

Шина памяти

Адрес

памяти

а

К вычислителю

б

От вычислителя

n

2

1

Очередь

От памяти

в

1

2

n

n

К памяти

Рис. 5.4

20. Особенности архитектуры универсальных производительных микропроцессоров

Рис. 6.1 Структураисполнительных блоков

Pentium III

Буфер предсказания

ветвлений

Очередь предварительной

выборки команд

Буфер стековых

возвратов

Блок выборки команд

пакетами по 16 байт

Упорядоченный

предпроцессор

Предварительный декодер

команд

Буфер 1

16 байт

Буфер 2

16 байт

Декодер

команд 1

Декодер

команд 2

Блок переименования регистров и выделения ресурсов

Переупорядочивающий буфер чтения данных из регистров

Беспорядочное ядро

Станция резервации

Порт 0 – АЛУ U и FPU

Порт 1 – АЛУ V

Порт 3 – вычисление адреса

Порт 4 – запись

результата

Порт 2 – загрузка данных

Переупорядочивающий буфер записи результата

21. Особенности архитектуры универсальных производительных микропроцессоров

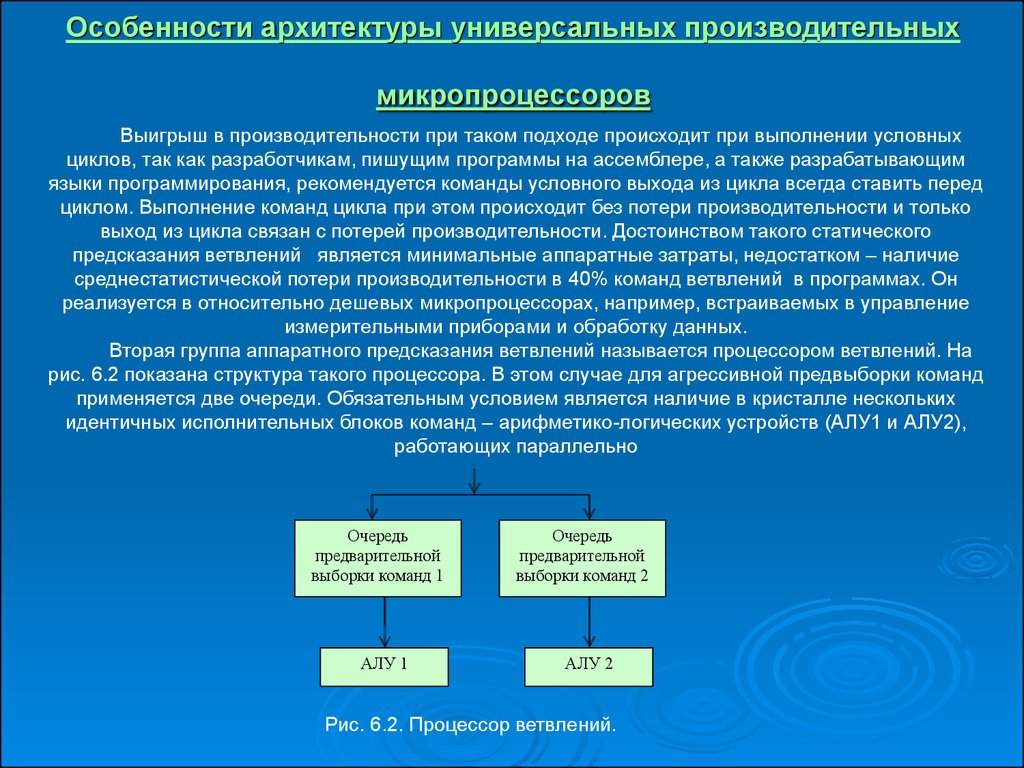

Выигрыш в производительности при таком подходе происходит при выполнении условныхциклов, так как разработчикам, пишущим программы на ассемблере, а также разрабатывающим

языки программирования, рекомендуется команды условного выхода из цикла всегда ставить перед

циклом. Выполнение команд цикла при этом происходит без потери производительности и только

выход из цикла связан с потерей производительности. Достоинством такого статического

предсказания ветвлений является минимальные аппаратные затраты, недостатком – наличие

среднестатистической потери производительности в 40% команд ветвлений в программах. Он

реализуется в относительно дешевых микропроцессорах, например, встраиваемых в управление

измерительными приборами и обработку данных.

Вторая группа аппаратного предсказания ветвлений называется процессором ветвлений. На

рис. 6.2 показана структура такого процессора. В этом случае для агрессивной предвыборки команд

применяется две очереди. Обязательным условием является наличие в кристалле нескольких

идентичных исполнительных блоков команд – арифметико-логических устройств (АЛУ1 и АЛУ2),

работающих параллельно

Очередь

предварительной

выборки команд 1

АЛУ 1

Очередь

предварительной

выборки команд 2

АЛУ 2

Рис. 6.2. Процессор ветвлений.

22. Особенности архитектуры универсальных производительных микропроцессоров

. Пока отсутствуют команды ветвлений, последовательность команд загружается в первуюочередь. При появлении команды ветвления команды прямой ветки загружаются в первую очередь, а

команды обратной ветки загружаются во вторую очередь. До вычисления ветвления в двух АЛУ

выполняются команды прямой и обратной ветки параллельно. После вычисления ветвления

принимается результат выполнения команд соответствующей ветки – той, куда нужно было перейти, а

второй результат отбрасывается и далее выполняются команды из соответствующей очереди.

Появление следующих команд ветвления вызывает использование двух очередей. Достоинством

такого подхода является отсутствие потери производительности независимо от результата ветвления.

Недостаток применения процессора ветвлений – существенные аппаратные затраты, поэтому такой

подход используется только в дорогостоящих производительных процессорах, например, рабочих

станций фирмы SUN.

Третьим видом аппаратуры предсказания ветвлений является динамическое предсказание

ветвлений (рис. 6.3).

Рис. 6.3.

Динамическое

предсказание

ветвлений.

Буфер

предсказания

ветвлений

Очередь

предварительной

выборки команд

Дешифратор

команд

Исполнительные

блоки

23. Цифровые сигнальные процессоры.

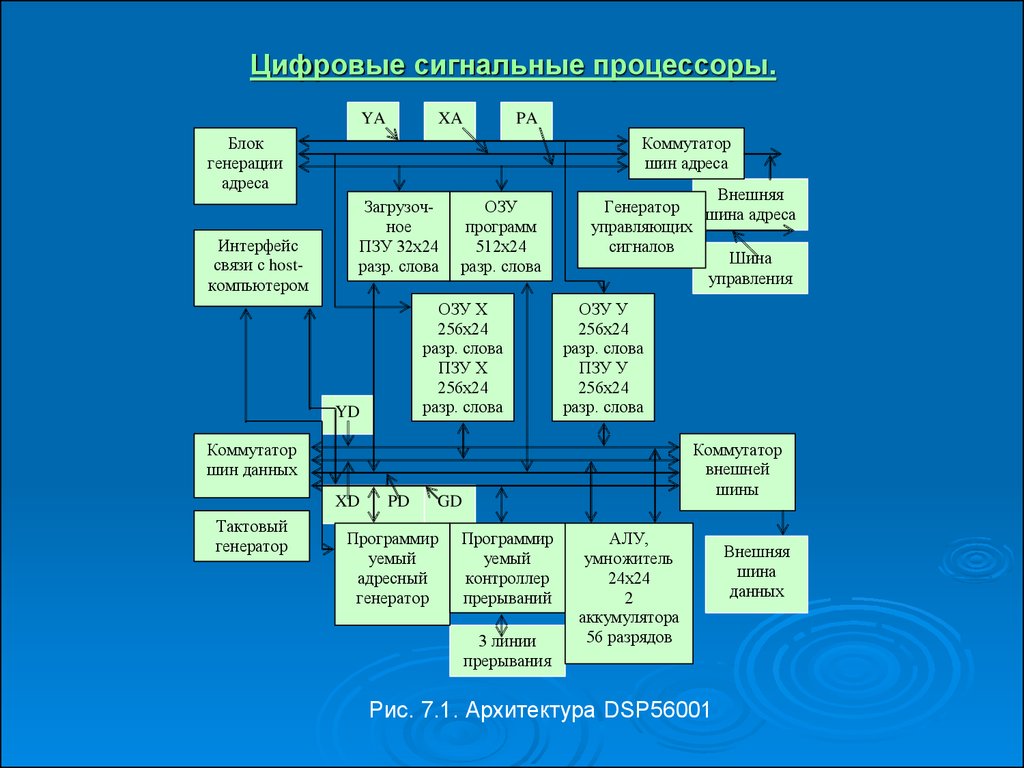

YAXA

PA

Блок

генерации

адреса

Интерфейс

связи с hostкомпьютером

Коммутатор

шин адреса

Загрузочное

ПЗУ 32х24

разр. слова

ОЗУ

программ

512х24

разр. слова

ОЗУ Х

256х24

разр. слова

ПЗУ Х

256х24

разр. слова

YD

Внешняя

Генератор

шина адреса

управляющих

сигналов

Шина

управления

ОЗУ У

256х24

разр. слова

ПЗУ У

256х24

разр. слова

Коммутатор

шин данных

XD

Тактовый

генератор

PD

Коммутатор

внешней

шины

GD

Программир

уемый

адресный

генератор

Программир

уемый

контроллер

прерываний

3 линии

прерывания

АЛУ,

умножитель

24х24

2

аккумулятора

56 разрядов

Рис. 7.1. Архитектура DSP56001

Внешняя

шина

данных

24. Цифровые сигнальные процессоры.

ПЗУ16Кх32

разр. слов

КЭШ-ОЗУ

команд

512х32

разр. слов

ОЗУ Х

1024х32

разр. слов

Буфер

шины

X

Шины адреса и данных X и Y

Умножитель и

АЛУ целых и

плавающей

точки

12 40разрядных

регистров

2 адресных

генератора

14 32разрядных

регистров

Шина

вводавывода

Таймер 1

Таймер 2

ОЗУ У

1024х32

разр. слов

Блок

анализа и

маршрутиз

ации

Буфер

Буфер

шины

Y

Порт 0

сопроцессор

ПДП

канал 0

канал 1

канал 2

канал 3

канал 4

канал 5

Порт 1

Порт 2

Порт 3

Порт 4

Порт 5

Рис. 7.2. Архитектура TMS320C40

25. Цифровые сигнальные процессоры.

На рис. 7.3 показан вариант топологии связей процессоров.Рис. 7.3. Топология связей ЦСП

26. Цифровые сигнальные процессоры.

Рис. 7.4. Процессразработки аппаратуры на ЦСП и

ПЛИС

Написание программы

обработки на языке С

Написание на ассемблере

критических участков

программы

Компиляция программы

Правка программы на

ассемблере

Ассемблирование

Объектные файлы

Построение выполняемого

кода

Программный отладчик на

персональном компьютере

(симуляция)

Отладка с помощью платы

эмулятора с ЦСП

Проектирование стандартных

портов ввода – вывода

выбором спец. БИС

Проектирование аппаратной

поддержки в

программируемой логике

Разработка платы с ЦСП,

спец. БИС и ПЛИС

Программная эмуляция

ввода – вывода сигналов

Подпрограммы-таймеры

для подсчета времени

выполнения ветвей

программы

Имитация сигналов через

порты эмулятора

Окончательная отладка программы и

аппаратуры на плате

programming

programming