Similar presentations:

Тема 4. Обработка информации

1.

Санкт-Петербургский государственный электротехническийуниверситет «ЛЭТИ»

Факультет электротехники и автоматики

Информатика

Тема 4. Обработка информации

Шевченко Алексей Владимирович

Кафедра РАПС

Санкт-Петербург, 2024 г.

2.

Обработка информации в компьютерных системахЧисла

Изображения

13

Звук

Текст

Абв

Данные

Графика

Видео

Обработка информации в компьютерных системах заключается в

выполнении операций над данными, которые эту информацию

представляют. При этом, основными процессами обработки

информации являются создание, изменение и удаление данных.

Шевченко А. В.

Информатика. Тема 4. Обработка информации

2

3.

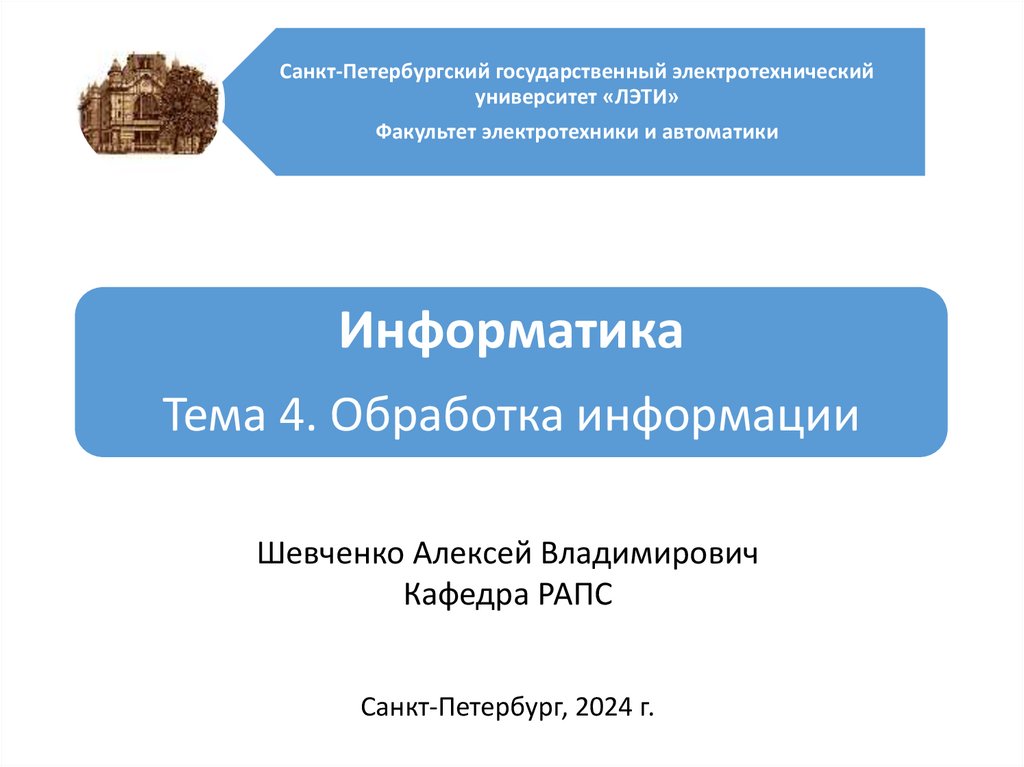

Пример обработки числовой информации№

Наименование

Количество

Цена

Стоимость

1

Лента для хомута

60

41.25

2475.00

2

Зажим для хомута

150

31.42

4713.00

3

Заклёпка глухая 4.0х15

1000

4.31

4310.00

4

Винт М4х20

340

0.98

333.20

Итого

1550

11831.20

Обработка числовой информации, как правило, заключается в

выполнении арифметических или математических действий над

данными, представленными в виде целых чисел и чисел с плавающей

точкой.

Шевченко А. В.

Информатика. Тема 4. Обработка информации

3

4.

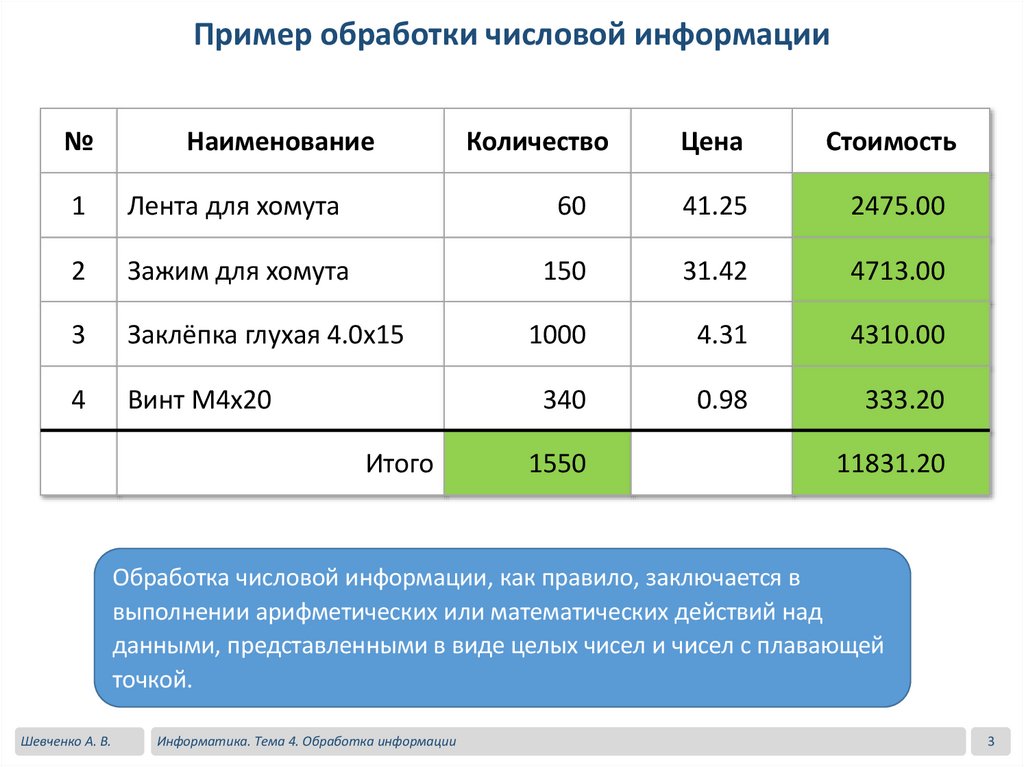

Пример обработки текстаР о д и л с я

Р о д и л с я

н а

н а

б р е г а х

б р е г а х

н е в ы

,

Н е в ы ,

Обработка текста, как правило, связана с перестановкой или заменой

символов. Поскольку символы представляются целыми числами, то

здесь задействуется, главным образом, арифметика целых чисел.

Шевченко А. В.

Информатика. Тема 4. Обработка информации

4

5.

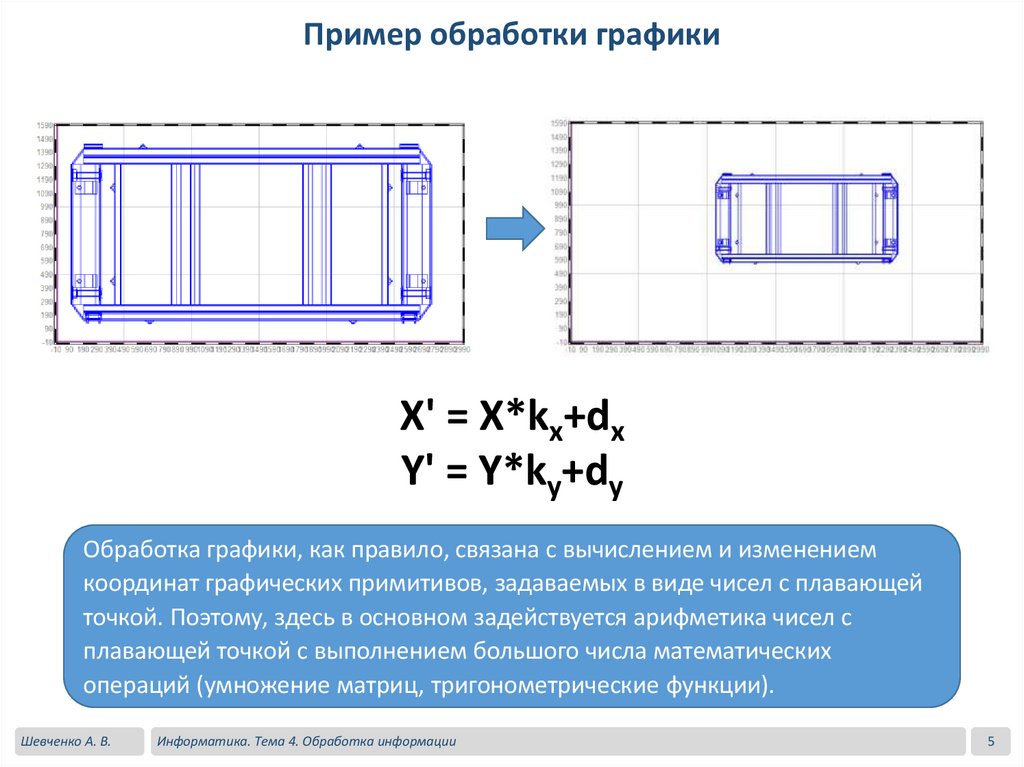

Пример обработки графикиX' = X*kx+dx

Y' = Y*ky+dy

Обработка графики, как правило, связана с вычислением и изменением

координат графических примитивов, задаваемых в виде чисел с плавающей

точкой. Поэтому, здесь в основном задействуется арифметика чисел с

плавающей точкой с выполнением большого числа математических

операций (умножение матриц, тригонометрические функции).

Шевченко А. В.

Информатика. Тема 4. Обработка информации

5

6.

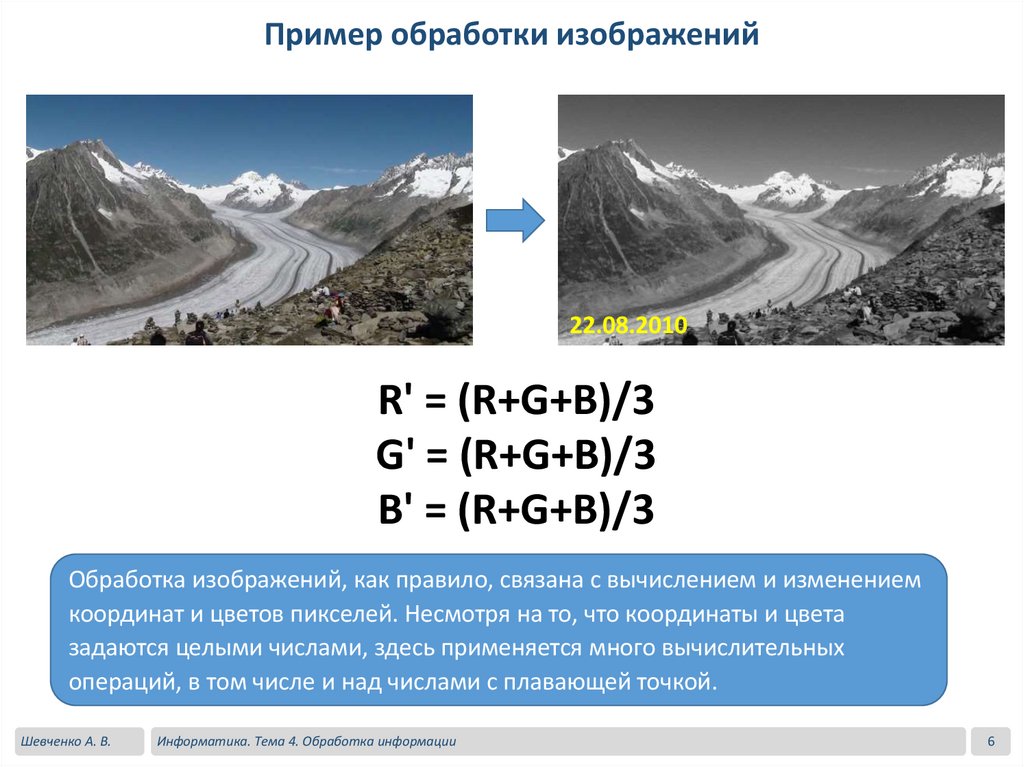

Пример обработки изображений22.08.2010

R' = (R+G+B)/3

G' = (R+G+B)/3

B' = (R+G+B)/3

Обработка изображений, как правило, связана с вычислением и изменением

координат и цветов пикселей. Несмотря на то, что координаты и цвета

задаются целыми числами, здесь применяется много вычислительных

операций, в том числе и над числами с плавающей точкой.

Шевченко А. В.

Информатика. Тема 4. Обработка информации

6

7.

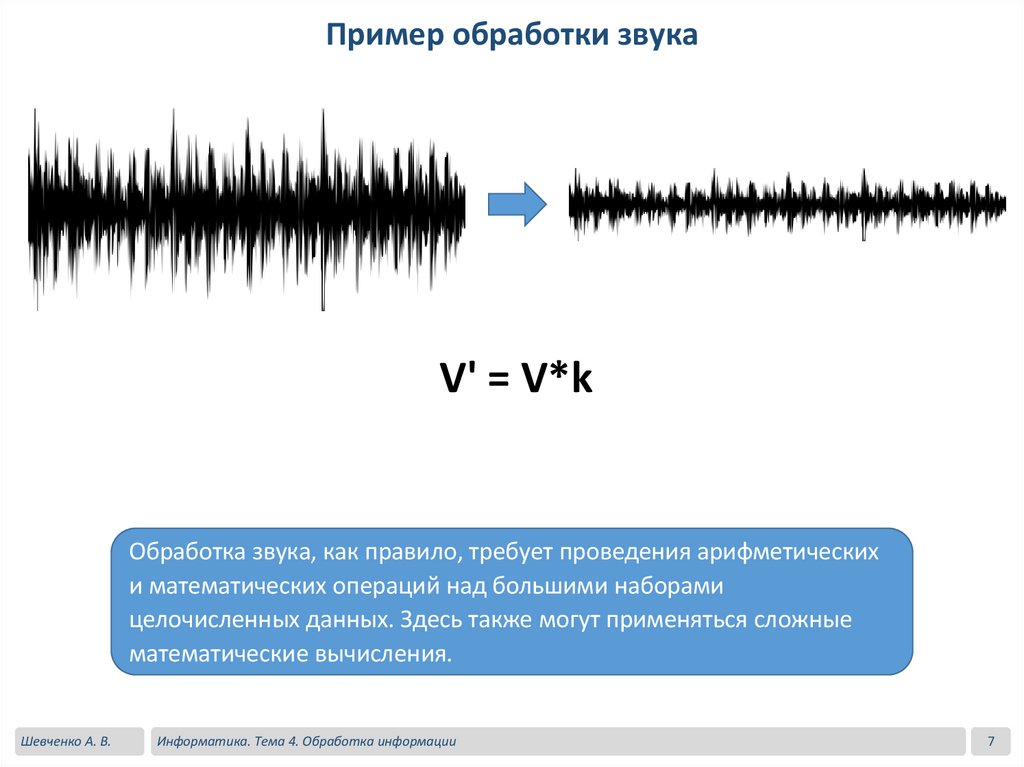

Пример обработки звукаV' = V*k

Обработка звука, как правило, требует проведения арифметических

и математических операций над большими наборами

целочисленных данных. Здесь также могут применяться сложные

математические вычисления.

Шевченко А. В.

Информатика. Тема 4. Обработка информации

7

8.

Пример обработки видеоОбработка видео, особенно в реальном времени, требует больших

вычислительных ресурсов. Это связано как с объемами данных, так и с

динамикой их изменения. Характерным примером являются задачи

распознавания образов и управления движущимися объектами.

Шевченко А. В.

Информатика. Тема 4. Обработка информации

8

9.

Архитектура компьютерных системОбработка

данных

Хранение

данных

Ввод/вывод

данных

Архитектура компьютера – это модель компьютерной системы, воплощённая в

её компонентах, их взаимодействии между собой и окружением, включающая

также принципы её проектирования и развития.

Шевченко А. В.

Информатика. Тема 4. Обработка информации

9

10.

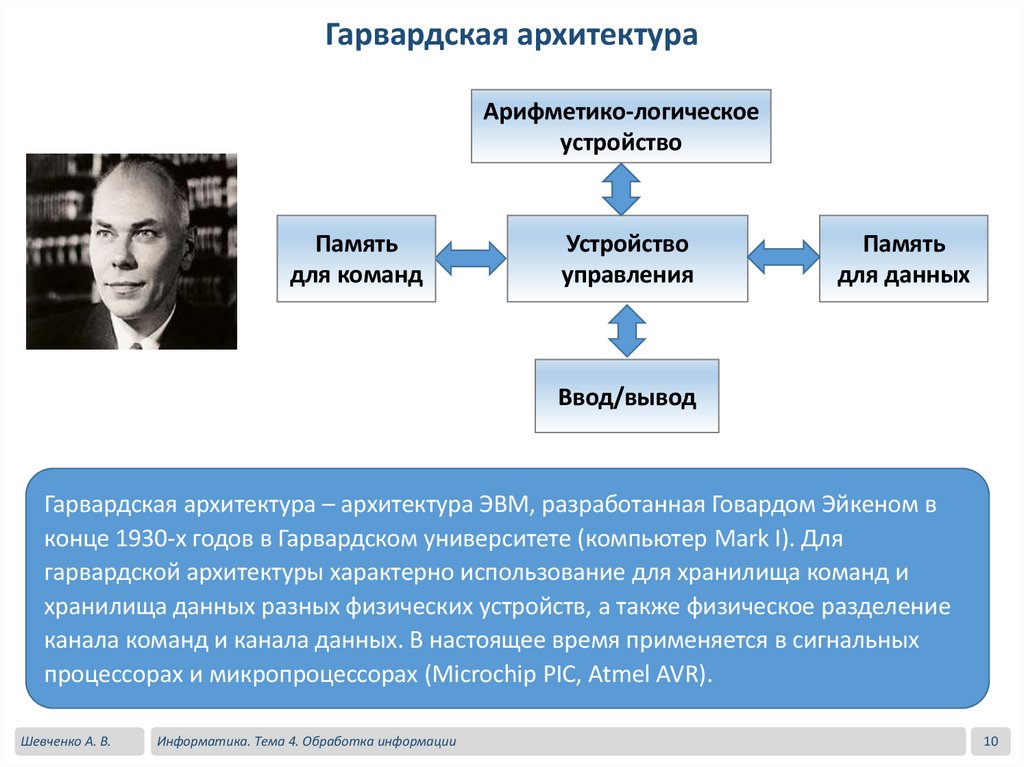

Гарвардская архитектураАрифметико-логическое

устройство

Память

для команд

Устройство

управления

Память

для данных

Ввод/вывод

Гарвардская архитектура – архитектура ЭВМ, разработанная Говардом Эйкеном в

конце 1930-х годов в Гарвардском университете (компьютер Mark I). Для

гарвардской архитектуры характерно использование для хранилища команд и

хранилища данных разных физических устройств, а также физическое разделение

канала команд и канала данных. В настоящее время применяется в сигнальных

процессорах и микропроцессорах (Microchip PIC, Atmel AVR).

Шевченко А. В.

Информатика. Тема 4. Обработка информации

10

11.

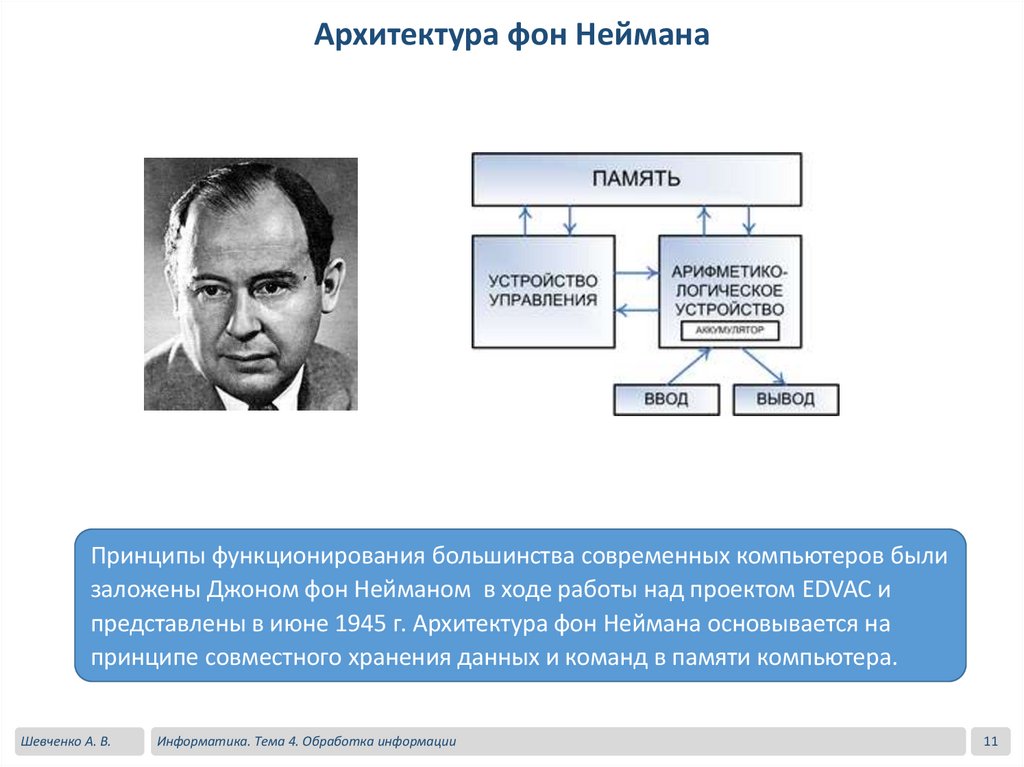

Архитектура фон НейманаПринципы функционирования большинства современных компьютеров были

заложены Джоном фон Нейманом в ходе работы над проектом EDVAC и

представлены в июне 1945 г. Архитектура фон Неймана основывается на

принципе совместного хранения данных и команд в памяти компьютера.

Шевченко А. В.

Информатика. Тема 4. Обработка информации

11

12.

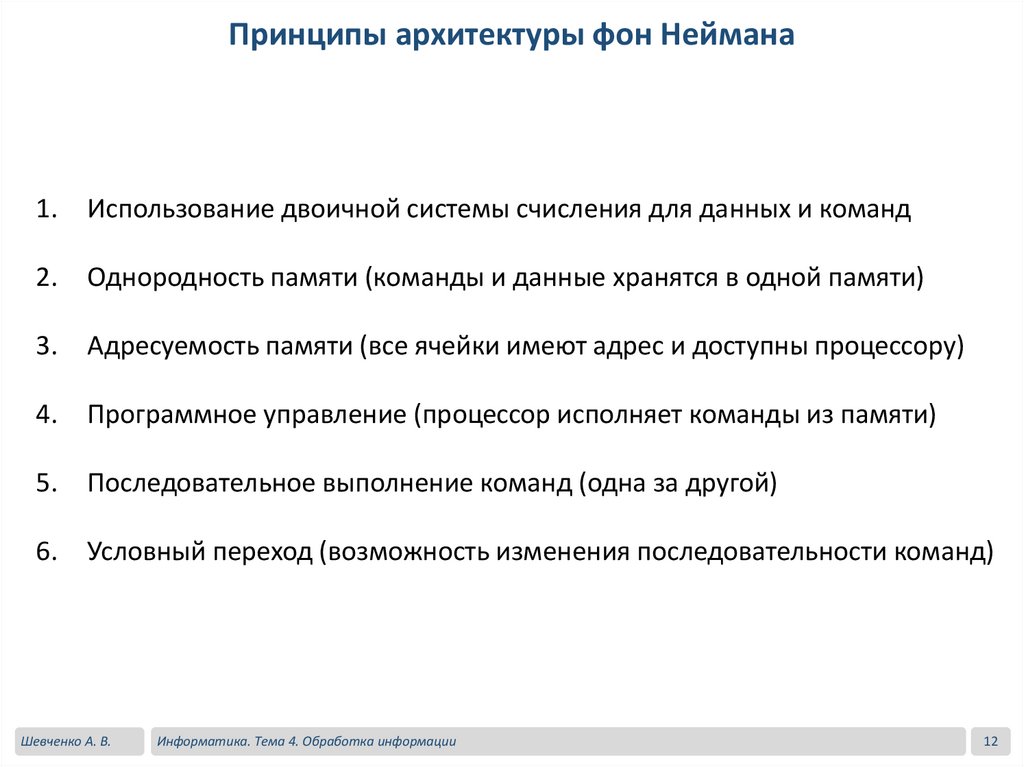

Принципы архитектуры фон Неймана1.

Использование двоичной системы счисления для данных и команд

2.

Однородность памяти (команды и данные хранятся в одной памяти)

3.

Адресуемость памяти (все ячейки имеют адрес и доступны процессору)

4.

Программное управление (процессор исполняет команды из памяти)

5.

Последовательное выполнение команд (одна за другой)

6.

Условный переход (возможность изменения последовательности команд)

Шевченко А. В.

Информатика. Тема 4. Обработка информации

12

13.

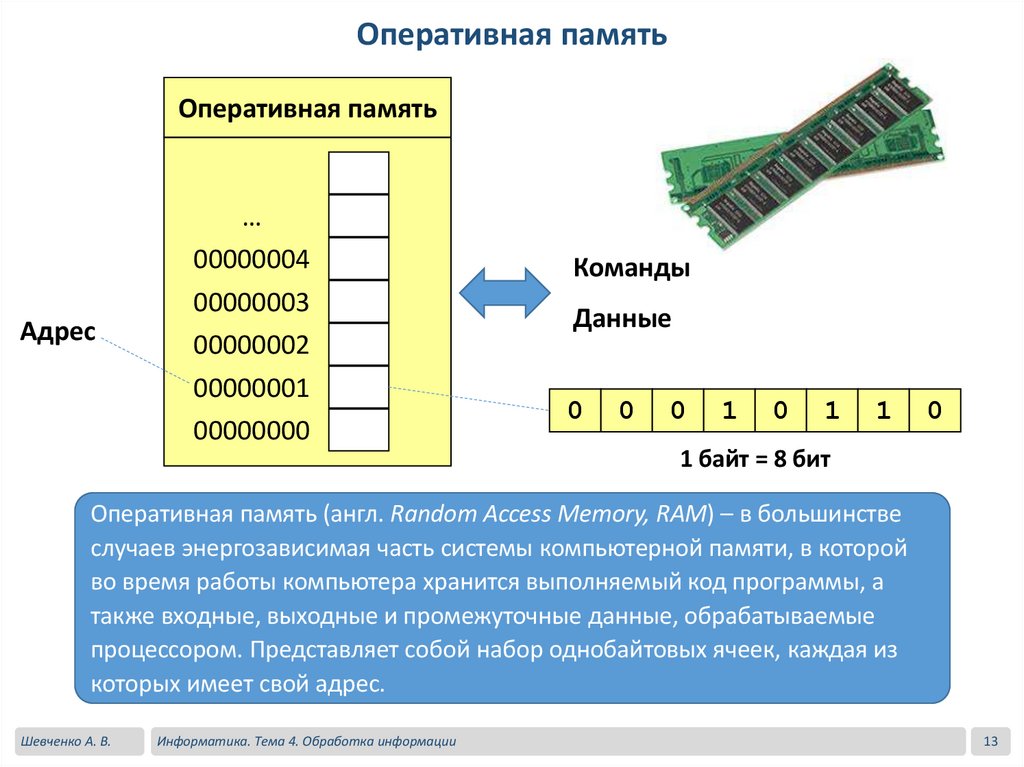

Оперативная памятьОперативная память

Адрес

…

00000004

00000003

00000002

00000001

00000000

Команды

Данные

0

0

0

1

0

1

1

0

1 байт = 8 бит

Оперативная память (англ. Random Access Memory, RAM) – в большинстве

случаев энергозависимая часть системы компьютерной памяти, в которой

во время работы компьютера хранится выполняемый код программы, а

также входные, выходные и промежуточные данные, обрабатываемые

процессором. Представляет собой набор однобайтовых ячеек, каждая из

которых имеет свой адрес.

Шевченко А. В.

Информатика. Тема 4. Обработка информации

13

14.

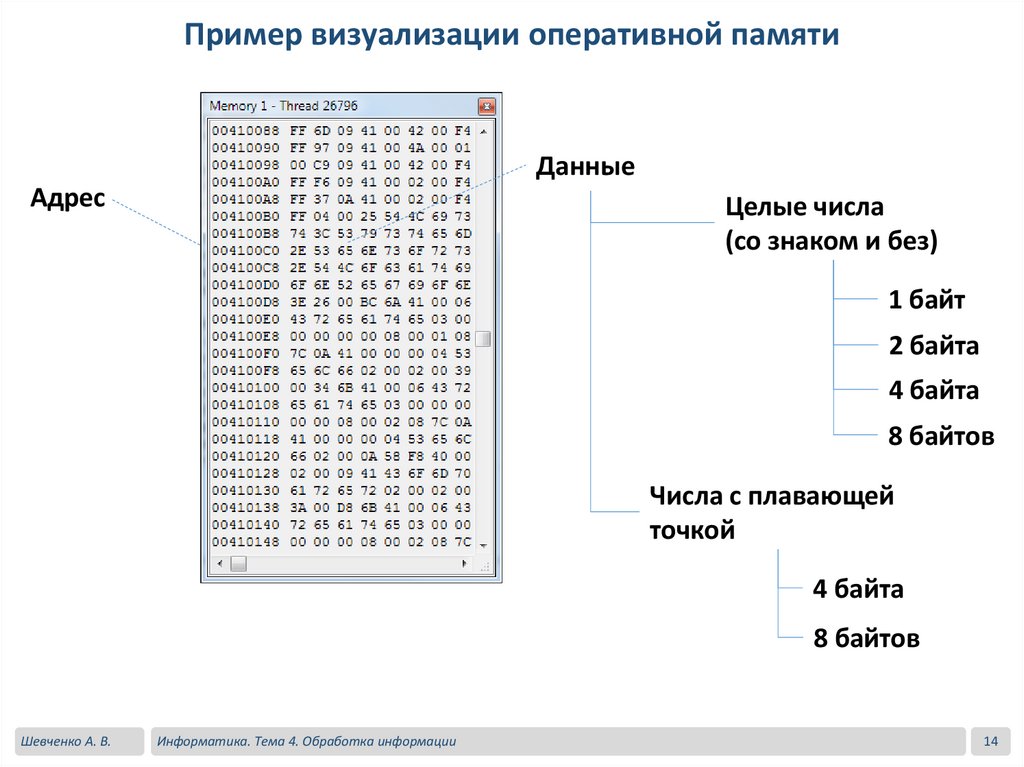

Пример визуализации оперативной памятиДанные

Адрес

Целые числа

(со знаком и без)

1 байт

2 байта

4 байта

8 байтов

Числа с плавающей

точкой

4 байта

8 байтов

Шевченко А. В.

Информатика. Тема 4. Обработка информации

14

15.

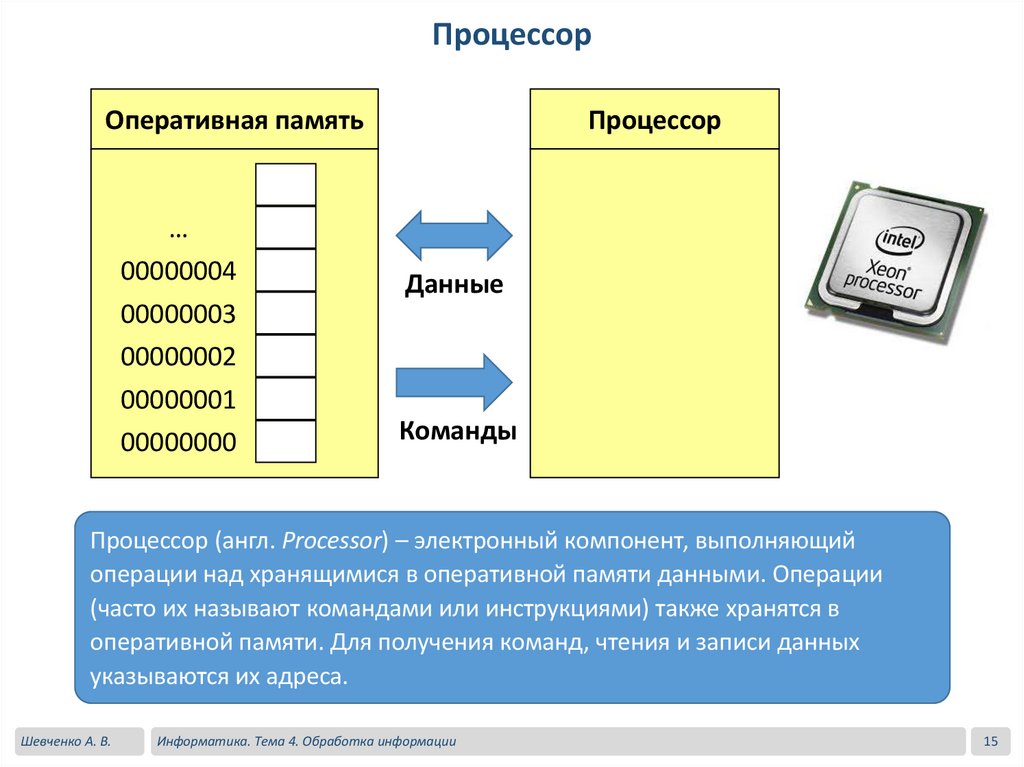

ПроцессорОперативная память

…

00000004

00000003

00000002

00000001

00000000

Процессор

Данные

Команды

Процессор (англ. Processor) – электронный компонент, выполняющий

операции над хранящимися в оперативной памяти данными. Операции

(часто их называют командами или инструкциями) также хранятся в

оперативной памяти. Для получения команд, чтения и записи данных

указываются их адреса.

Шевченко А. В.

Информатика. Тема 4. Обработка информации

15

16.

Устройство процессораПроцессор

Регистр 1

Регистр 2

Регистр 3

АЛУ

...

PC – программный счетчик

SP – указатель стека

PS – слово состояния

УУ

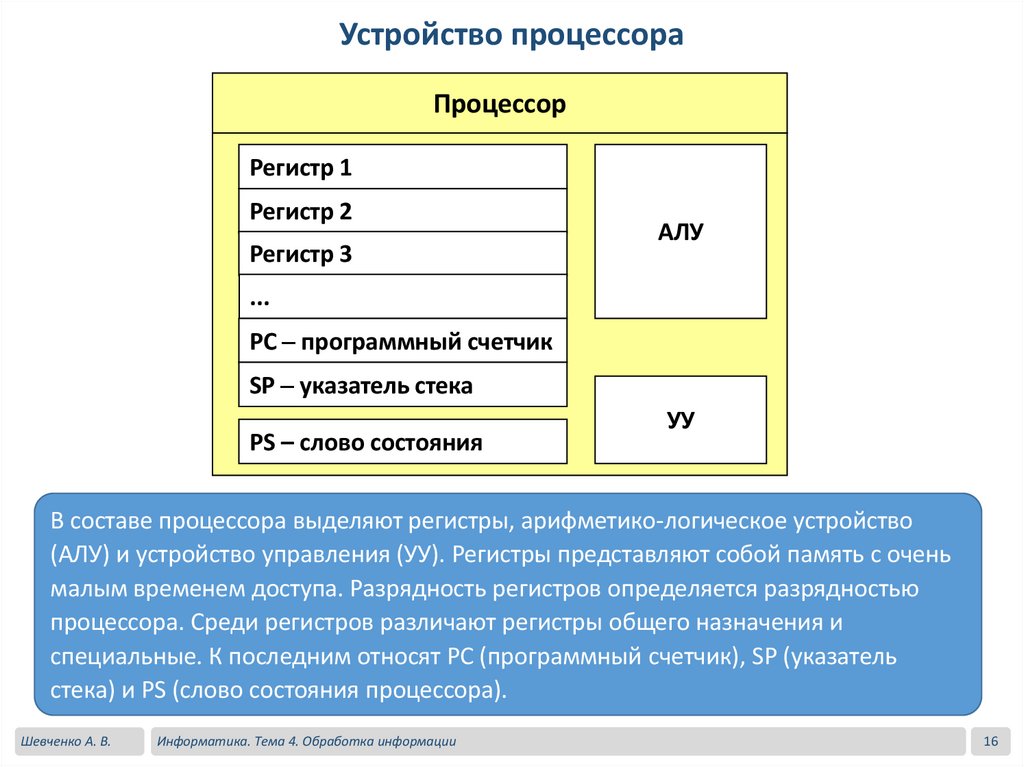

В составе процессора выделяют регистры, арифметико-логическое устройство

(АЛУ) и устройство управления (УУ). Регистры представляют собой память с очень

малым временем доступа. Разрядность регистров определяется разрядностью

процессора. Среди регистров различают регистры общего назначения и

специальные. К последним относят PC (программный счетчик), SP (указатель

стека) и PS (слово состояния процессора).

Шевченко А. В.

Информатика. Тема 4. Обработка информации

16

17.

Регистры общего назначения процессора Intel x86-64Процессор Intel x86-64

AH

AL

Регистр A

AX

EAX

Регистр B

RAX

Регистр C

Регистр D

64

32

16

8

0

…

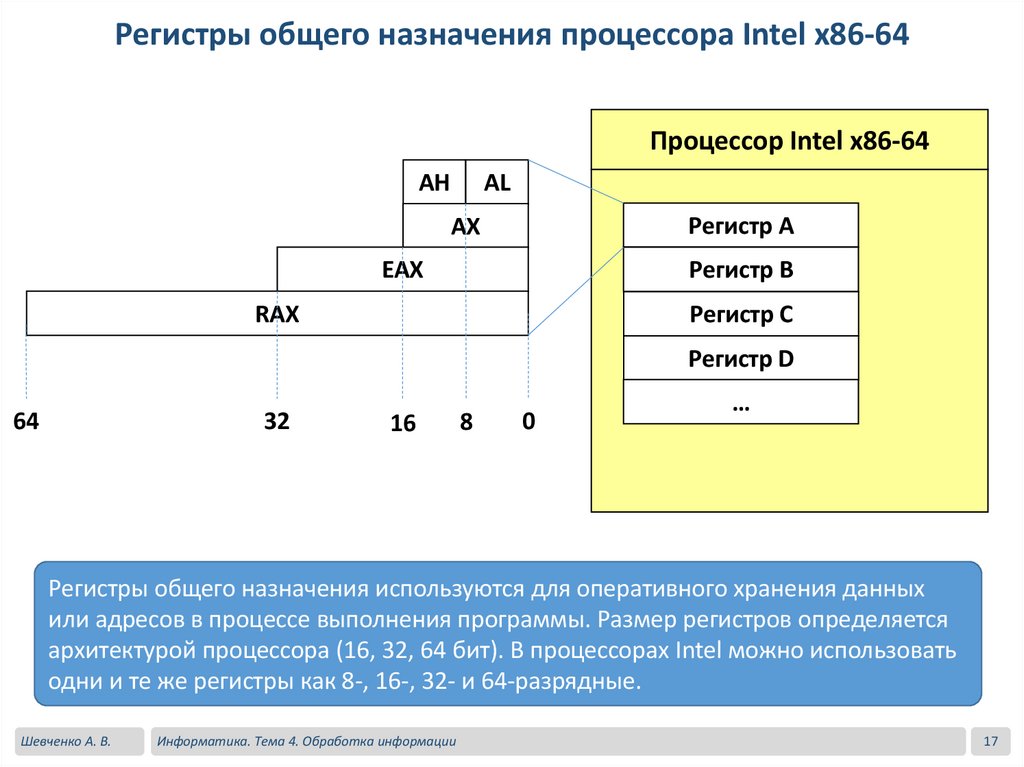

Регистры общего назначения используются для оперативного хранения данных

или адресов в процессе выполнения программы. Размер регистров определяется

архитектурой процессора (16, 32, 64 бит). В процессорах Intel можно использовать

одни и те же регистры как 8-, 16-, 32- и 64-разрядные.

Шевченко А. В.

Информатика. Тема 4. Обработка информации

17

18.

Регистры процессора Intel x86-64Процессор Intel x86-64

RAX

RBX

RCX

RDX

RBP

RSI

RDI

RSP

ST0

ST1

ST2

ST3

ST4

ST5

ST6

ST7

MM0

MM1

MM2

MM3

MM4

MM5

MM6

MM7

XMM0

XMM1

XMM2

XMM3

XMM4

XMM5

XMM6

XMM7

RIP

R8

R9

R10

R11

R12

R13

R14

R15

XMM8

XMM9

XMM10

XMM11

XMM12

XMM13

XMM14

XMM15

RFLAGS

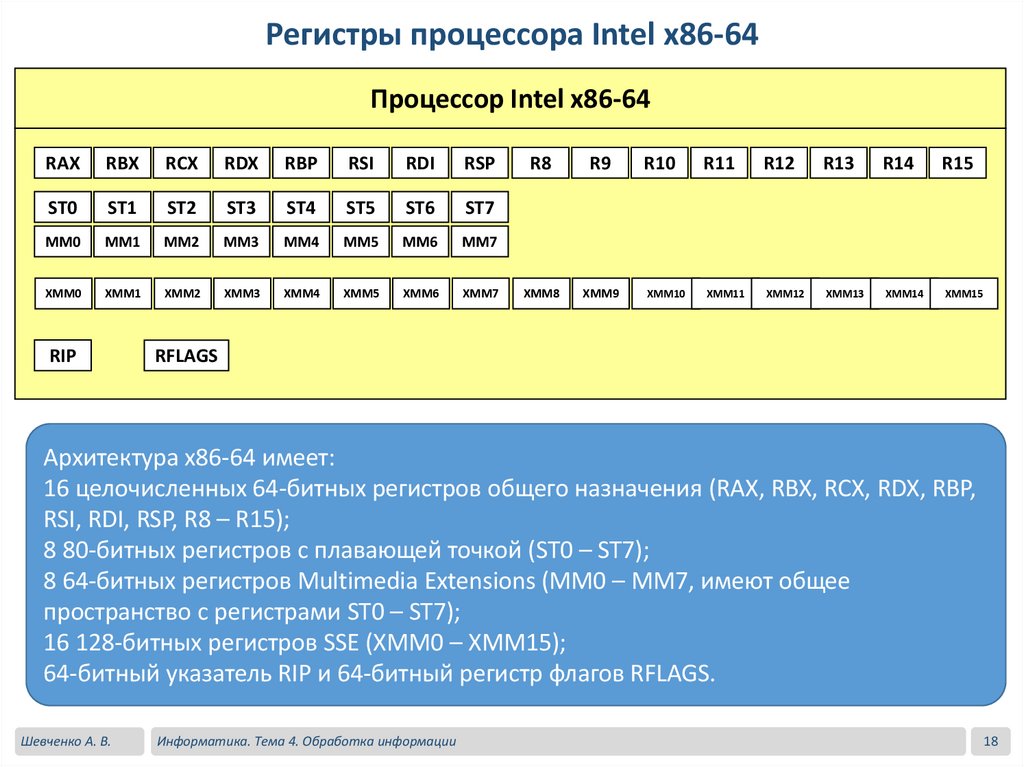

Архитектура x86-64 имеет:

16 целочисленных 64-битных регистров общего назначения (RAX, RBX, RCX, RDX, RBP,

RSI, RDI, RSP, R8 – R15);

8 80-битных регистров с плавающей точкой (ST0 – ST7);

8 64-битных регистров Multimedia Extensions (MM0 – MM7, имеют общее

пространство с регистрами ST0 – ST7);

16 128-битных регистров SSE (XMM0 – XMM15);

64-битный указатель RIP и 64-битный регистр флагов RFLAGS.

Шевченко А. В.

Информатика. Тема 4. Обработка информации

18

19.

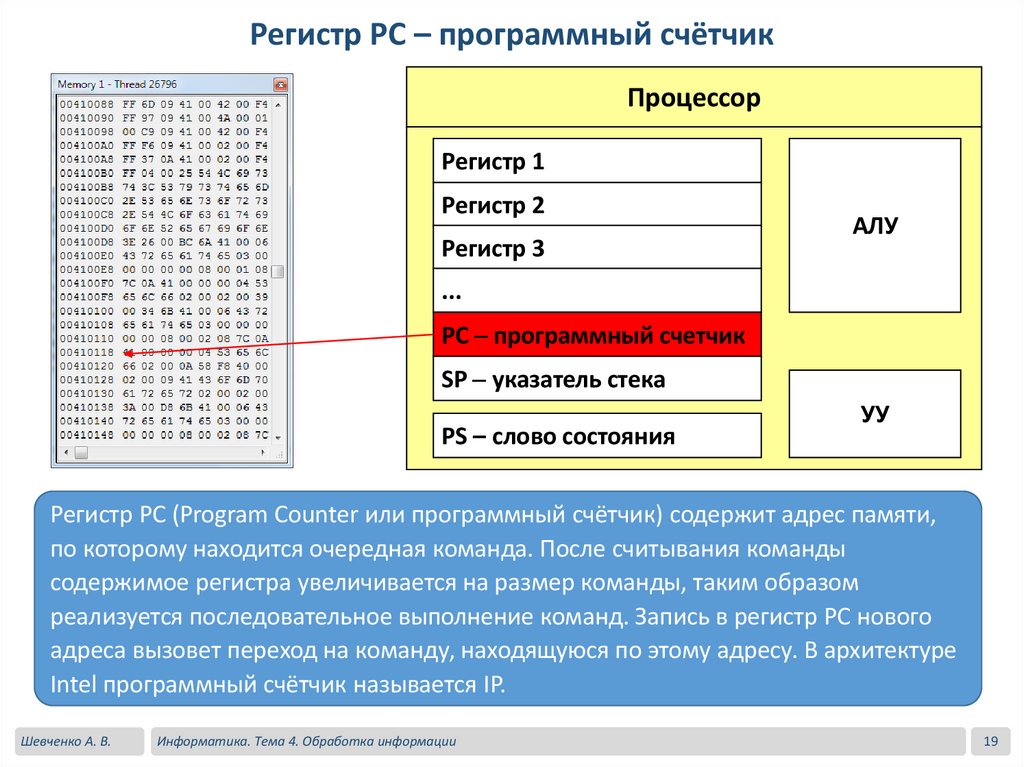

Регистр PC – программный счётчикПроцессор

Регистр 1

Регистр 2

Регистр 3

АЛУ

...

PC – программный счетчик

SP – указатель стека

PS – слово состояния

УУ

Регистр PC (Program Counter или программный счётчик) содержит адрес памяти,

по которому находится очередная команда. После считывания команды

содержимое регистра увеличивается на размер команды, таким образом

реализуется последовательное выполнение команд. Запись в регистр PC нового

адреса вызовет переход на команду, находящуюся по этому адресу. В архитектуре

Intel программный счётчик называется IP.

Шевченко А. В.

Информатика. Тема 4. Обработка информации

19

20.

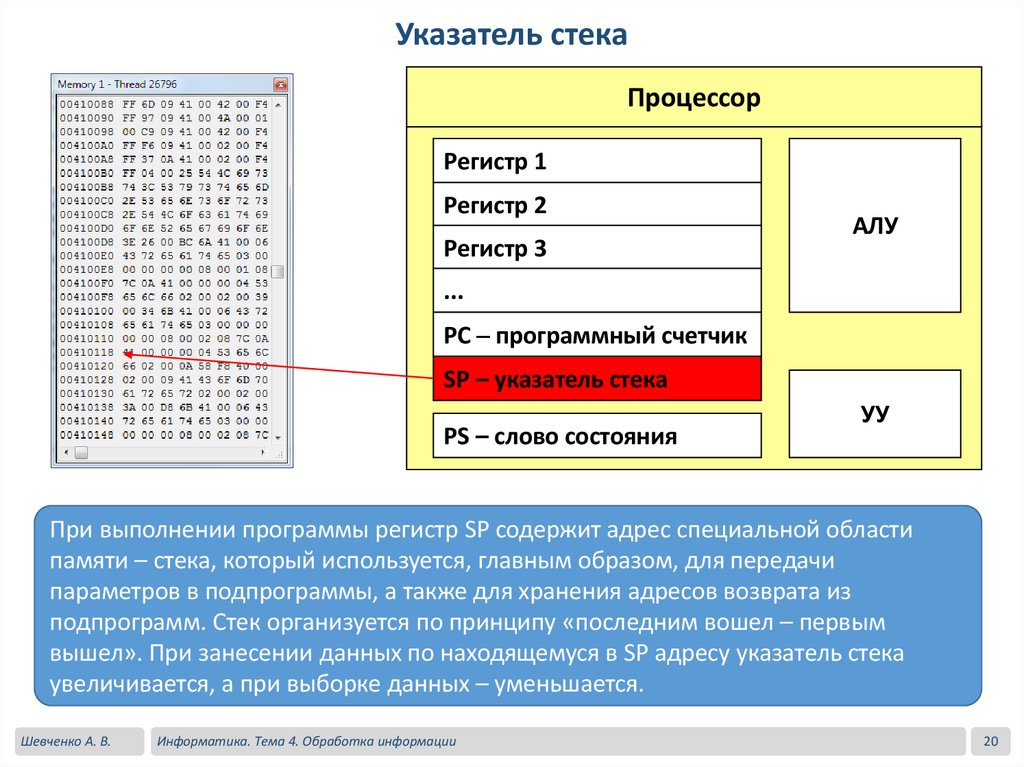

Указатель стекаПроцессор

Регистр 1

Регистр 2

Регистр 3

АЛУ

...

PC – программный счетчик

SP – указатель стека

PS – слово состояния

УУ

При выполнении программы регистр SP содержит адрес специальной области

памяти – стека, который используется, главным образом, для передачи

параметров в подпрограммы, а также для хранения адресов возврата из

подпрограмм. Стек организуется по принципу «последним вошел – первым

вышел». При занесении данных по находящемуся в SP адресу указатель стека

увеличивается, а при выборке данных – уменьшается.

Шевченко А. В.

Информатика. Тема 4. Обработка информации

20

21.

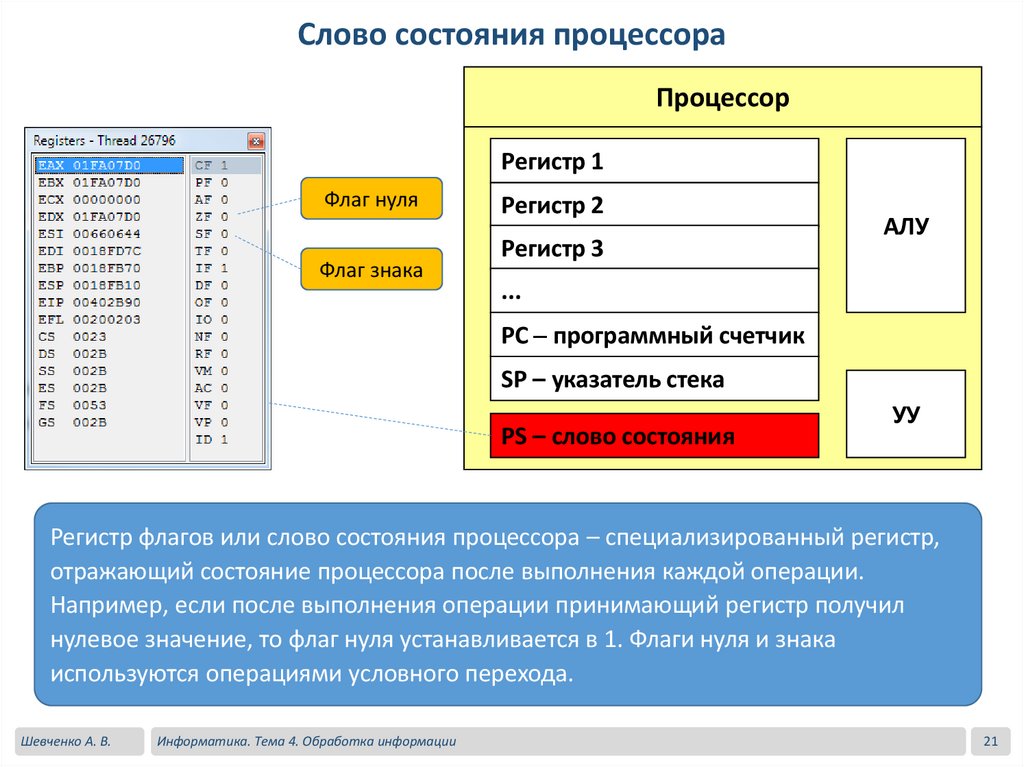

Слово состояния процессораПроцессор

Регистр 1

Флаг нуля

Флаг знака

Регистр 2

Регистр 3

АЛУ

...

PC – программный счетчик

SP – указатель стека

PS – слово состояния

УУ

Регистр флагов или слово состояния процессора – специализированный регистр,

отражающий состояние процессора после выполнения каждой операции.

Например, если после выполнения операции принимающий регистр получил

нулевое значение, то флаг нуля устанавливается в 1. Флаги нуля и знака

используются операциями условного перехода.

Шевченко А. В.

Информатика. Тема 4. Обработка информации

21

22.

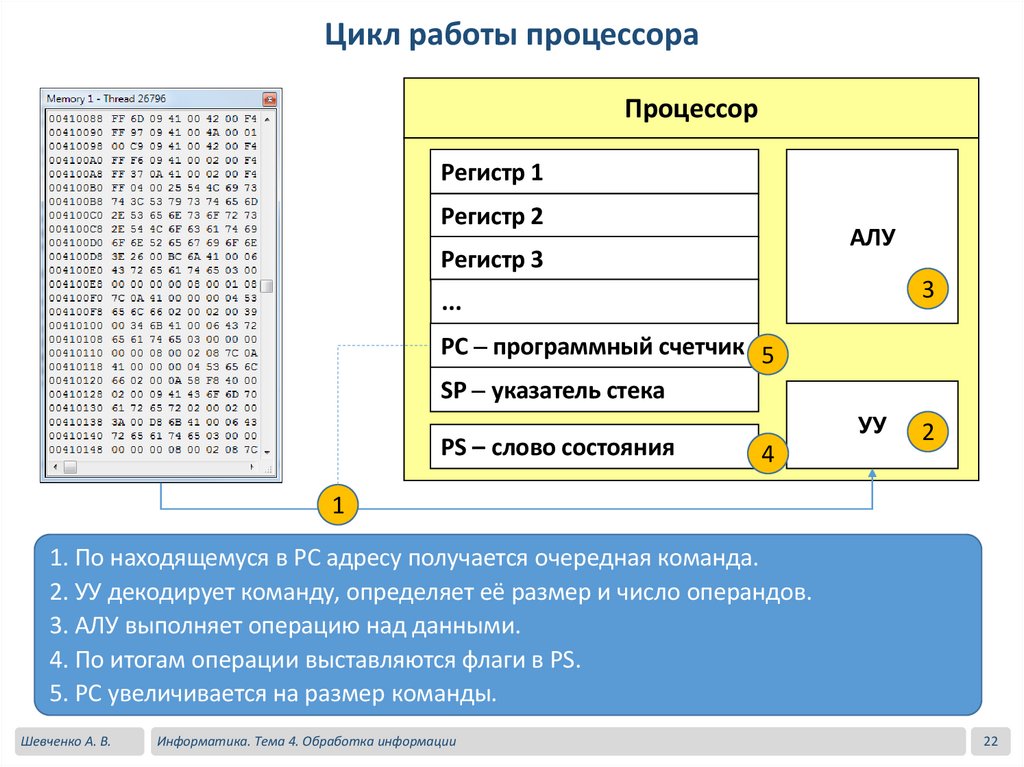

Цикл работы процессораПроцессор

Регистр 1

Регистр 2

АЛУ

Регистр 3

3

...

PC – программный счетчик 5

SP – указатель стека

PS – слово состояния

УУ

4

2

1

1. По находящемуся в PC адресу получается очередная команда.

2. УУ декодирует команду, определяет её размер и число операндов.

3. АЛУ выполняет операцию над данными.

4. По итогам операции выставляются флаги в PS.

5. PC увеличивается на размер команды.

Шевченко А. В.

Информатика. Тема 4. Обработка информации

22

23.

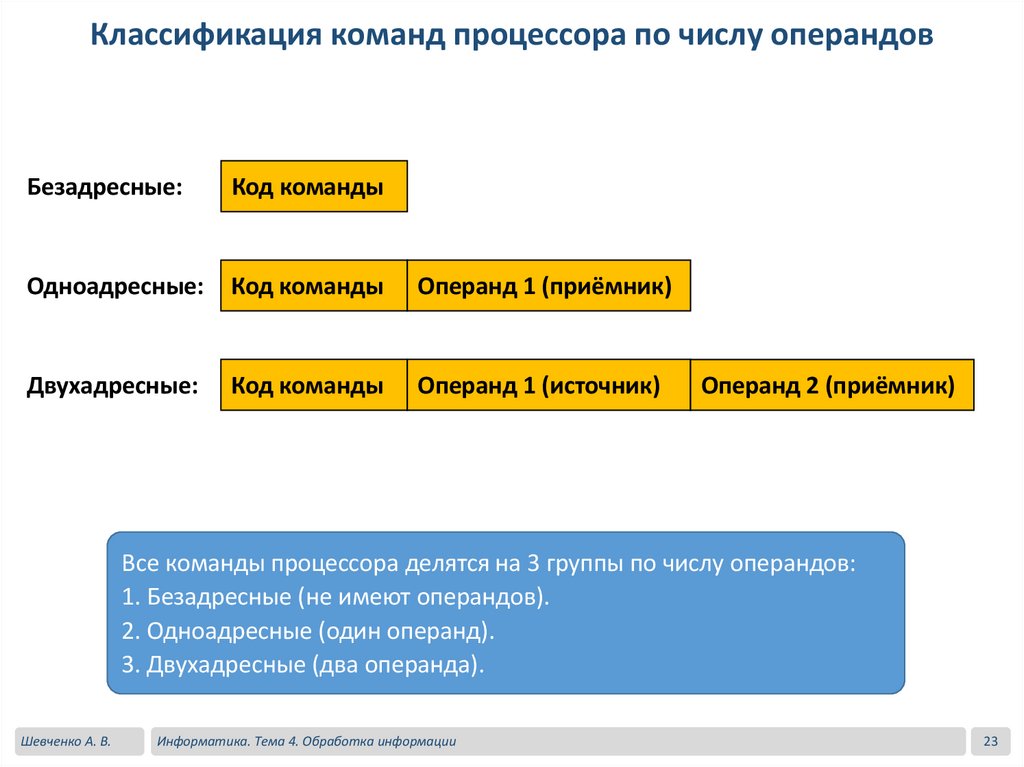

Классификация команд процессора по числу операндовБезадресные:

Код команды

Одноадресные:

Код команды

Операнд 1 (приёмник)

Двухадресные:

Код команды

Операнд 1 (источник)

Операнд 2 (приёмник)

Все команды процессора делятся на 3 группы по числу операндов:

1. Безадресные (не имеют операндов).

2. Одноадресные (один операнд).

3. Двухадресные (два операнда).

Шевченко А. В.

Информатика. Тема 4. Обработка информации

23

24.

Примеры команд с разным числом операндовБезадресные:

HALT

Одноадресные:

CLR

Операнд 1 (приёмник)

Двухадресные:

MOV

Операнд 1 (источник)

Операнд 2 (приёмник)

Команда остановки процессора (HALT) не требует указания

операндов, для команды очистки (CLR) задаётся один операнд, для

команды пересылки (MOV) – два операнда.

Шевченко А. В.

Информатика. Тема 4. Обработка информации

24

25.

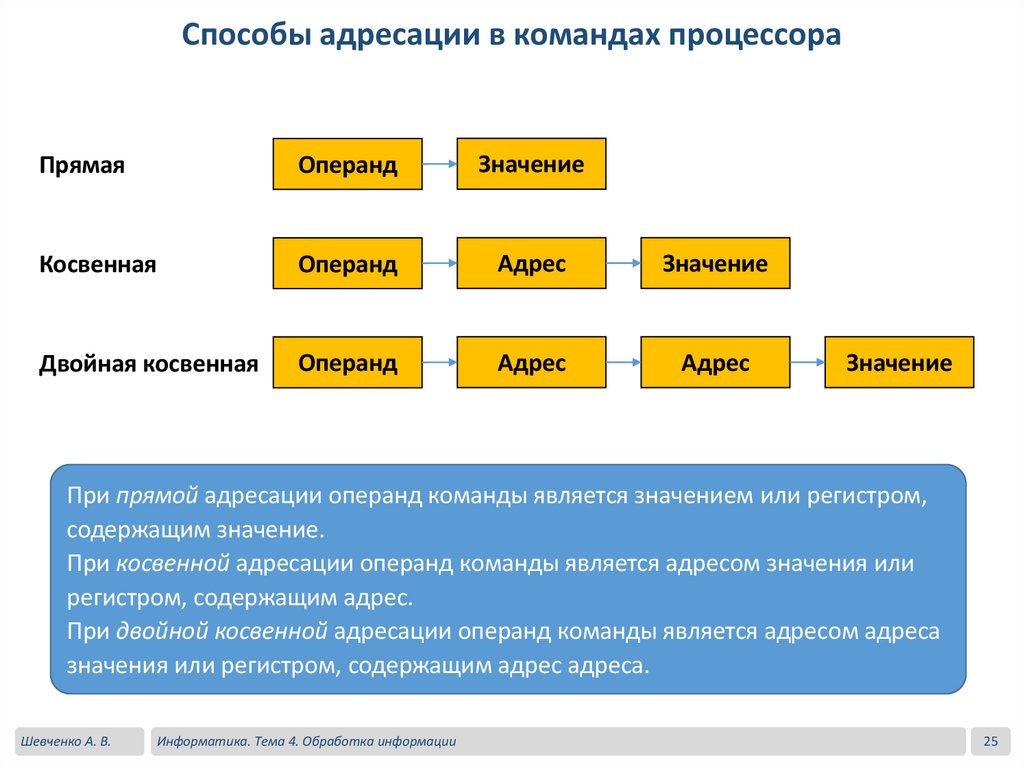

Способы адресации в командах процессораПрямая

Операнд

Значение

Косвенная

Операнд

Адрес

Значение

Двойная косвенная

Операнд

Адрес

Адрес

Значение

При прямой адресации операнд команды является значением или регистром,

содержащим значение.

При косвенной адресации операнд команды является адресом значения или

регистром, содержащим адрес.

При двойной косвенной адресации операнд команды является адресом адреса

значения или регистром, содержащим адрес адреса.

Шевченко А. В.

Информатика. Тема 4. Обработка информации

25

26.

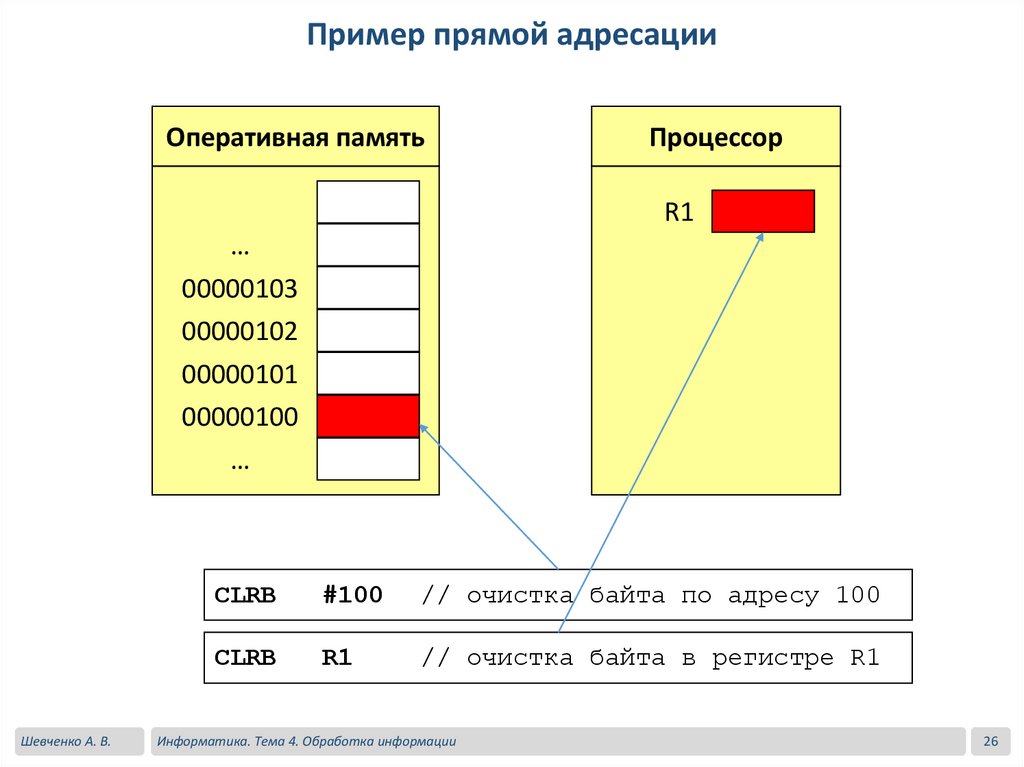

Пример прямой адресацииОперативная память

Процессор

R1

…

00000103

00000102

00000101

00000100

…

Шевченко А. В.

CLRB

#100

// очистка байта по адресу 100

CLRB

R1

// очистка байта в регистре R1

Информатика. Тема 4. Обработка информации

26

27.

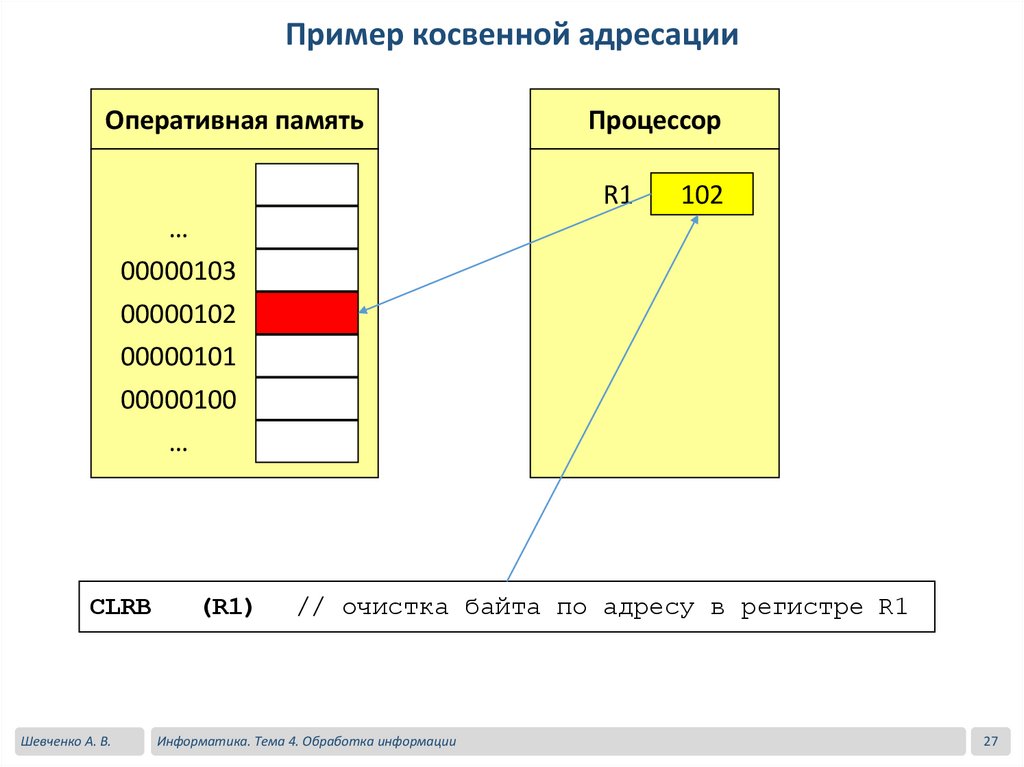

Пример косвенной адресацииОперативная память

Процессор

R1

102

…

00000103

00000102

00000101

00000100

…

CLRB

Шевченко А. В.

(R1)

// очистка байта по адресу в регистре R1

Информатика. Тема 4. Обработка информации

27

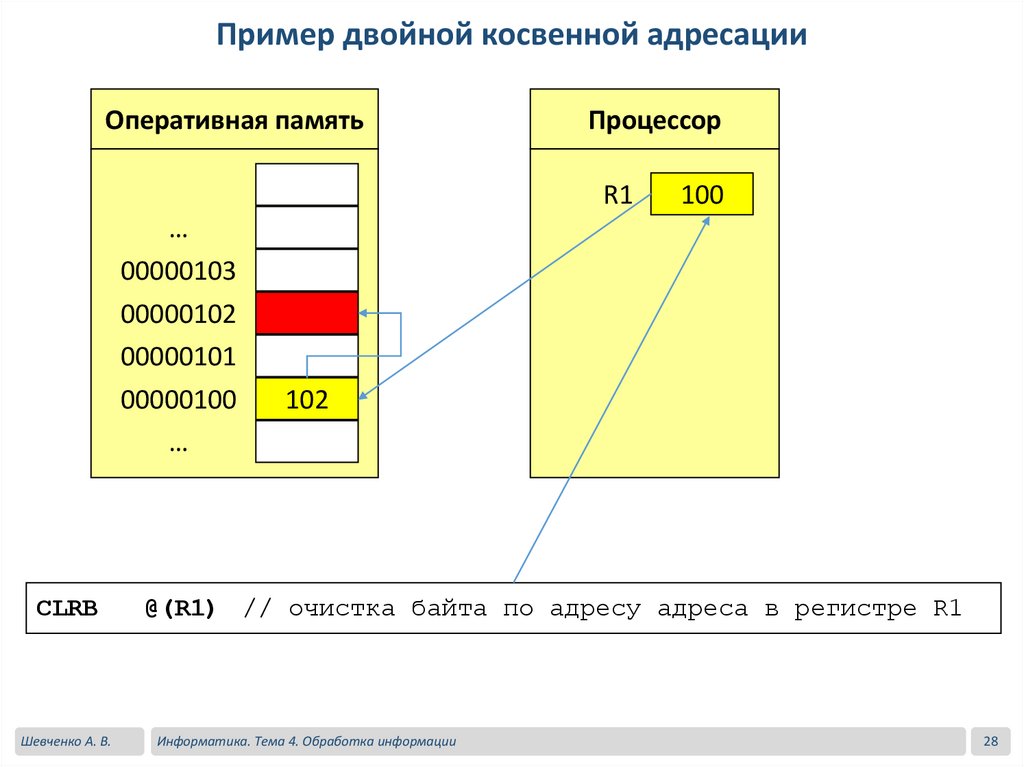

28.

Пример двойной косвенной адресацииОперативная память

Процессор

R1

…

00000103

00000102

00000101

00000100

…

CLRB

Шевченко А. В.

100

102

@(R1) // очистка байта по адресу адреса в регистре R1

Информатика. Тема 4. Обработка информации

28

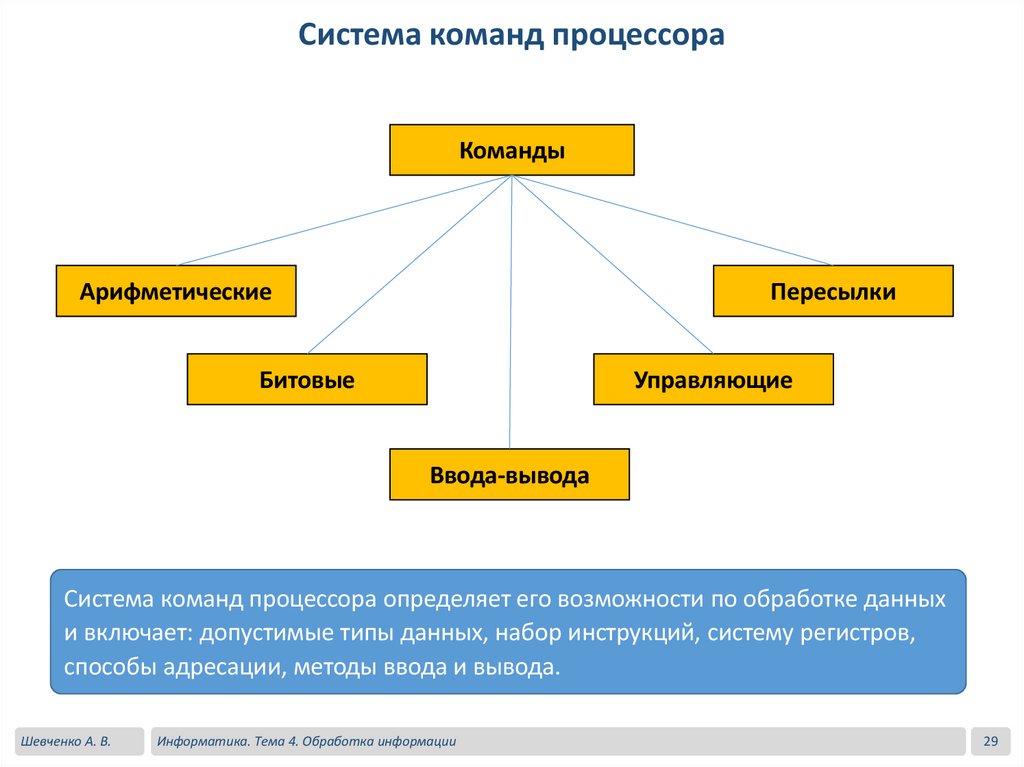

29.

Система команд процессораКоманды

Арифметические

Пересылки

Битовые

Управляющие

Ввода-вывода

Система команд процессора определяет его возможности по обработке данных

и включает: допустимые типы данных, набор инструкций, систему регистров,

способы адресации, методы ввода и вывода.

Шевченко А. В.

Информатика. Тема 4. Обработка информации

29

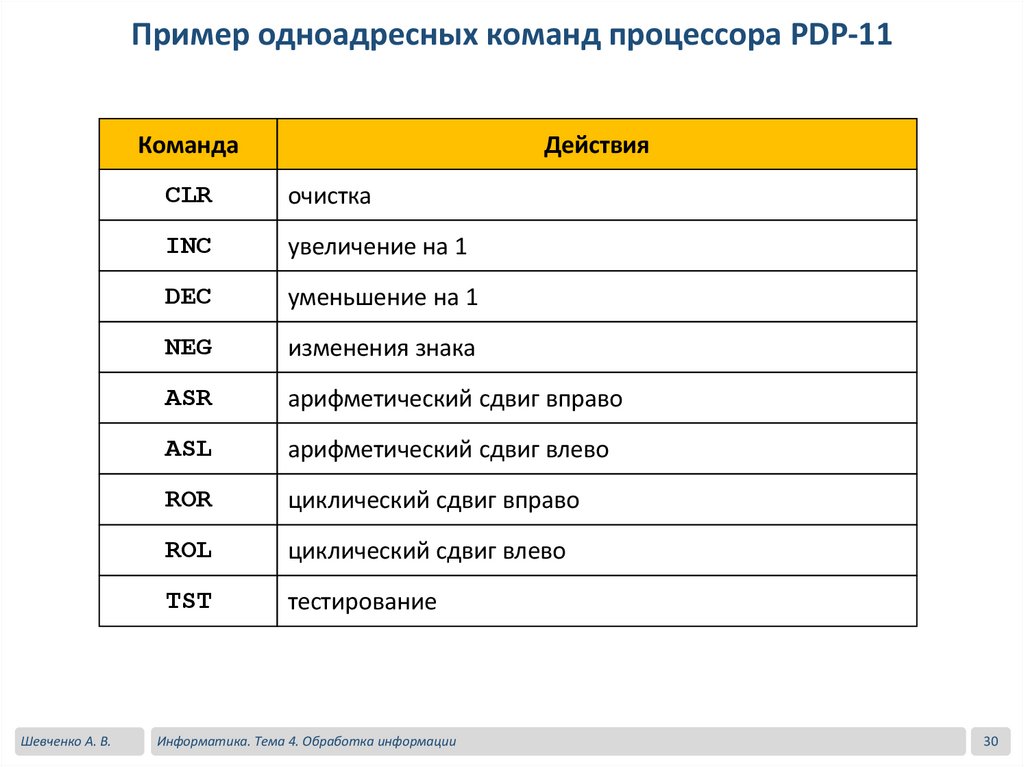

30.

Пример одноадресных команд процессора PDP-11Команда

Шевченко А. В.

Действия

CLR

очистка

INC

увеличение на 1

DEC

уменьшение на 1

NEG

изменения знака

ASR

арифметический сдвиг вправо

ASL

арифметический сдвиг влево

ROR

циклический сдвиг вправо

ROL

циклический сдвиг влево

TST

тестирование

Информатика. Тема 4. Обработка информации

30

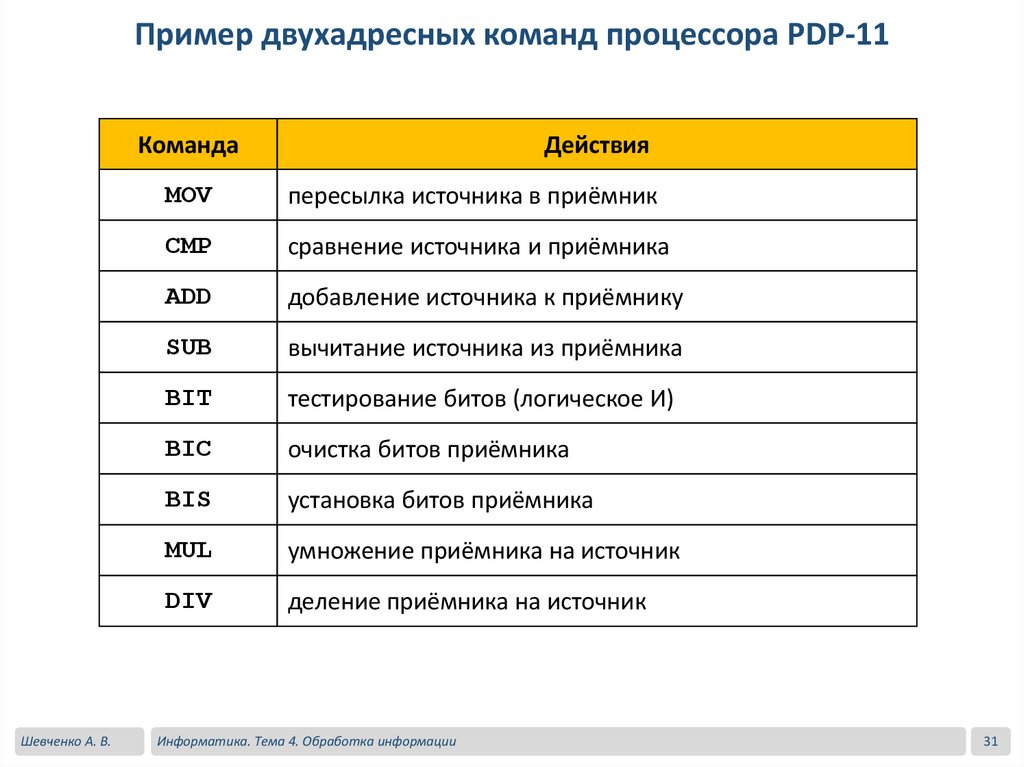

31.

Пример двухадресных команд процессора PDP-11Команда

Шевченко А. В.

Действия

MOV

пересылка источника в приёмник

CMP

сравнение источника и приёмника

ADD

добавление источника к приёмнику

SUB

вычитание источника из приёмника

BIT

тестирование битов (логическое И)

BIC

очистка битов приёмника

BIS

установка битов приёмника

MUL

умножение приёмника на источник

DIV

деление приёмника на источник

Информатика. Тема 4. Обработка информации

31

32.

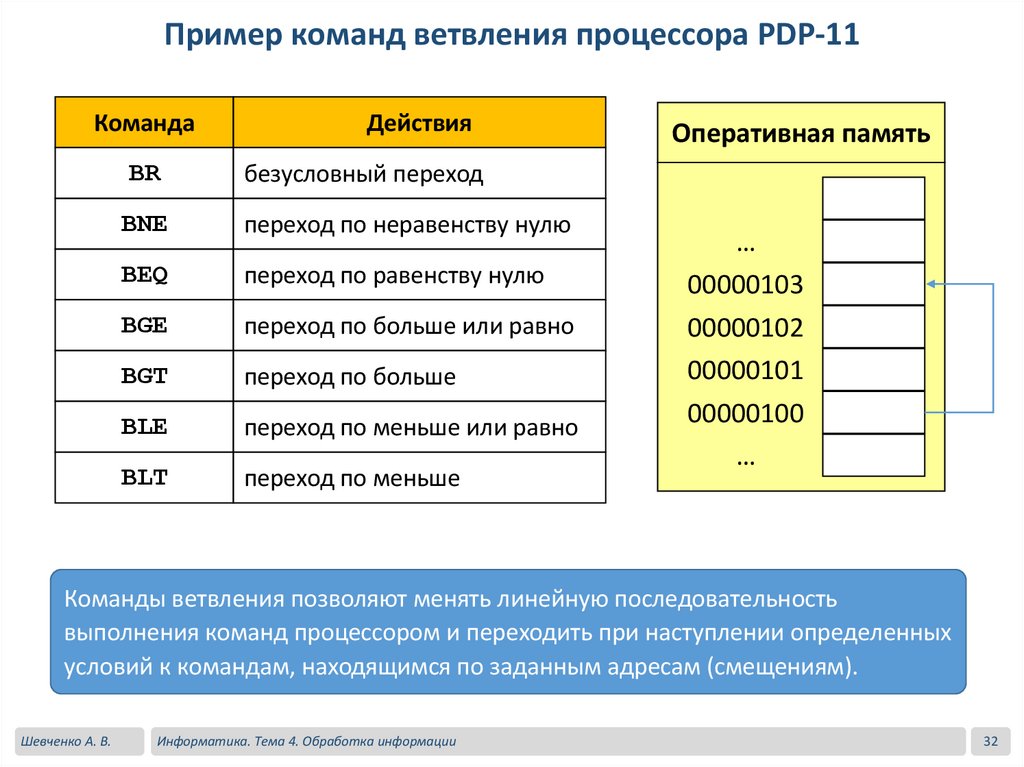

Пример команд ветвления процессора PDP-11Команда

Действия

BR

безусловный переход

BNE

переход по неравенству нулю

BEQ

переход по равенству нулю

BGE

переход по больше или равно

BGT

переход по больше

BLE

переход по меньше или равно

BLT

переход по меньше

Оперативная память

…

00000103

00000102

00000101

00000100

…

Команды ветвления позволяют менять линейную последовательность

выполнения команд процессором и переходить при наступлении определенных

условий к командам, находящимся по заданным адресам (смещениям).

Шевченко А. В.

Информатика. Тема 4. Обработка информации

32

33.

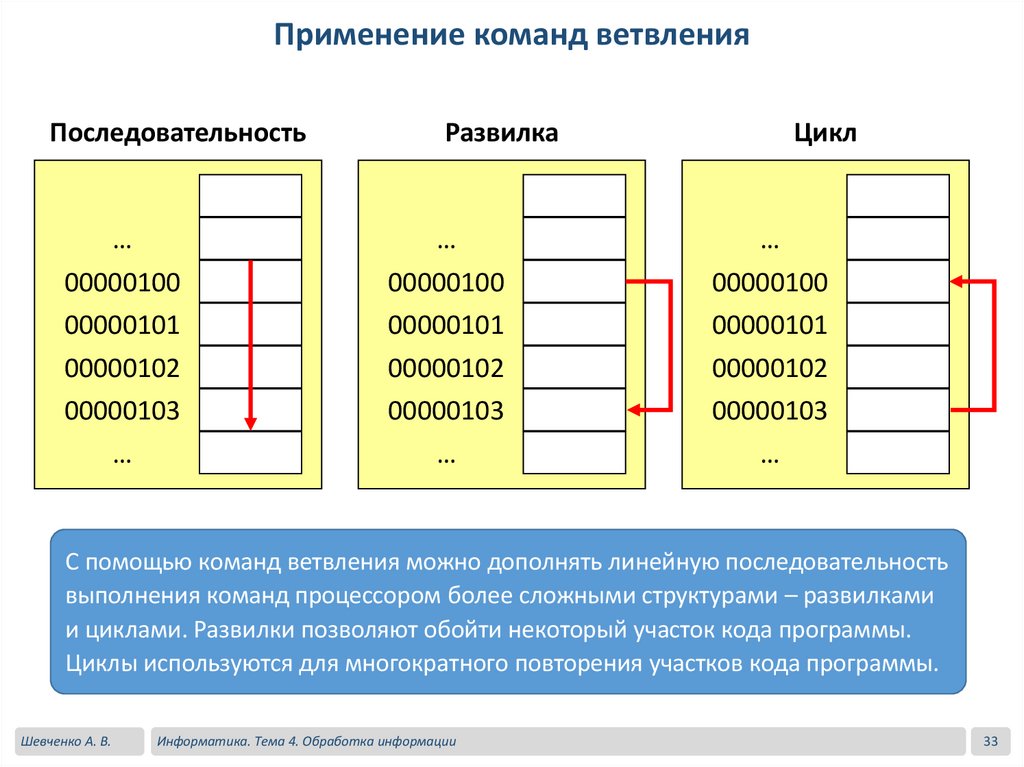

Применение команд ветвленияПоследовательность

…

00000100

00000101

00000102

00000103

…

Развилка

…

00000100

00000101

00000102

00000103

…

Цикл

…

00000100

00000101

00000102

00000103

…

С помощью команд ветвления можно дополнять линейную последовательность

выполнения команд процессором более сложными структурами – развилками

и циклами. Развилки позволяют обойти некоторый участок кода программы.

Циклы используются для многократного повторения участков кода программы.

Шевченко А. В.

Информатика. Тема 4. Обработка информации

33

34.

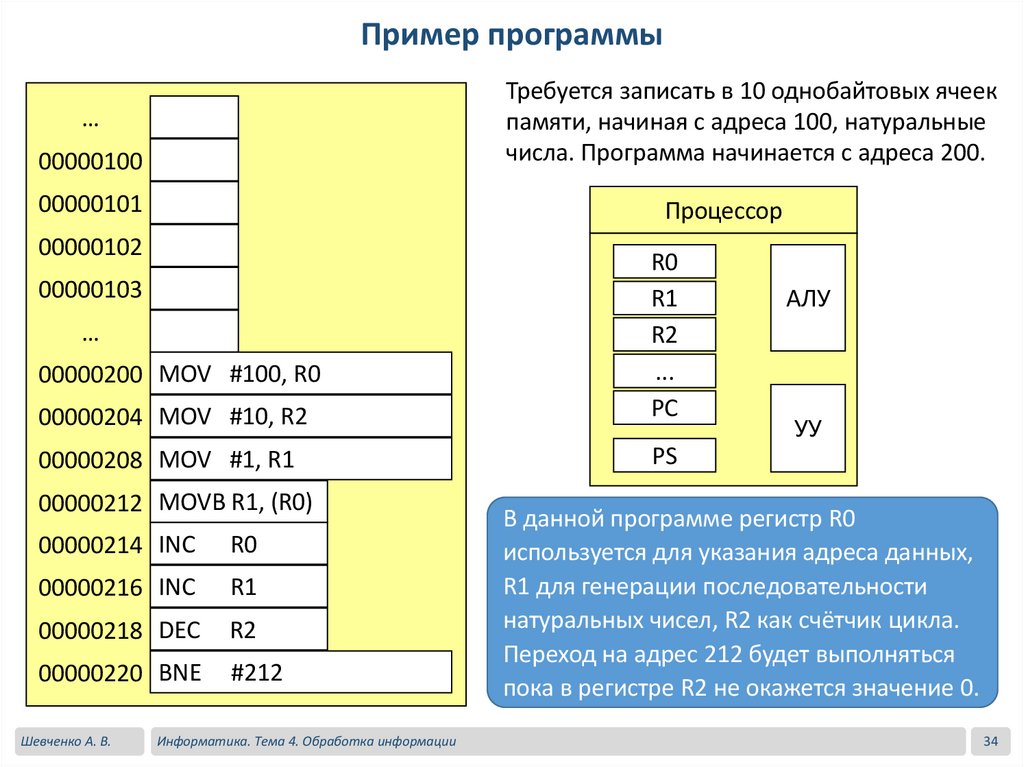

Пример программыТребуется записать в 10 однобайтовых ячеек

памяти, начиная с адреса 100, натуральные

числа. Программа начинается с адреса 200.

…

00000100

00000101

Процессор

00000102

00000204 MOV #10, R2

R0

R1

R2

...

PC

00000208 MOV #1, R1

PS

00000103

…

00000200 MOV #100, R0

00000212 MOVB R1, (R0)

00000214 INC

R0

00000216 INC

R1

00000218 DEC

R2

00000220 BNE

#212

Шевченко А. В.

Информатика. Тема 4. Обработка информации

АЛУ

УУ

В данной программе регистр R0

используется для указания адреса данных,

R1 для генерации последовательности

натуральных чисел, R2 как счётчик цикла.

Переход на адрес 212 будет выполняться

пока в регистре R2 не окажется значение 0.

34

35.

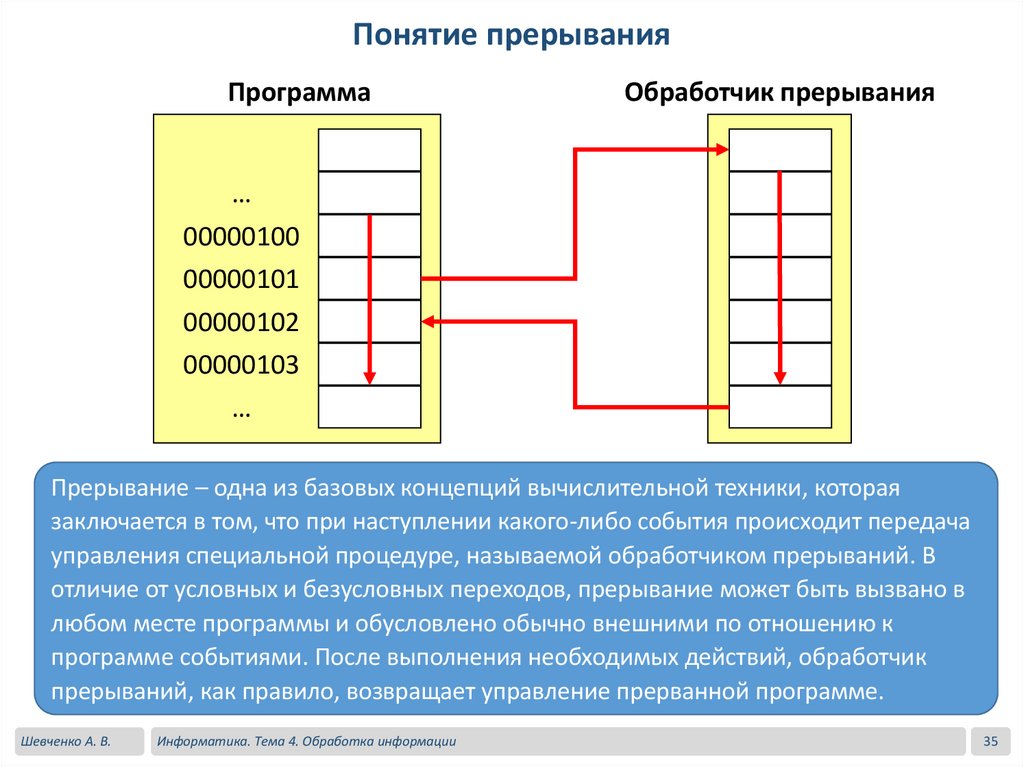

Понятие прерыванияПрограмма

Обработчик прерывания

…

00000100

00000101

00000102

00000103

…

Прерывание – одна из базовых концепций вычислительной техники, которая

заключается в том, что при наступлении какого-либо события происходит передача

управления специальной процедуре, называемой обработчиком прерываний. В

отличие от условных и безусловных переходов, прерывание может быть вызвано в

любом месте программы и обусловлено обычно внешними по отношению к

программе событиями. После выполнения необходимых действий, обработчик

прерываний, как правило, возвращает управление прерванной программе.

Шевченко А. В.

Информатика. Тема 4. Обработка информации

35

36.

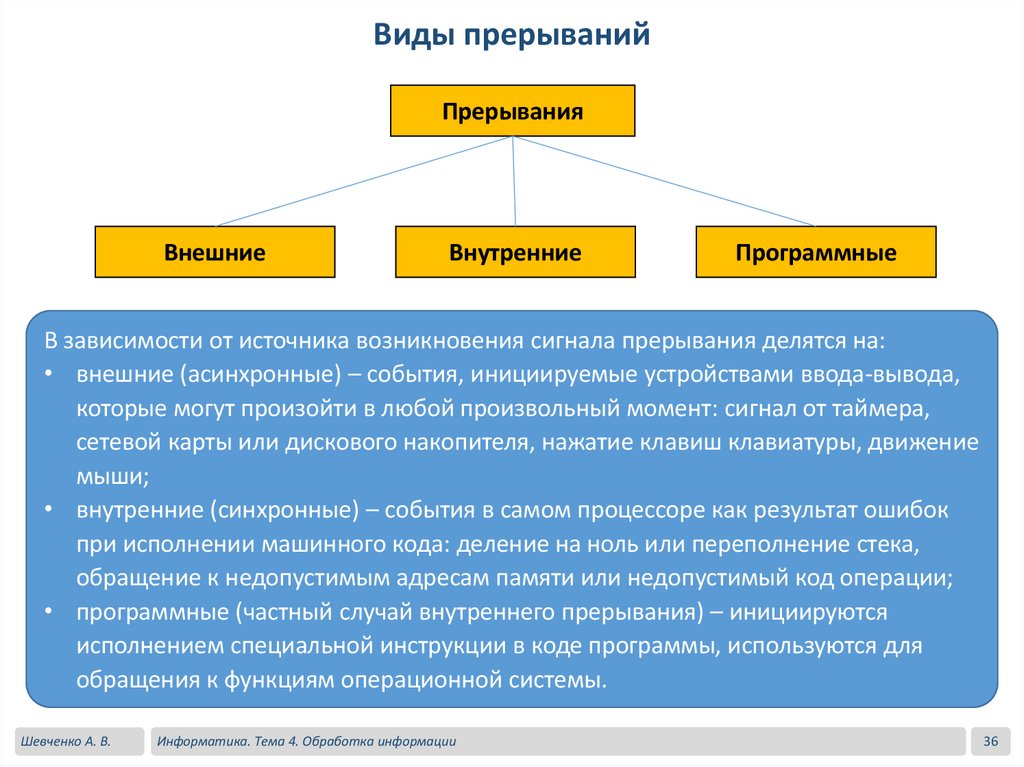

Виды прерыванийПрерывания

Внешние

Внутренние

Программные

В зависимости от источника возникновения сигнала прерывания делятся на:

• внешние (асинхронные) – события, инициируемые устройствами ввода-вывода,

которые могут произойти в любой произвольный момент: сигнал от таймера,

сетевой карты или дискового накопителя, нажатие клавиш клавиатуры, движение

мыши;

• внутренние (синхронные) – события в самом процессоре как результат ошибок

при исполнении машинного кода: деление на ноль или переполнение стека,

обращение к недопустимым адресам памяти или недопустимый код операции;

• программные (частный случай внутреннего прерывания) – инициируются

исполнением специальной инструкции в коде программы, используются для

обращения к функциям операционной системы.

Шевченко А. В.

Информатика. Тема 4. Обработка информации

36

37.

Пример прерывания…

000B7500 MOV R0, (SP)+

00000100

000B7504 MOV R1, (SP)+

00000101

000B7508 MOV R2, (SP)+

00000102

…

00000103

000B9314 MOV -(SP), R2

…

000B9316 MOV -(SP), R1

00000200 MOV #100, R0

000B9318 MOV -(SP), R0

00000204 MOV #10, R2

000B9320 RET

00000208 MOV #1, R1

00000212 MOVB R1, (R0)

00000214 INC

R0

00000216 INC

R1

00000218 DEC

R2

00000220 BNE

#212

Шевченко А. В.

Информатика. Тема 4. Обработка информации

После выполнения команды по адресу

214 происходит прерывание, обработчик

которого находится по адресу B7500. В

обработчике прерывания сохраняются

регистры, выполняются некоторые

действия, восстанавливаются регистры и

происходит возврат к прерванной

программе (адрес 216).

37

38.

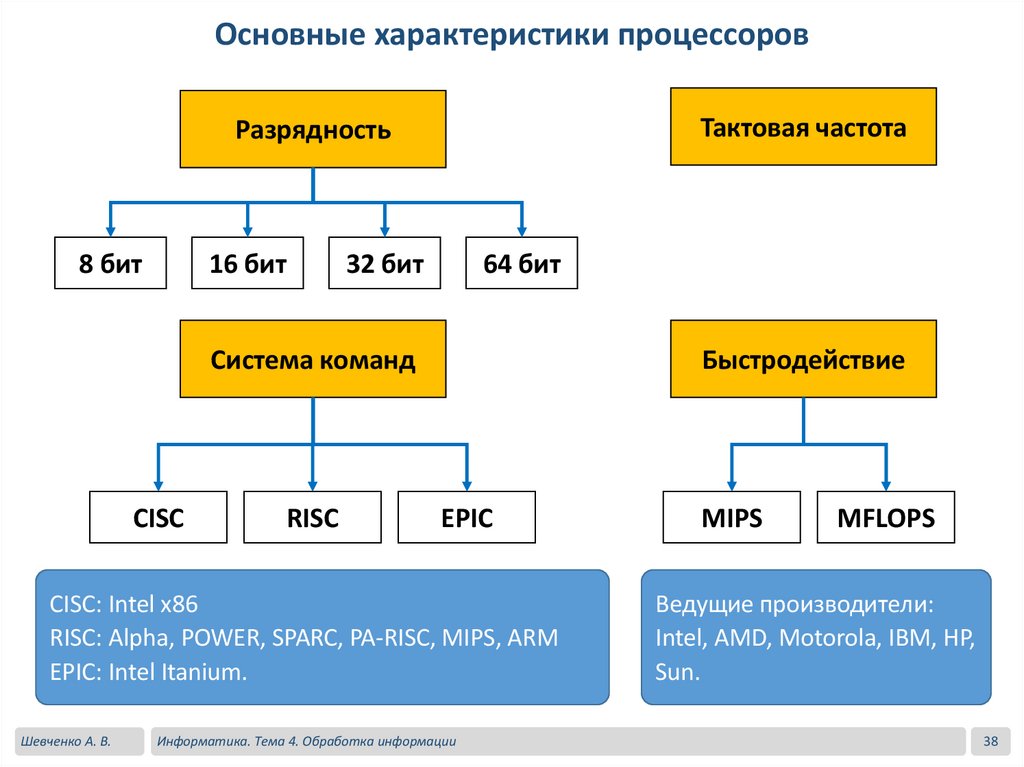

Основные характеристики процессоровТактовая частота

Разрядность

8 бит

16 бит

32 бит

64 бит

Система команд

CISC

RISC

Быстродействие

EPIC

CISC: Intel x86

RISC: Alpha, POWER, SPARC, PA-RISC, MIPS, ARM

EPIC: Intel Itanium.

Шевченко А. В.

Информатика. Тема 4. Обработка информации

MIPS

MFLOPS

Ведущие производители:

Intel, AMD, Motorola, IBM, HP,

Sun.

38

39.

Разрядность процессора и адресное пространствоПроцессор

Регистр 1

Регистр 2

Регистр 3

АЛУ

...

PC – программный счетчик

SP – указатель стека

PS – слово состояния

УУ

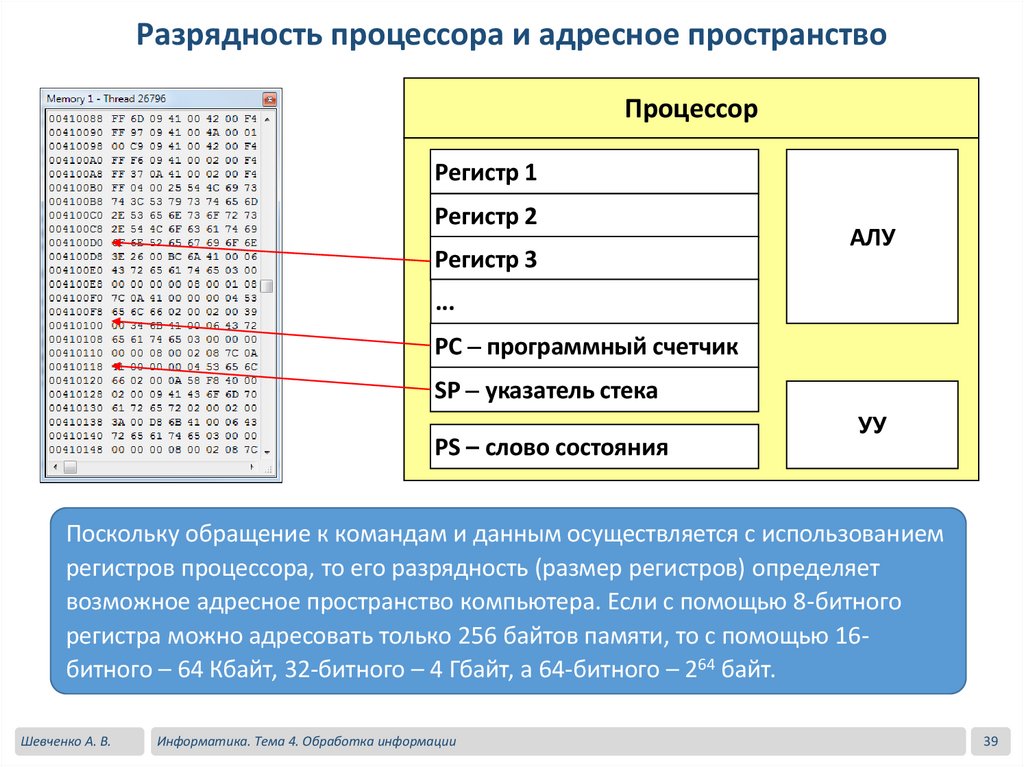

Поскольку обращение к командам и данным осуществляется с использованием

регистров процессора, то его разрядность (размер регистров) определяет

возможное адресное пространство компьютера. Если с помощью 8-битного

регистра можно адресовать только 256 байтов памяти, то с помощью 16битного – 64 Кбайт, 32-битного – 4 Гбайт, а 64-битного – 264 байт.

Шевченко А. В.

Информатика. Тема 4. Обработка информации

39

40.

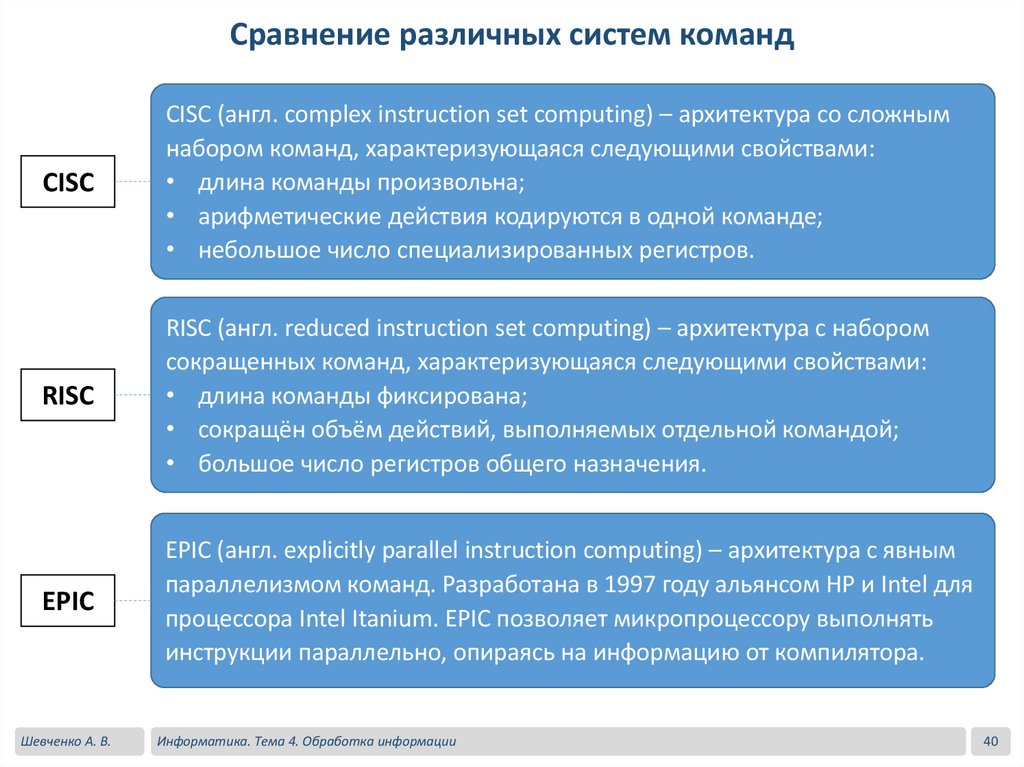

Сравнение различных систем командCISC

CISC (англ. complex instruction set computing) – архитектура со сложным

набором команд, характеризующаяся следующими свойствами:

• длина команды произвольна;

• арифметические действия кодируются в одной команде;

• небольшое число специализированных регистров.

RISC

RISC (англ. reduced instruction set computing) – архитектура с набором

сокращенных команд, характеризующаяся следующими свойствами:

• длина команды фиксирована;

• сокращён объём действий, выполняемых отдельной командой;

• большое число регистров общего назначения.

EPIC

EPIC (англ. explicitly parallel instruction computing) – архитектура с явным

параллелизмом команд. Разработана в 1997 году альянсом HP и Intel для

процессора Intel Itanium. EPIC позволяет микропроцессору выполнять

инструкции параллельно, опираясь на информацию от компилятора.

Шевченко А. В.

Информатика. Тема 4. Обработка информации

40

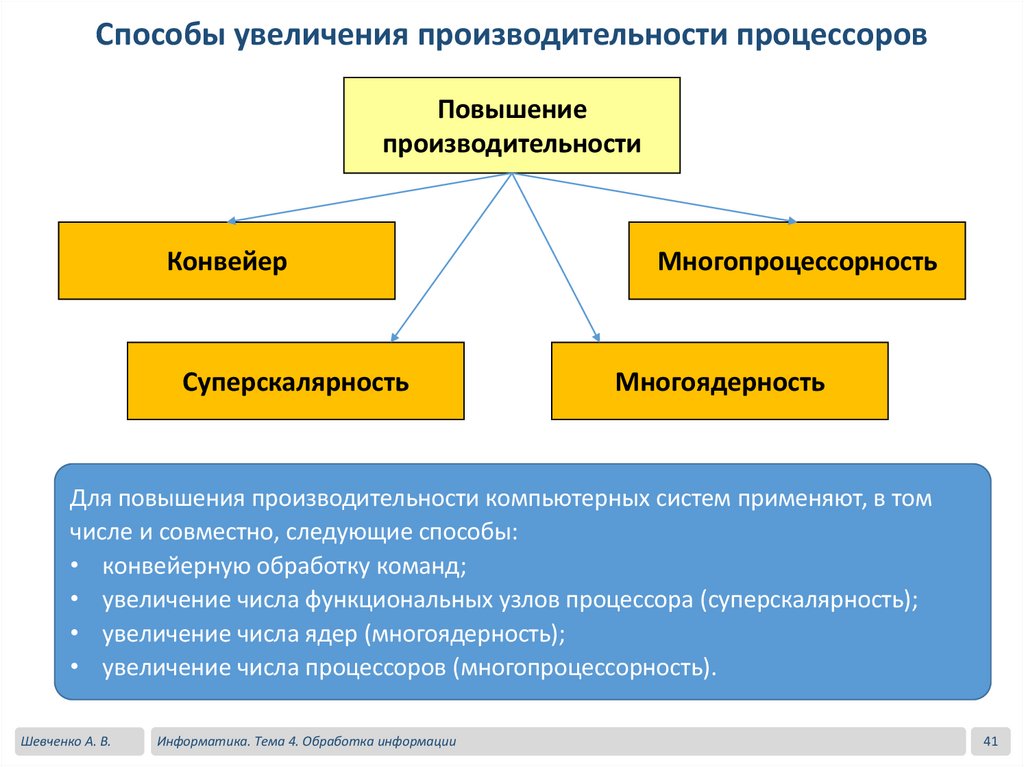

41.

Способы увеличения производительности процессоровПовышение

производительности

Конвейер

Суперскалярность

Многопроцессорность

Многоядерность

Для повышения производительности компьютерных систем применяют, в том

числе и совместно, следующие способы:

• конвейерную обработку команд;

• увеличение числа функциональных узлов процессора (суперскалярность);

• увеличение числа ядер (многоядерность);

• увеличение числа процессоров (многопроцессорность).

Шевченко А. В.

Информатика. Тема 4. Обработка информации

41

42.

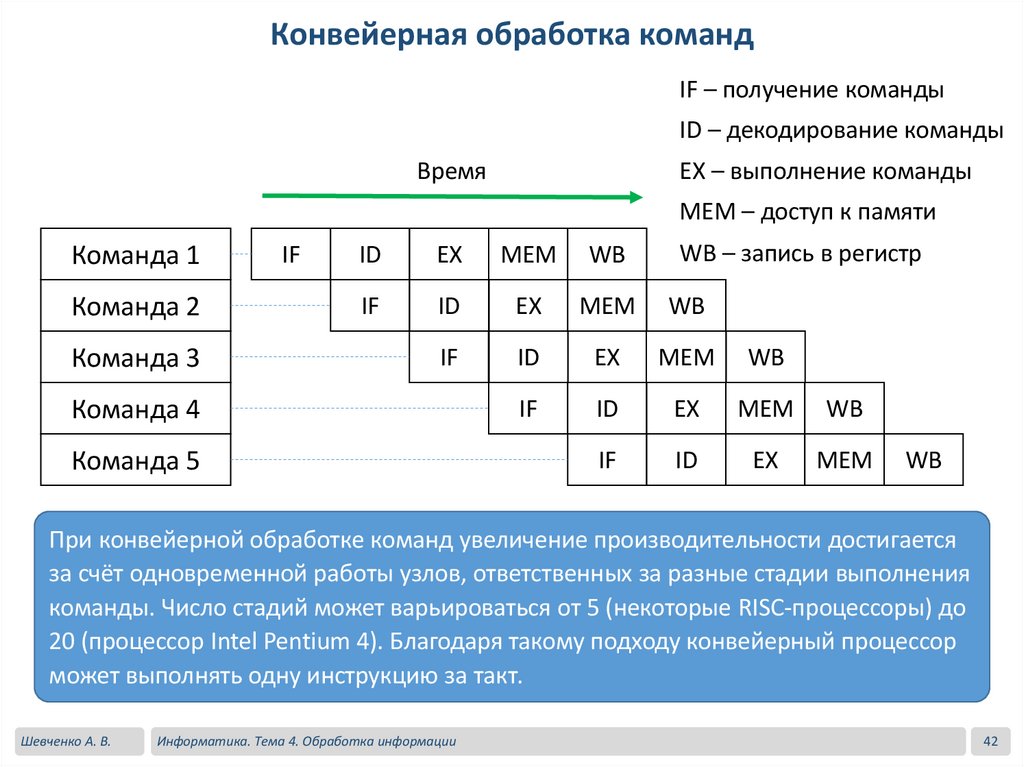

Конвейерная обработка командIF – получение команды

ID – декодирование команды

Время

EX – выполнение команды

MEM – доступ к памяти

Команда 1

Команда 2

Команда 3

IF

ID

EX

MEM

WB

WB – запись в регистр

IF

ID

EX

MEM

WB

IF

ID

EX

MEM

WB

IF

ID

EX

MEM

WB

IF

ID

EX

MEM

Команда 4

Команда 5

WB

При конвейерной обработке команд увеличение производительности достигается

за счёт одновременной работы узлов, ответственных за разные стадии выполнения

команды. Число стадий может варьироваться от 5 (некоторые RISC-процессоры) до

20 (процессор Intel Pentium 4). Благодаря такому подходу конвейерный процессор

может выполнять одну инструкцию за такт.

Шевченко А. В.

Информатика. Тема 4. Обработка информации

42

43.

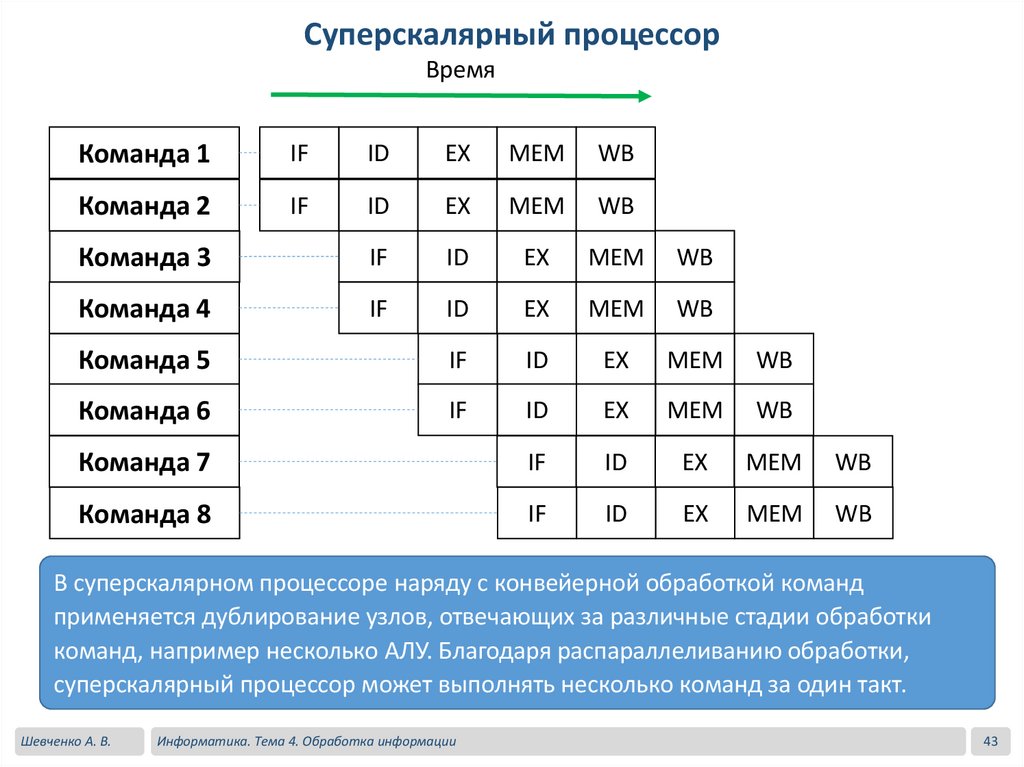

Суперскалярный процессорВремя

Команда 1

IF

ID

EX

MEM

WB

Команда 2

IF

ID

EX

MEM

WB

Команда 3

IF

ID

EX

MEM

WB

Команда 4

IF

ID

EX

MEM

WB

Команда 5

IF

ID

EX

MEM

WB

Команда 6

IF

ID

EX

MEM

WB

Команда 7

IF

ID

EX

MEM

WB

Команда 8

IF

ID

EX

MEM

WB

В суперскалярном процессоре наряду с конвейерной обработкой команд

применяется дублирование узлов, отвечающих за различные стадии обработки

команд, например несколько АЛУ. Благодаря распараллеливанию обработки,

суперскалярный процессор может выполнять несколько команд за один такт.

Шевченко А. В.

Информатика. Тема 4. Обработка информации

43

44.

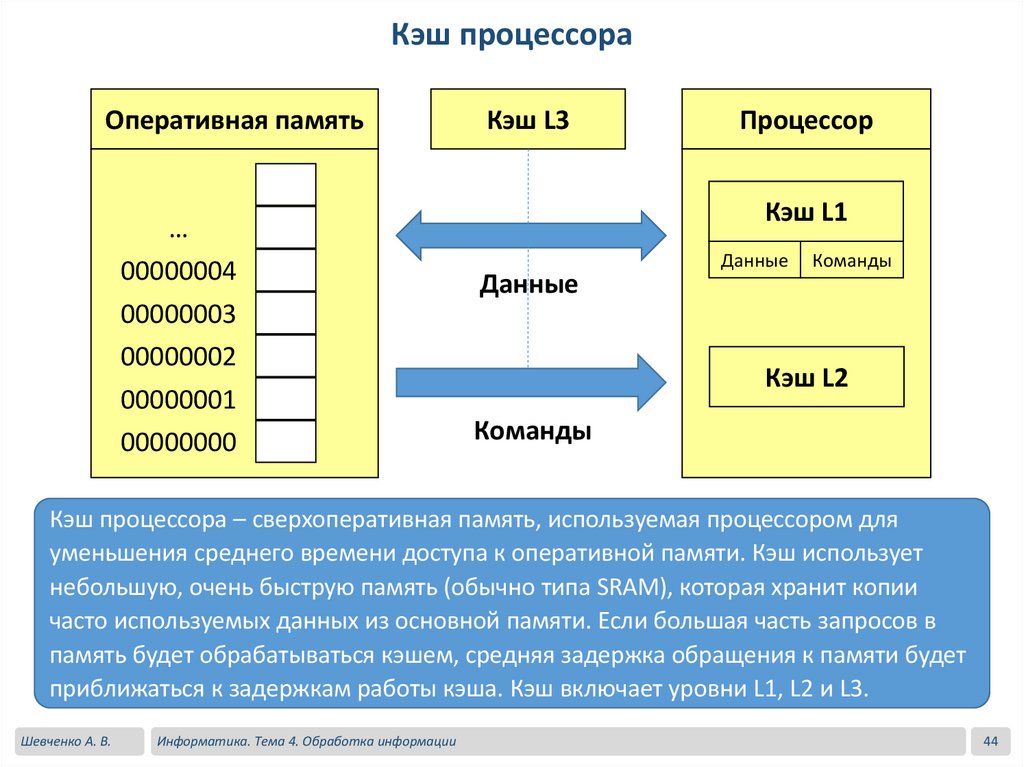

Кэш процессораОперативная память

…

00000004

00000003

00000002

00000001

00000000

Кэш L3

Процессор

Кэш L1

Данные

Команды

Данные

Кэш L2

Команды

Кэш процессора – сверхоперативная память, используемая процессором для

уменьшения среднего времени доступа к оперативной памяти. Кэш использует

небольшую, очень быструю память (обычно типа SRAM), которая хранит копии

часто используемых данных из основной памяти. Если большая часть запросов в

память будет обрабатываться кэшем, средняя задержка обращения к памяти будет

приближаться к задержкам работы кэша. Кэш включает уровни L1, L2 и L3.

Шевченко А. В.

Информатика. Тема 4. Обработка информации

44

45.

Устройство компьютераЦентральная часть

Периферийные

устройства

Процессор

Устройства вводавывода

Оперативная

память

Диски

Ленты ...

В составе любого компьютера присутствует центральная часть, включающая

процессор (один или несколько) и оперативную память (ОЗУ), а также

периферийные устройства. Периферийные устройства обеспечивают операции

ввода-вывода, долговременное хранение данных, а также взаимодействие с

пользователем.

Шевченко А. В.

Информатика. Тема 4. Обработка информации

45

46.

Понятие шины обмена даннымиОперативная

память

Процессор

Шина

адреса

Шина

Шина

данных управления

Связь между устройствами компьютера, например между процессором и

оперативной памятью, осуществляется посредством шин – набора электрических

проводников. Среди этих проводников часть обеспечивает передачу адреса (шина

адреса), другая – передачу данных (шина данных) и третья – управляющие сигналы

для синхронизации обмена данными (шина управления).

Шевченко А. В.

Информатика. Тема 4. Обработка информации

46

47.

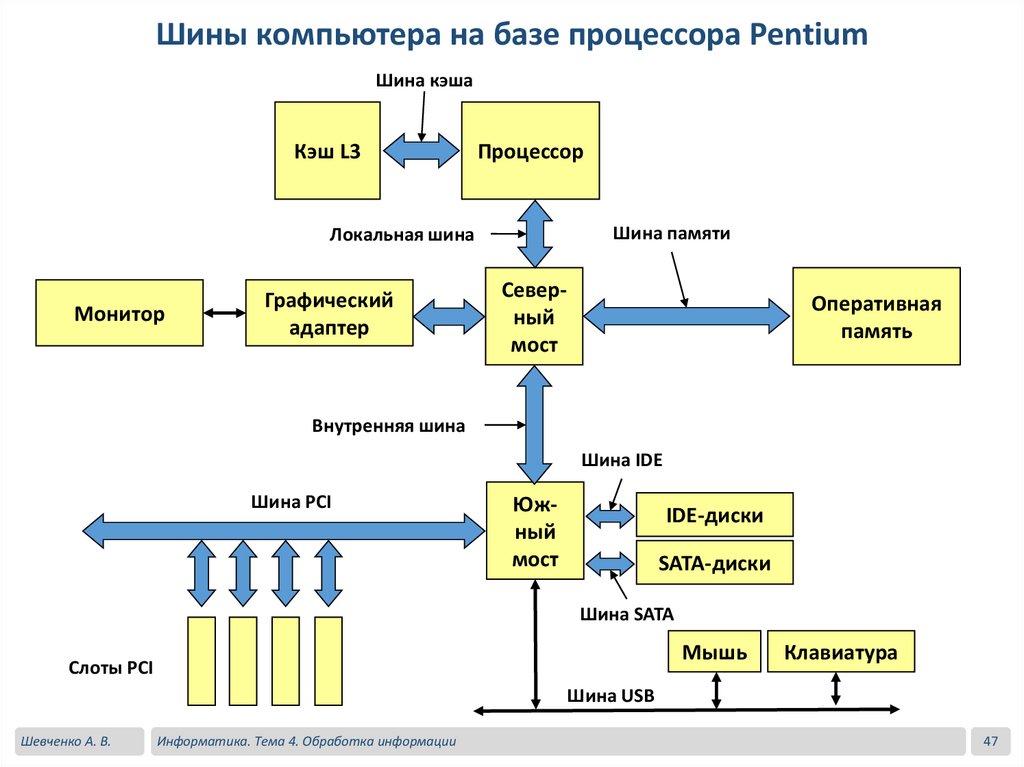

Шины компьютера на базе процессора PentiumШина кэша

Кэш L3

Процессор

Шина памяти

Локальная шина

Монитор

Графический

адаптер

Северный

мост

Оперативная

память

Внутренняя шина

Шина IDE

Шина PCI

Южный

мост

IDE-диски

SATA-диски

Шина SATA

Мышь

Слоты PCI

Клавиатура

Шина USB

Шевченко А. В.

Информатика. Тема 4. Обработка информации

47

48.

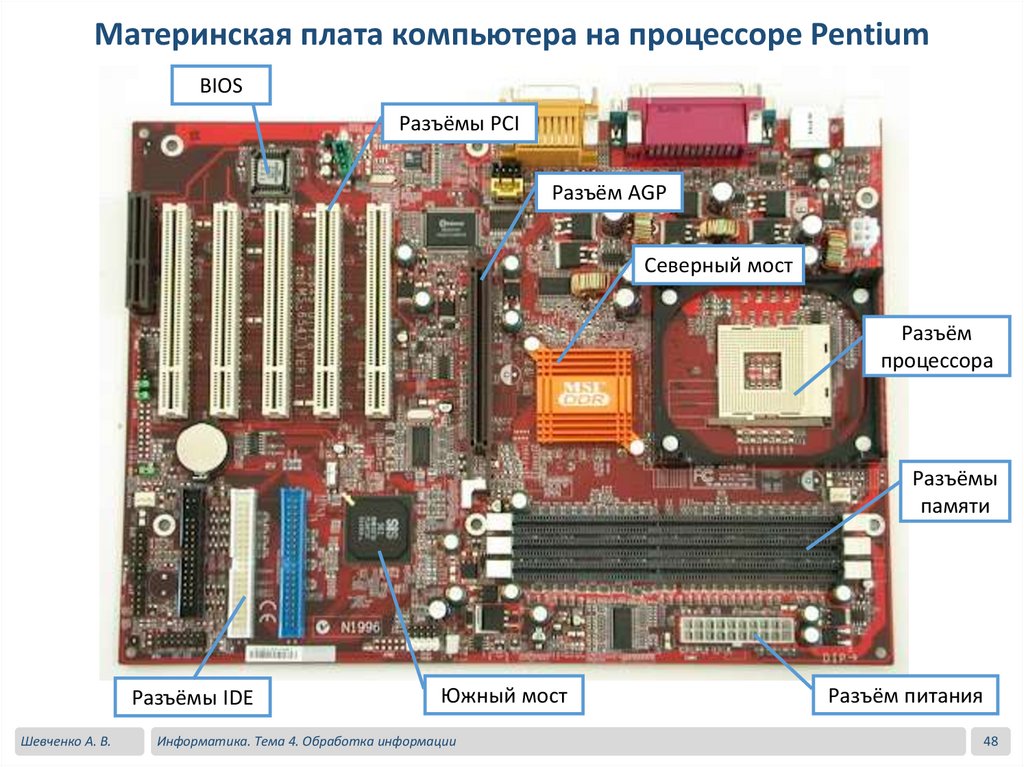

Материнская плата компьютера на процессоре PentiumBIOS

Разъёмы PCI

Разъём AGP

Северный мост

Разъём

процессора

Разъёмы

памяти

Разъёмы IDE

Шевченко А. В.

Южный мост

Информатика. Тема 4. Обработка информации

Разъём питания

48

49.

Процессор Pentium и его система охлажденияНа материнской плате компьютера с процессором Intel Pentium имеется специальное

гнездо, в которое устанавливается и фиксируется защёлкой процессор. Над ним

устанавливается и фиксируется защёлками радиатор охлаждения с вентилятором.

Шевченко А. В.

Информатика. Тема 4. Обработка информации

49

50.

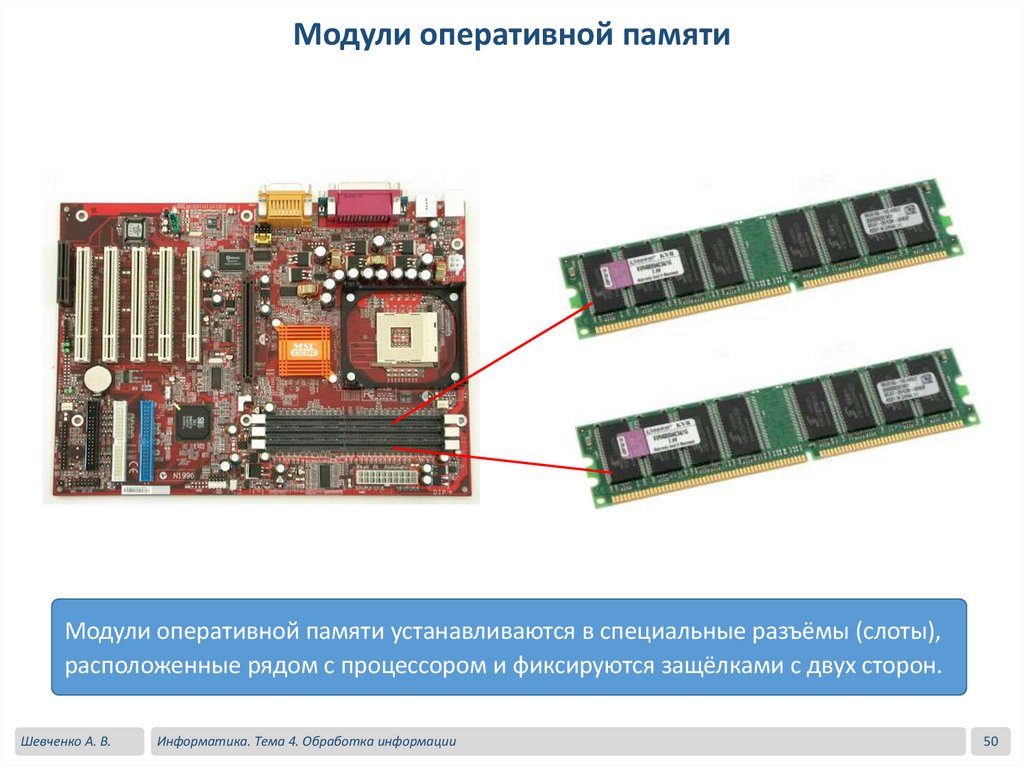

Модули оперативной памятиМодули оперативной памяти устанавливаются в специальные разъёмы (слоты),

расположенные рядом с процессором и фиксируются защёлками с двух сторон.

Шевченко А. В.

Информатика. Тема 4. Обработка информации

50

51.

Многоядерные процессорыВ многоядерном процессоре в одной микросхеме (на одном кристалле или в

одном корпусе) размещают несколько вычислительных ядер, каждое из которых

является полноценным микропроцессором с конвейерной обработкой команд.

Напротив, суперскалярность используется в меньшей степени, поскольку

распараллеливание осуществляется за счёт дублирования ядер процессора. В

многоядерных процессорах тактовая частота бывает намеренно снижена для

снижения энергопотребления (оно зависит как куб от частоты).

Шевченко А. В.

Информатика. Тема 4. Обработка информации

51

52.

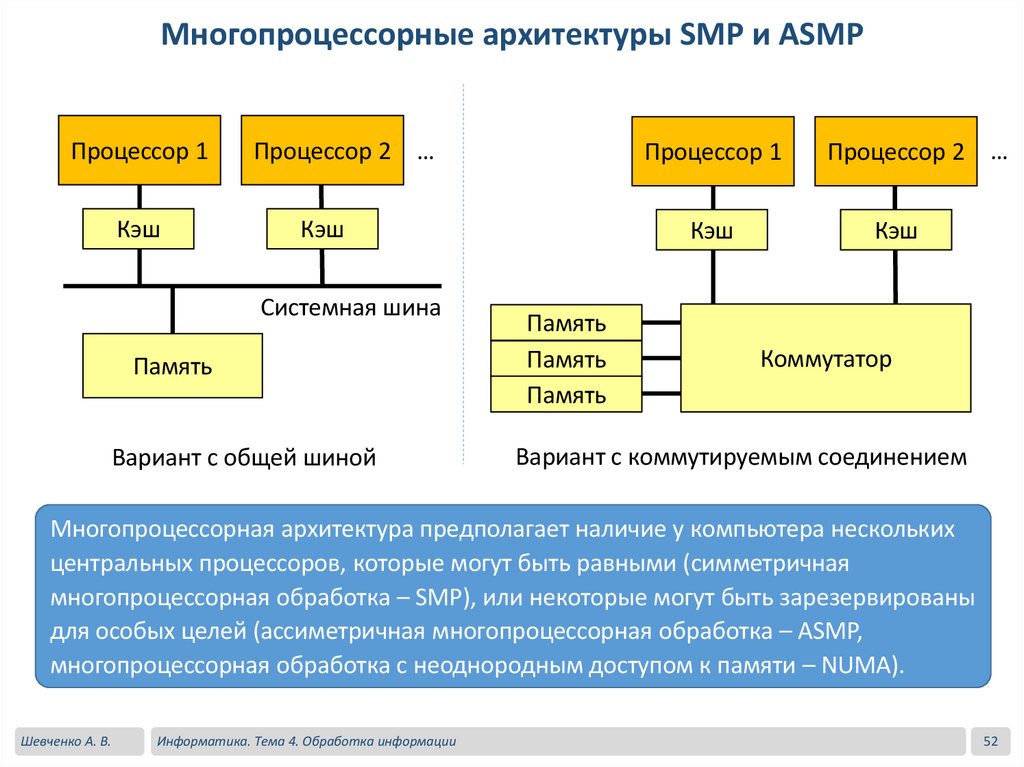

Многопроцессорные архитектуры SMP и ASMPПроцессор 1

Кэш

Процессор 2 …

Процессор 1

Кэш

Системная шина

Память

Вариант с общей шиной

Кэш

Память

Память

Память

Процессор 2 …

Кэш

Коммутатор

Вариант с коммутируемым соединением

Многопроцессорная архитектура предполагает наличие у компьютера нескольких

центральных процессоров, которые могут быть равными (симметричная

многопроцессорная обработка – SMP), или некоторые могут быть зарезервированы

для особых целей (ассиметричная многопроцессорная обработка – ASMP,

многопроцессорная обработка с неоднородным доступом к памяти – NUMA).

Шевченко А. В.

Информатика. Тема 4. Обработка информации

52

53.

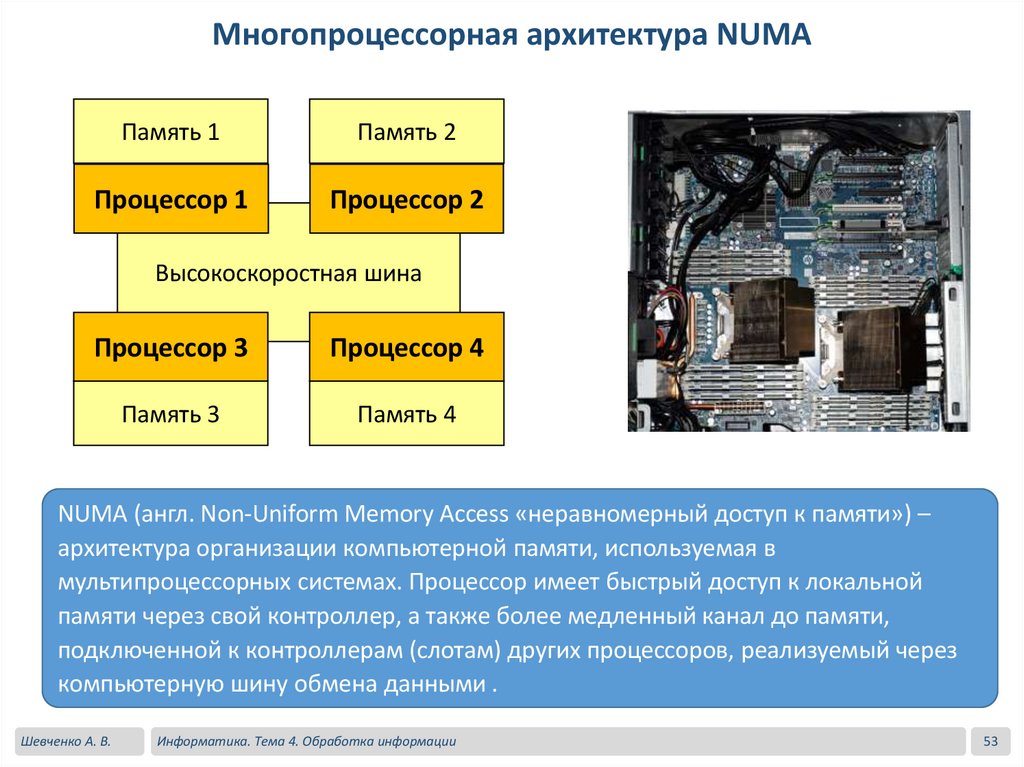

Многопроцессорная архитектура NUMAПамять 1

Память 2

Процессор 1

Процессор 2

Высокоскоростная шина

Процессор 3

Процессор 4

Память 3

Память 4

NUMA (англ. Non-Uniform Memory Access «неравномерный доступ к памяти») –

архитектура организации компьютерной памяти, используемая в

мультипроцессорных системах. Процессор имеет быстрый доступ к локальной

памяти через свой контроллер, а также более медленный канал до памяти,

подключенной к контроллерам (слотам) других процессоров, реализуемый через

компьютерную шину обмена данными .

Шевченко А. В.

Информатика. Тема 4. Обработка информации

53

electronics

electronics