Similar presentations:

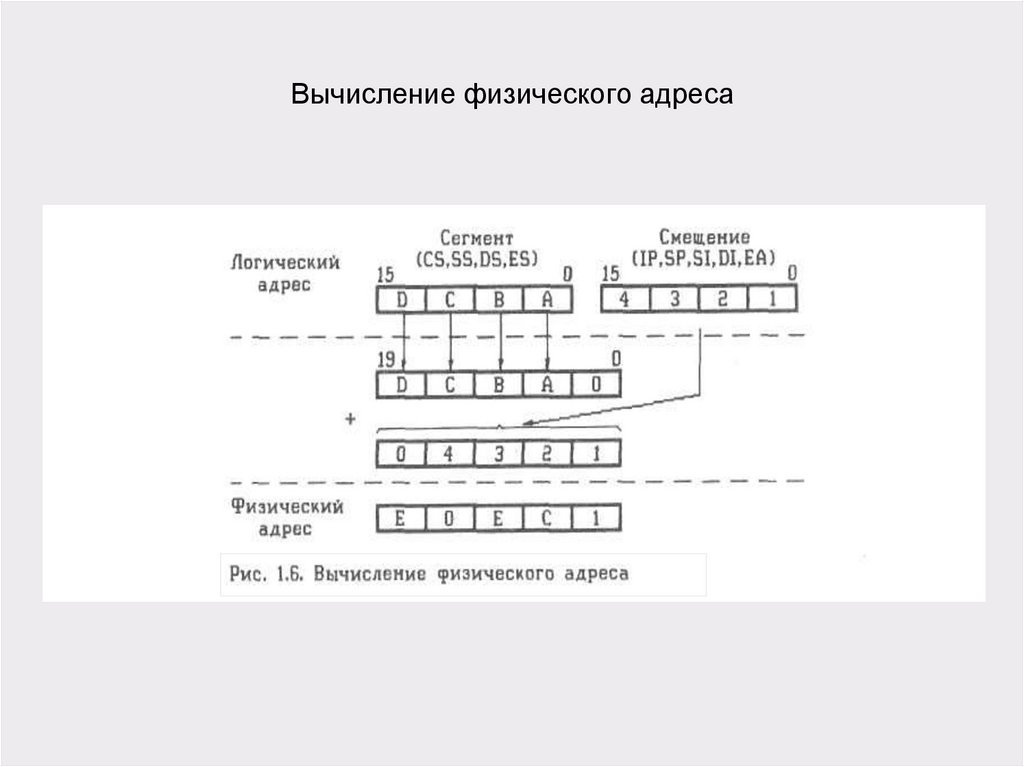

Вычисление физического адреса

1. Вычисление физического адреса

2.

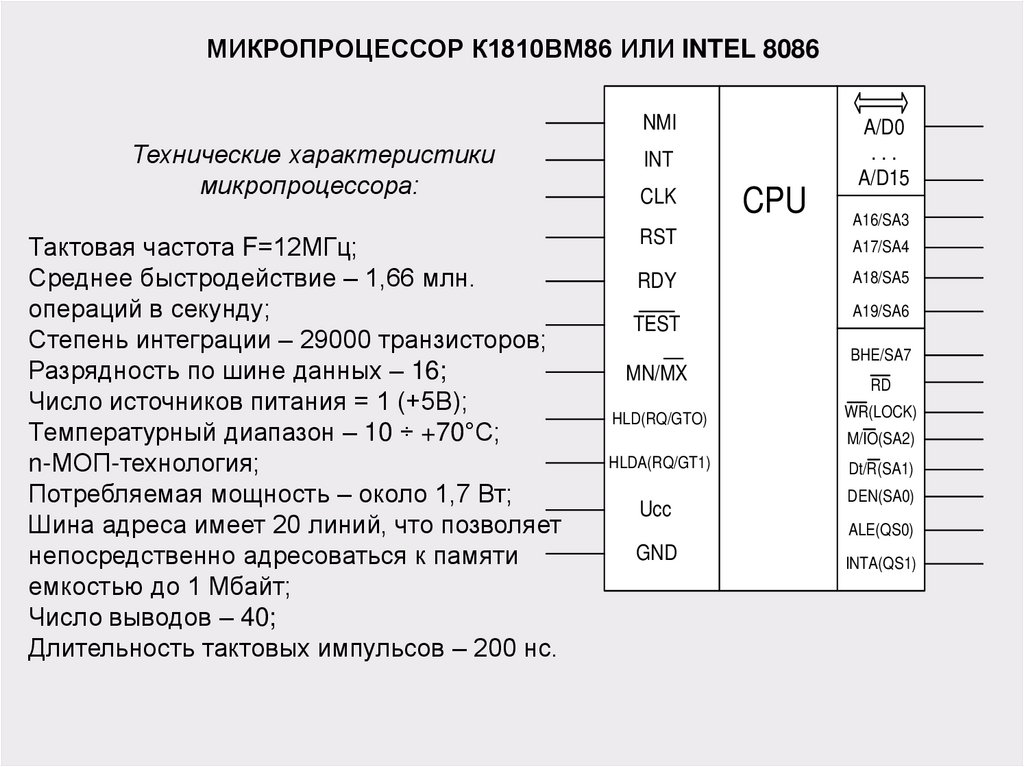

МИКРОПРОЦЕССОР К1810ВМ86 ИЛИ INTEL 8086NMI

Технические характеристики

микропроцессора:

Тактовая частота F=12МГц;

Среднее быстродействие – 1,66 млн.

операций в секунду;

Степень интеграции – 29000 транзисторов;

Разрядность по шине данных – 16;

Число источников питания = 1 (+5В);

Температурный диапазон – 10 ÷ +70°С;

n-МОП-технология;

Потребляемая мощность – около 1,7 Вт;

Шина адреса имеет 20 линий, что позволяет

непосредственно адресоваться к памяти

емкостью до 1 Мбайт;

Число выводов – 40;

Длительность тактовых импульсов – 200 нс.

INT

CLK

RST

RDY

TEST

CPU

A/D0

...

A/D15

A16/SA3

A17/SA4

A18/SA5

A19/SA6

BHE/SA7

MN/MX

HLD(RQ/GTO)

RD

WR(LOCK)

M/IO(SA2)

HLDA(RQ/GT1)

Ucc

Dt/R(SA1)

DEN(SA0)

ALE(QS0)

GND

INTA(QS1)

3.

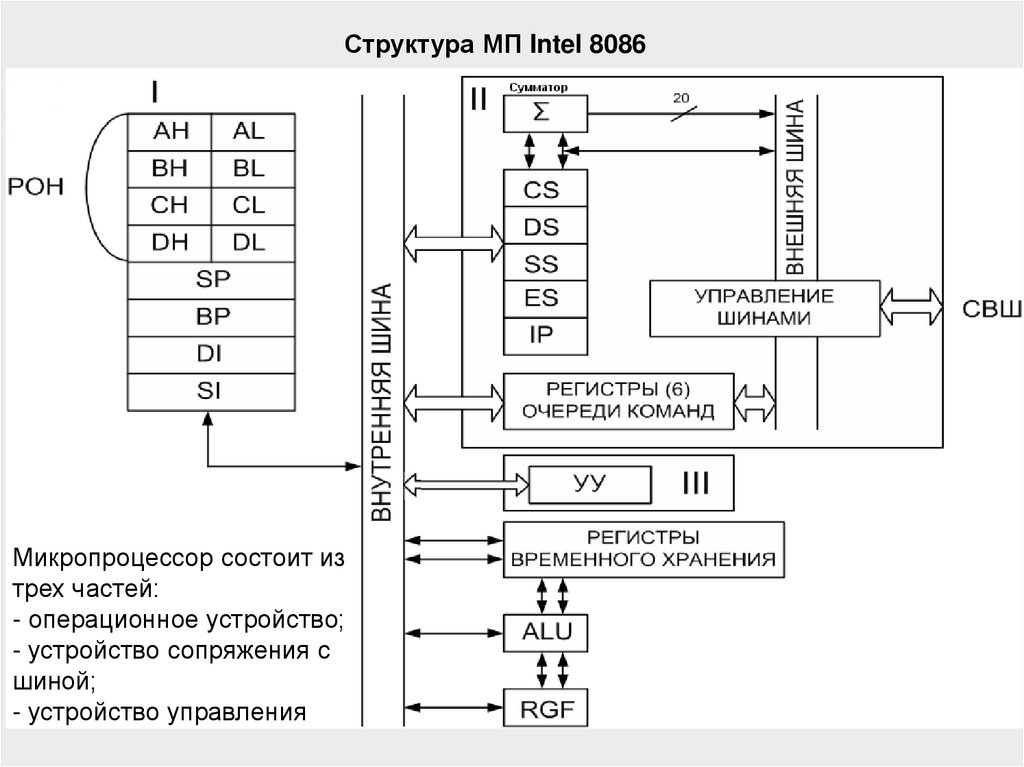

Структура МП Intel 8086Микропроцессор состоит из

трех частей:

- операционное устройство;

- устройство сопряжения с

шиной;

- устройство управления

4.

Система прерываний в МП Intel 8086ВНЕШНИЕ

ПРЕРЫВАНИЯ

МАСКИРУЕМЫЕ

ПРЕРЫВАНИЯ

INTR (тип n)

НЕМАСКИРУЕМЫЕ

ПРЕРЫВАНИЯ

NMI (тип 2)

Программные прерывания

Данные прерывания

осуществляются по 2-байтной

команде INTn или по

однобайтной команде INT3.

СИСТЕМА ПРЕРЫВАНИЙ

ПРОГРАММНЫЕ

ПРЕРЫВАНИЯ

ВНУТРЕННИЕ

ПРЕРЫВАНИЯ

Ошибка деления (тип 0)

Команда INTR

n (тип n)

Переполнение (тип 4)

PIC или ВУ

Команда INT3 (тип 3)

Пошаговый режим

(тип 1)

Внешние прерывания

Внешние прерывания бывают маскируемые и

немаскируемые. Если прерывание маскируемое,

Внутренние прерывания

то запрос может быть от контроллера прерываний

Внутренние прерывания

или внешнего устройства.

характеризуются типом, который

либо предопределен, либо

содержится в коде команды.

5.

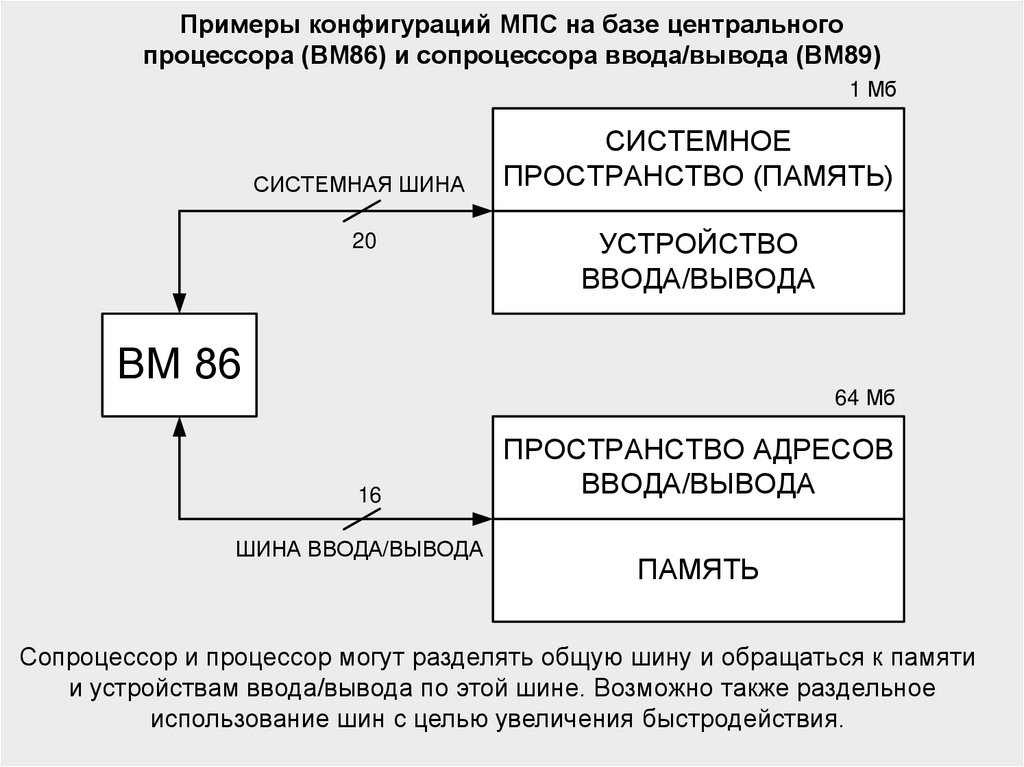

Примеры конфигураций МПС на базе центральногопроцессора (ВМ86) и сопроцессора ввода/вывода (ВМ89)

1 Мб

СИСТЕМНАЯ ШИНА

20

СИСТЕМНОЕ

ПРОСТРАНСТВО (ПАМЯТЬ)

УСТРОЙСТВО

ВВОДА/ВЫВОДА

ВМ 86

64 Мб

16

ШИНА ВВОДА/ВЫВОДА

ПРОСТРАНСТВО АДРЕСОВ

ВВОДА/ВЫВОДА

ПАМЯТЬ

Сопроцессор и процессор могут разделять общую шину и обращаться к памяти

и устройствам ввода/вывода по этой шине. Возможно также раздельное

использование шин с целью увеличения быстродействия.

6.

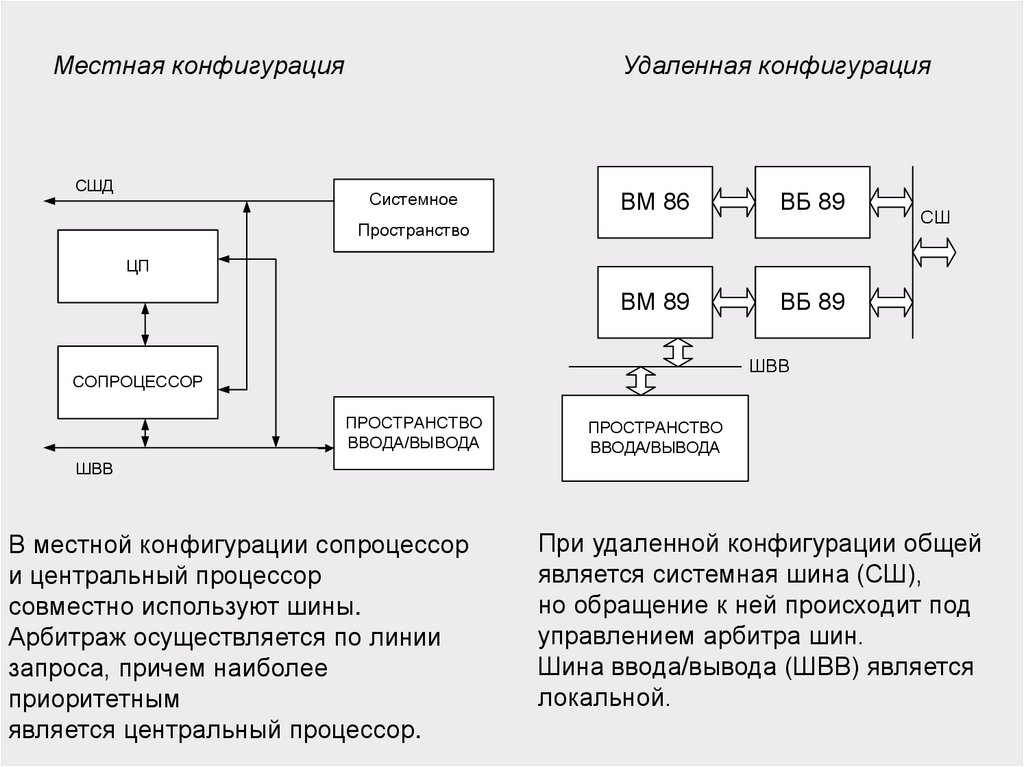

Местная конфигурацияСШД

Удаленная конфигурация

Системное

СП

ВМ 86

ВБ 89

ВМ 89

ВБ 89

Пространство

СШ

ЦП

ШВВ

СОПРОЦЕССОР

ПРОСТРАНСТВО

ВВОДА/ВЫВОДА

ПРОСТРАНСТВО

ВВОДА/ВЫВОДА

ШВВ

В местной конфигурации сопроцессор

и центральный процессор

совместно используют шины.

Арбитраж осуществляется по линии

запроса, причем наиболее

приоритетным

является центральный процессор.

При удаленной конфигурации общей

является системная шина (СШ),

но обращение к ней происходит под

управлением арбитра шин.

Шина ввода/вывода (ШВВ) является

локальной.

7.

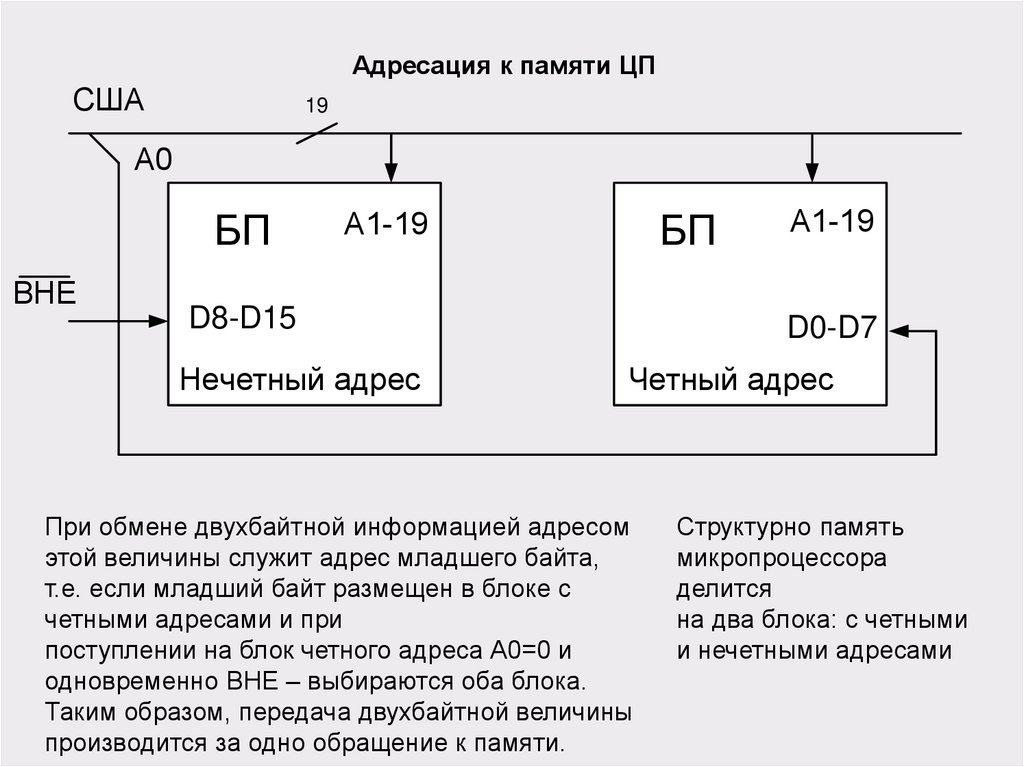

Адресация к памяти ЦПСША

19

А0

БП

ВНЕ

А1-19

БП

D8-D15

Нечетный адрес

А1-19

D0-D7

Четный адрес

При обмене двухбайтной информацией адресом

этой величины служит адрес младшего байта,

т.е. если младший байт размещен в блоке с

четными адресами и при

поступлении на блок четного адреса А0=0 и

одновременно ВНЕ – выбираются оба блока.

Таким образом, передача двухбайтной величины

производится за одно обращение к памяти.

Структурно память

микропроцессора

делится

на два блока: с четными

и нечетными адресами

8.

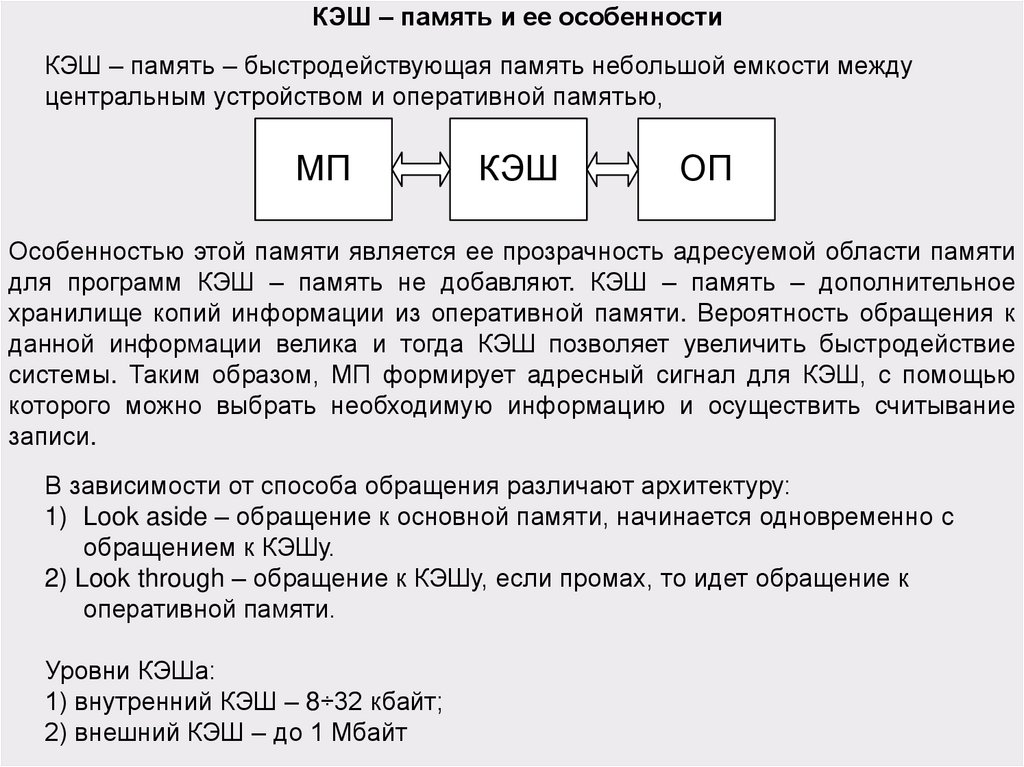

КЭШ – память и ее особенностиКЭШ – память – быстродействующая память небольшой емкости между

центральным устройством и оперативной памятью,

МП

КЭШ

ОП

Особенностью этой памяти является ее прозрачность адресуемой области памяти

для программ КЭШ – память не добавляют. КЭШ – память – дополнительное

хранилище копий информации из оперативной памяти. Вероятность обращения к

данной информации велика и тогда КЭШ позволяет увеличить быстродействие

системы. Таким образом, МП формирует адресный сигнал для КЭШ, с помощью

которого можно выбрать необходимую информацию и осуществить считывание

записи.

В зависимости от способа обращения различают архитектуру:

1) Look aside – обращение к основной памяти, начинается одновременно с

обращением к КЭШу.

2) Look through – обращение к КЭШу, если промах, то идет обращение к

оперативной памяти.

Уровни КЭШа:

1) внутренний КЭШ – 8÷32 кбайт;

2) внешний КЭШ – до 1 Мбайт

9.

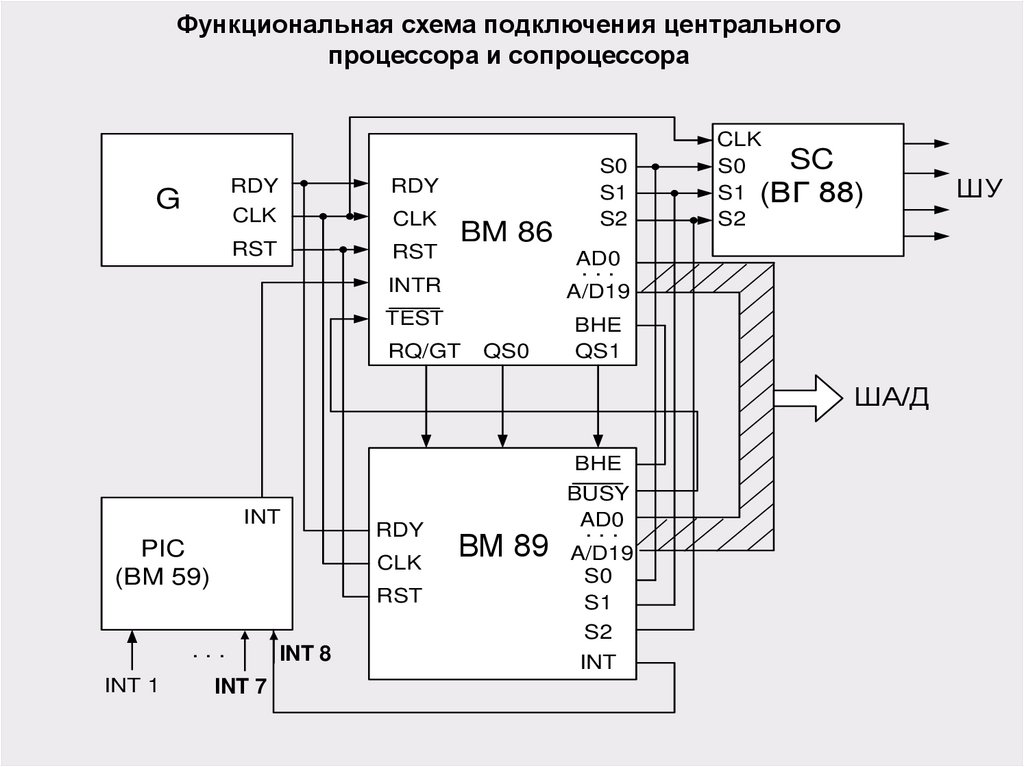

Функциональная схема подключения центральногопроцессора и сопроцессора

G

RDY

RDY

CLK

CLK

RST

RST

BM 86

S0

S1

S2

CLK

SC

S0

S1 (ВГ 88)

S2

AD0

...

INTR

A/D19

TEST

BHE

QS1

RQ/GT

QS0

ША/Д

BHE

INT

PIC

(BM 59)

CLK

RST

...

INT 1

RDY

INT 7

BM

ВМ 86

89

BUSY

AD0

...

A/D19

S0

S1

S2

INT 8

INT

ШУ

10.

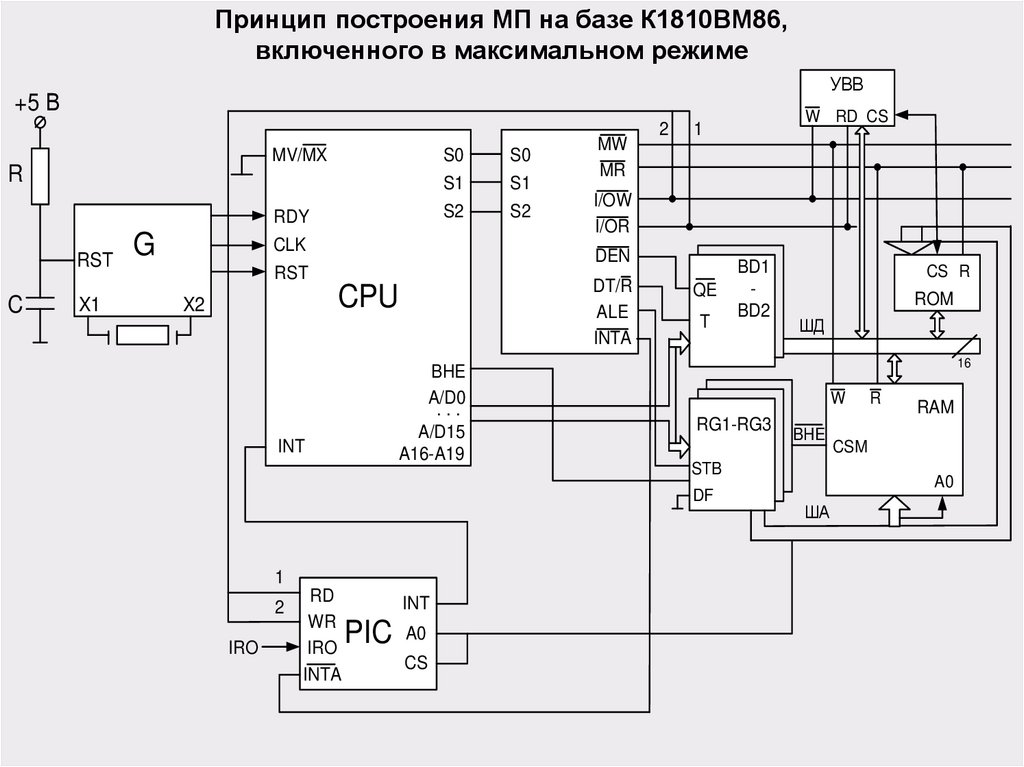

Принцип построения МП на базе К1810ВМ86,включенного в максимальном режиме

УВВ

+5 В

MV/MX

R

RDY

RST

C

X1

G

S0

S0

S1

S1

S2

S2

CLK

I/OW

I/OR

DT/R

ALE

INTA

CPU

BHE

A/D0

...

A/D15

A16-A19

INT

QE

T

2

IRO

RD

WR

IRO

INTA

INT

PIC

A0

CS

BD1

BD2

CS R

ROM

ШД

16

W

RG1-RG3

BHE

STB

DF

1

W RD CS

1

DEN

RST

X2

MW

MR

2

R

RAM

CSM

A0

ША

11.

МИКРОКОНТРОЛЛЕРЫВнутренние компоненты МК:

АЛУ, устройство управления, регистры, счетчик

команд, стековый указатель, имеется внутренняя

(резидентная) память программ, внутренняя память

данных,

последовательный

и

параллельный

интерфейсы, таймеры-счетчики, сторожевой таймер,

генератор, АПЦ-преобразователь, ШИМ и др.

Достоинства микроконтроллеров:

- дешевизна;

- простота;

- компактность;

- RISC-архитектура.

12.

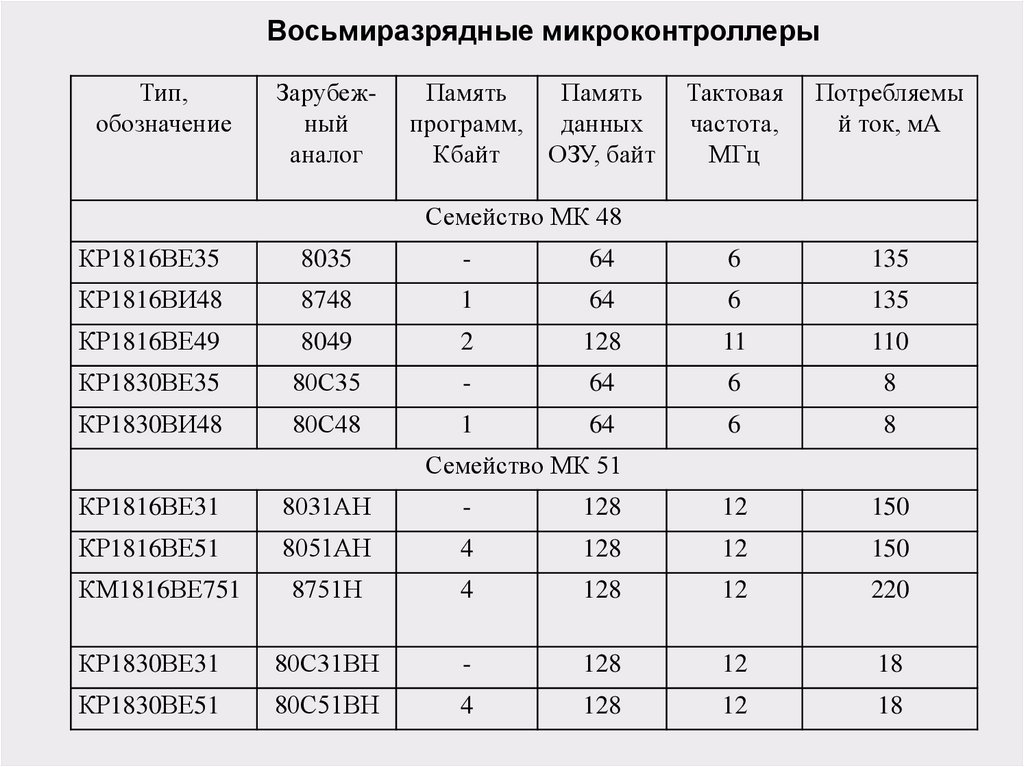

Восьмиразрядные микроконтроллерыТип,

обозначение

Зарубежный

аналог

Память

Память

программ, данных

Кбайт

ОЗУ, байт

Тактовая

частота,

МГц

Потребляемы

й ток, мА

Семейство МК 48

КР1816ВЕ35

8035

-

64

6

135

КР1816ВИ48

8748

1

64

6

135

КР1816ВЕ49

8049

2

128

11

110

КР1830ВЕ35

80С35

-

64

6

8

КР1830ВИ48

80С48

1

64

6

8

Семейство МК 51

КР1816ВЕ31

8031АН

-

128

12

150

КР1816ВЕ51

8051АН

4

128

12

150

8751Н

4

128

12

220

КР1830ВЕ31

80С31ВН

-

128

12

18

КР1830ВЕ51

80С51ВН

4

128

12

18

КМ1816ВЕ751

13.

Р1.0Р1.1

Р1.2

Порт Р1.3

Р1.4

1

Р1.5

Р1.6

Р1.7

СБР/АП

ВХПР

ВЫХПЕР

ЗПР0

Порт ЗПР1

3

Т0

Т1

ЗП

ЧТ

Х2

Х1

ОБЩ

(RST/VPD)

(RXD)

(TXD)

(INT0)

(INT1)

(WR)

(RD)

(XTAL2)

(XTAL1)

(VSS)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

КМ1816ВЕ51

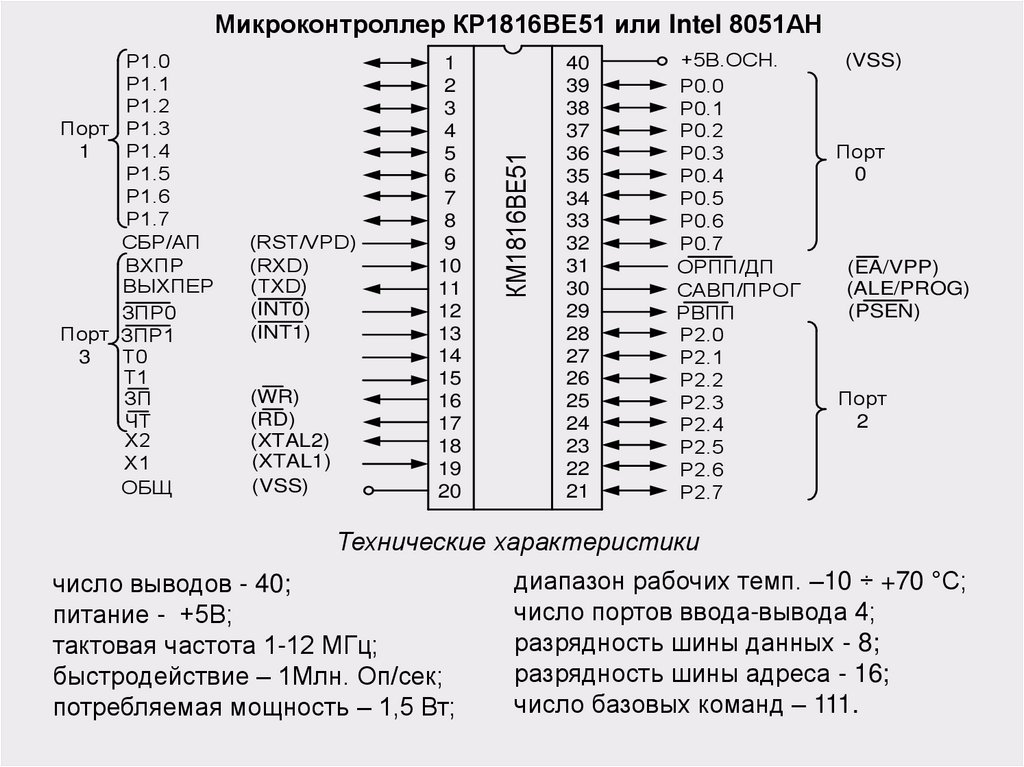

Микроконтроллер КР1816ВЕ51 или Intel 8051АН

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

+5В.ОСН.

Р0.0

Р0.1

Р0.2

Р0.3

Р0.4

Р0.5

Р0.6

Р0.7

ОРПП/ДП

САВП/ПРОГ

РВПП

Р2.0

Р2.1

Р2.2

Р2.3

Р2.4

Р2.5

Р2.6

Р2.7

(VSS)

Порт

0

(EA/VPP)

(ALE/PROG)

(PSEN)

Порт

2

Технические характеристики

число выводов - 40;

питание - +5В;

тактовая частота 1-12 МГц;

быстродействие – 1Млн. Оп/сек;

потребляемая мощность – 1,5 Вт;

диапазон рабочих темп. –10 ÷ +70 °С;

число портов ввода-вывода 4;

разрядность шины данных - 8;

разрядность шины адреса - 16;

число базовых команд – 111.

14.

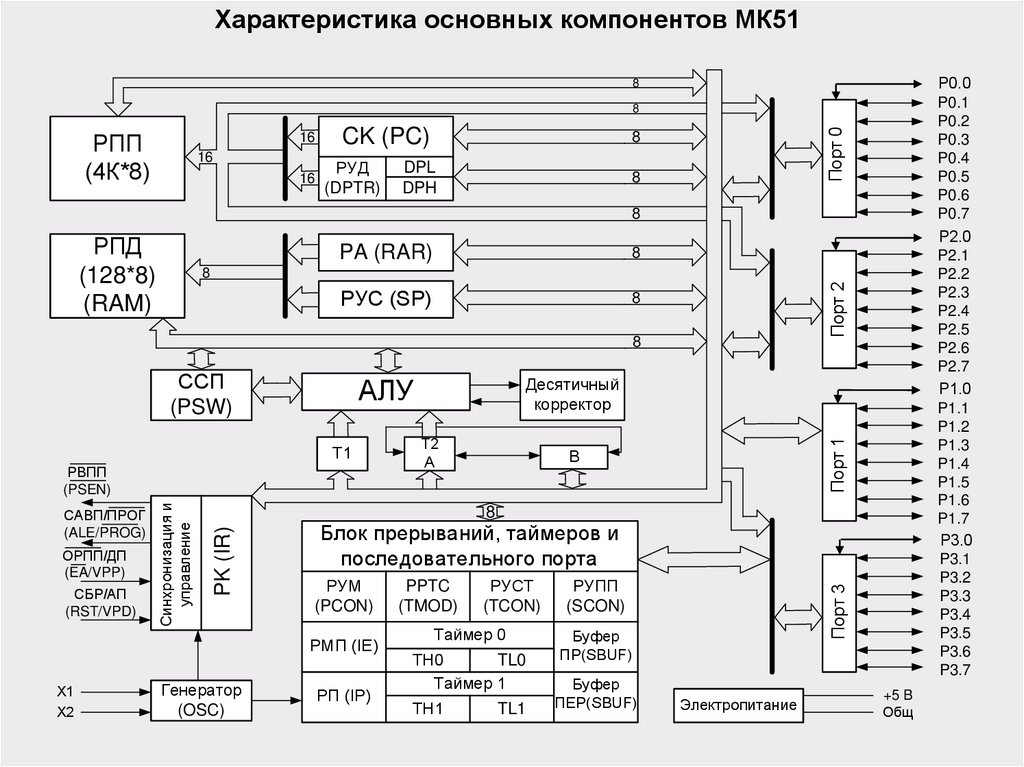

Характеристика основных компонентов МК51Р0.0

P0.1

P0.2

P0.3

P0.4

P0.5

P0.6

P0.7

Р2.0

P2.1

P2.2

P2.3

P2.4

P2.5

P2.6

P2.7

Р1.0

P1.1

P1.2

P1.3

P1.4

P1.5

P1.6

P1.7

Р3.0

P3.1

P3.2

P3.3

P3.4

P3.5

P3.6

P3.7

8

РПП

(4К*8)

16

16

16

CK (PC)

РУД

(DPTR)

Порт 0

8

8

DPL

DPH

8

8

РПД

(128*8)

(RAM)

PA (RAR)

8

РУС (SP)

8

Порт 2

8

8

АЛУ

Т1

СБР/АП

(RST/VPD)

Блок прерываний, таймеров и

последовательного порта

РУМ

(PCON)

РМП (IE)

Х1

Х2

В

Генератор

(OSC)

РП (IP)

PPTC

(TMOD)

РУСТ

(TCON)

Таймер 0

ТН0

TL0

Таймер 1

ТН1

TL1

РУПП

(SCON)

Порт 3

ОРПП/ДП

(EA/VPP)

Т2

А

8

PK (IR)

САВП/ПРОГ

(ALE/PROG)

Синхронизация и

управление

РВПП

(PSEN)

Десятичный

корректор

Порт 1

ССП

(PSW)

Буфер

ПР(SBUF)

Буфер

ПEР(SBUF)

Электропитание

+5 B

Общ

15.

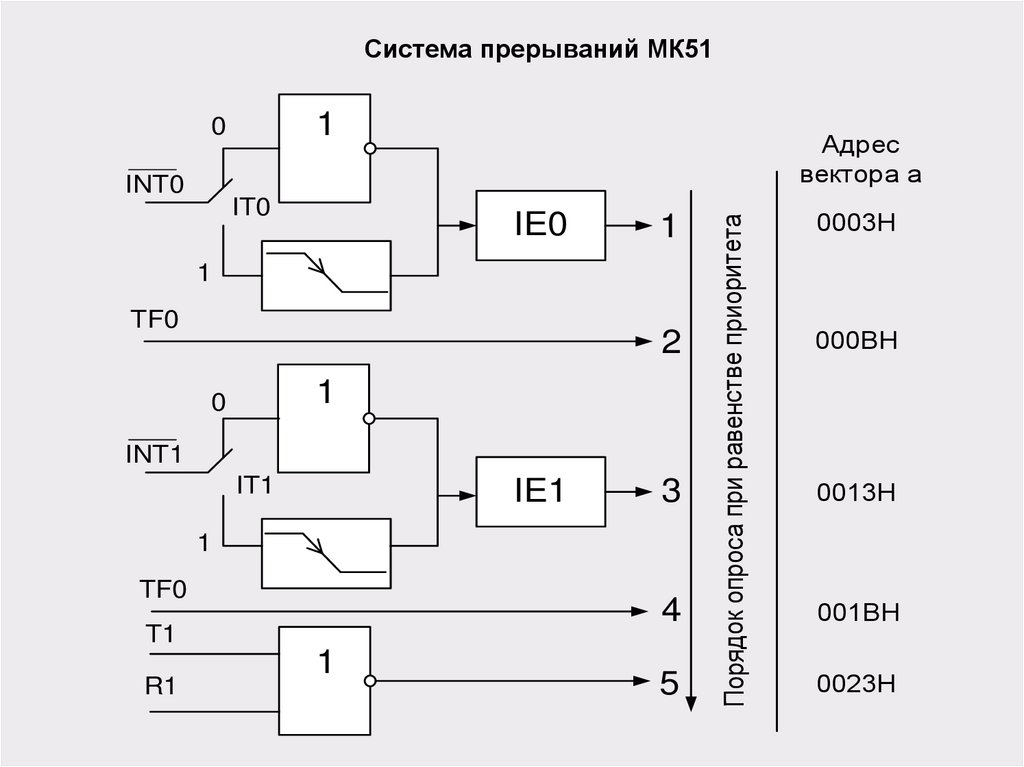

Система прерываний МК511

0

Адрес

вектора а

IT0

IE0

1

1

TF0

2

1

0

INT1

IT1

IE1

3

1

TF0

4

T1

R1

1

5

Порядок опроса при равенстве приоритета

INT0

0003Н

000ВН

0013Н

001ВН

0023Н

16.

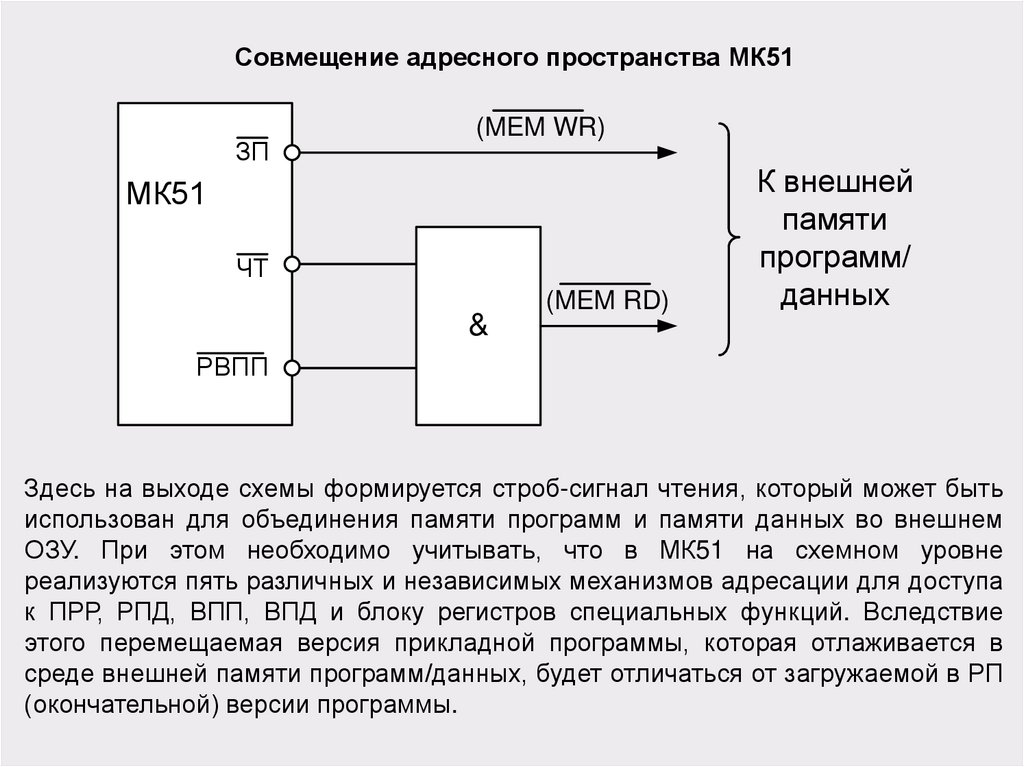

Совмещение адресного пространства МК51ЗП

(MEM WR)

МК51

ЧТ

&

(MEM RD)

К внешней

памяти

программ/

данных

РВПП

Здесь на выходе схемы формируется строб-сигнал чтения, который может быть

использован для объединения памяти программ и памяти данных во внешнем

ОЗУ. При этом необходимо учитывать, что в МК51 на схемном уровне

реализуются пять различных и независимых механизмов адресации для доступа

к ПРР, РПД, ВПП, ВПД и блоку регистров специальных функций. Вследствие

этого перемещаемая версия прикладной программы, которая отлаживается в

среде внешней памяти программ/данных, будет отличаться от загружаемой в РП

(окончательной) версии программы.

17. Последовательности выборки и выполнения команд

18. Программирование МК

C1BQ

C2

19. Запись бита защиты Бит защиты РПП, будучи установлен, запрещает доступ к РПП любыми внешними средствами

C1BQ

C2

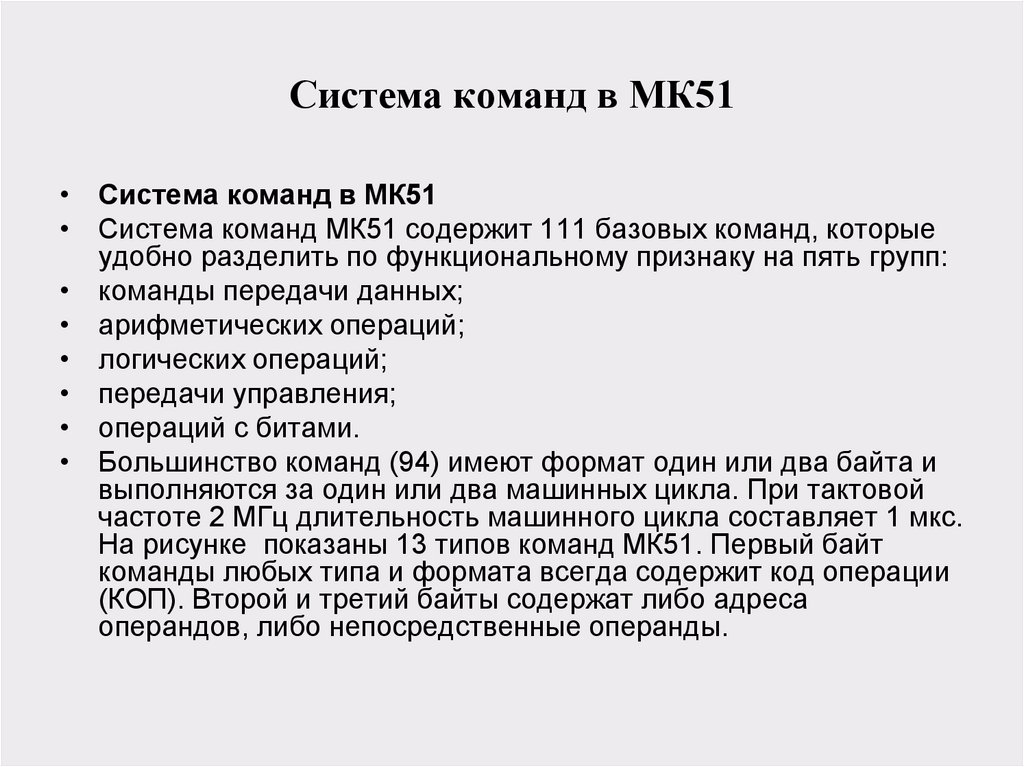

20. Система команд в МК51

• Система команд в МК51• Система команд МК51 содержит 111 базовых команд, которые

удобно разделить по функциональному признаку на пять групп:

• команды передачи данных;

• арифметических операций;

• логических операций;

• передачи управления;

• операций с битами.

• Большинство команд (94) имеют формат один или два байта и

выполняются за один или два машинных цикла. При тактовой

частоте 2 МГц длительность машинного цикла составляет 1 мкс.

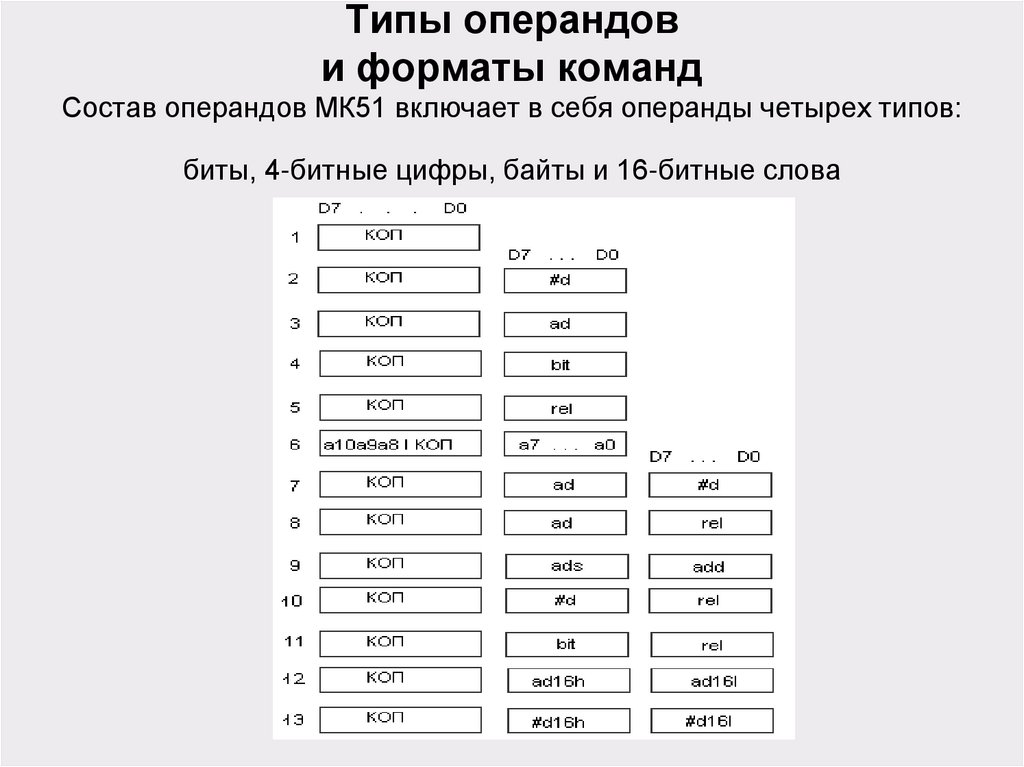

На рисунке показаны 13 типов команд МК51. Первый байт

команды любых типа и формата всегда содержит код операции

(КОП). Второй и третий байты содержат либо адреса

операндов, либо непосредственные операнды.

21. Типы операндов и форматы команд Состав операндов МК51 включает в себя операнды четырех типов: биты, 4-битные цифры, байты и

16-битные слова22.

Группа команд передачи данныхНазвание команды

Мнемокод

КОП

Т

Б

Ц

Операция

Пересылка в

аккумулятор из

регистра (n = 0 - 7)

MOV A, Rn

11101rrr

1

1

1

(A) = (Rn)

Пересылка в

аккумулятор прямо

адресуемого байта

MOV A, ad

11100101

3

2

1

(A) = (ad)

1110011i

1

1

1

(A) = ((Ri))

MOV A, #d

01110100

2

2

1

(A) = #d

MOV Rn, A

11111rrr

1

1

1

(Rn) = (A)

MOV Rn, ad

10101rrr

3

2

2

<font size="4

Пересылка в

аккумулятор байта из MOV A, @Ri

РДП (i = 0, 1)

Загрузка в

аккумулятор

константы

Пересылка в регистр

из аккумулятора

Пересылка в регистр

прямо адресуемого

байта

23.

Схема подключения МК к клавиатуре и дисплею сиспользованием контроллера, клавиатуры и дисплея

МК51

SMS

SMC

G

RS

CLK

RS

DD1

КР580 ВД79

Клавиатура

_

*

/

RL3

0

1

2

3

8

9

A

B

F1

RL4

4

C

F2

RL5

5

6

7

D

F3

E

F

F4

F5

P0.0

...

P0.7

DB0

...

DB7

RL0

P3.6

P3.7

P1.0

P1.1

ALE

WR

RD

AO

IRQ

CLK

RL1

RL2

RL6

RS

RL7

CS

CNTL

VD1-VD3

Shift

PCKD

1

SL0

SL1

2

3

SL2

DC

DD3

BD

OB

OA

0

1

2

3

0

1

2

3

4

4

5

6

7

5

6

7

R

4

4

HG

...

abcdefgh

24.

Расширители, подключаемые к МККР580 ВР43

( С МК )

ALE/PROG

P2.5

P2.0

P2.1

P2.2

P2.3

PROG

CS

P2.0

P2.1

P2.2

P2.3

P4.0

...

P4.3

P5.0

...

P5.3

MUX IOS

5V

0V

P6.0

...

P6.3

P7.0

...

P7.3

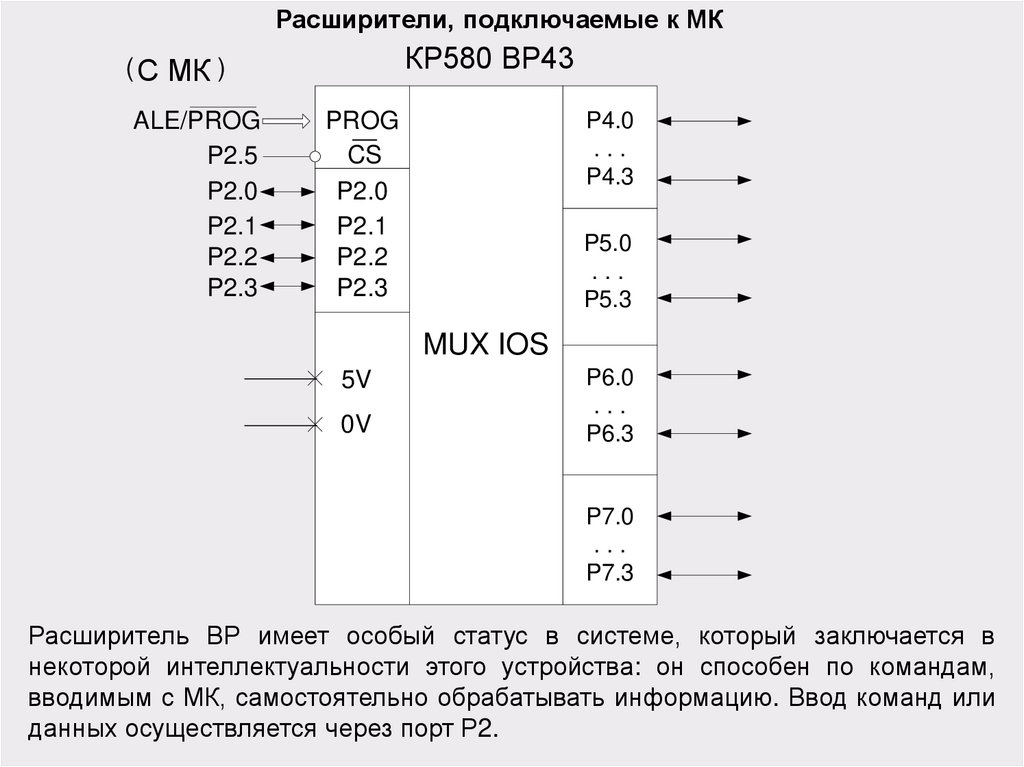

Расширитель ВР имеет особый статус в системе, который заключается в

некоторой интеллектуальности этого устройства: он способен по командам,

вводимым с МК, самостоятельно обрабатывать информацию. Ввод команд или

данных осуществляется через порт Р2.

25.

44

P2

МК-51

P4

P2

PROG ВР43

PROG

P2.5

4

P5

4

P6

4

CS

P7

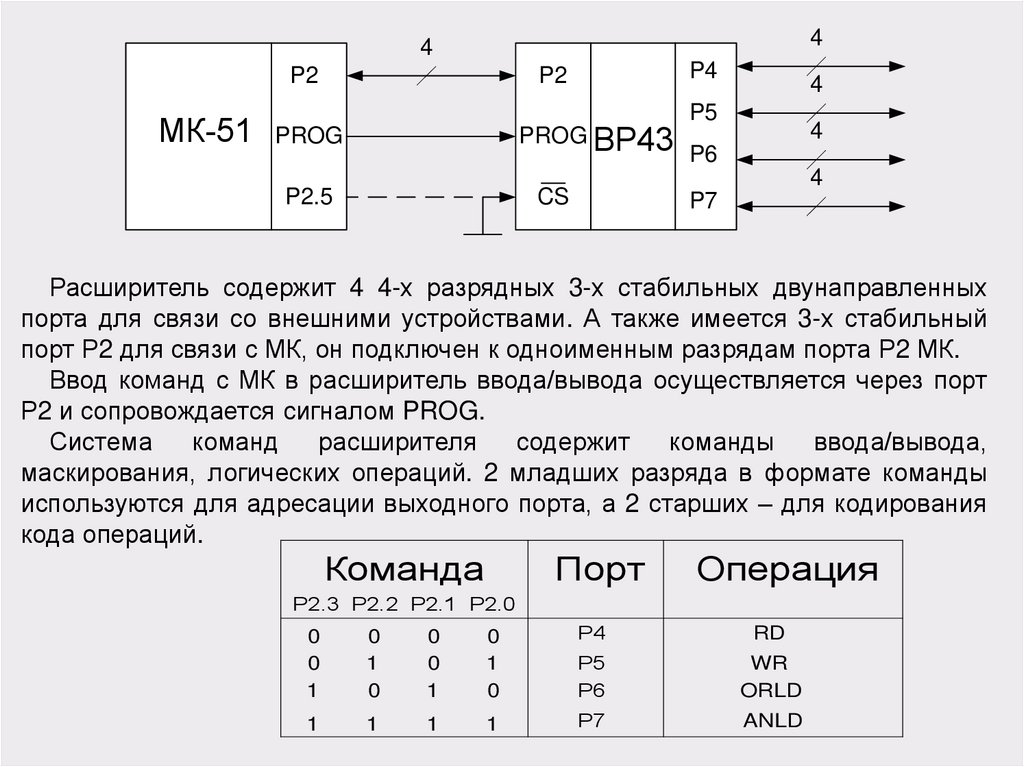

Расширитель содержит 4 4-х разрядных 3-х стабильных двунаправленных

порта для связи со внешними устройствами. А также имеется 3-х стабильный

порт Р2 для связи с МК, он подключен к одноименным разрядам порта Р2 МК.

Ввод команд с МК в расширитель ввода/вывода осуществляется через порт

Р2 и сопровождается сигналом PROG.

Система

команд

расширителя

содержит

команды

ввода/вывода,

маскирования, логических операций. 2 младших разряда в формате команды

используются для адресации выходного порта, а 2 старших – для кодирования

кода операций.

Команда

Порт

Операция

Р2.3 Р2.2 Р2.1 Р2.0

0

0

1

0

1

0

0

0

1

0

1

0

Р4

RD

Р5

Р6

WR

ORLD

1

1

1

1

Р7

ANLD

26.

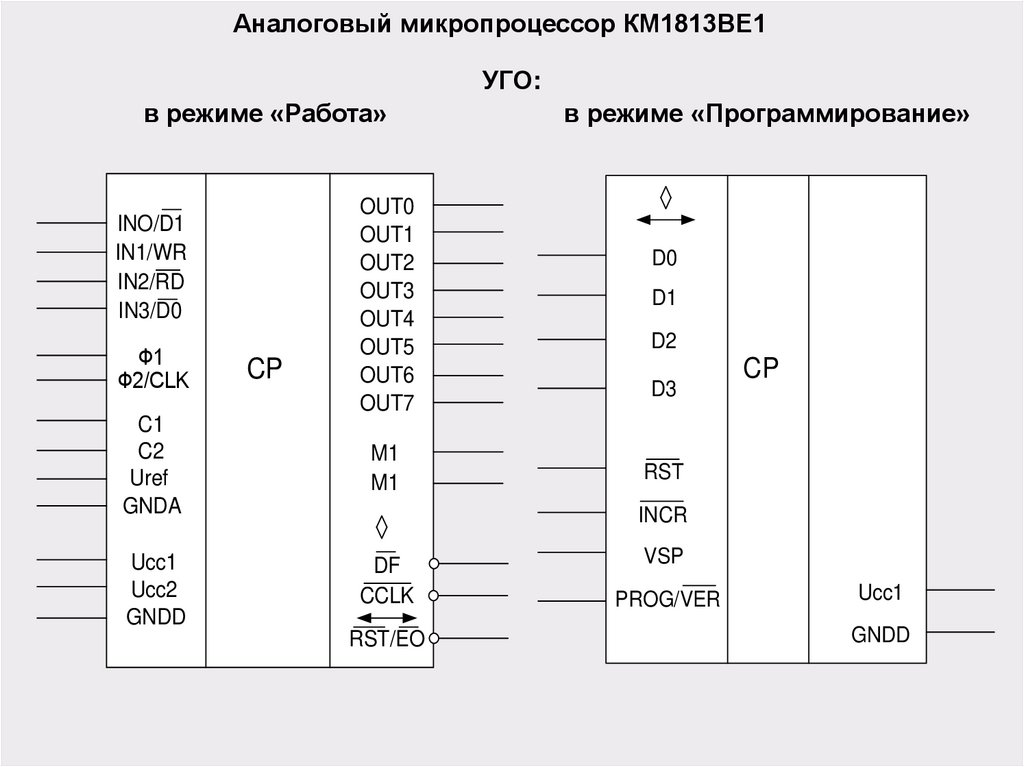

Аналоговый микропроцессор КМ1813ВЕ1УГО:

в режиме «Работа»

INO/D1

IN1/WR

IN2/RD

IN3/D0

Ф1

Ф2/CLK

CP

OUT0

OUT1

OUT2

OUT3

OUT4

OUT5

OUT6

OUT7

C1

C2

Uref

GNDA

M1

M1

Ucc1

Ucc2

GNDD

DF

CCLK

в режиме «Программирование»

D0

D1

D2

D3

CP

RST

INCR

RST/EO

VSP

PROG/VER

Ucc1

GNDD

27.

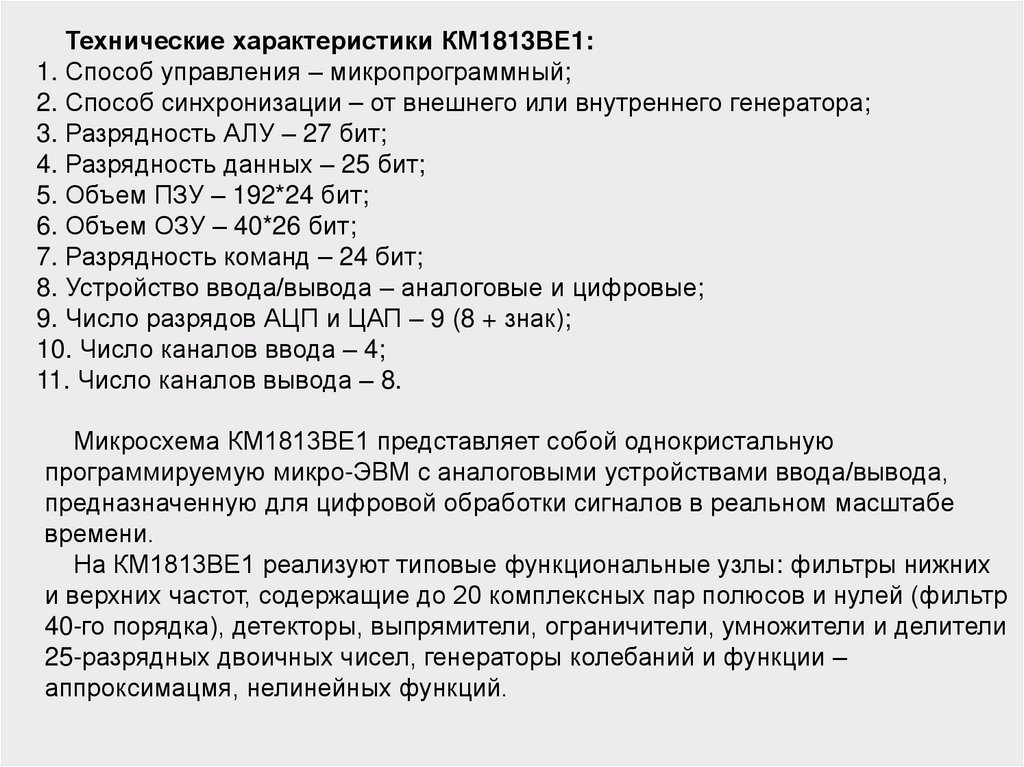

Технические характеристики КМ1813ВЕ1:1. Способ управления – микропрограммный;

2. Способ синхронизации – от внешнего или внутреннего генератора;

3. Разрядность АЛУ – 27 бит;

4. Разрядность данных – 25 бит;

5. Объем ПЗУ – 192*24 бит;

6. Объем ОЗУ – 40*26 бит;

7. Разрядность команд – 24 бит;

8. Устройство ввода/вывода – аналоговые и цифровые;

9. Число разрядов АЦП и ЦАП – 9 (8 + знак);

10. Число каналов ввода – 4;

11. Число каналов вывода – 8.

Микросхема КМ1813ВЕ1 представляет собой однокристальную

программируемую микро-ЭВМ с аналоговыми устройствами ввода/вывода,

предназначенную для цифровой обработки сигналов в реальном масштабе

времени.

На КМ1813ВЕ1 реализуют типовые функциональные узлы: фильтры нижних

и верхних частот, содержащие до 20 комплексных пар полюсов и нулей (фильтр

40-го порядка), детекторы, выпрямители, ограничители, умножители и делители

25-разрядных двоичных чисел, генераторы колебаний и функции –

аппроксимацмя, нелинейных функций.

28.

Структура системы самоконтроляМикропроцессор

Адаптер

Срыв

ОШ

Блок контроля

(счетчики)

Основная память

Дополнительная память

29.

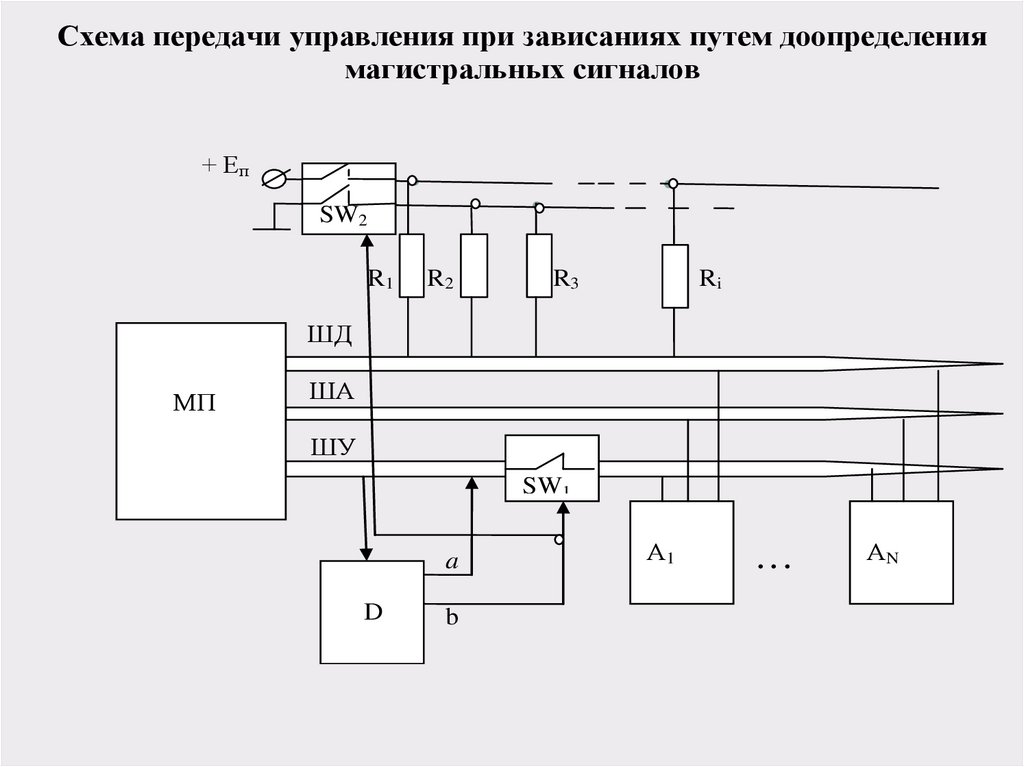

Схема передачи управления при зависаниях путем доопределениямагистральных сигналов

+ Еп

SW2

aаа

R1

R2

R3

Ri

ШД

МП

ША

ШУ

SW1

Aaf

D

МП

a

А1

b

МП

...

АN

МП

30.

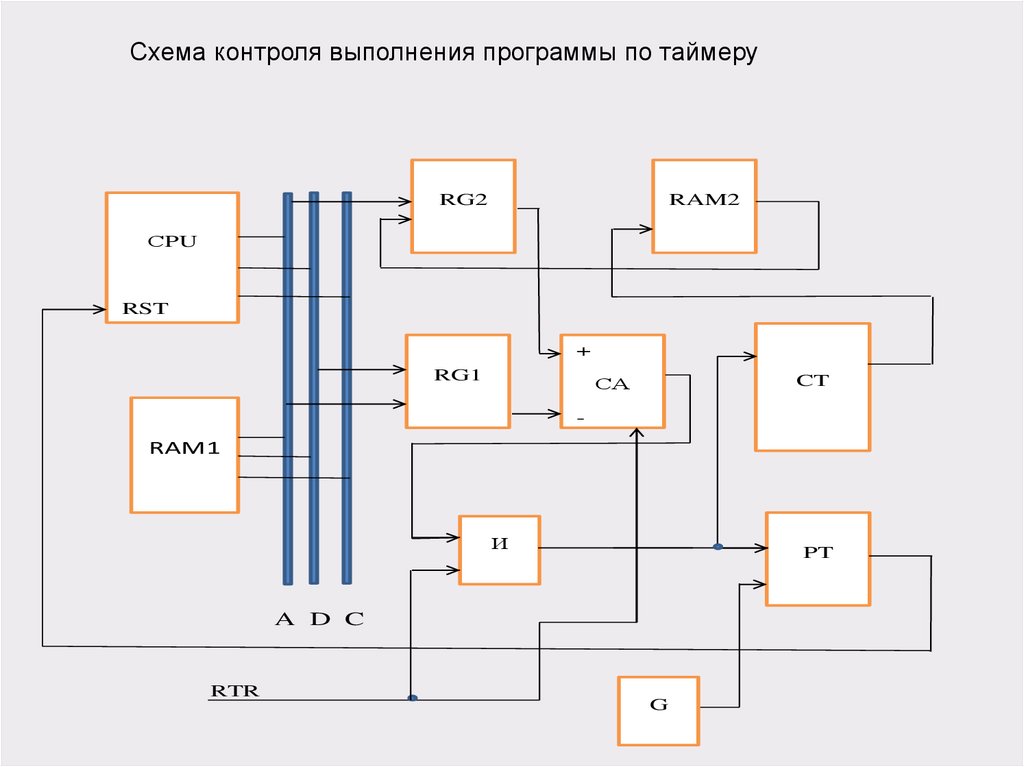

Схема контроля выполнения программы по таймеруRG2

RAM2

СPU

RST

+

RG1

CT

СА

-____

RAM1

И

PT

A D C

RTR

G

31.

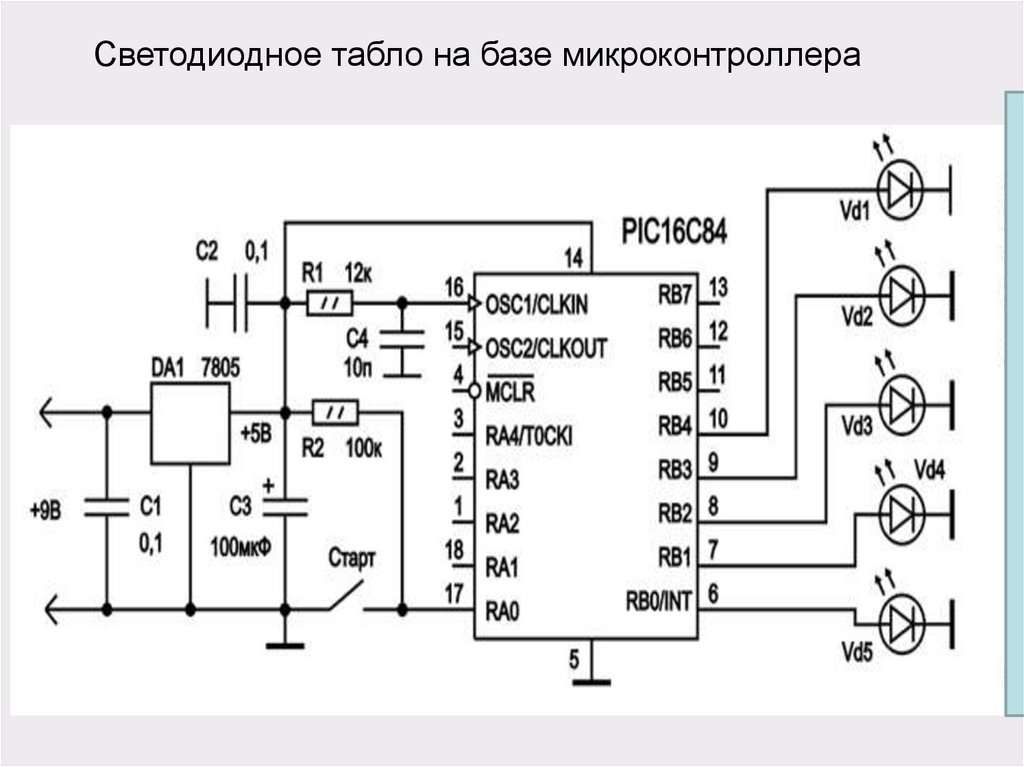

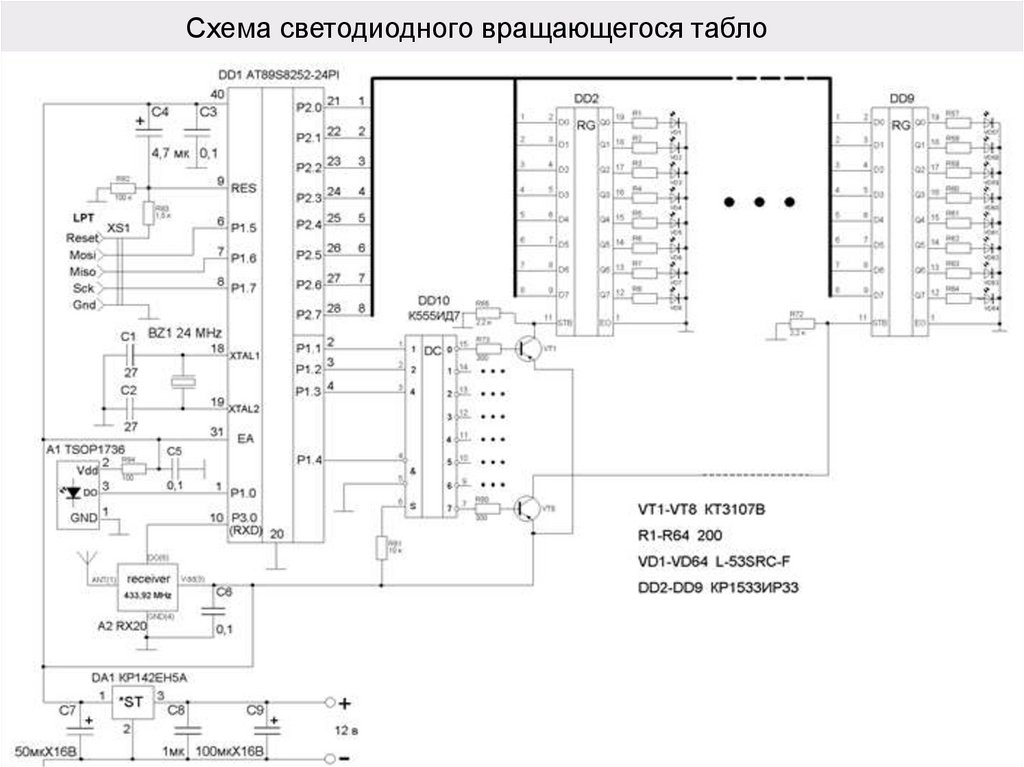

Светодиодное табло на базе микроконтроллера32.

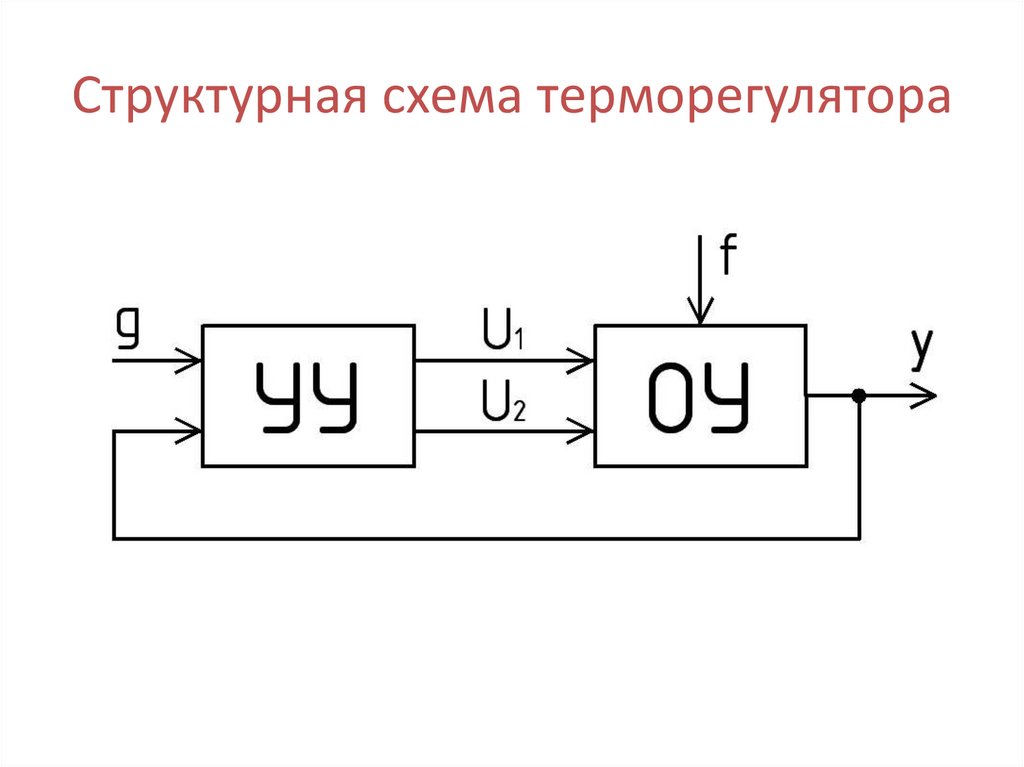

Схема светодиодного вращающегося табло33. Структурная схема терморегулятора

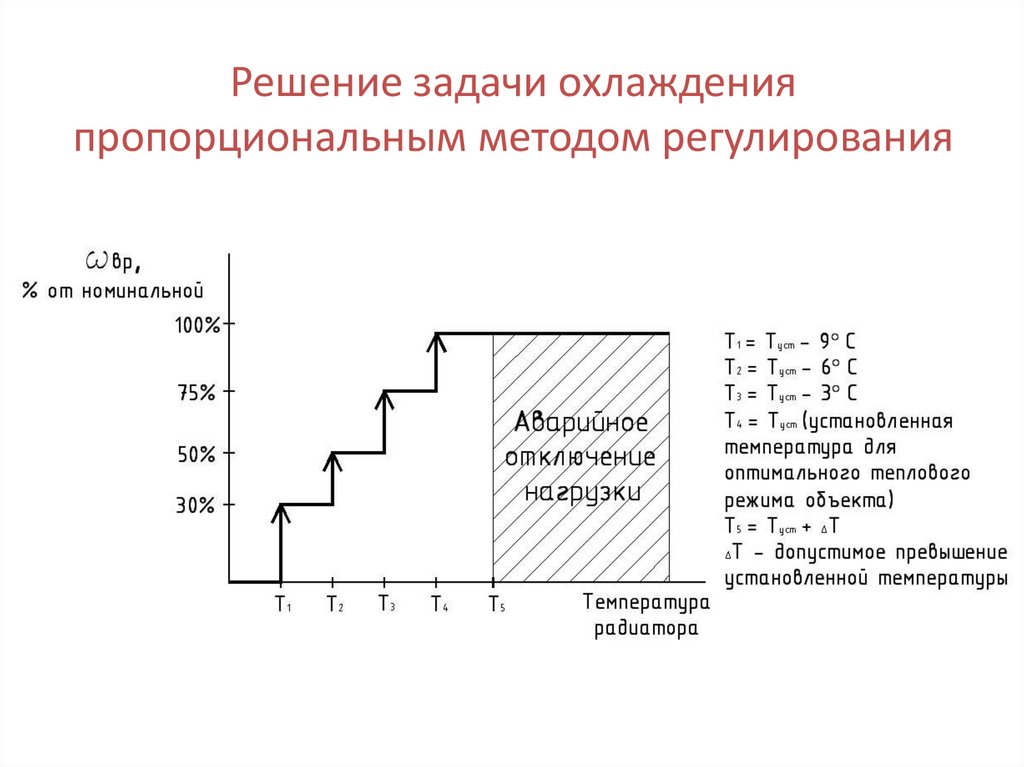

34. Решение задачи охлаждения пропорциональным методом регулирования

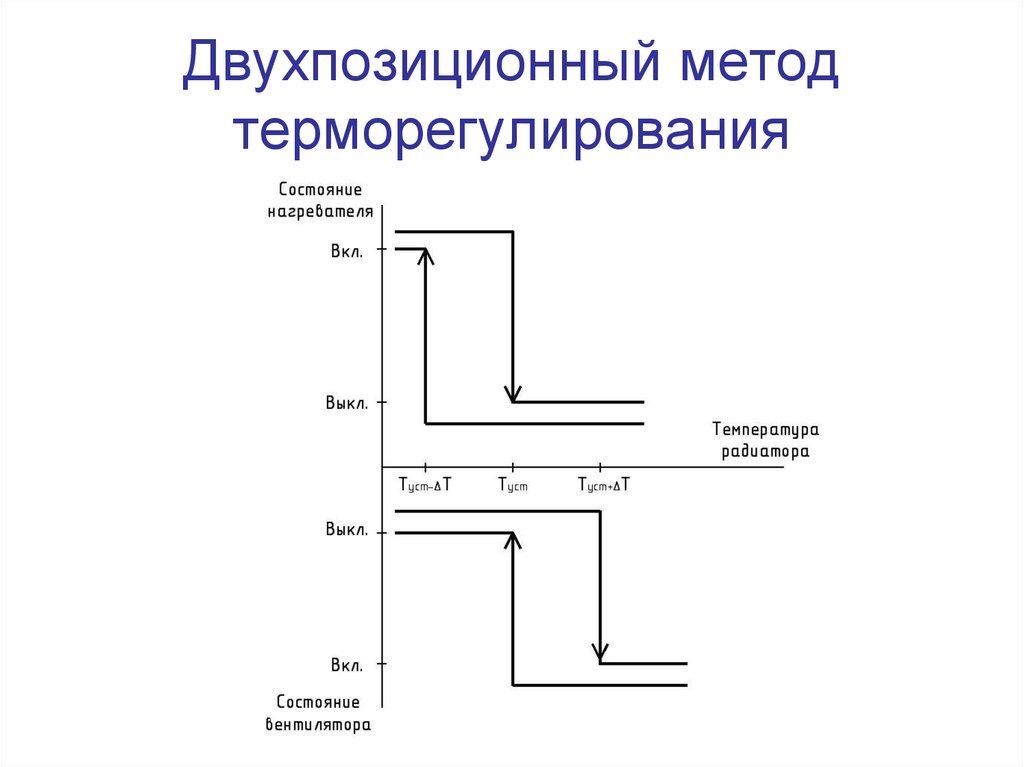

35. Двухпозиционный метод терморегулирования

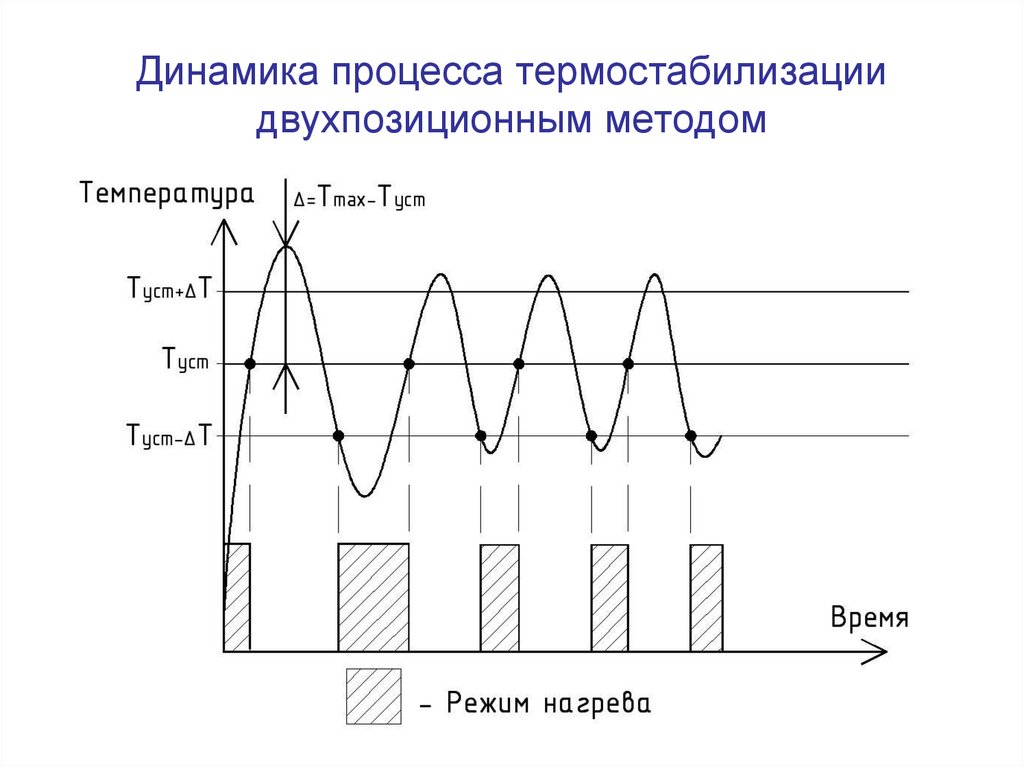

36. Динамика процесса термостабилизации двухпозиционным методом

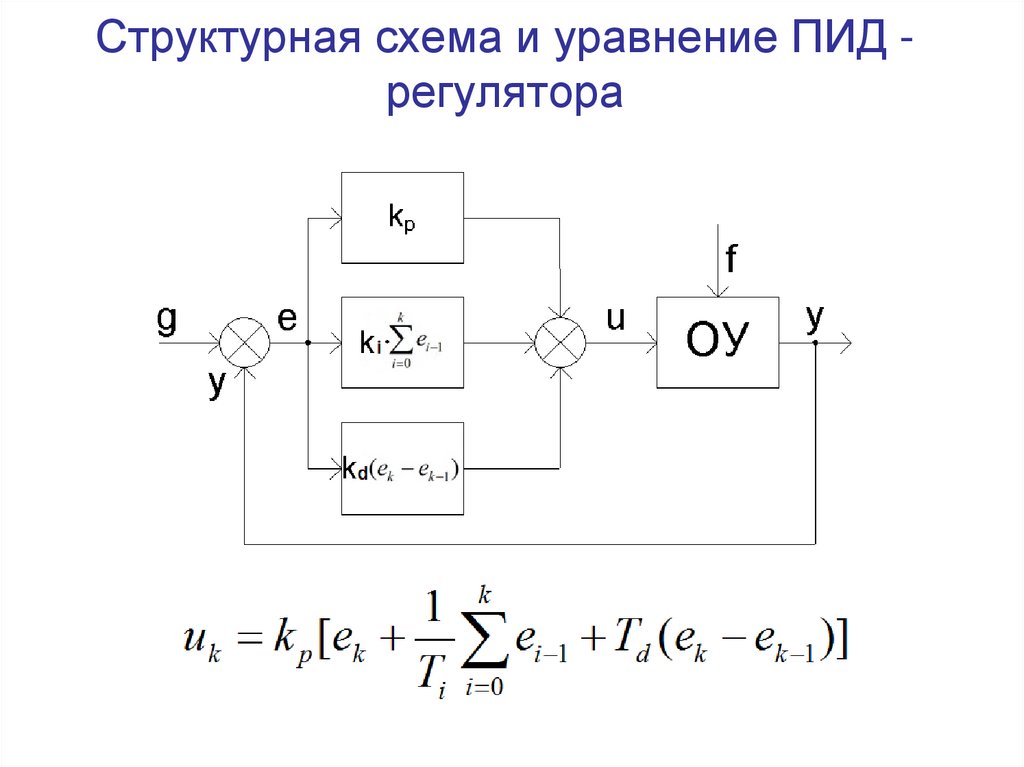

37. Структурная схема и уравнение ПИД - регулятора

Структурная схема и уравнение ПИД регулятора38. Структурная схема устройства

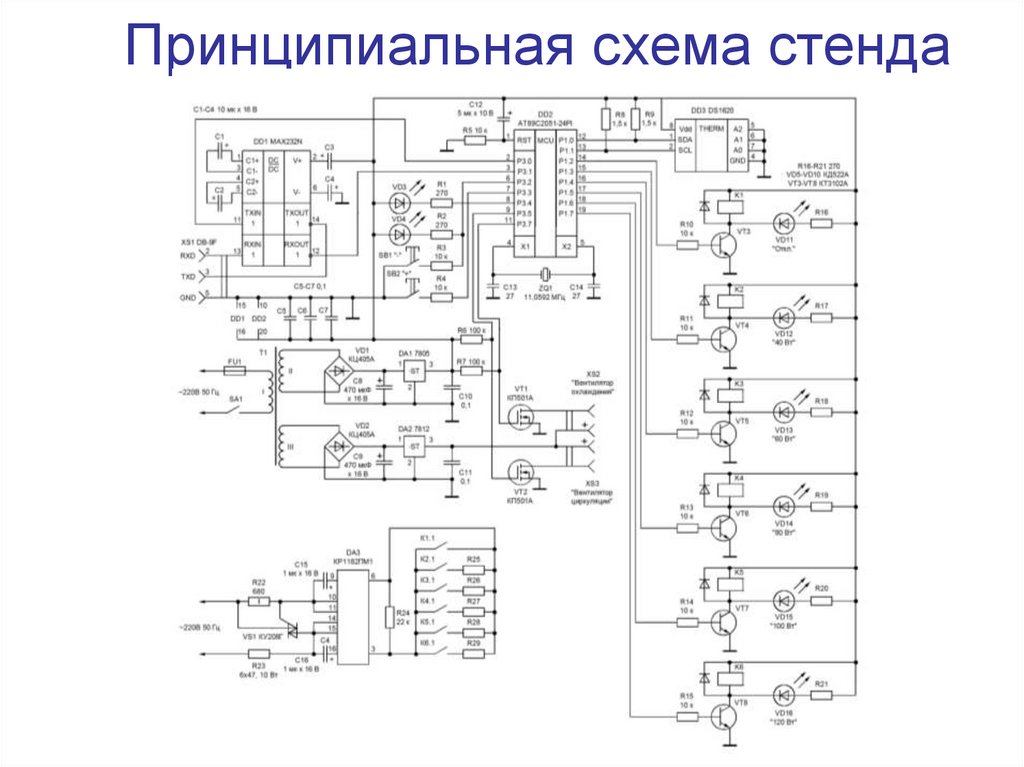

39. Принципиальная схема стенда

40. Алгоритм управляющей программы для микроконтроллера

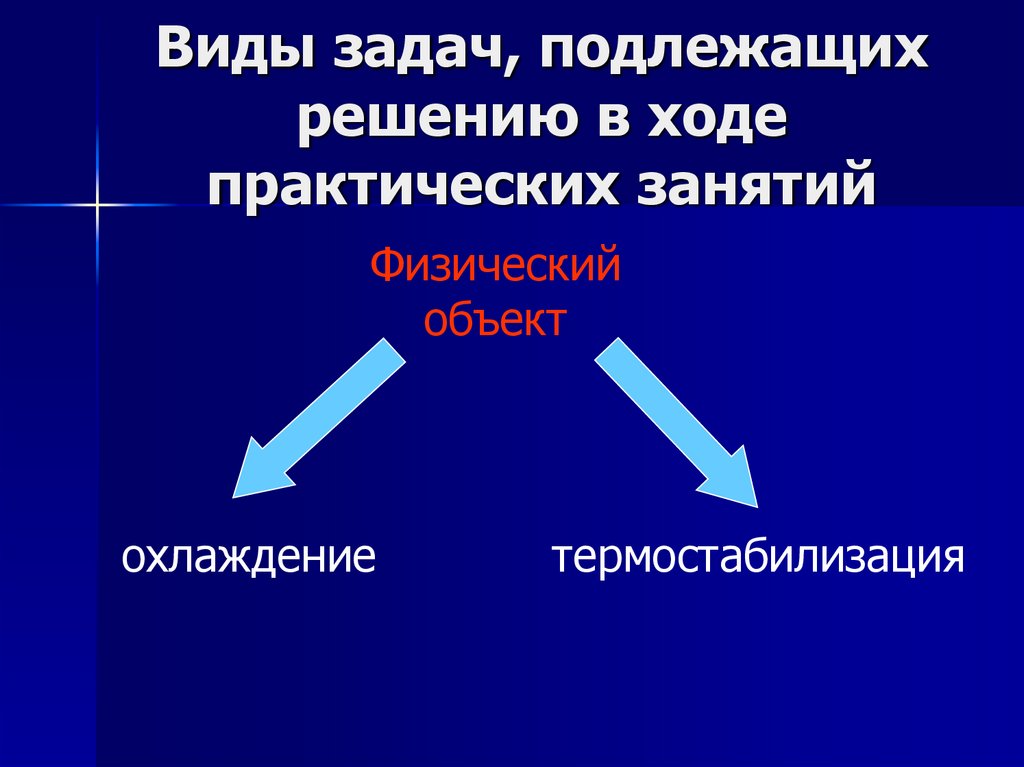

41. Виды задач, подлежащих решению в ходе практических занятий

Физическийобъект

охлаждение

термостабилизация

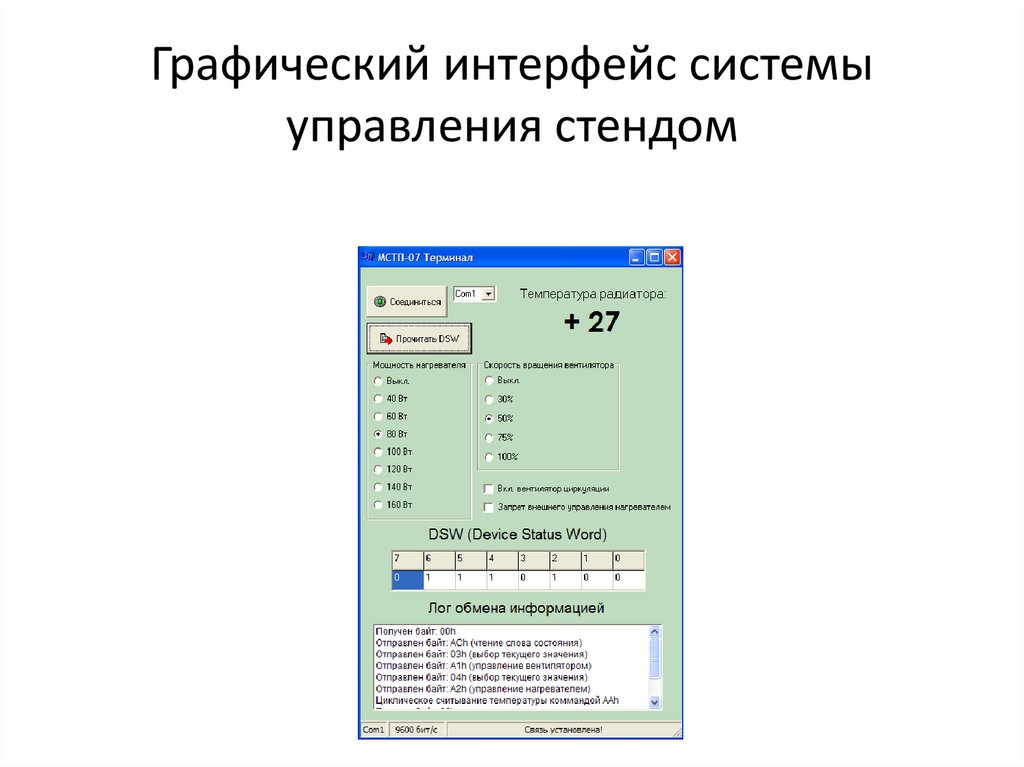

42. Графический интерфейс системы управления стендом

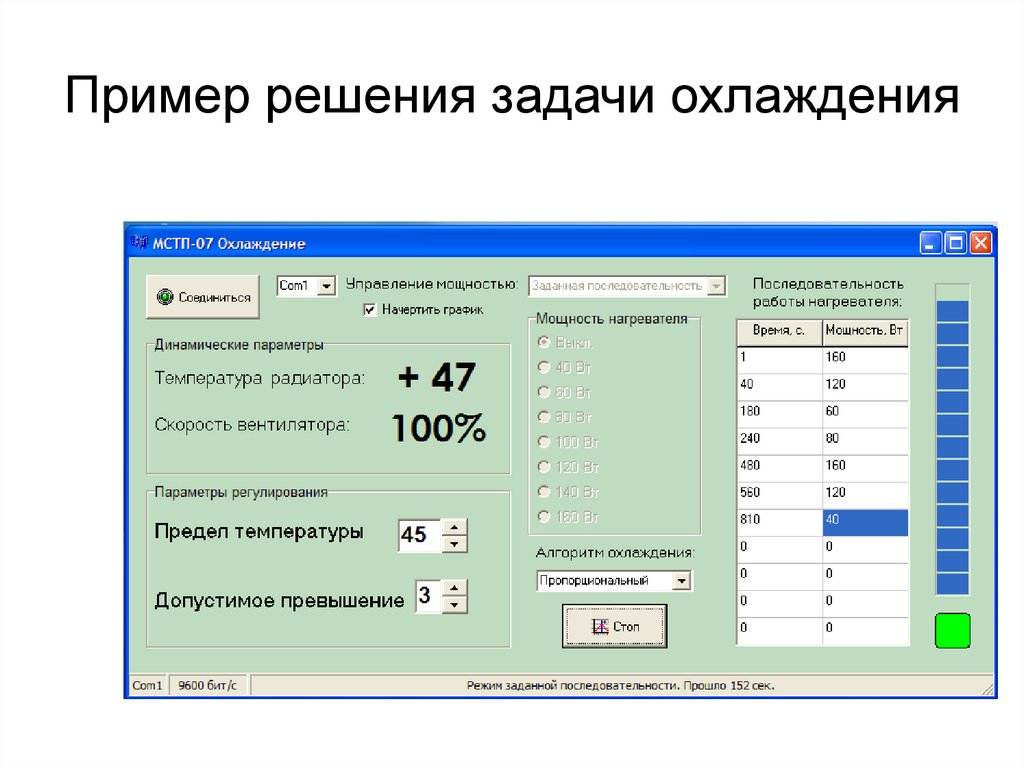

43. Пример решения задачи охлаждения

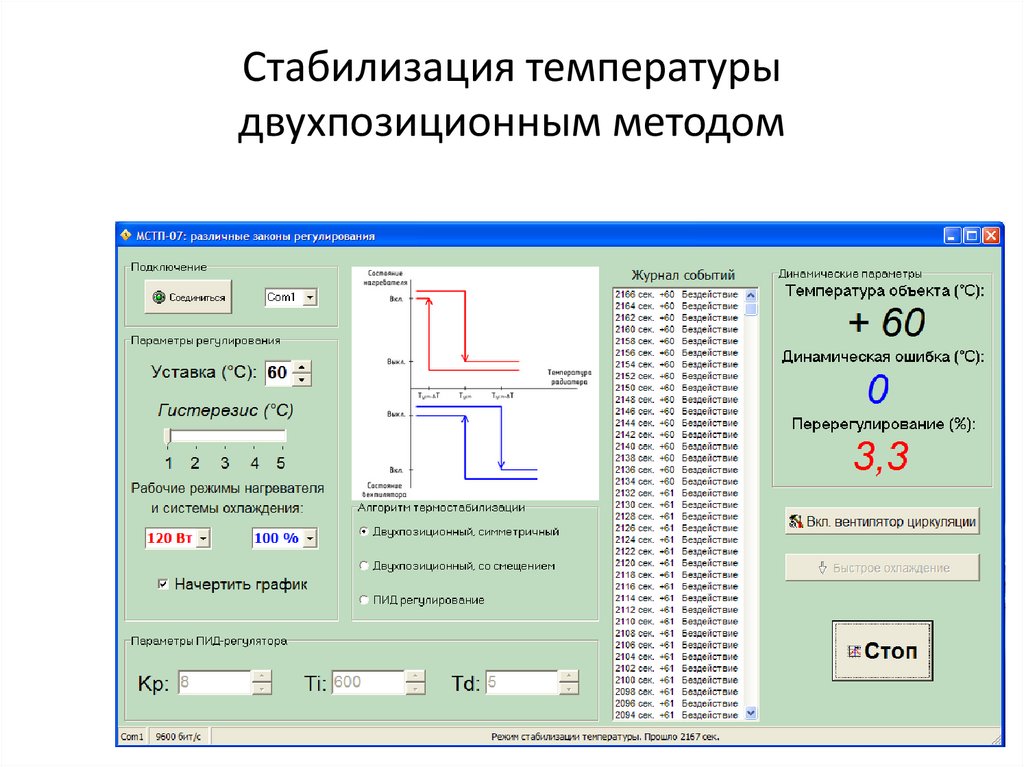

44. Стабилизация температуры двухпозиционным методом

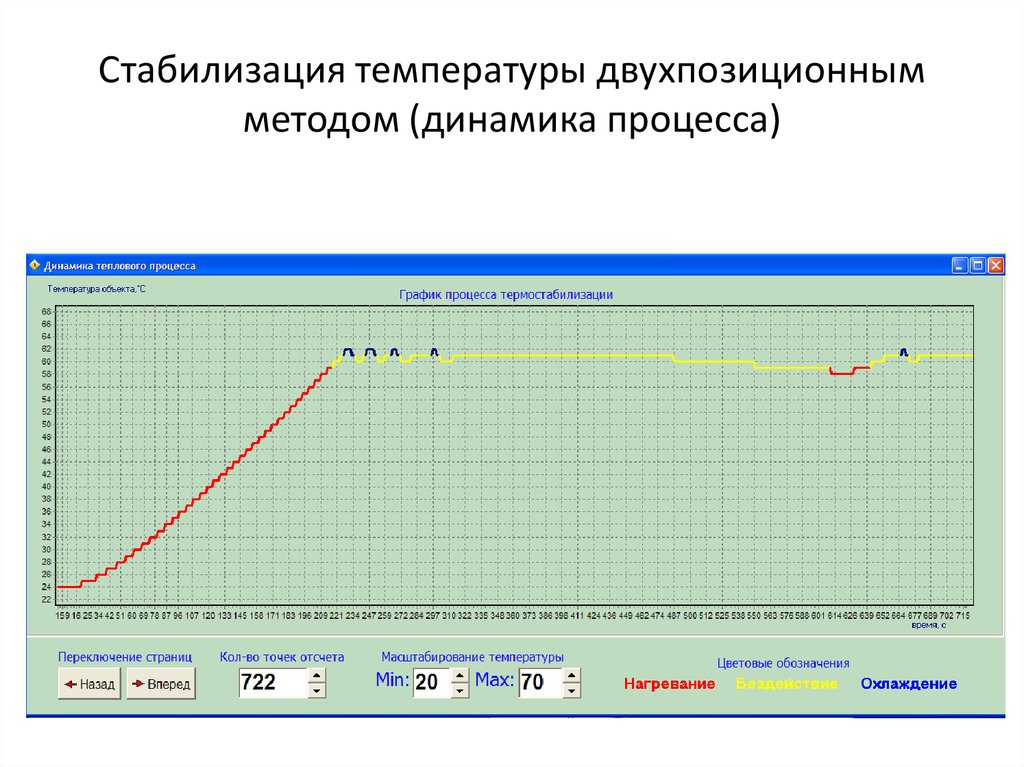

45. Стабилизация температуры двухпозиционным методом (динамика процесса)

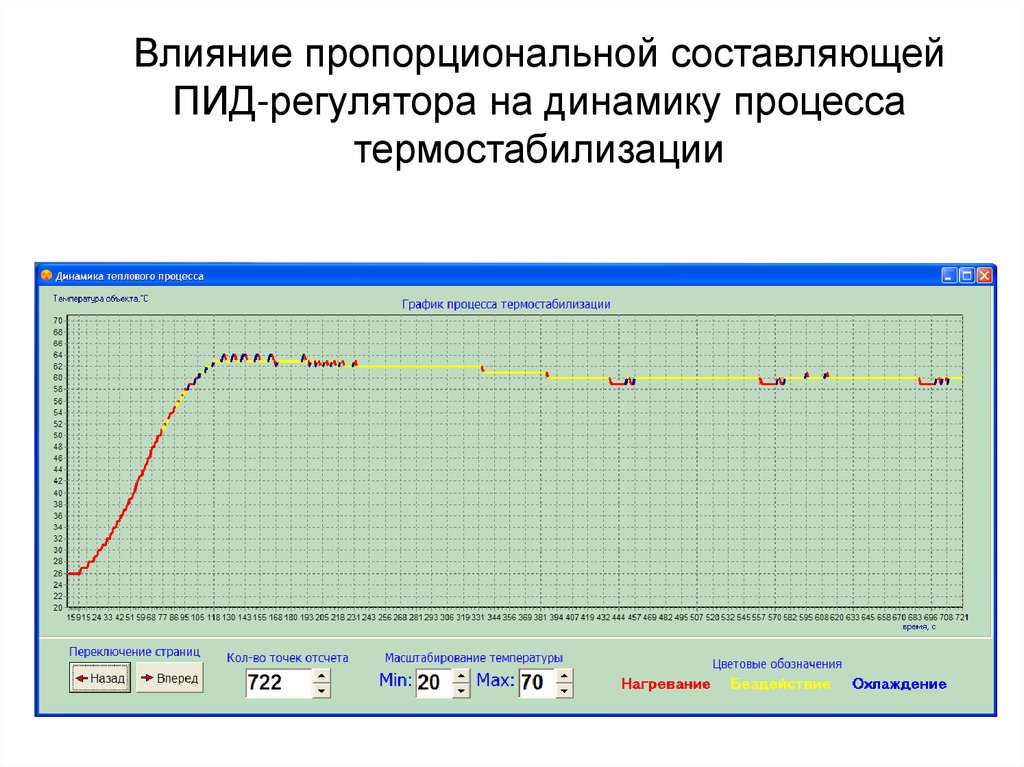

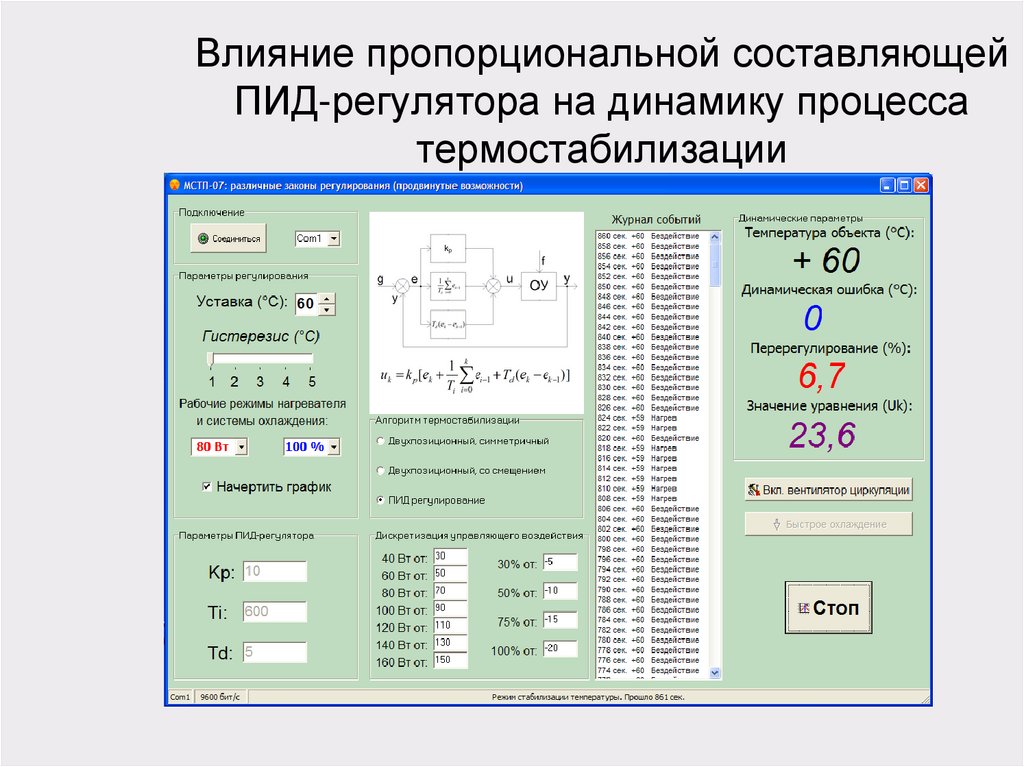

46. Влияние пропорциональной составляющей ПИД-регулятора на динамику процесса термостабилизации

47. Влияние пропорциональной составляющей ПИД-регулятора на динамику процесса термостабилизации

48.

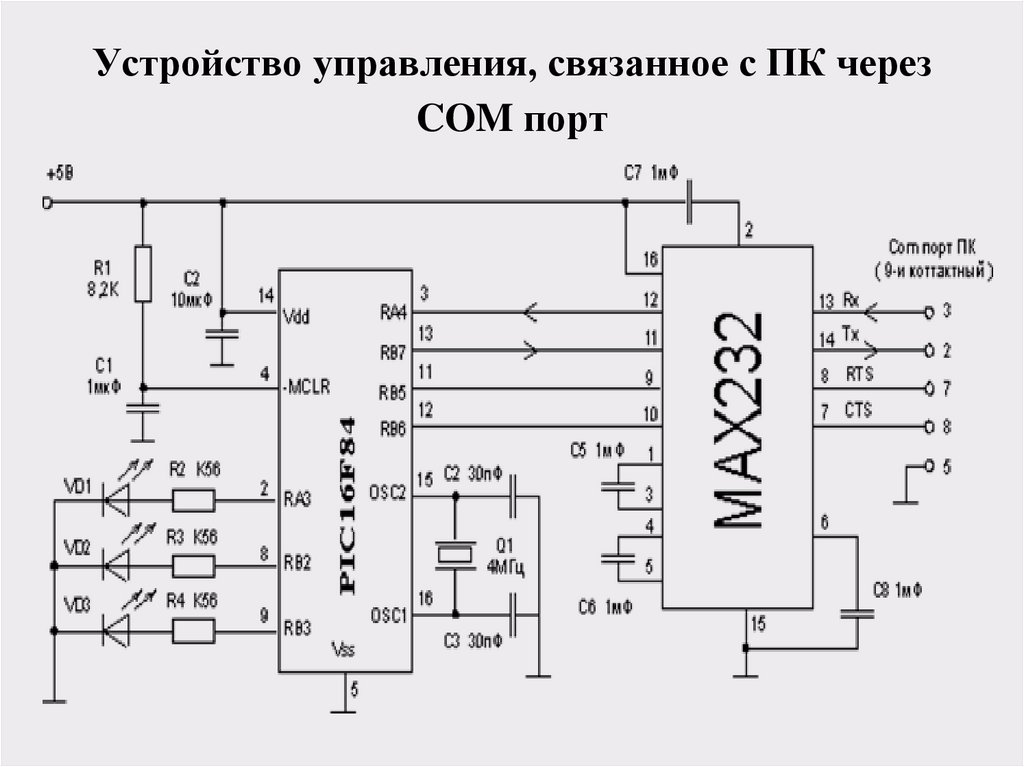

Устройство управления, связанное с ПК черезCOM порт

49.

Схема для просмотра ПЗУ микроконтроллера50.

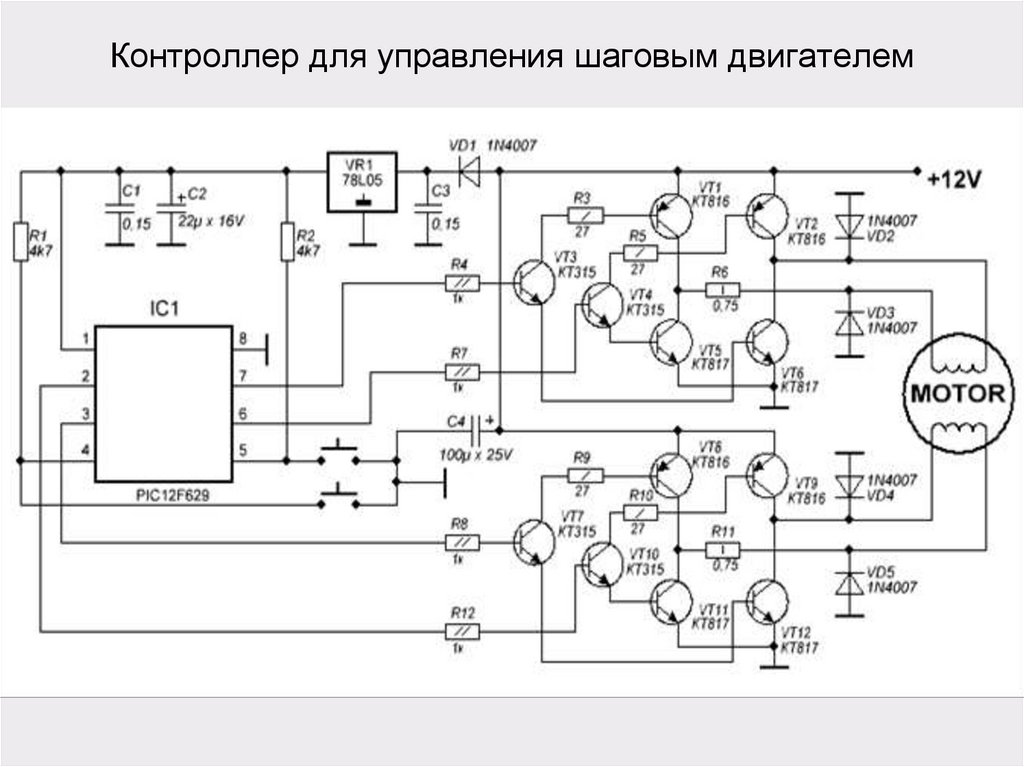

Контроллер для управления шаговым двигателем51.

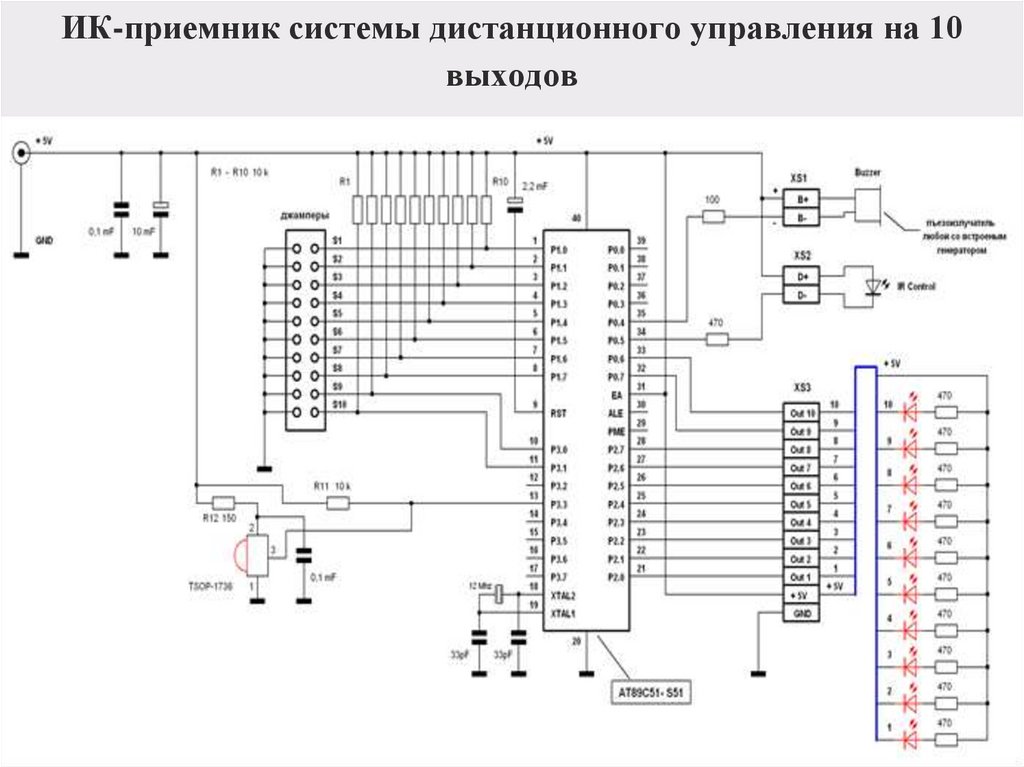

ИК-приемник системы дистанционного управления на 10выходов

electronics

electronics