Similar presentations:

Технологически инвариантный кремниевый компилятор конвейерного матричного делителя

1.

Санкт-Петербургский государственный электротехническийУниверситет им. В. И. Ульянова (Ленина)

Технологически инвариантный

кремниевый компилятор

конвейерного матричного делителя

Выполнил студент группы 6306: Милакин Александр Дмитриевич

Руководитель: к. т. н., доцент Миронов Сергей Эльмарович

2.

Цель работыизучение технологии проектирования топологии макроблоков интегральных

схем в технологически инвариантной концепции, на примере конвейерного

матричного делителя.

Основные задачи

• Изучение алгоритма деления без восстановления остатка

• Исследование и разработка структурно-топологического плана конвейерного

матричного делителя

• Схемотехническое проектирование

• Разработка топологических эскизов ячеек (система TopDesign)

• Разработка топологического описания макроблока

• Генерация топологических чертежей макроблока разной разрядности в разный

проектных нормах (система Matching of cells)

3.

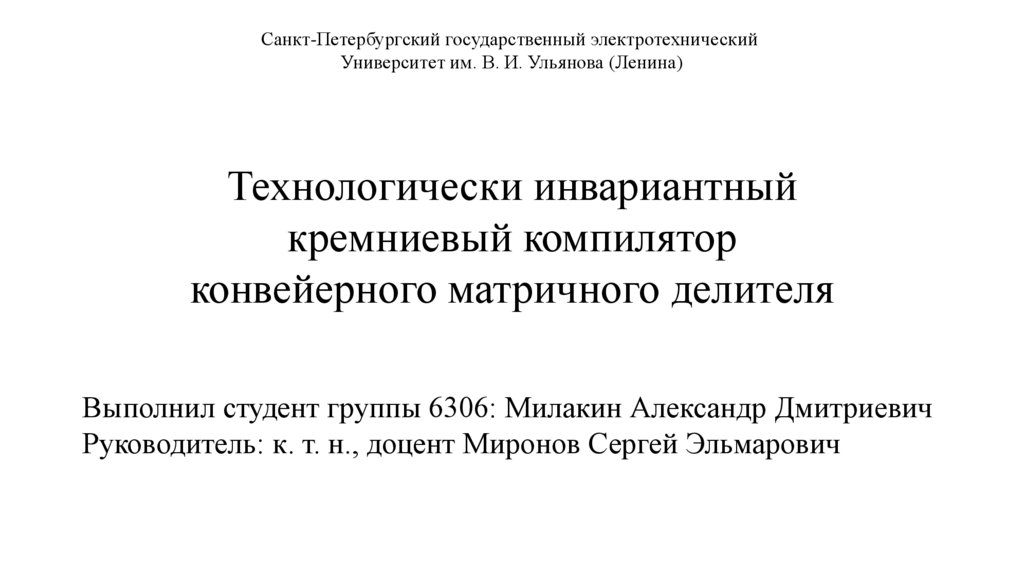

Деление без восстановленияостатка

Структурная схема

матричного делителя

Структурная схема

конвейерного матричного делителя

4.

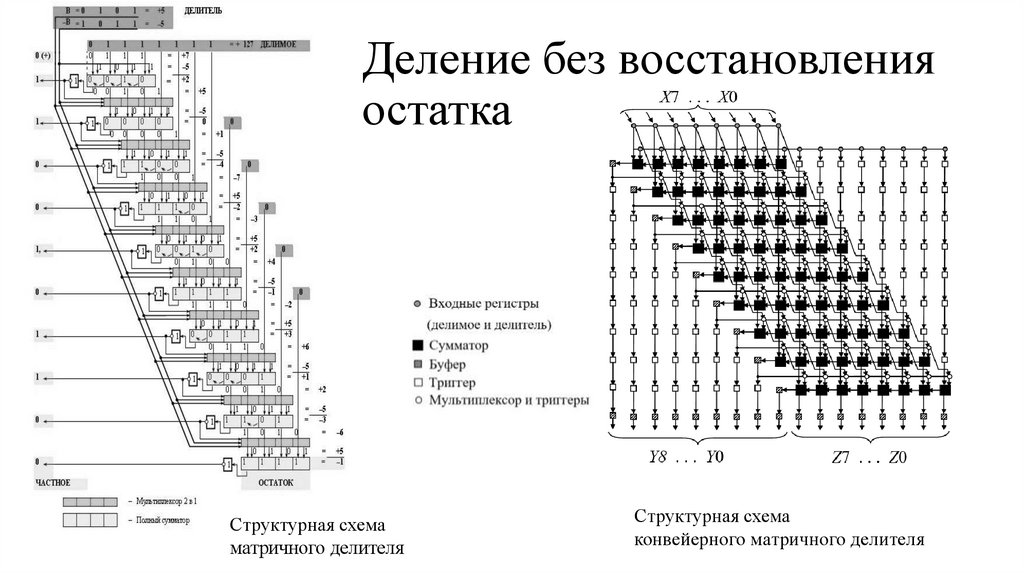

Структурно-топологическая оптимизацияконвейерного матричного делителя

Оптимизация структурно-топологического плана

Оптимизация области триггеров

5.

Структура конвейерного матричного делителяСтруктурно-топологический план конвейерного матричного делителя

Структурно-топологическая

схема конвейерного

матричного делителя

6.

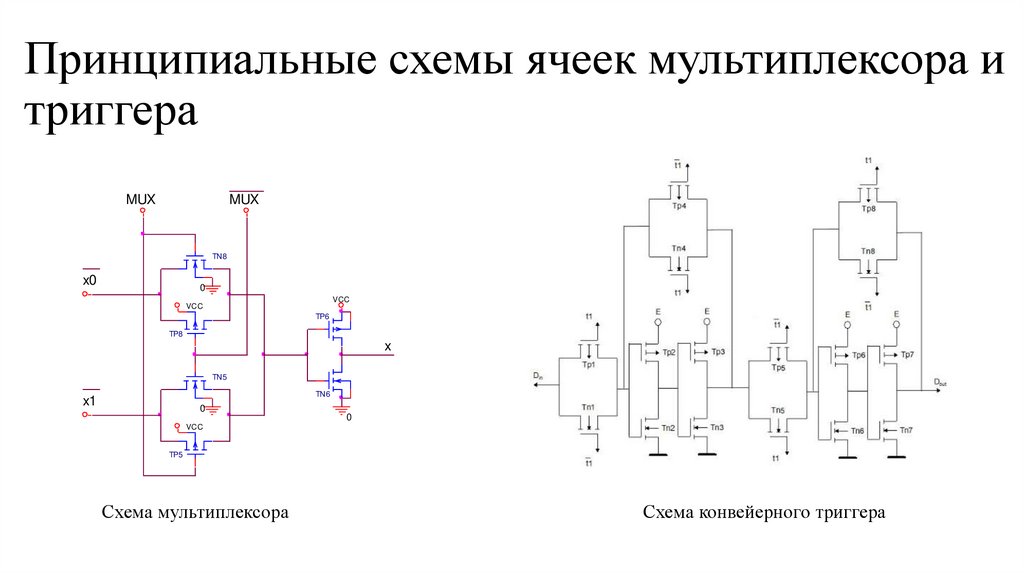

Принципиальные схемы ячеек мультиплексора итриггера

MUX

MUX

TN8

x0

0

VCC

VCC

TP6

TP8

x

TN5

TN6

x1

0

0

VCC

TP5

Схема мультиплексора

Схема конвейерного триггера

7.

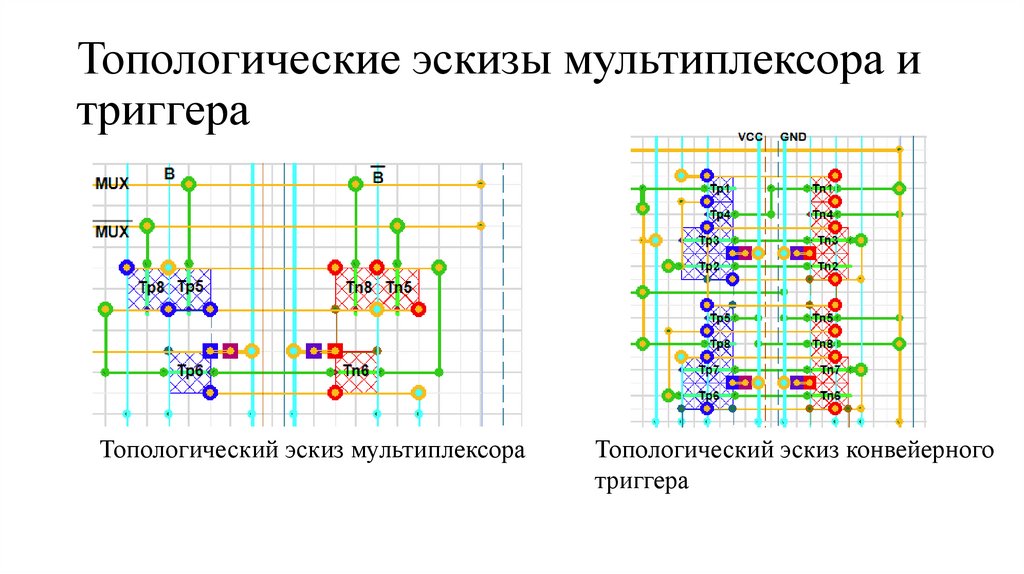

Топологические эскизы мультиплексора итриггера

Топологический эскиз мультиплексора

Топологический эскиз конвейерного

триггера

8.

Манчестерская цепочкаAi

Bi

Tp3

E

Tp4

Tp1

E

E

Tn3

Tp2

Tp6

E

Tp5

P=A

Tn4

Tp7

Tn5

Tn1

B

Ci+1

Tn2

Tp8

Tn7

Tn8

Ci

E

Tn10

E

Tp9

Tp11

Tn11

E

Tp13

E

Tp12

Si

Tn9

Tn12

Tn10

Одноразрядный сумматор на

манчестерской цепочке

Структура тетрады манчестерской цепочки

9.

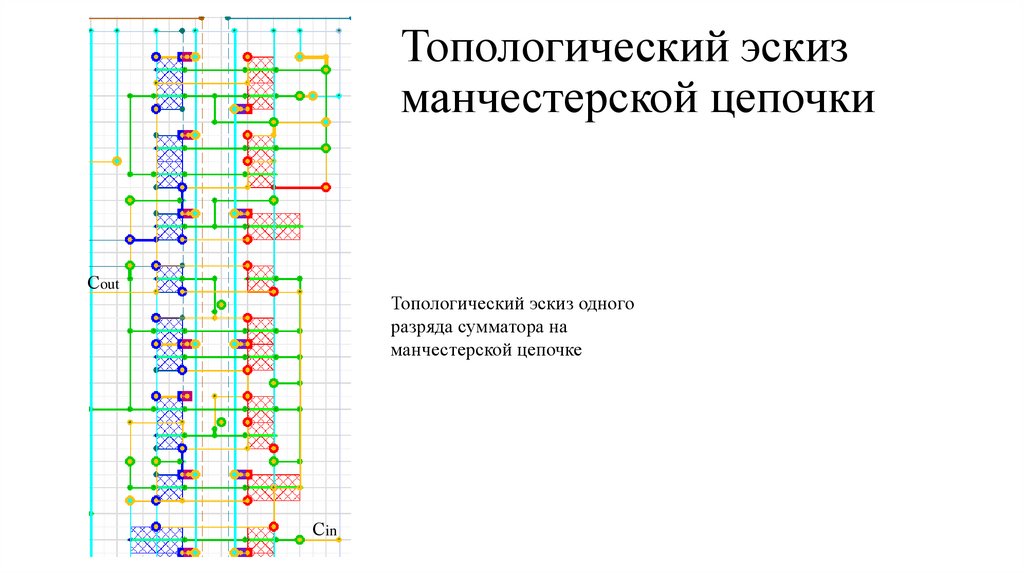

Топологический эскизманчестерской цепочки

Сout

Топологический эскиз одного

разряда сумматора на

манчестерской цепочке

Сin

10.

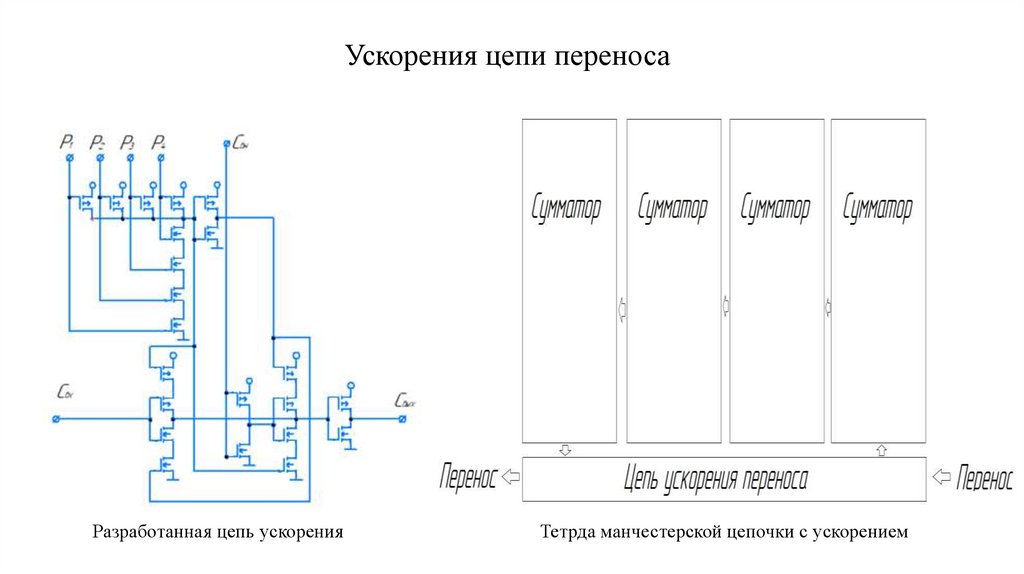

Ускорения цепи переносаРазработанная цепь ускорения

Тетрда манчестерской цепочки с ускорением

11.

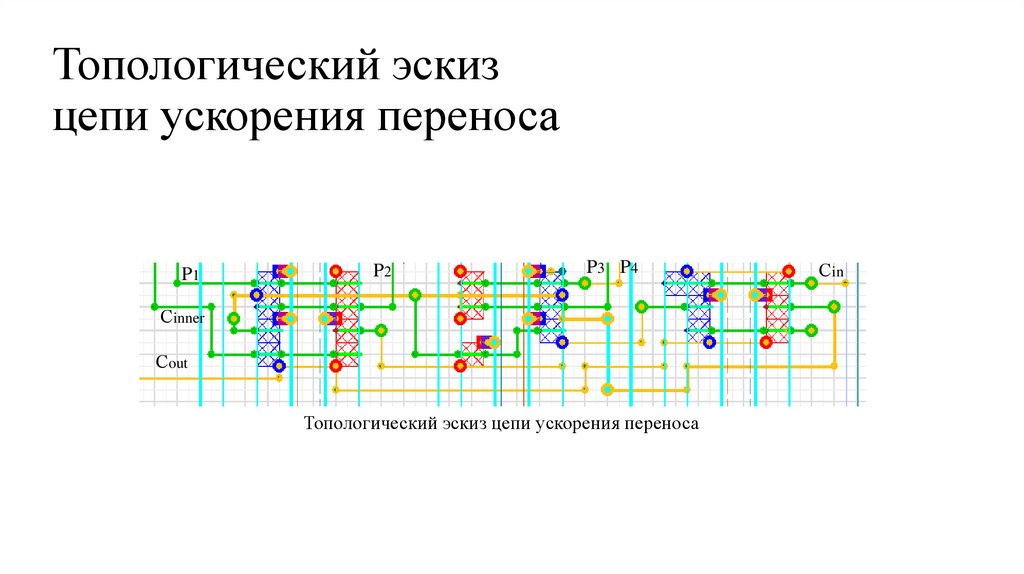

Топологический эскизцепи ускорения переноса

P1

P2

P3 P4

Сinner

Сout

Топологический эскиз цепи ускорения переноса

Сin

12.

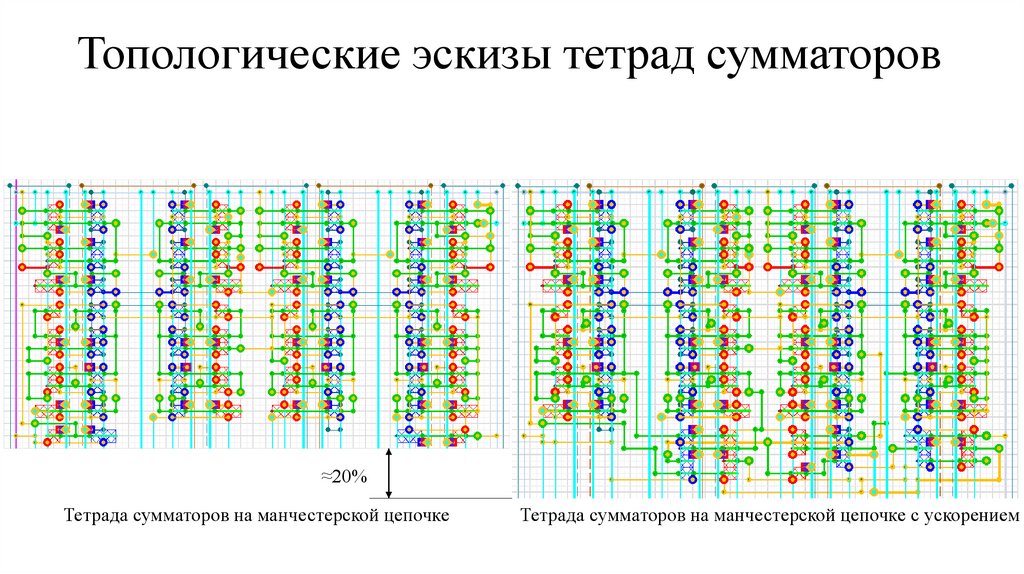

Топологические эскизы тетрад сумматоров≈20%

Тетрада сумматоров на манчестерской цепочке

Тетрада сумматоров на манчестерской цепочке с ускорением

13.

Моделирование схемы манчестерскойцепочки с ускорением в системе OrCAD

Схема прохождения сигнала

Схема прохождения сигнала с

ускорением

Схема, состоящая из 4 каскадов

Время прохождения сигнала от

входа к выходу ячейки

1,5 нс

3 нс

Результаты моделирования

Схема ячейки манчестерской цепочки с ускорением в системе

OrCAD

14.

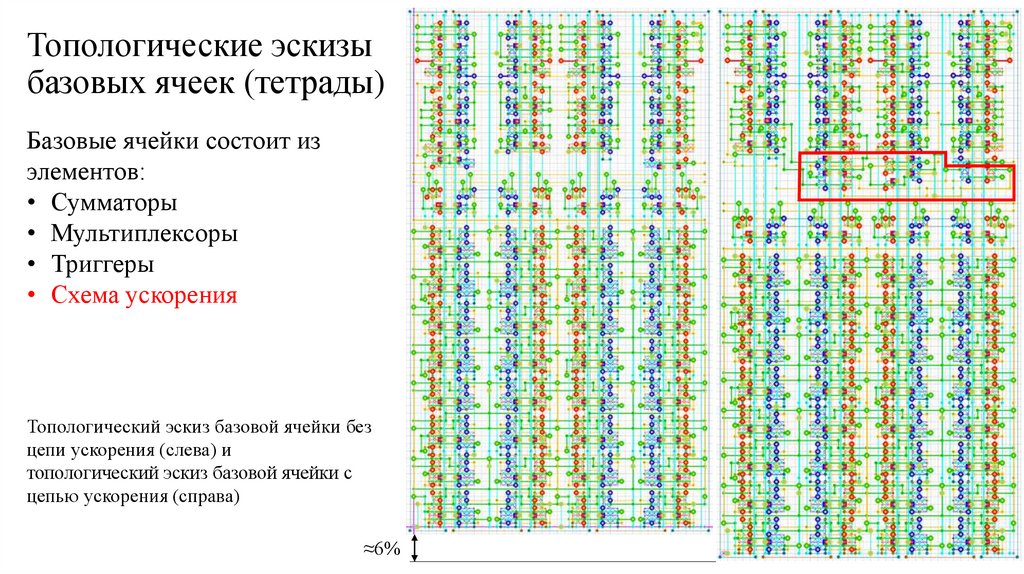

Топологические эскизыбазовых ячеек (тетрады)

Базовые ячейки состоит из

элементов:

• Сумматоры

• Мультиплексоры

• Триггеры

• Схема ускорения

Топологический эскиз базовой ячейки без

цепи ускорения (слева) и

топологический эскиз базовой ячейки с

цепью ускорения (справа)

≈6%

15.

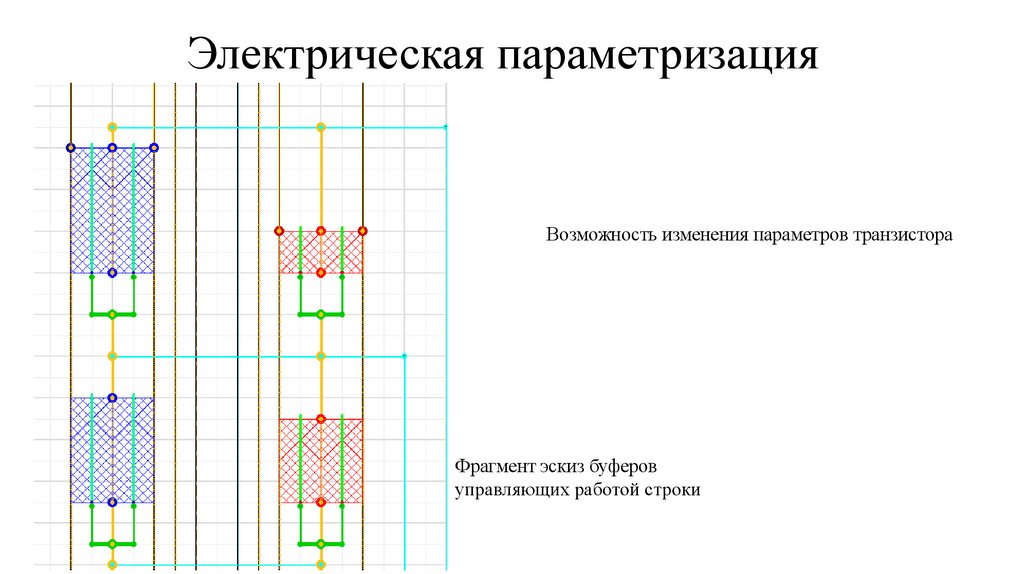

Электрическая параметризацияВозможность изменения параметров транзистора

Фрагмент эскиз буферов

управляющих работой строки

16.

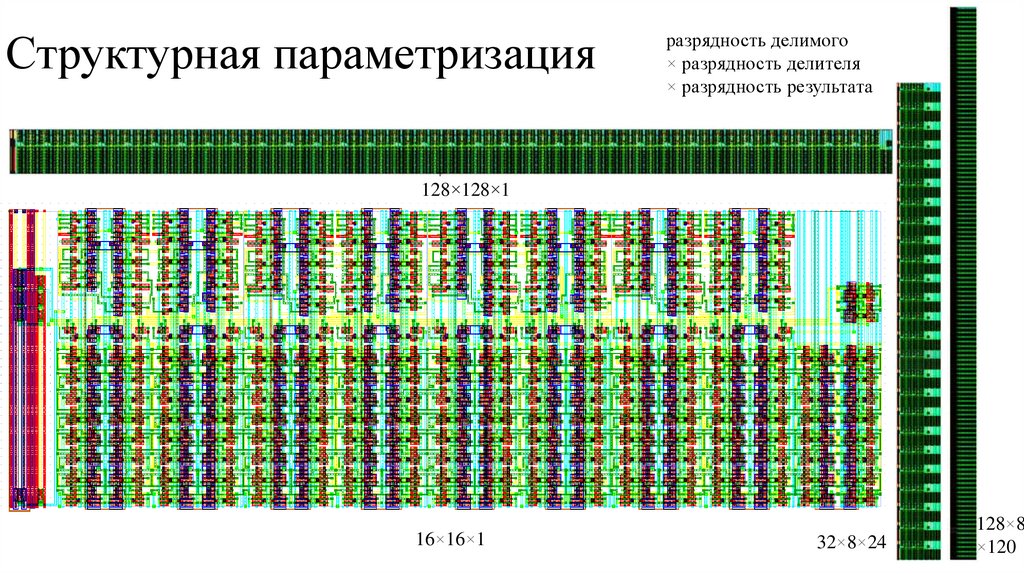

Структурная параметризацияразрядность делимого

× разрядность делителя

× разрядность результата

128×128×1

16×16×1

32×8×24

128×8

×120

17.

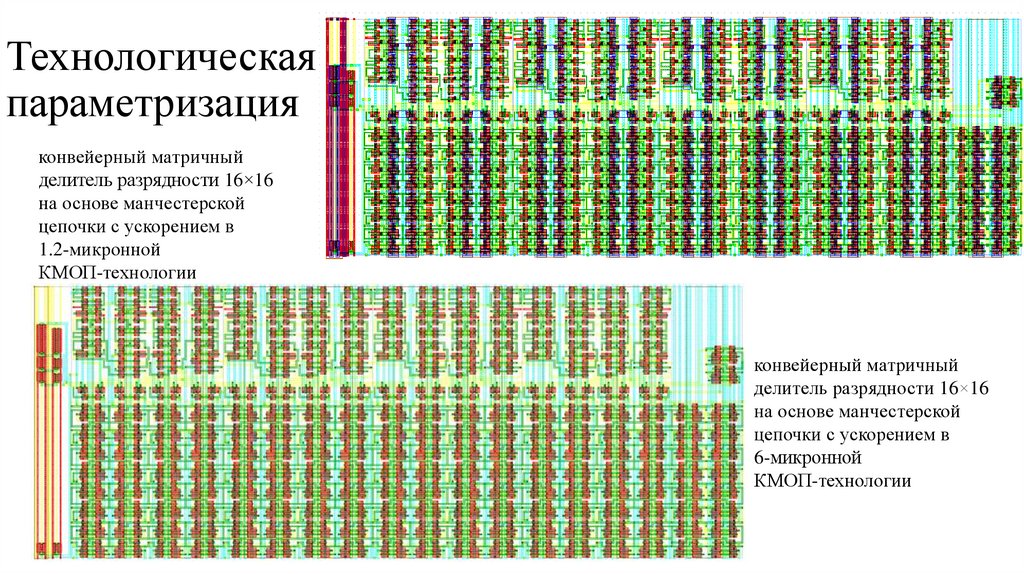

Технологическаяпараметризация

конвейерный матричный

делитель разрядности 16×16

на основе манчестерской

цепочки с ускорением в

1.2-микронной

КМОП-технологии

конвейерный матричный

делитель разрядности 16×16

на основе манчестерской

цепочки с ускорением в

6-микронной

КМОП-технологии

18.

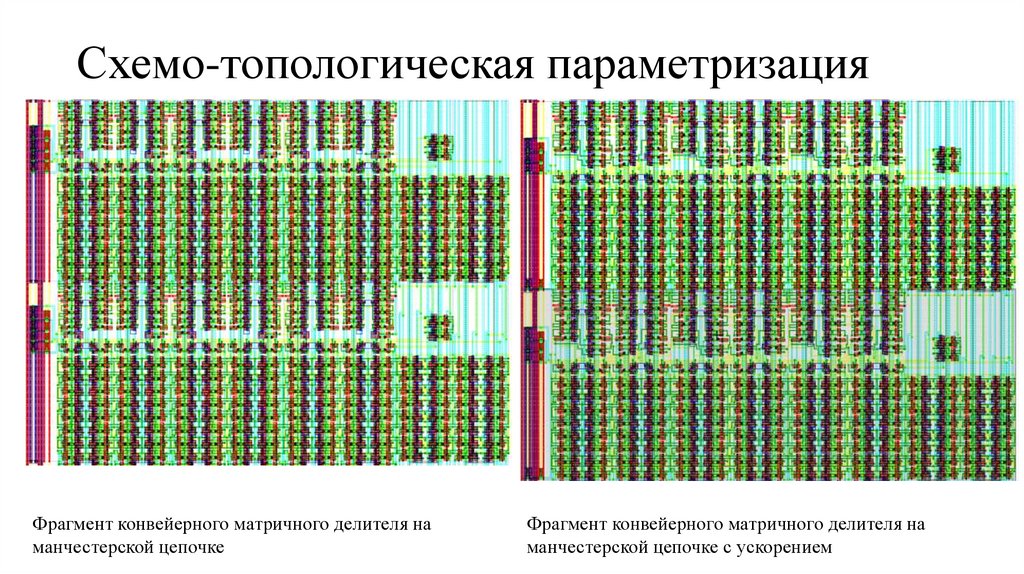

Схемо-топологическая параметризацияФрагмент конвейерного матричного делителя на

манчестерской цепочке

Фрагмент конвейерного матричного делителя на

манчестерской цепочке с ускорением

19.

Направления дальнейшего развития• Другие схемные решения сумматоров

• Другие конвейерные устройства (умножитель,

извлечения корня и др.)

• Сравнение конвейерных матричных

устройств с репликационными устройствами

20.

Результаты• Выполнена оптимизация структурно-топологической организации

конвейерного матричного делителя

• Разработана библиотека ячеек

• Разработана цепь ускорения переноса

• Разработан специализированный кремниевый компилятор конвейерного

матричного делителя с комплексной параметризацией

Результаты используются в кафедральных исследованиях по потоковой

обработки информации, внедряются в учебный процесс

Подготовлен материал для публикации в «Известиях «ЛЭТИ»

electronics

electronics