Similar presentations:

Вычислительные машины, системы и сети. Лекция 5. Тема 9. Системный интерфейс. Структура ЭВМ

1.

Вычислительные машины,системы и сети

Лекция 5

к.т.н., доцент, Тычинина Юлия

Александровна

2.

9. Системный интерфейс. Структура ЭВМ.По способу организации взаимодействия межу процессором,

памятью и периферийными устройствами в машинах с шинной

организацией можно выделить два основных способа организации

шин:

1. Двухшинная организация, или интерфейс с изолированной

системой шин.

2. Одношинная организация интерфейса, или интерфейс с общей

шиной.

Двухшинную организацию имеют, например, персональные

ЭВМ фирмы IBM. Название «двухшинная» отражает тот факт, что

с функциональной точки зрения есть два тракта передачи

данных, процессор – память и процессор – периферийные

устройства, обращение к которым осуществляется отдельными

группами команд.

3.

9. Системный интерфейс. Структура ЭВМ.При двухшинном способе организации используется четыре

логических шины: две шины данных, различные для портов

внешних устройств и для памяти, и две шины адреса. Эти четыре

логические шины могут соответствовать всего двум или даже

одной физической шине, просто для разных целей могут

использоваться разные группы линий.

Эта неоднозначность проистекает из того, что разработчики посвоему описывают уже известные организации, делая акцент на

отличиях в непринципиальных моментах.

4.

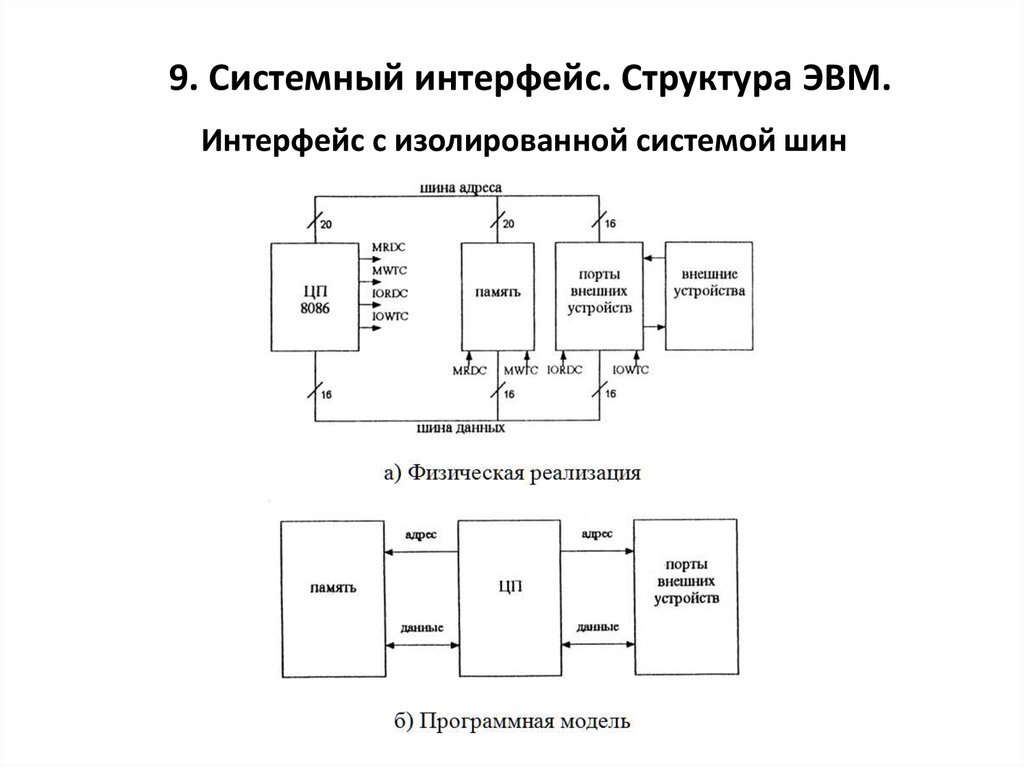

9. Системный интерфейс. Структура ЭВМ.Интерфейс с изолированной системой шин

5.

9. Системный интерфейс. Структура ЭВМ.Характерной особенностью интерфейса с изолированной

системой шин является раздельная адресация памяти и

периферийных устройств при обмене информацией. В ПЭВМ с

процессором 8086 физически используется одна адресная шина.

Для адресации памяти используются все 20 линий адресной шины,

для адресации внешних устройств только 16 линий адресной

шины. Данные передаются по одной и той же 16-разрядной шине.

При работе с памятью используются управляющие сигналы MRDC

(Memory ReaD Command – чтение памяти) и MWTC (Memory

WriTe Command – запись в память), при работе с портами

внешних устройств сигналы IORDC (Input Output ReaD Command –

чтение порта ввода-вывода) и IOWTC (Input Output WriTe

Command – запись в порт ввода-вывода). Для организации

доступа к портам внешних устройств процессор использует

команды типа IN (ввести) и OUT (вывести).

6.

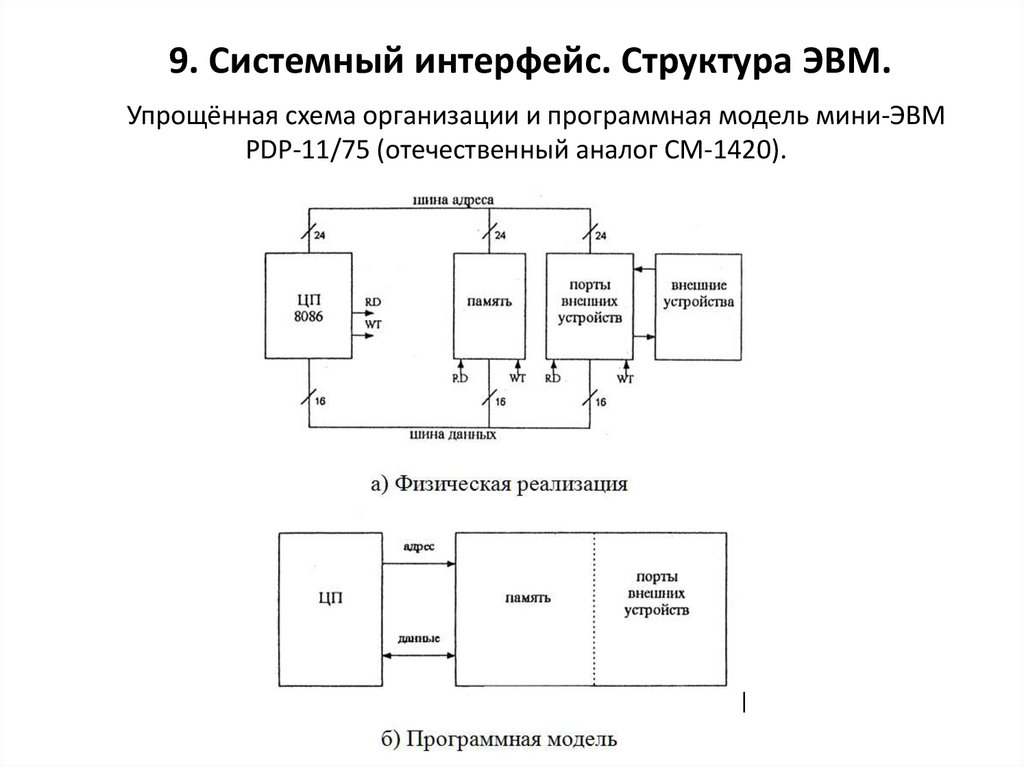

9. Системный интерфейс. Структура ЭВМ.Интерфейс с общей шиной использован в мини-ЭВМ семейства

PDP-11, LSI-11, VAX-11 фирмы Digital Equipment. В последствии

многие разработчики микроЭВМ стали широко использовать

данный способ построения интерфейса.

При данной организации интерфейса часть общего адресного

пространства отводится для периферийных устройств, порты

которых адресуются так же, как и ячейки памяти. Обращение к

портам внешних устройств осуществляется теми же командами,

что и работа с памятью, с использованием того же набора режимов

адресации. При этом команды ввода-вывода не используются или

вовсе отсутствуют.

упрощённая схема организации и программная модель миниЭВМ PDP-11/75 (отечественный аналог СМ-1420).

7.

9. Системный интерфейс. Структура ЭВМ.Упрощённая схема организации и программная модель мини-ЭВМ

PDP-11/75 (отечественный аналог СМ-1420).

8.

9. Системный интерфейс. Структура ЭВМ.В ЭВМ СМ-1420, например, общий размер адресного

пространства составляет 16 Мбайт, часть, размером в 15,992 Мбайт

отведена для адресации памяти, и 8 Кбайт – для адресации портов

внешних устройств. Такая организация интерфейса сокращает

объём памяти доступный программе, но существенно упрощает

разработку схем управления и дешифрирования адреса. Шина в

такой системе является «общей», в том смысле, что процессор

считает и память, и порты внешних устройств равноправными по

отношению к шине и использует для доступа к ним один набор

команд и управляющих сигналов. При такой схеме обмен данными

реализуется с использованием всего двух управляющих сигналов –

RD (ReaD – чтение) и WR (WRite – запись).

9.

10. Структура современной ЭВМ.Все

рассмотренные

ранее

принципы

организации

и

функционирования ЭВМ можно отнести к некоторой «базовой ЭВМ»,

которой в полной мере можно считать ЭВМ начала 80-х.

В настоящее время в структуру ЭВМ внесены несколько

принципиальных

изменений,

обусловленных

повышением

производительности:

• Появилась процессорная шина, объединяющая процессор (или

несколько процессоров, в случае многопроцессорных систем), кэшпамять и системный контроллер.

• В отдельное устройство выделена шина памяти, объединяющая

системный контроллер (СМ) и память.

• Отдельным интерфейсом оформлена шина связи системного

контроллера (СМ) с графическим адаптером.

• Появились новые интерфейсы, позволяющие увеличить скорость

обмена между памятью и внешними устройствами

• Количество микросхем, входящих в состав чипсета значительно

уменьшилось, т.к. в одной микросхеме сейчас объединяют несколько

функциональных устройств.

10.

10. Структура современной ЭВМ.11.

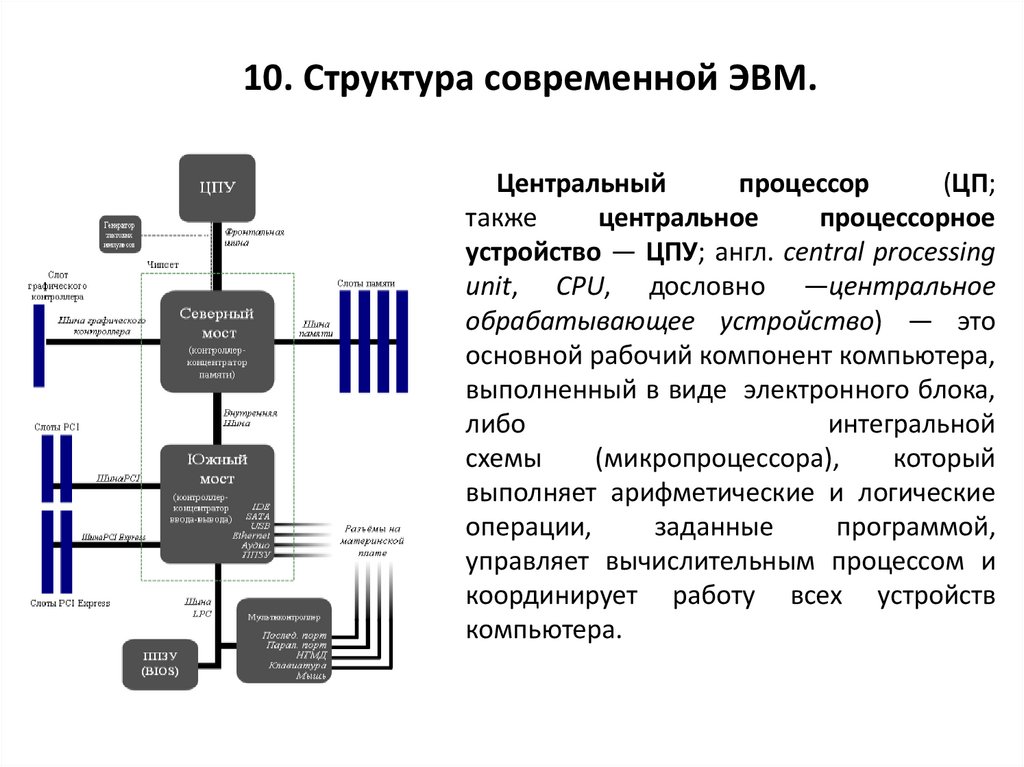

10. Структура современной ЭВМ.Центральный

процессор

(ЦП;

также

центральное

процессорное

устройство — ЦПУ; англ. central processing

unit, CPU, дословно —центральное

обрабатывающее устройство) — это

основной рабочий компонент компьютера,

выполненный в виде электронного блока,

либо

интегральной

схемы

(микропроцессора),

который

выполняет арифметические и логические

операции,

заданные

программой,

управляет вычислительным процессом и

координирует работу всех устройств

компьютера.

12.

10. Структура современной ЭВМ.Центральный процессор в общем случае содержит в себе:

• арифметико-логическое устройство;

• регистры;

• внутренние шины данных и шины адресов;

• счетчики команд;

• кэш — очень быструю память малого объема;

• математический сопроцессор чисел с плавающей точкой (FPU

floating point unit).

Главными характеристиками ЦПУ являются:

• тактовая частота,

• производительность,

• энергопотребление,

• нормы литографического процесса, используемого при

производстве (для микропроцессоров),

• архитектура.

13.

10. Структура современной ЭВМ.Кэш или кеш (англ. cache) — промежуточный буфер с

быстрым доступом, содержащий информацию, которая

может быть запрошена с наибольшей вероятностью. Доступ к

данным в кэше идёт быстрее, чем выборка исходных данных

из оперативной (ОЗУ) и быстрее внешней (жёсткий диск или

твердотельный накопитель) памяти, за счёт чего уменьшается

среднее

время

доступа

и

увеличивается

общая

производительность компьютерной системы.

Кэш центрального процессора разделён на несколько

уровней. Максимальное количество кэшей — четыре. Кэшпамять уровня N+1, как правило, больше по размеру и

медленнее по скорости доступа и передаче данных, чем кэшпамять уровня N.

14.

10. Структура современной ЭВМ.Самым быстрым является кэш первого уровня — L1 cache (level

1 cache). По сути, она является неотъемлемой частью процессора,

поскольку расположена на одном с ним кристалле и входит в

состав функциональных блоков. В современных процессорах

обычно L1 разделен на два кэша — кэш команд (инструкций) и кэш

данных (Гарвардская архитектура). L1 работает на частоте

процессора, и, в общем случае, обращение к нему может

производиться каждый такт. Зачастую является возможным

выполнять несколько операций чтения/записи одновременно.

Вторым по быстродействию является кэш второго уровня — L2

cache, который обычно, как и L1, расположен на одном кристалле с

процессором. В ранних версиях процессоров L2 реализован в виде

отдельного набора микросхем памяти на материнской плате.

Объём L2 от 128 кбайт до 1−12 Мбайт. В современных

многоядерных процессорах кэш второго уровня, находясь на том

же кристалле.

15.

10. Структура современной ЭВМ.Кэш третьего уровня наименее быстродействующий, но он

может быть очень большим — более 24 Мбайт. L3 медленнее

предыдущих кэшей, но всё равно значительно быстрее, чем

оперативная память. Обычно расположен отдельно от ядра ЦП. В

многопроцессорных системах находится в общем пользовании и

предназначен для синхронизации данных различных L2.

16.

17.

10. Структура современной ЭВМ.Сокет – это разъём центрального

процессора

—

гнездовой

или

щелевой разъём (гнездо) в материнской

плате определенного типа процессора или

CPU-карты. На физическом уровне, разъёмы

отличаются количеством контактов, типом

контактов, расстоянием креплений для

процессорных

кулеров,

что

делает

практически все разъёмы несовместимыми.

При

выборе

процессора

необходимо

учитывать сокет.

Front Side Bus (FSB) — это фронтальная

шина,

обеспечивающая

соединение

между

x86-совместимым

центральным

процессором и внутренними устройствами.

Таким образом, FSB работает в качестве

магистрального канала между процессором и

чипсетом.

18.

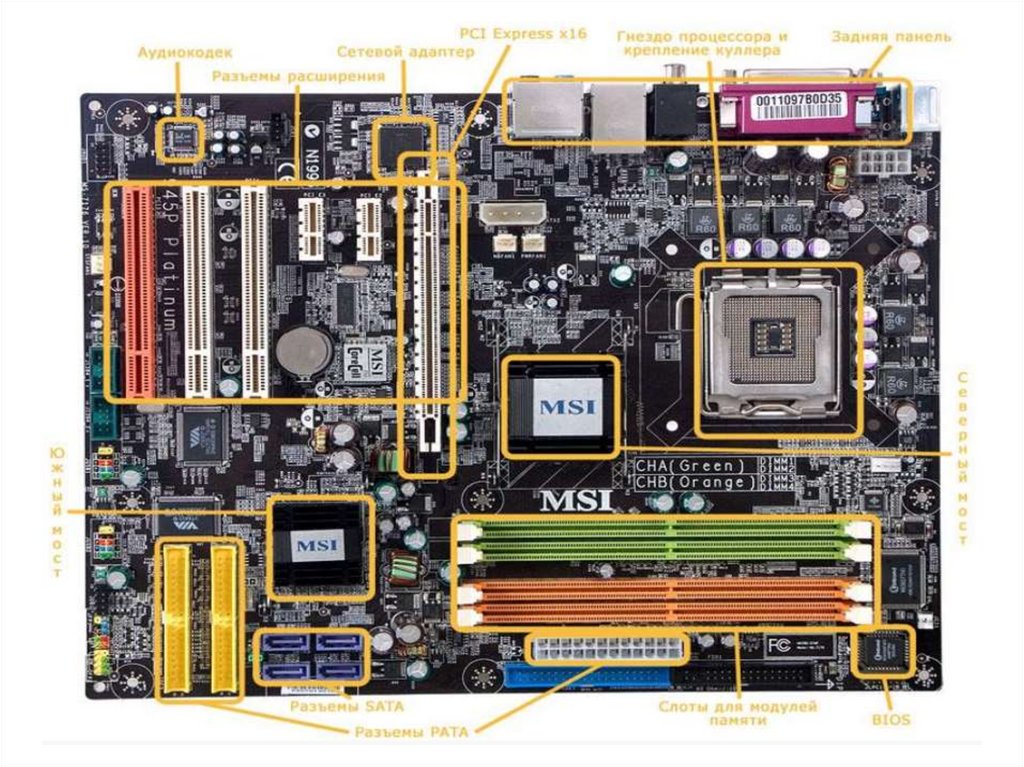

10. Структура современной ЭВМ.Материнская плата (англ. motherboard, MB, также используется

название англ. mainboard — главная плата) — сложная

многослойная печатная плата, на которой устанавливаются

основные компоненты персонального компьютера. Именно

материнская плата объединяет и координирует работу таких

различных по своей сути и функциональности комплектующих, как

процессор, оперативная память, платы расширения и

всевозможные накопители.

Каждое из устройств выполнено в виде отдельной микросхемы

(chip). Все вместе они образуют чипсет (chipset). Чипсет – набор

специализированных микросхем, при подключении которых друг к

другу формируется функциональный блок вычислительной

системы.

Чипсет материнской платы служит для «обвязки» центрального

процессора. Главные компоненты чипсета: северный и южный

мост.

19.

10. Структура современной ЭВМ.Северный мост (Northbridge) - это системный контроллер

(контроллер-концентратор памяти, Memory Controller Hub, MCH),

отвечающий за работу с оперативной памятью (RAM),

видеоадаптером (через графическую шину PCI-E, которая пришла

на смену AGP или PCI) и процессором (CPU). Северный мост

отвечает также за частоту системной шины, тип оперативной

памяти и ее максимально возможный объем. Одной из основных

функций северного моста является обеспечение взаимодействия

системной платы и процессора, а также определение скорости

работы. Частью северного моста во многих материнских платах

является

встроенный

видеоадаптер.

Таким

образом,

функциональная особенность северного моста являет собой еще и

управление шиной видеоадаптера и ее быстродействием. Также

северный мост обеспечивает связь всех вышеперечисленных

устройств с южным мостом.

20.

10. Структура современной ЭВМ.Южный мост (Southbridge) - это функциональный контроллер,

известен как контроллер ввода-вывода или ICH (In/Out Controller

Hub). Отвечает за так называемые "медленные" операции, к

которым относится отработка взаимодействия между различными

интерфейсами (IDE, SATA, USB, LAN, Embeded Audio) и северным

мостом системы, который, в свою очередь, напрямую связан с

процессором и другими важными компонентами, такими как

оперативная память или видеоподсистема. Также южный мост

отвечает за обработку данных на шинах PCI, PCIe и ISA (в старых

моделях системных плат).

Функционально южный мост включает в себя контроллеры

различных шин и устройств. Список обслуживаемых систем

материнской платы южным мостом довольно велик, в основном

это различные параллельные и последовательные шины.

informatics

informatics electronics

electronics