Similar presentations:

Вычислительные машины, системы и сети. Лекция 4. Тема 5. Состав минимальной ЭВМ с шинной организацией

1.

Вычислительные машины, системыи сети

Лекция 4

Состав минимальной ЭВМ с

шинной организацией.

Обмен на шине. Цикл процессора.

к.т.н., доцент, Тычинина Юлия Александровна

2.

5. Состав минимальной ЭВМ с шиннойорганизацией

Практически можно реализовать принцип

фон-Неймана множеством разных способов.

Большинство современных ЭВМ имеют

шинную организацию. Шинная организация

является простейшей формой организации

ЭВМ. В соответствии с принципами фонНеймана, подобная ЭВМ имеет в своём составе

следующие функциональные блоки:

УУ – устройство управления, АЛУ –

арифметико-логическое устройство, память и

порты УВВ (устройства ввода-вывода).

3.

5. Состав минимальной ЭВМ с шиннойорганизацией

4.

5. Состав минимальной ЭВМ с шиннойорганизацией

Устройство управления (УУ) – часть центрального процессора (ЦП).

Вырабатывает распределённую во времени и в пространстве

последовательность внутренних и внешних управляющих сигналов,

обеспечивающих выборку и выполнение команд. Эти сигналы задают

последовательность простейших низкоуровневых операций. Такие

элементарные

низкоуровневые

операции

называют

микрооперациями, а команды, формируемые устройством управления,

называются микрокомандами. Последовательность микрокоманд,

соответствующая одной команде, называется микропрограммой.

В простейшем случае устройство управления имеет в своём составе

три устройства – регистр команды, который содержит код команды во

время её выполнения, программный счётчик, в котором содержится

адрес очередной подлежащей выполнению команды, регистр адреса,

в котором вычисляются адреса операндов, находящихся в памяти.

Для связи пользователя с ЭВМ может быть предусмотрен пульт

управления, который позволяет выполнять такие действия как сброс

ЭВМ в начальное состояние, просмотр регистра или ячейки памяти,

запись адреса в программный счётчик, пошаговое выполнение

программы при её отладке и т.д.

5.

5. Состав минимальной ЭВМ с шиннойорганизацией

Арифметико-логическое устройство (АЛУ). Обычно формирует по

двум входным переменным одну – выходную, выполняя заданную

функцию (сложение, вычитание, сдвиг и т.д.). Выполняемая функция

определяется командой, получаемой от устройства управления.

Арифметико-логическое устройство содержит в своём составе

устройство, хранящее характеристику результата выполнения операции

над данными и называемое флаговым регистром. Отдельные

разряды этого регистра указывают на равенство результата операции

нулю, знак результата операции (плюс или минус), правильность

выполнения операции (наличие переноса за пределы разрядной сетки

или переполнения). Программный анализ флагов позволяет

производить операции ветвления программы в зависимости от

конкретных значений данных.

Кроме того, в АЛУ имеется набор программно-доступных

быстродействующих ячеек памяти, которые называются регистрами

процессора. Регистры составляют основу архитектуры процессора.

6.

5. Состав минимальной ЭВМ с шиннойорганизацией

Среди обязательного набора регистров можно отметить следующие.

Регистр данных – служит для временного хранения промежуточных

результатов при выполнении операций.

Регистр аккумулятор – регистр временного хранения, который

используется в процессе вычислений (например, в нём формируется

результат команды умножения).

Регистр указатель стека – используется при операциях со стеком, т.е.

такой структурой данных, которая работает по принципу: последним вошёл

– первым вышел, т.е. последнее записанное в него значение извлекается из

него первым.

Индексные, указательные и базовые регистры используются для

хранения и вычисления адресов операндов в памяти.

Регистры-счётчики используются для организации циклических

участков в программах.

Регистры общего назначения (РОН), имеющиеся во многих ЭВМ, могут

использоваться для любых целей. Точное назначение такого регистра

определяет программист при написании программы.

7.

5. Состав минимальной ЭВМ с шиннойорганизацией

РОН могут использоваться для временного хранения данных, в

качестве аккумуляторов, а также в качестве индексных, базовых,

указательных регистров. Количество регистров и связей между ними

оказывает существенное влияние на сложность и стоимость

процессора. Однако с другой стороны, наличие большого количества

регистров

с

богатым

набором

возможностей

упрощает

программирование и повышает гибкость программного обеспечения.

Кроме перечисленных регистров в состав АЛУ могут входить

внутренние системные регистры недоступные программно и

используемые во время внутренних пересылок информации при

выполнении команд.

При описании характеристик процессора используется термин

машинное слово – совокупность битов, которые арифметикологическое устройство может одновременно поместить в регистр или

обработать.

8.

5. Состав минимальной ЭВМ с шиннойорганизацией

Генератор тактовой частоты (ГТЧ) генерирует электрические

импульсы заданной частоты для синхронизации различных процессов в

ЭВМ.

Память (ПАМ) – устройство, предназначенное для запоминания,

хранения и выборки программ и данных. Память состоит из конечного

числа ячеек, каждая из которых имеет свой уникальный номер или

адрес. Доступ к ячейке осуществляется указанием её адреса. Память

способна выполнять два вида операций над данными – чтение с

сохранением содержимого и запись нового значения со стиранием

предыдущего.

Периферийные устройства (ПУ). В их число входят устройства двух

типов – устройства внешней памяти, предназначенные для

долговременного хранения данных большого объёма и программ, и

коммуникационные устройства, предназначенные для связи ЭВМ с

внешним миром (с пользователем, другими ЭВМ и т.д.).

9.

5. Состав минимальной ЭВМ с шиннойорганизацией

Обмен данными с внешним устройством осуществляется через

порты ввода-вывода. Порт (в переводе с английского port – ворота,

дверь, отверстие) – это абстрактное понятие, на самом деле не

существующее. По аналогии с ячейками памяти порты можно

рассматривать как ячейки, через которые можно что-либо записать в

периферийное устройство или наоборот – прочитать из него. Так же, как

и ячейки памяти порты имеют уникальные номера – адреса портов

ввода-вывода.

Объединение функциональных блоков в ЭВМ осуществляется

посредством следующей системы шин.

Шина состоит из отдельных проводов (линий). Каждая линия

используется для передачи соответствующего бита. Сигналы по линиям

шины могут передаваться либо импульсами (наличие импульса

соответствует логической 1, а отсутствие импульса – 0), либо уровнем

напряжения (например, высокий уровень – логическая единица, низкий

– 0).

10.

5. Состав минимальной ЭВМ с шиннойорганизацией

Различают шины данных (ШД), по которой осуществляется обмен

информацией между блоками ЭВМ, шины адреса (ША), используемой

для передачи адресов (номеров ячеек памяти или портов ввода-вывода

к которым производится обращение), и шины управления (ШУ) для

передачи управляющих сигналов. Совокупность этих трёх шин называют

системной шиной, системной магистралью или системным

интерфейсом. Состав и назначение линий шины, правила их

использования, виды передаваемых по шине сигналов и другие

характеристики шины могут существенно различаться у разных видов

ЭВМ. Однако есть принципиально общие закономерности в

организации шин.

Шириной шины называется количество линий, входящих в состав

шины. Ширина шины адреса определяет размер адресного

пространства ЭВМ. Если, например, количество линий адреса,

используемых для адресации памяти равно 20, то общее количество

адресуемых ячеек памяти составит 220, т.е. примерно, один миллион

ячеек (точнее 1048576 ячеек).

11.

5. Состав минимальной ЭВМ с шиннойорганизацией

Несмотря на то, что электрический провод позволяет передавать

сигналы в любом направлении, шина служит для передачи информации

лишь в направлении, обозначенном стрелкой на шине. Такая

однонаправленность передачи обусловлена не свойствами шины, а

характеристиками схем, соединяющих шину с устройствами ЭВМ.

Специальные схемы позволяют, например, в одни моменты времени

передавать информацию по шине в одну сторону, а в другие – в

обратном направлении, т.е. организовать двунаправленную шину.

12.

6. Обмен на шине. Цикл процессора.Обмен на шине

Рассмотрим процесс обмена данными между процессором

и памятью в ЭВМ с шинной организацией.

Обычно на шине в любой момент можно выделить два

активных устройства. Одно из них называется задатчиком и

инициирует операцию обмена данными (формирует адреса

и управляющие сигналы), другое называется исполнителем

и выполняет операцию (дешифрует адреса и управляющие

сигналы и принимает или передаёт данные). В большинстве

случаев задатчиком является процессор. Память всегда

выступает только в качестве исполнителя.

13.

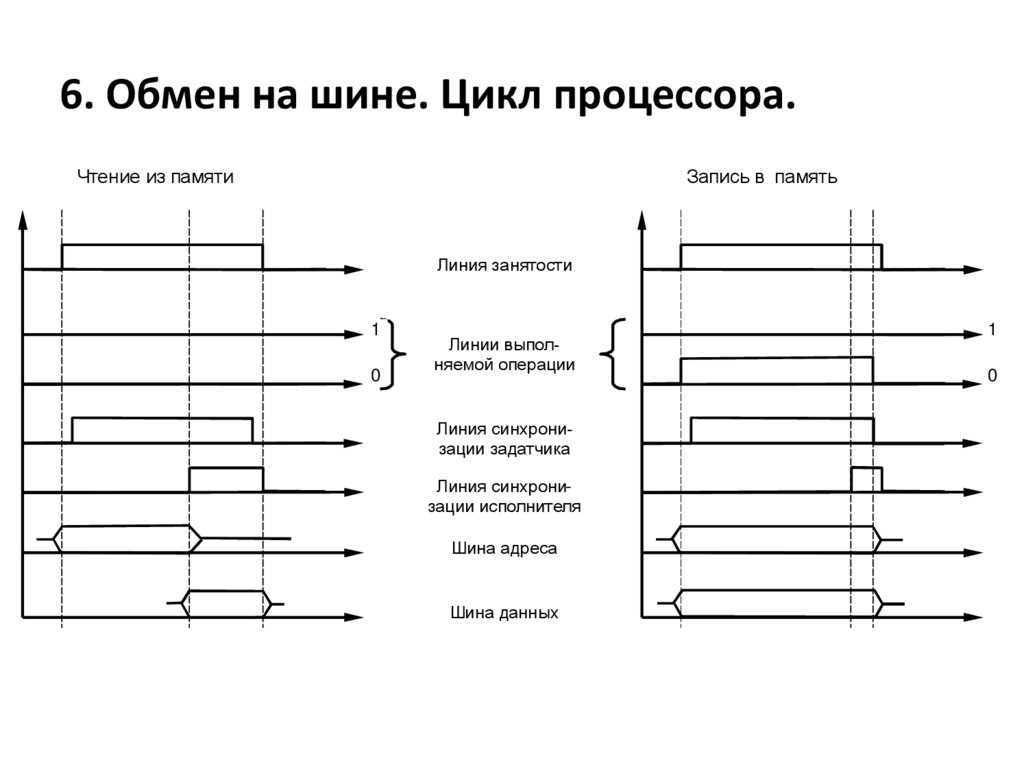

6. Обмен на шине. Цикл процессора.Чтение из памяти

Запись в память

Линия занятости

1

0

Линии выполняемой операции

Линия синхронизации задатчика

Линия синхронизации исполнителя

Шина адреса

Шина данных

1

0

14.

6. Обмен на шине. Цикл процессора.Управляющие линии:

Линия занятости. Если она в состоянии «шина свободна»,

любой задатчик, включая процессор, может начать операцию

обмена данными на шине, иначе задатчику придётся ожидать,

пока шина не освободится.

Линии выполняемой операции. Указывают, какая именно

операция будет выполняться. Как минимум необходим следующий

набор операций – чтение из памяти (процессор принимает

данные от памяти), запись в память (процессор передает данные

в память), ввод из порта ввода-вывода (процессор принимает

данные из порта ввода-вывода) и вывод в порт ввода-вывода

(процессор передаёт данные в порт ввода-вывода). Четыре

команды могут быть закодированы двухразрядным двоичным

числом, например: 00 – чтение, 01 – запись, 10 – ввод, 11 – вывод.

15.

6. Обмен на шине. Цикл процессора.Линии синхронизации. Синхронизация задатчиков и

исполнителей может осуществляться по-разному. Один из

распространённых способов состоит в следующем. Задатчик

в процессе операции обмена выставляет на шине сигнал

синхронизации задатчика. Получив сигнал от задатчика,

исполнитель выполняет операцию обмена (передаёт или

принимает данные) и выставляет на шине ответный сигнал

синхронизации исполнителя. Получив ответ от исполнителя,

задатчик освобождает шину.

16.

6. Обмен на шине. Цикл процессора.Операция «считывание ячейки памяти» выполняется

следующим образом:

- процессор переводит шину в состояние «занято»,

- на адресную шину помещается адрес требуемой ячейки

памяти,

- Процессор устанавливается на шине управления сигнал

«чтение»,

- процессор выдаёт сигнал синхронизации задатчика,

- память принимает адрес, дешифрует его, находит нужную

ячейку и помещает её содержимое на шину данных,

- память выдает сигнал синхронизации исполнителя,

- получив ответ от памяти, процессор считывает данные с

шины, снимает свои управляющие сигналы и освобождает

шину.

17.

6. Обмен на шине. Цикл процессора.При операции «запись в память» необходимо выполнить

следующие действия:

- шина переводится процессором в состояние «занято»,

- адрес требуемой ячейки памяти помещается на шину

адреса,

- данные, которые необходимо записать в память

помещаются на шину данных,

- на шине управления устанавливается сигнал «запись»,

выдаётся сигнал синхронизации задатчика,

- память принимает адрес, дешифрирует его, помещает в

соответствующую ячейку данные с шины и выдаёт сигнал

синхронизации исполнителя,

- получив ответ от памяти, процессор снимает управляющие

сигналы и освобождает шину.

18.

6. Обмен на шине. Цикл процессора.Такой способ обмена данными называется асинхронным

обменом, а сама операция запроса/подтверждения носит

название квитирования или рукопожатия (handshake) и

широко применяется при построении системы шин

различного назначения в различных ЭВМ.

19.

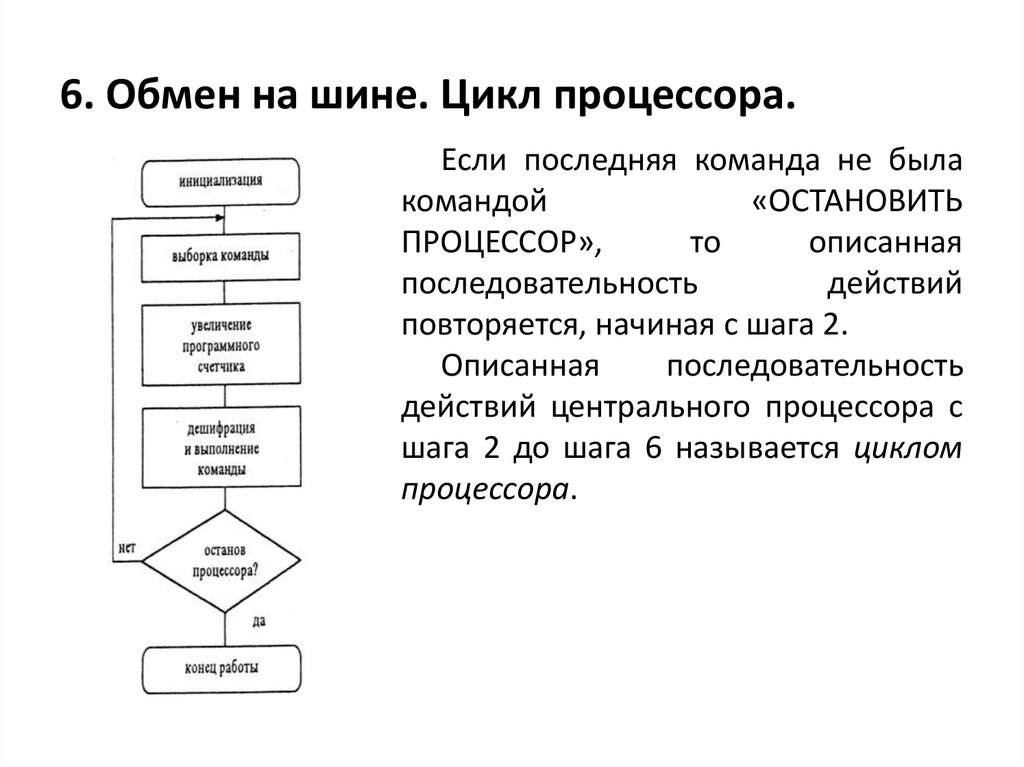

6. Обмен на шине. Цикл процессора.Команды исполняющейся программы

хранятся в памяти ЭВМ друг за другом.

Функционирование ЭВМ с приведённой

выше

структурой

можно

описать

следующим обобщённым алгоритмом (см.

рисунок).

Инициализация. После включения ЭВМ

или операции сброса в регистры

центрального

процессора

заносятся

некоторые

начальные

значения.

Программному счётчику присваивается

начальное значение, равное адресу

первой команды программы.

20.

6. Обмен на шине. Цикл процессора.Производится считывание команды из памяти. В качестве

адреса ячейки памяти используется содержимое программного

счётчика.

Содержимое считанной ячейки памяти интерпретируется как

команда и помещается в регистр команды. Устройство управления

приступает к интерпретации прочитанной команды. По полю кода

операции из первого слова команды устройство управления

определяет её длину, и, если это необходимо, организует

дополнительные операции считывания, пока вся команда

полностью не будет прочитана процессором. Вычисленная длина

команды прибавляется к исходному содержимому программного

счётчика, и когда команда полностью прочитана, программный

счётчик будет хранить адрес следующей команды.

21.

6. Обмен на шине. Цикл процессора.По адресным полям команды устройство управления

определяет, имеет ли команда операнды в памяти. Если это

так, то вычисляются адреса операндов и производятся

операции чтения памяти для считывания операндов.

Устройство

управления

и

арифметико-логическое

устройство выполняют операцию, указанную в поле кода

операции команды. Во флаговом регистре запоминаются

признаки результата операции (равно нулю или нет, знак

результата, наличие переполнения и т.д.)

Если это необходимо, устройство управления выполняет

операцию записи для того, чтобы поместить результат

выполнения команды в память.

22.

6. Обмен на шине. Цикл процессора.Если последняя команда не была

командой

«ОСТАНОВИТЬ

ПРОЦЕССОР»,

то

описанная

последовательность

действий

повторяется, начиная с шага 2.

Описанная

последовательность

действий центрального процессора с

шага 2 до шага 6 называется циклом

процессора.

23.

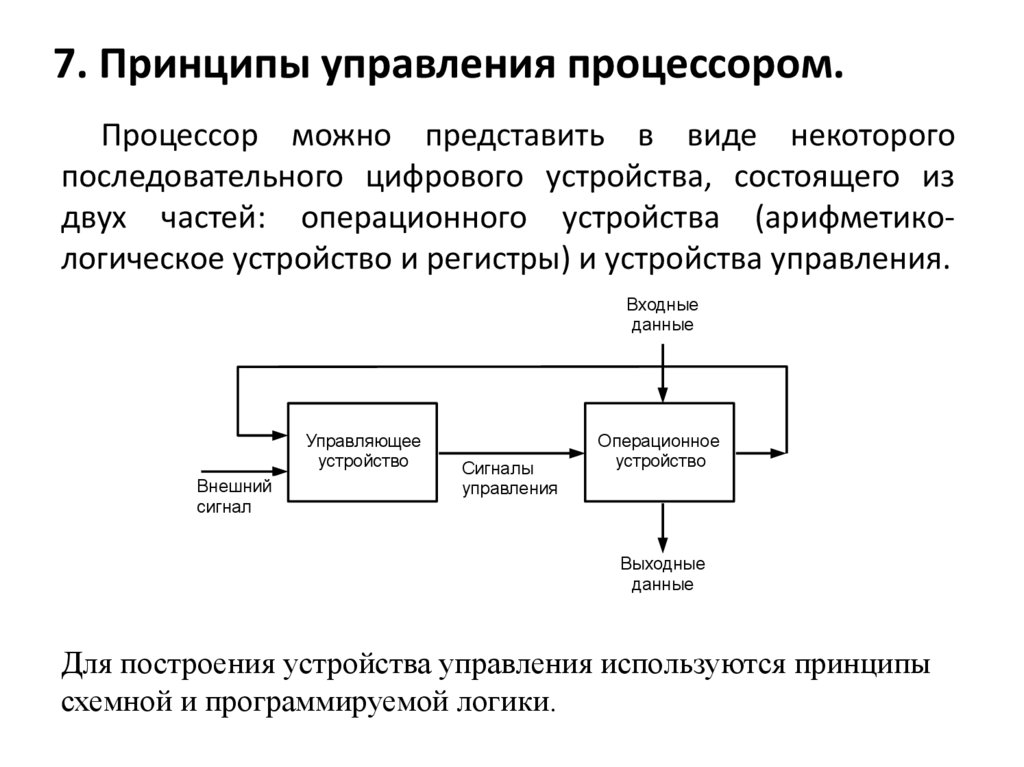

7. Принципы управления процессором.Процессор можно представить в виде некоторого

последовательного цифрового устройства, состоящего из

двух частей: операционного устройства (арифметикологическое устройство и регистры) и устройства управления.

Входные

данные

Управляющее

устройство

Внешний

сигнал

Сигналы

управления

Операционное

устройство

Выходные

данные

Для построения устройства управления используются принципы

схемной и программируемой логики.

24.

7. Принципы управления процессором.Принципы схемной логики

Входные

данные

РгК

Команда

Дешифратор

УУ команды 1

УУ команды 2

Операционное

устройство

УУ команды k

Выходные

данные

25.

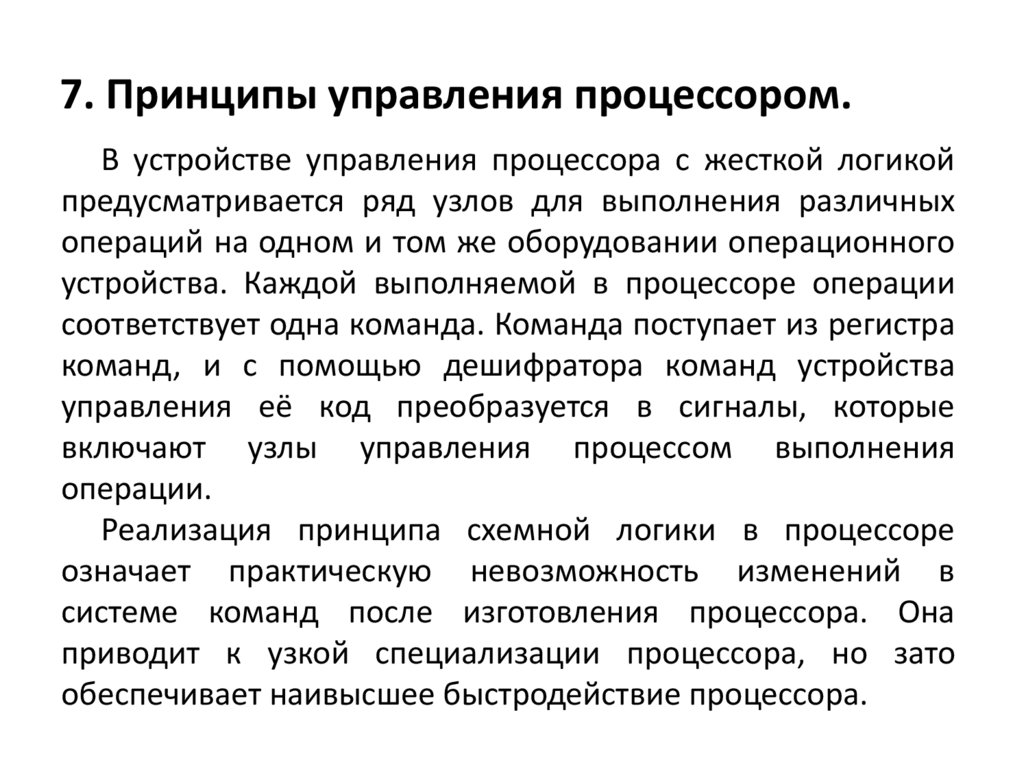

7. Принципы управления процессором.В устройстве управления процессора с жесткой логикой

предусматривается ряд узлов для выполнения различных

операций на одном и том же оборудовании операционного

устройства. Каждой выполняемой в процессоре операции

соответствует одна команда. Команда поступает из регистра

команд, и с помощью дешифратора команд устройства

управления её код преобразуется в сигналы, которые

включают узлы управления процессом выполнения

операции.

Реализация принципа схемной логики в процессоре

означает практическую невозможность изменений в

системе команд после изготовления процессора. Она

приводит к узкой специализации процессора, но зато

обеспечивает наивысшее быстродействие процессора.

26.

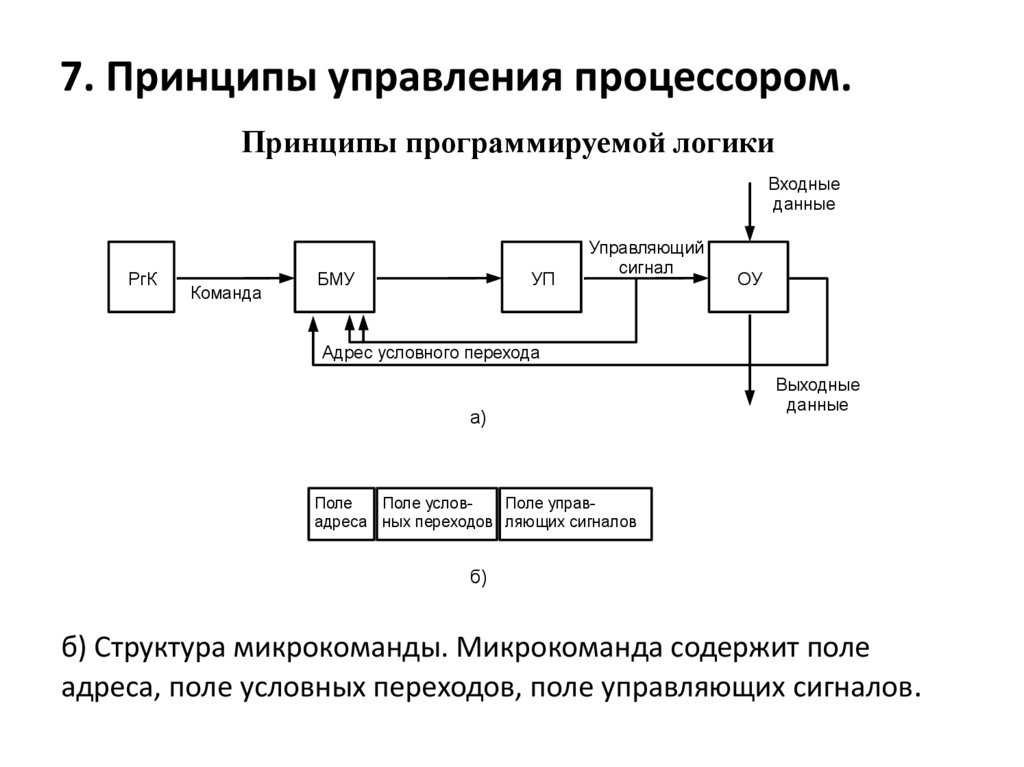

7. Принципы управления процессором.Принципы программируемой логики

Входные

данные

РгК

Команда

БМУ

УП

Управляющий

сигнал

ОУ

Адрес условного перехода

а)

Выходные

данные

Поле

Поле условПоле управадреса ных переходов ляющих сигналов

б)

б) Структура микрокоманды. Микрокоманда содержит поле

адреса, поле условных переходов, поле управляющих сигналов.

27.

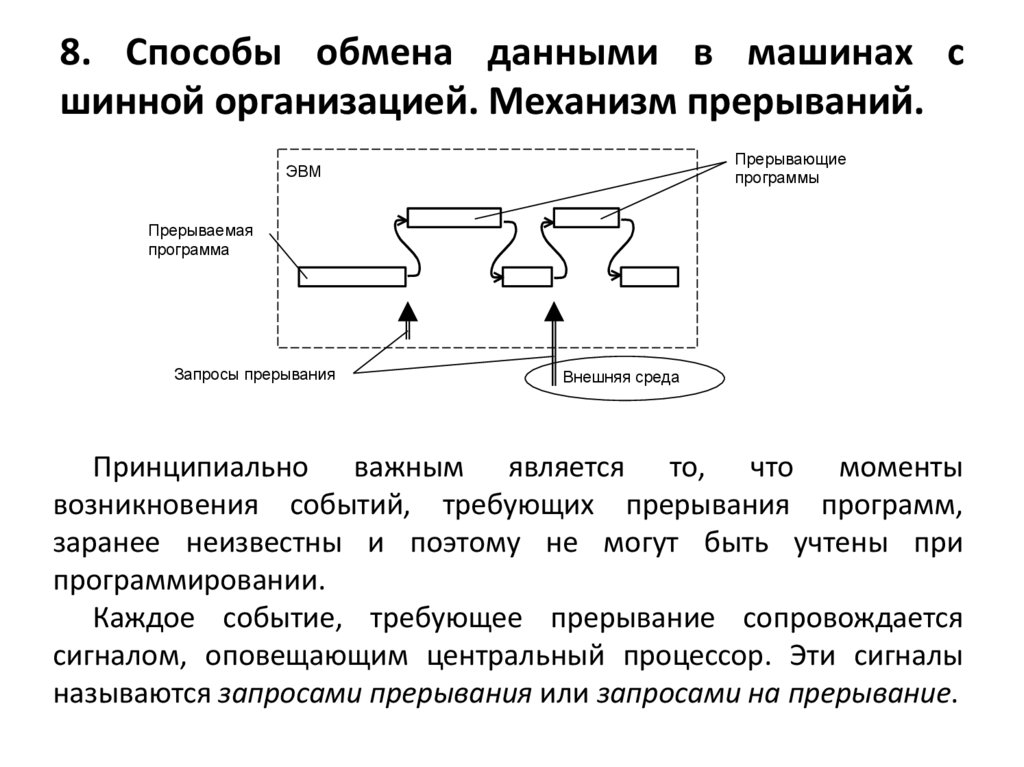

8. Способы обмена данными в машинах сшинной организацией. Механизм прерываний.

Прерывающие

программы

ЭВМ

Прерываемая

программа

Запросы прерывания

Внешняя среда

Принципиально важным является то, что моменты

возникновения событий, требующих прерывания программ,

заранее неизвестны и поэтому не могут быть учтены при

программировании.

Каждое событие, требующее прерывание сопровождается

сигналом, оповещающим центральный процессор. Эти сигналы

называются запросами прерывания или запросами на прерывание.

28.

8. Способы обмена данными в машинах сшинной организацией. Механизм прерываний.

Реализация механизма прерываний по сигналам запросов

внешних устройств имеет наибольшую важность при обмене

данными процессора с большим числом асинхронно работающих

внешних устройств.

Запросы прерываний поступают в произвольный момент

времени, поэтому процессор должен закончить выполнение

текущей команды и только после этого приступить к обработке

запроса. При этом промежуточные результаты работы процессора

по программе должны быть переданы на хранение в память.

После обработки прерывания зафиксированные в памяти

промежуточные результаты возвращаются обратно в регистры

процессора. Такой порядок реализации процесса прерывания

позволяет переходить от программы к подпрограмме обработки

прерываний и обратно без потерь промежуточной информации и

нарушения процесса вычислений.

29.

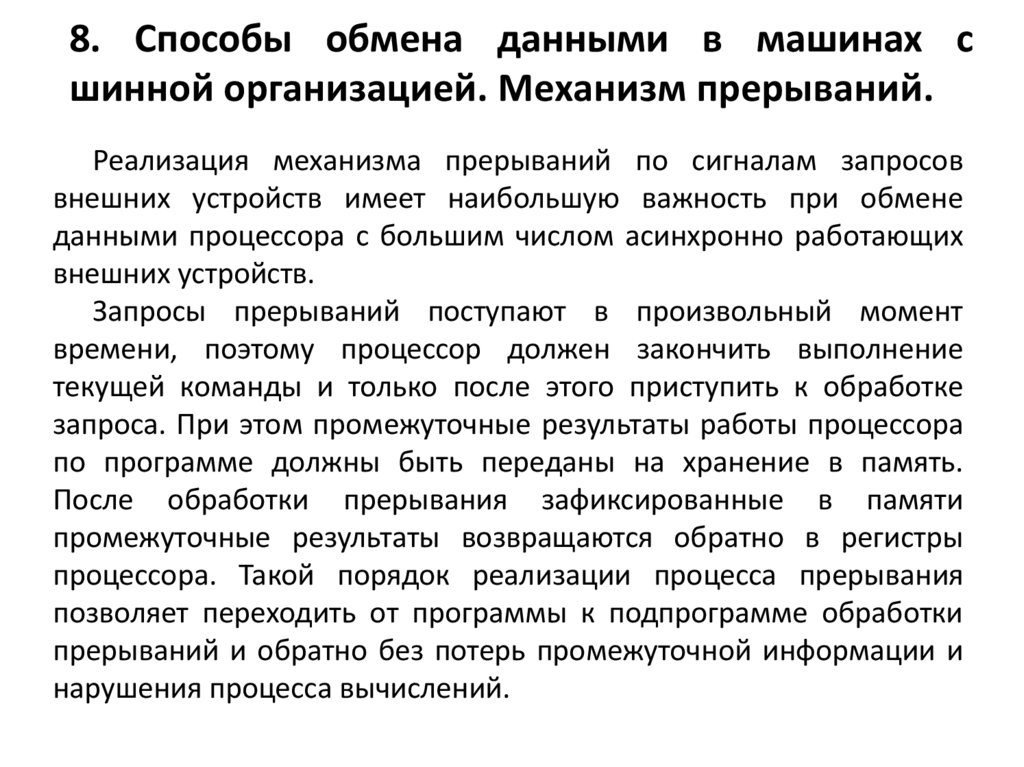

8. Способы обмена данными в машинах сшинной организацией. Механизм прерываний.

1

2

3

t

Запросы на

прерывание

3

2

2

1

1

t

1

2

3

t

Очерёдность исполнения

программ при нулевой глубине

или при приоритетах 1>2>3

t

Очерёдность исполнения

программ при приоритетах

2>1>3

2

1

Очерёдность исполнения

программ при глубине >2

1 3

Глубина прерывания – максимальное число программ, которые могут

прерывать друг друга. Если процессор построен так, что нельзя прервать

прерывающую программу, то считается, что микропроцессор имеет нулевой

уровень программного прерывания.

Приоритет прерываний это характеристика важности, присваиваемая

прерыванию. Как правило, процессор может одновременно обслуживать

только одно прерывание, однако в некоторых случаях скорость поступления

прерываний превышает скорость их обслуживания. В подобной ситуации

система может прерывать обслуживание некоторых прерываний при

наличии более важных прерываний.

30.

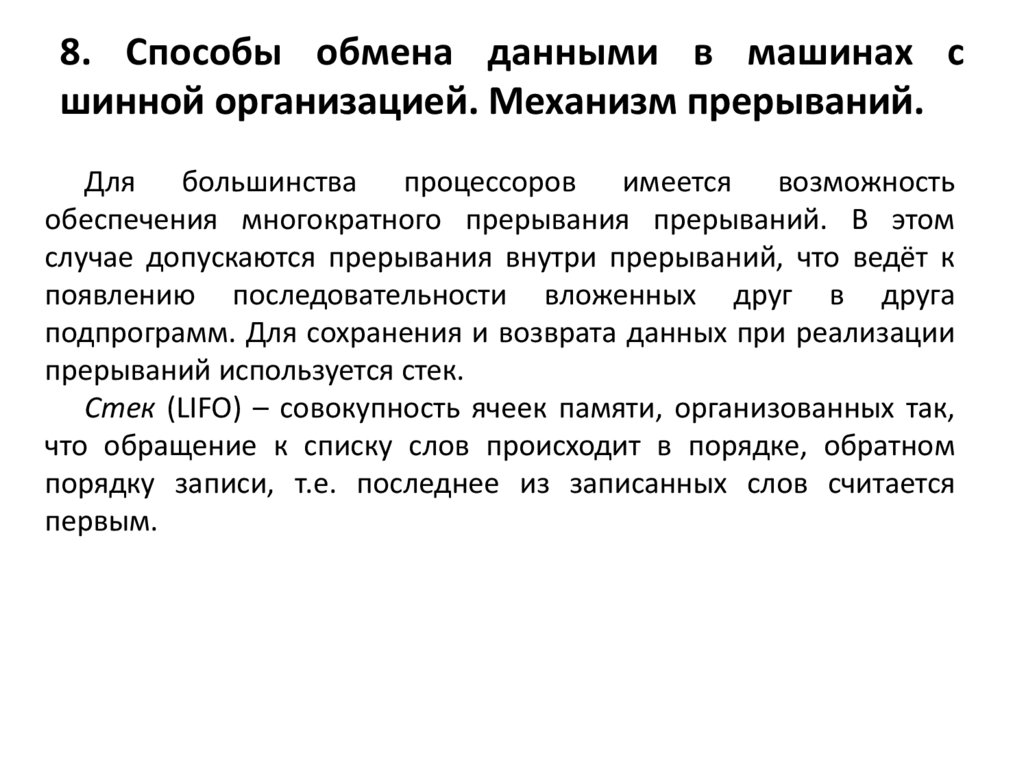

8. Способы обмена данными в машинах сшинной организацией. Механизм прерываний.

Для большинства процессоров имеется возможность

обеспечения многократного прерывания прерываний. В этом

случае допускаются прерывания внутри прерываний, что ведёт к

появлению последовательности вложенных друг в друга

подпрограмм. Для сохранения и возврата данных при реализации

прерываний используется стек.

Стек (LIFO) – совокупность ячеек памяти, организованных так,

что обращение к списку слов происходит в порядке, обратном

порядку записи, т.е. последнее из записанных слов считается

первым.

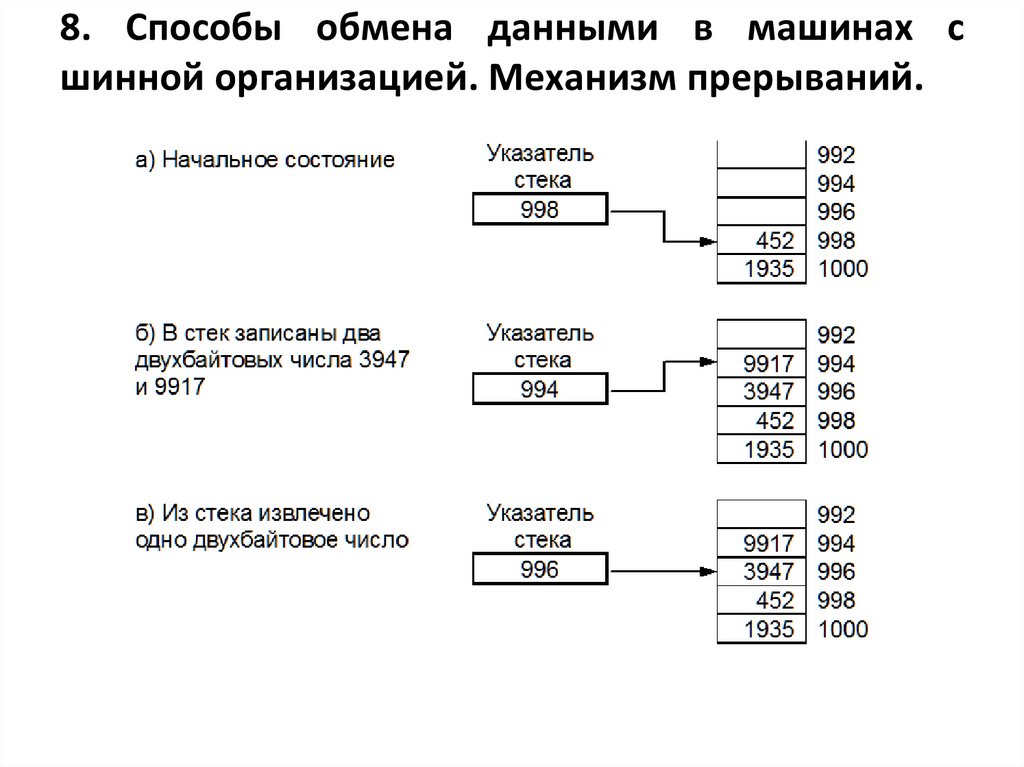

31.

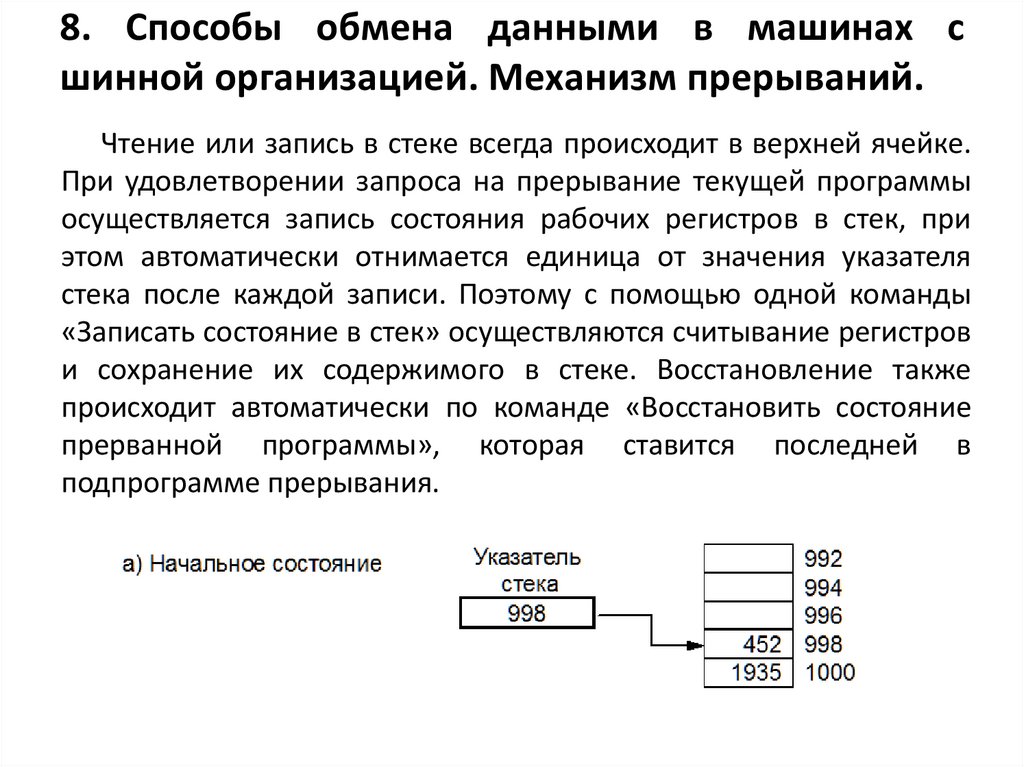

8. Способы обмена данными в машинах сшинной организацией. Механизм прерываний.

Чтение или запись в стеке всегда происходит в верхней ячейке.

При удовлетворении запроса на прерывание текущей программы

осуществляется запись состояния рабочих регистров в стек, при

этом автоматически отнимается единица от значения указателя

стека после каждой записи. Поэтому с помощью одной команды

«Записать состояние в стек» осуществляются считывание регистров

и сохранение их содержимого в стеке. Восстановление также

происходит автоматически по команде «Восстановить состояние

прерванной программы», которая ставится последней в

подпрограмме прерывания.

32.

8. Способы обмена данными в машинах сшинной организацией. Механизм прерываний.

33.

8. Способы обмена данными в машинах сшинной организацией. Механизм прерываний.

34.

8. Способы обмена данными в машинах сшинной организацией. Механизм прерываний.

Различают маскируемые и немаскируемые запросы на

прерывание.

Немаскируемые

реализуются

аппаратно

вне

программного контроля и не управляются программно. Эти

прерывания имеют высший приоритет и исполняются ранее

других запросов на прерывания. Примерами немаскируемых

запросов могут служить запросы на прерывания от схем

питания, схем контроля правильности передачи данных.

Маскируемые управляются командами программы и

обеспечивают

возможность

гибкого

управления

вычислительным процессом.

35.

8. Способы обмена данными в машинах сшинной организацией. Механизм прерываний.

Для определения адреса программы при прерывании по

запросу от внешнего устройства используются различные

методы. Например, в памяти ЭВМ хранится вектор

прерываний – массив адресов подпрограмм обслуживания

прерываний. В момент подтверждения прерывания,

устройство ввода-вывода выставляет на шине данных код,

который используется процессором как номер элемента

вектора прерываний. По этому номеру из массива

извлекается один из элементов – адрес требуемой

подпрограммы обслуживания прерывания.

36.

8. Способы обмена данными в машинах сшинной организацией. Механизм прерываний.

Организация ввода-вывода данных

В машинах с шинной организацией можно выделить три

базовых способа обмена данными между «быстрой» частью

(процессор и память) и «медленной» частью (контроллеры и

периферийные устройства). К таким способам относятся:

• Программно – управляемый обмен данными.

• Обмен по прерываниям.

• Внепроцессорный доступ к памяти.

37.

8. Способы обмена данными в машинах сшинной организацией. Механизм прерываний.

При программном обмене данными по командам

условного перехода центральный процессор определяет

программным путем, готово ли внешнее устройство к

выполнению операций ввода-вывода до начала передачи

данных. Процессор считывает информацию о состоянии

готовности внешнего устройства, производит её анализ и

принимает решение о готовности устройства. При этом

процессор находится в режиме ожидания готовности

внешнего

устройства,

выполняя

соответствующую

подпрограмму. После обнаружения готовности процессор

передает данные и затем приступает к продолжению

основной программы. В качестве примера программного

обмена данными можно рассматривать вывод документа на

принтер.

38.

8. Способы обмена данными в машинах сшинной организацией. Механизм прерываний.

При обмене данными по сигналам прерывания работы

процессора от внешних устройств последние сами являются

инициаторами обмена. Процессор работает параллельно с

внешними устройствами по основной программе и не

занимается анализом состояния внешних устройств. При

появлении запроса на прерывание от какого-либо внешнего

устройства процессор переходит

к подпрограмме

обслуживания прерывания, основной частью которой

являются команды обмена данными между процессором и

внешними устройствами. По окончанию подпрограммы

процессор возвращается к основной программе.

39.

8. Способы обмена данными в машинах сшинной организацией. Механизм прерываний.

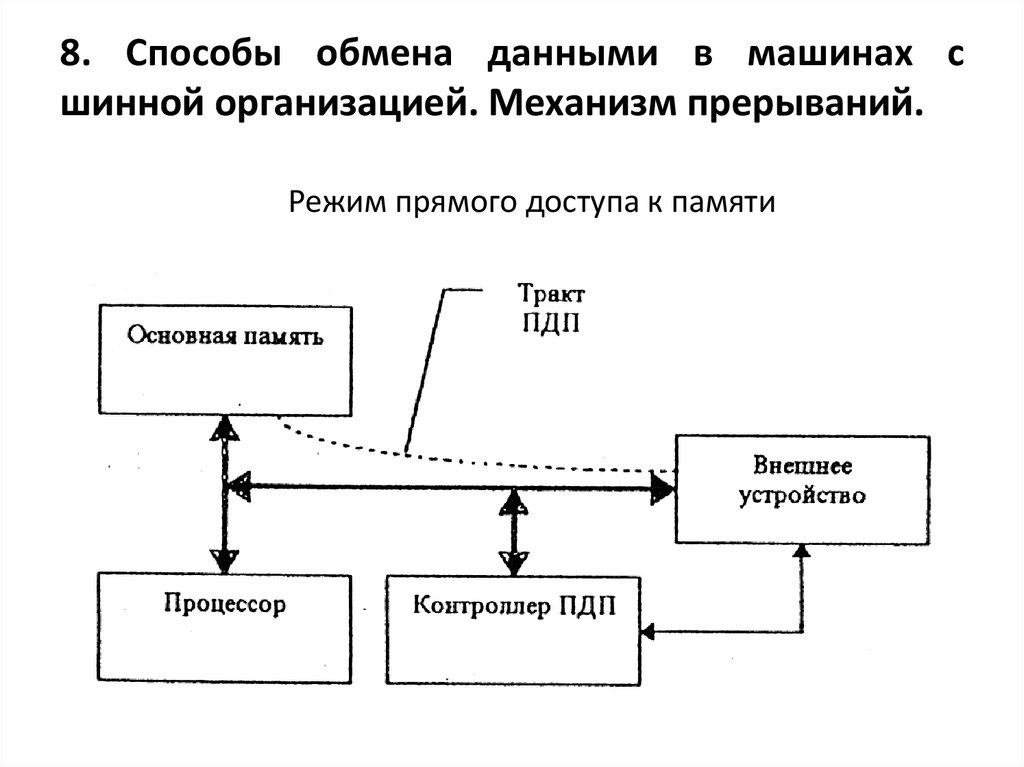

Внепроцессорный доступ. При обмене данными между

внешними устройствами и памятью нет необходимости

пересылать данные через процессор. Для этих целей используется

обмен данных по каналу прямого доступа (ПДП). В состав ЭВМ

вводится специальный контроллер прямого доступа в память

(контроллер ПДП), который берет на себя управление передачей

без применения процессора.

Контроллер ПДП может быть реализован в виде отдельного

устройства, доступного всем периферийным устройствам

(централизованная

система

ПДП).

Внешние

устройства,

нуждающиеся в ПДП, могут иметь в своём контроллере

собственные средства организации ПДП. Второй случай приводит к

узкоспециализированным средствам ПДП, однако позволяет

учитывать специфические потребности каждого устройства

(контроллер жесткого диска).

40.

8. Способы обмена данными в машинах сшинной организацией. Механизм прерываний.

В идеальном случае контроллер ПДП совершенно не

должен влиять на действия процессора, но для этого

потребуется дополнительный сложный и дорогой тракт

доступа к оперативной памяти. Такие средства имеются в

дорогих больших ЭВМ. Для микроЭВМ такие средства

неприемлемы из-за их высокой стоимости.

В микроЭВМ используется более простой и менее

производительный

приём

мультиплексирования

общей

системной шины между процессором и контроллером ПДП.

41.

8. Способы обмена данными в машинах сшинной организацией. Механизм прерываний.

В обычных условиях системной шиной «распоряжается»

центральный процессор, он является задатчиком при

большинстве операций на шине. При подготовке операции

обмена с использованием ПДП процессор программирует

контроллер ПДП: «указывает» ему, сколько нужно переслать

данных и по какому адресу эти данные необходимо

поместить. Когда режим ПДП инициируется, задатчиком

становится контроллер ПДП. Он «распоряжается» шиной,

управляя передачей данных непосредственно между

основной и внешней памятью, а действия процессора

приостанавливаются, и он отключается от системной шины

42.

8. Способы обмена данными в машинах сшинной организацией. Механизм прерываний.

Режим прямого доступа к памяти

informatics

informatics electronics

electronics