Similar presentations:

Цифровые комбинационные устройства. Тема 4.2

1. Тема 4.2. Цифровые комбинационные устройства (2 час) (шифратор и дешифратор; мультиплексор и демультиплексор; цифровой

компаратор;полусумматор и сумматор; арифметикологическое устройство)

2.

3.

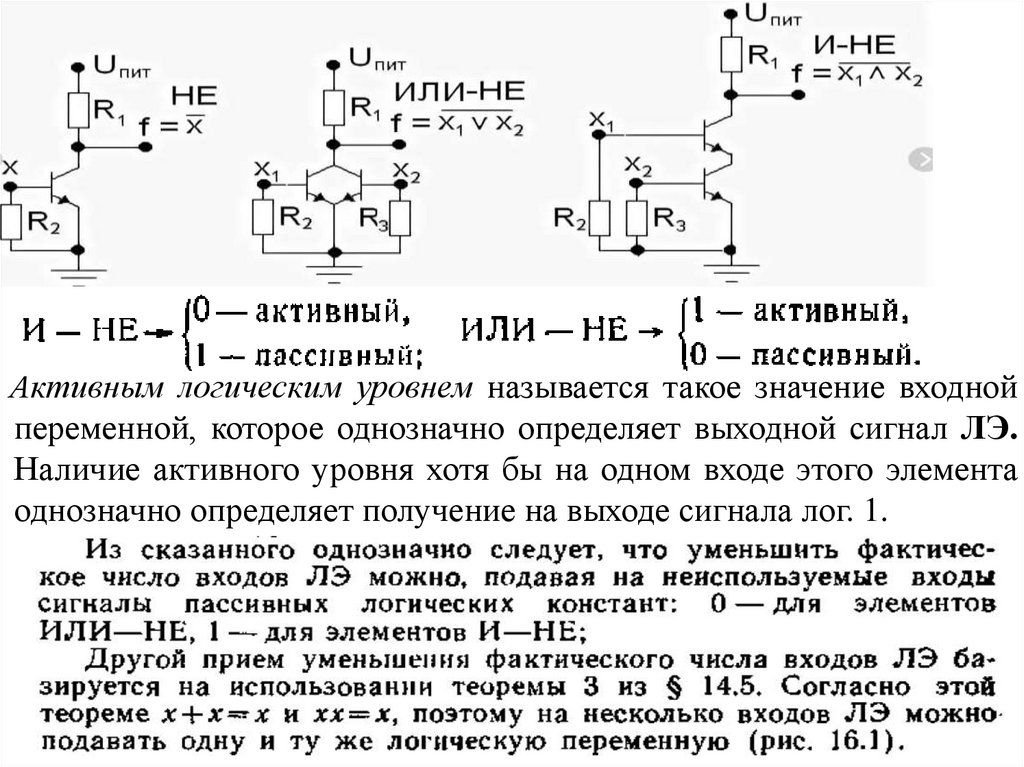

Активным логическим уровнем называется такое значение входнойпеременной, которое однозначно определяет выходной сигнал ЛЭ.

Наличие активного уровня хотя бы на одном входе этого элемента

однозначно определяет получение на выходе сигнала лог. 1.

4.

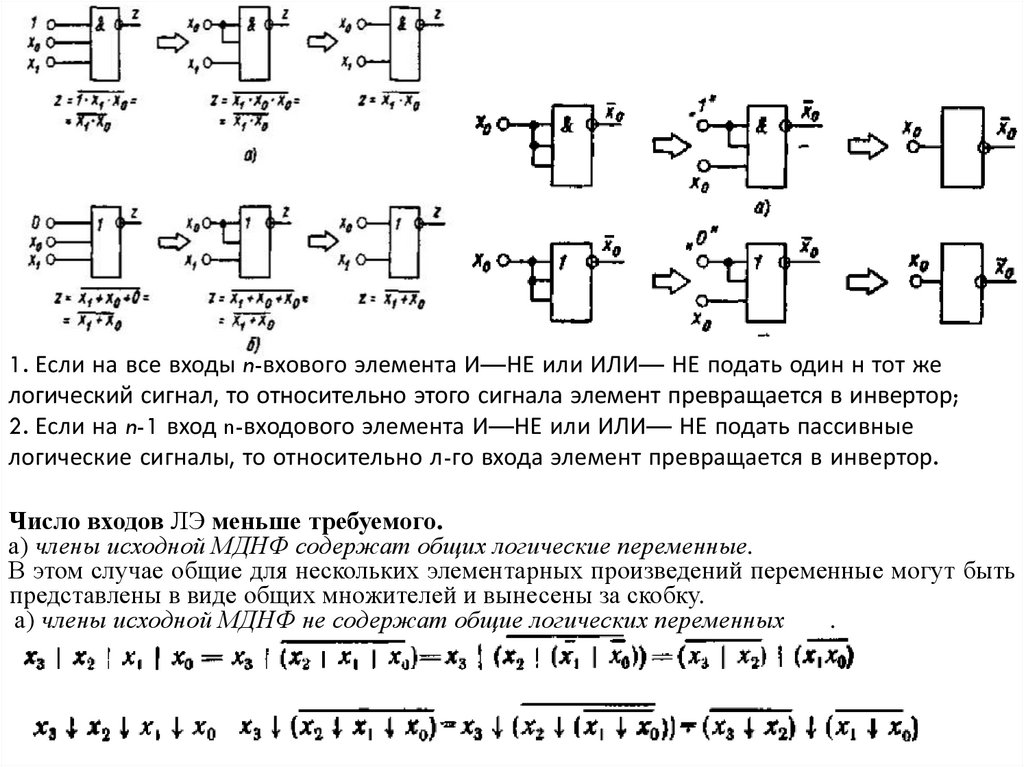

1. Если на все входы n-вхового элемента И—НЕ или ИЛИ— НЕ подать один н тот желогический сигнал, то относительно этого сигнала элемент превращается в инвертор;

2. Если на n-1 вход n-входового элемента И—НЕ или ИЛИ— НЕ подать пассивные

логические сигналы, то относительно л-го входа элемент превращается в инвертор.

Число входов ЛЭ меньше требуемого.

а) члены исходной МДНФ содержат общих логические переменные.

В этом случае общие для нескольких элементарных произведений переменные могут быть

представлены в виде общих множителей и вынесены за скобку.

а) члены исходной МДНФ не содержат общие логических переменных

.

5.

В общем случае на вход цифрового устройства поступает n (n 1) двоичныхпеременных Х (х1х2хп), а с выхода снимается m (m 1) двоичных переменных У

(у1у2уm). При этом устройства осуществляют (реализуют) определенную связь (ФАЛ)

между входными и выходными переменными.

В комбинационных устройствах (КУ) – автоматах без памяти

значения выходных переменных в течение каждого такта работы

определяют значения входных и выходных переменных только в

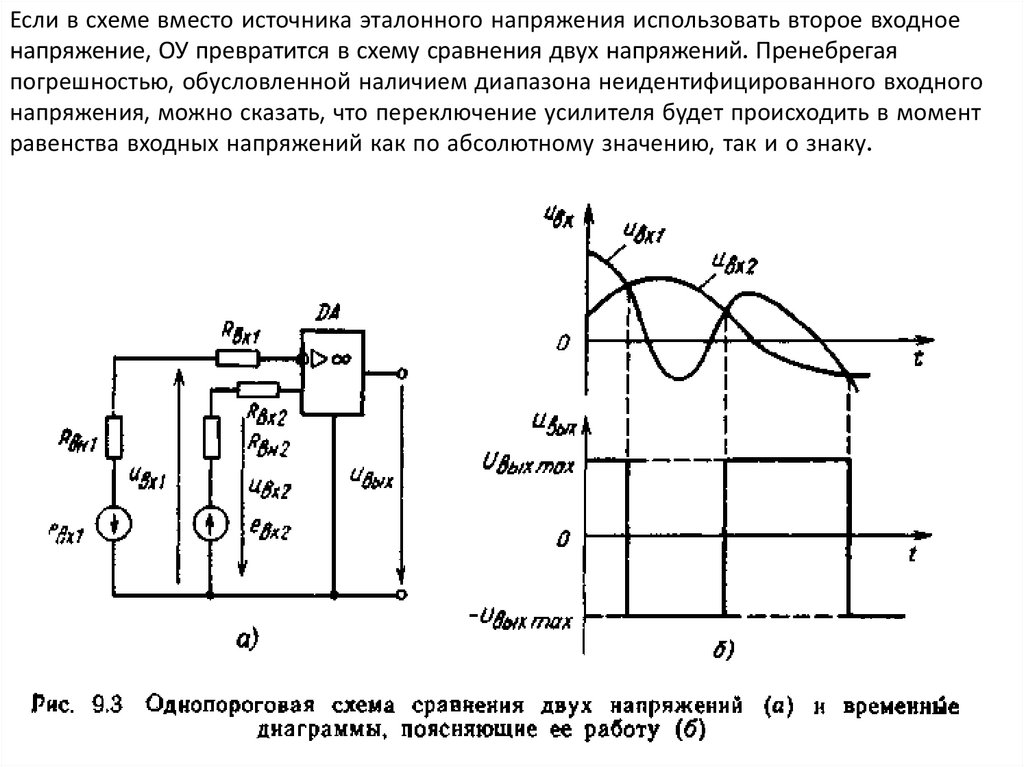

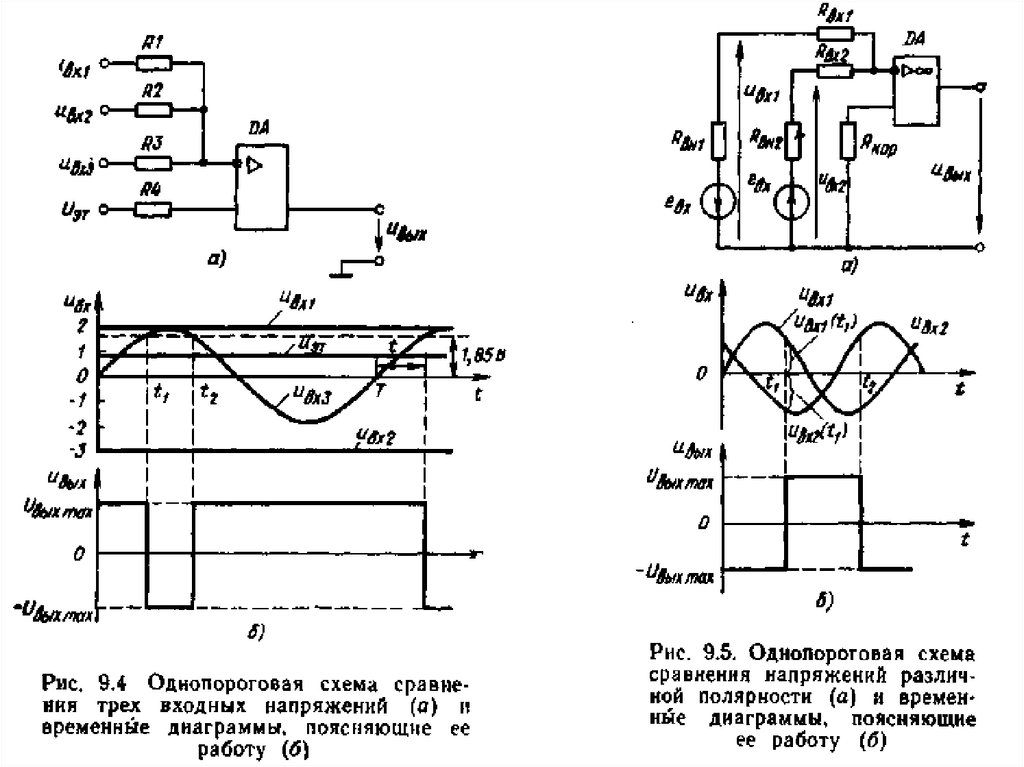

этот же такт, и не зависят значений переменные на входе в

предыдущие такты, т. е. У = f(Х). Другими словами, эти устройства,

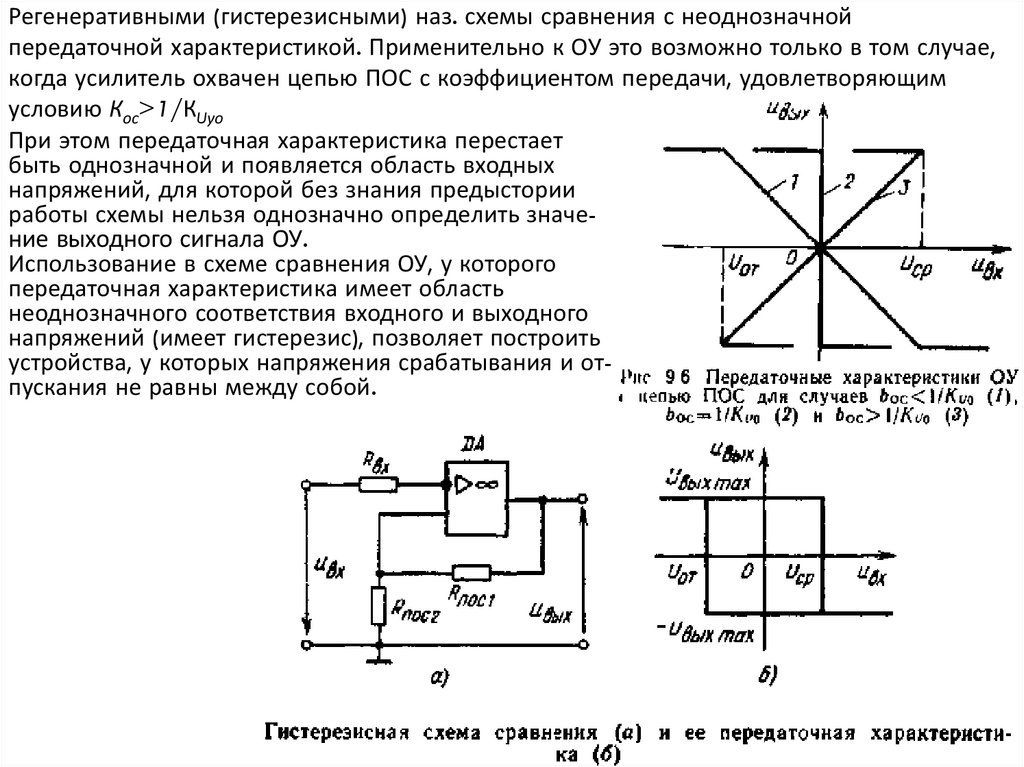

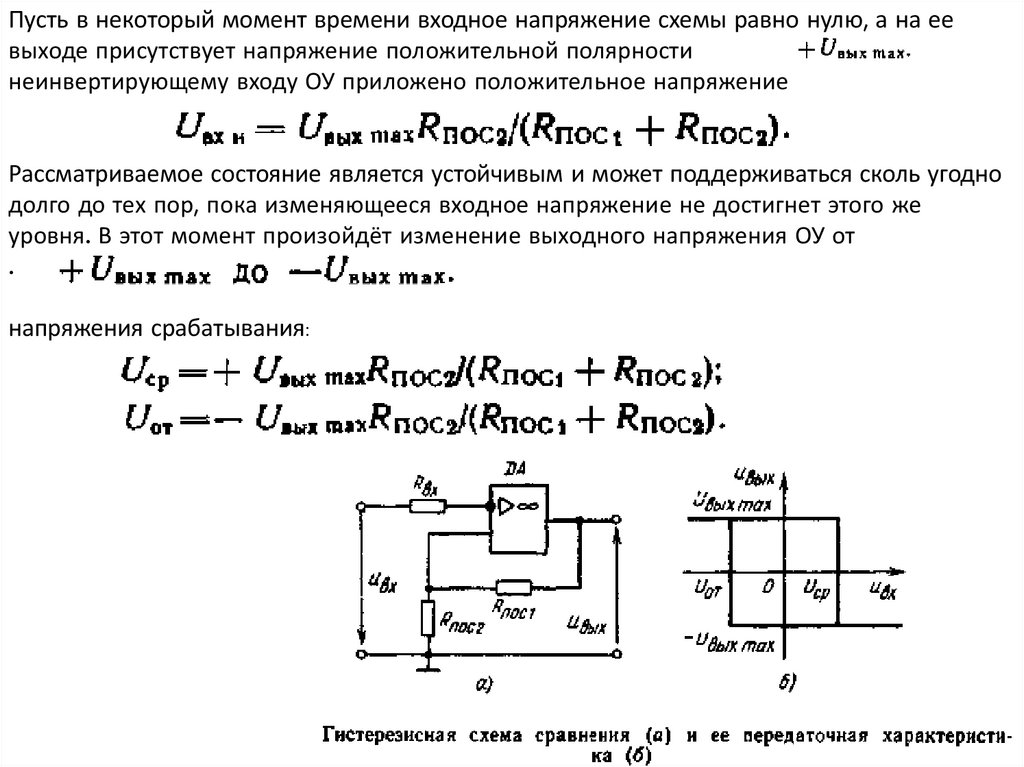

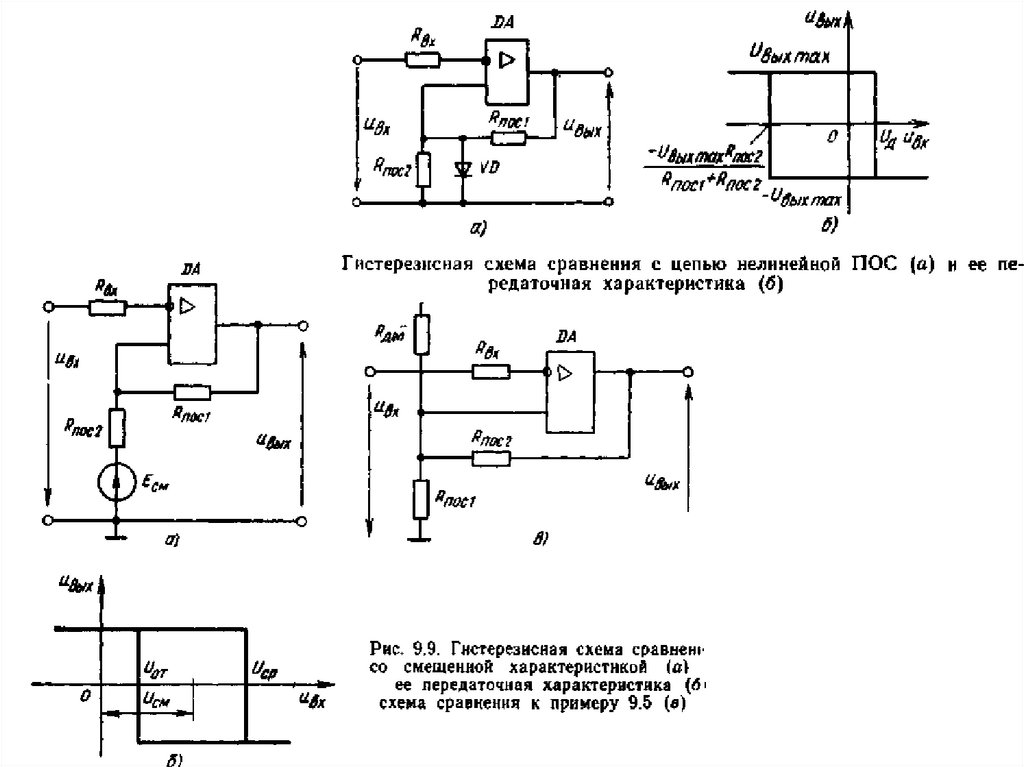

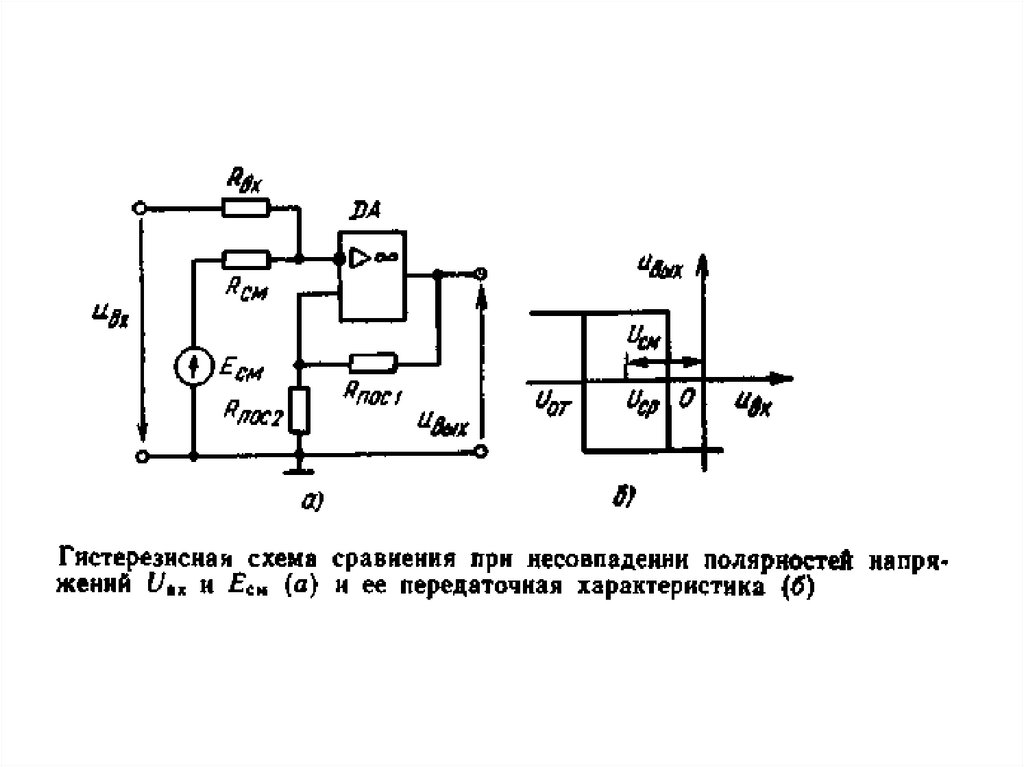

состоящие только из логических элементов, лишены памяти: не

хранят информацию о прошлом. Входные и выходные сигналы

комбинационных устройств могут принимать только два значения: 1 и 0.

6.

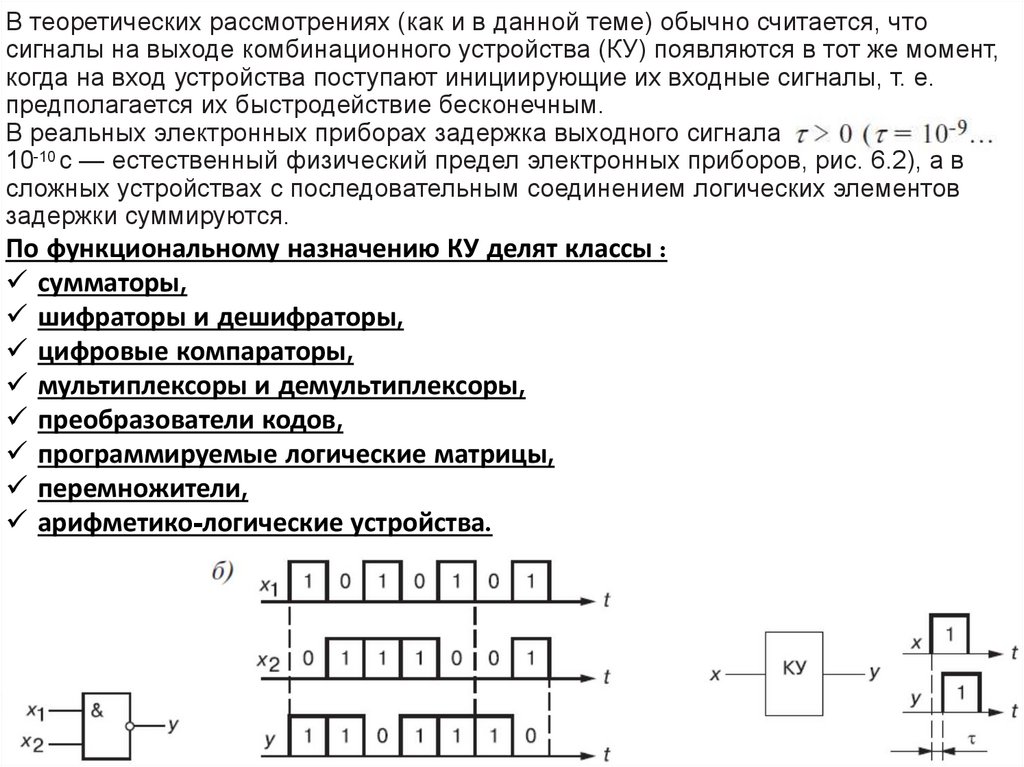

В теоретических рассмотрениях (как и в данной теме) обычно считается, чтосигналы на выходе комбинационного устройства (КУ) появляются в тот же момент,

когда на вход устройства поступают инициирующие их входные сигналы, т. е.

предполагается их быстродействие бесконечным.

В реальных электронных приборах задержка выходного сигнала

10-10 с — естественный физический предел электронных приборов, рис. 6.2), а в

сложных устройствах с последовательным соединением логических элементов

задержки суммируются.

По функциональному назначению КУ делят классы :

сумматоры,

шифраторы и дешифраторы,

цифровые компараторы,

мультиплексоры и демультиплексоры,

преобразователи кодов,

программируемые логические матрицы,

перемножители,

арифметико-логические устройства.

7.

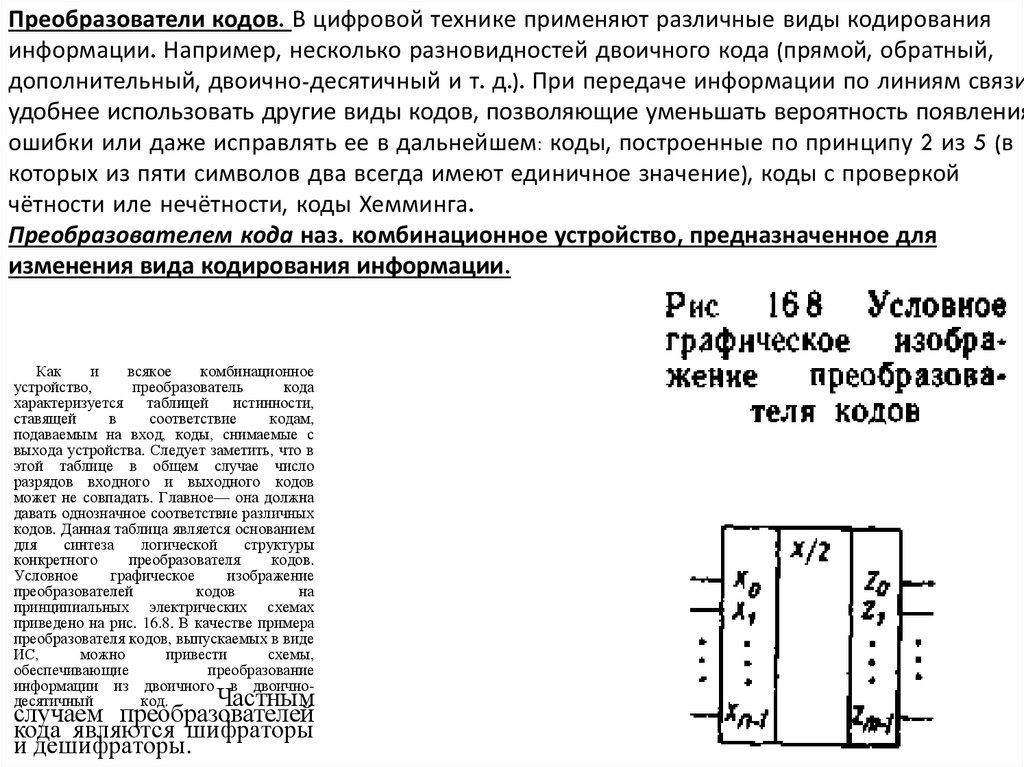

Преобразователи кодов. В цифровой технике применяют различные виды кодированияинформации. Например, несколько разновидностей двоичного кода (прямой, обратный,

дополнительный, двоично-десятичный и т. д.). При передаче информации по линиям связи

удобнее использовать другие виды кодов, позволяющие уменьшать вероятность появления

ошибки или даже исправлять ее в дальнейшем: коды, построенные по принципу 2 из 5 (в

которых из пяти символов два всегда имеют единичное значение), коды с проверкой

чётности иле нечётности, коды Хемминга.

Преобразователем кода наз. комбинационное устройство, предназначенное для

изменения вида кодирования информации.

Как

и

всякое

комбинационное

устройство,

преобразователь

кода

характеризуется

таблицей

истинности,

ставящей

в

соответствие

кодам,

подаваемым на вход, коды, снимаемые с

выхода устройства. Следует заметить, что в

этой таблице в общем случае число

разрядов входного и выходного кодов

может не совпадать. Главное— она должна

давать однозначное соответствие различных

кодов. Данная таблица является основанием

для

синтеза

логической

структуры

конкретного

преобразователя

кодов.

Условное

графическое

изображение

преобразователей

кодов

на

принципиальных электрических схемах

приведено на рис. 16.8. В качестве примера

преобразователя кодов, выпускаемых в виде

ИС,

можно

привести

схемы,

обеспечивающие

преобразование

информации из двоичного в двоичнодесятичный

код.

Частным

случаем преобразователей

кода являются шифраторы

и дешифраторы.

8.

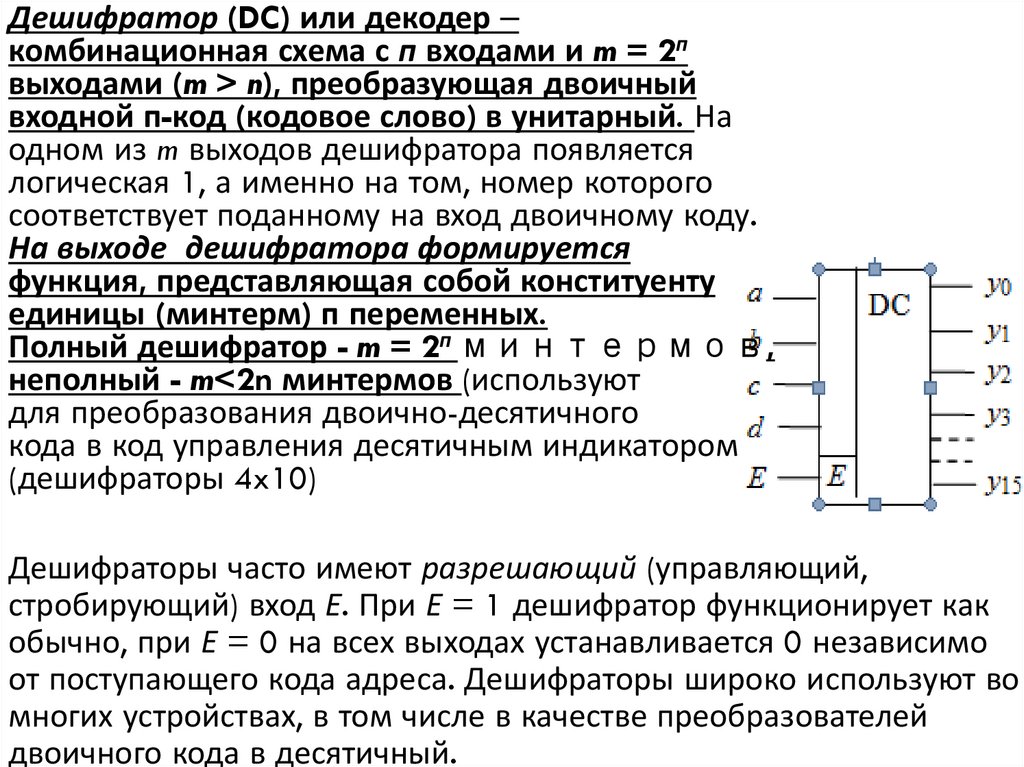

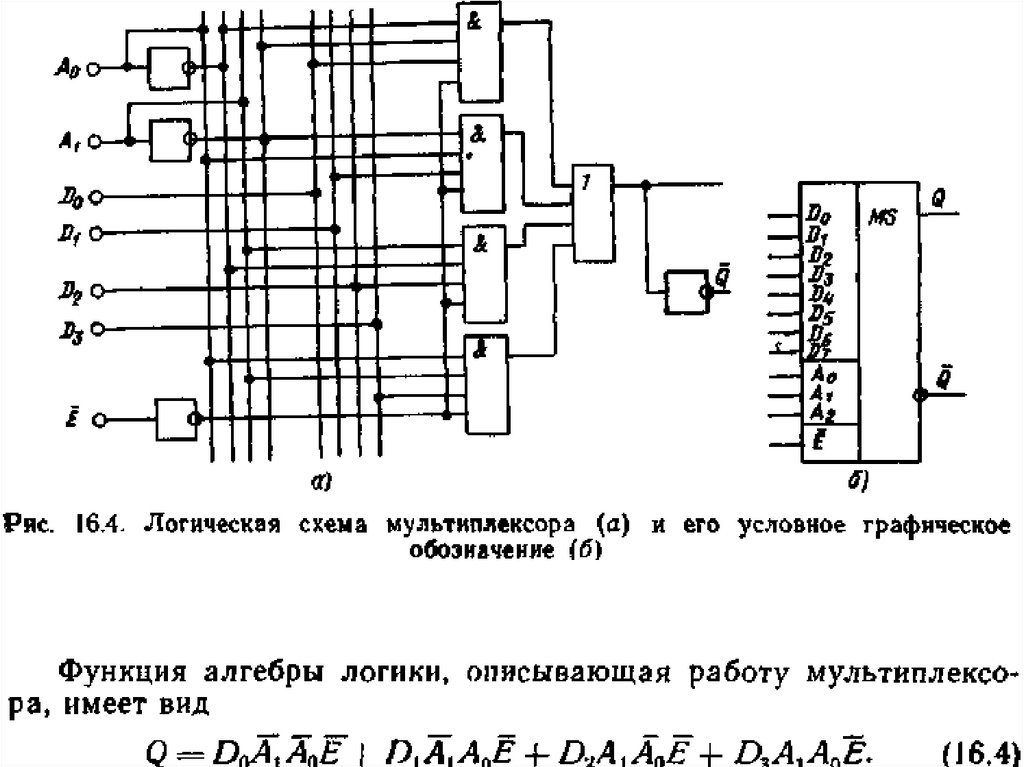

Дешифратор (DC) или декодеркомбинационная схема с п входами и m = 2п

выходами (m > n), преобразующая двоичный

входной п-код (кодовое слово) в унитарный. На

одном из m выходов дешифратора появляется

логическая 1, а именно на том, номер которого

соответствует поданному на вход двоичному коду.

На выходе дешифратора формируется

функция, представляющая собой конституенту

единицы (минтерм) п переменных.

Полный дешифратор - m = 2п минтермов,

неполный - m<2n минтермов (используют

для преобразования двоично-десятичного

кода в код управления десятичным индикатором

(дешифраторы 4x10)

Дешифраторы часто имеют разрешающий (управляющий,

стробирующий) вход Е. При Е = 1 дешифратор функционирует как

обычно, при Е = 0 на всех выходах устанавливается 0 независимо

от поступающего кода адреса. Дешифраторы широко используют во

многих устройствах, в том числе в качестве преобразователей

двоичного кода в десятичный.

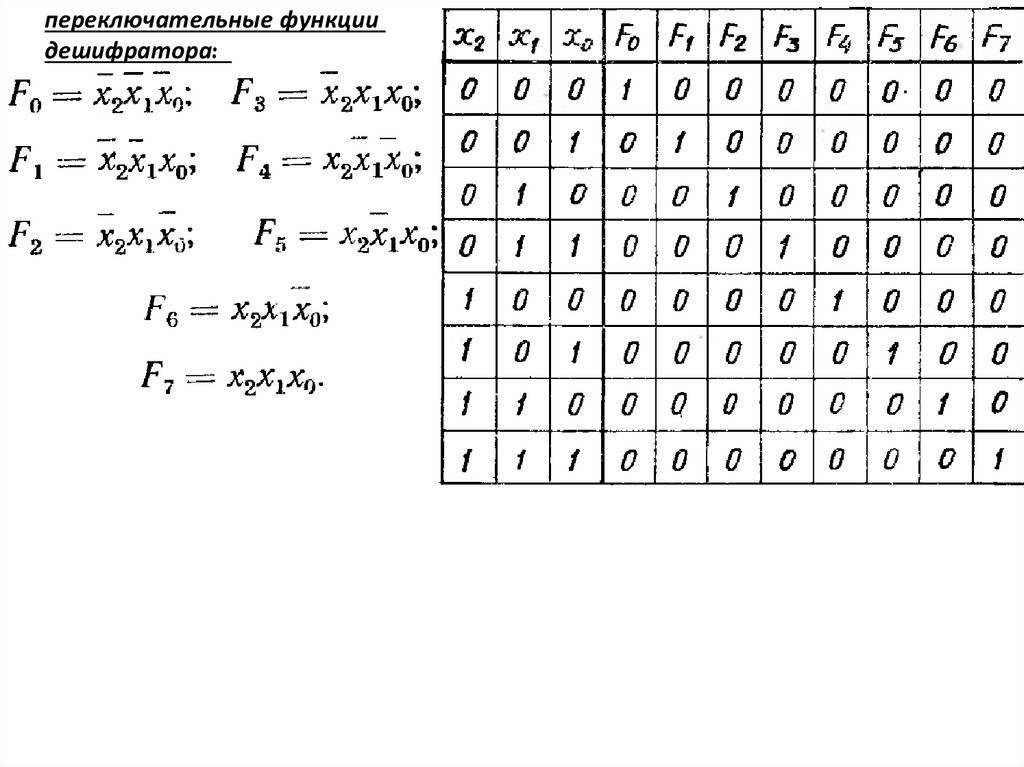

9.

переключательные функциидешифратора:

10.

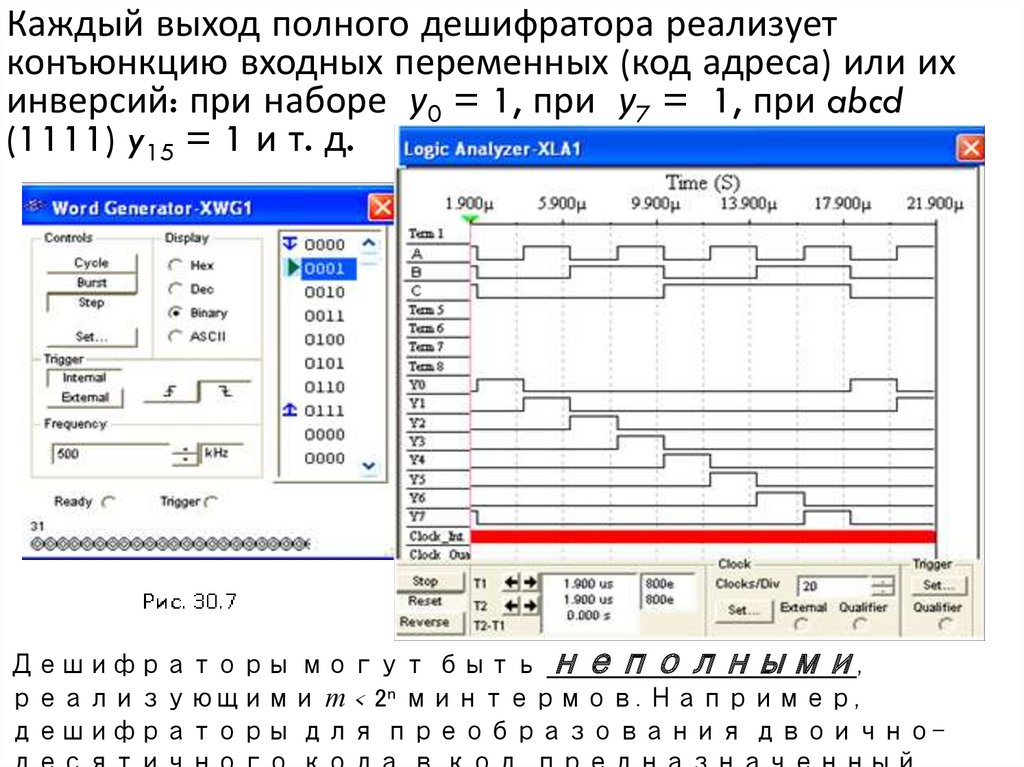

Каждый выход полного дешифратора реализуетконъюнкцию входных переменных (код адреса) или их

инверсий: при наборе у0 = 1, при у7 = 1, при abcd

(1111) y15 = 1 и т. д.

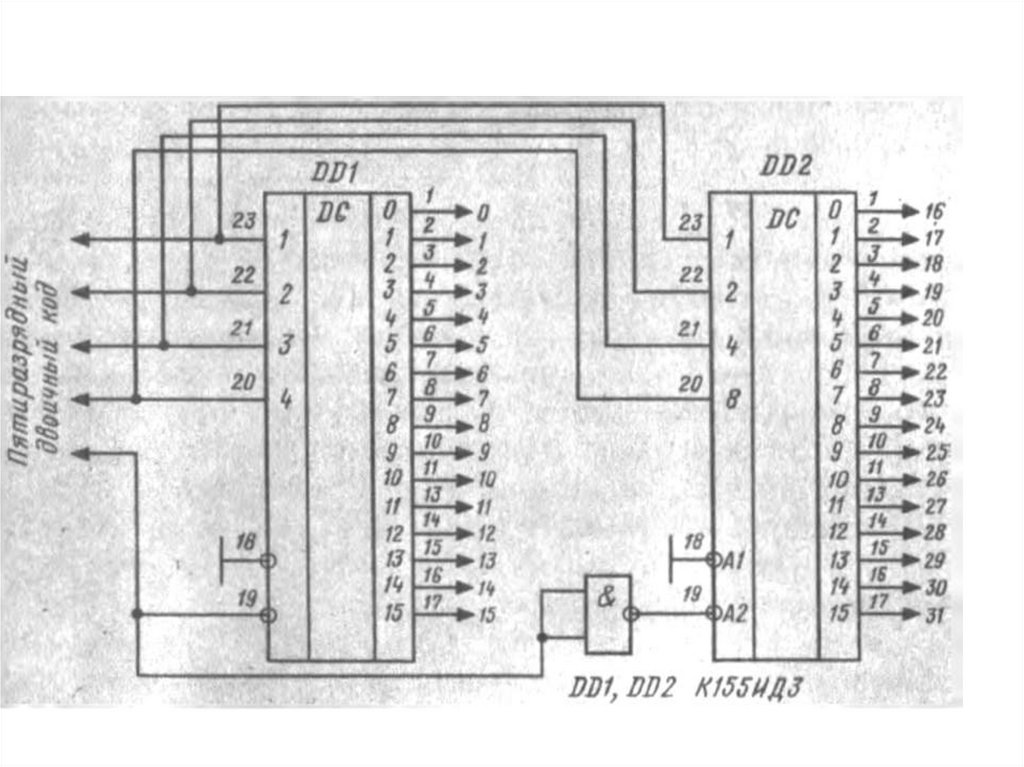

Дешифраторы могут быть неполными,

реализующими т < 2n минтермов. Например,

дешифраторы для преобразования двоично-

11.

12.

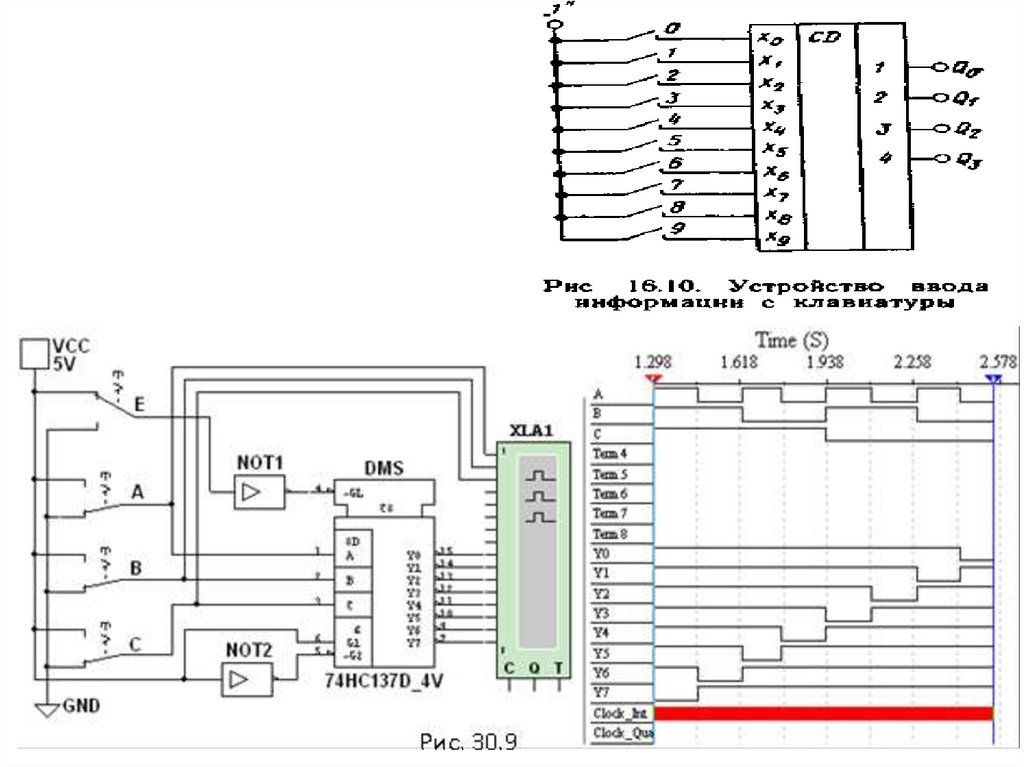

Шифратор (CD) или кодер выполняет функцию, обратнуюфункции дешифратора. Классический шифратор имеет n входов и

m выходов (m < n), и при подаче сигнала 1 на один из входов (и не

более) на выходе кодера появляется двоичный код номера

возбужденного выхода. Число входов и выходов такого шифратора

связано соотношением n = 2m

Области использования шифраторов

отображение в виде двоичного кода номера

нажатой кнопки или положения

многопозиционного переключателя, а также

номера устройства, подавшего сигнал на

обслуживание в микропроцессорных системах

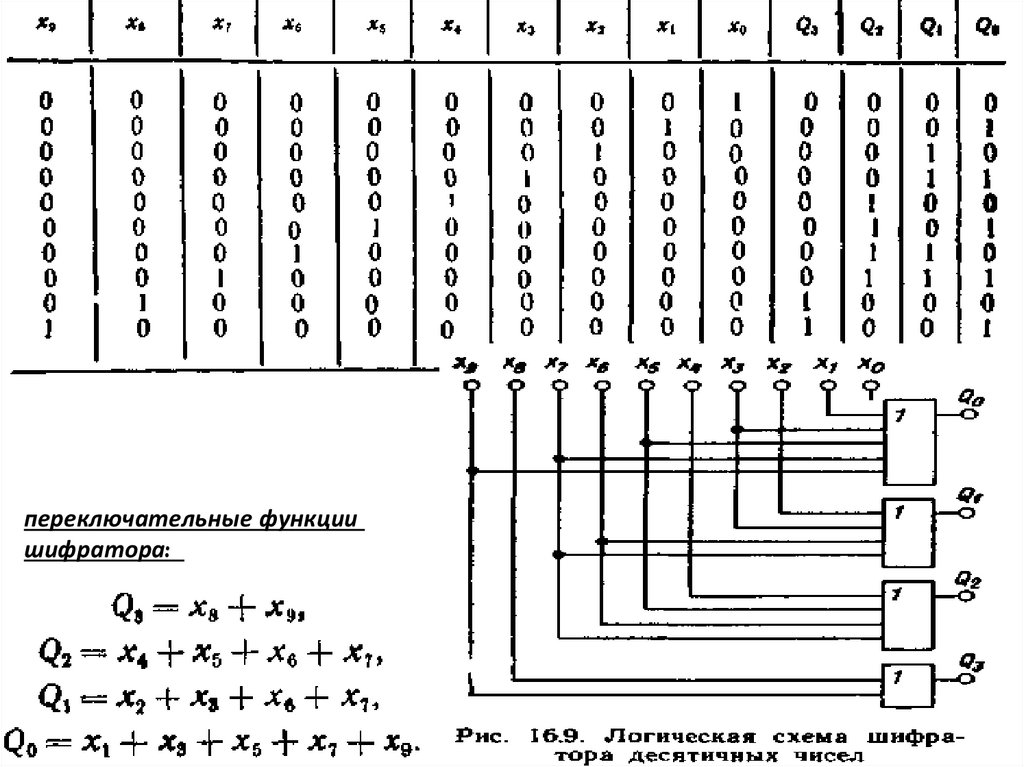

13.

переключательные функциишифратора:

14.

15.

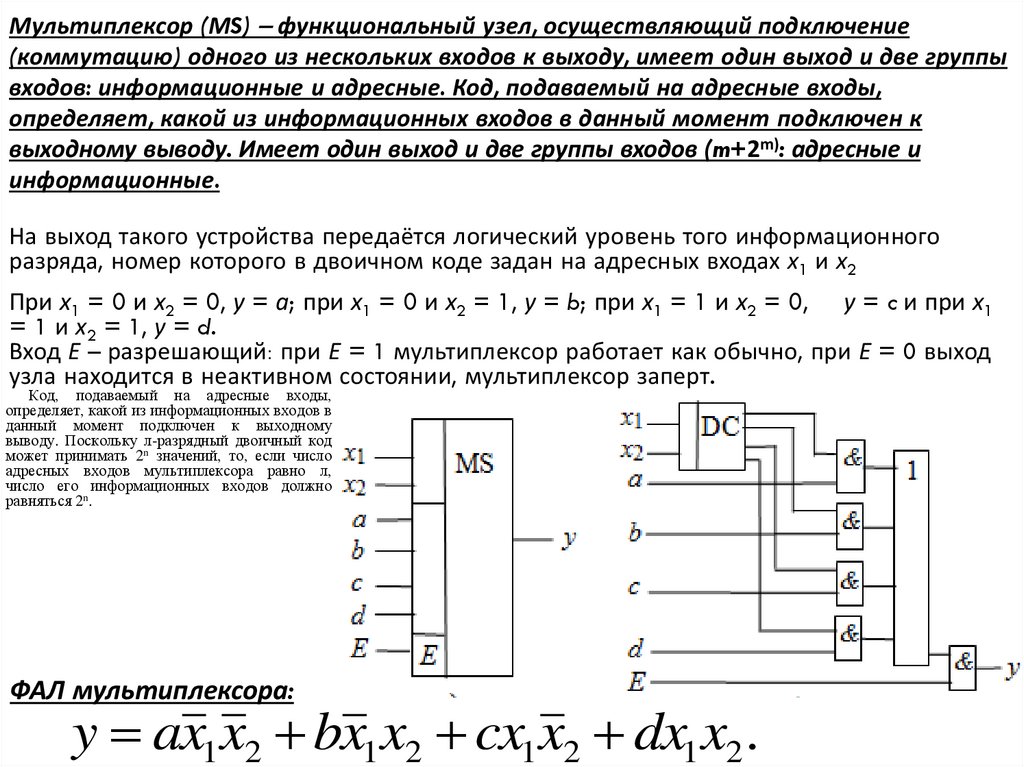

Мультиплексор (МS) функциональный узел, осуществляющий подключение(коммутацию) одного из нескольких входов к выходу, имеет один выход и две группы

входов: информационные и адресные. Код, подаваемый на адресные входы,

определяет, какой из информационных входов в данный момент подключен к

выходному выводу. Имеет один выход и две группы входов (m+2m): адресные и

информационные.

На выход такого устройства передаётся логический уровень того информационного

разряда, номер которого в двоичном коде задан на адресных входах х1 и х2

При х1 = 0 и х2 = 0, у = а; при х1 = 0 и х2 = 1, у = b; при х1 = 1 и х2 = 0, у = c и при х1

= 1 и х2 = 1, у = d.

Вход Е – разрешающий: при Е = 1 мультиплексор работает как обычно, при Е = 0 выход

узла находится в неактивном состоянии, мультиплексор заперт.

Код, подаваемый на адресные входы,

определяет, какой из информационных входов в

данный момент подключен к выходному

выводу. Поскольку л-разрядный двоичный код

может принимать 2n значений, то, если число

адресных входов мультиплексора равно л,

число его информационных входов должно

равняться 2n.

ФАЛ мультиплексора:

y ax1 x2 bx1 x2 cx1 x2 dx1 x2 .

16.

ФАЛ мультиплексора:y ax1 x2 bx1 x2 cx1 x2 dx1 x2 .

Типовое применение мультиплексора — это передача информации от нескольких разнесенных в

пространстве источников (датчиков) информации на вход одного приемника. Предположим, что

измеряется температура окружающей среды в нескольких помещениях и результаты этих измерений

должны быть введены в одно регистрирующее устройство, например ЭВМ.

17.

18.

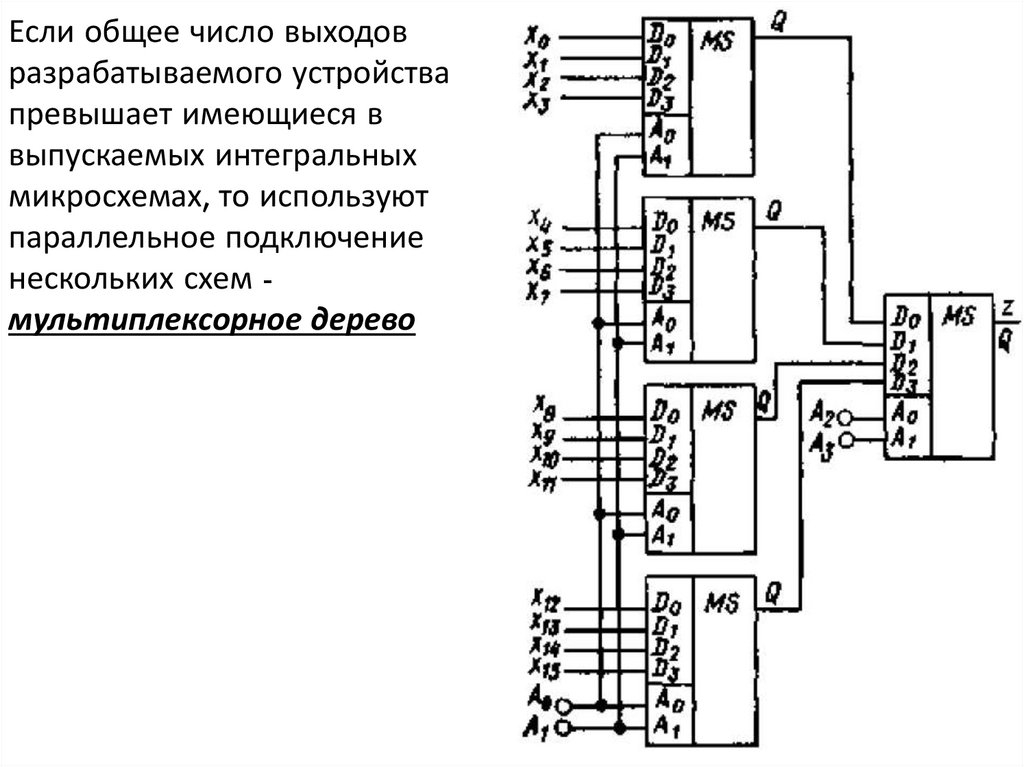

Если общее число выходовразрабатываемого устройства

превышает имеющиеся в

выпускаемых интегральных

микросхемах, то используют

параллельное подключение

нескольких схем мультиплексорное дерево

19.

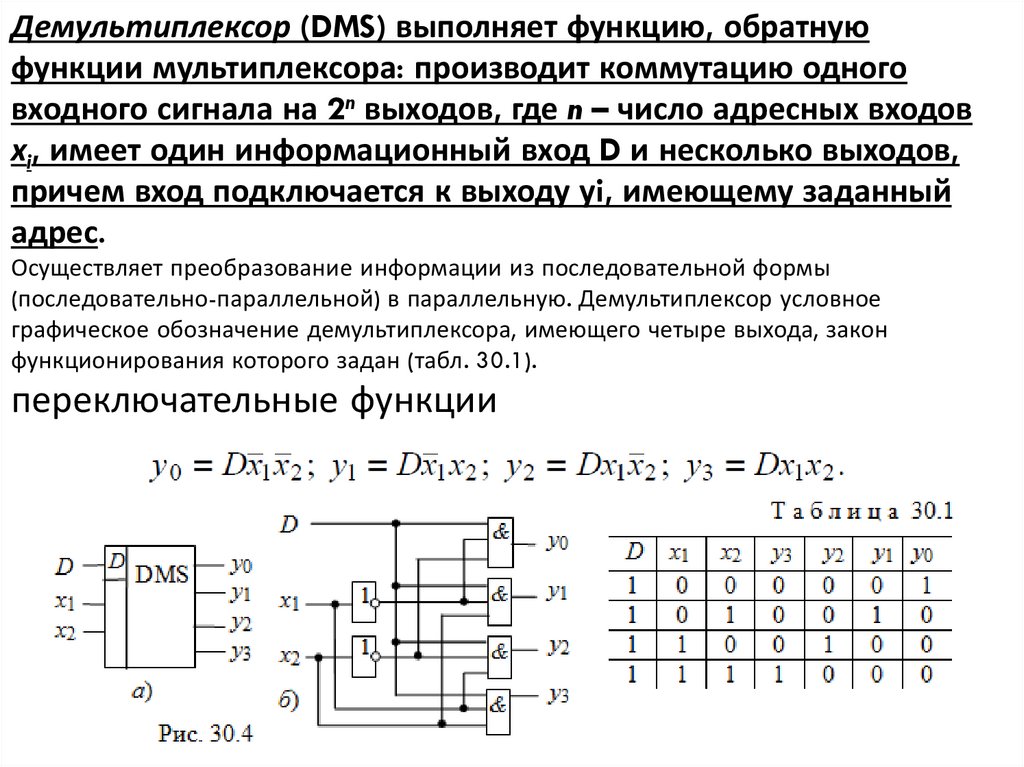

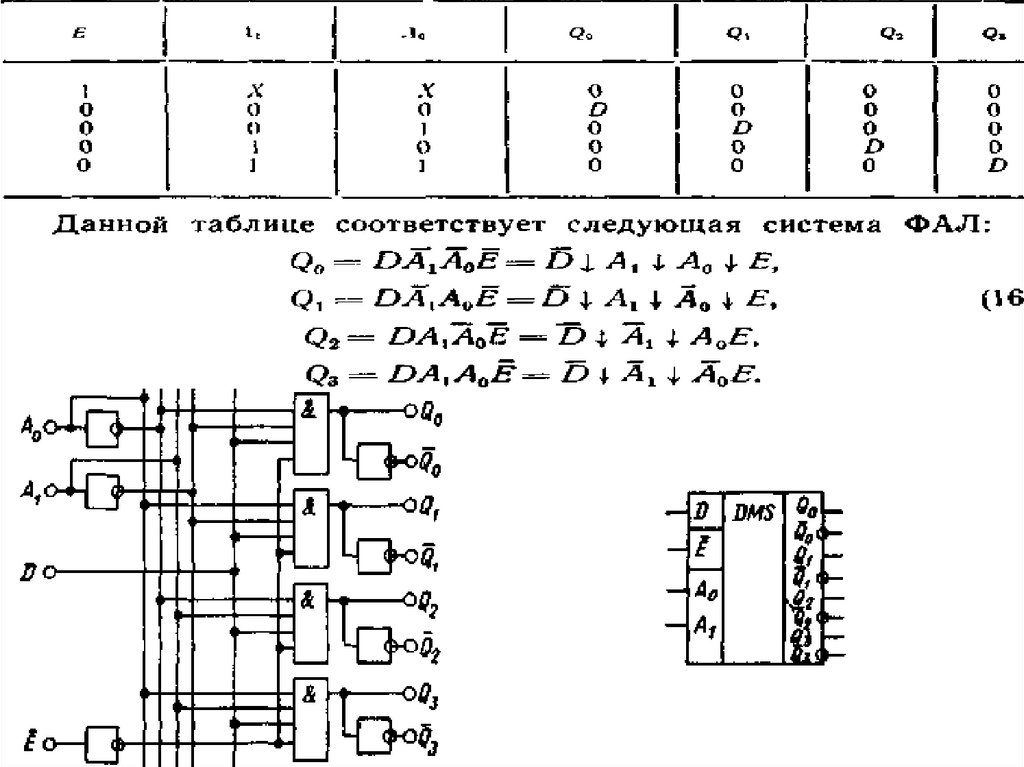

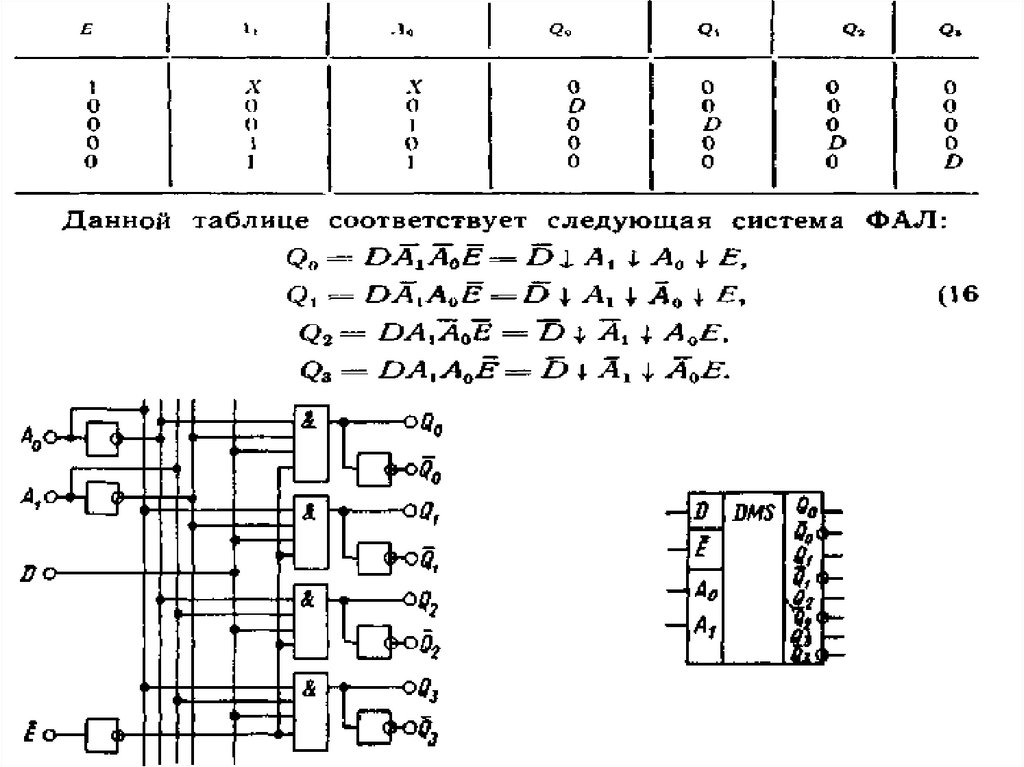

Демультиплексор (DMS) выполняет функцию, обратнуюфункции мультиплексора: производит коммутацию одного

входного сигнала на 2n выходов, где n – число адресных входов

хi, имеет один информационный вход D и несколько выходов,

причем вход подключается к выходу уi, имеющему заданный

адрес.

Осуществляет преобразование информации из последовательной формы

(последовательно-параллельной) в параллельную. Демультиплексор условное

графическое обозначение демультиплексора, имеющего четыре выхода, закон

функционирования которого задан (табл. 30.1).

переключательные функции

20.

21.

22.

23.

демультиплексорное дерево, построенное намультиплексорах с четырьмя выходами. Объединяя

мультиплексор с демультиплексором, получают

комбинационное устройство, в котором по

заданным адресам один из входов подключается к

одному из его выходов

24.

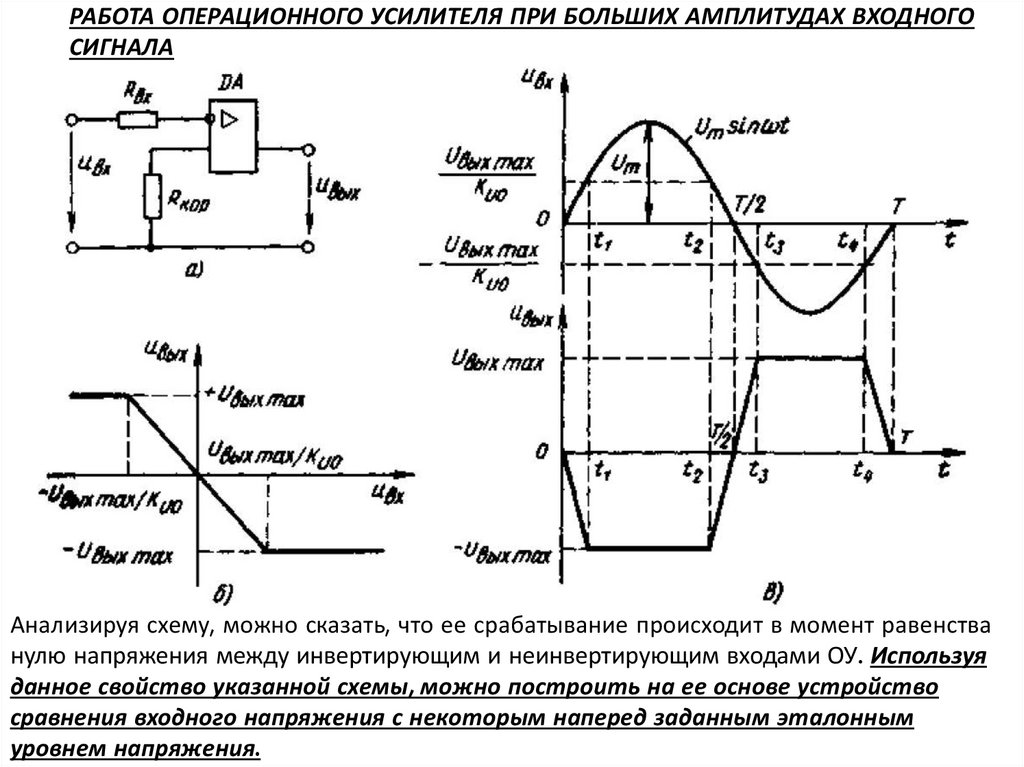

РАБОТА ОПЕРАЦИОННОГО УСИЛИТЕЛЯ ПРИ БОЛЬШИХ АМПЛИТУДАХ ВХОДНОГОСИГНАЛА

Анализируя схему, можно сказать, что ее срабатывание происходит в момент равенства

нулю напряжения между инвертирующим и неинвертирующим входами ОУ. Используя

данное свойство указанной схемы, можно построить на ее основе устройство

сравнения входного напряжения с некоторым наперед заданным эталонным

уровнем напряжения.

25.

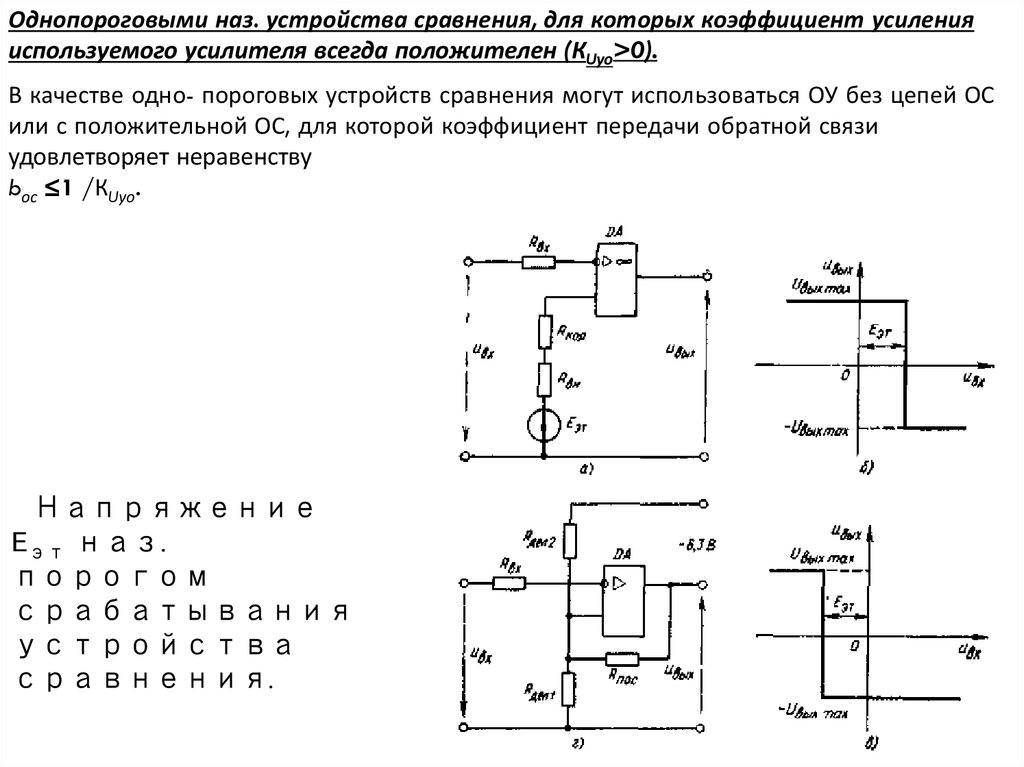

Однопороговыми наз. устройства сравнения, для которых коэффициент усиленияиспользуемого усилителя всегда положителен (КUуо>0).

В качестве одно- пороговых устройств сравнения могут использоваться ОУ без цепей ОС

или с положительной ОС, для которой коэффициент передачи обратной связи

удовлетворяет неравенству

bос ≤1 /КUуо.

Напряжение

Eэт наз.

порогом

срабатывания

устройства

сравнения.

26.

Если в схеме вместо источника эталонного напряжения использовать второе входноенапряжение, ОУ превратится в схему сравнения двух напряжений. Пренебрегая

погрешностью, обусловленной наличием диапазона неидентифицированного входного

напряжения, можно сказать, что переключение усилителя будет происходить в момент

равенства входных напряжений как по абсолютному значению, так и о знаку.

27.

28.

Регенеративными (гистерезисными) наз. схемы сравнения с неоднозначнойпередаточной характеристикой. Применительно к ОУ это возможно только в том случае,

когда усилитель охвачен цепью ПОС с коэффициентом передачи, удовлетворяющим

условию Кос>1/КUуо

При этом передаточная характеристика перестает

быть однозначной и появляется область входных

напряжений, для которой без знания предыстории

работы схемы нельзя однозначно определить значение выходного сигнала ОУ.

Использование в схеме сравнения ОУ, у которого

передаточная характеристика имеет область

неоднозначного соответствия входного и выходного

напряжений (имеет гистерезис), позволяет построить

устройства, у которых напряжения срабатывания и отпускания не равны между собой.

29.

Пусть в некоторый момент времени входное напряжение схемы равно нулю, а на еевыходе присутствует напряжение положительной полярности

Тогда к

неинвертирующему входу ОУ приложено положительное напряжение

Рассматриваемое состояние является устойчивым и может поддерживаться сколь угодно

долго до тех пор, пока изменяющееся входное напряжение не достигнет этого же

уровня. В этот момент произойдёт изменение выходного напряжения ОУ от

.

напряжения срабатывания:

30.

31.

32.

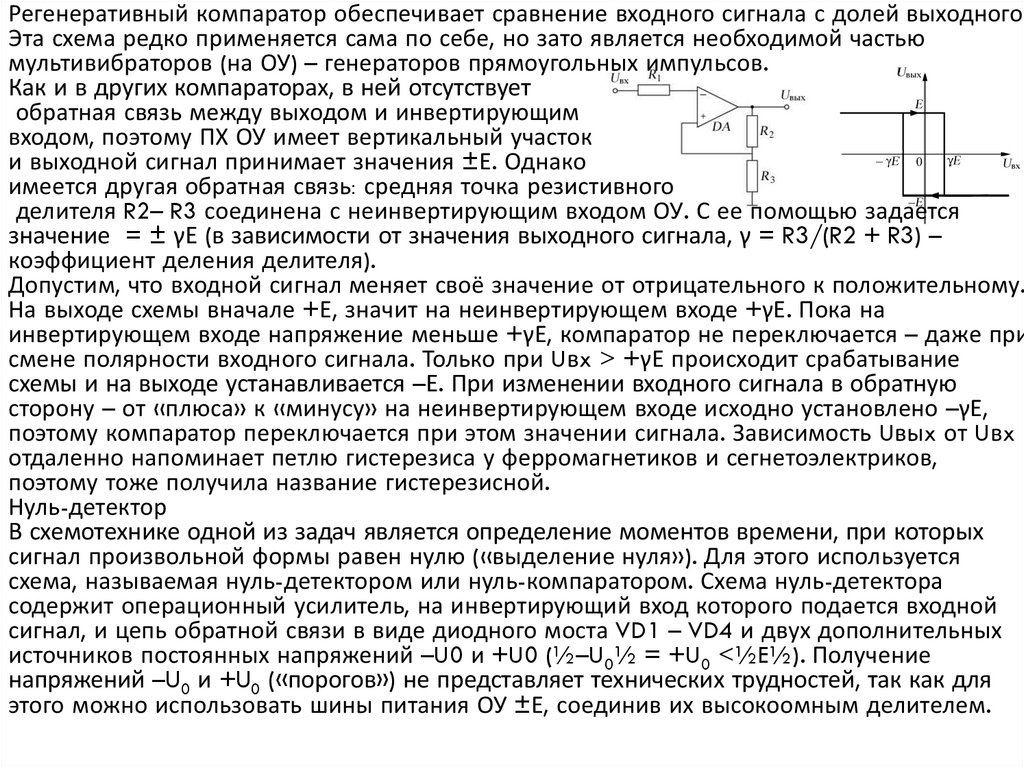

Регенеративный компаратор обеспечивает сравнение входного сигнала с долей выходного.Эта схема редко применяется сама по себе, но зато является необходимой частью

мультивибраторов (на ОУ) – генераторов прямоугольных импульсов.

Как и в других компараторах, в ней отсутствует

обратная связь между выходом и инвертирующим

входом, поэтому ПХ ОУ имеет вертикальный участок

и выходной сигнал принимает значения ±Е. Однако

имеется другая обратная связь: средняя точка резистивного

делителя R2– R3 соединена с неинвертирующим входом ОУ. С ее помощью задается

значение = ± γЕ (в зависимости от значения выходного сигнала, γ = R3/(R2 + R3) –

коэффициент деления делителя).

Допустим, что входной сигнал меняет своё значение от отрицательного к положительному.

На выходе схемы вначале +Е, значит на неинвертирующем входе +γЕ. Пока на

инвертирующем входе напряжение меньше +γЕ, компаратор не переключается – даже при

смене полярности входного сигнала. Только при Uвx > +γЕ происходит срабатывание

схемы и на выходе устанавливается –Е. При изменении входного сигнала в обратную

сторону – от «плюса» к «минусу» на неинвертирующем входе исходно установлено –γЕ,

поэтому компаратор переключается при этом значении сигнала. Зависимость Uвыx от Uвx

отдаленно напоминает петлю гистерезиса у ферромагнетиков и сегнетоэлектриков,

поэтому тоже получила название гистерезисной.

Нуль-детектор

В схемотехнике одной из задач является определение моментов времени, при которых

сигнал произвольной формы равен нулю («выделение нуля»). Для этого используется

схема, называемая нуль-детектором или нуль-компаратором. Схема нуль-детектора

содержит операционный усилитель, на инвертирующий вход которого подается входной

сигнал, и цепь обратной связи в виде диодного моста VD1 – VD4 и двух дополнительных

источников постоянных напряжений –U0 и +U0 (½–U0½ = +U0 <½E½). Получение

напряжений –U0 и +U0 («порогов») не представляет технических трудностей, так как для

этого можно использовать шины питания ОУ ±Е, соединив их высокоомным делителем.

33.

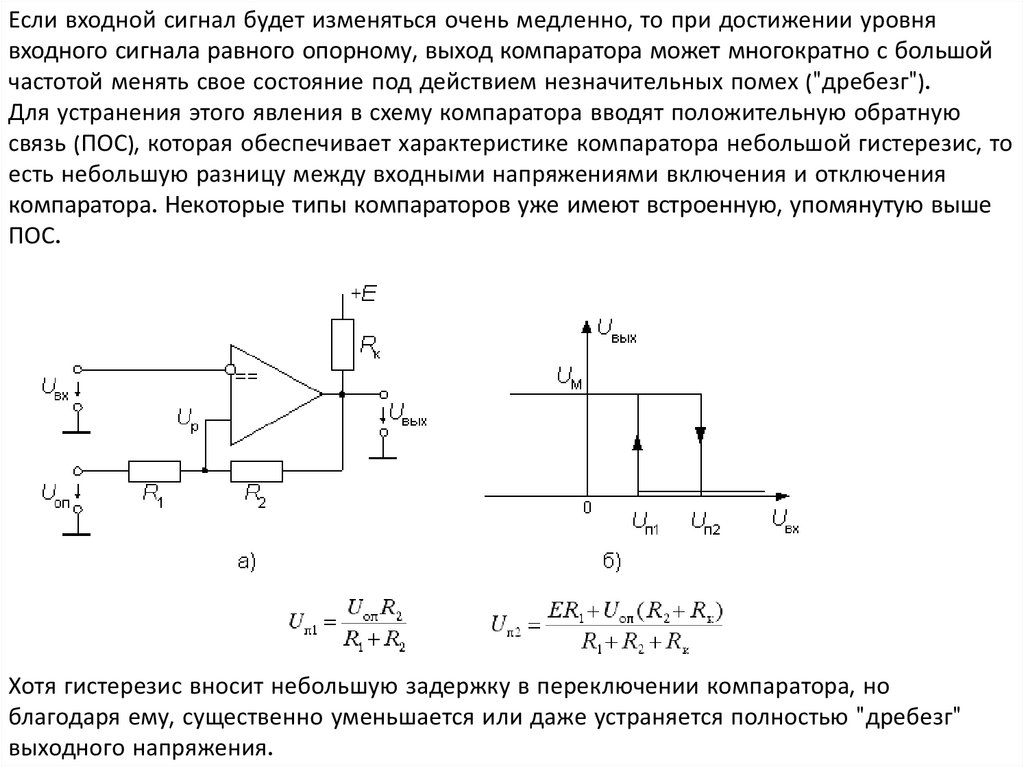

Если входной сигнал будет изменяться очень медленно, то при достижении уровнявходного сигнала равного опорному, выход компаратора может многократно с большой

частотой менять свое состояние под действием незначительных помех ("дребезг").

Для устранения этого явления в схему компаратора вводят положительную обратную

связь (ПОС), которая обеспечивает характеристике компаратора небольшой гистерезис, то

есть небольшую разницу между входными напряжениями включения и отключения

компаратора. Некоторые типы компараторов уже имеют встроенную, упомянутую выше

ПОС.

Хотя гистерезис вносит небольшую задержку в переключении компаратора, но

благодаря ему, существенно уменьшается или даже устраняется полностью "дребезг"

выходного напряжения.

34.

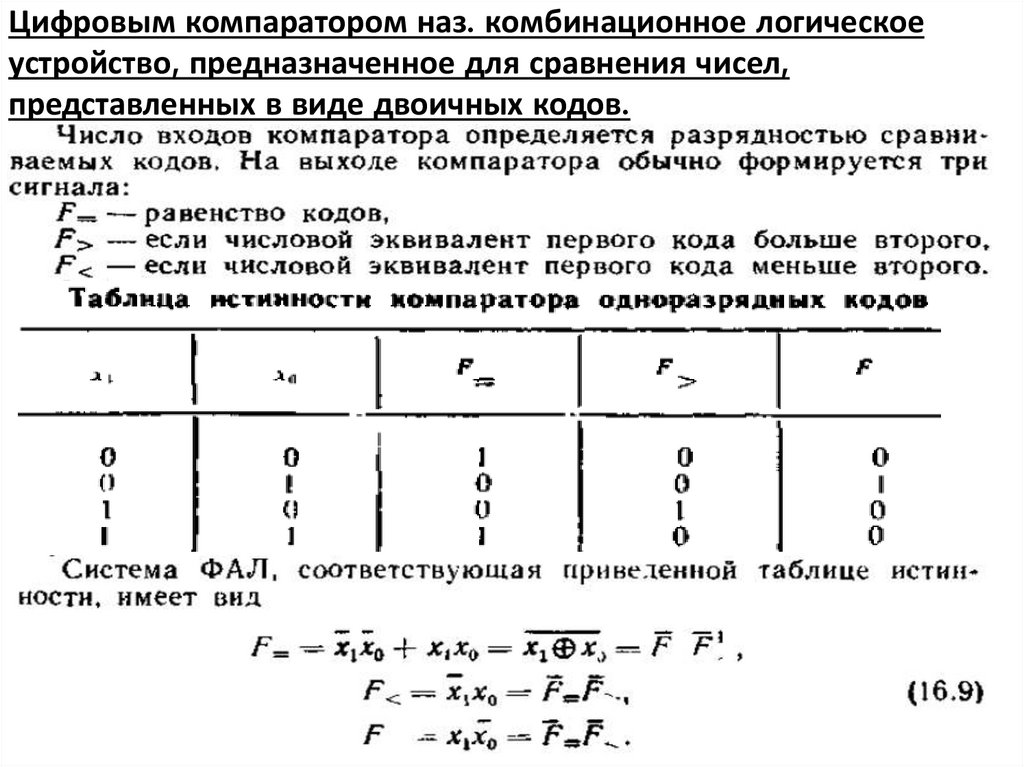

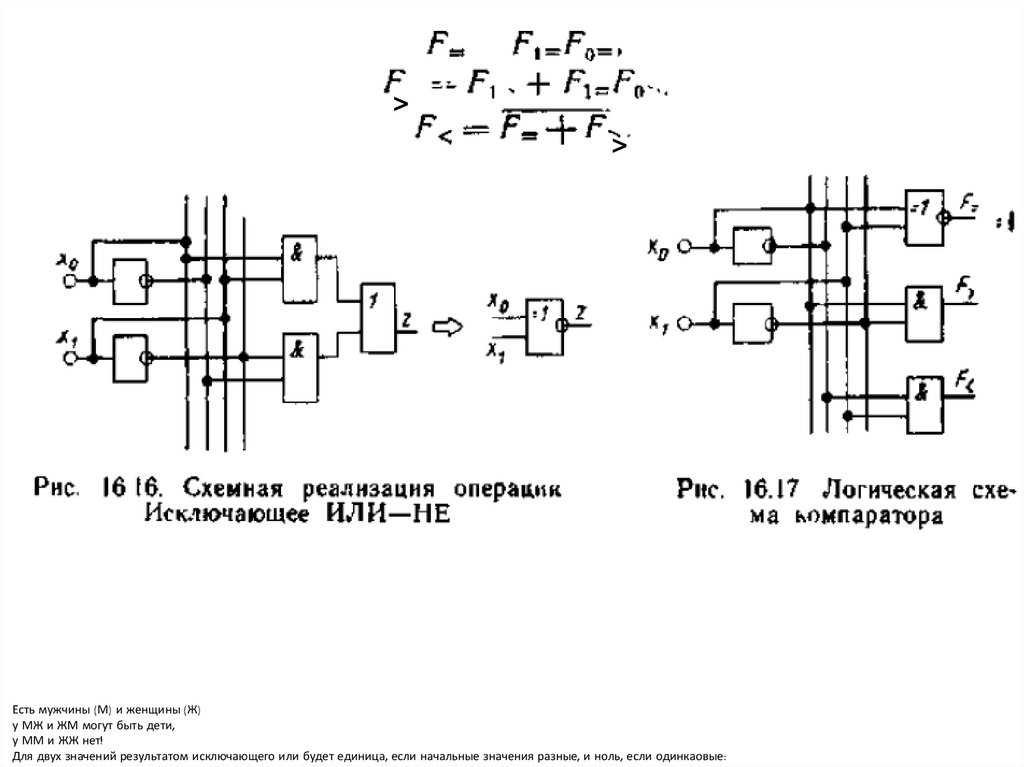

Цифровым компаратором наз. комбинационное логическоеустройство, предназначенное для сравнения чисел,

представленных в виде двоичных кодов.

35.

>>

Есть мужчины (М) и женщины (Ж)

у МЖ и ЖМ могут быть дети,

у ММ и ЖЖ нет!

Для двух значений результатом исключающего или будет единица, если начальные значения разные, и ноль, если одинкаовые:

36.

Компараторы(устройства сравнения)

определяют отношения между двумя

словами. Основными отношениями,

через которые можно выразить

остальные, можно считать два —

"равно" и "больше".

37.

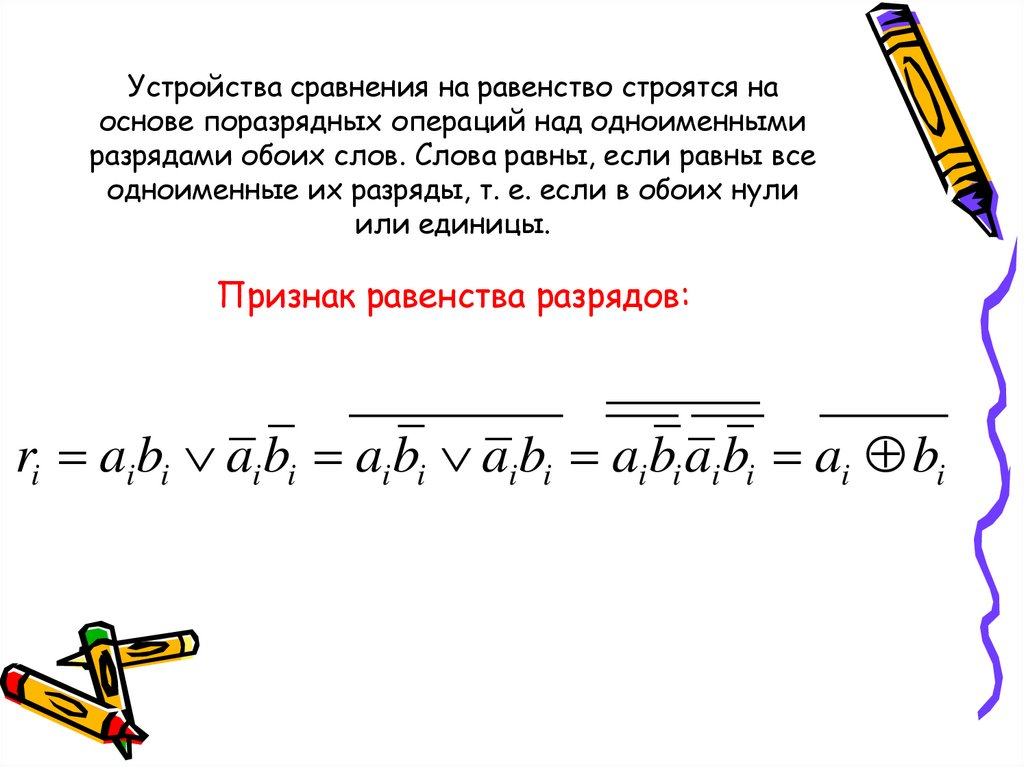

Условное обозначение компаратора с тремя выходами38. Устройства сравнения на равенство строятся на основе поразрядных операций над одноименными разрядами обоих слов. Слова равны,

если равны всеодноименные их разряды, т. е. если в обоих нули

или единицы.

Признак равенства разрядов:

ri ai bi ai bi ai bi ai bi ai bi ai bi ai bi

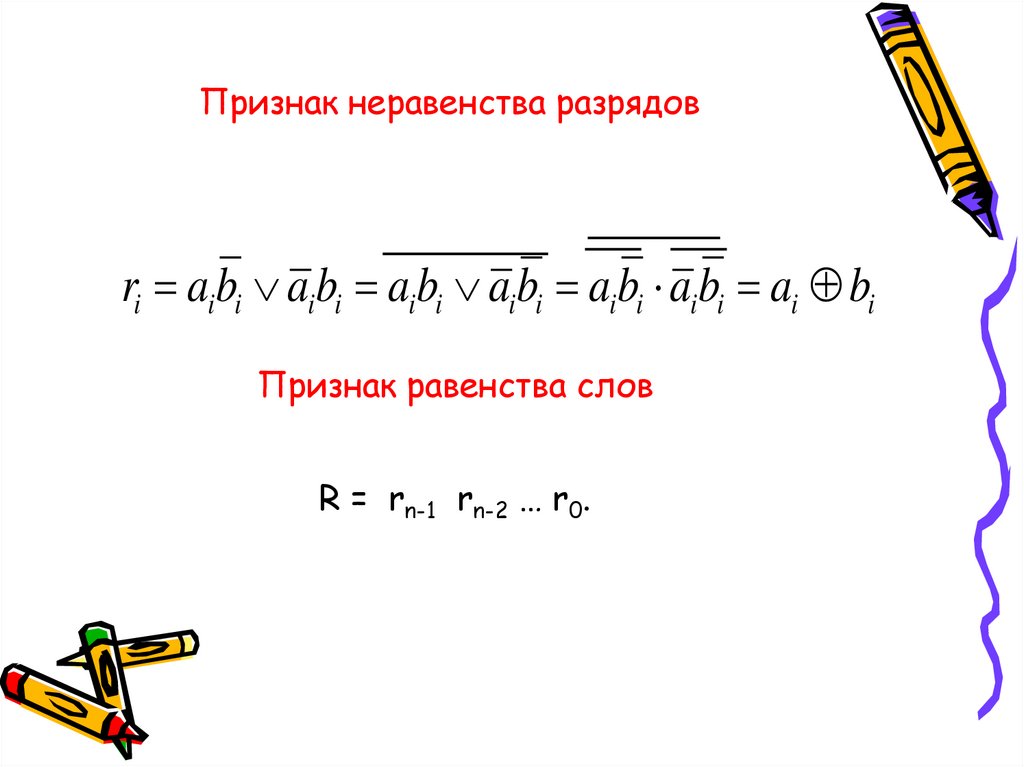

39.

Признак неравенства разрядовri aibi aibi aibi aibi aibi aibi ai bi

Признак равенства слов

R = rn-1 rn-2 … r0.

40.

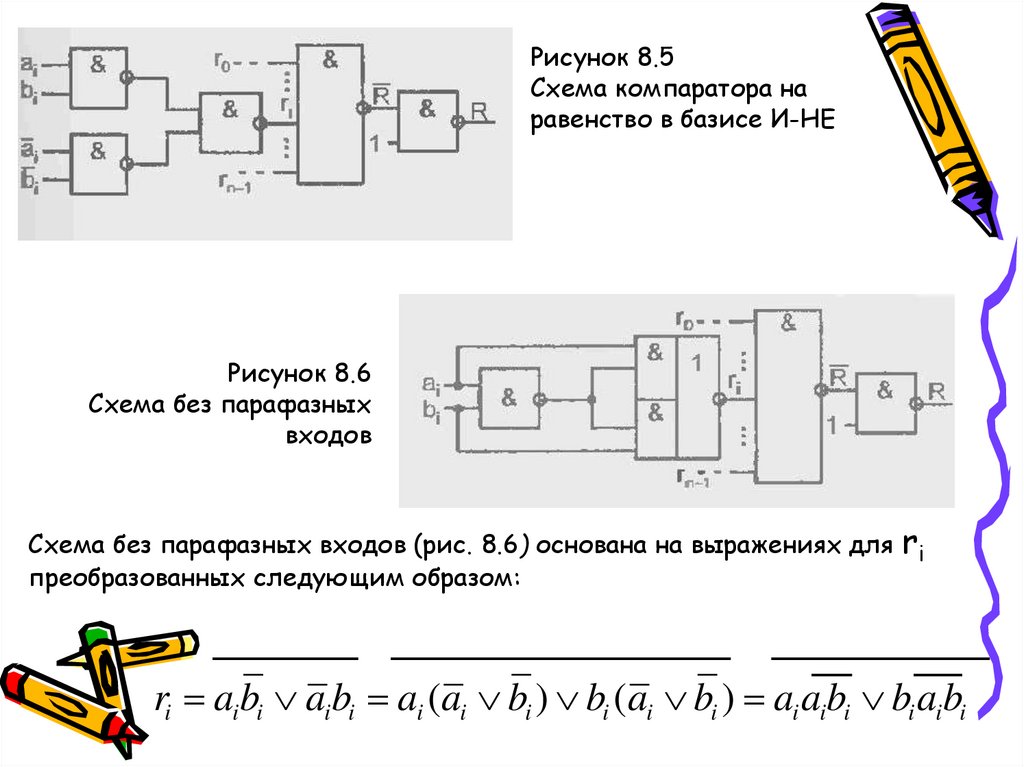

Рисунок 8.5Схема компаратора на

равенство в базисе И-НЕ

Рисунок 8.6

Схема без парафазных

входов

Схема без парафазных входов (рис. 8.6) основана на выражениях для ri

преобразованных следующим образом:

ri aibi aibi ai (ai bi ) bi (ai bi ) ai aibi bi aibi

41.

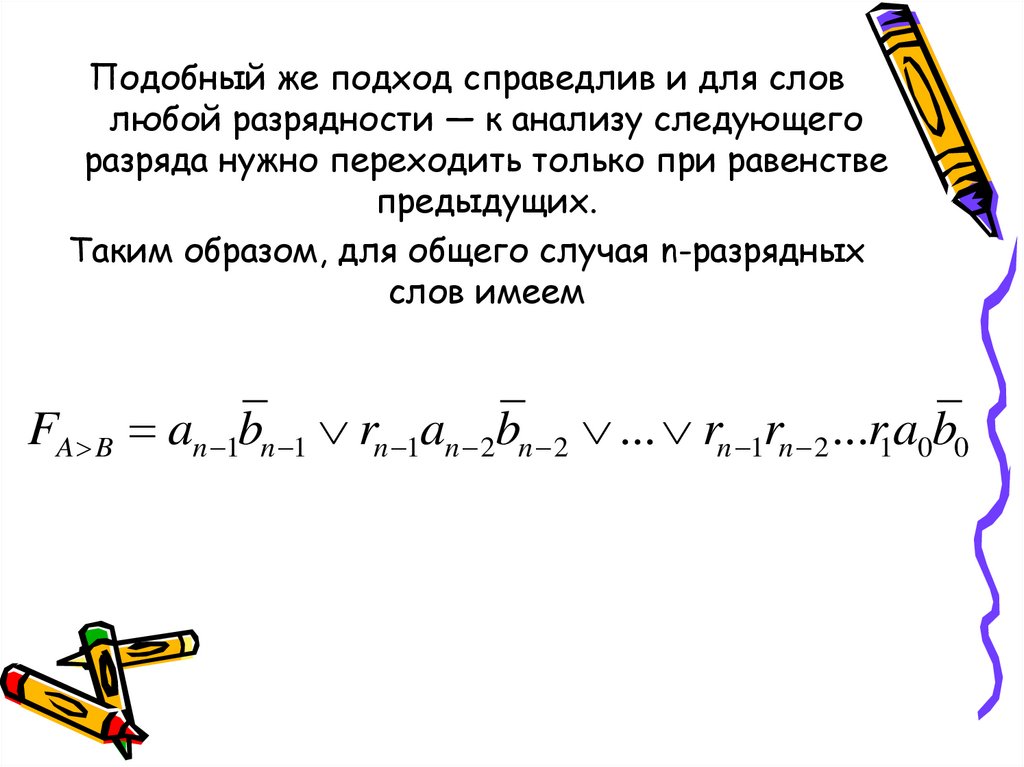

Подобный же подход справедлив и для словлюбой разрядности — к анализу следующего

разряда нужно переходить только при равенстве

предыдущих.

Таким образом, для общего случая n-разрядных

слов имеем

FA B an 1bn 1 rn 1an 2bn 2 ... rn 1rn 2 ...r1a0b0

42. Сумматоры и полусумматоры

43. Сумматоры

Сумматор – устройство, осуществляющееоперацию сложения

двоичных кодов по правилам:

0+0 = 0,

0+1 = 1,

1+0 = 1 ,

1+1 = 0 и 1- перенос

44.

Для сложения младших разрядов кодаприменяется полусумматор.

Рисунок 9.7

45.

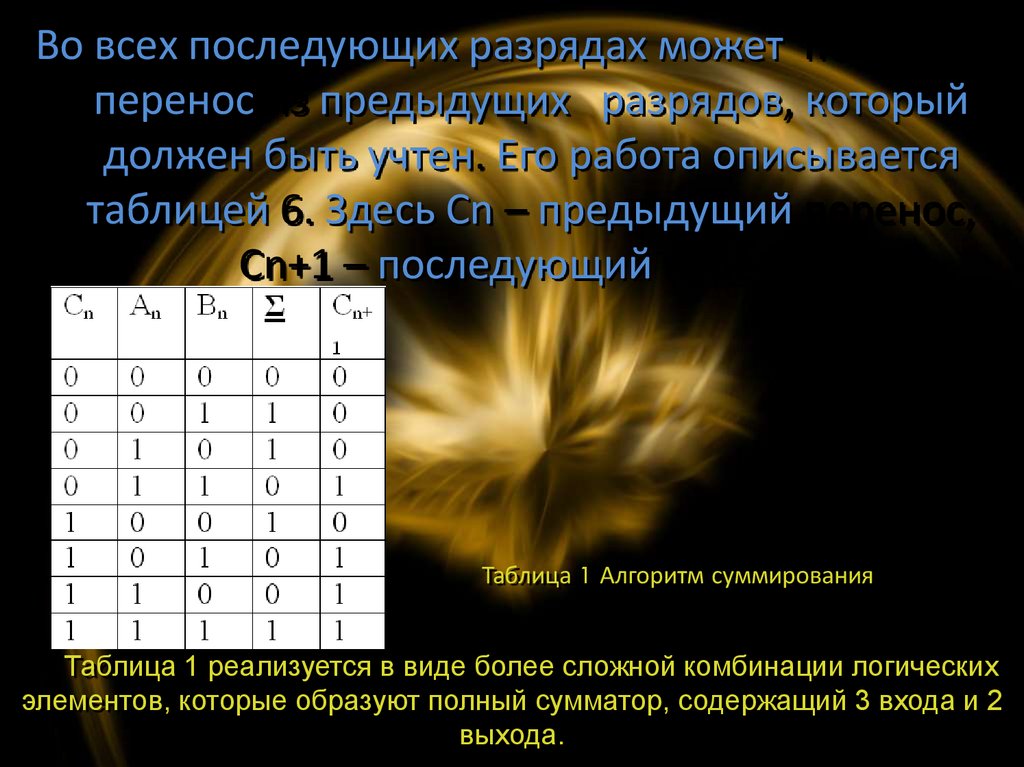

Во всех последующих разрядах может появитьсяперенос из предыдущих разрядов, который

должен быть учтен. Его работа описывается

таблицей 6. Здесь Cn – предыдущий перенос,

Cn+1 – последующий перенос

Таблица 1 Алгоритм суммирования

Таблица 1 реализуется в виде более сложной комбинации логических

элементов, которые образуют полный сумматор, содержащий 3 входа и 2

выхода.

46.

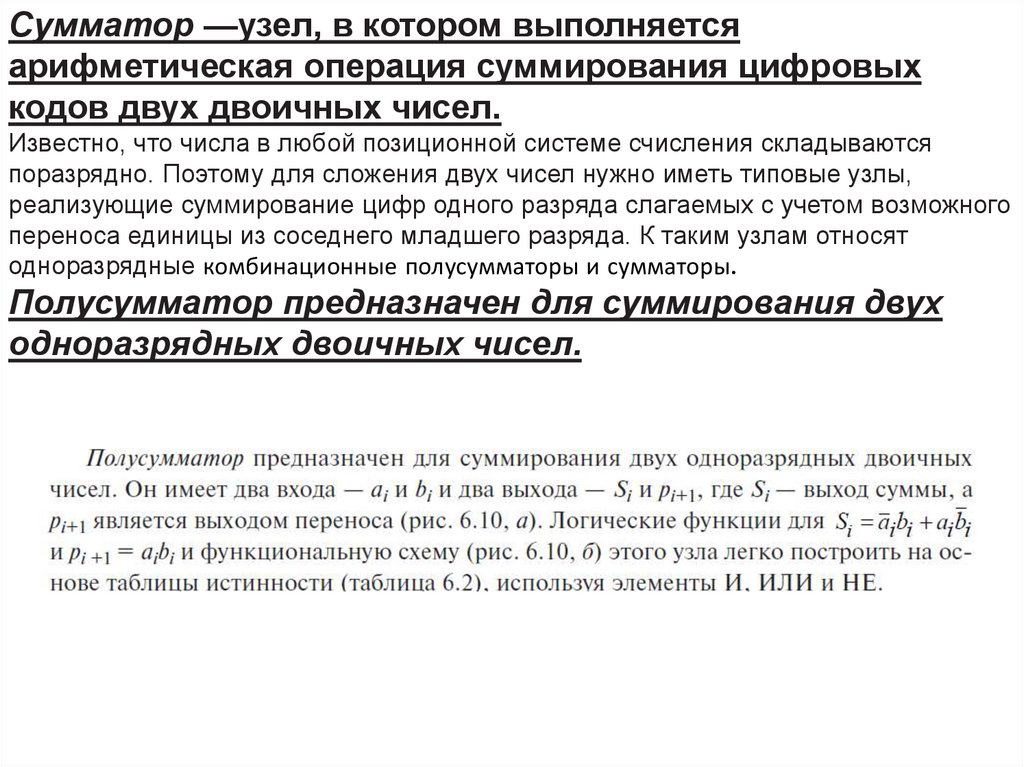

Сумматор —узел, в котором выполняетсяарифметическая операция суммирования цифровых

кодов двух двоичных чисел.

Известно, что числа в любой позиционной системе счисления складываются

поразрядно. Поэтому для сложения двух чисел нужно иметь типовые узлы,

реализующие суммирование цифр одного разряда слагаемых с учетом возможного

переноса единицы из соседнего младшего разряда. К таким узлам относят

одноразрядные комбинационные полусумматоры и сумматоры.

Полусумматор предназначен для суммирования двух

одноразрядных двоичных чисел.

47.

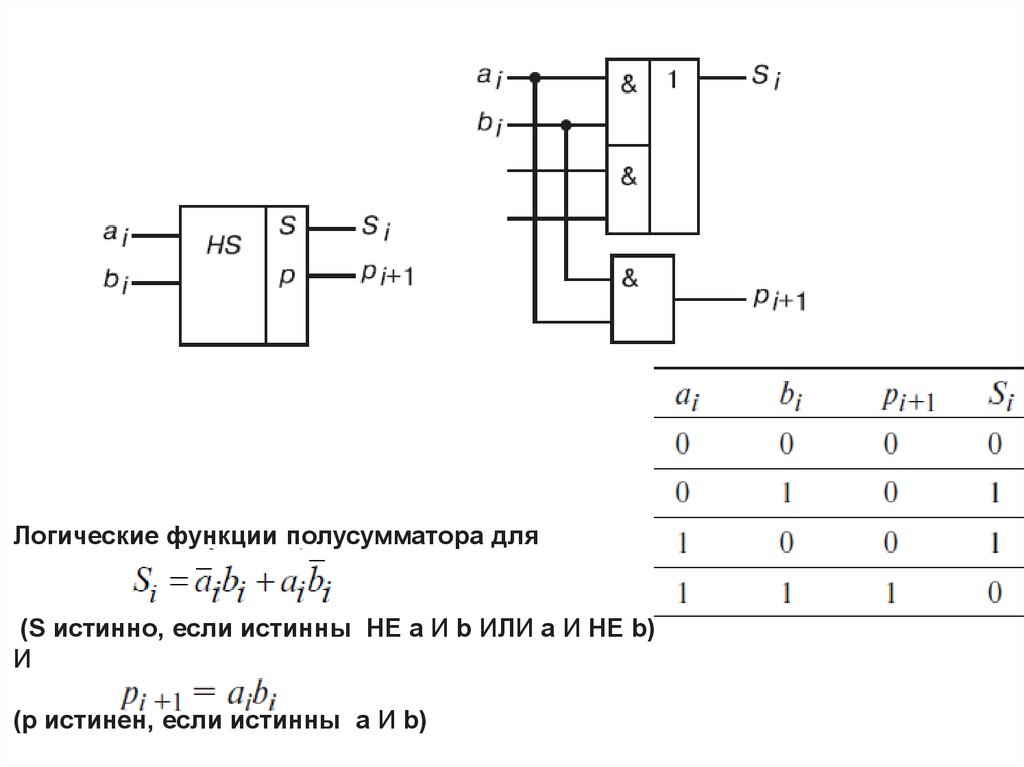

Логические функции полусумматора для(S истинно, если истинны НЕ a И b ИЛИ a И НЕ b)

И

(р истинен, если истинны a И b)

48.

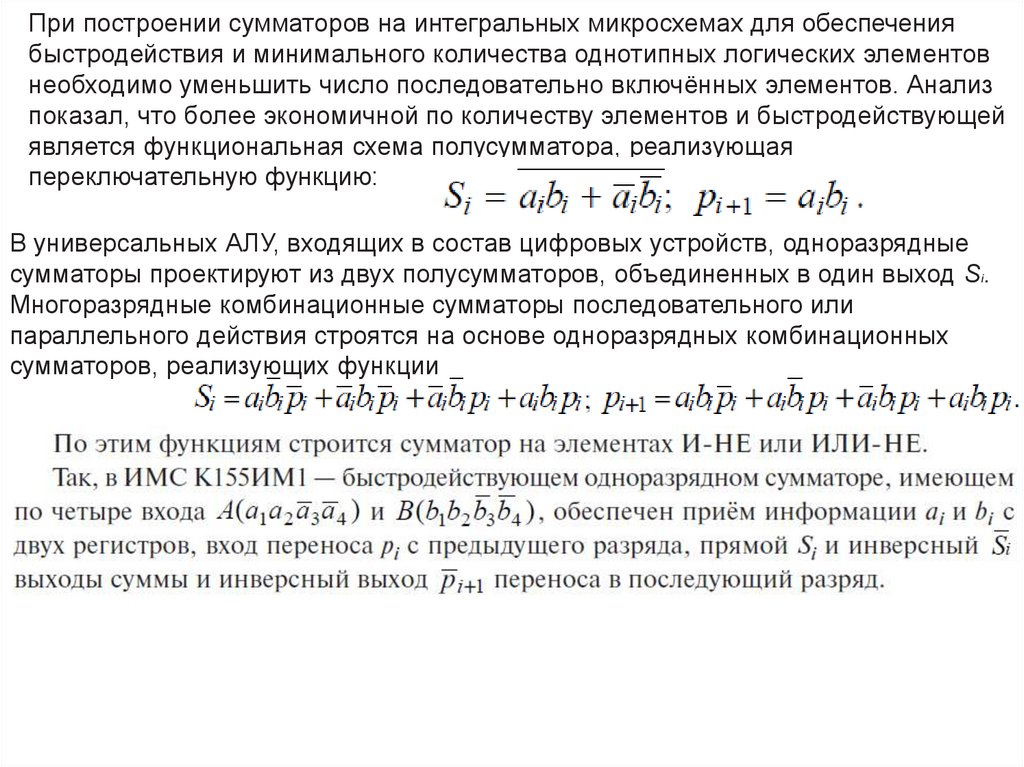

При построении сумматоров на интегральных микросхемах для обеспечениябыстродействия и минимального количества однотипных логических элементов

необходимо уменьшить число последовательно включённых элементов. Анализ

показал, что более экономичной по количеству элементов и быстродействующей

является функциональная схема полусумматора, реализующая

переключательную функцию:

В универсальных АЛУ, входящих в состав цифровых устройств, одноразрядные

сумматоры проектируют из двух полусумматоров, объединенных в один выход Si.

Многоразрядные комбинационные сумматоры последовательного или

параллельного действия строятся на основе одноразрядных комбинационных

сумматоров, реализующих функции

49.

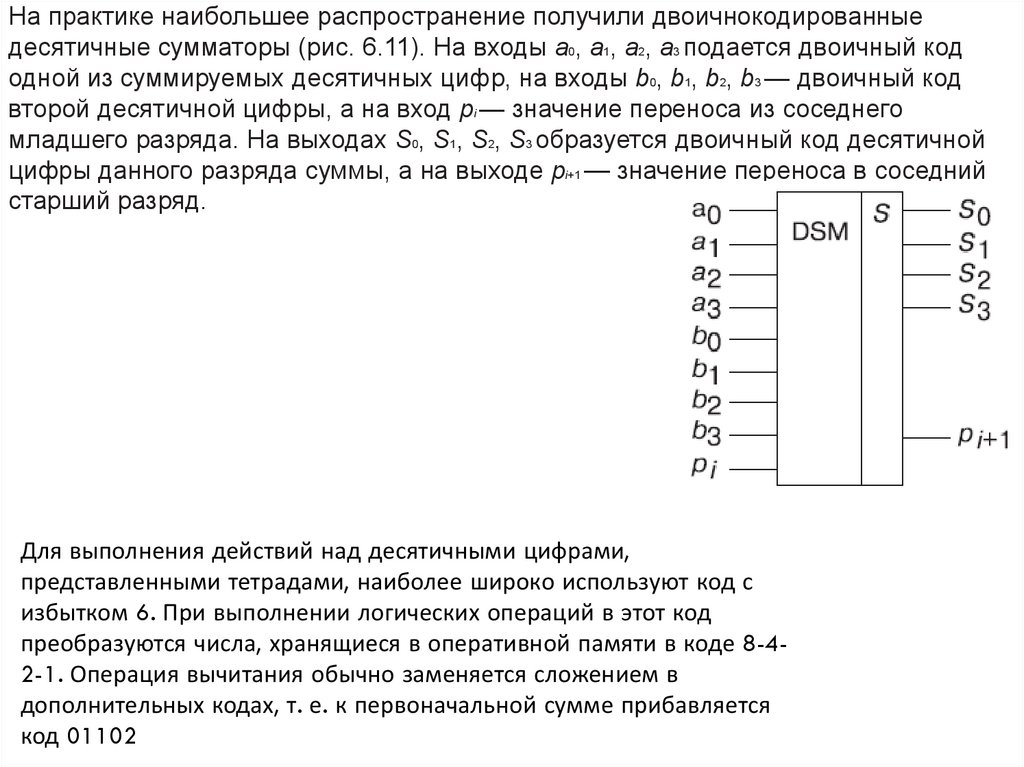

На практике наибольшее распространение получили двоичнокодированныедесятичные сумматоры (рис. 6.11). На входы а0, а1, а2, а3 подается двоичный код

одной из суммируемых десятичных цифр, на входы b0, b1, b2, b3 — двоичный код

второй десятичной цифры, а на вход рi — значение переноса из соседнего

младшего разряда. На выходах S0, S1, S2, S3 образуется двоичный код десятичной

цифры данного разряда суммы, а на выходе pi+1 — значение переноса в соседний

старший разряд.

Для выполнения действий над десятичными цифрами,

представленными тетрадами, наиболее широко используют код с

избытком 6. При выполнении логических операций в этот код

преобразуются числа, хранящиеся в оперативной памяти в коде 8-42-1. Операция вычитания обычно заменяется сложением в

дополнительных кодах, т. е. к первоначальной сумме прибавляется

код 01102

50.

Арифметико-логическое устройство (АЛУ) — частьцентрального процессора, формирующая функции двух

входных переменных и порождающая одну выходную

переменную. Эти функции состоят из простых

арифметических операций, простых логических операций

и операций сдвига.

Вне зависимости от того, насколько широк круг операций, реализуемых

современными АЛУ, главными среди них остаются операции арифметического

сложения и умножения, продолжительность выполнения которых указывается в

качестве основных характеристик вычислительного устройства. Простейшие

операции: арифметическое сложение (вычитание), логическое умножение,

логическое сложение, сумма по модулю два, инверсия, сдвиг влево, сдвиг вправо,

инкремент (положительное приращение), декремент (отрицательное приращение)

выполняются в АЛУ с помощью только аппаратных средств (схем на логических

элементах). Операция умножения (деления), как правило, выполняется

программным способом (с применением последовательного исполнения нескольких

операций сложения и сдвига, выполненных аппаратным способом).

51.

По способу действия над операндами АЛУ подразделяют на параллельного ипоследовательного действия.

По способу представления чисел различают АЛУ для чисел с фиксированной и

плавающей запятой (точкой), для десятичных чисел.

По способу организации работы АЛУ делят на синхронные и асинхронные, а

по характеру используемых элементов и узлов — на универсальные, в

которых операции для всех форм представления чисел выполняются одними и

теми же схемами, и функциональные, в которых операции над операндами с

фиксированной и плавающей запятой, с десятичными переменными и

логическими переменными осуществляются в отдельных операционных

блоках.

По связи с оперативной памятью (ОЗУ) вычислительного устройства различают

АЛУ с непосредственной и магистральной связями. В АЛУ с непосредственной

связью схемы управления передачей информации соединены

непосредственно с выходами регистров, а в АЛУ с магистральной связью

схемы для преобразования информации выделены в отдельные блоки с

двумя шинами (входной и выходной), а регистры служат лишь для хранения

операндов во время их обработки. АЛУ с магистральной связью используется в

процессорах с микропрограммным управлением.

52.

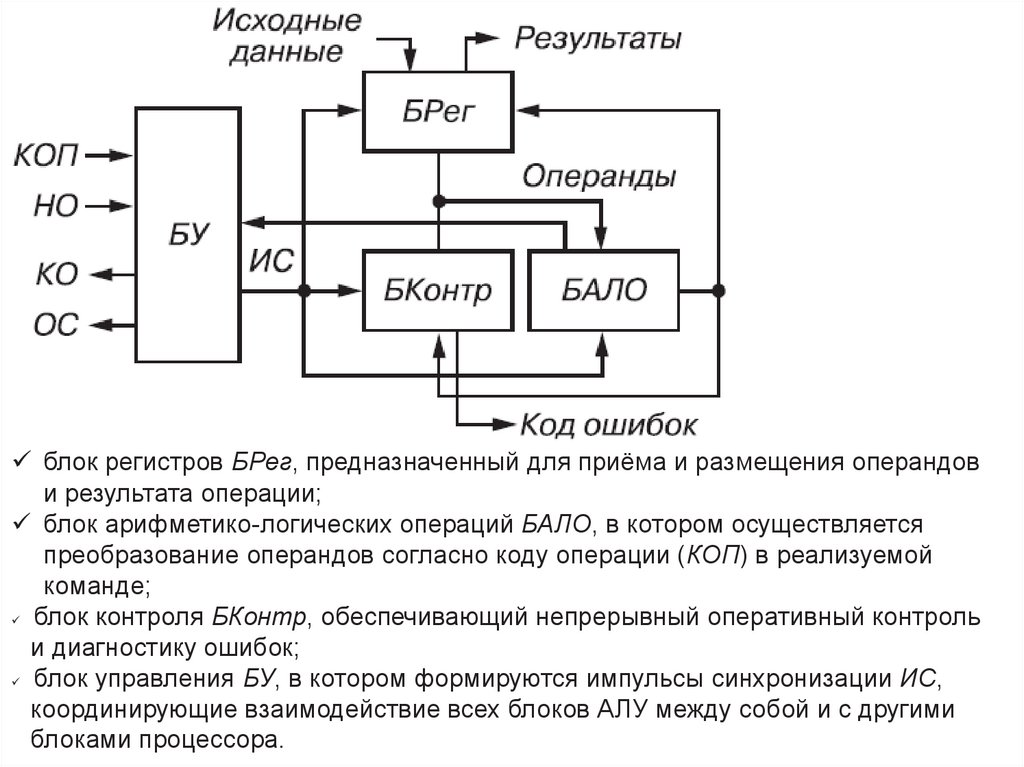

блок регистров БРег, предназначенный для приёма и размещения операндови результата операции;

блок арифметико-логических операций БАЛО, в котором осуществляется

преобразование операндов согласно коду операции (КОП) в реализуемой

команде;

блок контроля БКонтр, обеспечивающий непрерывный оперативный контроль

и диагностику ошибок;

блок управления БУ, в котором формируются импульсы синхронизации ИС,

координирующие взаимодействие всех блоков АЛУ между собой и с другими

блоками процессора.

53.

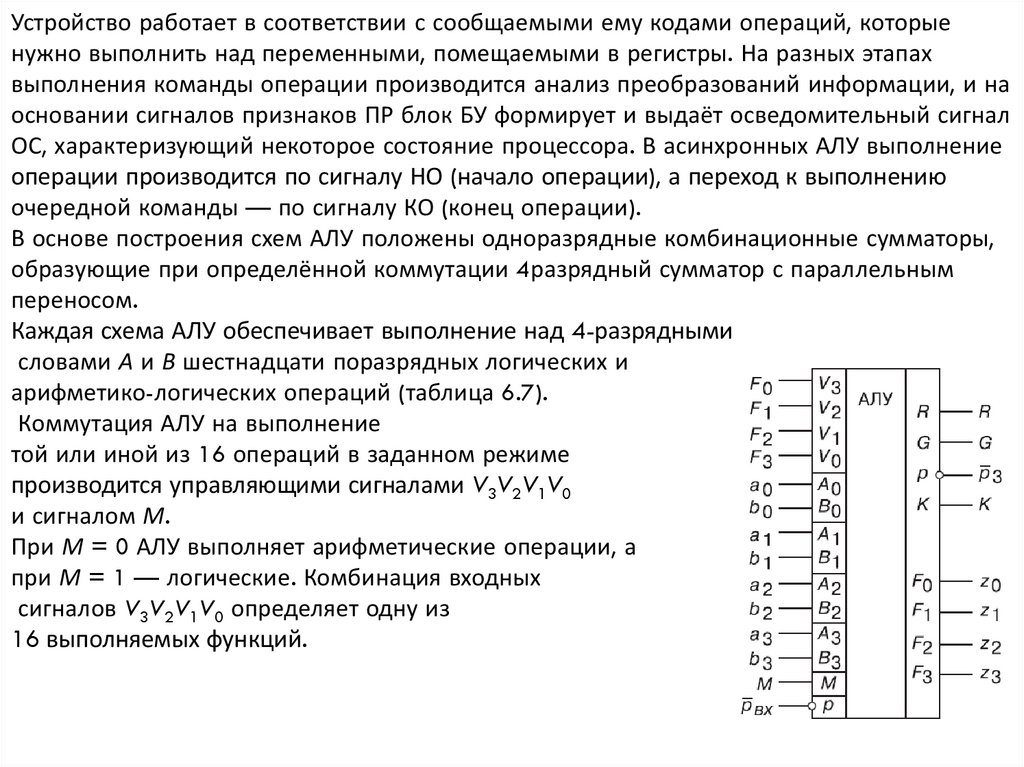

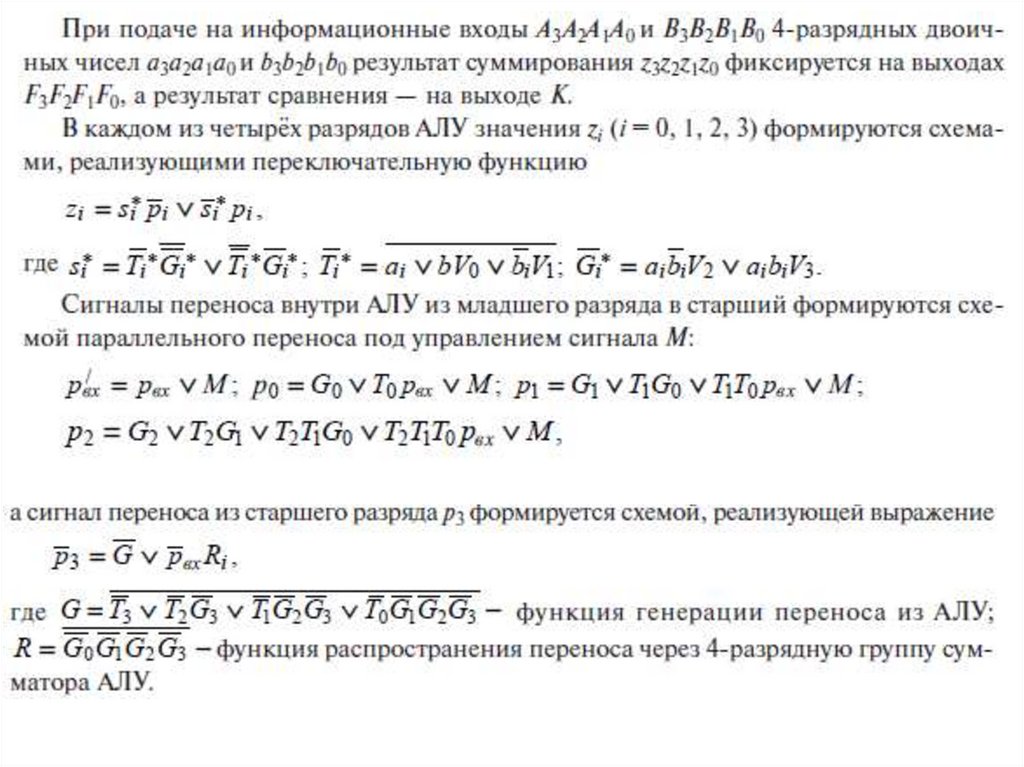

Устройство работает в соответствии с сообщаемыми ему кодами операций, которыенужно выполнить над переменными, помещаемыми в регистры. На разных этапах

выполнения команды операции производится анализ преобразований информации, и на

основании сигналов признаков ПР блок БУ формирует и выдаёт осведомительный сигнал

ОС, характеризующий некоторое состояние процессора. В асинхронных АЛУ выполнение

операции производится по сигналу НО (начало операции), а переход к выполнению

очередной команды — по сигналу КО (конец операции).

В основе построения схем АЛУ положены одноразрядные комбинационные сумматоры,

образующие при определённой коммутации 4разрядный сумматор с параллельным

переносом.

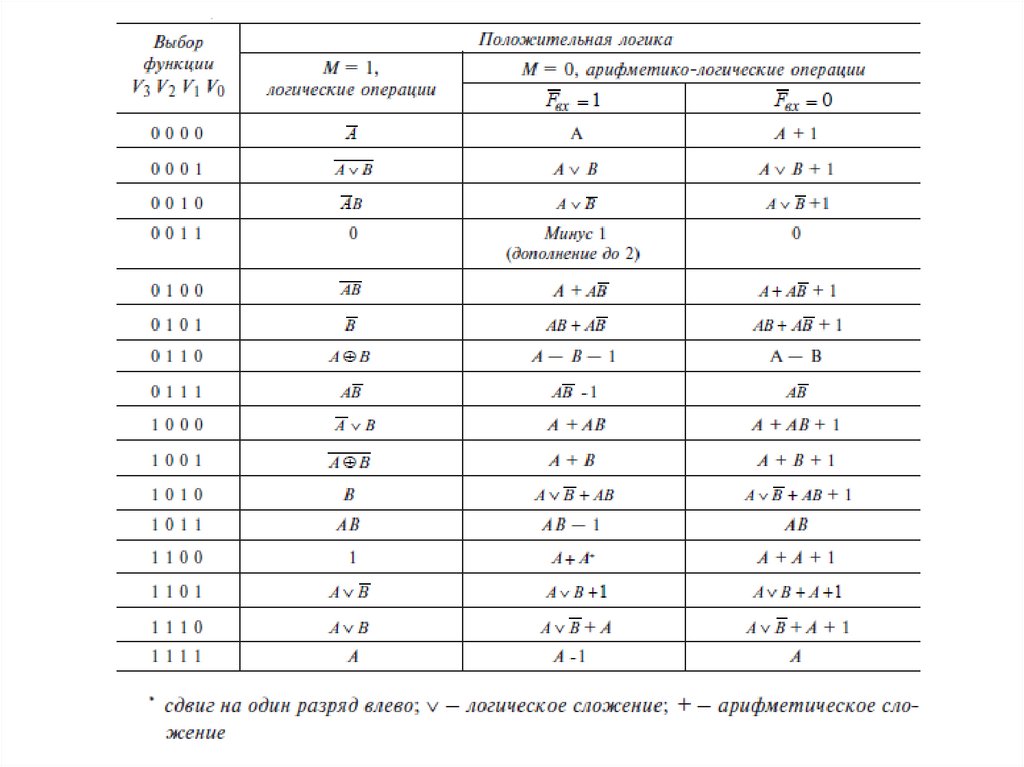

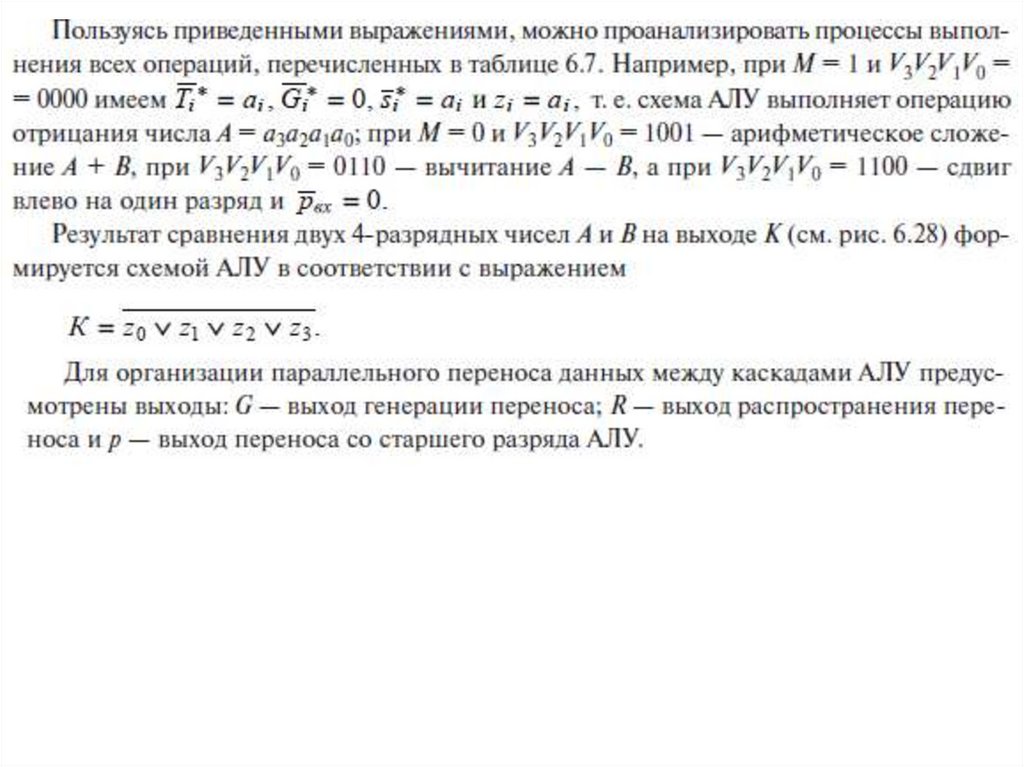

Каждая схема АЛУ обеспечивает выполнение над 4-разрядными

словами А и В шестнадцати поразрядных логических и

арифметико-логических операций (таблица 6.7).

Коммутация АЛУ на выполнение

той или иной из 16 операций в заданном режиме

производится управляющими сигналами V3V2V1V0

и сигналом М.

При М = 0 АЛУ выполняет арифметические операции, а

при М = 1 — логические. Комбинация входных

сигналов V3V2V1V0 определяет одну из

16 выполняемых функций.

electronics

electronics