Similar presentations:

Архитектура IA-32. Формат команды IA-32

1. Архитектура IA-32.

2. Формат команды IA-32.

префикс КОПMod R/M SIB

0/1 байт 1/2 байта 0/1 байт

смещение

0/1 байт 0/1/2/4 байта 0/1/2/4 байта

Типы префиксов:

1.

2.

3.

4.

На

командные префиксы (префиксы

повторения) REP, REPE/REPZ,

REPNE/REPNZ;

префикс блокировки шины LOCK;

префиксы размера;

префиксы замены сегмента.

Байт "Mod R/M"

адресации,

иногда

код операции.

непосредственный операнд

определяет режим

а

также

дополнительный

Байт

SIB

(Scale-Index-Base)

определяет способ адресации при

обращении к памяти в 32-битном

режиме

размер инструкции накладывается

ограничение в 15 байт.

Инструкция большего размера может

получиться

при

некорректном

использовании большого количества

префиксов.

↓

В

IA-32

в

таком

случае

генерируют исключение #13.

Если инструкция микропроцессора

требует операнды, то они могут

задаваться следующими

способами:

1.

непосредственно в коде инструкции

(только операнд-источник);

2.

в одном из регистров;

3.

через порт ввода-вывода;

4.

в памяти.

Для совместимости с 16-битными процессорами архитектура IA-32 использует одинаковые

коды для инструкций, оперирующих как с 16-битными, так и 32-битными операндами.

3.

Новая архитектура - новые возможностипри указании адреса для операнда в

памяти.

Регистровый режим адресации

определят операнд-источник или операндприемник в одном из регистров процессора

или сопроцессора.

Как процессор будет считать операнд или

его адрес, зависит от:

1.

эффективного размера операнда,

2.

эффективного размера адреса для

данной команды.

В некоторых случаях,

могут использоваться пары 32-битных регистров

(например, EDX:EAX), образуя 64битный операнд.

Эти значения определяются на основе:

режима работы,

1.

бита D дескриптора используемого

сегмента,

2.

наличия в инструкции определенных

префиксов.

Адресация через порт ввода-вывода получение

операнда

или

сохранение

операнда через пространство портов

ввода-вывода.

Адрес

порта

ввода-вывода

либо

непосредственно

включается

в

код

инструкции, либо берется из регистра DX.

Непосредственный режим

адресации подразумевает включение

операнда-источника в код инструкции.

Адресация через память. Таким образом,

может быть указан операнд-источник

или операнд-приемник.

Операнд может быть 8-битовым или 16битовым, если значение эффективного

размера операнда - 16.

Процессор

не

позволяет

одновременно

задавать оба операнда через память (за

исключением

некоторых

цепочечных

команд).

Операнд может быть 8-битовым или 32битовым, если значение эффективного

размера операнда - 32.

4.

Для получения операнда из памятипроцессору необходимо знать:

1. селектор сегмента,

2. смещение в сегменте.

Явное использование сегментных

регистров возможно, если в код

инструкции включается префикс смены

сегмента.

В некоторых командах селектор может

быть указан непосредственно в коде

инструкции.

Указание префикса смены сегмента

допустимо не для всех команд:

1. нельзя менять сегмент для команд

работы со стеком (всегда используется

SS);

2. для цепочечных команд можно менять

сегмент только операнда-источника

(операнд-приемник всегда адресуется

через ES).

В других случаях процессор может явно

или неявно использовать

значение одного из сегментных

регистров.

Под неявным использованием

сегментных регистров

подразумевается то, что в зависимости

от предназначения

операнда процессор использует

определенный сегментный

регистр для обращения к памяти:

1. CS -для выборки инструкций;

2. SS - для работы со стеком или

обращения к памяти через

регистры ESP или EBP;

3. ES - для получения адреса операндаприемника в цепочечных командах;

4. DS - при всех остальных обращениях к

памяти.

Смещение в сегменте (эффективный или

исполнительный адрес - EA) может

быть вычислено на основе значений

РОН и/или указанного в коде

инструкции относительного смещения,

при этом любой или даже несколько из

указанных компонентов могут

отсутствовать:

EA = BASE + (INDEX*SCALE) + DISPLACEMENT

5. Функциональная классификация машинных команд.

1.2.

Обычно машинная команда имеет два операнда:

1. приемник,

2. источник.

Возможны их следующие сочетания:

3.

4.

Группы внутри всего

набора машинных

команд:

команды общего

назначения,

исполняемые

целочисленным

устройством, в том

числе системные

команды;

команды

сопроцессора;

команды MMXрасширения;

команды XMMрасширения (наборы

команд SSE и SSE2).

6.

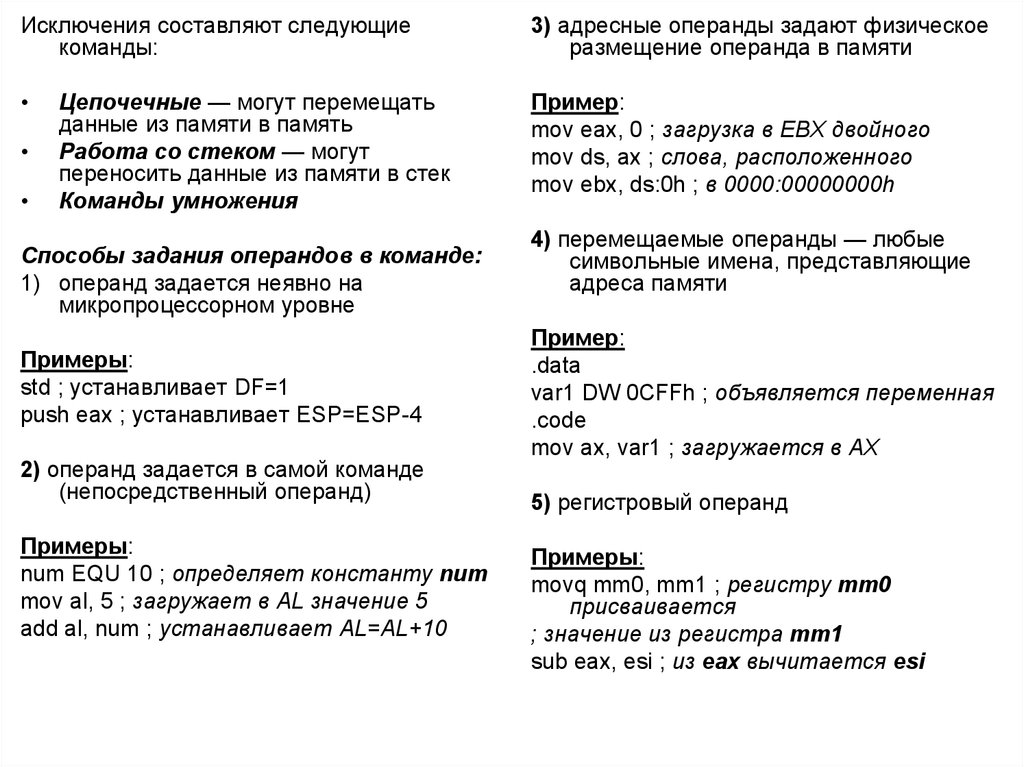

Исключения составляют следующиекоманды:

3) адресные операнды задают физическое

размещение операнда в памяти

Пример:

mov eax, 0 ; загрузка в EBX двойного

mov ds, ax ; слова, расположенного

mov ebx, ds:0h ; в 0000:00000000h

Цепочечные — могут перемещать

данные из памяти в память

Работа со стеком — могут

переносить данные из памяти в стек

Команды умножения

Способы задания операндов в команде:

1) операнд задается неявно на

микропроцессорном уровне

Примеры:

std ; устанавливает DF=1

push eax ; устанавливает ESP=ESP-4

2) операнд задается в самой команде

(непосредственный операнд)

Примеры:

num EQU 10 ; определяет константу num

mov al, 5 ; загружает в AL значение 5

add al, num ; устанавливает AL=AL+10

4) перемещаемые операнды — любые

символьные имена, представляющие

адреса памяти

Пример:

.data

var1 DW 0CFFh ; объявляется переменная

.code

mov ax, var1 ; загружается в AX

5) регистровый операнд

Примеры:

movq mm0, mm1 ; регистру mm0

присваивается

; значение из регистра mm1

sub eax, esi ; из eax вычитается esi

7.

6) операнд — порт ввода/выводаПримеры:

in al, 48h ; взять байт из порта 48h

mov al, 20h ; вывести слово в

out dx, al ; порт 20h

7) операнд находится в стеке

Примеры:

push eax ; обменять значения

push ebx ; регистров EAX и EBX

pop eax ; через стек

pop ebx ;

8) операнд находится в памяти

Примеры:

.data

var DD 100 DUP(0)

...

lea esi, var ; загрузить в EAX второй

mov eax, [esi+4] ; элемент массива VAR

Виды адресации операндов делятся на

два вида:

● Прямые — эффективный адрес

операнда находится непосредственно

в коде команды

● Косвенные — в самой команде

находится лишь часть эффективного

адреса, а остальные его компоненты

находятся в регистрах.

Относительная прямая адресация:

Используется в командах условных

переходов, поле смещения машинной

команды содержит значение, которое

будет складываться с регистром EIP.

jz METKA ; переход на метку METKA, если

ZF=1

mov al, 5

...

METKA:

8.

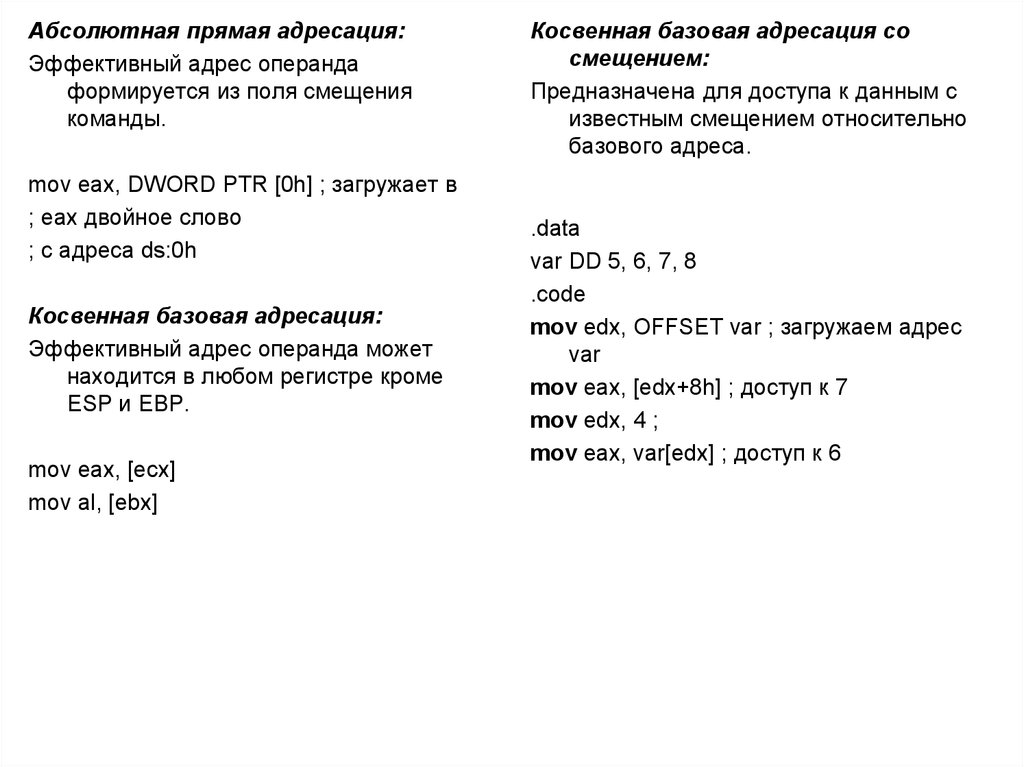

Абсолютная прямая адресация:Эффективный адрес операнда

формируется из поля смещения

команды.

mov eax, DWORD PTR [0h] ; загружает в

; eax двойное слово

; с адреса ds:0h

Косвенная базовая адресация:

Эффективный адрес операнда может

находится в любом регистре кроме

ESP и EBP.

mov eax, [ecx]

mov al, [ebx]

Косвенная базовая адресация со

смещением:

Предназначена для доступа к данным с

известным смещением относительно

базового адреса.

.data

var DD 5, 6, 7, 8

.code

mov edx, OFFSET var ; загружаем адрес

var

mov eax, [edx+8h] ; доступ к 7

mov edx, 4 ;

mov eax, var[edx] ; доступ к 6

9.

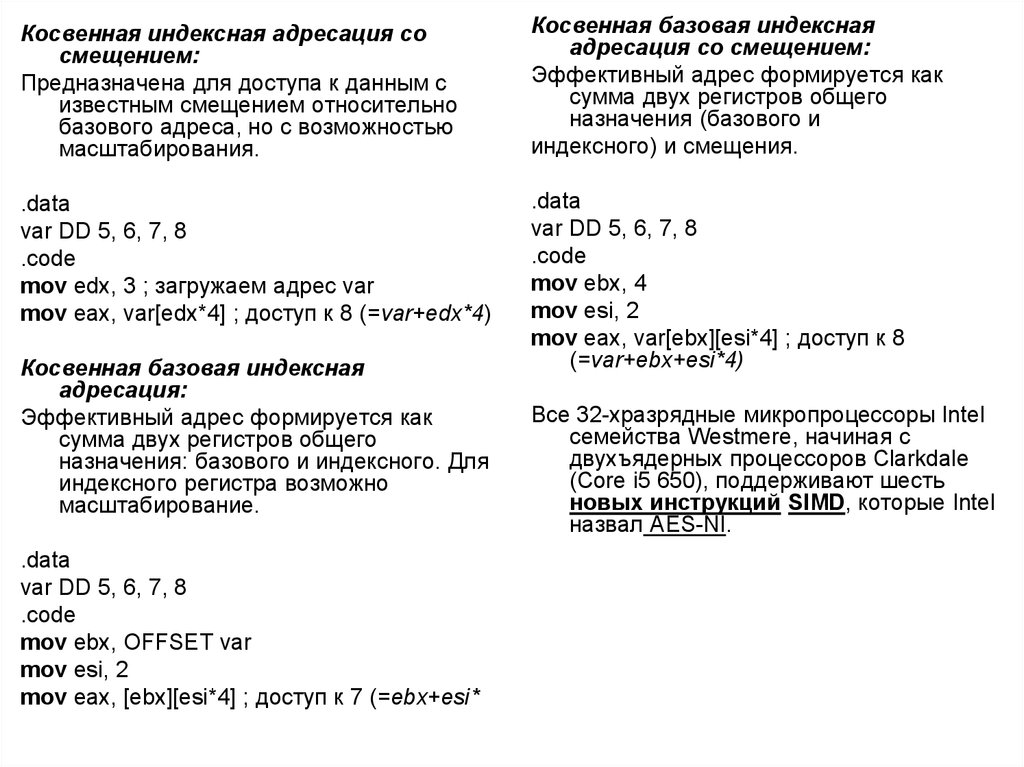

Косвенная индексная адресация сосмещением:

Предназначена для доступа к данным с

известным смещением относительно

базового адреса, но с возможностью

масштабирования.

Косвенная базовая индексная

адресация со смещением:

Эффективный адрес формируется как

сумма двух регистров общего

назначения (базового и

индексного) и смещения.

.data

var DD 5, 6, 7, 8

.code

mov edx, 3 ; загружаем адрес var

mov eax, var[edx*4] ; доступ к 8 (=var+edx*4)

.data

var DD 5, 6, 7, 8

.code

mov ebx, 4

mov esi, 2

mov eax, var[ebx][esi*4] ; доступ к 8

(=var+ebx+esi*4)

Косвенная базовая индексная

адресация:

Эффективный адрес формируется как

сумма двух регистров общего

назначения: базового и индексного. Для

индексного регистра возможно

масштабирование.

.data

var DD 5, 6, 7, 8

.code

mov ebx, OFFSET var

mov esi, 2

mov eax, [ebx][esi*4] ; доступ к 7 (=ebx+esi*

Все 32-хразрядные микропроцессоры Intel

семейства Westmere, начиная с

двухъядерных процессоров Clarkdale

(Core i5 650), поддерживают шесть

новых инструкций SIMD, которые Intel

назвал AES-NI.

10.

ММХ-технологияSSE-расширение

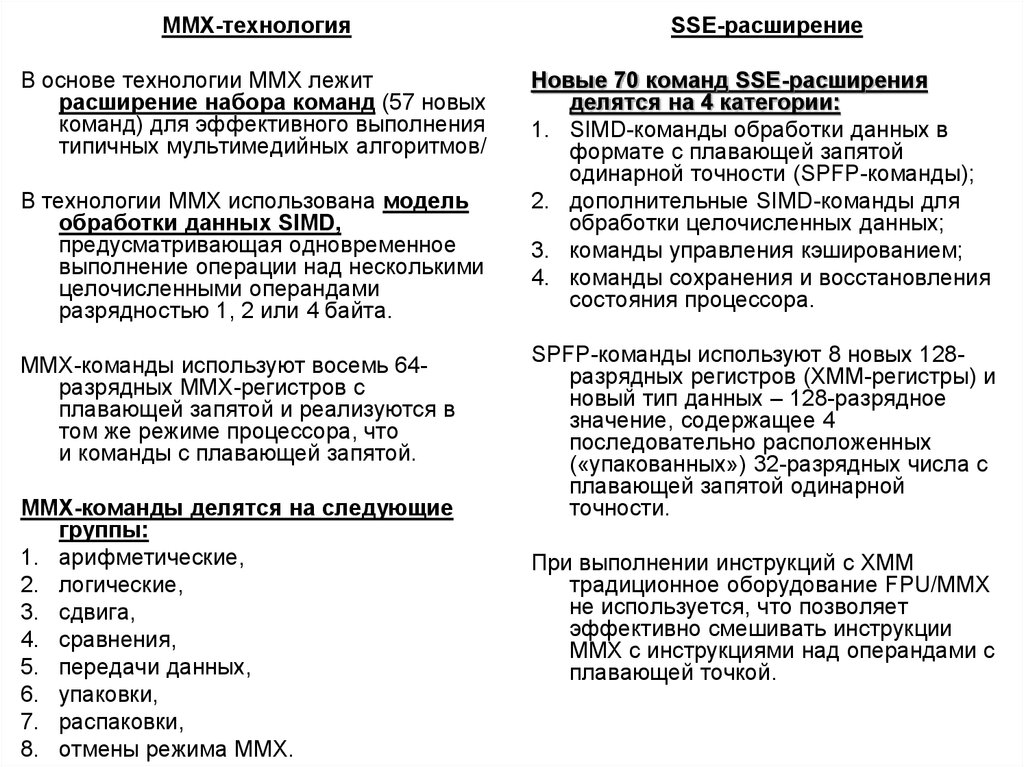

В основе технологии ММХ лежит

расширение набора команд (57 новых

команд) для эффективного выполнения

типичных мультимедийных алгоритмов/

Новые 70 команд SSE-расширения

делятся на 4 категории:

1. SIMD-команды обработки данных в

формате с плавающей запятой

одинарной точности (SPFP-команды);

2. дополнительные SIMD-команды для

обработки целочисленных данных;

3. команды управления кэшированием;

4. команды сохранения и восстановления

состояния процессора.

В технологии ММХ использована модель

обработки данных SIMD,

предусматривающая одновременное

выполнение операции над несколькими

целочисленными операндами

разрядностью 1, 2 или 4 байта.

ММХ-команды используют восемь 64разрядных ММХ-регистров с

плавающей запятой и реализуются в

том же режиме процессора, что

и команды с плавающей запятой.

ММХ-команды делятся на следующие

группы:

1. арифметические,

2. логические,

3. сдвига,

4. сравнения,

5. передачи данных,

6. упаковки,

7. распаковки,

8. отмены режима ММХ.

SPFP-команды используют 8 новых 128разрядных регистров (ХММ-регистры) и

новый тип данных – 128-разрядное

значение, содержащее 4

последовательно расположенных

(«упакованных») 32-разрядных числа с

плавающей запятой одинарной

точности.

При выполнении инструкций с ХММ

традиционное оборудование FPU/MMX

не используется, что позволяет

эффективно смешивать инструкции

ММХ с инструкциями над операндами с

плавающей точкой.

11.

Большинство SPFP-команд имеют дваоперанда. Данные, содержащиеся в

первом операнде, после выполнения

команды, как правило, замещаются

результатами, а данные, содержащиеся

во втором операнде, остаются

неизменными.

SPFP-команды поддерживают два типа

операций над упакованными данными

с плавающей запятой:

1. параллельные,

2. скалярные.

Параллельные операции выполняются

над четырьмя 32-разрядными

элементами данных, упакованными в

каждый 128-разрядный операнд.

Скалярные операции выполняются над

младшими (занимающие разряды 0–31)

элементами данных двух операндов.

Остальные три элемента данных не

изменяются.

В расширение SSE включены

дополнительные SIMD-команды для

работы с целочисленными данными.

Эти новые команды расширяют

возможности существующего набора

команд технологии ММХ. Они

выполняют SIMD-операции над

несколькими целочисленными

данными, упакованными в 64разрядные группы, загружают и хранят

упакованные данные в 64-разрядных

ММХ-регистрах.

Кроме того, в SSE введены команды

нового типа, обеспечивающие:

1. управление кэшированием данных с

целью повышения эффективности

использования кэш-памяти и

сокращения числа обращений к

основной памяти;

2. упреждающее кэширование данных с

целью организации параллельной

работы конвейера команд и обмена с

памятью.

Первая группа команд выполняет запись

данных из ММХ (ХММ) регистра в

память, минуя кэш.

Вторая – обеспечивает запись данных из

памяти в кэш различных уровней.

12.

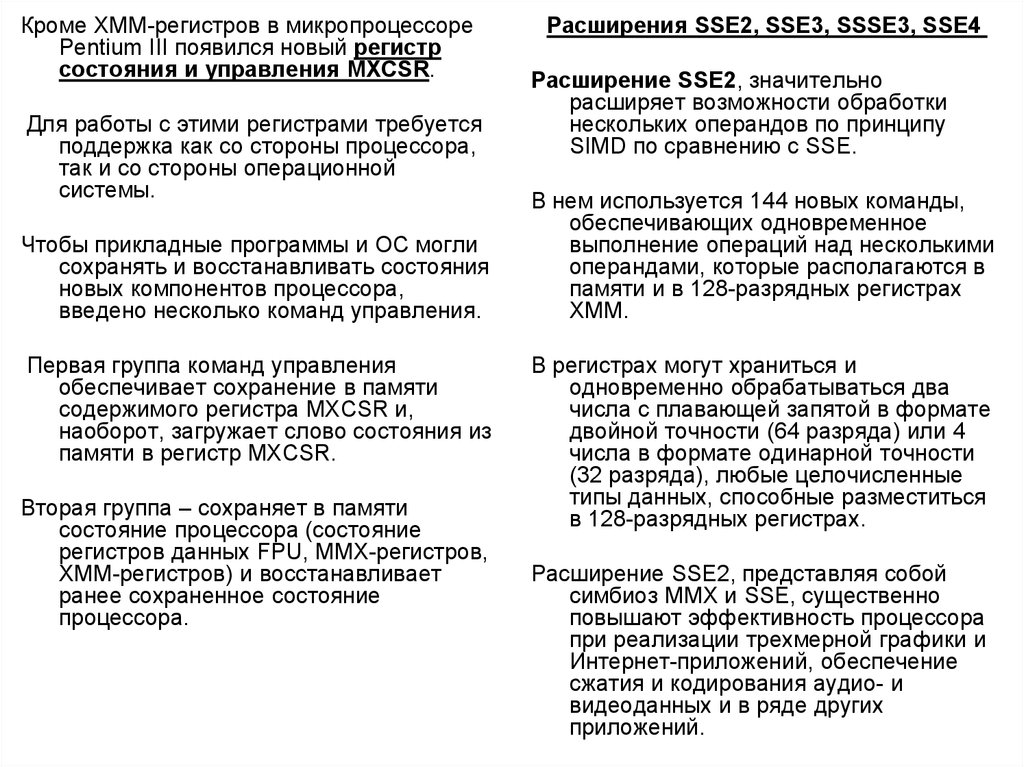

Кроме ХММ-регистров в микропроцессореPentium III появился новый регистр

состояния и управления MXCSR.

Для работы с этими регистрами требуется

поддержка как со стороны процессора,

так и со стороны операционной

системы.

Чтобы прикладные программы и ОС могли

сохранять и восстанавливать состояния

новых компонентов процессора,

введено несколько команд управления.

Первая группа команд управления

обеспечивает сохранение в памяти

содержимого регистра МХCSR и,

наоборот, загружает слово состояния из

памяти в регистр MXCSR.

Вторая группа – сохраняет в памяти

состояние процессора (состояние

регистров данных FPU, MMX-регистров,

ХММ-регистров) и восстанавливает

ранее сохраненное состояние

процессора.

Расширения SSE2, SSE3, SSSE3, SSE4

Расширение SSE2, значительно

расширяет возможности обработки

нескольких операндов по принципу

SIMD по сравнению с SSE.

В нем используется 144 новых команды,

обеспечивающих одновременное

выполнение операций над несколькими

операндами, которые располагаются в

памяти и в 128-разрядных регистрах

ХММ.

В регистрах могут храниться и

одновременно обрабатываться два

числа с плавающей запятой в формате

двойной точности (64 разряда) или 4

числа в формате одинарной точности

(32 разряда), любые целочисленные

типы данных, способные разместиться

в 128-разрядных регистрах.

Расширение SSE2, представляя собой

симбиоз ММХ и SSE, существенно

повышают эффективность процессора

при реализации трехмерной графики и

Интернет-приложений, обеспечение

сжатия и кодирования аудио- и

видеоданных и в ряде других

приложений.

13.

Расширение SSE3, включает 5 новыхопераций с комплексными числами, 5

потоковых операций над числами с

плавающей запятой, 2 команды для

синхронизации потоков и одну

специальную инструкцию для

применения при кодировании видео.

Расширение SSSE3 (Supplemental SSE3 –

дополнительное потоковое SIMDрасширение 3). Новыми в SSSE3

являются 16 уникальных команд,

работающих с упакованными целыми

данными. Каждый из них может

работать как с 64-битными (ММХ), так и

с 128-битными (ХММ) регистрами,

поэтому Intel в своих материалах

ссылается на 32 новые команды. Новые

инструкции включают работу со знаком,

сдвиги, перемешивание байт,

умножение, горизонтальное

сложение/вычитание целых.

Расширение SSE4.1 Набор команд SSE4.1

включает 47 новых инновационных

инструкций, основными из которых

являются примитивы векторизации для

компиляторов и ускорители

кодирования видеозаписей с высоким

расширением и обработки

фотоизображений.

Расширение SSE4.2. Введенные в набор

SSE4.2 инструкции ориентированы на

ускорение обработки строк и текстовой

информации.

Ни одна из SSE4 инструкций не работает с

64-битными ММХ-регистрами, только с

128-битными ХММ-регистрами.

Расширения AES-NI, AVX

Расширение AES-NI (Advanced Encryption

Standard New Instructions) – набор из 6

новых SIMD-инструкций, ускоряющий

процесс шифрования и дешифрования

информации по стандарту AES.

Стандарт AES является стандартом

шифрования США, принятым в 2000 г.

Он специфицирует алгоритм Rijndael,

который представляет собой

симметричный блочный шифр,

работающий с блоками длиной 128

бит, и использует ключи длиной 128,

192 и 256 бит.

14.

Новое расширение AVX (Advanced Vector Extensions) –представляет различныеулучшения, новые инструкции и новую схему кодирования машинных кодов.

Размер векторных регистров SIMD увеличивается со 128 (ХММ) до 256 бит (регистры

YMM).

Существующие 128-битные инструкции будут использовать только младшую половину

новых YMM-регистров. В будущем возможно расширение до 512 или 1024 бит.

Набор инструкций AVX позволяет использовать любую двухоперандную инструкцию ХММ

в трехоперандном виде без модификации двух регистров-источников, с отдельным

регистром для результата.

Добавлены инструкции с количеством операндов более трех.

Новая система кодирования машинных кодов VEX предоставляет новый набор префиксов

кода, которые расширяют пространство возможных машинных кодов.

Использование YMM-регистров поддерживают операционные системы: Windows 7,

Windows Server 2008 R2, Linux (версия ядра 2.6.30).

Расширение AVX подходит для интенсивных вычислений с плавающей точкой в

мультимедийных, научных и финансовых задачах. Увеличивает степень параллелизма

и пропускную способность в вещественных SIMD-вычислениях.

programming

programming