Similar presentations:

Interrupt. The AVR microcontroller and embedded systems. (Chapter 10)

1. Interrupt Chapter 10

The AVR microcontrollerand embedded

systems

using assembly and c

AVR Microcontroller and Embedded System Using Assembly and C

Mazidi, Naimi, and Naimi

© 2011 Pearson Higher Education,

Upper Saddle River, NJ 07458. • All Rights Reserved.

2. Contents

Polling Vs. interruptInterrupt unit

Steps in executing an interrupt

Edge trigger Vs. Level trigger in external

interrupts

Timer interrupt

Interrupt priority

Interrupt inside an interrupt

Task switching and resource conflict

AVR Microcontroller and Embedded System Using Assembly and C: By: Mazidi, Naimi, and Naimi

Edited by : Dr. Irfanud Din , Prof., INHA University in Tashkent.

© 2011 Pearson Higher Education,

Upper Saddle River, NJ 07458. • All Rights Reserved.

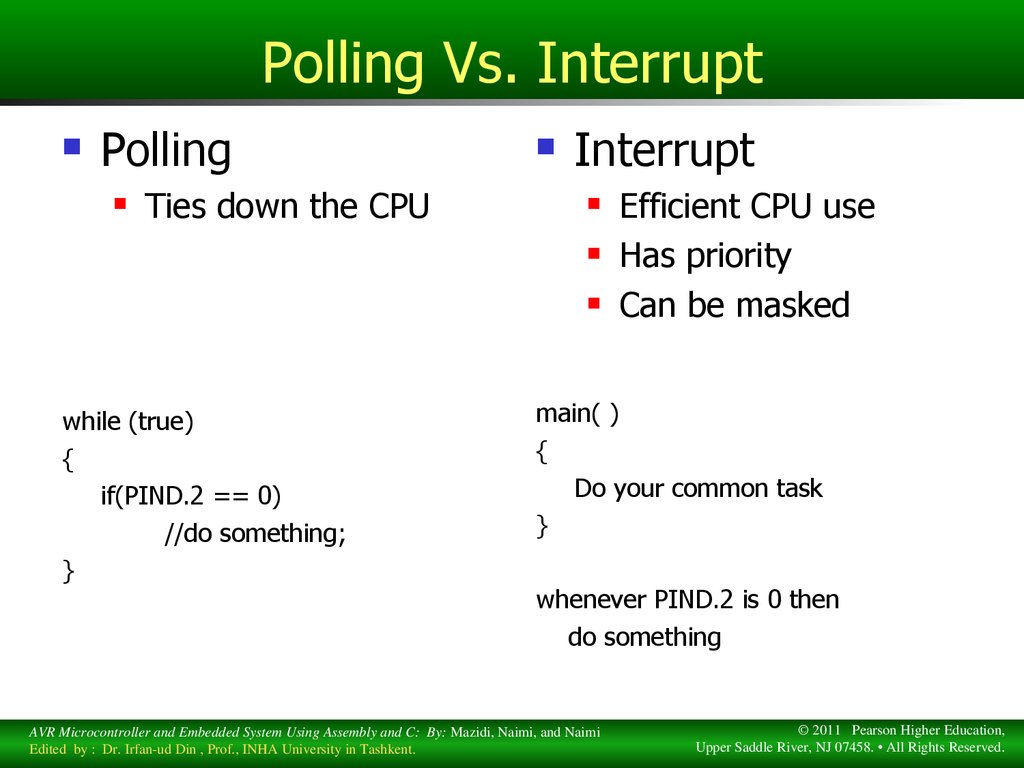

3. Polling Vs. Interrupt

PollingTies down the CPU

Interrupt

while (true)

{

if(PIND.2 == 0)

//do something;

}

Efficient CPU use

Has priority

Can be masked

main( )

{

Do your common task

}

whenever PIND.2 is 0 then

do something

AVR Microcontroller and Embedded System Using Assembly and C: By: Mazidi, Naimi, and Naimi

Edited by : Dr. Irfanud Din , Prof., INHA University in Tashkent.

© 2011 Pearson Higher Education,

Upper Saddle River, NJ 07458. • All Rights Reserved.

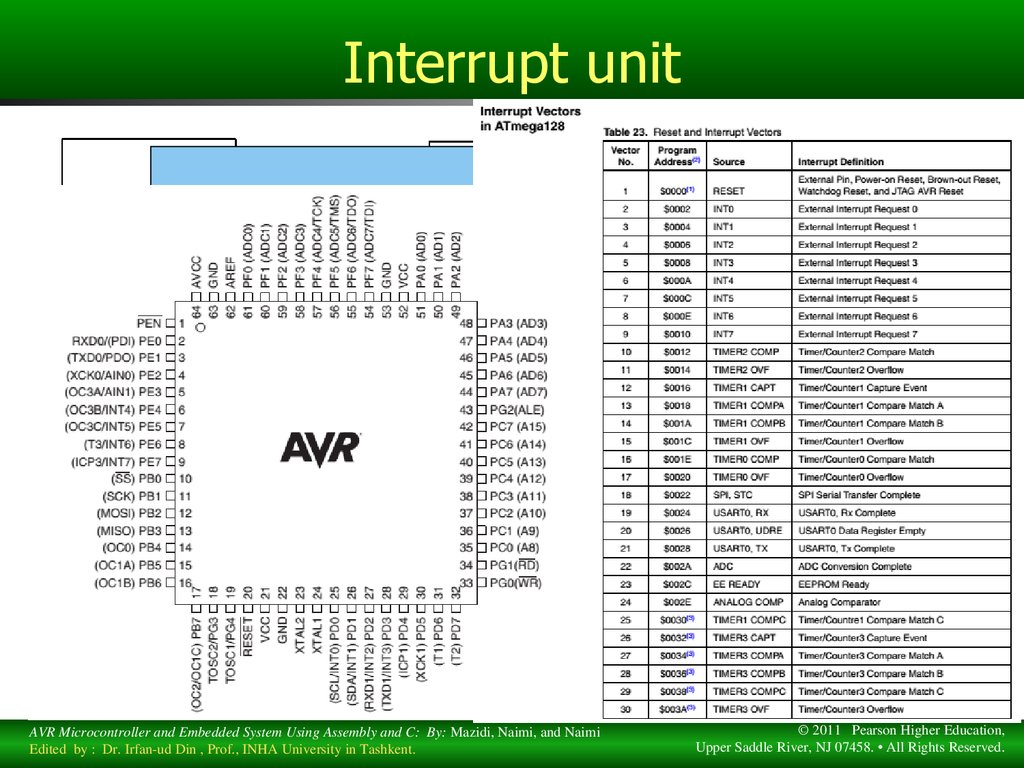

4. Interrupt unit

AVR Microcontroller and Embedded System Using Assembly and C: By: Mazidi, Naimi, and NaimiEdited by : Dr. Irfanud Din , Prof., INHA University in Tashkent.

© 2011 Pearson Higher Education,

Upper Saddle River, NJ 07458. • All Rights Reserved.

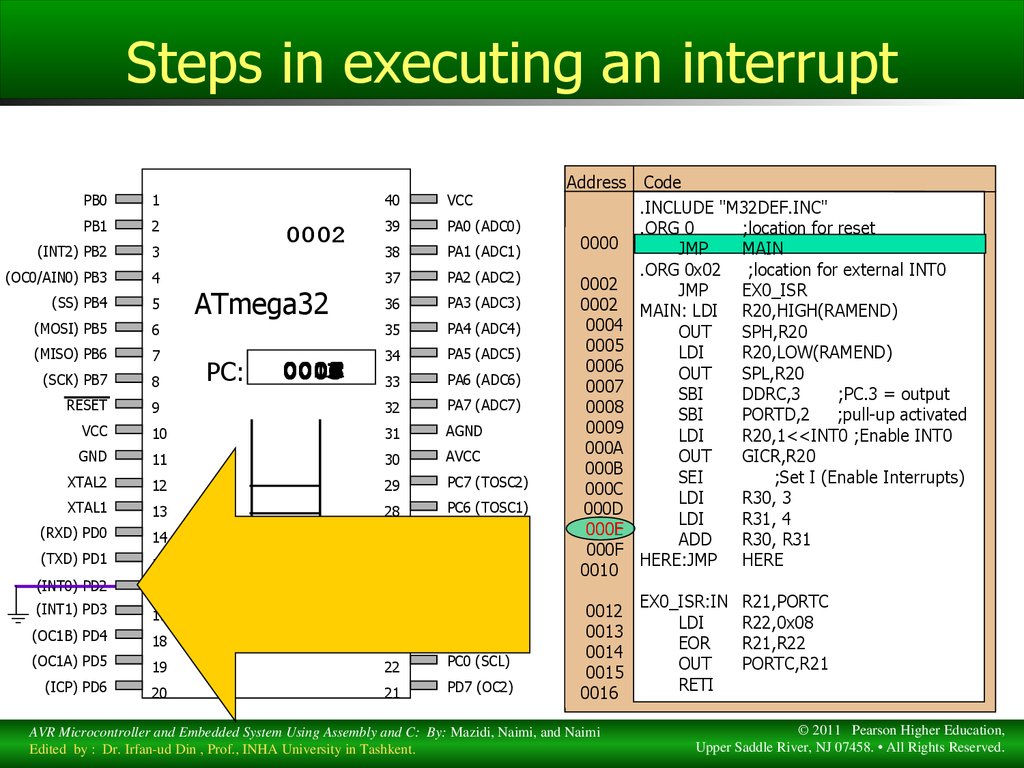

5. Steps in executing an interrupt

PB01

40

VCC

PB1

2

39

PA0 (ADC0)

(INT2) PB2

3

38

PA1 (ADC1)

(OC0/AIN0) PB3

4

37

PA2 (ADC2)

(SS) PB4

5

36

PA3 (ADC3)

(MOSI) PB5

6

35

PA4 (ADC4)

(MISO) PB6

7

34

PA5 (ADC5)

(SCK) PB7

8

33

PA6 (ADC6)

RESET

9

32

PA7 (ADC7)

VCC

10

31

AGND

GND

11

30

AVCC

XTAL2

12

29

PC7 (TOSC2)

XTAL1

13

28

PC6 (TOSC1)

(RXD) PD0

14

27

PC5 (TDI)

(TXD) PD1

15

26

PC4 (TDO)

(INT0) PD2

16

25

PC3 (TMS)

(INT1) PD3

17

24

PC2 (TCK)

(OC1B) PD4

18

23

PC1 (SDA)

(OC1A) PD5

19

22

PC0 (SCL)

(ICP) PD6

20

21

PD7 (OC2)

0002

ATmega32

PC:

0016

0015

0014

0013

0012

000D

0009

000A

000B

000C

0006

0008

000F

0004

000E

0007

0005

0000

SP

Stack

Address

0000

0002

0002

0004

0005

0006

0007

0008

0009

000A

000B

000C

000D

000F

000E

000F

0010

0012

0013

0014

0015

0016

AVR Microcontroller and Embedded System Using Assembly and C: By: Mazidi, Naimi, and Naimi

Edited by : Dr. Irfanud Din , Prof., INHA University in Tashkent.

Code

.INCLUDE "M32DEF.INC"

.ORG 0

;location for reset

JMP

MAIN

.ORG 0x02

;location for external INT0

JMP

EX0_ISR

MAIN: LDI R20,HIGH(RAMEND)

OUT

SPH,R20

LDI

R20,LOW(RAMEND)

OUT

SPL,R20

SBI

DDRC,3

;PC.3 = output

SBI

PORTD,2

;pull-up activated

LDI

R20,1<<INT0 ;Enable INT0

OUT

GICR,R20

SEI

;Set I (Enable Interrupts)

LDI

R30, 3

LDI

R31, 4

ADD

R30, R31

HERE:JMP HERE

EX0_ISR:IN

LDI

EOR

OUT

RETI

R21,PORTC

R22,0x08

R21,R22

PORTC,R21

© 2011 Pearson Higher Education,

Upper Saddle River, NJ 07458. • All Rights Reserved.

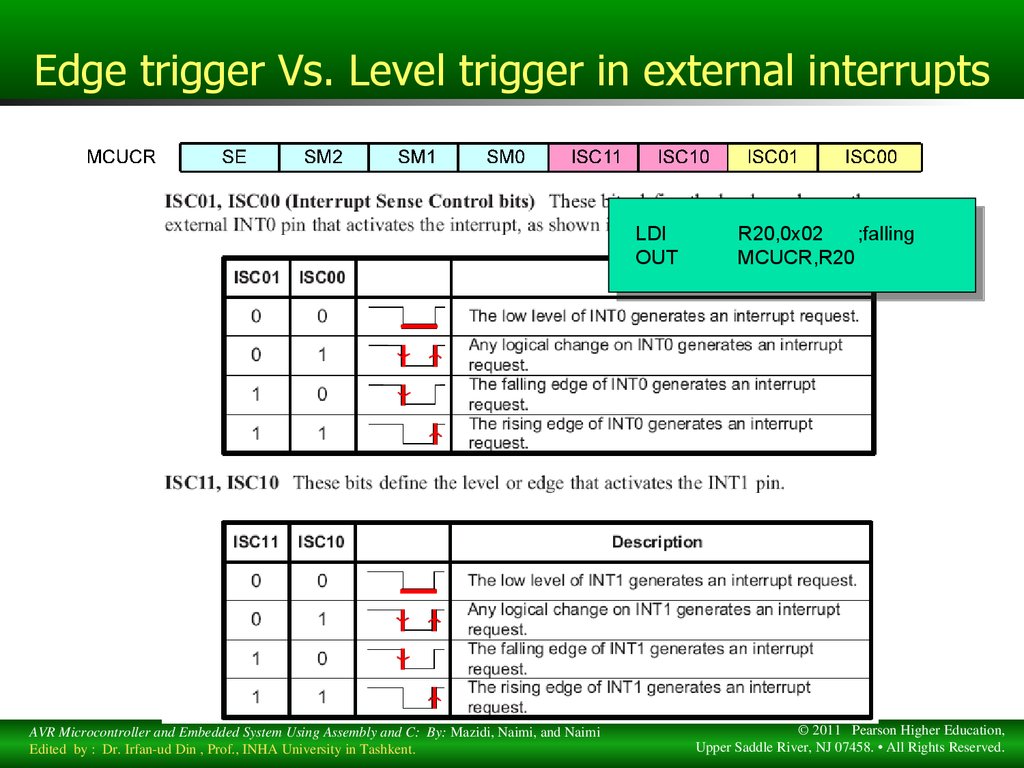

6. Edge trigger Vs. Level trigger in external interrupts

LDIOUT

AVR Microcontroller and Embedded System Using Assembly and C: By: Mazidi, Naimi, and Naimi

Edited by : Dr. Irfanud Din , Prof., INHA University in Tashkent.

R20,0x02

;falling

MCUCR,R20

© 2011 Pearson Higher Education,

Upper Saddle River, NJ 07458. • All Rights Reserved.

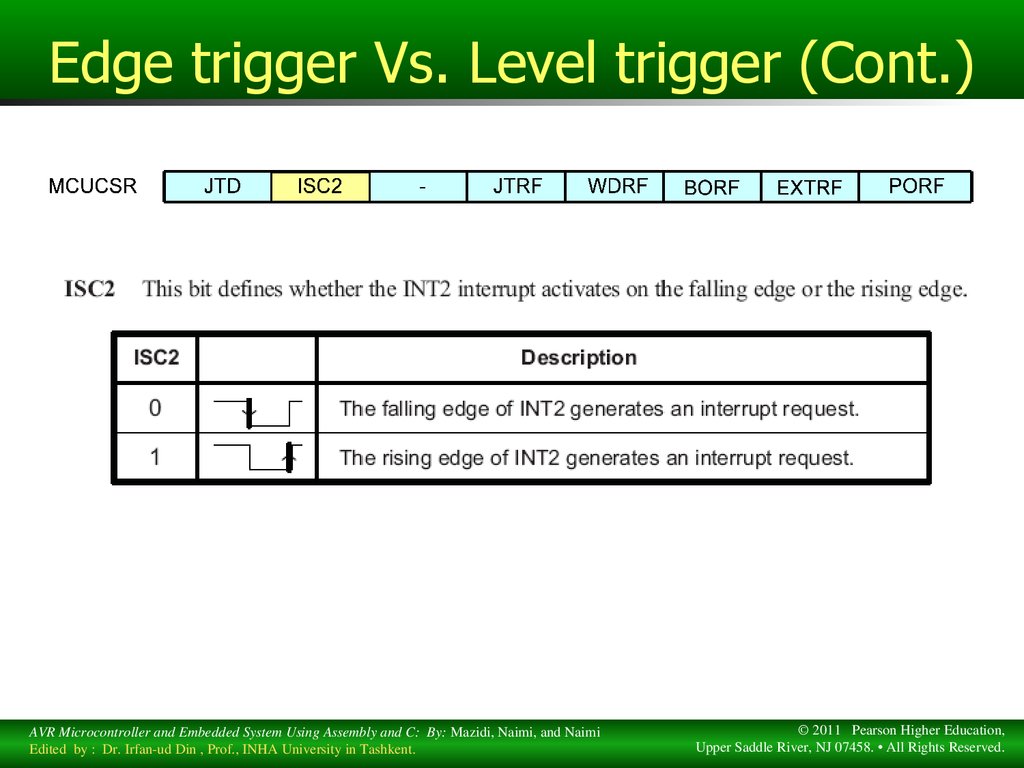

7. Edge trigger Vs. Level trigger (Cont.)

AVR Microcontroller and Embedded System Using Assembly and C: By: Mazidi, Naimi, and NaimiEdited by : Dr. Irfanud Din , Prof., INHA University in Tashkent.

© 2011 Pearson Higher Education,

Upper Saddle River, NJ 07458. • All Rights Reserved.

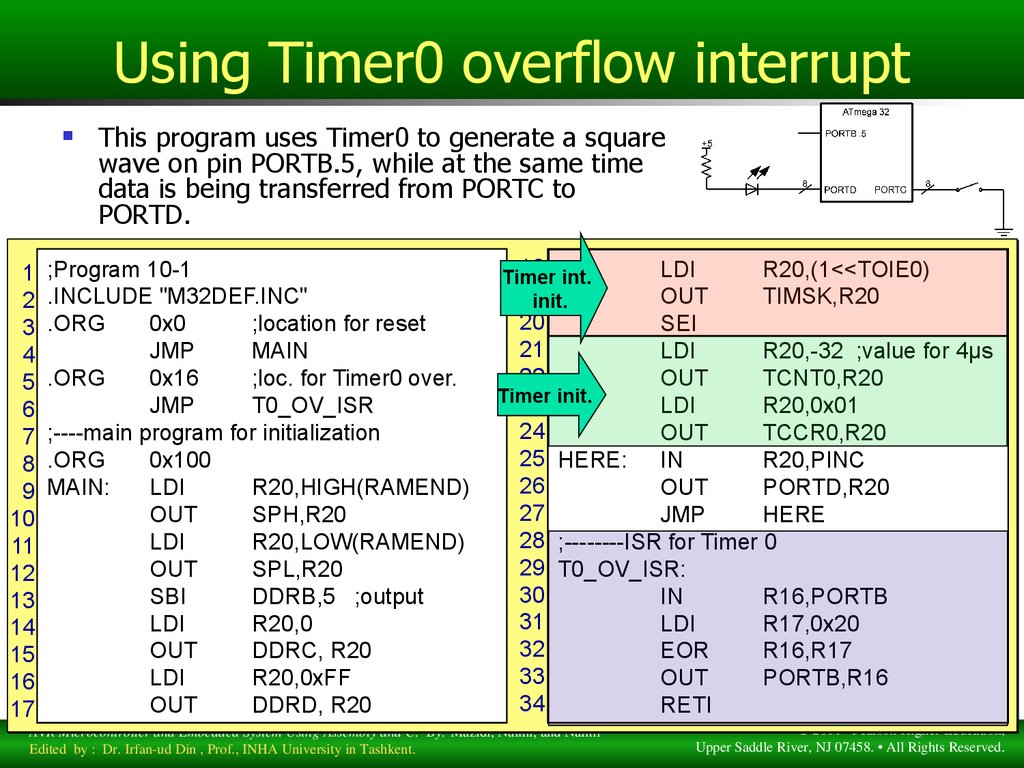

8. Using Timer0 overflow interrupt

12

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

This program uses Timer0 to generate a square

wave on pin PORTB.5, while at the same time

data is being transferred from PORTC to

PORTD.

;Program 10-1

.INCLUDE "M32DEF.INC"

.ORG

0x0

;location for reset

JMP

MAIN

.ORG

0x16

;loc. for Timer0 over.

JMP

T0_OV_ISR

;----main program for initialization

.ORG

0x100

MAIN:

LDI

R20,HIGH(RAMEND)

OUT

SPH,R20

LDI

R20,LOW(RAMEND)

OUT

SPL,R20

SBI

DDRB,5 ;output

LDI

R20,0

OUT

DDRC, R20

LDI

R20,0xFF

OUT

DDRD, R20

18 int.

Timer

19

init.

LDI

R20,(1<<TOIE0)

OUT

TIMSK,R20

20

SEI

21

LDI

R20,-32 ;value for 4µs

22

OUT

TCNT0,R20

Timer

init.

23

LDI

R20,0x01

24

OUT

TCCR0,R20

25 HERE: IN

R20,PINC

26

OUT

PORTD,R20

27

JMP

HERE

28 ;--------ISR for Timer 0

29 T0_OV_ISR:

30

IN

R16,PORTB

31

LDI

R17,0x20

32

EOR

R16,R17

33

OUT

PORTB,R16

34

RETI

AVR Microcontroller and Embedded System Using Assembly and C: By: Mazidi, Naimi, and Naimi

Edited by : Dr. Irfanud Din , Prof., INHA University in Tashkent.

© 2011 Pearson Higher Education,

Upper Saddle River, NJ 07458. • All Rights Reserved.

9. Timer0 compare match interrupt

using Timer0 and CTC mode generate a square wave on pin PORTB.5, while at thesame time data is being transferred from PORTC to PORTD.

.INCLUDE "M32DEF.INC"

.ORG

0x0

;location for reset

JMP

MAIN

.ORG

0x14

;location for Timer0 compare match

JMP

T0_CM_ISR

;-main program for initialization and keeping CPU busy

.ORG

0x100

MAIN:

LDI

R20,HIGH(RAMEND)

Time (µS)

OUT

SPH,R20

LDI

R20,LOW(RAMEND)

OUT

SPL,R20

HERE:

IN

R20,PINC

LDI

R20,39

OUT

PORTD,R20

OUT

OCR0,R20

;OCR0

=

39

Timer init.

JMP

HERE

LDI

R20,0x09

;--------ISR for Timer 0

OUT

TCCR0,R20

;Start Timer0

T0_CM_ISR:

SBI

DDRB,5

;PB5 as an output

IN

R16,PORTB

LDI

R20,(1<<OCIE0) ;Timer0 compare match

LDI

R17,0x20

Timer int.

OUT

TIMSK,R20

EOR

R16,R17

init.

SEI

;Set I

OUT

PORTB,R16

LDI

R20,0x00

RETI

OUT

DDRC,R20

;make PORTC input

LDI

R20,0xFF

© 2011 Pearson Higher Education,

AVR Microcontroller and Embedded System Using Assembly and C: By: Mazidi, Naimi, and Naimi

OUT

DDRD,R20

;make PORTD output

Edited by : Dr. Irfanud Din , Prof., INHA University in Tashkent.

Upper Saddle River, NJ 07458. • All Rights Reserved.

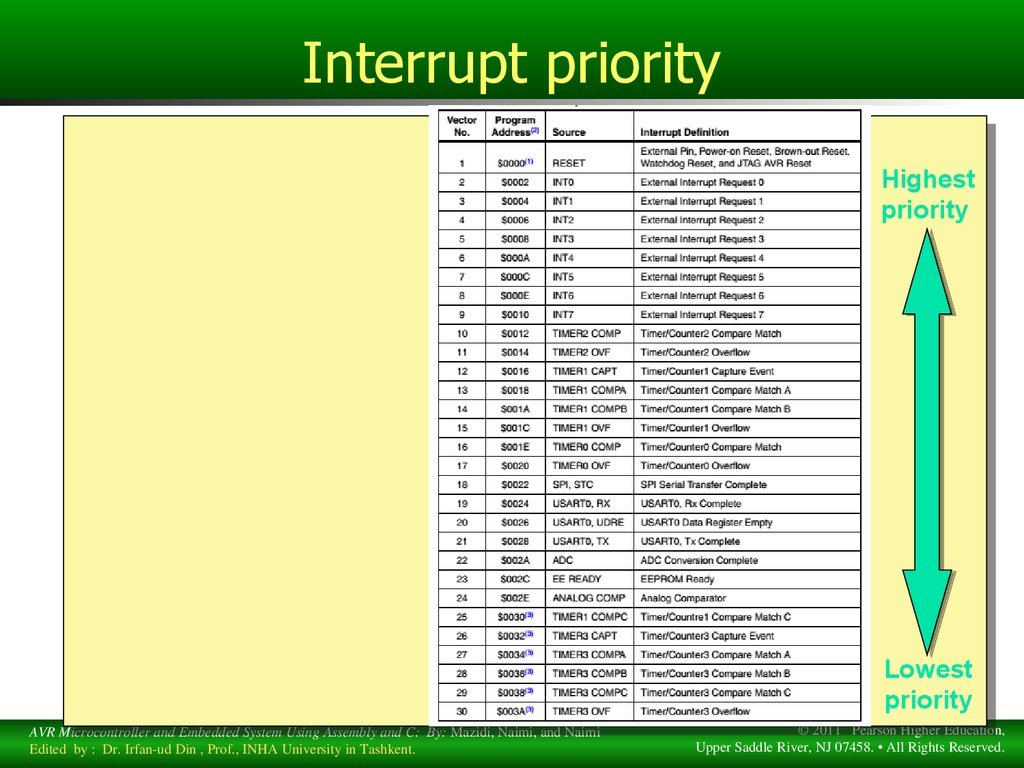

10. Interrupt priority

Highestpriority

Lowest

priority

AVR Microcontroller and Embedded System Using Assembly and C: By: Mazidi, Naimi, and Naimi

Edited by : Dr. Irfanud Din , Prof., INHA University in Tashkent.

© 2011 Pearson Higher Education,

Upper Saddle River, NJ 07458. • All Rights Reserved.

11. Interrupt inside an interrupt

The I flag is cleared when the AVR beginsto execute an ISR. So, interrupts are

disabled.

The I flag is set when RETI is executed.

AVR Microcontroller and Embedded System Using Assembly and C: By: Mazidi, Naimi, and Naimi

Edited by : Dr. Irfanud Din , Prof., INHA University in Tashkent.

© 2011 Pearson Higher Education,

Upper Saddle River, NJ 07458. • All Rights Reserved.

12. Task switching and resource conflict

12

3

4

5

6

7

8

9

10

11

12

13

14

15

16

Does the following program work?

.INCLUDE "M32DEF.INC"

.ORG

0x0

;location for reset

JMP

MAIN

.ORG

0x14

;Timer0 compare match

JMP

T0_CM_ISR

;---------main program-----------------------------.ORG

0x100

MAIN:

LDI

R20,HIGH(RAMEND)

OUT

SPH,R20

LDI

R20,LOW(RAMEND)

OUT

SPL,R20 ;set up stack

SBI

DDRB,5 ;PB5 = output

LDI

R20,160

OUT

OCR0,R20

LDI

R20,0x09

OUT

TCCR0,R20

17

LDI

R20,(1<<OCIE0)

18

OUT

TIMSK,R20

19

SEI

20

LDI

R20,0xFF

21

OUT

DDRC,R20

22

OUT

DDRD,R20

23

LDI

R20, 0

24 HERE: OUT

PORTC,R20

25

INC

R20

26

JMP

HERE

27 ;--------------------------ISR for Timer0

28 T0_CM_ISR:

29

IN

R20,PIND

30

INC

R20

31

OUT

PORTD,R20

32

RETI

AVR Microcontroller and Embedded System Using Assembly and C: By: Mazidi, Naimi, and Naimi

Edited by : Dr. Irfanud Din , Prof., INHA University in Tashkent.

© 2011 Pearson Higher Education,

Upper Saddle River, NJ 07458. • All Rights Reserved.

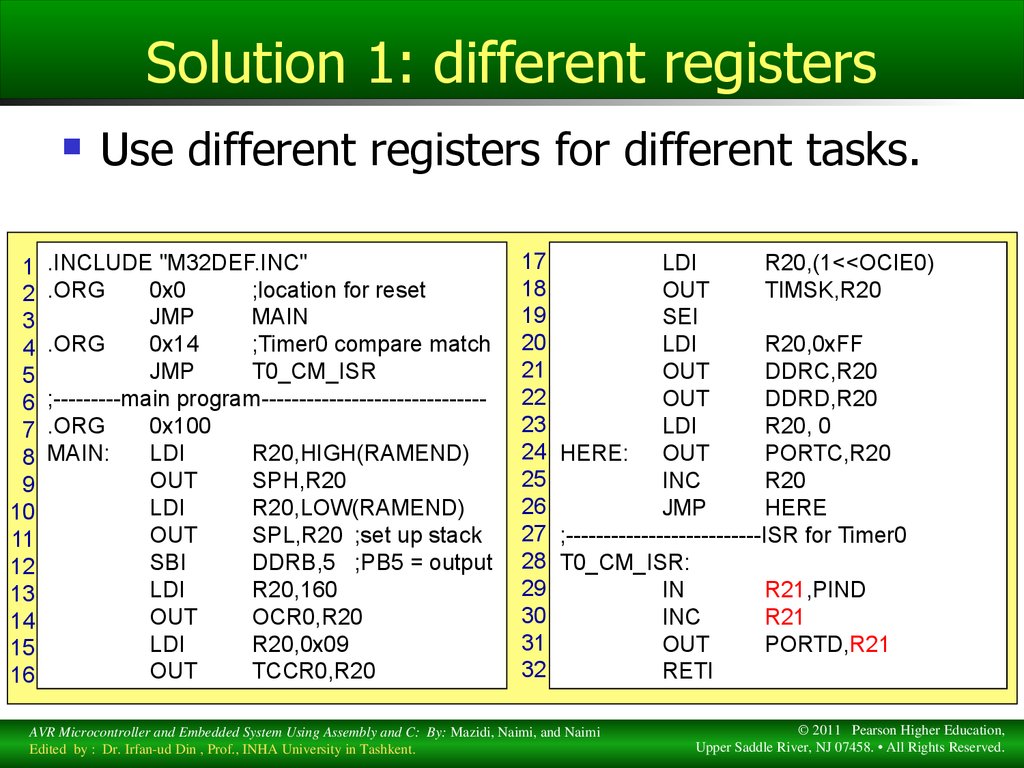

13. Solution 1: different registers

12

3

4

5

6

7

8

9

10

11

12

13

14

15

16

Use different registers for different tasks.

.INCLUDE "M32DEF.INC"

.ORG

0x0

;location for reset

JMP

MAIN

.ORG

0x14

;Timer0 compare match

JMP

T0_CM_ISR

;---------main program-----------------------------.ORG

0x100

MAIN:

LDI

R20,HIGH(RAMEND)

OUT

SPH,R20

LDI

R20,LOW(RAMEND)

OUT

SPL,R20 ;set up stack

SBI

DDRB,5 ;PB5 = output

LDI

R20,160

OUT

OCR0,R20

LDI

R20,0x09

OUT

TCCR0,R20

17

LDI

R20,(1<<OCIE0)

18

OUT

TIMSK,R20

19

SEI

20

LDI

R20,0xFF

21

OUT

DDRC,R20

22

OUT

DDRD,R20

23

LDI

R20, 0

24 HERE: OUT

PORTC,R20

25

INC

R20

26

JMP

HERE

27 ;--------------------------ISR for Timer0

28 T0_CM_ISR:

29

IN

R21,PIND

30

INC

R21

31

OUT

PORTD,R21

32

RETI

AVR Microcontroller and Embedded System Using Assembly and C: By: Mazidi, Naimi, and Naimi

Edited by : Dr. Irfanud Din , Prof., INHA University in Tashkent.

© 2011 Pearson Higher Education,

Upper Saddle River, NJ 07458. • All Rights Reserved.

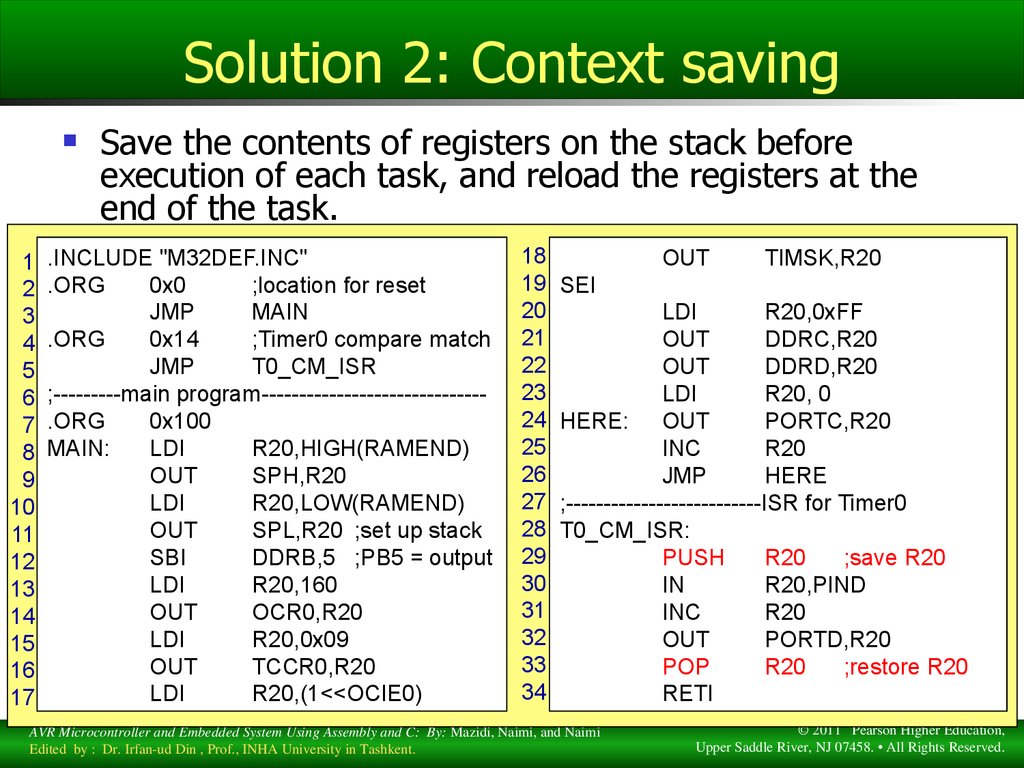

14. Solution 2: Context saving

12

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

Save the contents of registers on the stack before

execution of each task, and reload the registers at the

end of the task.

.INCLUDE "M32DEF.INC"

.ORG

0x0

;location for reset

JMP

MAIN

.ORG

0x14

;Timer0 compare match

JMP

T0_CM_ISR

;---------main program-----------------------------.ORG

0x100

MAIN:

LDI

R20,HIGH(RAMEND)

OUT

SPH,R20

LDI

R20,LOW(RAMEND)

OUT

SPL,R20 ;set up stack

SBI

DDRB,5 ;PB5 = output

LDI

R20,160

OUT

OCR0,R20

LDI

R20,0x09

OUT

TCCR0,R20

LDI

R20,(1<<OCIE0)

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

OUT

TIMSK,R20

SEI

LDI

R20,0xFF

OUT

DDRC,R20

OUT

DDRD,R20

LDI

R20, 0

HERE: OUT

PORTC,R20

INC

R20

JMP

HERE

;--------------------------ISR for Timer0

T0_CM_ISR:

PUSH

R20

;save R20

IN

R20,PIND

INC

R20

OUT

PORTD,R20

POP

R20

;restore R20

RETI

AVR Microcontroller and Embedded System Using Assembly and C: By: Mazidi, Naimi, and Naimi

Edited by : Dr. Irfanud Din , Prof., INHA University in Tashkent.

© 2011 Pearson Higher Education,

Upper Saddle River, NJ 07458. • All Rights Reserved.

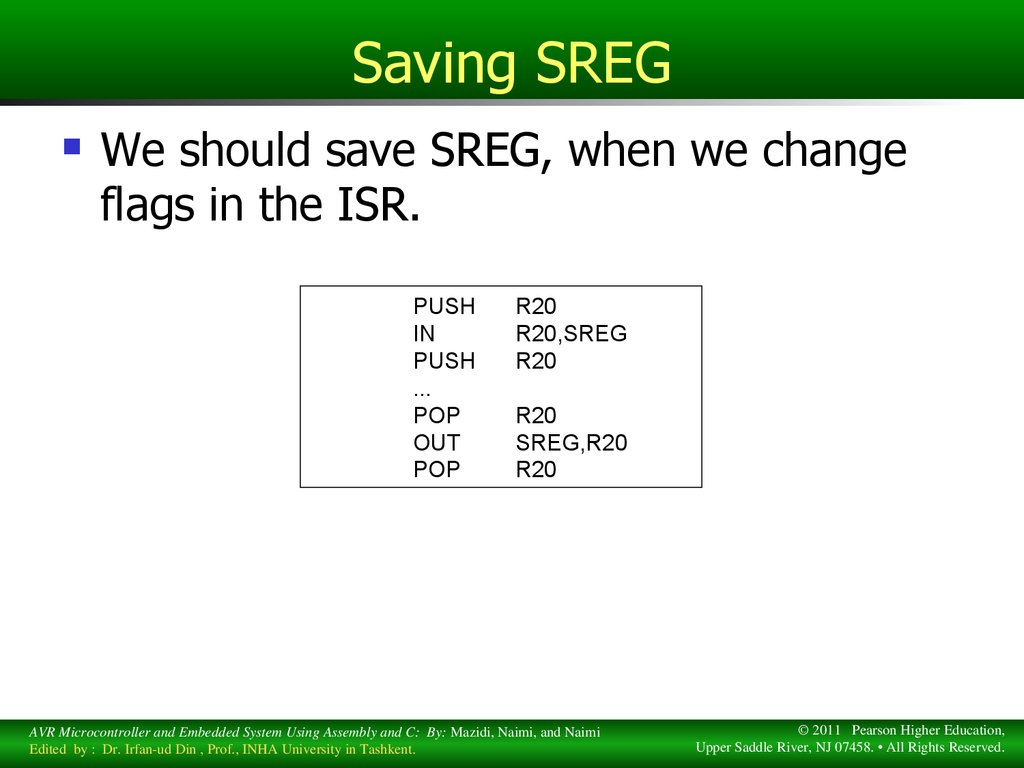

15. Saving SREG

We should save SREG, when we changeflags in the ISR.

PUSH

IN

PUSH

...

POP

OUT

POP

R20

R20,SREG

R20

R20

SREG,R20

R20

AVR Microcontroller and Embedded System Using Assembly and C: By: Mazidi, Naimi, and Naimi

Edited by : Dr. Irfanud Din , Prof., INHA University in Tashkent.

© 2011 Pearson Higher Education,

Upper Saddle River, NJ 07458. • All Rights Reserved.

informatics

informatics english

english