Similar presentations:

Интегральные микросхемы (часть 1)

1.

Интегральные микросхемыВесна 2016

Лекция 9

Интегральные микросхемы ( часть 1)

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

1

2.

Интегральные микросхемыВесна 2016

Интегральная микросхема –

микроэлектронное изделие, выполняющее

определённые функции преобразования,

хранения, обработки информации и

имеющая высокую плотность упаковки

электрически соединенных между собой

элементов и компонентов и представляющая

единое целое с точки зрения требований к

испытаниям, приемке и эксплуатации.

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

2

3.

Интегральные микросхемыВесна 2016

1952 — Джэффри Даммер, идея интегральной

схемы («брусок без проводов»)

1958 — Джэк Килби, первая интегральная схема

(пять элементов, генератор)

2000 — Джэк Килби, Нобелевская премия за

создание интегральной схемы

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

3

4.

Интегральные микросхемыВесна 2016

Серия ИМС – набор типов ИМС,

выполняющих различные функции и

имеющих единое конструктивнотехнологическое исполнение

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

4

5.

Интегральные микросхемыВесна 2016

Интегральные микросхемы

Классификация

По технологии

По

функциональному

назначению

Цифровые

изготовления

По

конструктивному

исполнению

Аналоговые

ТТЛ

КМОП

Комбинированные

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

Комбинированные

5

6.

Цифровые интегральные схемыВесна 2016

Статические параметры ЦИС

-

Входное

напряжение

логической

(минимальное)

-

Входное

единицы

U1ВХ (VIH);

напряжение

(максимальное)

логического

нуля

U0ВХ (VIL);

- Выходное напряжение логической единицы

(минимальное)

-

Выходное

U1ВЫХ(VOH);

напряжение

(максимальное)

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

логического

нуля

U0ВЫХ(VOL);

6

7.

Цифровые интегральные схемыВесна 2016

Статические параметры ЦИС

- Логический перепад UЛ =U1 - U0

- Пороговое напряжение элемента Uпор (VIK);

-Мощность потребления в состоянии

логического

“0” Р0П

-Мощность потребления в состоянии

логической “1” Р1П

-Средняя мощность потребления

РП.СР=(Р0П + Р1П)/2

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

7

8.

Цифровые интегральные схемыВесна 2016

Поля допусков входных и выходных

сигналов ИМС ТТЛ-технологии

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

8

9.

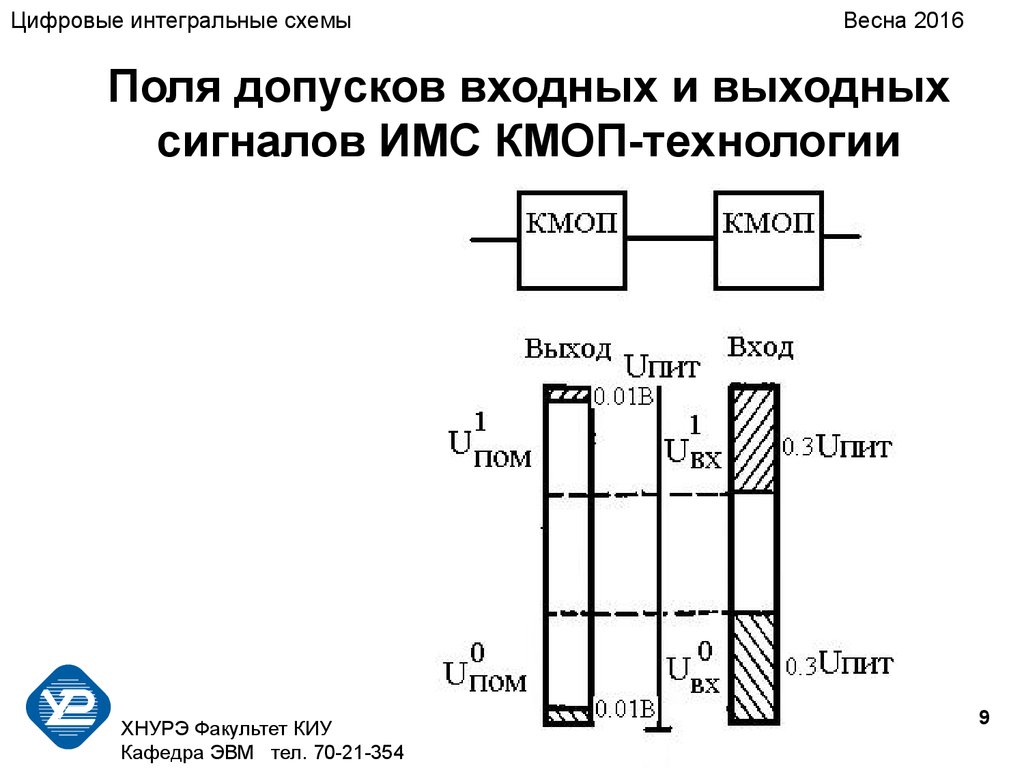

Цифровые интегральные схемыВесна 2016

Поля допусков входных и выходных

сигналов ИМС КМОП-технологии

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

9

10.

Цифровые интегральные схемыВесна 2016

Статические параметры ЦИС

- Напряжение источника питания

(указывается номинал, отклонение от

номинала, величина пульсации) Uпит (VCC)

(VDD);

- Выходной ток логической “1” I1ВЫХ (IOH);

- Выходной ток логического “0” I0ВЫХ(IOL);

- Входной ток логической “1” I1ВХ(IIH);

- Входной ток логического “0” I0ВХ (IIL);

- Ток потребления IПОТ (ICC);

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

10

11.

Цифровые интегральные схемыВесна 2016

Статические параметры ЦИС

-Входное сопротивление ЛЭ при UВХ=U0

R

1

R ВХ

-- Входное сопротивление ЛЭ при UВХ=U1

-- Выходное сопротивление ЛЭ при UВЫХ=U

0

-- Выходное сопротивление ЛЭ при UВЫХ=U

1

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

0

ВХ

R

R

0

ВЫХ

1

ВЫХ

11

12.

Цифровые интегральные схемыВесна 2016

Статические параметры ЦИС

0

- Диапазон рабочих температур tmin, tmax, C;

- Коэффициент разветвления по выходу Краз.

- Коэффициент объединения по входу Коб.

Краз=3

ЦИС

ЦИС

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

ЦИС

ЦИС

12

13.

Цифровые интегральные схемыВесна 2016

Передаточная характеристика Uвых=f(Uвх)

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

13

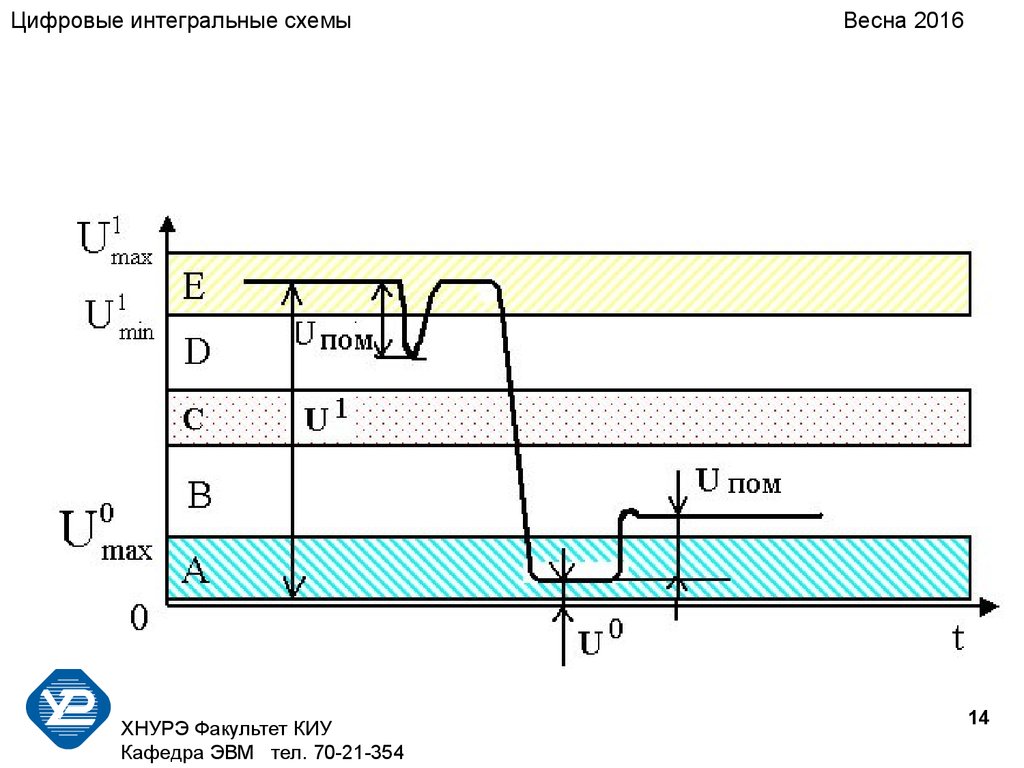

14.

Цифровые интегральные схемыХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

Весна 2016

14

15.

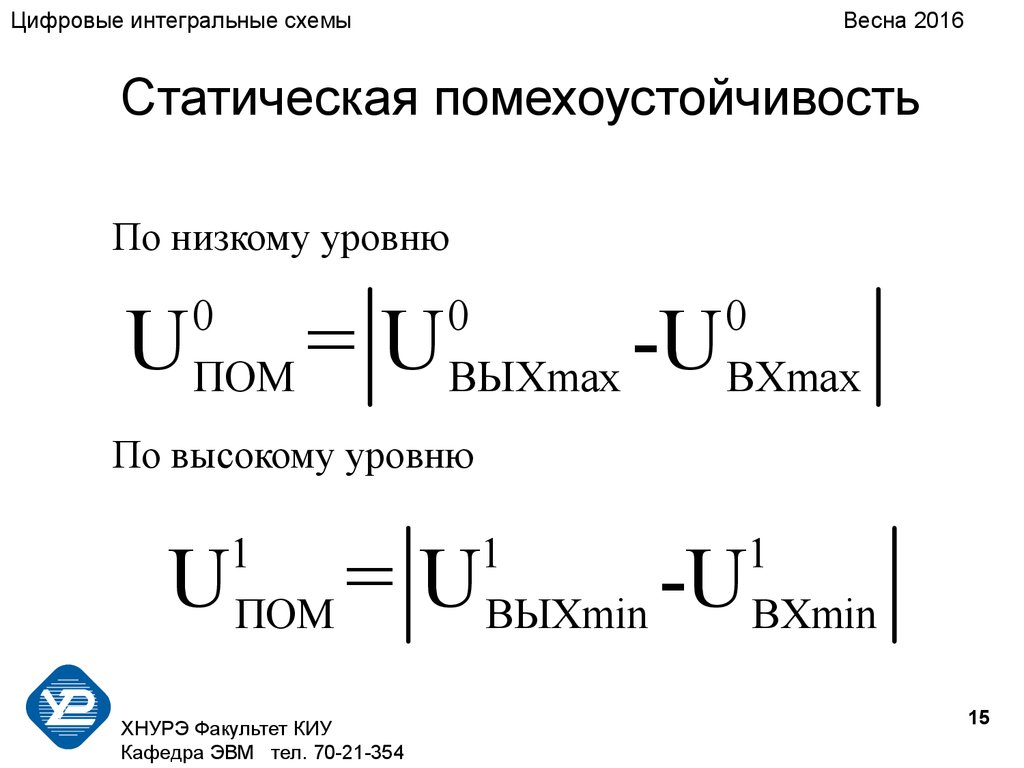

Цифровые интегральные схемыВесна 2016

Статическая помехоустойчивость

По низкому уровню

U

0

ПОМ

=U

0

ВЫХmax

-U

0

ВХmax

По высокому уровню

1

ПОМ

U

1

ВЫХmin

=U

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

-U

1

ВХmin

15

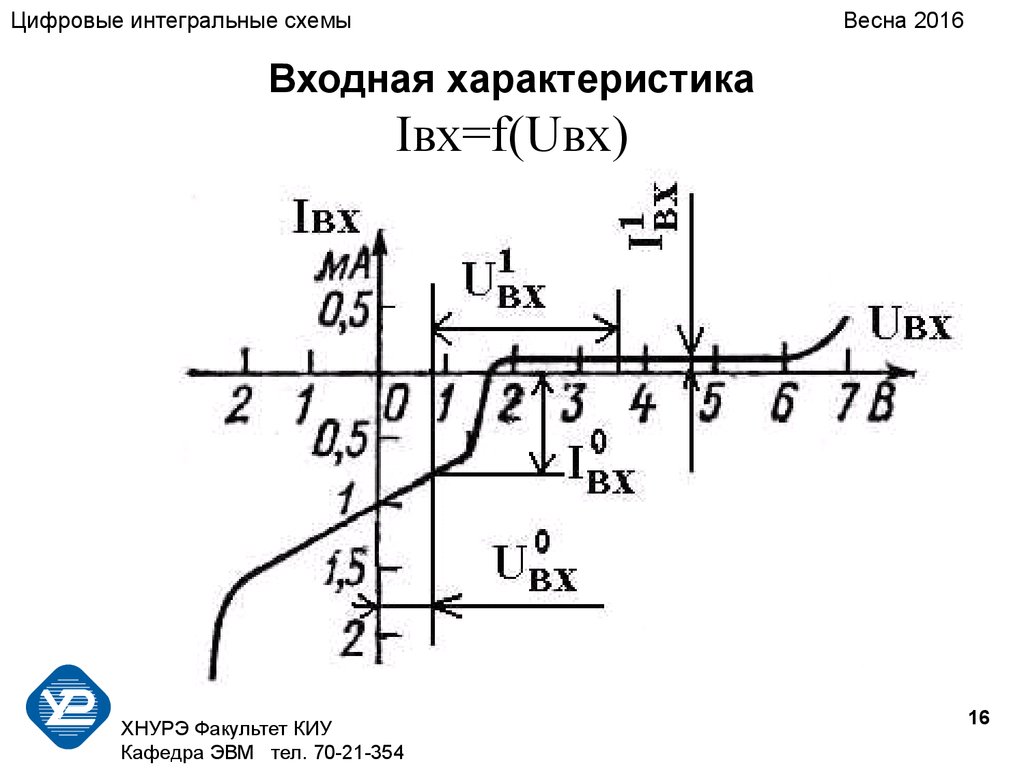

16.

Цифровые интегральные схемыВесна 2016

Входная характеристика

Iвх=f(Uвх)

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

16

17.

Цифровые интегральные схемыВесна 2016

Выходная характеристика

Iвых=f(Uвых)

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

17

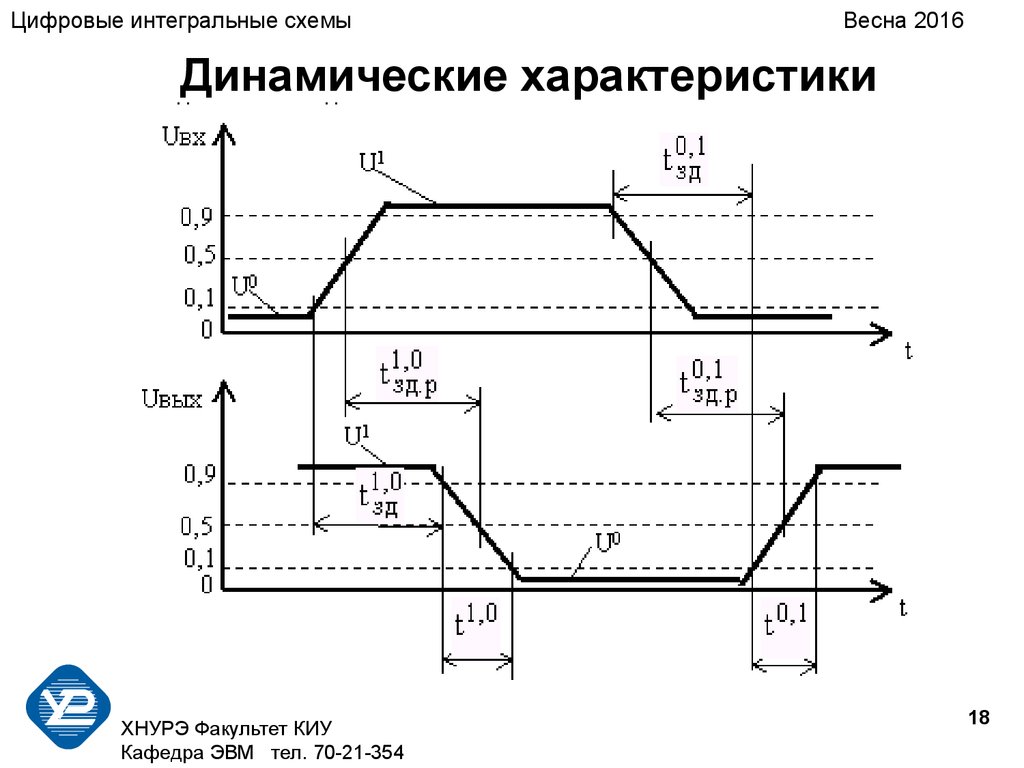

18.

Цифровые интегральные схемыВесна 2016

Динамические характеристики

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

18

19.

Цифровые интегральные схемыВесна 2016

Динамические параметры

- время перехода из состояния логической

«1» в состояние логического «0»

- время перехода из состояния логического

«0» в состояние логической «1»

- время задержки включения

- время задержки выключения

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

19

20.

Цифровые интегральные схемыВесна 2016

Динамические параметры

- время задержки распространения сигнала

при включении

- время задержки распространения сигнала

при выключении

- среднее время задержки распространения

сигнала

- рабочая частота переключения

(максимальная рабочая частота) fп

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

20

21.

Цифровые интегральные схемыВесна 2016

Динамические параметры

Предельно допустимая емкость нагрузки СН, Ф

Предельно допустимая индуктивность нагрузки

LН, Гн

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

21

22.

Интегральные микросхемыВесна 2016

Степень интеграции –

показатель сложности микросхемы,

характеризуемый числом

содержащихся в ней элементов и

компонентов K=lgN

K 2 – малая степень интеграции

2<K 4 средняя степень интеграции (СИС)

4<K 5 большая степень интеграции (БИС)

K>5 сверхбольшая (СБИС)

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

22

23.

Интегральные микросхемыВесна 2016

Элемент – часть ИС, в которой реализуется

функция какого-либо радиоэлемента

(транзистора, диода, резистора, конденсатора

и т.д.) и которую нельзя отделить от кристалла

и рассматривать как самостоятельное изделие

с точки зрения измерения параметров,

упаковки и эксплуатации.

Компонент – часть ИС, с помощью которой

можно реализовать функцию какого-либо

радиоэлемента.

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

23

24.

Интегральные микросхемыВесна 2016

Подложка ИС – заготовка, предназначенная

для изготовления на ней элементов

гибридных и плёночных ИС, межэлементных

и межкомпонентных соединений, контактных

площадок.

Плата ИС – часть подложки (или вся

подложка), на поверхности которой

выполнены плёночные элементы,

контактные площадки и линии соединений

элементов и компонентов.

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

24

25.

Интегральные микросхемыВесна 2016

Полупроводниковая пластина – заготовка,

используемая для создания ИС (иногда

пластина с выполненными на ней

элементами).

Кристалл ИС – часть пластины,

полученная после её резки, когда на одной

пластине выполнено несколько

функциональных устройств.

Вывод ИМС – проводник, соединенный

электрически с контактной площадкой

кристалла и механически с его поверхностью

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

25

26.

Интегральные микросхемыВесна 2016

Контактные площадки –

металлизированные участки на кристалле,

предназначенные для присоединения к

выводам корпуса ИС.

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

26

27.

Интегральные микросхемыВесна 2016

Сформированные микросхемы на кристалле

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

27

28.

Интегральные микросхемыВесна 2016

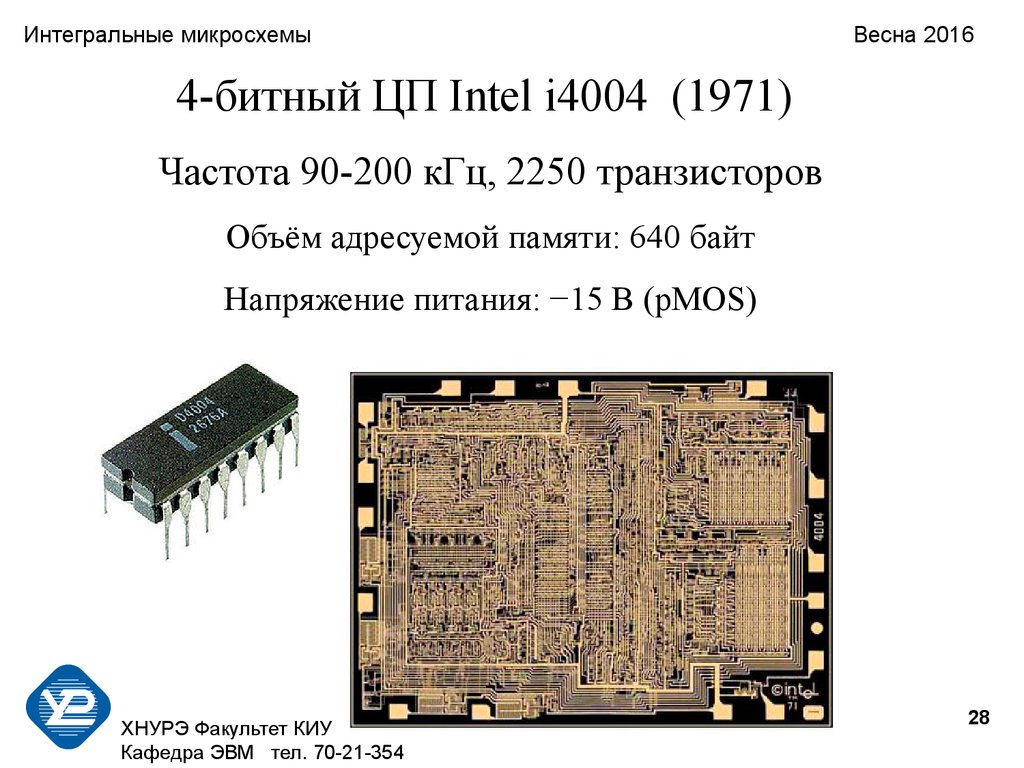

4-битный ЦП Intel i4004 (1971)

Частота 90-200 кГц, 2250 транзисторов

Объём адресуемой памяти: 640 байт

Напряжение питания: −15 В (pMOS)

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

28

29.

Интегральные микросхемыВесна 2016

Корпус – часть конструкции ИС, которая

защищает кристалл от внешних

воздействий. Типы и размеры корпусов, а

также число вводов и их расположение

стандартизированы. На корпусе имеется

“ключ” или корпус выполняется

несимметричной формы, что эквивалентно

ключу, который необходим для правильного

нахождения выводов микросхемы.

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

29

30.

Интегральные микросхемыВесна 2016

Примеры корпусов микросхем

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

30

31.

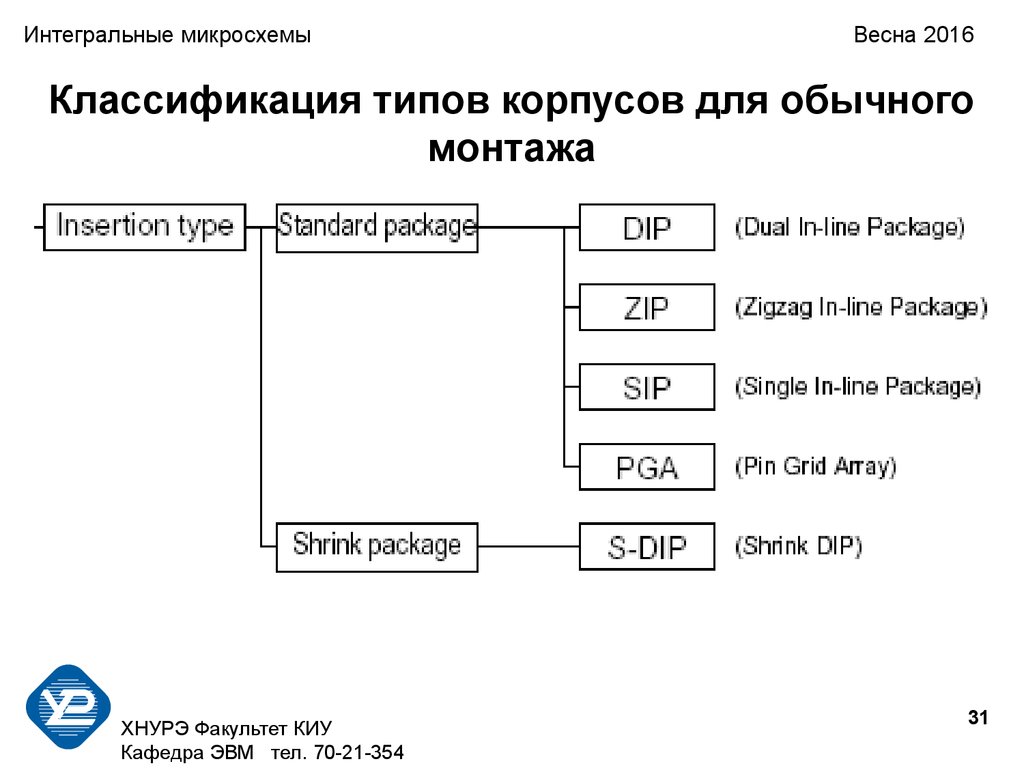

Интегральные микросхемыВесна 2016

Классификация типов корпусов для обычного

монтажа

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

31

32.

Интегральные микросхемыВесна 2016

Классификация типов корпусов для

поверхностного монтажа

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

32

33.

Интегральные микросхемыВесна 2016

DIP (Dual In-line Package)

Выводы расположены перпендикулярно плоскости корпуса

вдоль двух противоположных сторон.

Корпус может быть изготовлен из ударопрочного пластика

(PDIP) или из специальной керамики (CDIP).

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

33

34.

Интегральные микросхемыВесна 2016

SDIP (Shrink DIP)

Корпус типа DIP с уменьшенным шагом выводов

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

34

35.

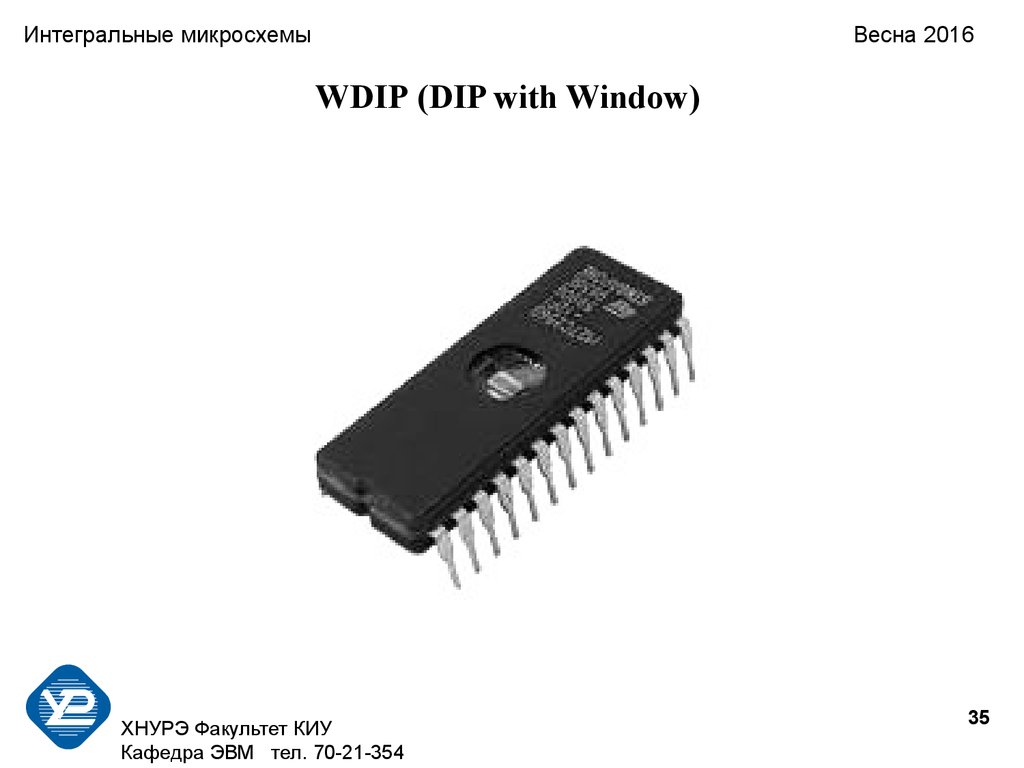

Интегральные микросхемыВесна 2016

WDIP (DIP with Window)

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

35

36.

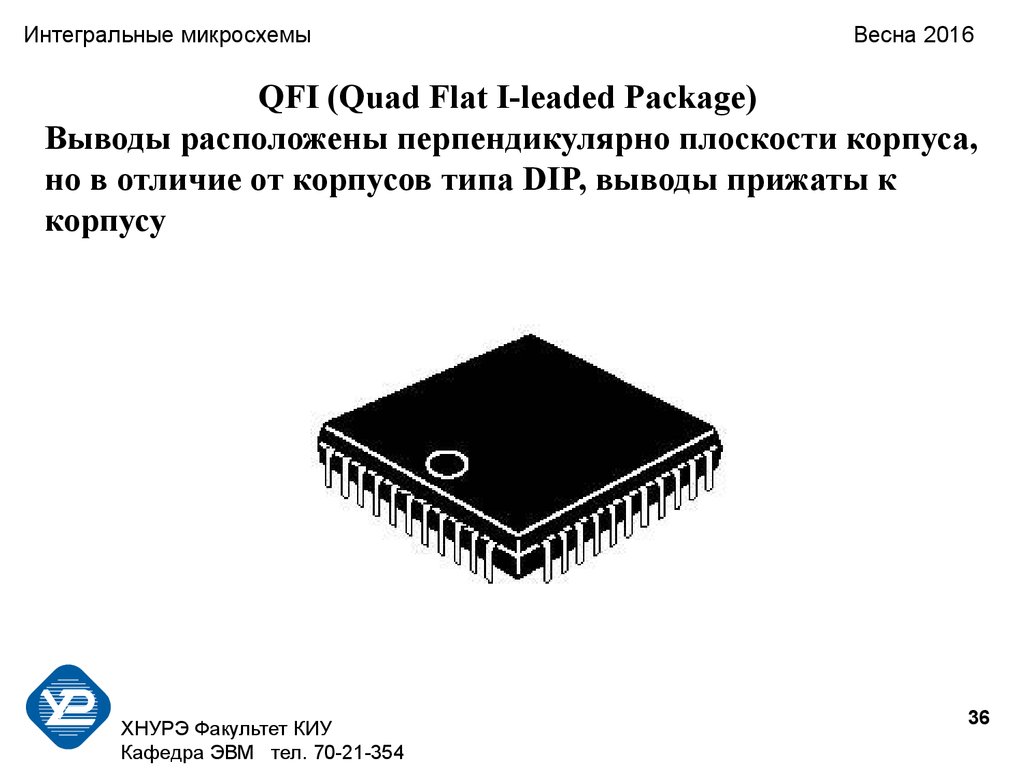

Интегральные микросхемыВесна 2016

QFI (Quad Flat I-leaded Package)

Выводы расположены перпендикулярно плоскости корпуса,

но в отличие от корпусов типа DIP, выводы прижаты к

корпусу

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

36

37.

Интегральные микросхемыВесна 2016

SIP (Single In-line Package)

Выводы расположены вдоль одной стороны в направлении,

совпадающим с плоскостью корпуса

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

37

38.

Интегральные микросхемыВесна 2016

HSIP (SIP with Heat Sink)

Корпус типа SIP с металлическим теплоотводом

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

38

39.

Интегральные микросхемыВесна 2016

ZIP (Zigzag In-line Package)

Направление выводов совпадает с плоскостью корпуса.

Выводы расположены с одной стороны по линии "зиг-заг"

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

39

40.

Интегральные микросхемыВесна 2016

ИМС в корпусах для поверхностного монтажа (Surface

mount type)

SOP(Small Outline Package)

Корпус с двусторонним расположением G-образных

выводов

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

40

41.

Интегральные микросхемыВесна 2016

SSOP (Shrink SOP)

Корпус типа SOP с уменьшенным шагом выводов

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

41

42.

Интегральные микросхемыВесна 2016

TSOP(Thin Small Outline Package)

От корпуса SOP отличается уменьшенной толщиной

корпуса

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

42

43.

Интегральные микросхемыВесна 2016

TSSOP (Thin Shrink Small Outline Package)

От корпуса SOP отличается уменьшенной толщиной

корпуса и уменьшенным шагом выводов

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

43

44.

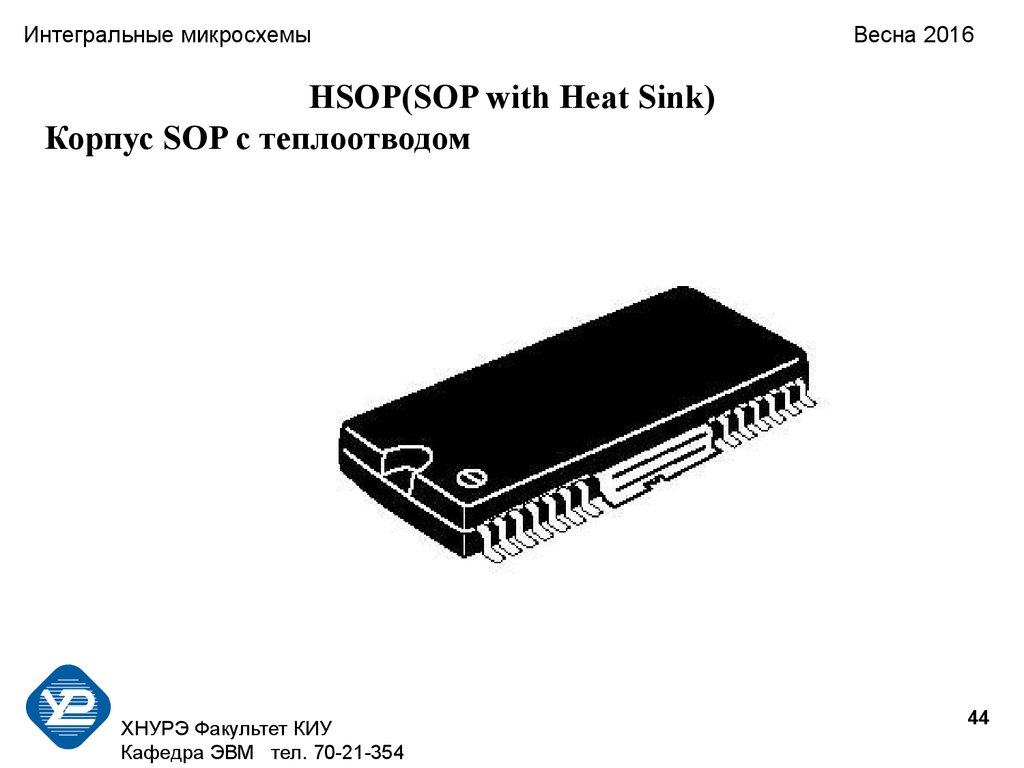

Интегральные микросхемыВесна 2016

HSOP(SOP with Heat Sink)

Корпус SOP с теплоотводом

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

44

45.

Интегральные микросхемыВесна 2016

PSOP (Power Small Outline Package)

Корпус SOP с теплоотводом в виде металлической

пластины под корпусом ИМС

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

45

46.

Интегральные микросхемыВесна 2016

РQFP (Plastic Quad Flat Packagе)

Корпус прямоугольной формы с G-образными выводами,

расположенными по четырем сторонам корпуса

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

46

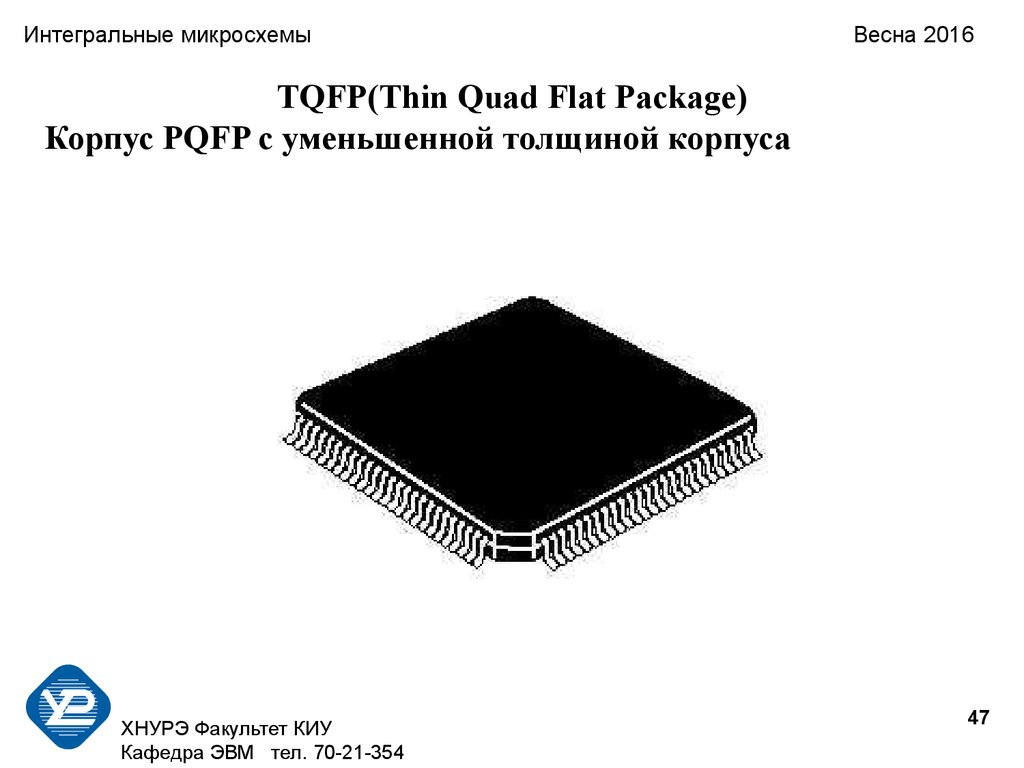

47.

Интегральные микросхемыВесна 2016

TQFP(Thin Quad Flat Package)

Корпус РQFP с уменьшенной толщиной корпуса

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

47

48.

Интегральные микросхемыВесна 2016

Корпуса J-lead package

Корпуса этой группы имеют загнутые под плоскость

корпуса выводы (отсюда символ J в названии)

SOJ (Small Outline J-leaded Package)

Корпуса с двусторонним расположением выводов

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

48

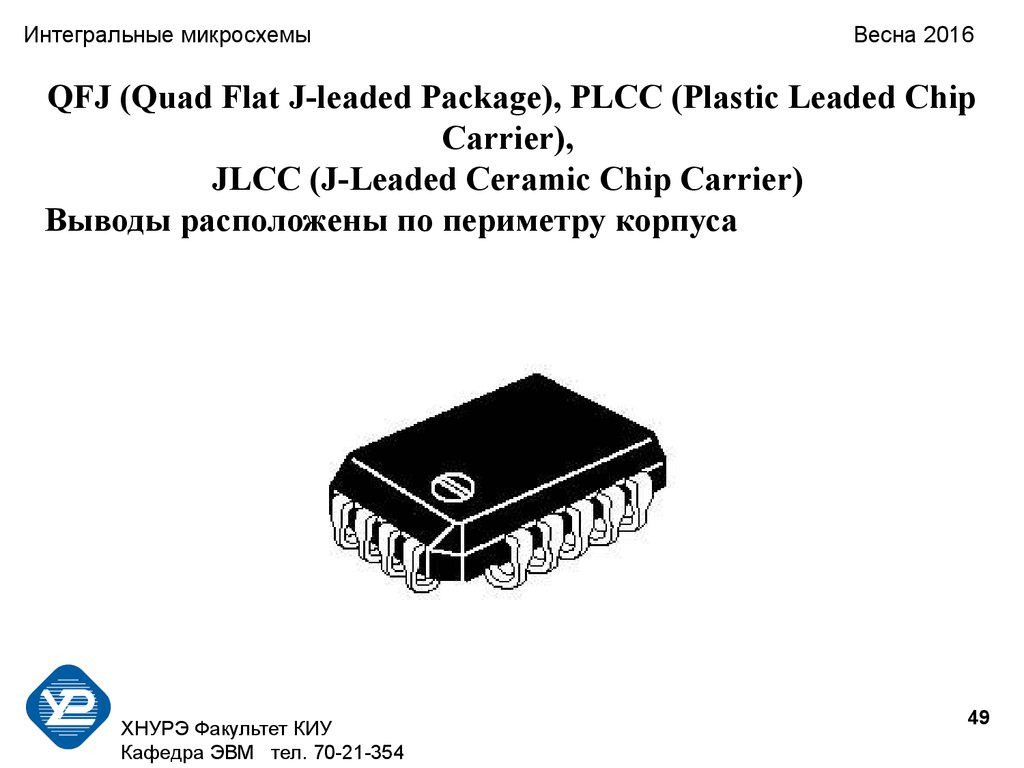

49.

Интегральные микросхемыВесна 2016

QFJ (Quad Flat J-leaded Package), PLCC (Plastic Leaded Chip

Carrier),

JLCC (J-Leaded Ceramic Chip Carrier)

Выводы расположены по периметру корпуса

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

49

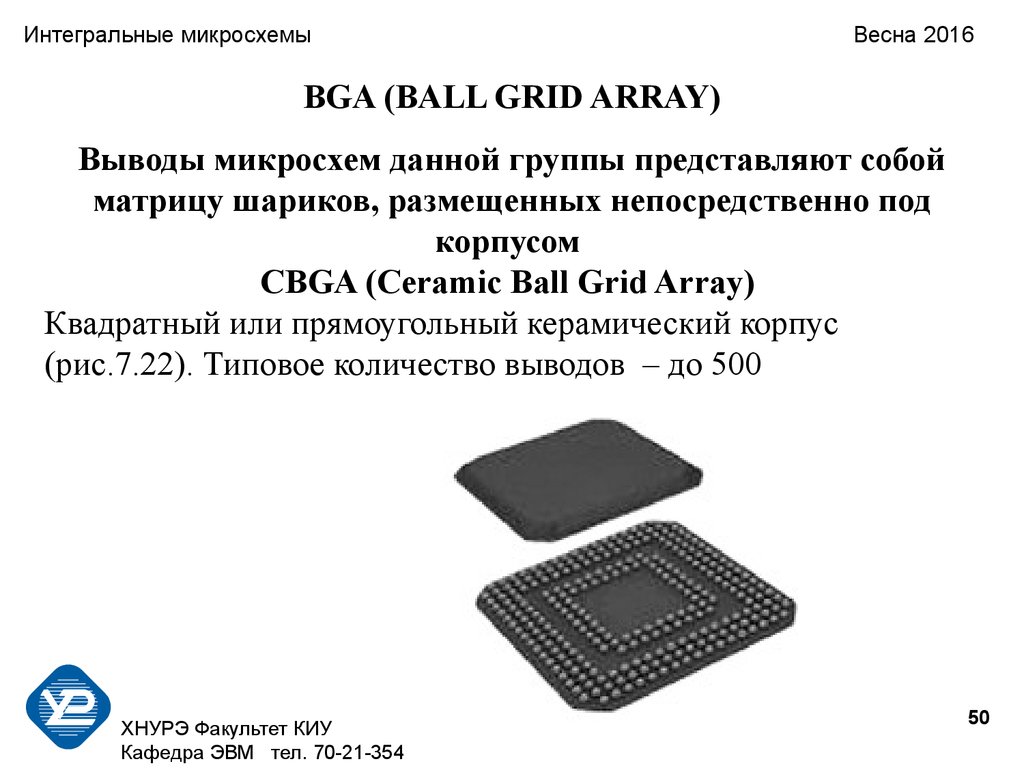

50.

Интегральные микросхемыВесна 2016

BGA (BALL GRID ARRAY)

Выводы микросхем данной группы представляют собой

матрицу шариков, размещенных непосредственно под

корпусом

CBGA (Ceramic Ball Grid Array)

Квадратный или прямоугольный керамический корпус

(рис.7.22). Типовое количество выводов – до 500

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

50

51.

Интегральные микросхемыВесна 2016

CPGA (Ceramic Pin Grid Array)

Керамический квадратный или прямоугольный корпус с

жесткими выводами, расположенными на нижней стороне

корпуса, перпендикулярно плоскости корпуса

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

51

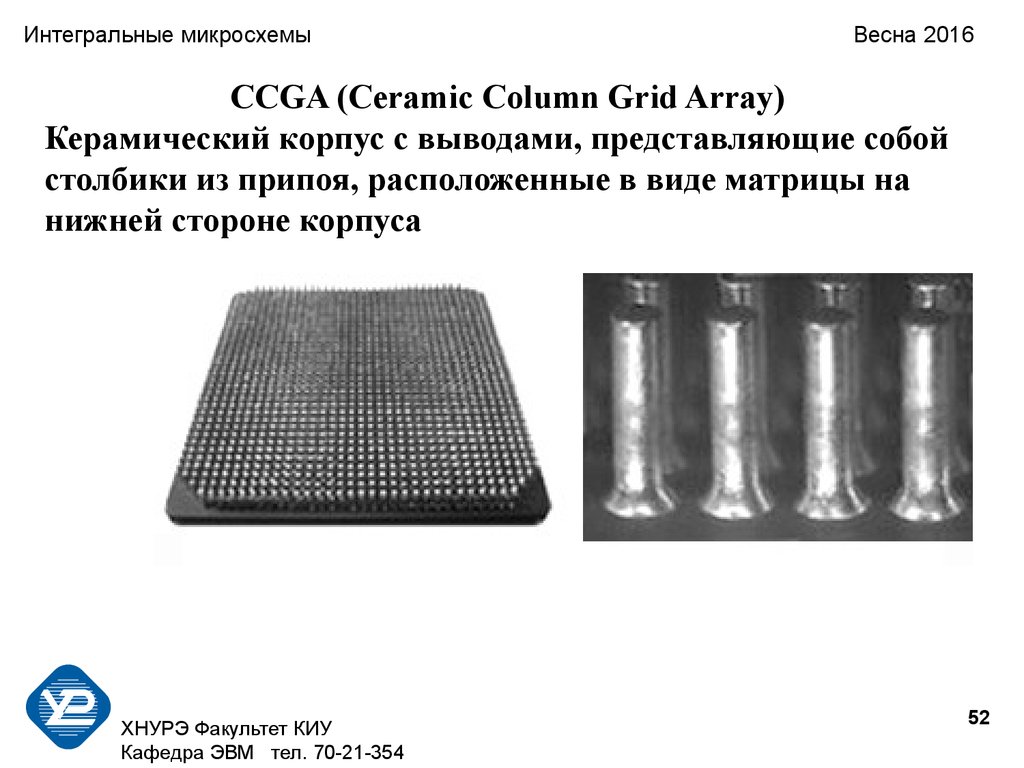

52.

Интегральные микросхемыВесна 2016

CCGA (Ceramic Column Grid Array)

Керамический корпус с выводами, представляющие собой

столбики из припоя, расположенные в виде матрицы на

нижней стороне корпуса

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

52

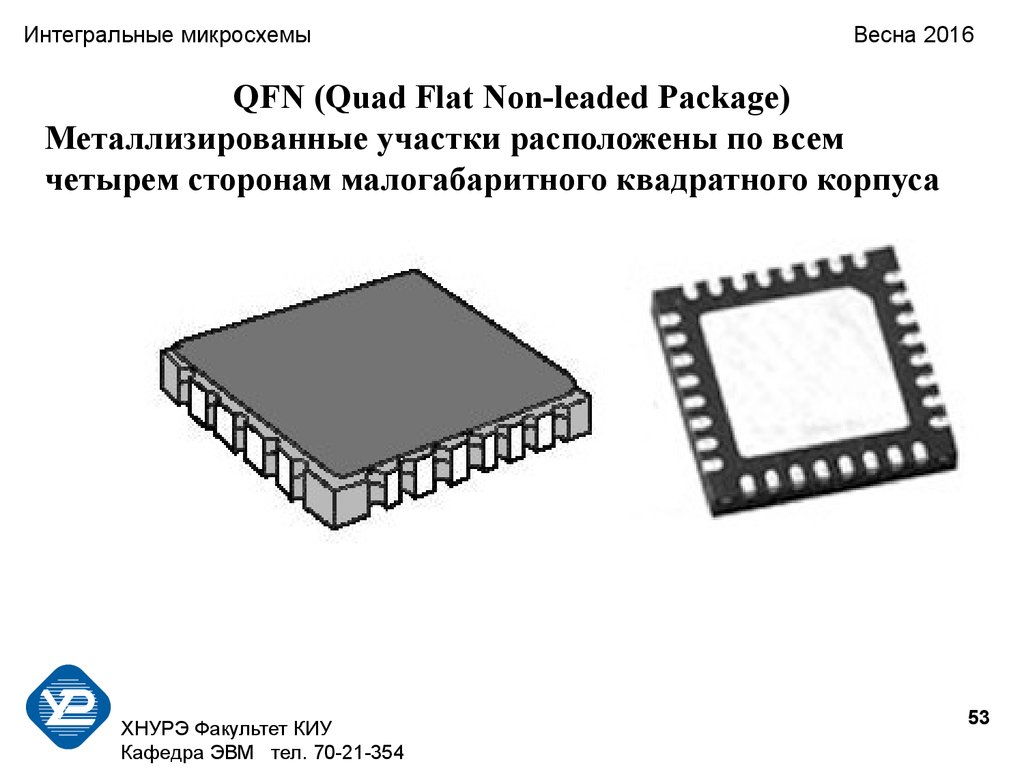

53.

Интегральные микросхемыВесна 2016

QFN (Quad Flat Non-leaded Package)

Металлизированные участки расположены по всем

четырем сторонам малогабаритного квадратного корпуса

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

53

54.

Интегральные микросхемыВесна 2016

PQFN (Power Quad Flat No Leads)

Прямоугольный или квадратный корпус с теплоотводом на

нижней стороне

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

54

55.

Интегральные микросхемыВесна 2016

DFN (Dual Flat No Leads)

Металлизированные участки расположены по двум

длинным сторонам корпуса

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

55

56.

Интегральные микросхемыВесна 2016

Диффузионный резистор п/п ИМС

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

56

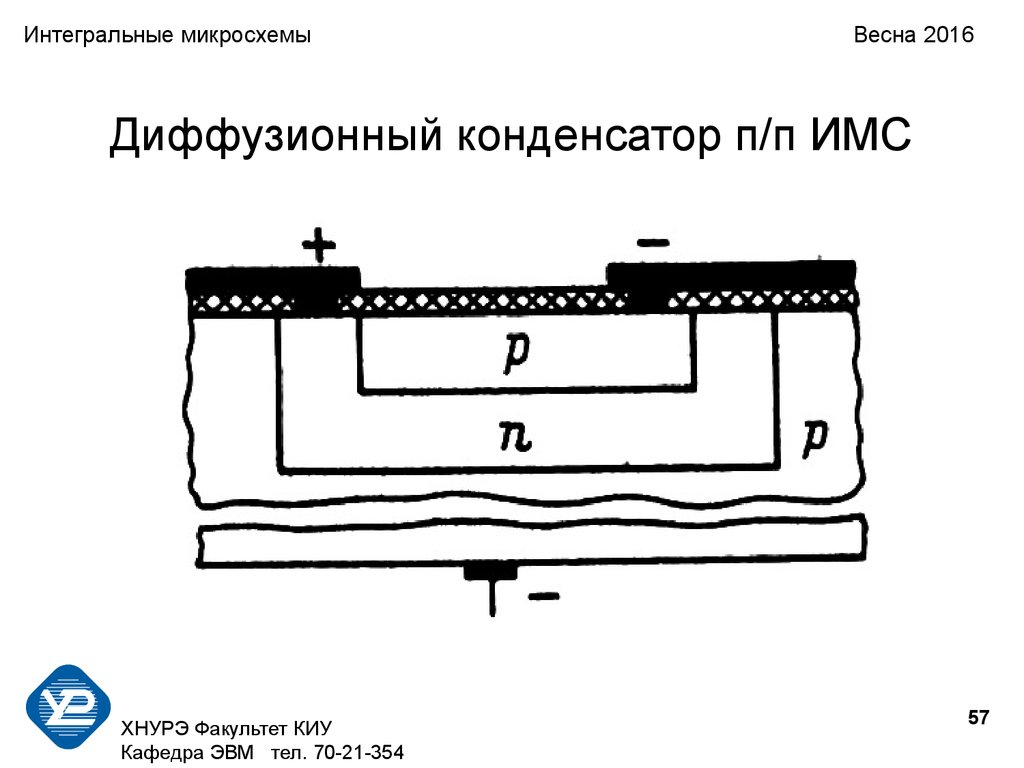

57.

Интегральные микросхемыВесна 2016

Диффузионный конденсатор п/п ИМС

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

57

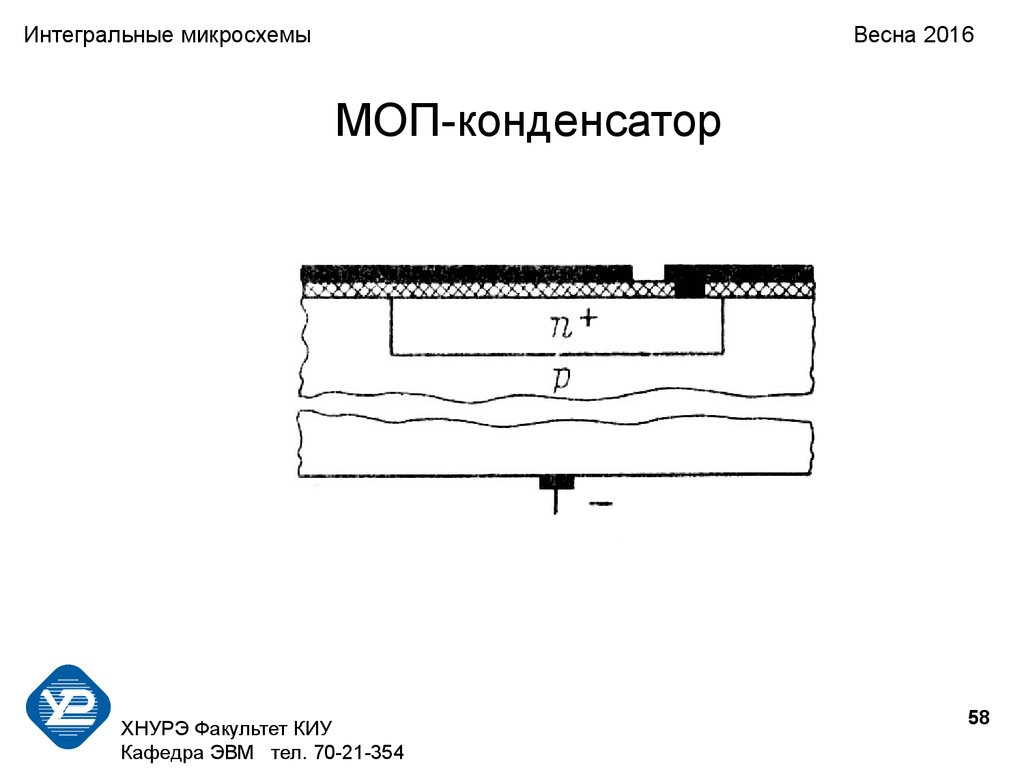

58.

Интегральные микросхемыВесна 2016

МОП-конденсатор

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

58

59.

Интегральные микросхемыВесна 2016

Вертикальный транзистор типа n-p-n

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

59

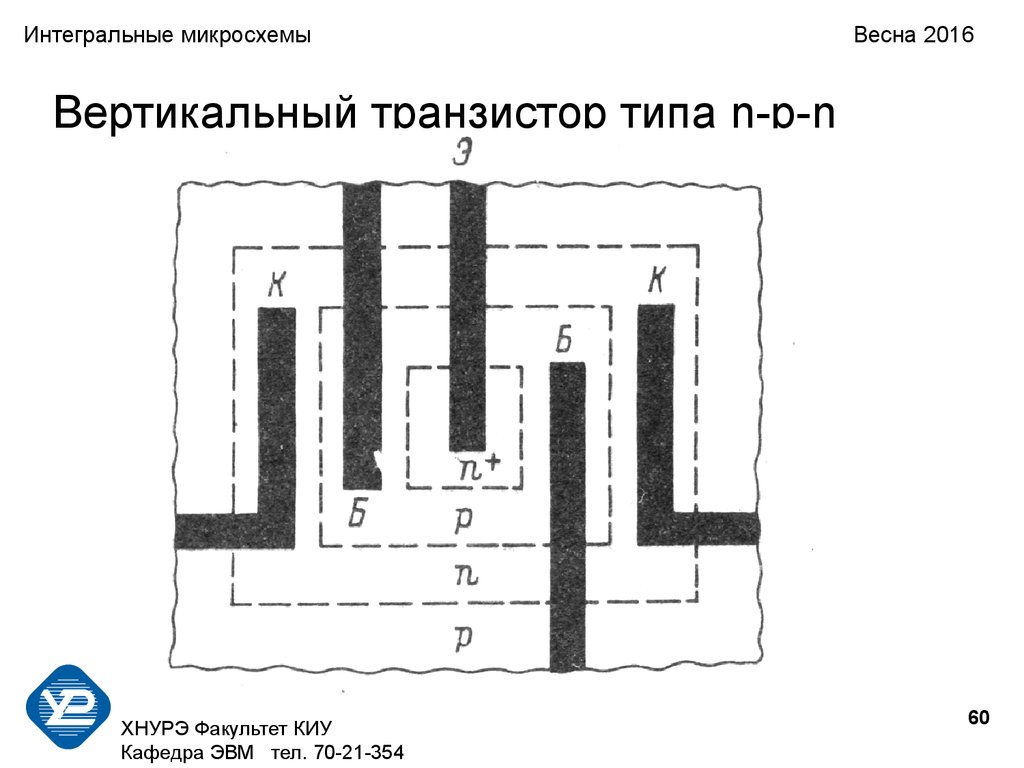

60.

Интегральные микросхемыВесна 2016

Вертикальный транзистор типа n-p-n

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

60

61.

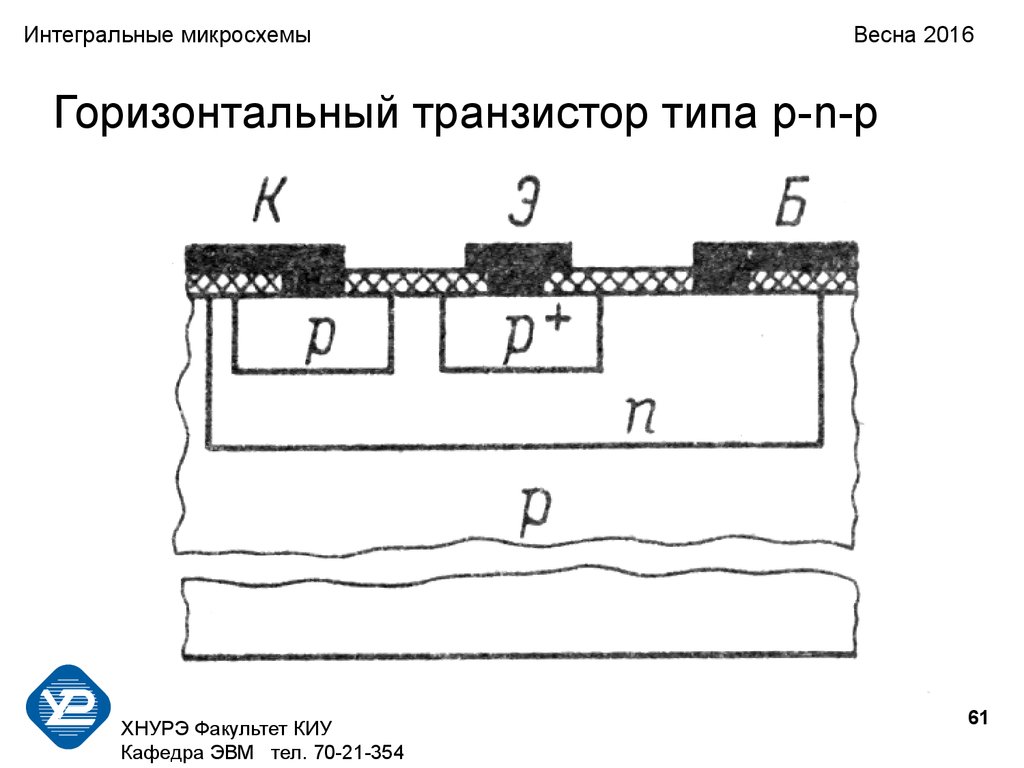

Интегральные микросхемыВесна 2016

Горизонтальный транзистор типа p-n-p

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

61

62.

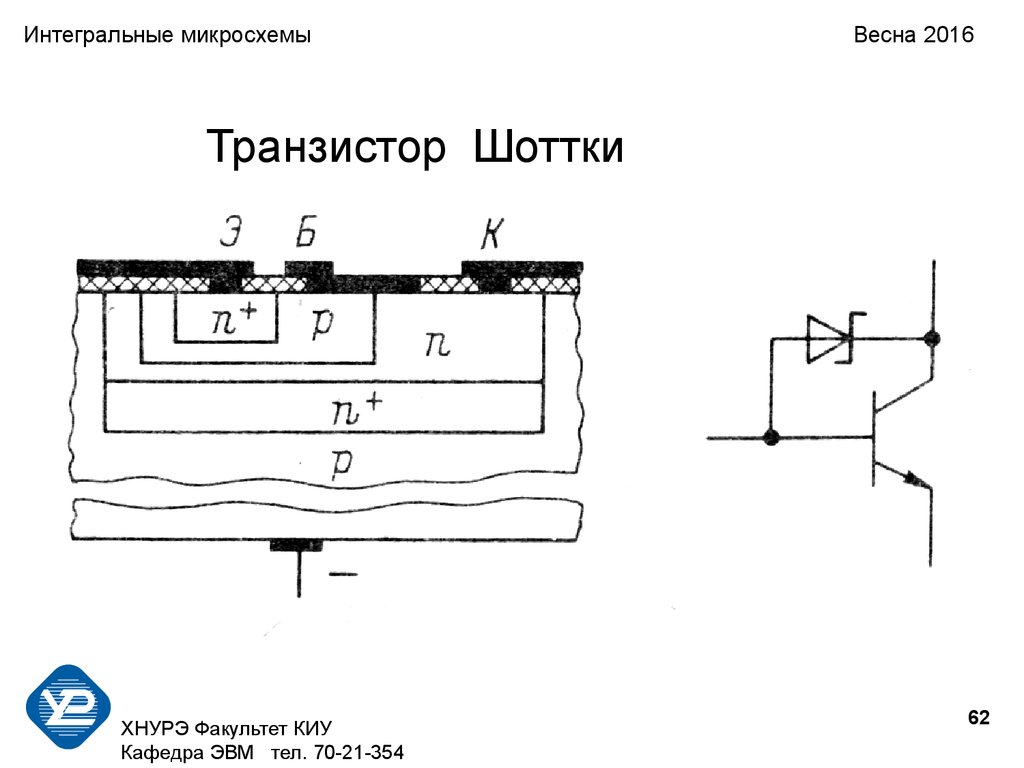

Интегральные микросхемыВесна 2016

Транзистор Шоттки

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

62

63.

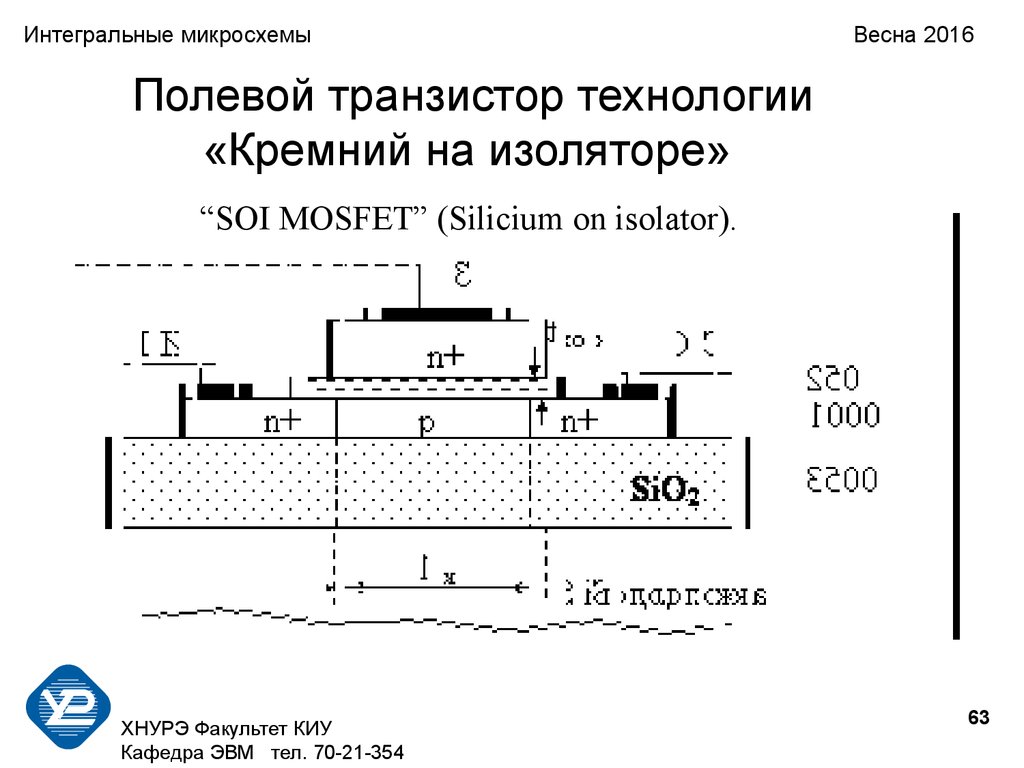

Интегральные микросхемыВесна 2016

Полевой транзистор технологии

«Кремний на изоляторе»

“SOI MOSFET” (Silicium on isolator).

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

63

64.

Интегральные микросхемыВесна 2016

Задание для самостоятельной работы

1. Система условных обозначений

отечественных ИМС

2. Система условных обозначений зарубежных

фирм (на примере одной фирмы)

ХНУРЭ Факультет КИУ

Кафедра ЭВМ тел. 70-21-354

64

electronics

electronics