Similar presentations:

Внутрення Структура МПУ

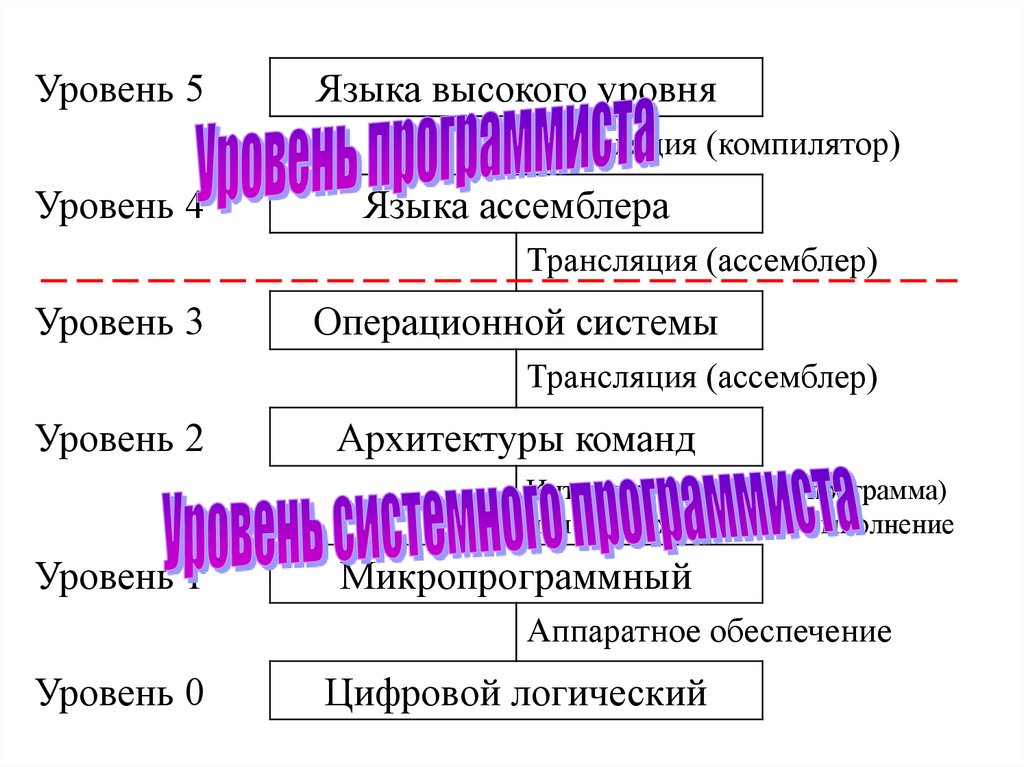

1. Понятие архитектуры ЭВМ

Архитектура ЭВМ какраспределение функций,

реализуемых системой, между её

уровнями

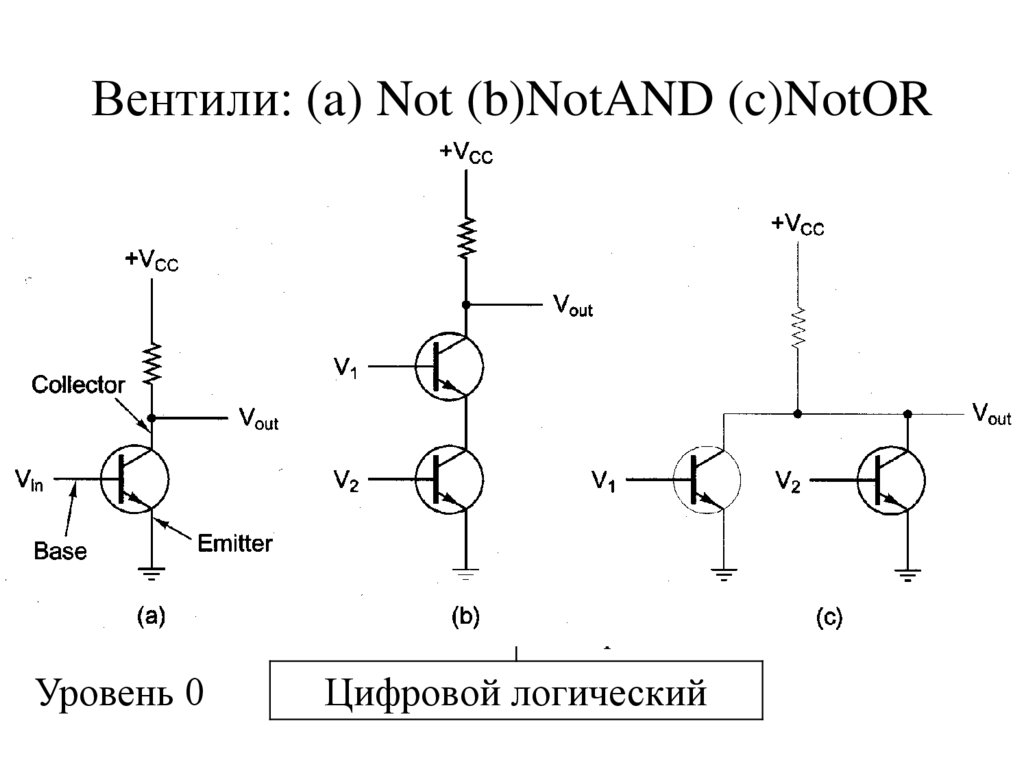

2. Вентили: (a) Not (b)NotAND (c)NotOR

Уровень5

Языка

уровня (c)NotOR

Вентили:

(a)

Notвысокого

(b)NotAND

Трансляция (компилятор)

Уровень 4

Языка ассемблера

Трансляция (ассемблер)

Уровень 3

Операционной системы

Трансляция (ассемблер)

Уровень 2

Архитектуры команд

Интерпретация (микропрограмма)

или непосредственное выполнение

Уровень 1

Микропрограммный

Аппаратное обеспечение

Уровень 0

Цифровой логический

3. Базовые вентили

Уровень 5Языка

высокого

уровня

Базовые

вентили

Трансляция (компилятор)

Уровень 4

Языка ассемблера

Трансляция (ассемблер)

Уровень 3

Операционной системы

Трансляция (ассемблер)

Уровень 2

Архитектуры команд

Интерпретация (микропрограмма)

или непосредственное выполнение

Уровень 1

Микропрограммный

Аппаратное обеспечение

Уровень 0

Цифровой логический

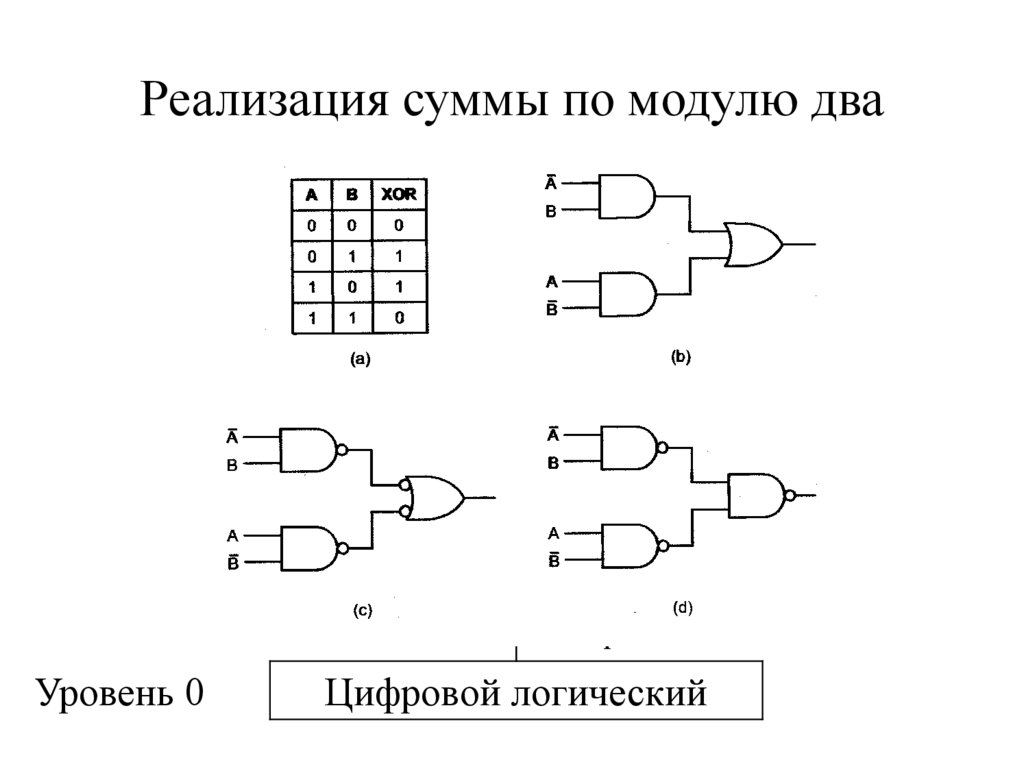

4. Реализация суммы по модулю два

Уровень5

Языкасуммы

высокого

Реализация

поуровня

модулю два

Трансляция (компилятор)

Уровень 4

Языка ассемблера

Трансляция (ассемблер)

Уровень 3

Операционной системы

Трансляция (ассемблер)

Уровень 2

Архитектуры команд

Интерпретация (микропрограмма)

или непосредственное выполнение

Уровень 1

Микропрограммный

Аппаратное обеспечение

Уровень 0

Цифровой логический

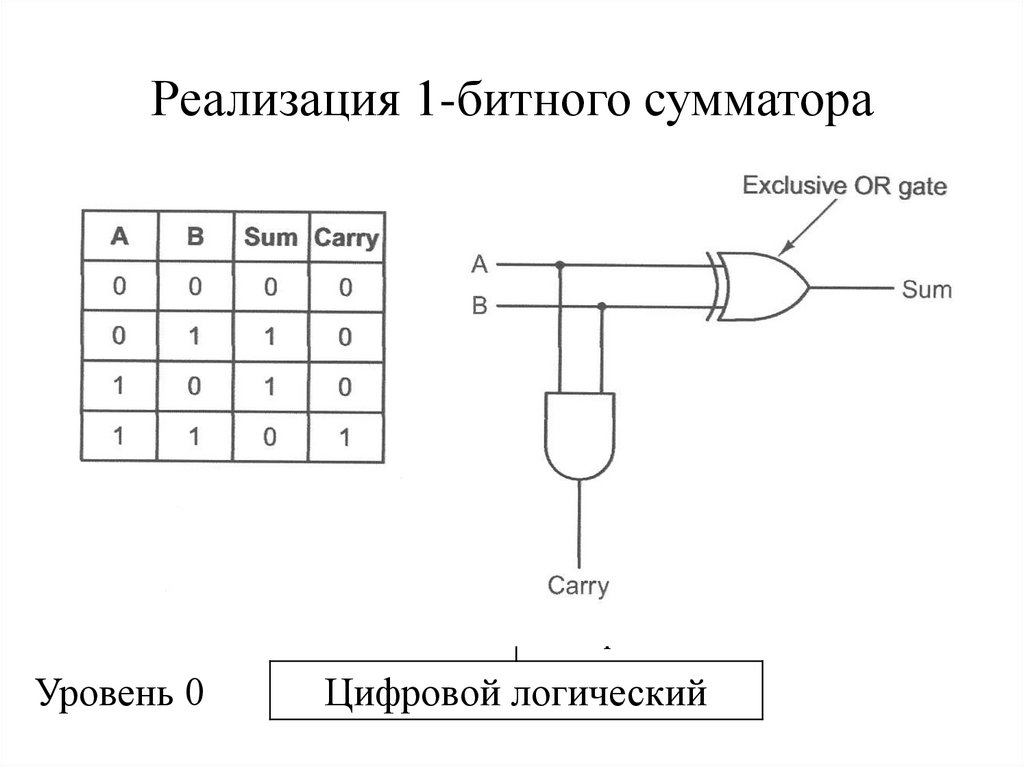

5. Реализация 1-битного сумматора

Уровень5

Языка1-битного

высокого уровня

Реализация

сумматора

Трансляция (компилятор)

Уровень 4

Языка ассемблера

Трансляция (ассемблер)

Уровень 3

Операционной системы

Трансляция (ассемблер)

Уровень 2

Архитектуры команд

Интерпретация (микропрограмма)

или непосредственное выполнение

Уровень 1

Микропрограммный

Аппаратное обеспечение

Уровень 0

Цифровой логический

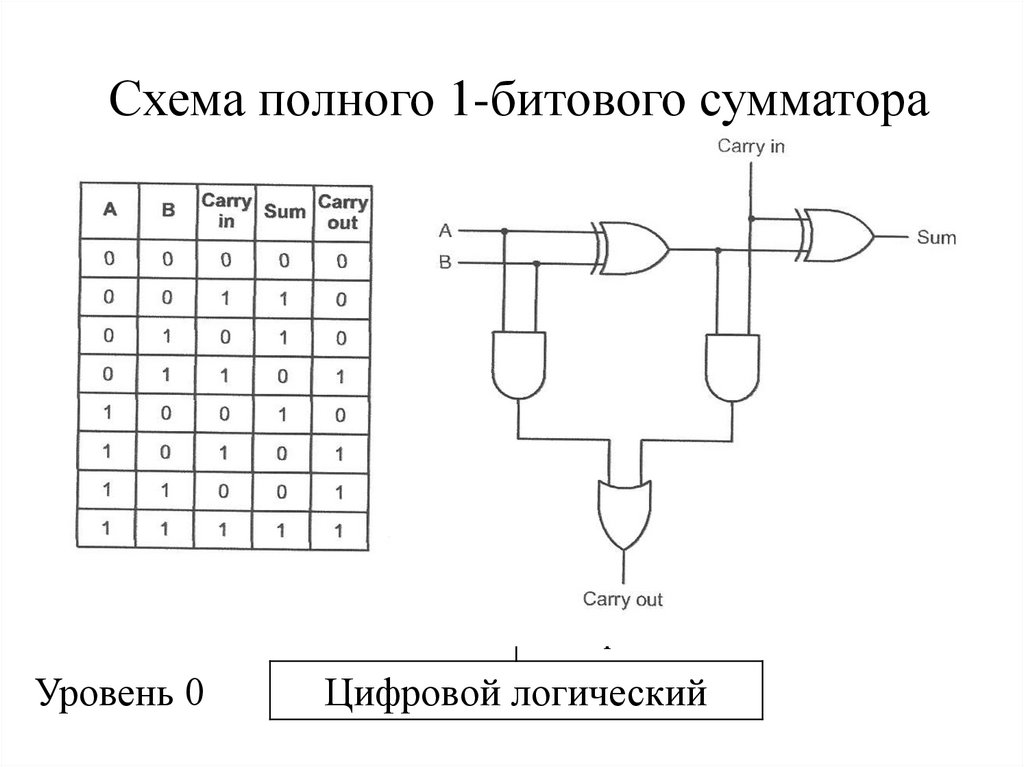

6. Схема полного 1-битового сумматора

Уровень5 полного

Языка высокого

уровнясумматора

Схема

1-битового

Трансляция (компилятор)

Уровень 4

Языка ассемблера

Трансляция (ассемблер)

Уровень 3

Операционной системы

Трансляция (ассемблер)

Уровень 2

Архитектуры команд

Интерпретация (микропрограмма)

или непосредственное выполнение

Уровень 1

Микропрограммный

Аппаратное обеспечение

Уровень 0

Цифровой логический

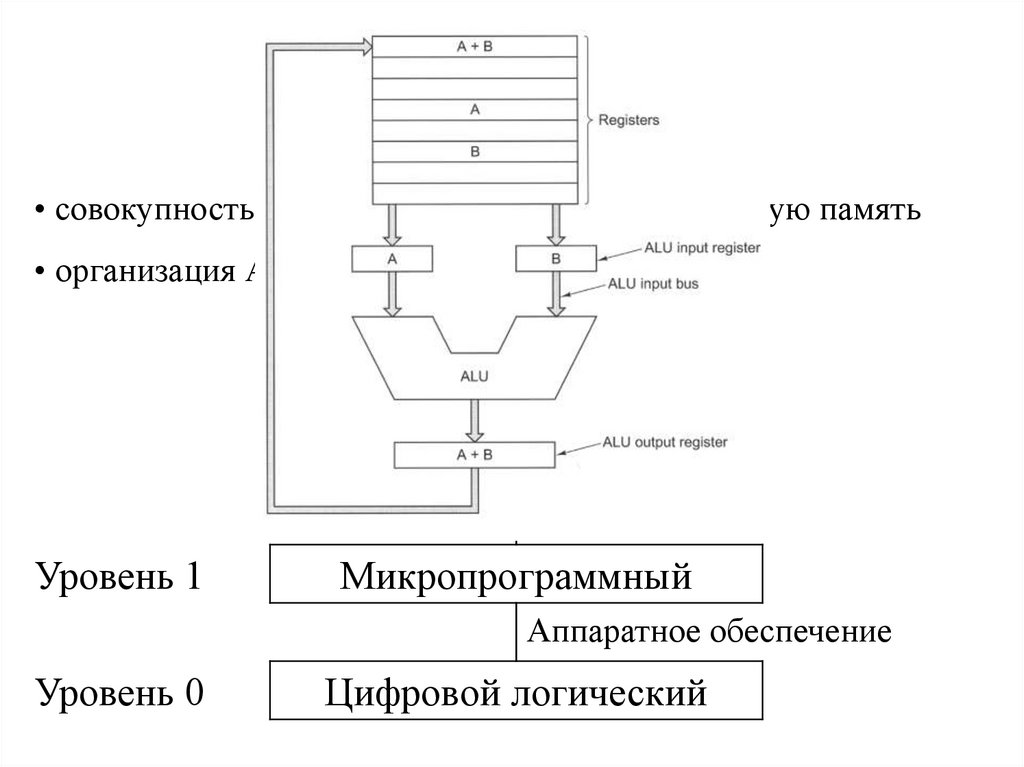

7.

Уровень 5Языка высокого уровня

Трансляция (компилятор)

Определяется:

4 регистров,

Языка ассемблера

•Уровень

совокупность

формирующих локальную память

Трансляция (ассемблер)

• организация АЛУ

Уровень 3

Операционной системы

тракт данных

Трансляция (ассемблер)

Уровень 2

Архитектуры команд

Интерпретация (микропрограмма)

или непосредственное выполнение

Уровень 1

Микропрограммный

Аппаратное обеспечение

Уровень 0

Цифровой логический

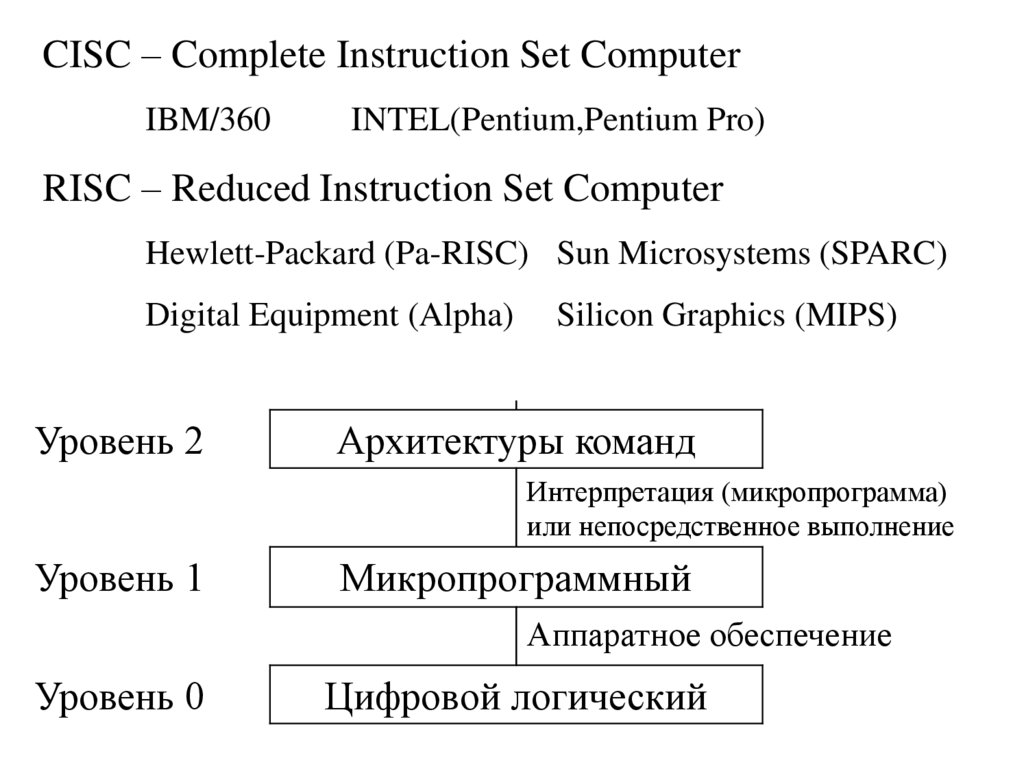

8.

CISC – Complete Instruction Set ComputerУровень 5

Языка высокого уровня

IBM/360

INTEL(Pentium,Pentium Pro)

Трансляция (компилятор)

RISC – Reduced

Instruction

Set Computer

Уровень

4

Языка ассемблера

Hewlett-Packard (Pa-RISC)Трансляция

Sun Microsystems

(SPARC)

(ассемблер)

Digital

(Alpha) Silicon

Graphics (MIPS)

Уровень

3 Equipment

Операционной

системы

Трансляция (ассемблер)

Уровень 2

Архитектуры команд

Интерпретация (микропрограмма)

или непосредственное выполнение

Уровень 1

Микропрограммный

Аппаратное обеспечение

Уровень 0

Цифровой логический

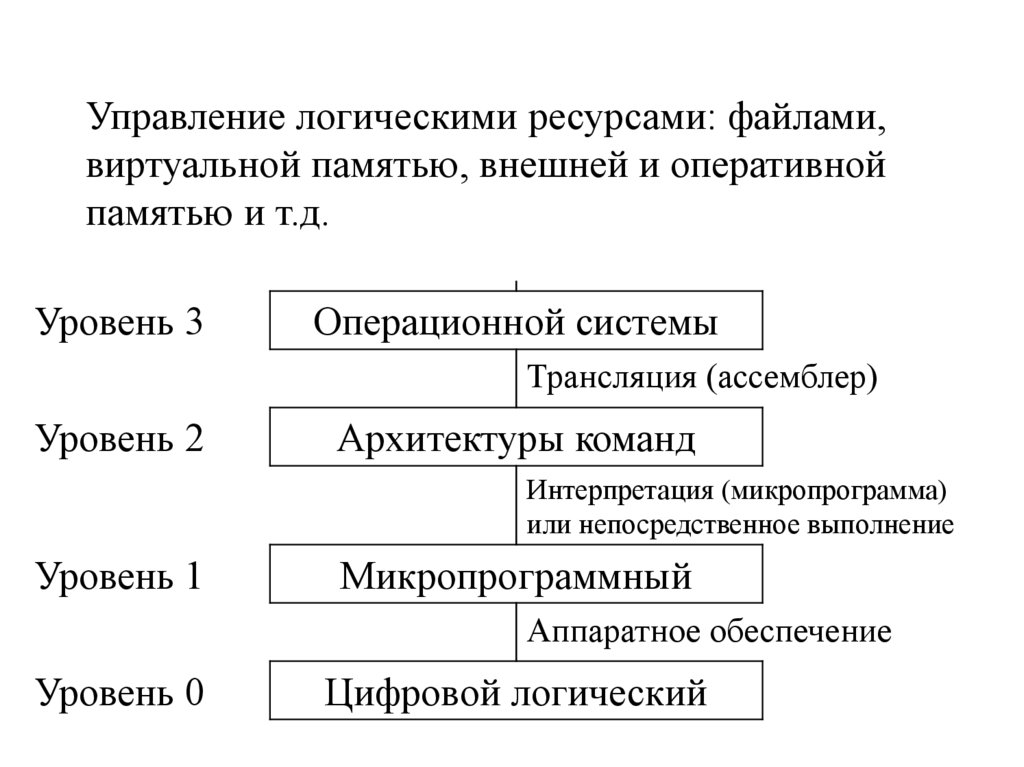

9.

Уровень 5Языка высокого уровня

Управление логическими ресурсами: файлами,

Трансляция (компилятор)

виртуальной памятью, внешней и оперативной

Уровень

4 и т.д. Языка ассемблера

памятью

Трансляция (ассемблер)

Уровень 3

Операционной системы

Трансляция (ассемблер)

Уровень 2

Архитектуры команд

Интерпретация (микропрограмма)

или непосредственное выполнение

Уровень 1

Микропрограммный

Аппаратное обеспечение

Уровень 0

Цифровой логический

10.

Уровень 5Языка высокого уровня

Трансляция (компилятор)

Уровень 4

Языка ассемблера

Трансляция (ассемблер)

Уровень 3

Операционной системы

Трансляция (ассемблер)

Уровень 2

Архитектуры команд

Интерпретация (микропрограмма)

или непосредственное выполнение

Уровень 1

Микропрограммный

Аппаратное обеспечение

Уровень 0

Цифровой логический

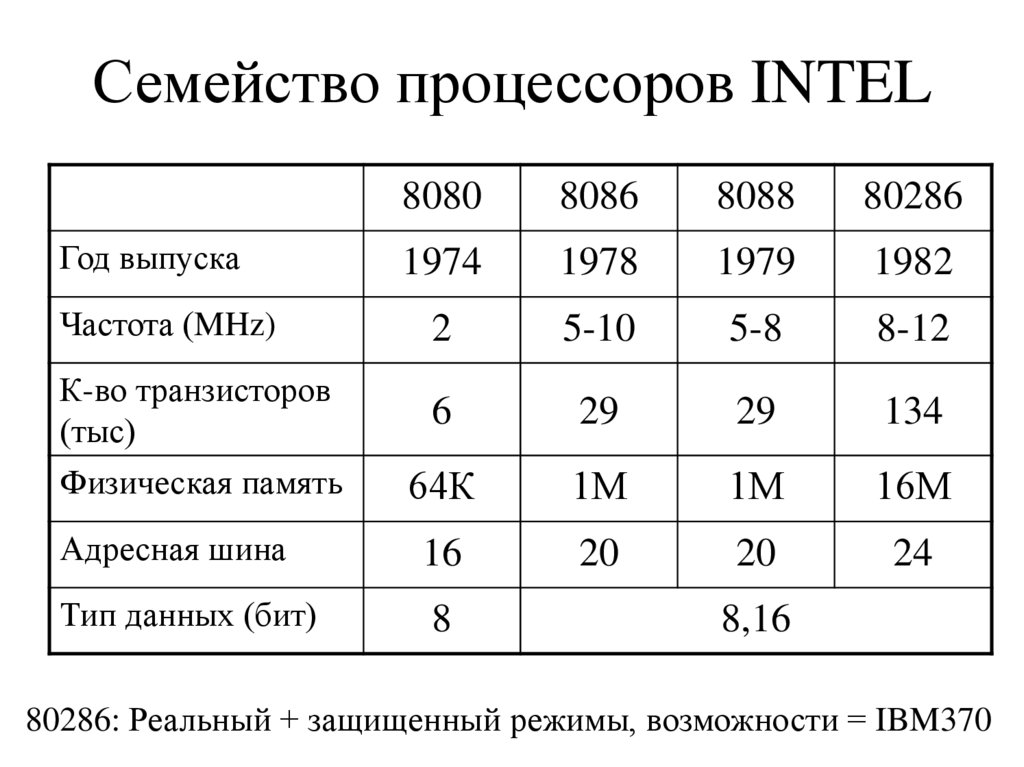

11. Семейство процессоров INTEL

80808086

8088

80286

Год выпуска

1974

1978

1979

1982

Частота (MHz)

2

5-10

5-8

8-12

К-во транзисторов

(тыс)

Физическая память

6

29

29

134

64К

1М

1М

16М

Адресная шина

16

20

20

24

Тип данных (бит)

8

8,16

80286:

8086:Реальный

сегментирование

+ защищенный

памяти,режимы,

совместимость

возможности

«назад»= IBM370

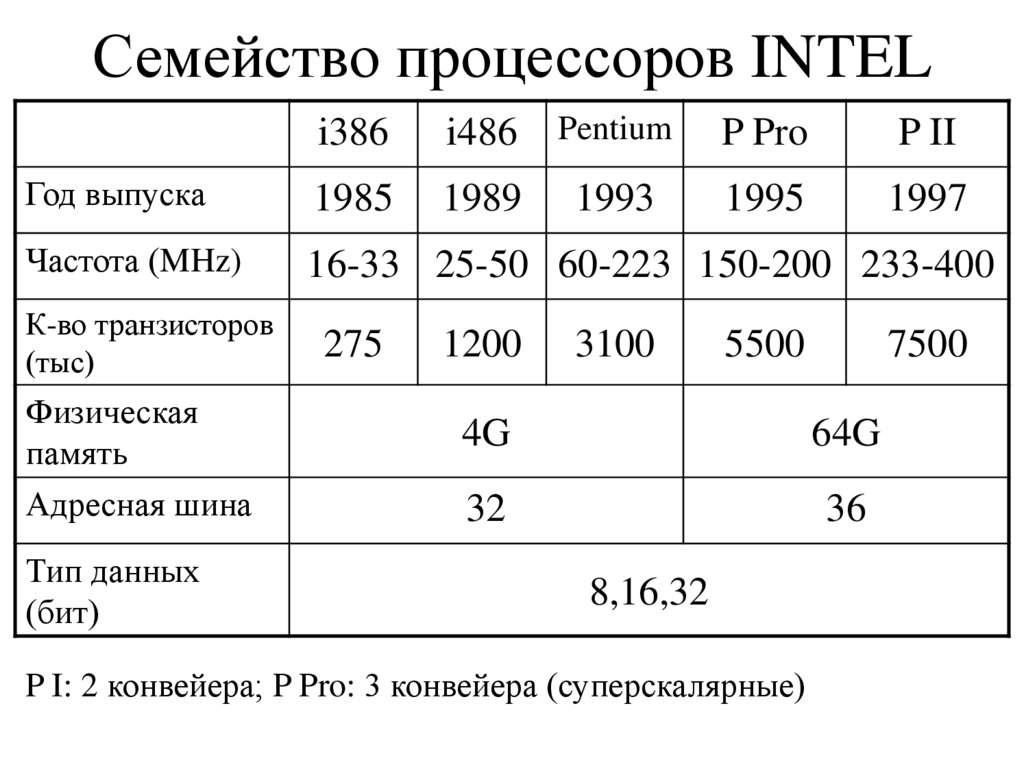

12. Семейство процессоров INTEL

i386i486

Pentium

P Pro

P II

Год выпуска

1985

1989

1993

1995

1997

Частота (MHz)

16-33 25-50 60-223 150-200 233-400

К-во транзисторов

(тыс)

275

1200

3100

5500

7500

Физическая

память

4G

64G

Адресная шина

32

36

Тип данных

(бит)

8,16,32

i386:

i486:

P

I: 2 скалярный

виртуальный

конвейера; 5P ступенчатый

Pro:

8086,3 УВВ

конвейера

параллельно

конвейер,

(суперскалярные)

КЭШ

с ЦП8, Кб

очередь команд

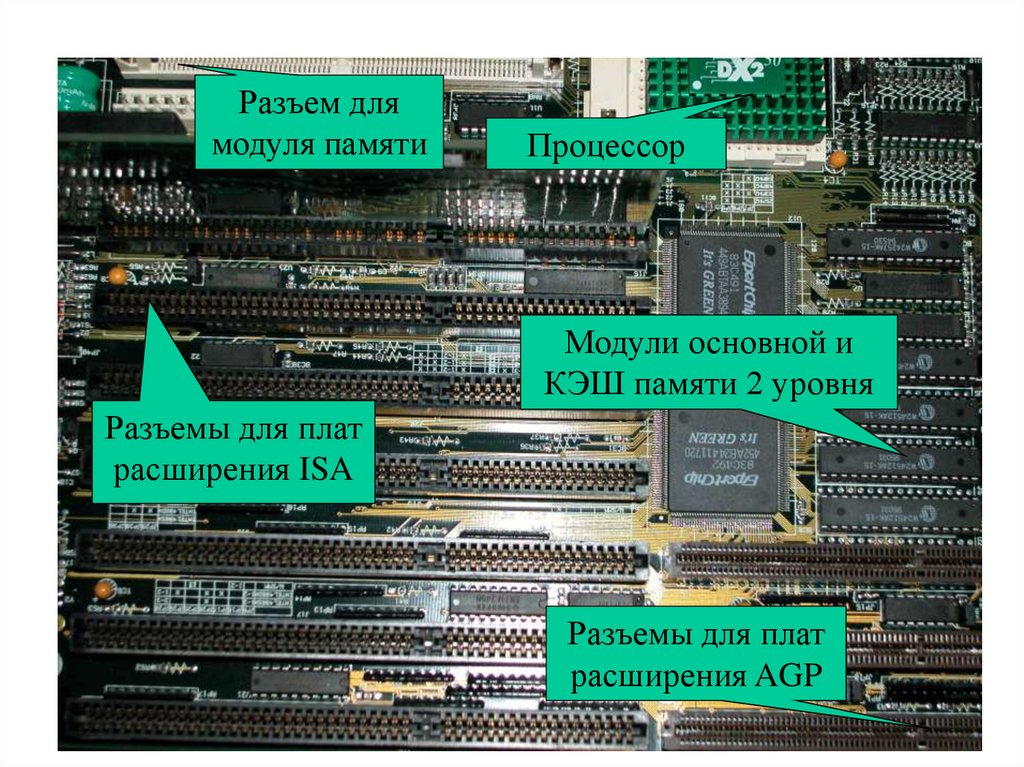

13.

Разъем длямодуля памяти

Процессор

Модули основной и

КЭШ памяти 2 уровня

Разъемы для плат

расширения ISA

Разъемы для плат

расширения AGP

14.

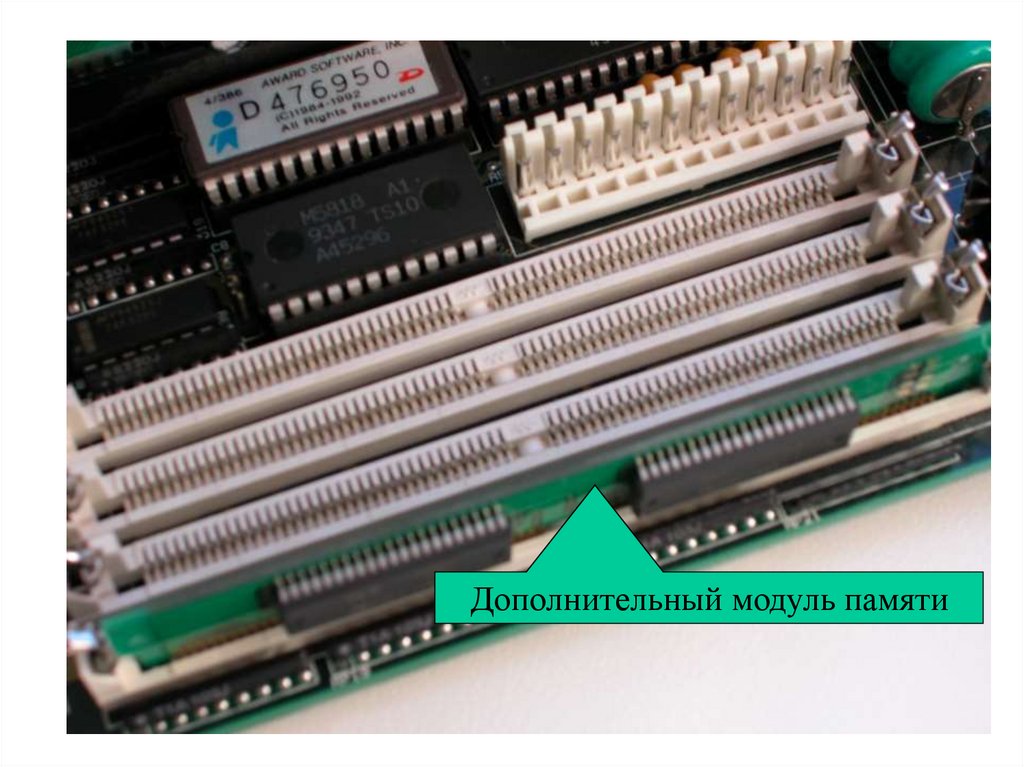

Дополнительный модуль памяти15.

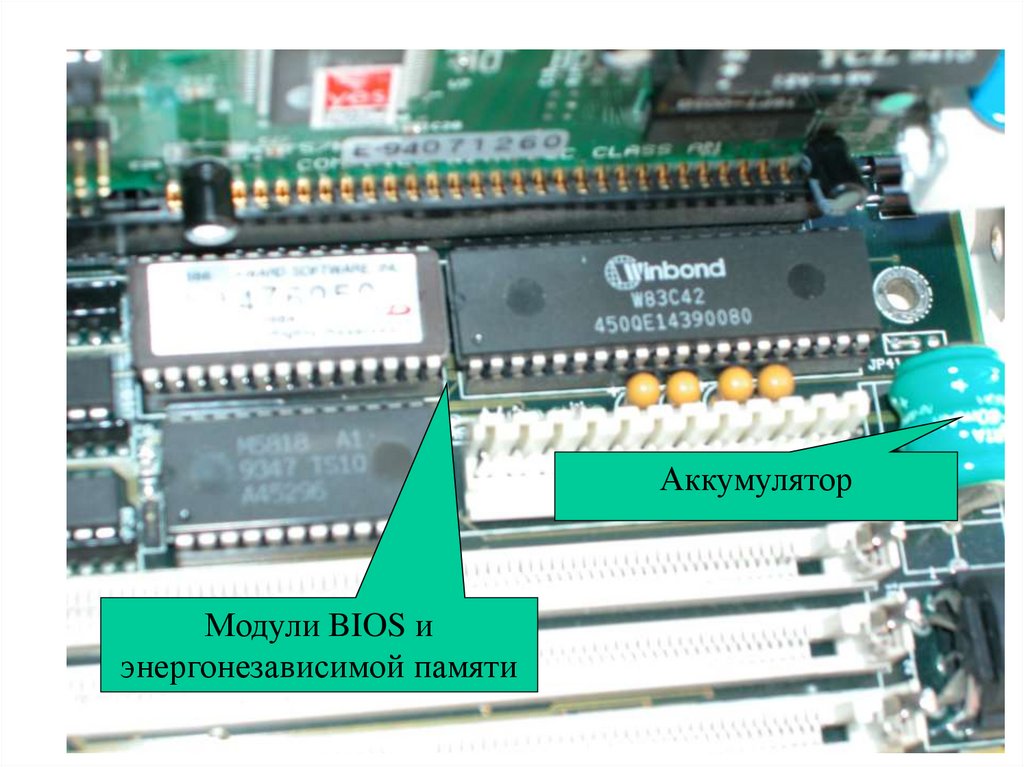

АккумуляторМодули BIOS и

энергонезависимой памяти

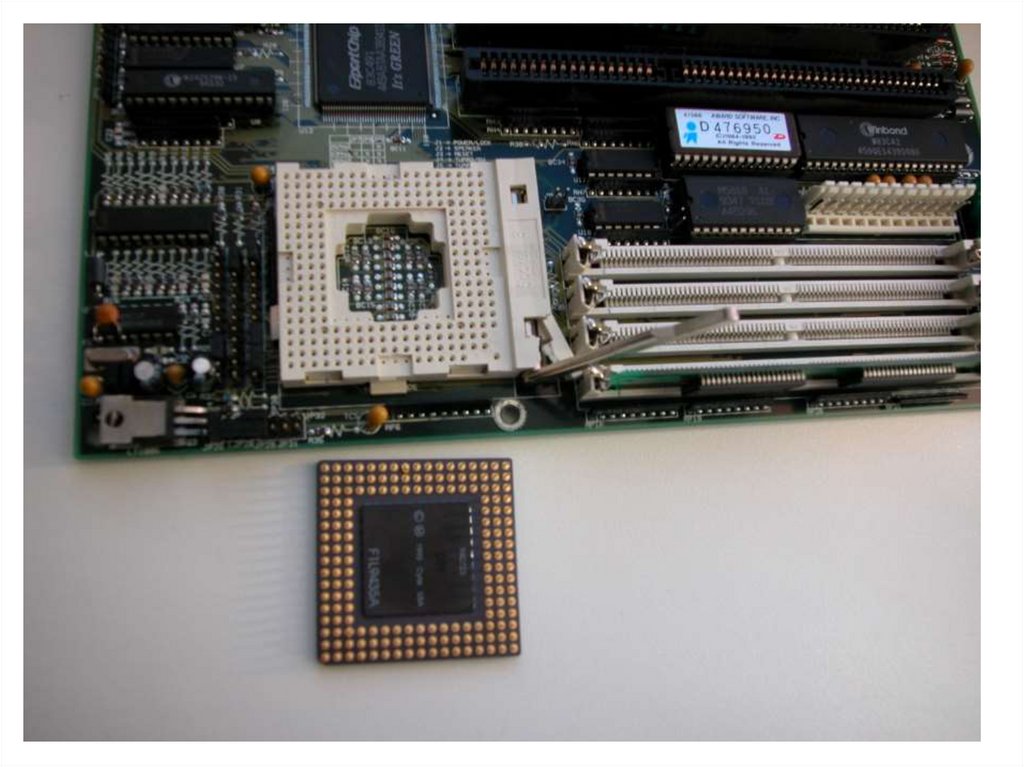

16.

17.

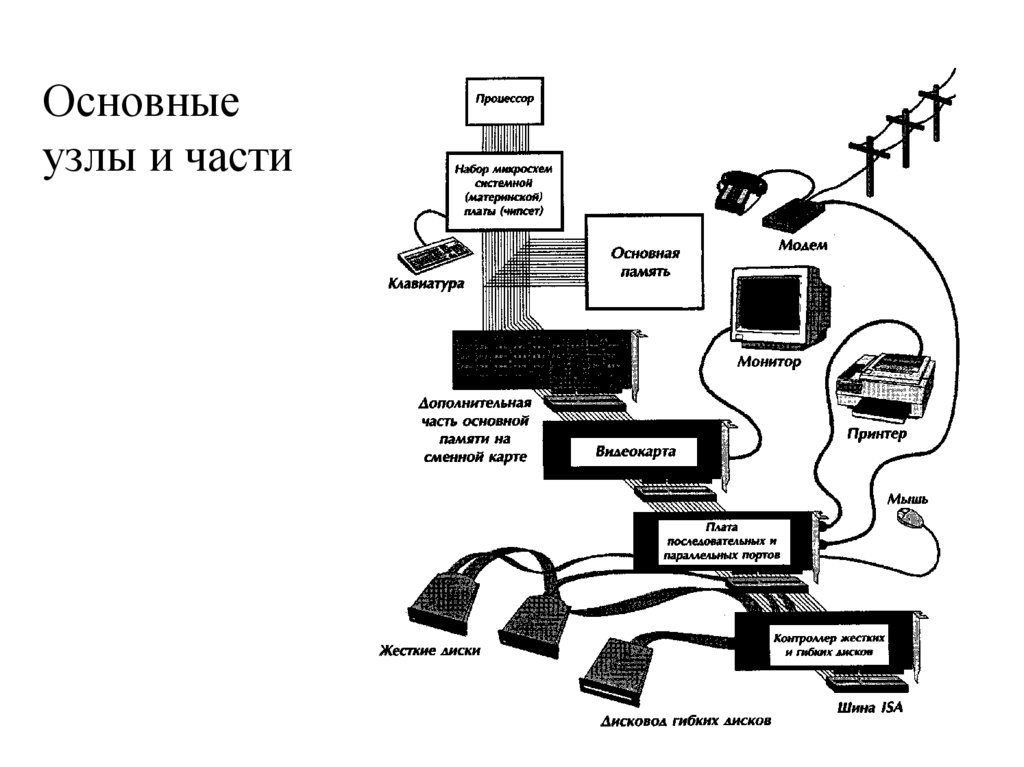

Основныеузлы и части

18.

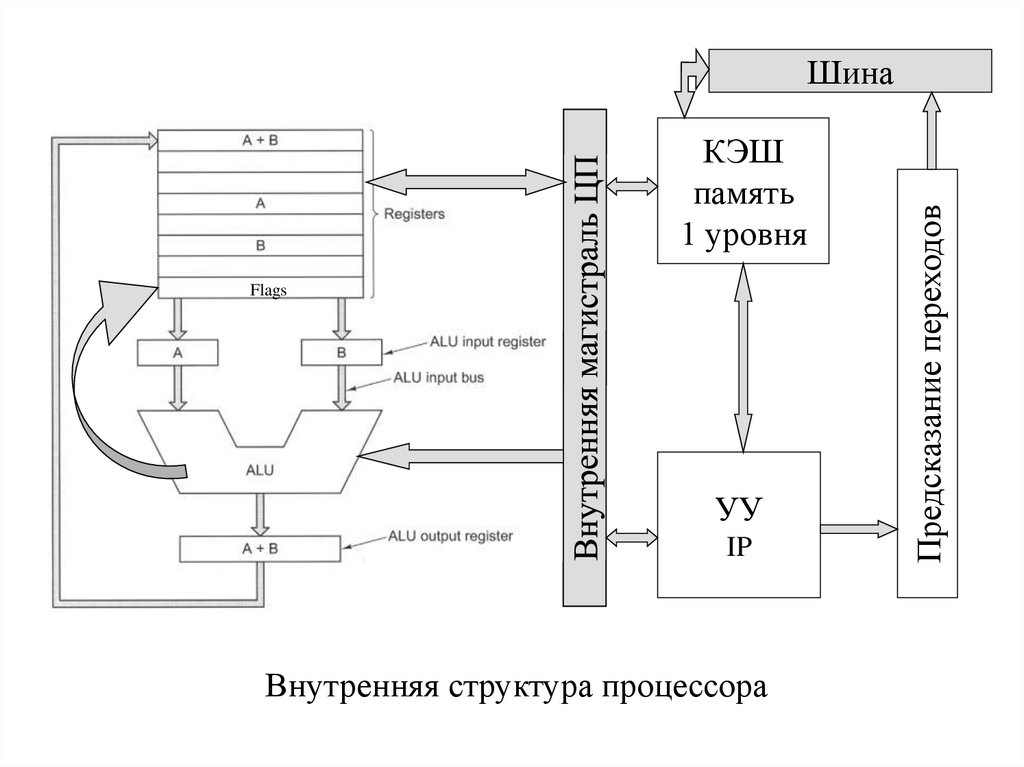

КЭШпамять

1 уровня

Flags

УУ

IP

Внутренняя структура процессора

Предсказание переходов

Шина

19.

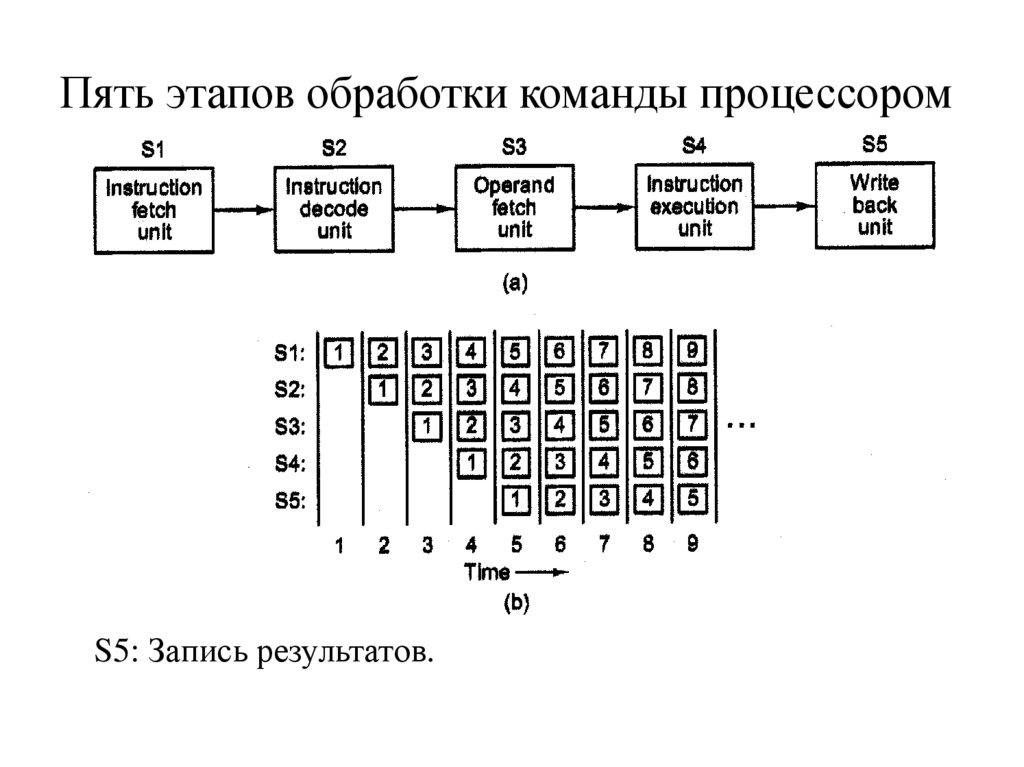

Пять этапов обработки команды процессоромS1: Запись

S2:

S3:

S4:

S5:

Помещение

Выделение

Выбор

Выполнение

операндов

результатов.

кода

ввычислений.

очередь.

и из

формирование

памяти.

Увеличение

Формирование

адреса.

IP.

флагов.

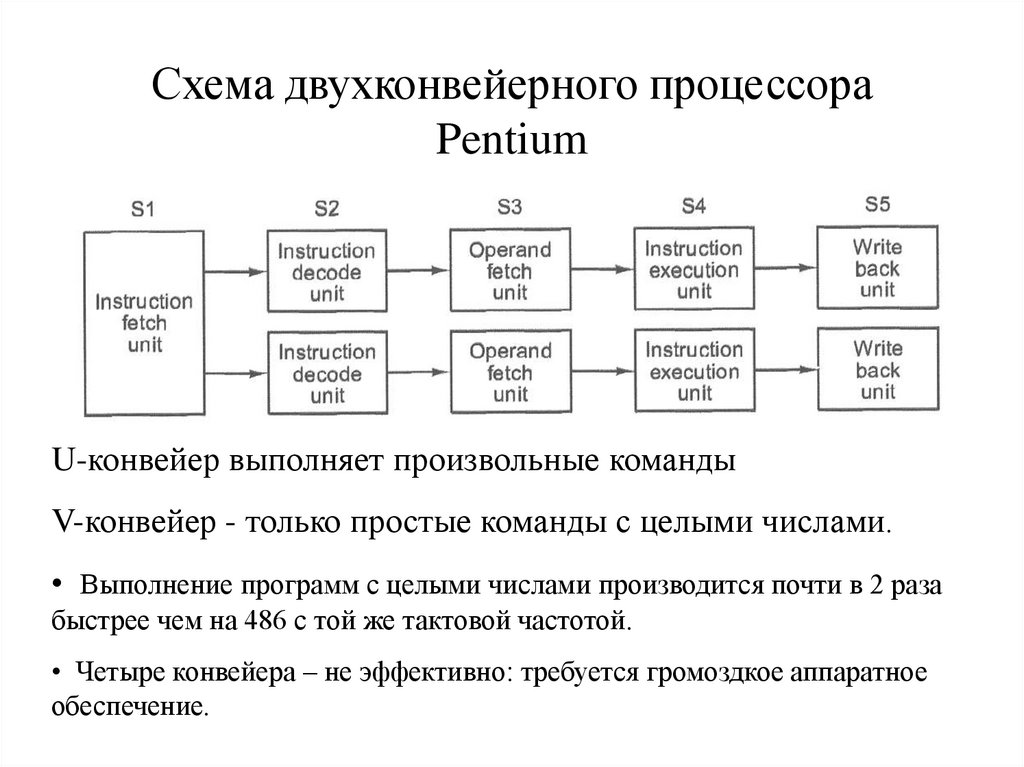

20. Схема двухконвейерного процессора Pentium

U-конвейер выполняет произвольные командыV-конвейер - только простые команды с целыми числами.

• Выполнение программ с целыми числами производится почти в 2 раза

быстрее чем на 486 с той же тактовой частотой.

• Четыре конвейера – не эффективно: требуется громоздкое аппаратное

обеспечение.

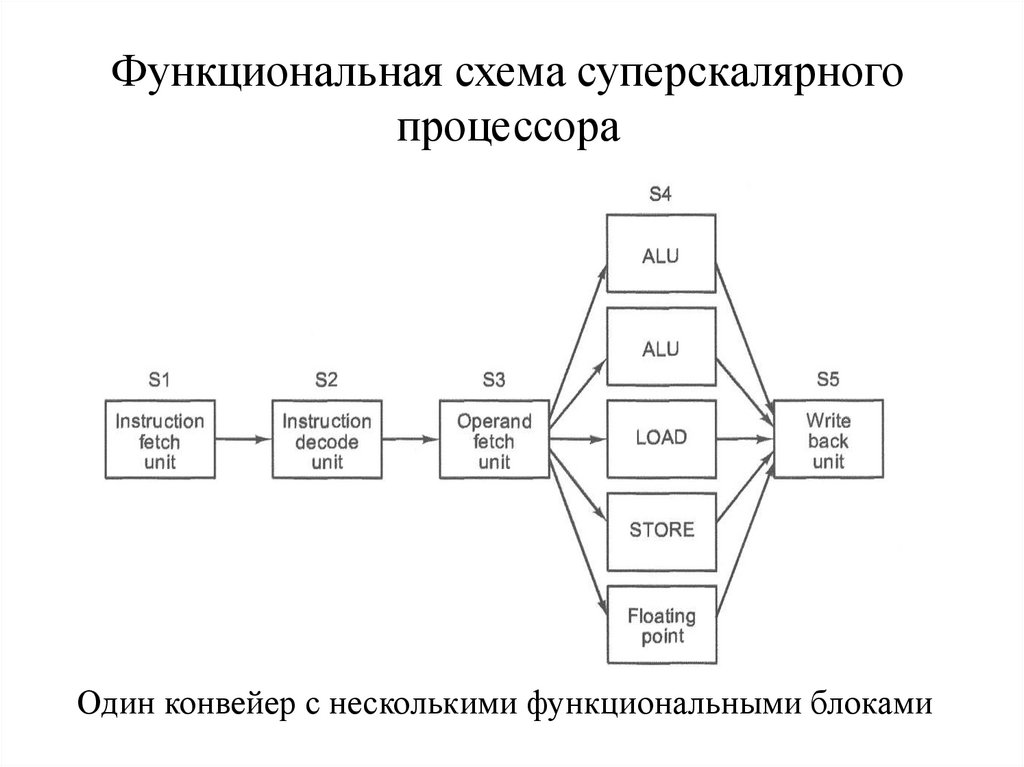

21. Функциональная схема суперскалярного процессора

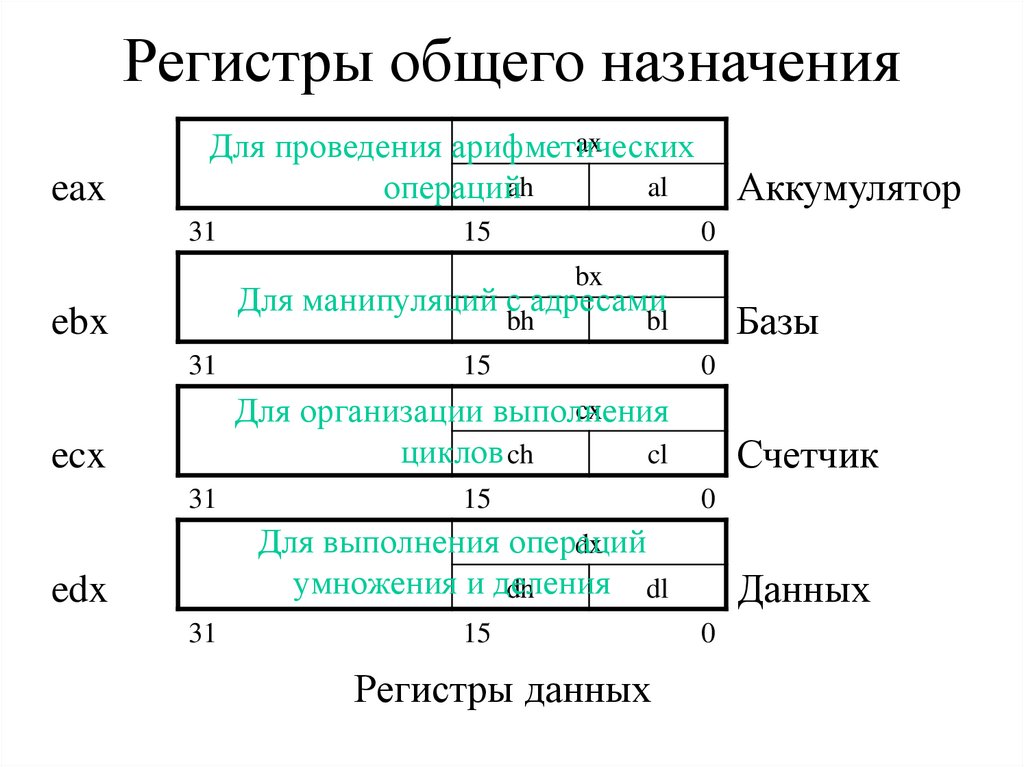

Один конвейер с несколькими функциональными блоками22. Регистры общего назначения

eaxax

Для проведения арифметических

al

операцийah

31

15

Аккумулятор

0

bx

Для манипуляций с адресами

ebx

bh

31

Базы

bl

15

0

cx

Для организации выполнения

циклов ch

cl

ecx

31

15

Счетчик

0

Для выполнения операций

dx

умножения и деления

dh

dl

edx

31

15

Регистры данных

Данных

0

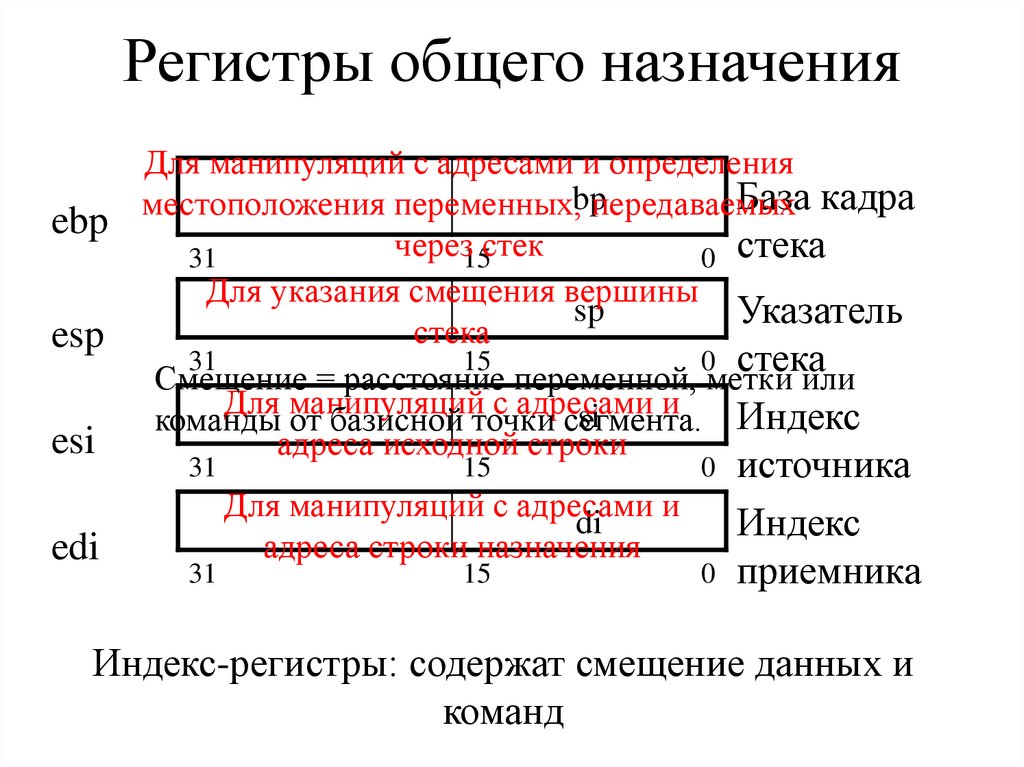

23. Регистры общего назначения

Для манипуляций с адресами и определенияБаза кадра

местоположения переменных,bpпередаваемых

ebp

через15стек

31

0 стека

Для указания смещения вершины

sp

Указатель

стека

esp

31

15

0 стека

Смещение = расстояние переменной, метки или

Для манипуляций с адресами

и

si

Индекс

команды от базисной точки сегмента.

esi

адреса исходной строки

источника

Для манипуляций с адресами и

di

Индекс

адреса строки назначения

31

15

0 приемника

31

edi

15

0

Индекс-регистры: содержат смещение данных и

команд

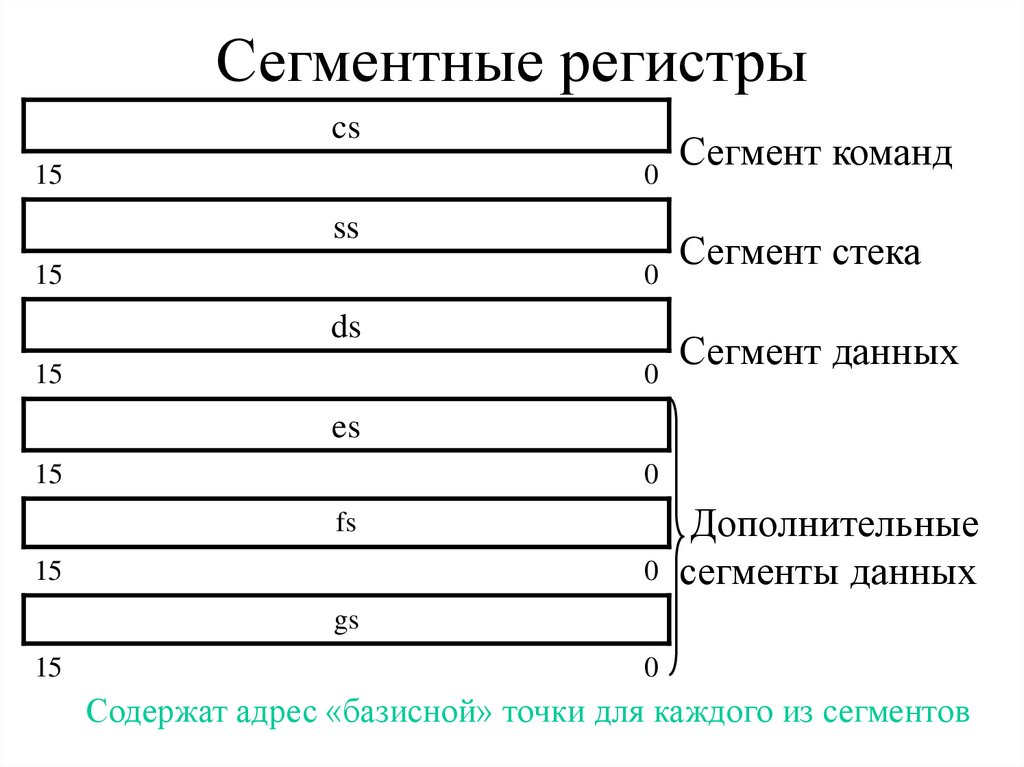

24. Сегментные регистры

cs15

0

ss

15

Сегмент

стека

0

ds

15

Сегмент команд

0

Сегмент данных

es

15

0

fs

15

Дополнительные

0 сегменты данных

gs

15

0

Содержат адрес «базисной» точки для каждого из сегментов

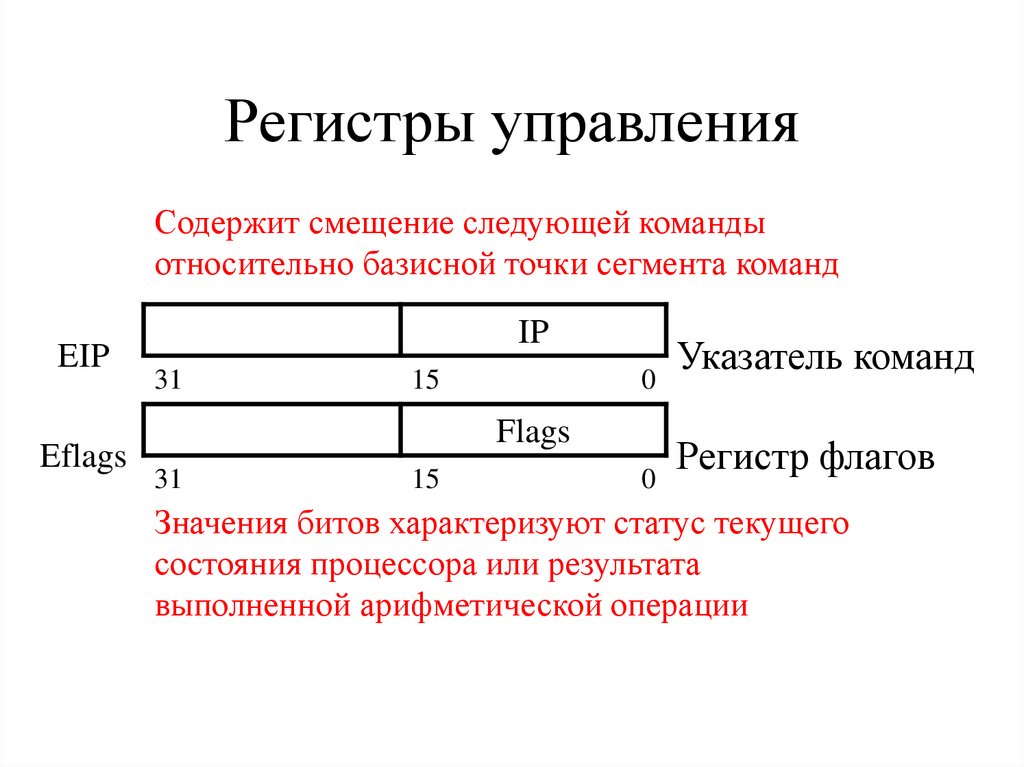

25. Регистры управления

Содержит смещение следующей командыотносительно базисной точки сегмента команд

EIP

Eflags

IP

31

15

Указатель

команд

0

Flags

31

15

0

Регистр флагов

Значения битов характеризуют статус текущего

состояния процессора или результата

выполненной арифметической операции

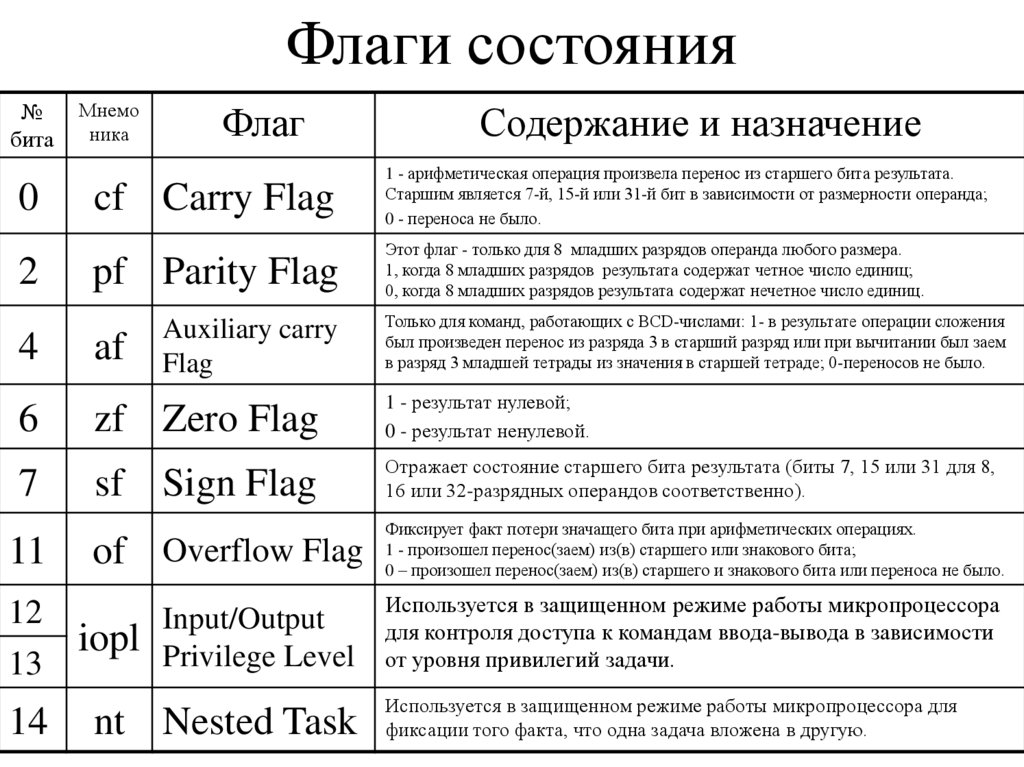

26. Флаги состояния

№бита

Мнемо

ника

Флаг

Содержание и назначение

cf Carry Flag

1 - арифметическая операция произвела перенос из старшего бита результата.

Старшим является 7-й, 15-й или 31-й бит в зависимости от размерности операнда;

0 - переноса не было.

2

pf Parity Flag

Этот флаг - только для 8 младших разрядов операнда любого размера.

1, когда 8 младших разрядов результата содержат четное число единиц;

0, когда 8 младших разрядов результата содержат нечетное число единиц.

4

Auxiliary carry

Flag

0

af

Только для команд, работающих с ВСD-числами: 1- в результате операции сложения

был произведен перенос из разряда 3 в старший разряд или при вычитании был заем

в разряд 3 младшей тетрады из значения в старшей тетраде; 0-переносов не было.

zf Zero Flag

1 - результат нулевой;

0 - результат ненулевой.

sf Sign Flag

Отражает состояние старшего бита результата (биты 7, 15 или 31 для 8,

16 или 32-разрядных операндов соответственно).

11

of Overflow Flag

Фиксирует факт потери значащего бита при арифметических операциях.

1 - произошел перенос(заем) из(в) старшего или знакового бита;

0 – произошел перенос(заем) из(в) старшего и знакового бита или переноса не было.

12

13

iopl

Input/Output

Privilege Level

Используется в защищенном режиме работы микропроцессора

для контроля доступа к командам ввода-вывода в зависимости

от уровня привилегий задачи.

14

nt Nested Task фиксации того факта, что одна задача вложена в другую.

6

7

Используется в защищенном режиме работы микропроцессора для

27. Системные флаги

№бита

8

9

16

Мнемо

ника

Флаг

Содержание и назначение

Предназначен для организации пошаговой работы микропроцессора:

1- микропроцессор генерирует прерывание с номером 1 после выполнения каждой

машинной команды. Может использоваться при отладке программ, в частности

отладчиками; 0 - обычная работа

tf

Trace Flag

if

Interrupt enable

Flag

Предназначен для маскирования аппаратных прерываний (прерываний по входу

INTR): 1- аппаратные прерывания разрешены; 0- аппаратные прерывания запрещены

rf

Resume Flag

Используется при обработке прерываний от регистров отладки

Virtual 8086

17 vm Mode

Alignment

18 ac Check

Признак работы микропроцессора в режиме виртуального 8086:

1 - процессор работает в режиме виртуального 8086;

0 - процессор работает в реальном или защищенном режиме.

Предназначен для разрешения контроля выравнивания при

обращениях к памяти.

Флаг управления

10

df Directory Flag

Определяет направление поэлементной обработки в

цепочечных командах:

0 - от начала строки к концу; 1 - от конца строки к ее началу.

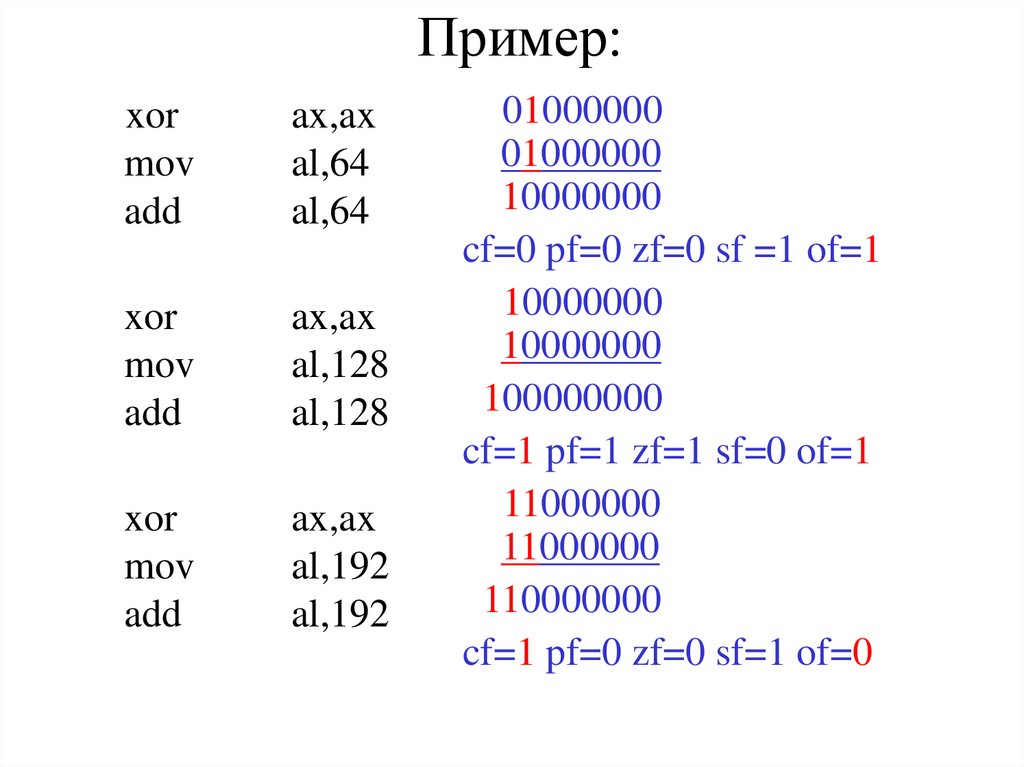

28. Пример:

xormov

add

ax,ax

al,64

al,64

xor

mov

add

ax,ax

al,128

al,128

xor

mov

add

ax,ax

al,192

al,192

01000000

01000000

10000000

cf=0 pf=0 zf=0 sf =1 of=1

10000000

10000000

100000000

cf=1 pf=1 zf=1 sf=0 of=1

11000000

11000000

110000000

cf=1 pf=0 zf=0 sf=1 of=0

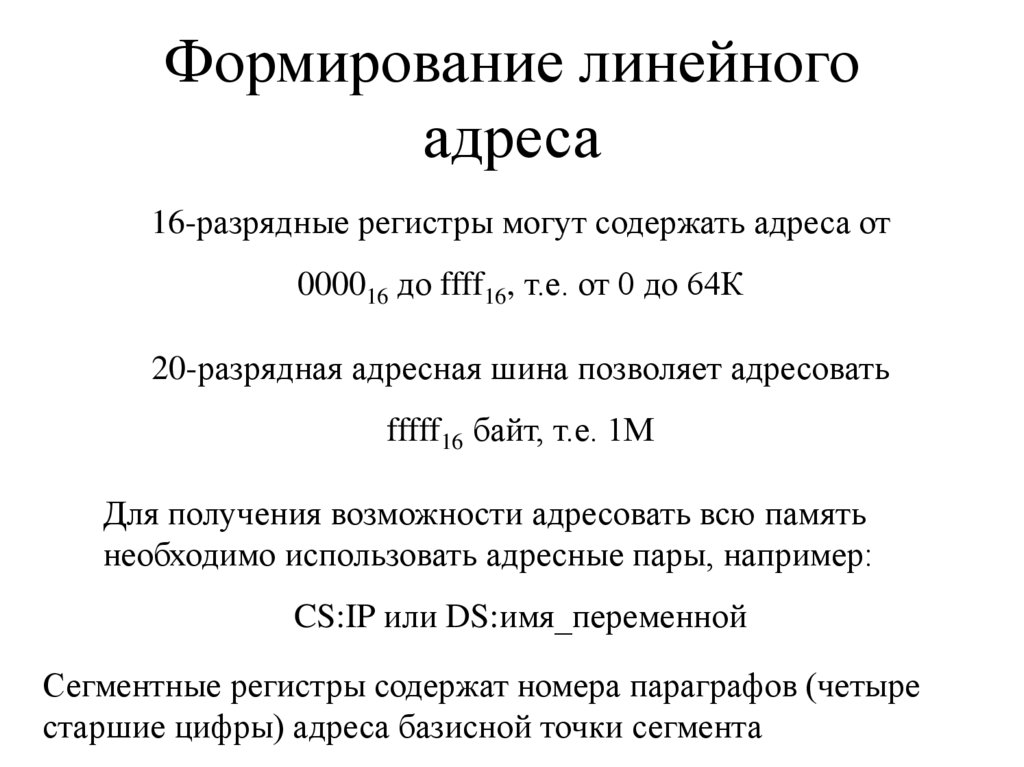

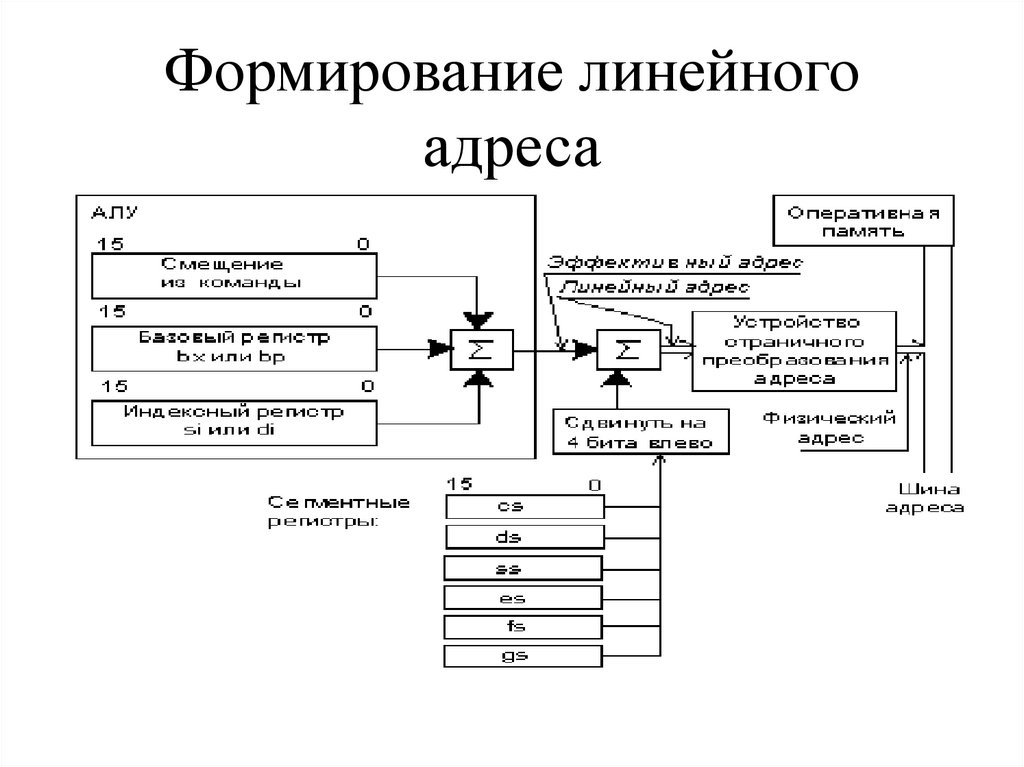

29. Формирование линейного адреса

16-разрядные регистры могут содержать адреса от000016 до ffff16, т.е. от 0 до 64К

20-разрядная адресная шина позволяет адресовать

fffff16 байт, т.е. 1М

Для получения возможности адресовать всю память

необходимо использовать адресные пары, например:

CS:IP или DS:имя_переменной

Сегментные регистры содержат номера параграфов (четыре

старшие цифры) адреса базисной точки сегмента

programming

programming