Similar presentations:

Синтез самосинхронных схем и его верификация

1.

Синтез самосинхронных схем и еговерификация

Дьяченко Ю.Г., Морозов Н.В., Орлов Г.А.

Федеральный исследовательский центр «Информатика

и управление» Российской академии наук

2.

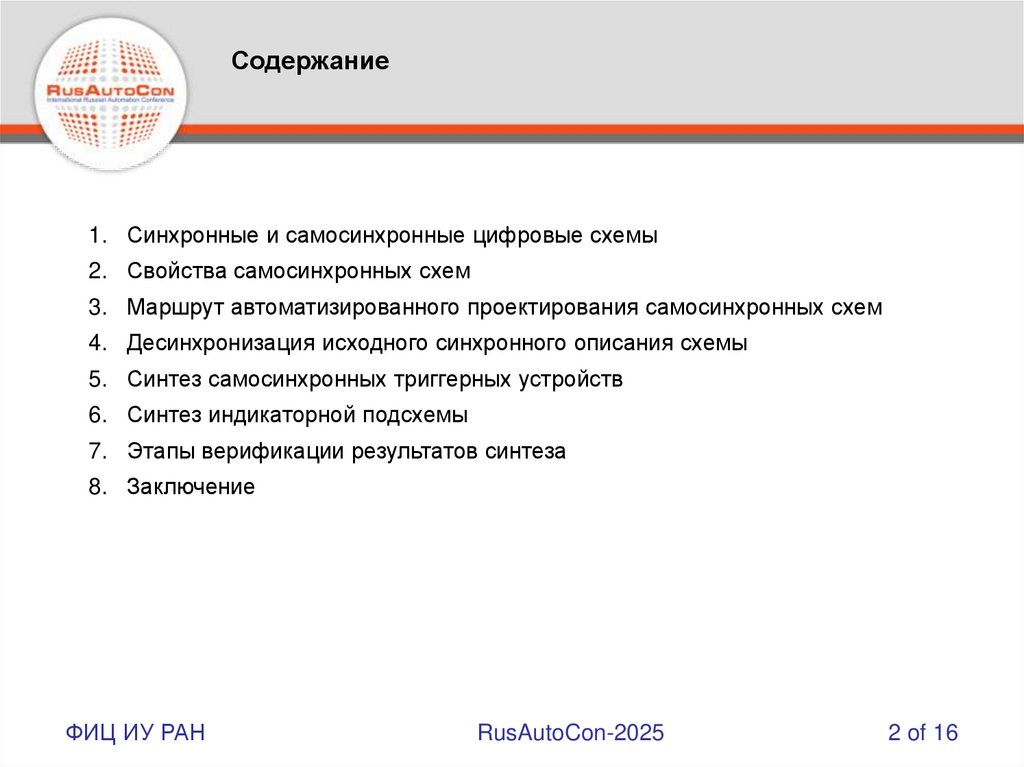

Содержание1. Синхронные и самосинхронные цифровые схемы

2. Свойства самосинхронных схем

3. Маршрут автоматизированного проектирования самосинхронных схем

4. Десинхронизация исходного синхронного описания схемы

5. Синтез самосинхронных триггерных устройств

6. Синтез индикаторной подсхемы

7. Этапы верификации результатов синтеза

8. Заключение

ФИЦ ИУ РАН

RusAutoCon-2025

2 of 16

3.

Классификация цифровых схемАсинхронные

Цифровые

схемы

Асинхронные

схемы

Самосинхронные

схемы

Синхронные

схемы

Самосинхронные

Синхронные

Диапазон работоспособности

Самосинхронные

схемы

Прочие схемы

Синхронные

схемы

ФИЦ ИУ РАН

RusAutoCon-2025

3 of 16

4.

Свойства самосинхронных (СС) схемDIn

Схема-1

Схема-2

Схема-3

Функциональная

логика

Функциональная

логика

Функциональная

логика

DOut

AckO

RqI

Индикация

Индикация

Индикация

AckI

RqO

Преимущества

Сохранение работоспособности при любых задержках логических элементов

Стопроцентная самопроверяемость относительно константных неисправностей с

автоматическим остановом и локализацией неисправности

Предельно широкий диапазон условий эксплуатации

Повышенная сбоеустойчивость и помехозащищенность

Недостатки

Аппаратная избыточность

Снижение быстродействия при увеличении разрядности вычислительного устройства

из-за индикаторной подсхемы

ФИЦ ИУ РАН

RusAutoCon-2025

4 of 16

5.

Автоматизация проектирования самосинхронных схемАлгоритм

функционирования

самосинхронной

схемы

Описание

синхронной

схемы

Список

цепей и

элементов

САПР

синхронных

схем

Библиотека

стандартных

элементов

Список

цепей и

элементов

Логический

синтез

СС-схемы

Библиотека

стандартных и

самосинхронных

элементов

Изготовление

СБИС

ФИЦ ИУ РАН

RusAutoCon-2025

5 of 16

6.

Маршрут проектирования самосинхронных схемПреобразование

поведенческого

описания синхронного

прототипа в

функциональное

Система логического

синтеза Yosys

Конвертация «дерева»

тактовых сигналов в

фазовые сигналы

Замена синхронных

устройств с памятью

самосинхронными

шаблонами

Дуализация функций,

парафазное

кодирование данных

Библиотека стандартных

и самосинхронных

элементов

Покрытие функций и

шаблонов

библиотечными

элементами

Верификация

самосинхронной

схемы

Синтез подсхемы

управления

Формирование

ограничений и

критериев для

физического синтеза

Синтез индикаторной

подсхемы

Физический синтез

ФИЦ ИУ РАН

RusAutoCon-2025

6 of 16

7.

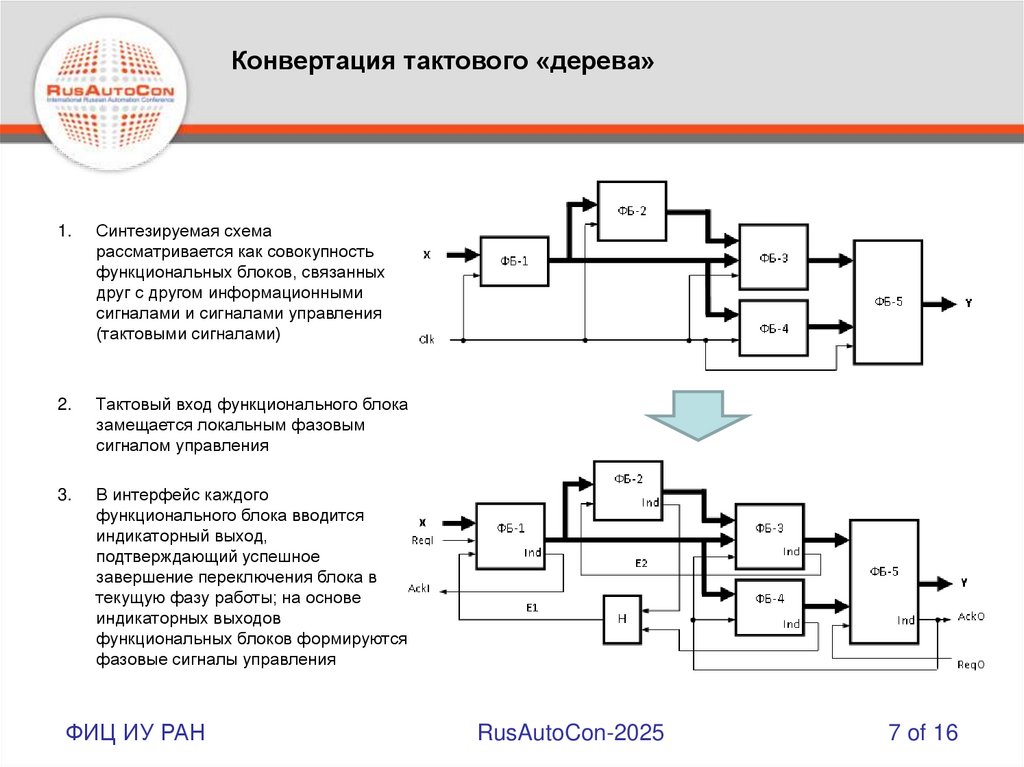

Конвертация тактового «дерева»1.

Синтезируемая схема

рассматривается как совокупность

функциональных блоков, связанных

друг с другом информационными

сигналами и сигналами управления

(тактовыми сигналами)

2.

Тактовый вход функционального блока

замещается локальным фазовым

сигналом управления

3.

В интерфейс каждого

функционального блока вводится

индикаторный выход,

подтверждающий успешное

завершение переключения блока в

текущую фазу работы; на основе

индикаторных выходов

функциональных блоков формируются

фазовые сигналы управления

ФИЦ ИУ РАН

RusAutoCon-2025

7 of 16

8.

Замена синхронных устройств с памятьюсамосинхронными шаблонами

Система логического

синтеза Yosys

Поиск соответствия между описаниями устройств

с памятью в синхронном прототипе и

синхронными шаблонами

Замена триггеров и

регистров одним

самосинхронным

шаблоном

Замена счетчиков

двумя

самосинхронными

шаблонами

Библиотека шаблонов

самосинхронных

триггеров, регистров и

счетчиков

ФИЦ ИУ РАН

RusAutoCon-2025

8 of 16

9.

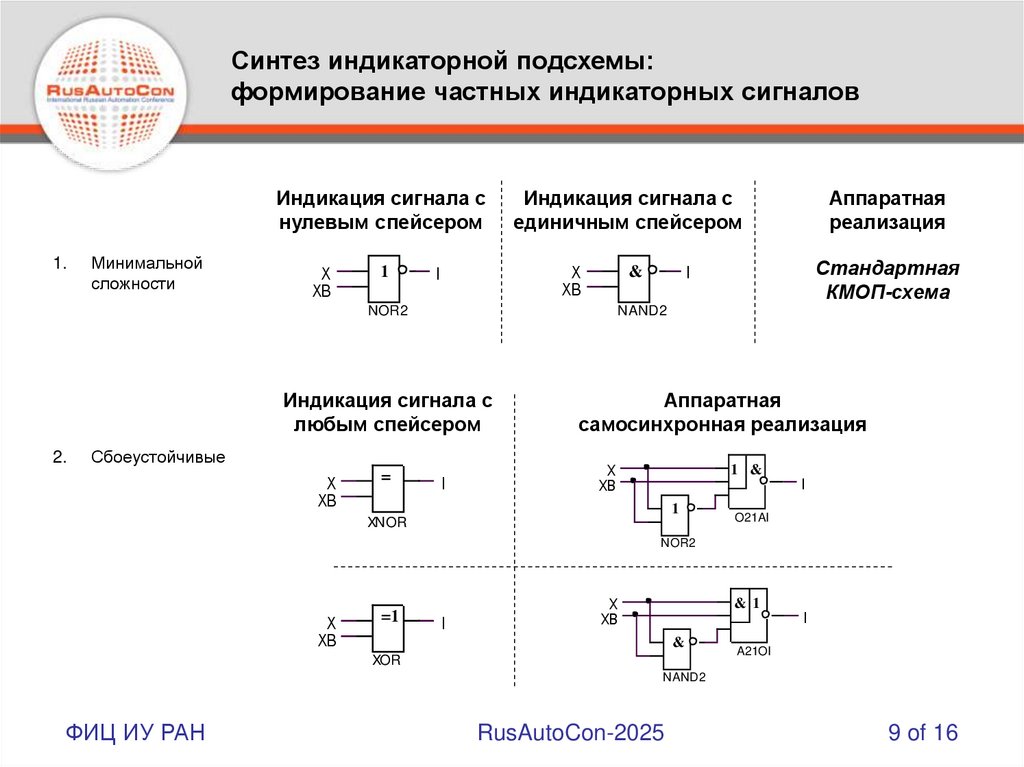

Синтез индикаторной подсхемы:формирование частных индикаторных сигналов

Индикация сигнала с

нулевым спейсером

1.

Минимальной

сложности

X

XB

1

Индикация сигнала с

единичным спейсером

X

XB

I

NAND2

Индикация сигнала с

любым спейсером

2.

Сбоеустойчивые

X

XB

=

Стандартная

КМОП-схема

I

&

NOR2

Аппаратная

реализация

I

Аппаратная

самосинхронная реализация

X

XB

1 &

1

XNOR

I

O21AI

NOR2

X

XB

=1

I

X

XB

& 1

&

XOR

I

A21OI

NAND2

ФИЦ ИУ РАН

RusAutoCon-2025

9 of 16

10.

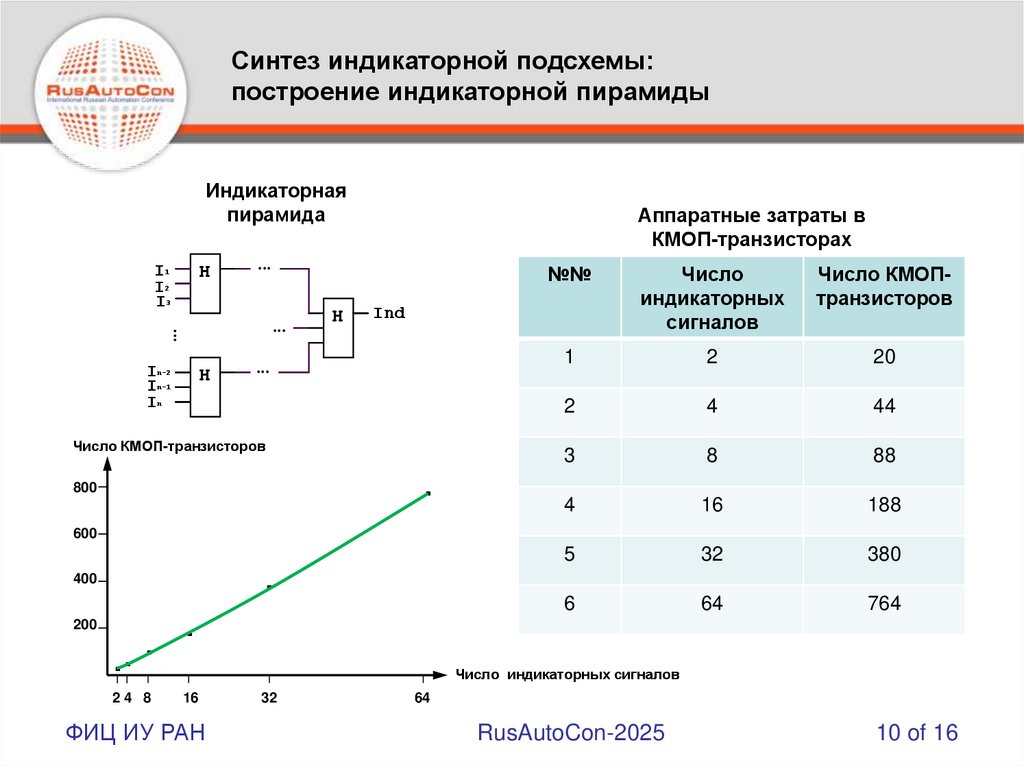

Синтез индикаторной подсхемы:построение индикаторной пирамиды

Индикаторная

пирамида

I1

I2

I3

H

...

...

...

In-2

In-1

In

H

Аппаратные затраты в

КМОП-транзисторах

H

Число

индикаторных

сигналов

Число КМОПтранзисторов

1

2

20

2

4

44

3

8

88

4

16

188

5

32

380

6

64

764

Ind

...

Число КМОП-транзисторов

.

800

№№

600

.

400

200

..

.

24 8

.

Число индикаторных сигналов

16

ФИЦ ИУ РАН

32

64

RusAutoCon-2025

10 of 16

11.

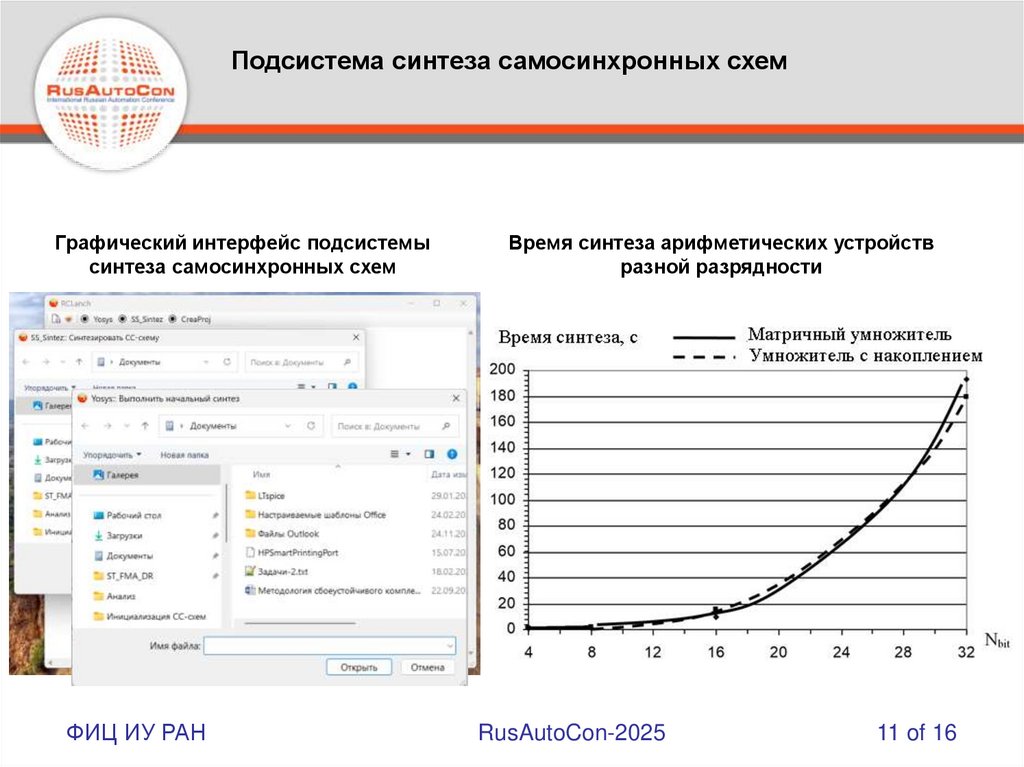

Подсистема синтеза самосинхронных схемГрафический интерфейс подсистемы

синтеза самосинхронных схем

ФИЦ ИУ РАН

Время синтеза арифметических устройств

разной разрядности

RusAutoCon-2025

11 of 16

12.

Верификация синтезированной самосинхронной схемыРезультат синтеза

самосинхронной

схемы

Система

функциональнологического

моделирования

Modelsim

Проверка

функционирования

схемы

Анализ схемы на

самосинхронность

Система

классификационного

анализа АСКЕТ

Физический синтез

самосинхронной

схемы

ФИЦ ИУ РАН

RusAutoCon-2025

12 of 16

13.

Классификационный анализ на самосинхронность(программа АСКЕТ, ФИЦ «ИУ» РАН)

1. Построение замыкания схемы (эмуляция

входного и выходного интерфейса

синтезированной схемы)

2. Вычисление начального состояния схемы,

соответствующего спейсерному состоянию

ее входов

3. Последовательный перебор рабочих

состояний входов схемы, гарантирующий

полноту анализа на самосинхронность

Генератор рабочих

состояний входов

Генератор фаз

Анализируемая схема

4. Проверка схемы на отсутствие нарушений

самосинхронности (событийный подход)

Индикатор

ФИЦ ИУ РАН

RusAutoCon-2025

13 of 16

14.

Время анализа на самосинхронностьФИЦ ИУ РАН

RusAutoCon-2025

14 of 16

15.

Синтез и анализ на самосинхронность тестовых примеровФИЦ ИУ РАН

RusAutoCon-2025

15 of 16

16.

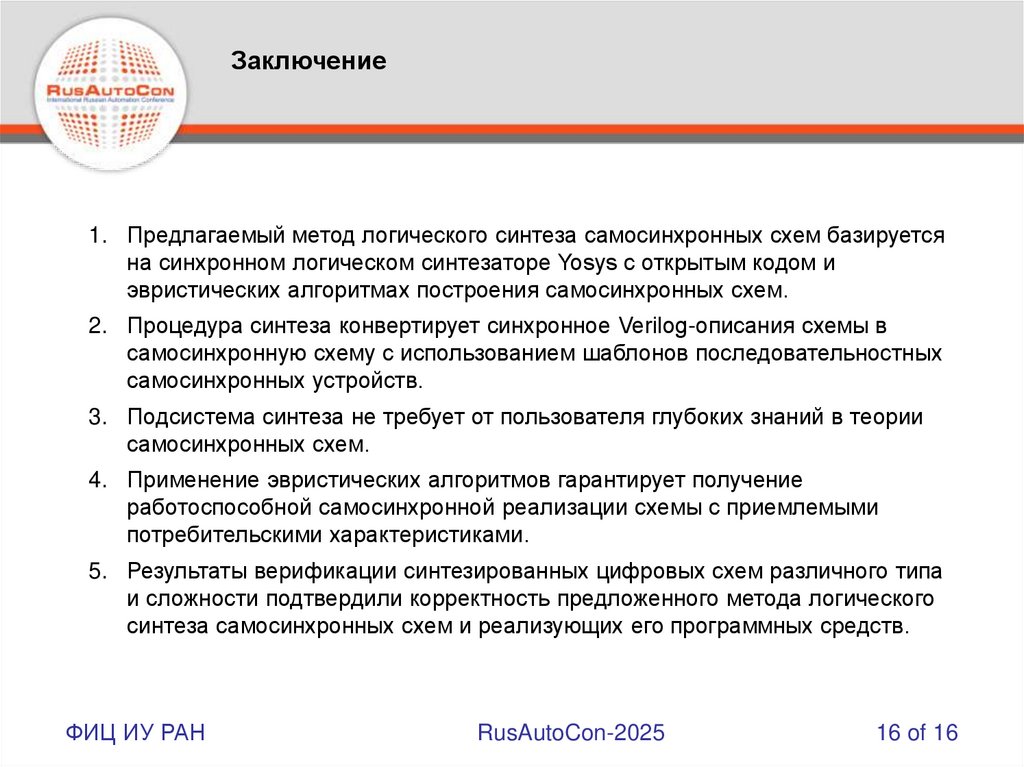

Заключение1. Предлагаемый метод логического синтеза самосинхронных схем базируется

на синхронном логическом синтезаторе Yosys с открытым кодом и

эвристических алгоритмах построения самосинхронных схем.

2. Процедура синтеза конвертирует синхронное Verilog-описания схемы в

самосинхронную схему с использованием шаблонов последовательностных

самосинхронных устройств.

3. Подсистема синтеза не требует от пользователя глубоких знаний в теории

самосинхронных схем.

4. Применение эвристических алгоритмов гарантирует получение

работоспособной самосинхронной реализации схемы с приемлемыми

потребительскими характеристиками.

5. Результаты верификации синтезированных цифровых схем различного типа

и сложности подтвердили корректность предложенного метода логического

синтеза самосинхронных схем и реализующих его программных средств.

ФИЦ ИУ РАН

RusAutoCon-2025

16 of 16

informatics

informatics