Similar presentations:

Генератор импульсной последовательности с заданными свойствами

1.

guap.ruИтоговый проект

«Генератор импульсной

последовательности с заданными

свойствами

»«Проектирование на FPGA»

Выполнил: студент гр 4921

Чуваев К.И.

2.

guap.ruТребования к разрабатываемому устройству

Требованием к проектированию Генератор импульсной последовательности с

заданными свойствами заключается в следующем: необходимо разработать

схему, период выходного сигнала которой (Твых) в целое число раз больше

периода входного сигнала (Твх), с заданной длительностью фазы состояния

высокого логического уровня (K1 тактов) и фазы низкого логического уровня

(K0 тактов), при этом выполняется соотношение: (K1 + K0)Tвх = Tвых

2

3.

guap.ruРаспределение задач проекта

Лидер команды: Чуваев К.И.

Ответственные за задачи:

1. Проектирование схемы устройства в графическом редакторе: Чуваев К.И.

2. Проектирование схемы устройства на Verilog: Репкин А.С.

3. Тестирование работы спроектированного устройства: Бобрышов Д.П.

3

4.

guap.ruОписание принципа работы устройства

Генератор импульсной последовательности основан на использовании комбинационной

логики и триггеров. При заданных условиях длительности высокого (K1 = 8) и низкого (K2 = 9)

логических уровней, с помощью триггеров формируется последовательно-параллельный

регистр

сдвига с обратной связью. Работа генератора начинается с определенного

состояния (Kнач = 0) и тактируется внешним сигналов (clk). После достижения определенного

количества тактов низкого и высокого логического уровня генератор возвращается к своему

начальному состоянию и начинает цикл заново.

4

5.

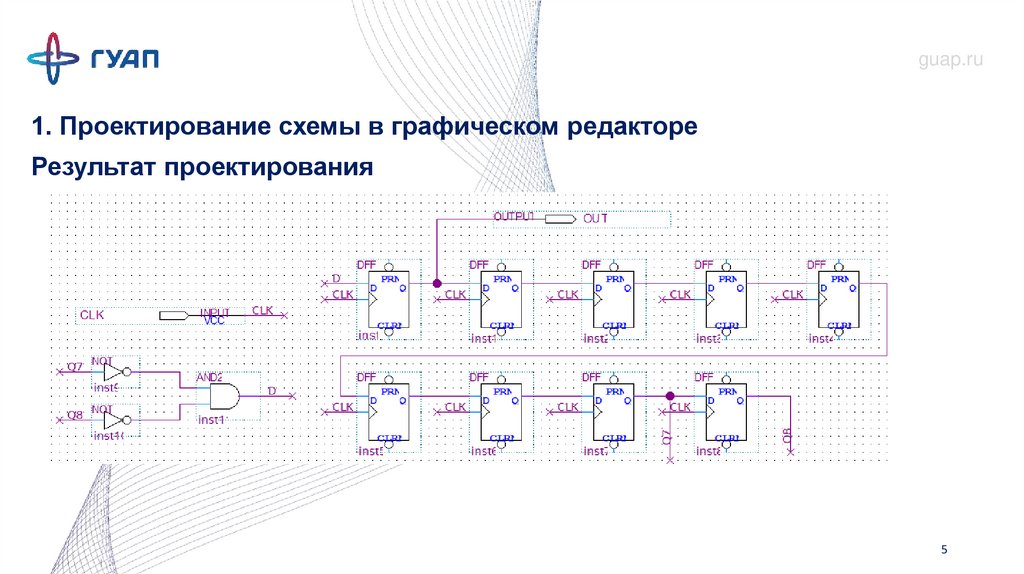

guap.ru1. Проектирование схемы в графическом редакторе

Результат проектирования

5

6.

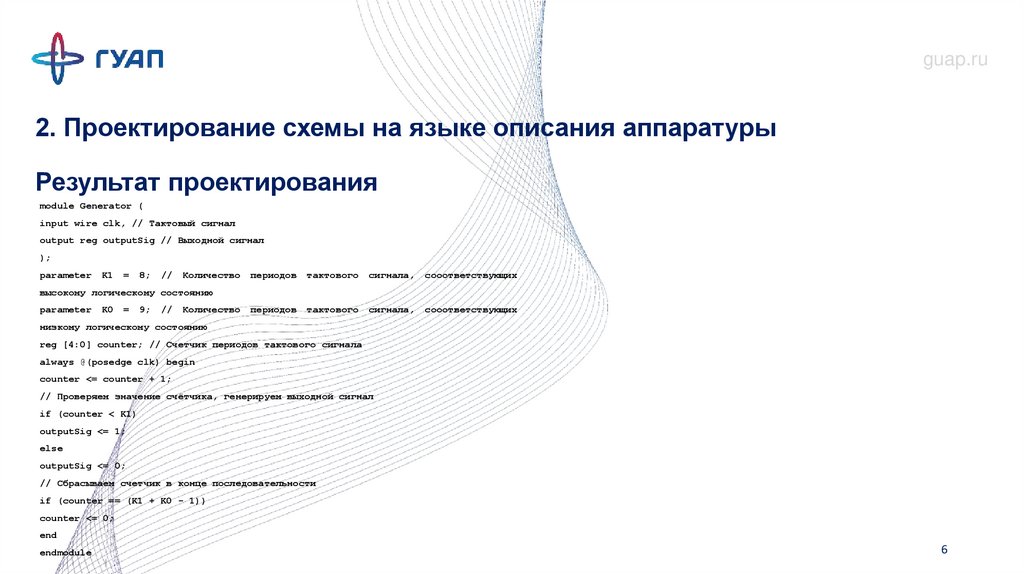

guap.ru2. Проектирование схемы на языке описания аппаратуры

Результат проектирования

module Generator (

input wire clk, // Тактовый сигнал

output reg outputSig // Выходной сигнал

);

parameter

K1

=

8;

//

Количество

периодов

тактового

сигнала,

сооответствующих

периодов

тактового

сигнала,

сооответствующих

высокому логическому состоянию

parameter

K0

=

9;

//

Количество

низкому логическому состоянию

reg [4:0] counter; // Счетчик периодов тактового сигнала

always @(posedge clk) begin

counter <= counter + 1;

// Проверяем значение счётчика, генерируем выходной сигнал

if (counter < K1)

outputSig <= 1;

else

outputSig <= 0;

// Сбрасываем счетчик в конце последовательности

if (counter == (K1 + K0 - 1))

counter <= 0;

end

endmodule

6

7.

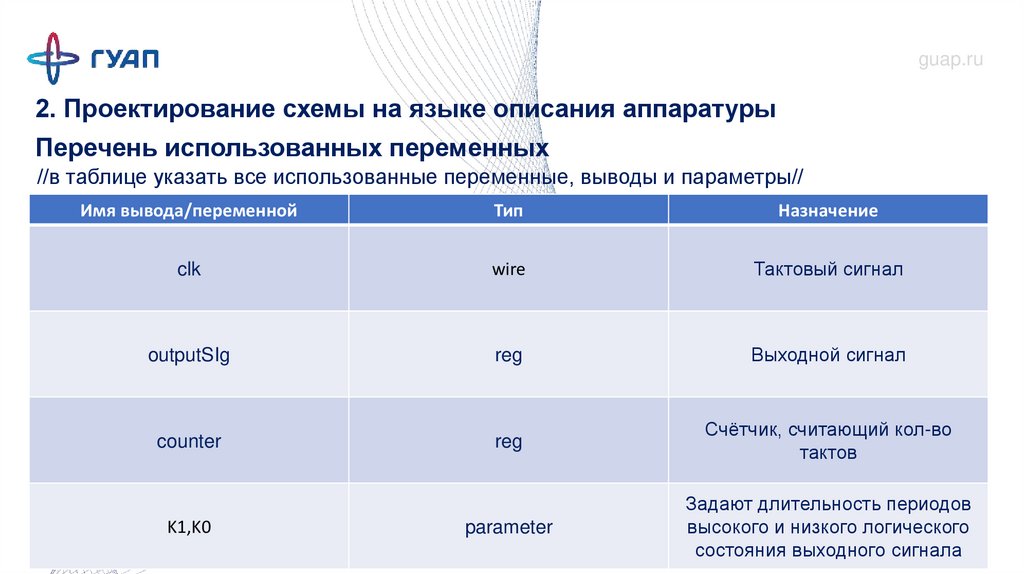

guap.ru2. Проектирование схемы на языке описания аппаратуры

Перечень использованных переменных

//в таблице указать все использованные переменные, выводы и параметры//

Имя вывода/переменной

Тип

Назначение

clk

wire

Тактовый сигнал

outputSIg

reg

Выходной сигнал

counter

reg

Счётчик, считающий кол-во

тактов

parameter

Задают длительность периодов

высокого и низкого логического

7

состояния выходного сигнала

K1,K0

8.

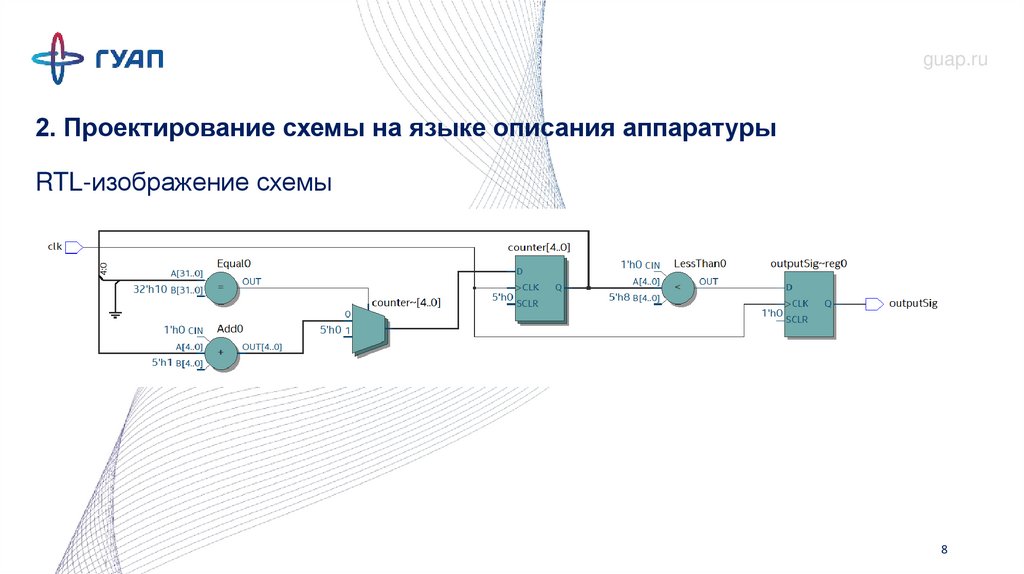

guap.ru2. Проектирование схемы на языке описания аппаратуры

RTL-изображение схемы

8

9.

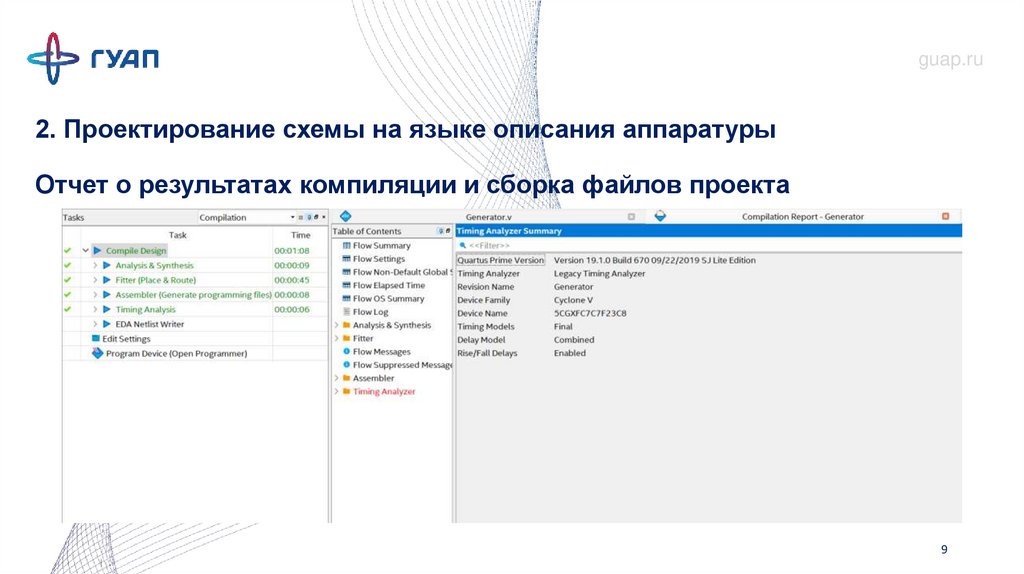

guap.ru2. Проектирование схемы на языке описания аппаратуры

Отчет о результатах компиляции и сборка файлов проекта

9

10.

guap.ru3. Тестирование разработанного устройства

Алгоритм тестирования

Для тестирования формирователя импульсной последовательности нецелесообразно

написание тест-бенча, т.к нет вариативных наборов входных данных – только тактовый

сигнал с заданными параметрами.

Для проверки устройства мы использовали vector waveform файл, в котором задали тактовый

сигнал и визуально сравнили выходной сигнал с требуемым техническим заданием.

10

11.

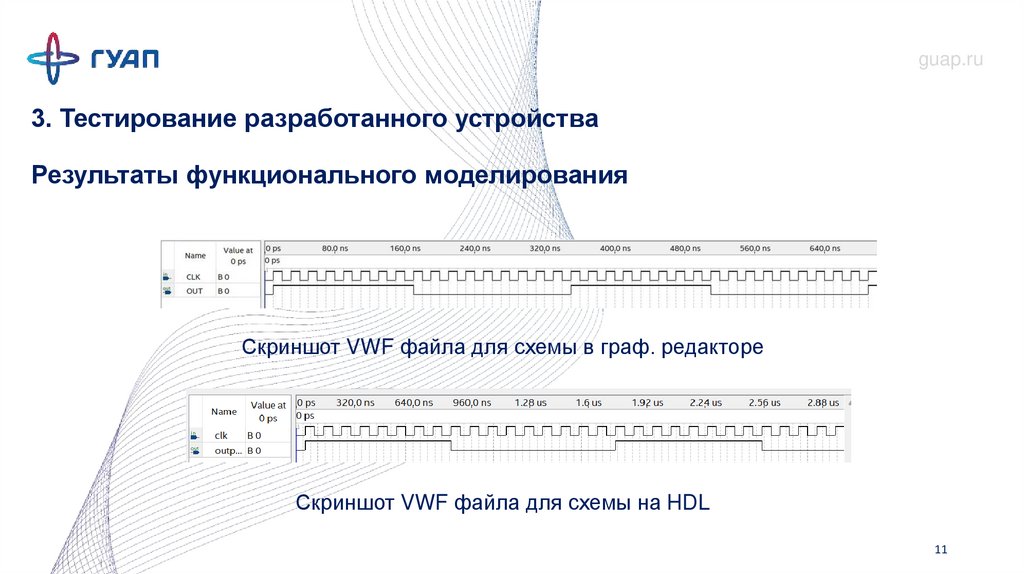

guap.ru3. Тестирование разработанного устройства

Результаты функционального моделирования

Скриншот VWF файла для схемы в граф. редакторе

Скриншот VWF файла для схемы на HDL

11

12.

guap.ru3. Тестирование разработанного устройства

Заключение

Спроектировали генератор последовательности в виде графической схемы и в виде модуля

Verilog

Провели тестирование с помощью vector waveform и убедились в правильности

спроектированных устройств.

12

13.

guap.ruСпасибо за внимание

Выполнил: студент гр 4921

Чуваев Константин

electronics

electronics