Similar presentations:

Основы микропроцессорной техники

1.

Основы микропроцессорной техникиНГТУ, Нижний Новгород, 2021

2.

Работа таймеров/счетчиковТаймеры-счётчики – это

такие устройства или модули

в микроконтроллере, которые

считают такты работы МК до

заданной величины, либо до

величины, ограниченной

разрядностью регистра этого

счетчика

Прерывания (Interrupts)

– это такие механизмы,

которые прерывают код в

зависимости от

определённых условий

2

3.

Регистры таймеров/счетчиковTCNTn - данный регистр хранит число, до которого и досчитал таймер. (nномер таймера)

OCRnA и OCRnB - это регистры, в которые заносится число, с которым

будет сравниваться значение в регистре TCNTn

TCCRnA и TCCRnB – регистры памяти 16-разрядного таймера

TCCR - это регистр управления, в котором настраивается конфигурация

таймера ( к примеру установка делителя

CTC – бит, очищающий регистр TCNTn при совпадении с регистром

OCRnA (OCRnB)

3

4.

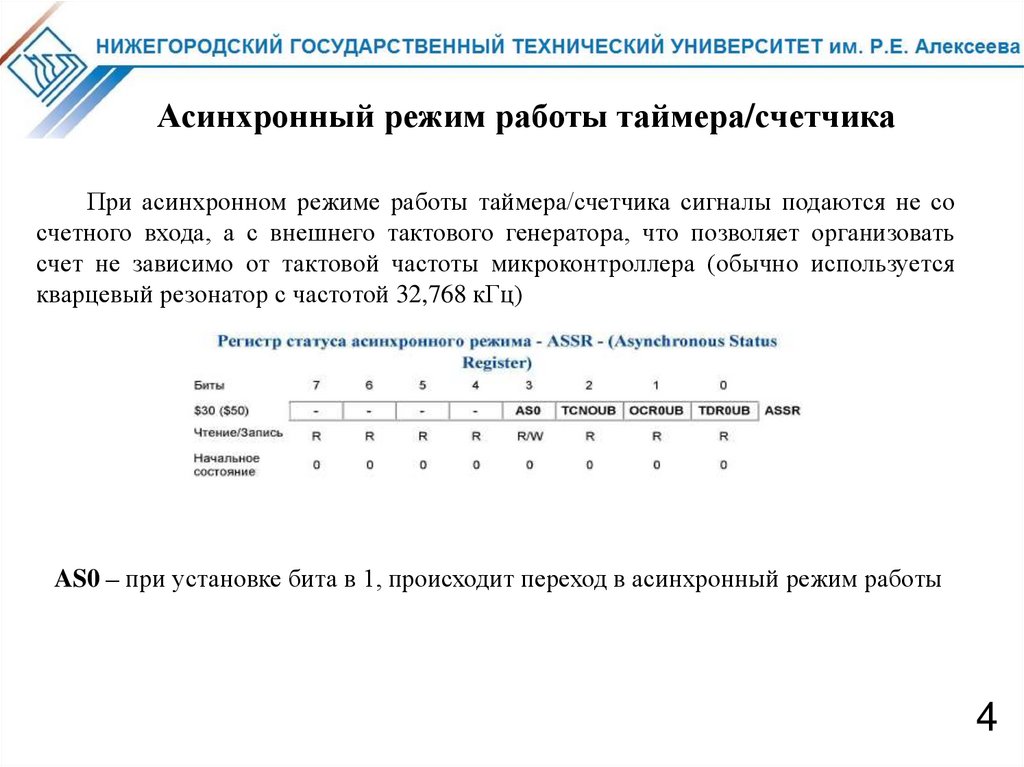

Асинхронный режим работы таймера/счетчикаПри асинхронном режиме работы таймера/счетчика сигналы подаются не со

счетного входа, а с внешнего тактового генератора, что позволяет организовать

счет не зависимо от тактовой частоты микроконтроллера (обычно используется

кварцевый резонатор с частотой 32,768 кГц)

AS0 – при установке бита в 1, происходит переход в асинхронный режим работы

4

5.

Подсистема сброса и прерыванийAtmega16 имеет 22 вектора

(источника) прерывания и 1

вектор сброса.

Reset имеет наивысший

уровень приоритета.

5

6.

Источники сброса1) Сброс по включению питания

2) Внешний сброс (пин RESET)

3) Сброс по сторожевому таймеру

6

7.

Обработка прерыванийПроцедура обработки прерывания (Interrupt Service Routine) – это ни что иное как

функция/подпрограмма, которую следует выполнить при возникновении

определенного события. Будем использовать именно слово "процедура”, для того

чтобы подчеркнуть ее отличие от всех остальных функций.

Отклик на выполнение всех разрешенных прерываний AVR составляет минимум 4

тактовых цикла. В течение 4 тактовых циклов после установки флага прерывания

выполняется переход по адресу вектора прерывания для выполнения

подпрограммы прерывания.

7

8.

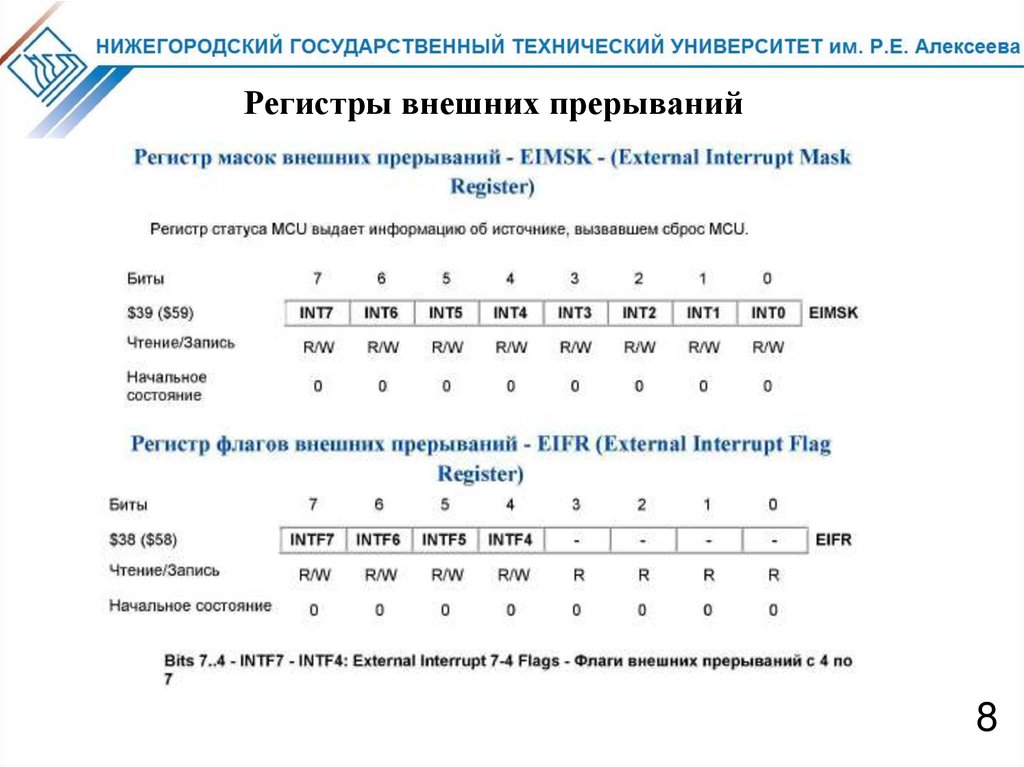

Регистры внешних прерываний8

9.

Регистры прерываний по таймерам/счетчикам9

10.

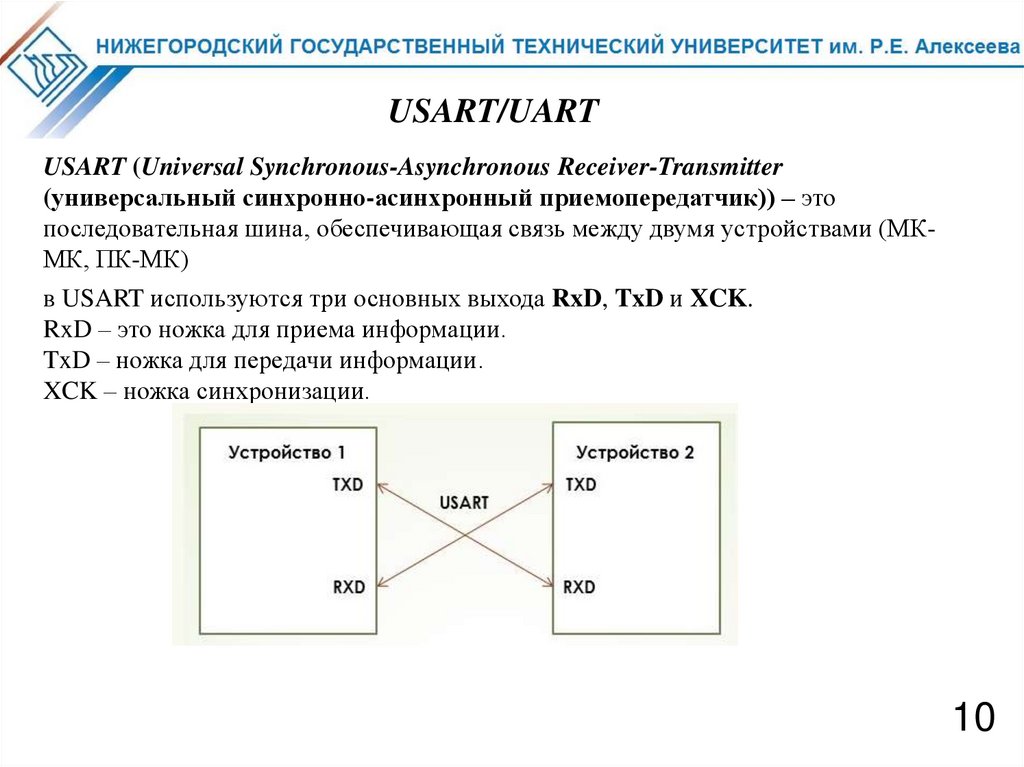

USART/UARTUSART (Universal Synchronous-Asynchronous Receiver-Transmitter

(универсальный синхронно-асинхронный приемопередатчик)) – это

последовательная шина, обеспечивающая связь между двумя устройствами (МКМК, ПК-МК)

в USART используются три основных выхода RxD, TxD и XCK.

RxD – это ножка для приема информации.

TxD – ножка для передачи информации.

XCK – ножка синхронизации.

10

11.

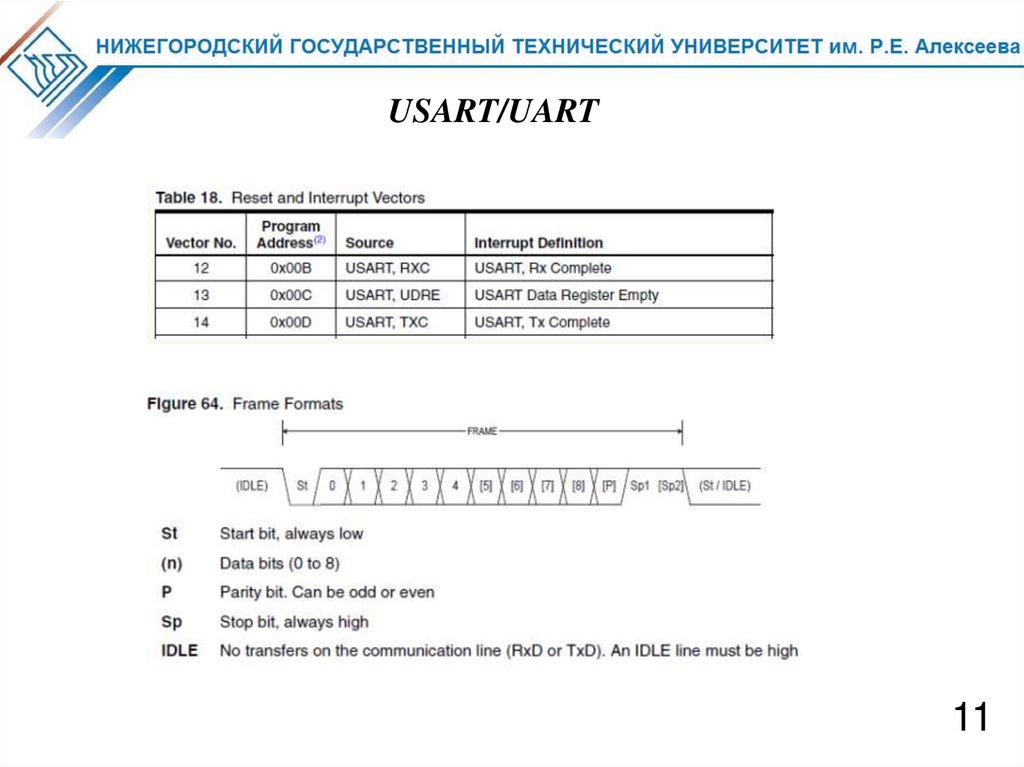

USART/UART11

12.

USART/UART оценка скорости12

13.

USART/UART регистрыУ интерфейса USART в контроллере Atmega8 существует три регистра управления –

UCSRA, UCSRB и UCSRC

RXC – это бит состояния приемной шины. То есть передался пакет в шину – флаг

установился. Можно отслеживать в цикле, чтобы узнать, пришёл ли пакет в

данную шину.

TXC – бит состояния шины передачи. Назначение аналогично вышеуказанному,

но только данный бит уже может изменяться программно, то есть он также и на

запись.

UDRE – бит освобождения регистра данных.

FE – бит также флаговый и устанавливается он в случае ошибки передачи пакета.

U2X –бит используется для удвоения скорости приёма-передачи данных по шине.

13

14.

USART/UART регистрыРегистровая пара UBRR отвечает за установку скорости. Она состоит из двух

регистров UBRRH и UBRRL, Первый отвечает за старшую часть двухбайтовой

величины регистра, а второй – за младшую

регистр данных USART

14

15.

RISC-микроконтроллерыRISC (Restricted (Reduced) Instruction Set Computer - компьютер с сокращенным

набором команд) - архитектура процессора, в которой быстродействие

увеличивается за счет упрощения инструкций, чтобы их декодирование было

более простым, а время выполнения - короче. В процессорах с RISCархитектурой используется ограниченный набор быстрых команд. Каждая

команда RISC-процессора должна выполняться за один машинный такт. В таких

микропроцессорах содержится меньшее количество транзисторов, что снижает

их стоимость и энергопотребление.

Архитектура RISC-процессоров характеризуется наличием команд

фиксированной длины, большого количества регистров, операций типа регистррегистр, а также отсутствием косвенной адресации.

15

electronics

electronics