Similar presentations:

Оптимизация конструкции NMOS - транзисторов для повышения стойкости к электростатическому разряду

1. ОПТИМИЗАЦИЯ КОНСТРУКЦИИ NMOS-ТРАНЗИСТОРОВ ДЛЯ ПОВЫШЕНИЯ СТОЙКОСТИ К ЭЛЕКТРОСТАТИЧЕСКОМУ РАЗРЯДУ

1ОПТИМИЗАЦИЯ КОНСТРУКЦИИ NMOSТРАНЗИСТОРОВ

ДЛЯ ПОВЫШЕНИЯ СТОЙКОСТИ К

ЭЛЕКТРОСТАТИЧЕСКОМУ РАЗРЯДУ

БОРОННИКОВА И.И.

СТУДЕНКА 2-ГО КУРСА МАГИСТРАТУРЫ КАФЕДРЫ ФИЗИКИ

ПОЛУПРОВОДНИКОВ И МИКРОЭЛЕКТРОНИКИ

РУКОВОДИТЕЛЬ – К.Т.Н., ДОЦЕНТ КАФЕДРЫ ФИЗИКИ ПОЛУПРОВОДНИКОВ

И МИКРОЭЛЕКТРОНИКИ БЫКАДОРОВА Г.В.

2.

Проблемы ESD-воздействия на микросхемыа

б

в

Повреждение схемы от электростатического разряда: а – разрушение

диэлектрика, б – скрытое повреждение; в - разрушение металлизации

2

3.

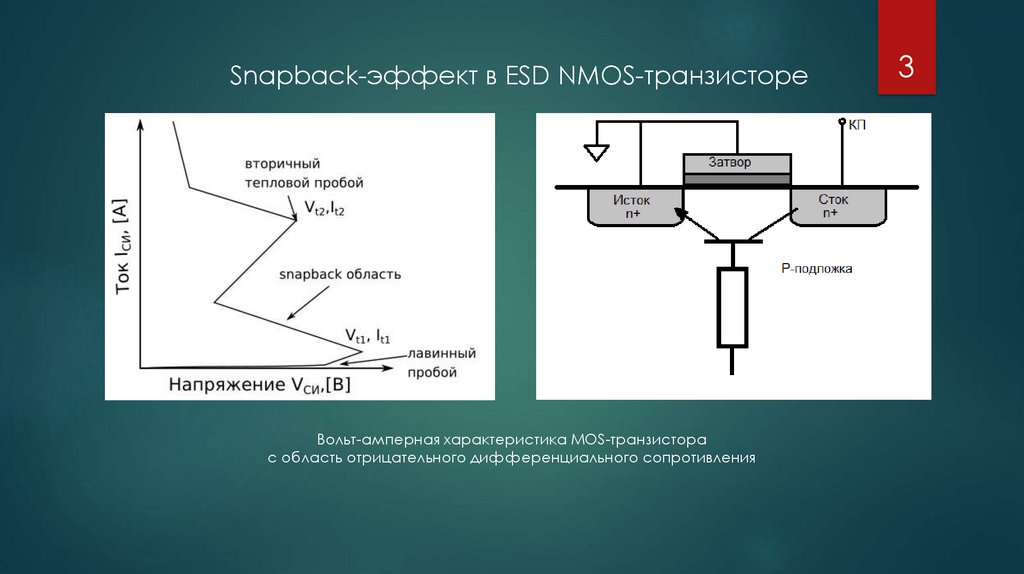

Snapback-эффект в ESD NMOS-транзистореВольт-амперная характеристика MOS-транзистора

с область отрицательного дифференциального сопротивления

3

4.

Цель работы: разработка способов повышения стойкости к ESDвоздействию NMOS-транзисторов технологии КНИ КМОП 0.6 мкм вфизико-технологической САПР Sentaurus TCAD.

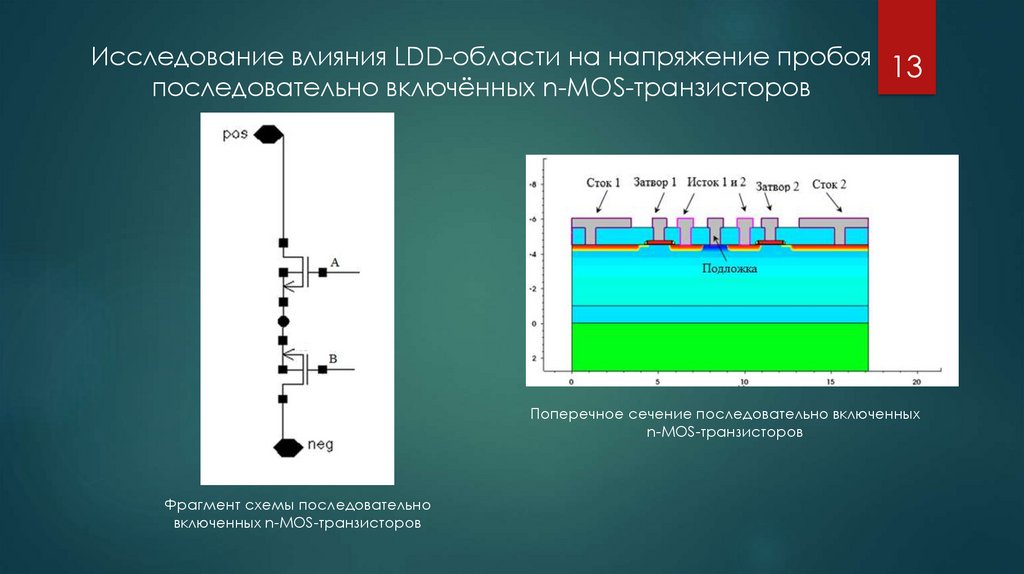

Объект исследования: обособленные и последовательно

включенные NMOS транзисторы с различными длинами канала и LDD-областей

Поставленные задачи:

построение физико-технологической модели n-MOS транзистора

калибровка технологических параметров n-MOS-транзистора

определение влияния длины затвора на основные ESD-характеристики n-MOSтранзистора

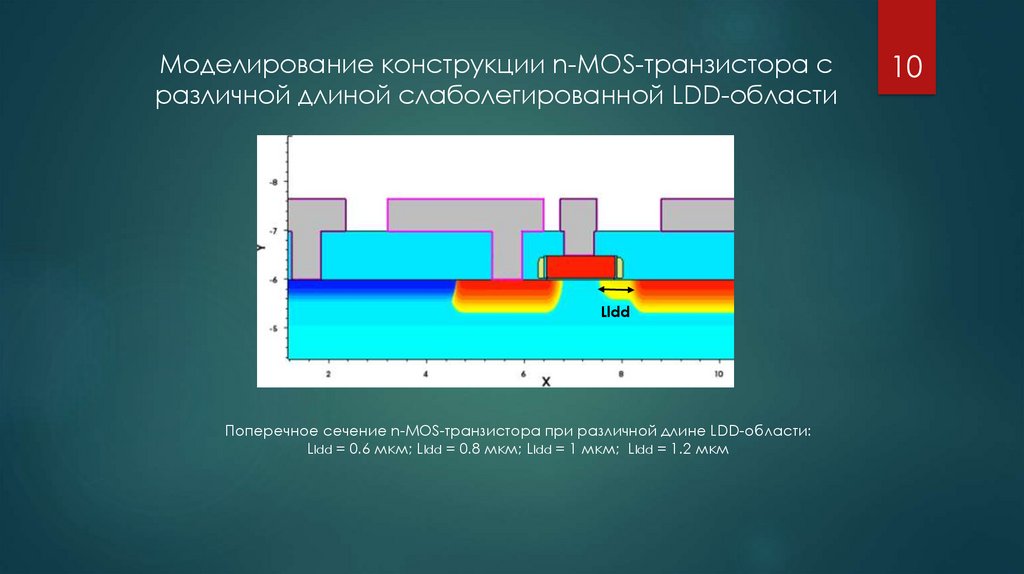

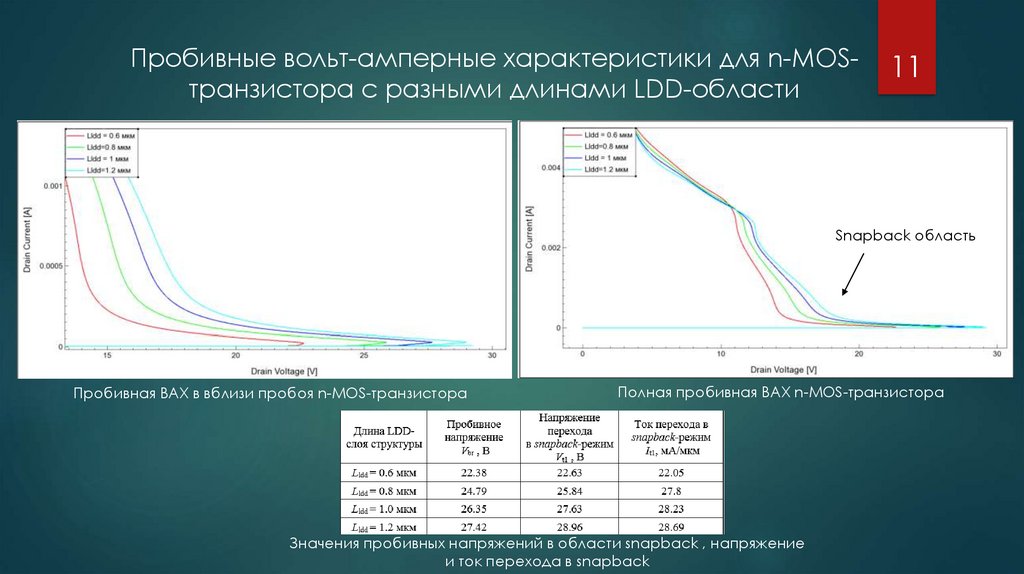

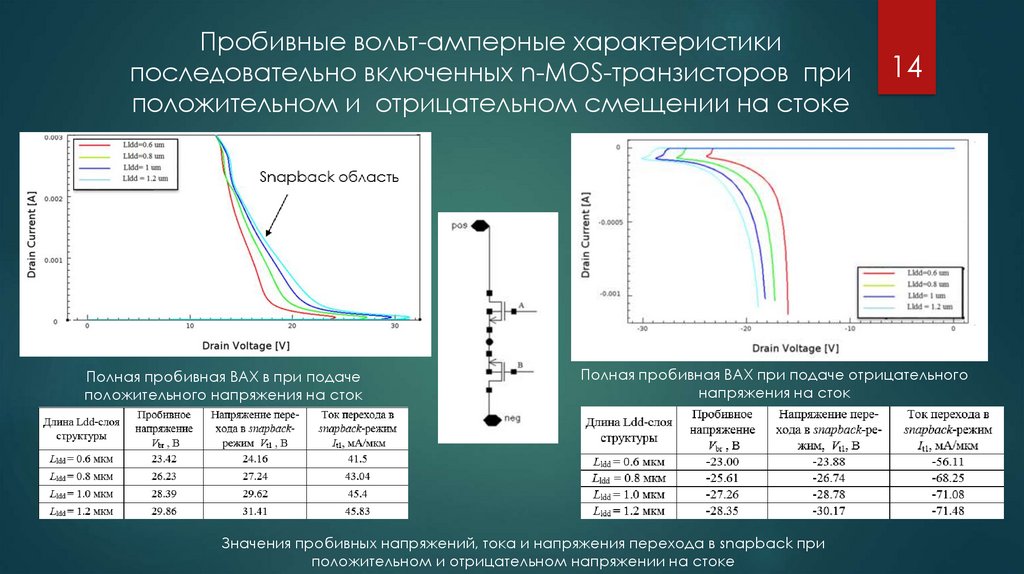

определение влияния LDD-области на основные ESD-характеристики n-MOSтранзистора

4

5.

Программная среда САПР Sentaurus TCAD дляисследования способов повышения стойкости к ESDвоздействию NMOS-транзисторов

5

6.

Построение приборно-технологической моделиn-MOS-транзистора

Поперечное сечение A

Топологический вид n-MOS-транзистора

со слаболегированной LDD-областью nтипа (Lightly Doped Drain)

Поперечное сечение n-MOS-транзистора со

слаболегированной LDD-областью nтипа(Lightly Doped Drain)

6

7.

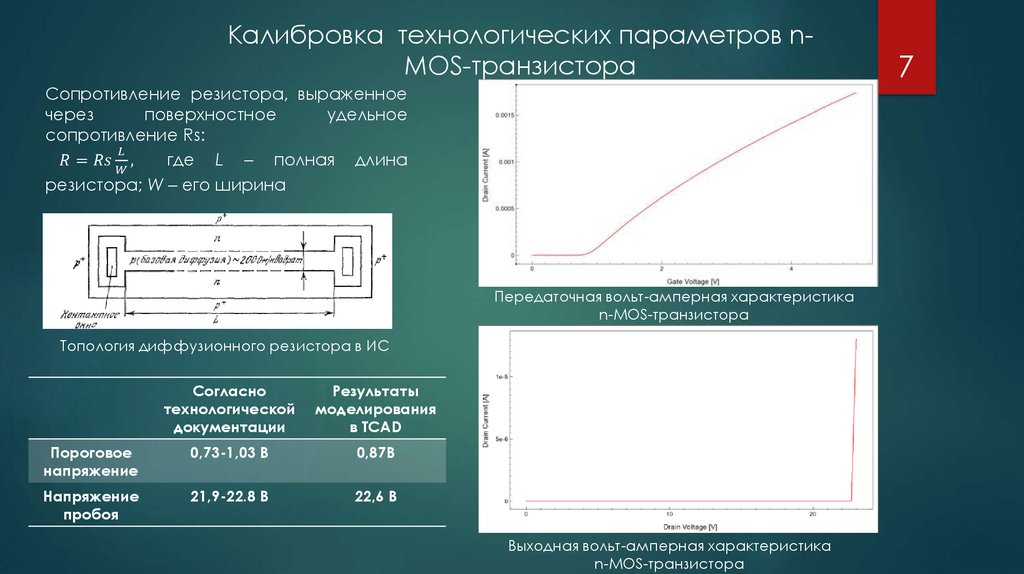

Калибровка технологических параметров nMOS-транзистораСопротивление резистора, выраженное

через

поверхностное

удельное

сопротивление Rs:

electronics

electronics