Similar presentations:

Определение параметров устройств защиты от ESD на основе высоковольтных транзисторов

1. Определение параметров устройств защиты от ESD на основе высоковольтных транзисторов

Воронежский государственный университетДобавить ФИО

2. ESD разряд

ESD (Electrostatic discharge)— резкий скачок напряжения,вызванный соприкасающимися или находящимися в

непосредственной близости заряженными объектами. Он

возникает вследствие трибоэлектрического эффекта, т. е.

перехода электронов с поверхности одного тела на

поверхность другого в результате трения. Чаще всего

причиной воздействия ESD на микросхему становится

прикосновение человека, переносящего этот заряд.

ESD разряд

Повреждение микросхемы ESD разрядом

3. МОП-транзисторы как устройства защиты от ESD

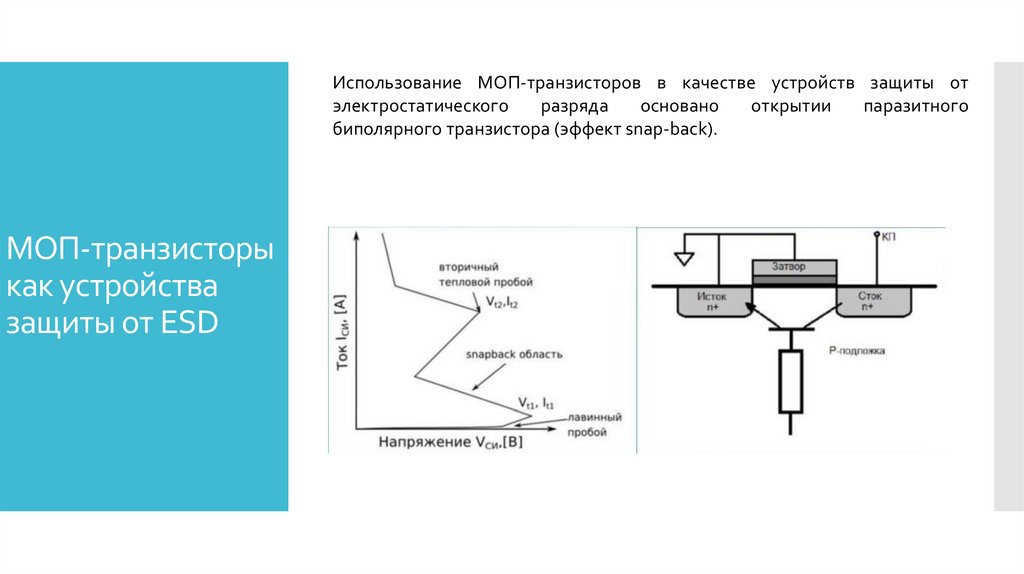

Использование МОП-транзисторов в качестве устройств защиты отэлектростатического

разряда

основано

открытии

паразитного

биполярного транзистора (эффект snap-back).

МОП-транзисторы

как устройства

защиты от ESD

4.

Современные микросхемы приемо-передатчиков, dc-dc преобразователей,automotive устройств, power-management систем выполняются по BCD или

КМОП технологиям, где в едином технологическом процессе изготавливаются

как низковольтные, так и высоковольтные транзисторы.

Высоковольтные транзисторы выполненные в КМОП или BCD технологии как

правило, имеют низкий уровень стойкости к ESD из-за тонкого подзатворного

диэлектрика (как у низковольтных приборов), наличия высокоомных областей

в стоке с высокой плотностью протекающего тока, что приводит к их

тепловому разрушению.

5. Актуальность

Цель работы: определение основных ESD характеристик 40В NMOSтранзисторов выполненных по технологии КНИ КМОП 180 нм для

разработки устройств защиты от электростатического разряда

микросхем.

Задачи:

Актуальность

TLP-исследование 40В NMOS транзисторов разных конструкций с

заземленным затвором

TLP-исследование 40В NMOS транзисторов с запускающей схемой

выполненной на цепочке диодов Зенера

Исследование конструкций транзисторов

Определение основных ESD характеристик исследуемых транзисторов

(напряжения пробоя, ток вторичного пробоя)

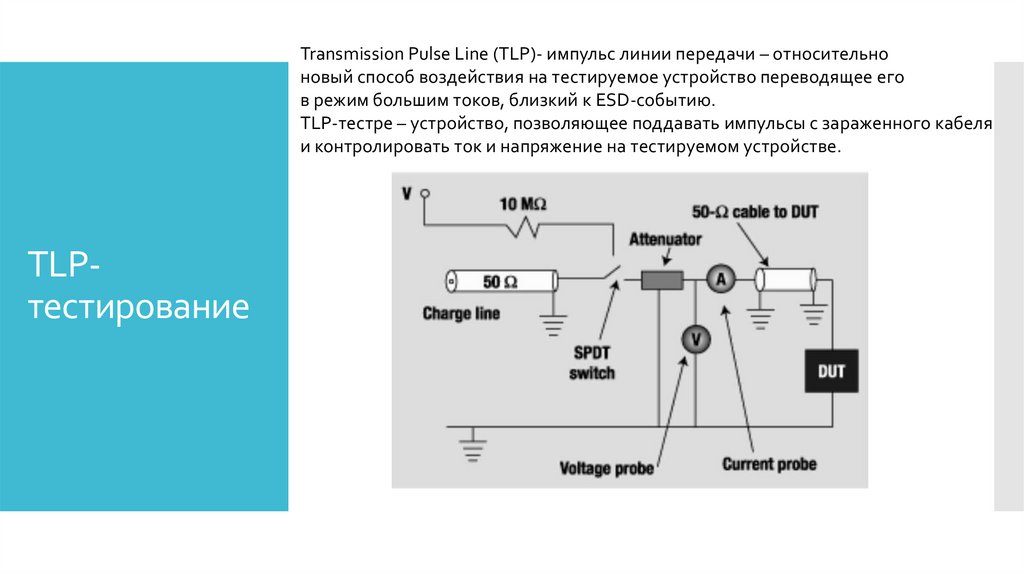

6. TLP- тестирование

Transmission Pulse Line (TLP)- импульс линии передачи – относительноновый способ воздействия на тестируемое устройство переводящее его

в режим большим токов, близкий к ESD-событию.

TLP-тестре – устройство, позволяющее поддавать импульсы с зараженного кабеля

и контролировать ток и напряжение на тестируемом устройстве.

TLPтестирование

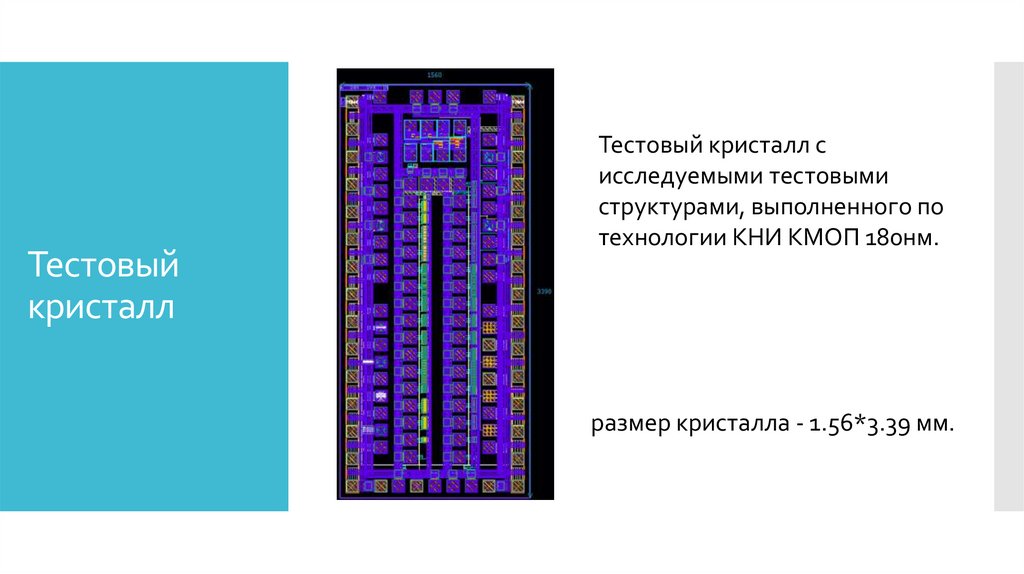

7. Тестовый кристалл

Тестовый кристалл сисследуемыми тестовыми

структурами, выполненного по

технологии КНИ КМОП 180нм.

размер кристалла - 1.56*3.39 мм.

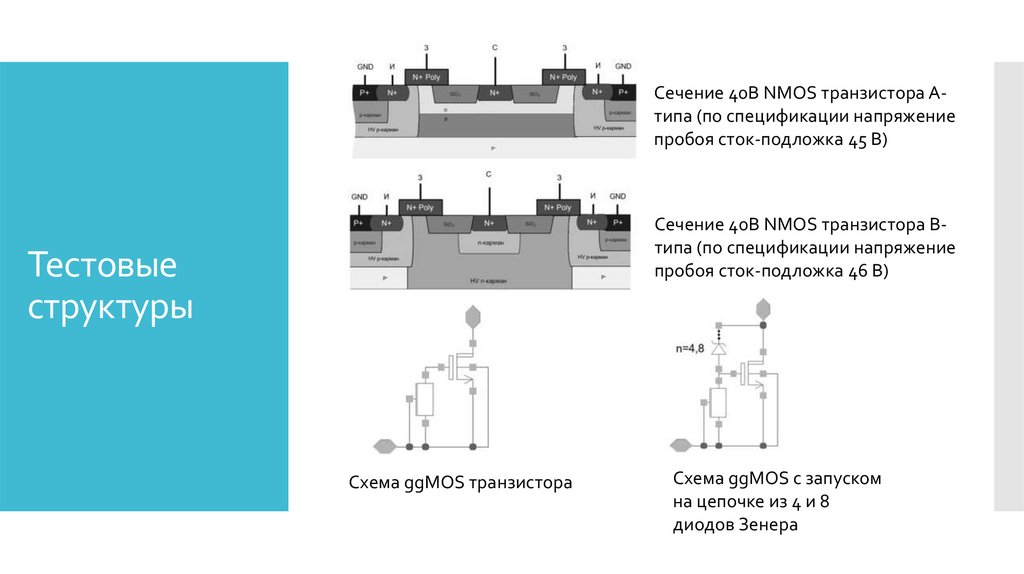

8. Тестовые структуры

Сечение 40В NMOS транзистора Атипа (по спецификации напряжениепробоя сток-подложка 45 В)

Сечение 40В NMOS транзистора Bтипа (по спецификации напряжение

пробоя сток-подложка 46 В)

Тестовые

структуры

Схема ggMOS транзистора

Схема ggMOS с запуском

на цепочке из 4 и 8

диодов Зенера

9. Результаты TLP-исследований 40В NMOS транзисторов A-типа

Результаты TLPисследований 40ВNMOS

транзисторов Aтипа

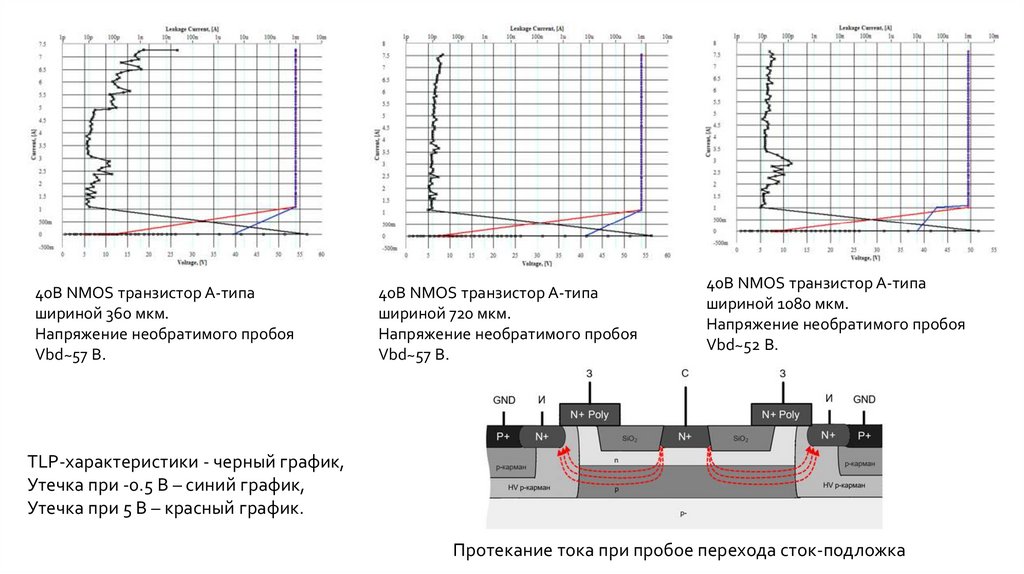

10.

40В NMOS транзистор A-типашириной 360 мкм.

Напряжение необратимого пробоя

Vbd~57 В.

40В NMOS транзистор A-типа

шириной 720 мкм.

Напряжение необратимого пробоя

Vbd~57 В.

40В NMOS транзистор A-типа

шириной 1080 мкм.

Напряжение необратимого пробоя

Vbd~52 В.

TLP-характеристики - черный график,

Утечка при -0.5 В – синий график,

Утечка при 5 В – красный график.

Протекание тока при пробое перехода сток-подложка

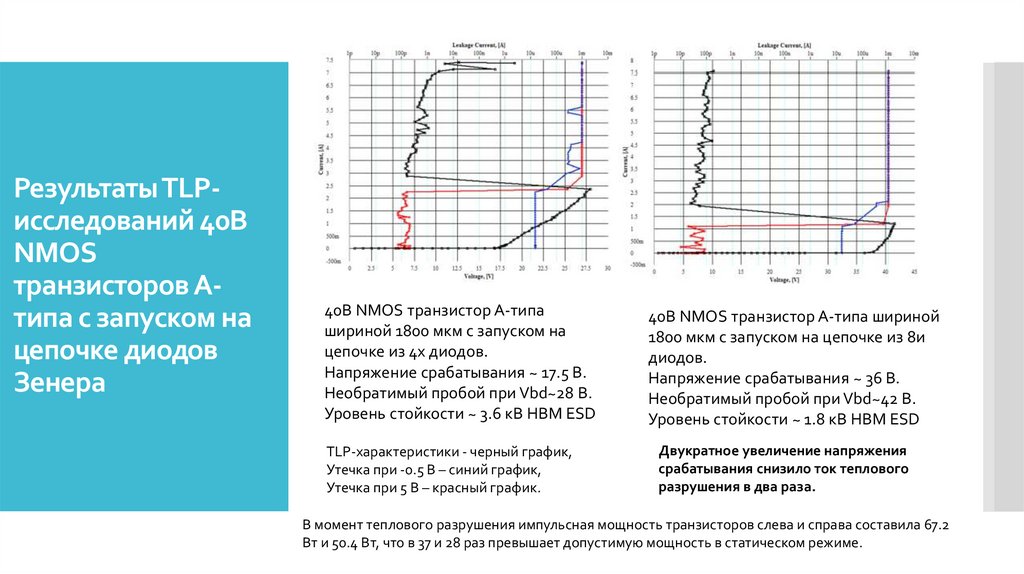

11. Результаты TLP-исследований 40В NMOS транзисторов A-типа с запуском на цепочке диодов Зенера

Результаты TLPисследований 40ВNMOS

транзисторов Aтипа с запуском на

цепочке диодов

Зенера

40В NMOS транзистор A-типа

шириной 1800 мкм с запуском на

цепочке из 4х диодов.

Напряжение срабатывания ~ 17.5 В.

Необратимый пробой при Vbd~28 В.

Уровень стойкости ~ 3.6 кВ HBM ESD

TLP-характеристики - черный график,

Утечка при -0.5 В – синий график,

Утечка при 5 В – красный график.

40В NMOS транзистор A-типа шириной

1800 мкм с запуском на цепочке из 8и

диодов.

Напряжение срабатывания ~ 36 В.

Необратимый пробой при Vbd~42 В.

Уровень стойкости ~ 1.8 кВ HBM ESD

Двукратное увеличение напряжения

срабатывания снизило ток теплового

разрушения в два раза.

В момент теплового разрушения импульсная мощность транзисторов слева и справа составила 67.2

Вт и 50.4 Вт, что в 37 и 28 раз превышает допустимую мощность в статическом режиме.

12. Результаты TLP-исследований 40В NMOS транзисторов В-типа

РезультатыTLPисследований

40В NMOS

транзисторов

В-типа

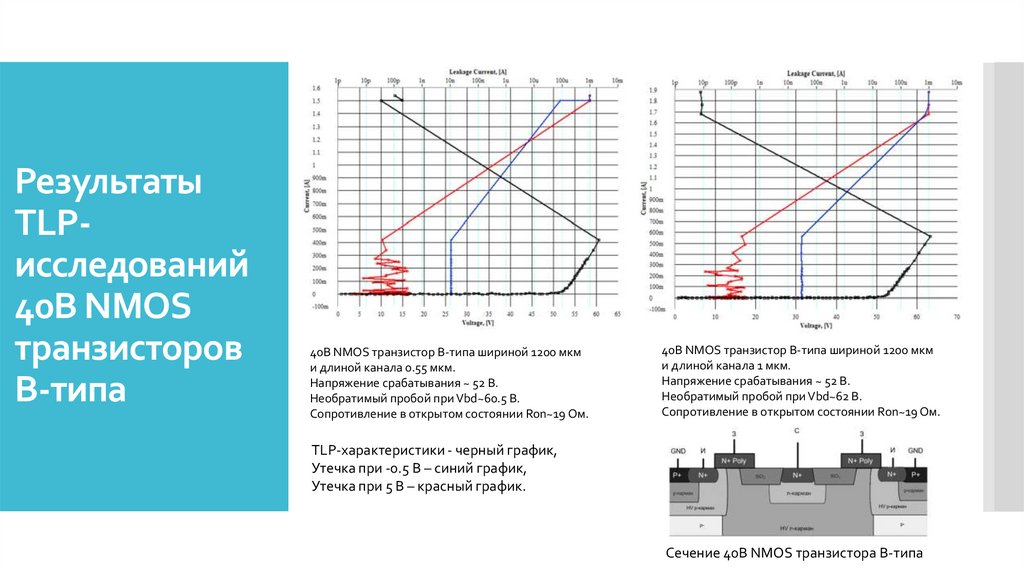

40В NMOS транзистор В-типа шириной 1200 мкм

и длиной канала 0.55 мкм.

Напряжение срабатывания ~ 52 В.

Необратимый пробой при Vbd~60.5 В.

Сопротивление в открытом состоянии Ron~19 Ом.

40В NMOS транзистор В-типа шириной 1200 мкм

и длиной канала 1 мкм.

Напряжение срабатывания ~ 52 В.

Необратимый пробой при Vbd~62 В.

Сопротивление в открытом состоянии Ron~19 Ом.

TLP-характеристики - черный график,

Утечка при -0.5 В – синий график,

Утечка при 5 В – красный график.

Сечение 40В NMOS транзистора B-типа

13. Выводы

Установлено, что 40В NMOS транзисторы А-типа не могут использоваться какустройства защиты от ESD в режиме пробоя из-за необратимого пробоя при

напряжении 52-57В. Анализ конструкции транзистора показал, что наиболее

вероятной причиной крайне низкого уровня стойкости к ESD является низкое

сопротивление n-области стока в режиме пробоя, что приводит к шнурованию

тока.

Показана возможность использоваться 40В NMOS транзисторов А-типа в

качестве устройств защиты от ESD при использовании запускающих цепочек.

Обнаружено, что напряжения пробоя диода Зенера в технологии КНИ КМОП

180 составляет 4.4-4.5 В вместо 5.5 В, как указано фабрикой.

Выводы

Показано, что ширина ключа транзистора определяет уровень стойкости к

ESD, по мере увеличения напряжения срабатывания ширина транзистора

должна быть пропорционально увеличена для обеспечения такого же уровня

стойкости. При увеличении количества диодов в запускающей цепочки с 4 до

8 напряжения срабатывания структуры увеличилось с 17.5 до 36 В, при

уменьшении тока теплового пробоя с 2.4 до 1.2 А.

Выявлено, что 40В NMOS транзисторы B-типа при ESD-стрессе не переходят в

режим snap-back из-за низкого сопротивления подложки после пробоя при 52

В тока разряда протекает через диод HV n-карман – HV p-карман. Определен

максимально допустимый удельный ток теплового пробоя 0.33 мА/мкм, что

можно использовать при разработке устройств защиты от ESD на данных

транзисторах.

Запускающие цепочки могут применяться к разным типам высоковольтных

устройств для нахождения компромиссов между уровнем стойкости и

занимаемой площадью устройств защиты от ESD, а также позволяют

использовать их в качестве защиты от статического превышения напряжения.

electronics

electronics