Similar presentations:

Шинная организация ЭВМ

1. Шинная организация ЭВМ

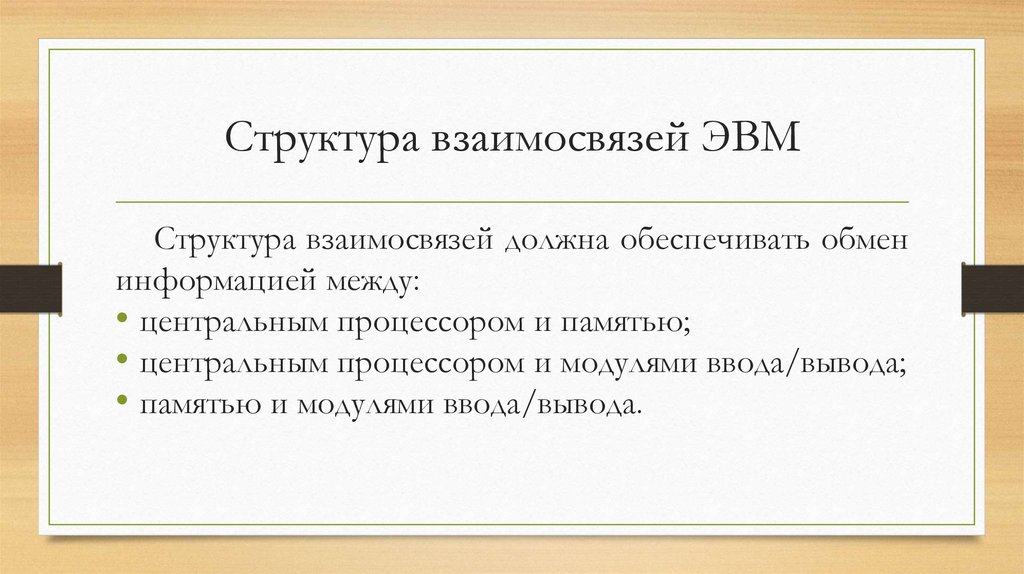

2. Структура взаимосвязей ЭВМ

Структура взаимосвязей должна обеспечивать обменинформацией между:

• центральным процессором и памятью;

• центральным процессором и модулями ввода/вывода;

• памятью и модулями ввода/вывода.

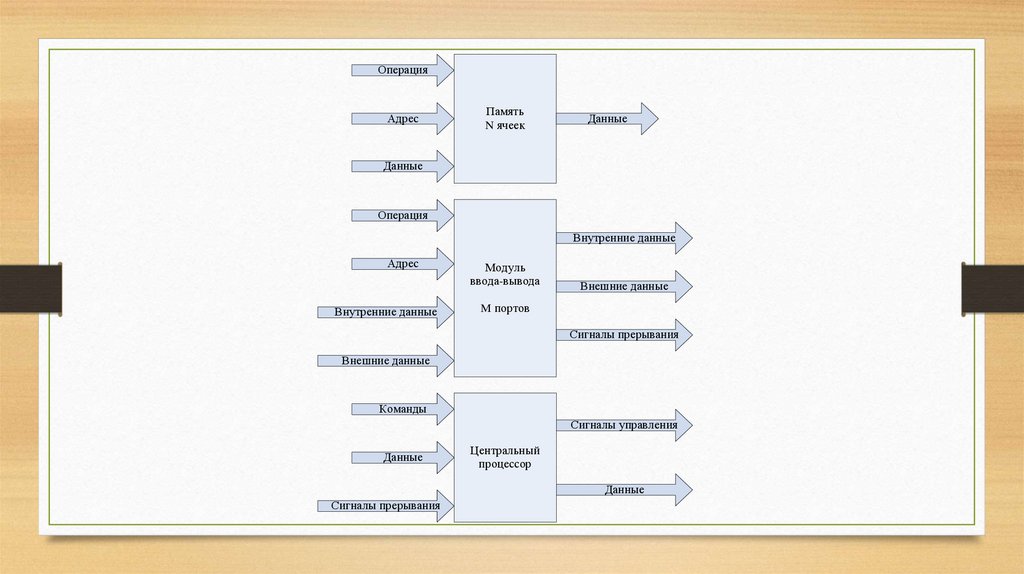

3.

ОперацияАдрес

Память

N ячеек

Данные

Данные

Операция

Внутренние данные

Адрес

Внутренние данные

Модуль

ввода-вывода

Внешние данные

M портов

Сигналы прерывания

Внешние данные

Команды

Сигналы управления

Данные

Центральный

процессор

Данные

Сигналы прерывания

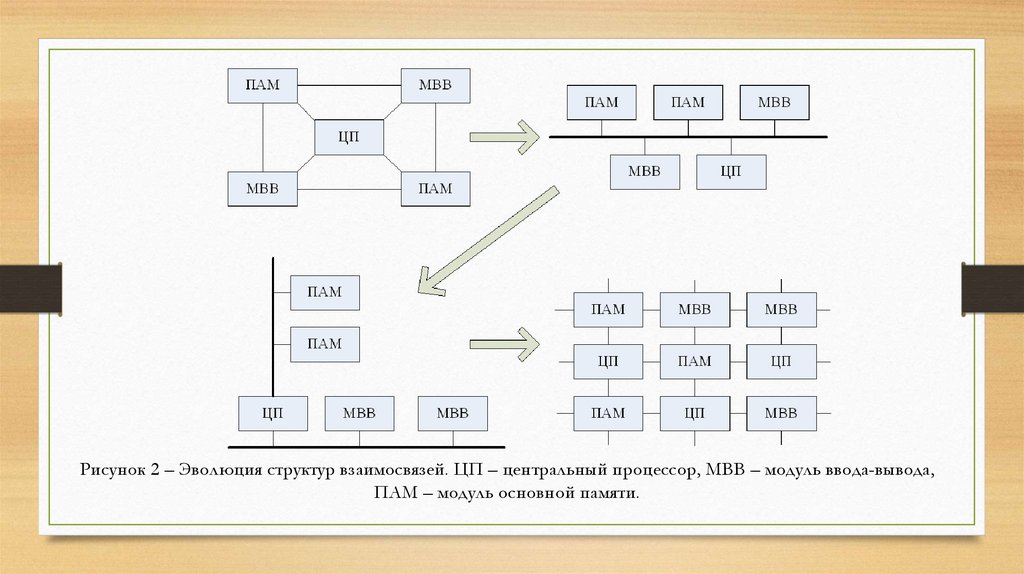

4.

Рисунок 2 – Эволюция структур взаимосвязей. ЦП – центральный процессор, МВВ – модуль ввода-вывода,ПАМ – модуль основной памяти.

5. Интерфейс

Интерфейс - это аппаратное и программноеобеспечение

(элементы

соединения

и

вспомогательные схемы управления, их физические,

электрические

и

логические

параметры),

предназначенное для сопряжения систем или частей

системы (программ или устройств).

6.

Под сопряжением подразумеваютсяследующие функции:

• выдача и прием информации;

• управление передачей данных;

• согласование источника и приемника

информации.

7. Шина (магистраль)

Шина (магистраль) - это среда передачисигналов, к которой может параллельно

подключаться

несколько

компонентов

вычислительной системы и через которую

осуществляется обмен данными.

8.

Чтобы охарактеризовать конкретную шину,нужно описать:

• совокупность сигнальных линий;

• физические, механические и электрические

характеристики шины;

• используемые сигналы арбитража, состояния,

управления и синхронизации;

• правила взаимодействия подключенных к шине

устройств (протокол шины).

9. Типы шин

По этому критерию можно выделить:• шины «процессор-память»;

• шины ввода/вывода;

• системные шины.

10. Шина процессор-память

Шина«процессор-память»

обеспечивает

непосредственную

связь

между

центральным

процессором (ЦП) вычислительной машины и

основной

памятью

(ОП).

В

современных

микропроцессорах такую шину часто называют

шиной переднего плана и обозначают аббревиатурой

FSB (Front-Side Bus).

11. Шина ввода/вывода

Шина ввода/вывода служит для соединенияпроцессора (памяти) с устройствами ввода/вывода

(УВВ).

Типичными примерами подобных шин могут

служить шины PCI и SCSI.

12. Системная шина

Системная шина служит для физического илогического объединения всех устройств ВМ.

13. Системные средства

К системным средствам относятся средстваслужбы времени: часы астрономического

времени, таймер, коммутатор и т. д.

14.

ЦППамять

...

Память

МВВ

...

МВВ

Шина данных

Шина адреса

Шина управления

Системная шина

Рисунок 3 – Структура системной шины

15. ЭВМ с одной шиной

В структурах взаимосвязей с одной шинойимеется одна системная шина, обеспечивающая

обмен информацией между процессором и

памятью, а также между УВВ с одной стороны, и

процессором либо памятью — с другой.

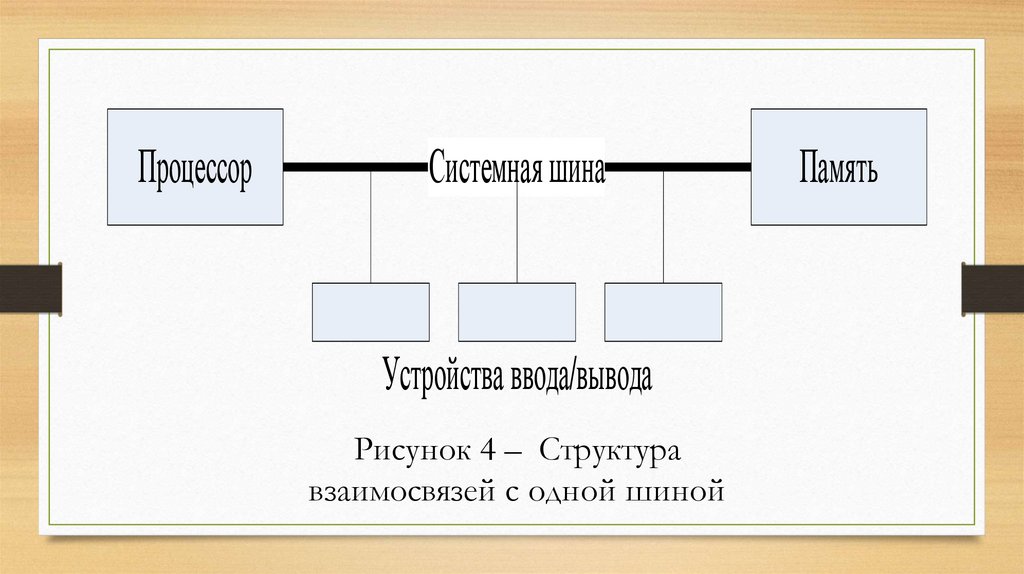

16.

ПроцессорСистемная шина

Устройства ввода/вывода

Рисунок 4 – Структура

взаимосвязей с одной шиной

Память

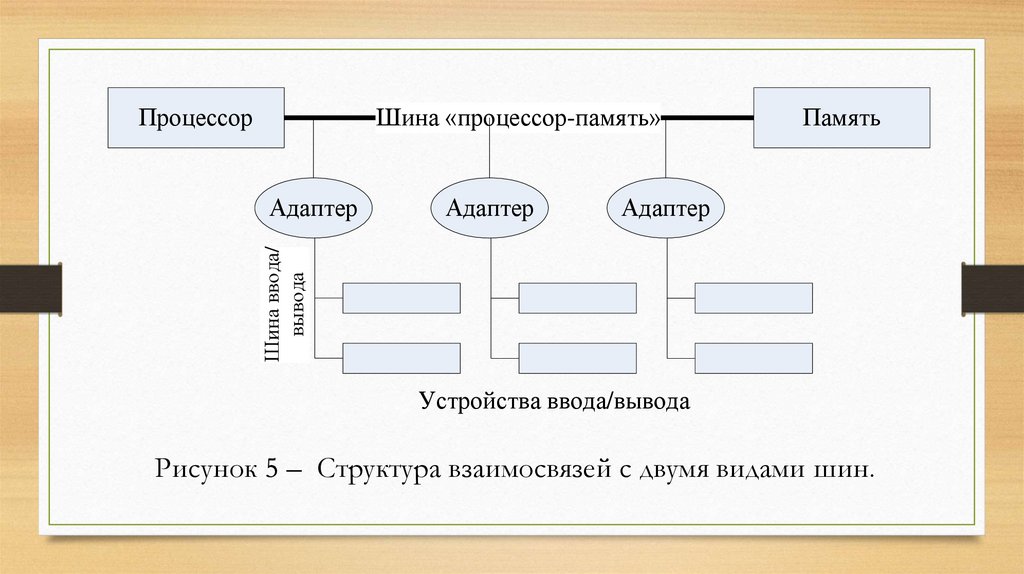

17. ЭВМ с двумя видами шин

Хотя контроллеры устройств ввода/вывода (УВВ) могутбыть подсоединены непосредственно к системной шине,

больший эффект достигается применением одной или

нескольких шин ввода/вывода. УВВ подключаются к шинам

ввода/вывода, которые берут на себя основной трафик, не

связанный с выходом на процессор или память.

18.

ПроцессорШина «процессор-память»

Адаптер

Адаптер

Шина ввода/

вывода

Адаптер

Память

Устройства ввода/вывода

Рисунок 5 – Структура взаимосвязей с двумя видами шин.

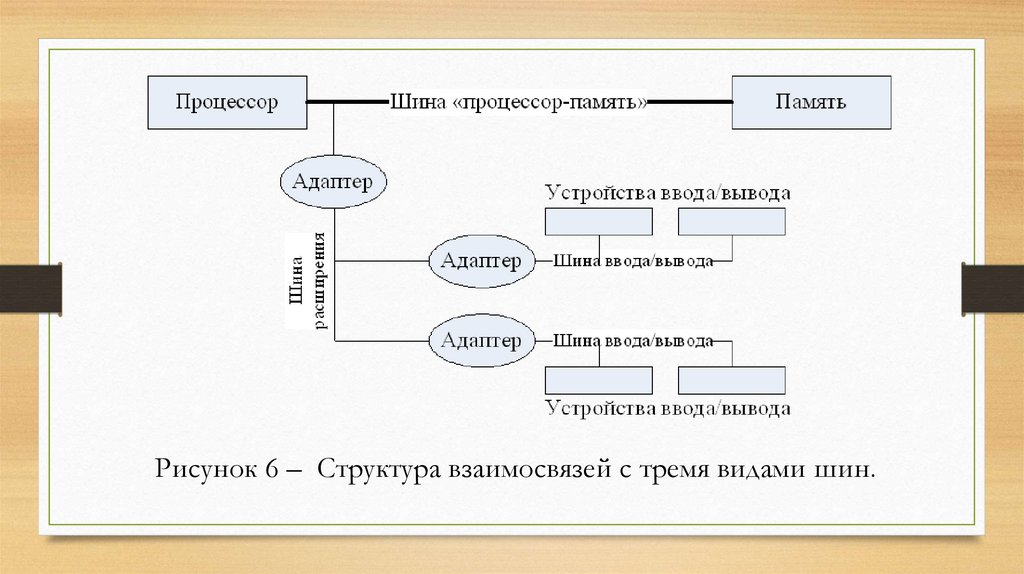

19. ЭВМ с тремя видами шин

Для подключения быстродействующих периферийныхустройств в систему шин может быть добавлена

высокоскоростная шина расширения.

Шины ввода/вывода подключаются к шине расширения,

а уже с нее через адаптер к шине «процессор-память».

20.

Рисунок 6 – Структура взаимосвязей с тремя видами шин.21. Механические аспекты реализации шин

Основная шина, объединяющая устройства вычислительноймашины, обычно размещается на так называемой объединительной

или материнской плате. Шину образуют тонкие параллельные

медные полоски, поперек которых через большие интервалы

установлены разъемы для подсоединения устройств ВМ.

Подключаемые к шине устройства обычно также выполняются в

виде печатных плат, часто называемых дочерними платами,

модулями или платами расширения.

22. Электрические аспекты реализации шин

Все устройства, использующие шину, электрически подсоединенык ее сигнальным линиям, представляющим собой электрические

проводники. Меняя уровни напряжения на сигнальных линиях,

ведущее устройство формирует на них информационные или

управляющие сигналы.

Когда ведущее устройство выставляет на сигнальной шине какойто уровень напряжения, этот уровень может быть воспринят

приемниками в любой точке линии.

23. Выделенные и мультиплексируемые линии

В некоторых ВМ линии адреса и данныхобъединены в единую мультиплексируемую шину

адреса/данных.

Такая шина функционирует в режиме разделения

времени, поскольку цикл шины разбит на временной

интервал для передачи адреса и временной интервал

для передачи данных.

24. Арбитраж шин

Арбитраж запросов на управление шинойможет быть организован по централизованной

или децентрализованной схеме.

25. Централизованный арбитраж

При централизованном арбитраже в системеимеется специальное устройство – центральный

арбитр, – ответственное за предоставление доступа к

шине только одному из запросивших ведущих.

26. Децентрализованный арбитраж

В последовательных схемах для выделения запросас наивысшим приоритетом используется один из

сигналов, поочередно проходящий через цепочку

ведущих, чем и объясняется другое название —

цепочечный или гирляндный арбитраж.

27. Схемы приоритетов

Каждому потенциальному ведущему присваиваетсяопределенный уровень приоритета, который может

оставаться

неизменным

(статический

или

фиксированный приоритет) либо изменяться по

какому-либо алгоритму (динамический приоритет).

28.

Наибольшеераспространение

получили

следующие алгоритмы динамического изменения

приоритетов:

• простая циклическая смена приоритетов;

• циклическая смена приоритетов с учетом

последнего запроса;

• смена приоритетов по случайному закону;

• схема равных приоритетов;

• алгоритм наиболее давнего использования.

29.

Полудинамические алгоритмы:• алгоритм очереди (первым пришел —

первым обслужен);

• алгоритм фиксированного кванта времени.

electronics

electronics