Similar presentations:

Цифровые устройства. Лекция 6-7

1.

ЦИФРОВЫЕустройства

1

2.

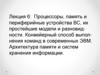

Лекция 6-7. Содержание лекции 7Темы

№ слайда

Виды памяти

36

Обозначение выводов микросхем памяти

40

Способы организации элементов памяти

42

Способы поиска информации (адресации)

45

Память 2D

45

Память 3D

49

Память 2DM

53

Оперативная память

58

ОЗУ статического типа

60

ОЗУ динамического типа

66

2

3.

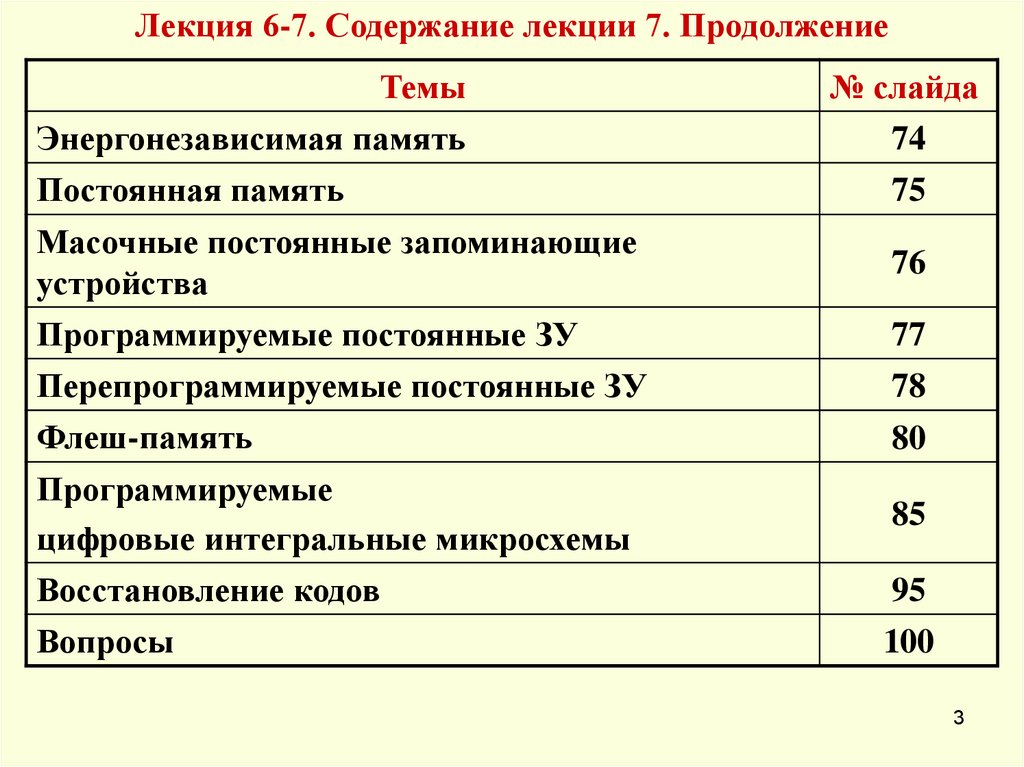

Лекция 6-7. Содержание лекции 7. ПродолжениеТемы

Энергонезависимая память

Постоянная память

Масочные постоянные запоминающие

устройства

Программируемые постоянные ЗУ

№ слайда

74

75

76

77

Перепрограммируемые постоянные ЗУ

78

Флеш-память

80

Программируемые

цифровые интегральные микросхемы

Восстановление кодов

Вопросы

85

95

100

3

4.

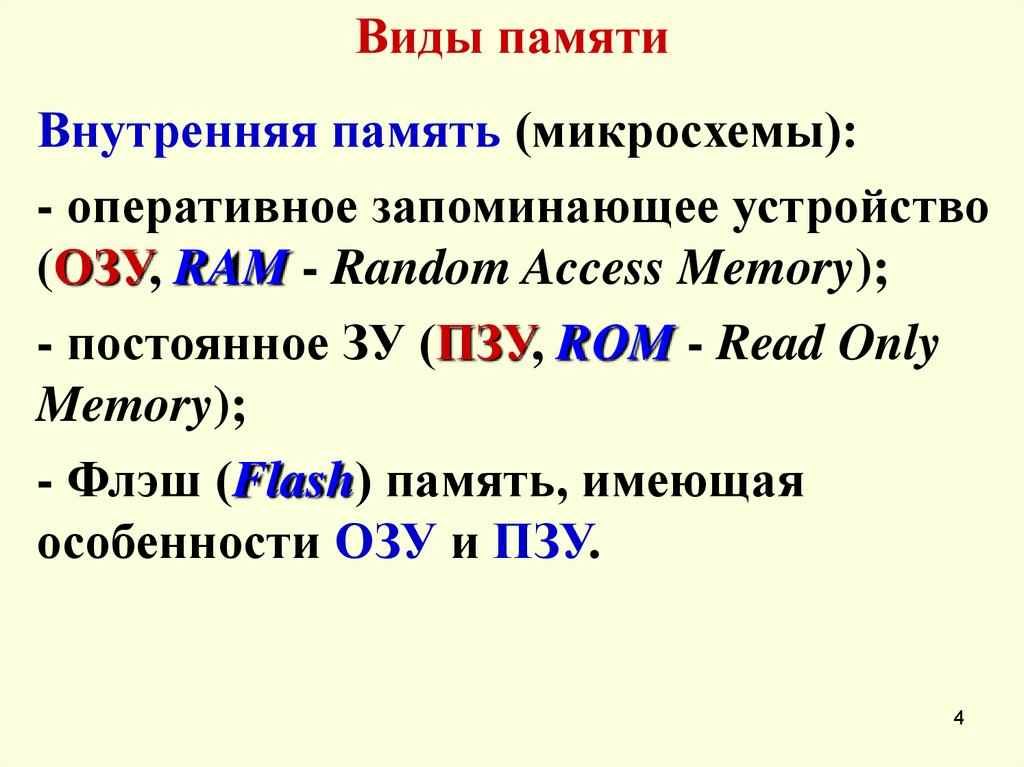

Виды памятиВнутренняя память (микросхемы):

- оперативное запоминающее устройство

(ОЗУ, RAM - Random Access Memory);

- постоянное ЗУ (ПЗУ, RОM - Read Only

Memory);

- Флэш (Flash) память, имеющая

особенности ОЗУ и ПЗУ.

4

5.

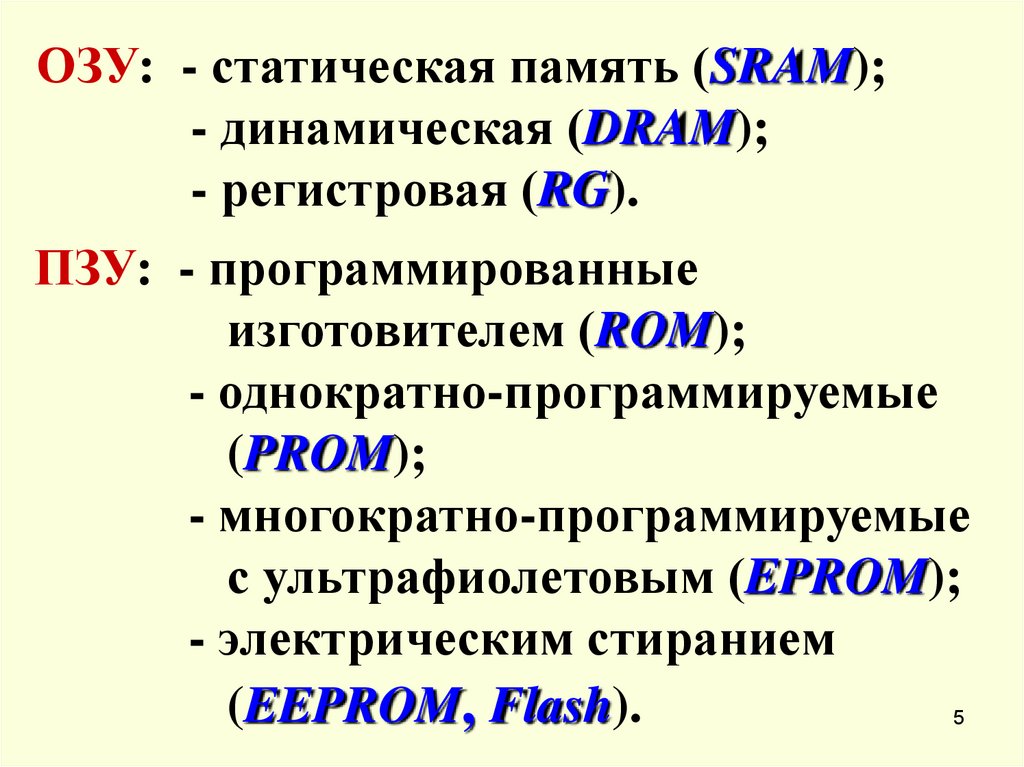

ОЗУ: - статическая память (SRAM);- динамическая (DRAM);

- регистровая (RG).

ПЗУ: - программированные

изготовителем (ROM);

- однократно-программируемые

(PROM);

- многократно-программируемые

с ультрафиолетовым (EPROM);

- электрическим стиранием

(EEPROM, Flash).

5

6.

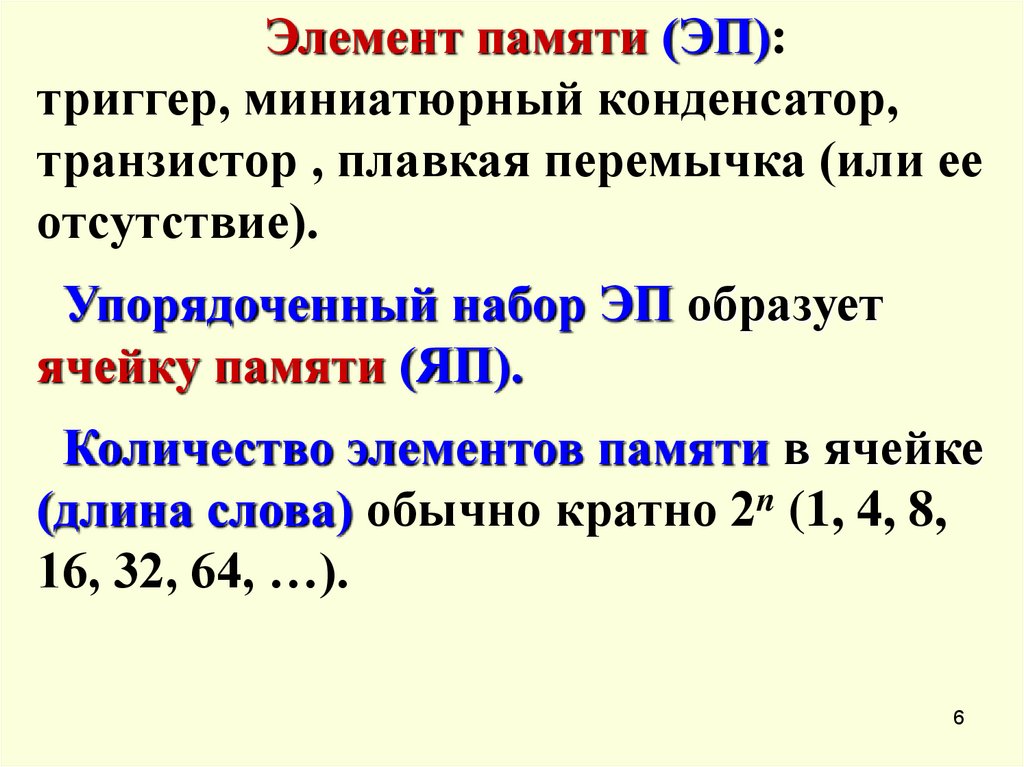

Элемент памяти (ЭП):триггер, миниатюрный конденсатор,

транзистор , плавкая перемычка (или ее

отсутствие).

Упорядоченный набор ЭП образует

ячейку памяти (ЯП).

Количество элементов памяти в ячейке

(длина слова) обычно кратно 2n (1, 4, 8,

16, 32, 64, …).

6

7.

Емкость ЗУ - в единицах кратных числу210 = 1024 = 1K.

Для длины слова равной биту (одному

двоичному разряду)

или байту (набору из восьми бит)

Эта единица называется килобит

или килобайт

и обозначается Kb или KB.

7

8.

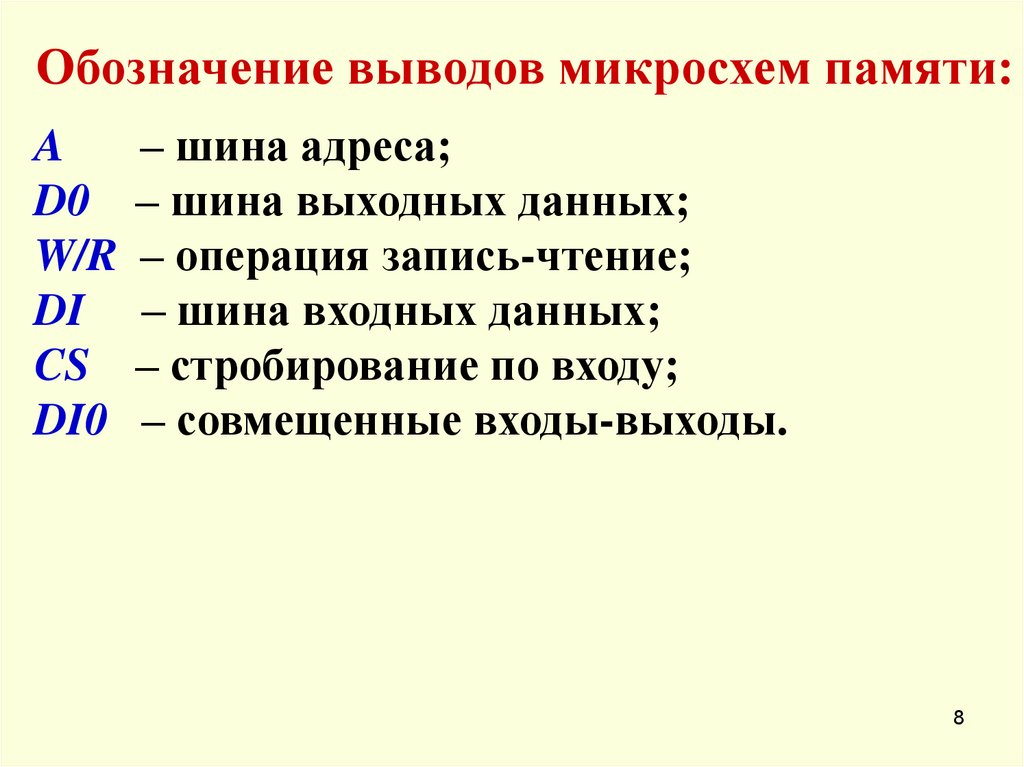

Обозначение выводов микросхем памяти:A

D0

W/R

DI

CS

DI0

– шина адреса;

– шина выходных данных;

– операция запись-чтение;

– шина входных данных;

– стробирование по входу;

– совмещенные входы-выходы.

8

9.

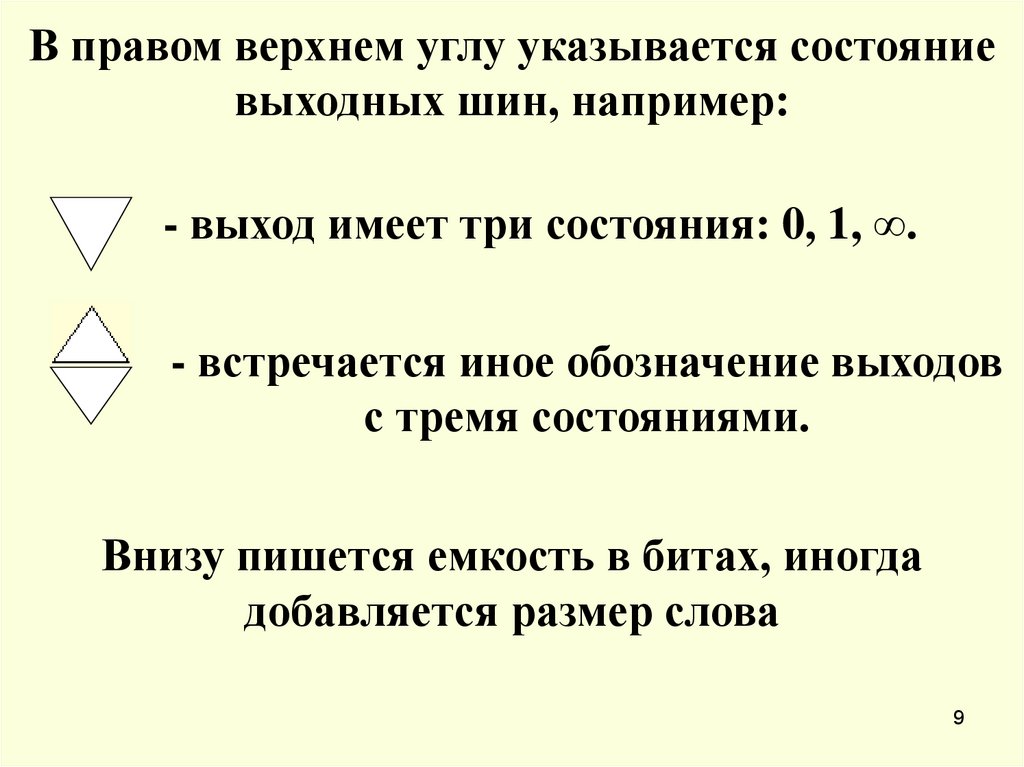

В правом верхнем углу указывается состояниевыходных шин, например:

- выход имеет три состояния: 0, 1, ∞.

- встречается иное обозначение выходов

с тремя состояниями.

Внизу пишется емкость в битах, иногда

добавляется размер слова

9

10.

Способы организации элементов памятиПоразрядная выборка информации:

каждый элемент памяти содержит только одну

ячейку памяти (адресуется индивидуально)

Пример объема памяти: 1024 ·1 или 1 K (1024

элементов памяти, содержащих по 1 ячейке).

Пословная выборка:

элемент памяти содержит несколько ячеек

(одновременное обращение к определенному

объему информации - пословная выборка)

Пример объема памяти:1024 ·8 или 8 Kb (1024

элементов памяти, содержащих по 8 ячеек).

10

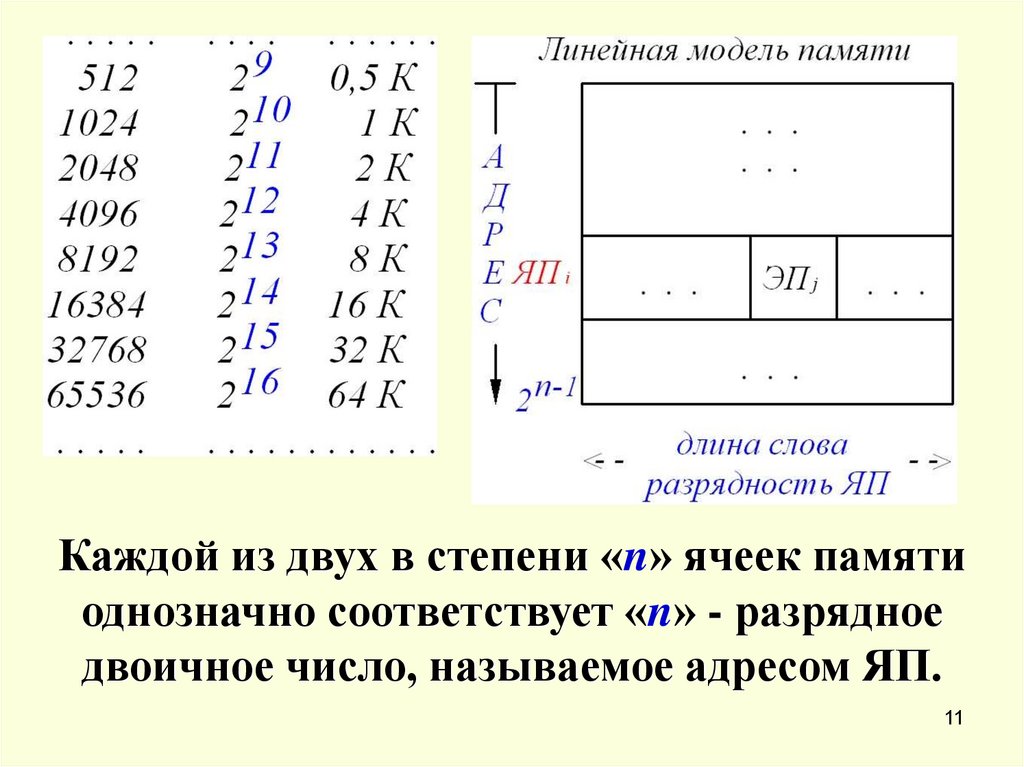

11.

Каждой из двух в степени «n» ячеек памятиоднозначно соответствует «n» - разрядное

двоичное число, называемое адресом ЯП.

11

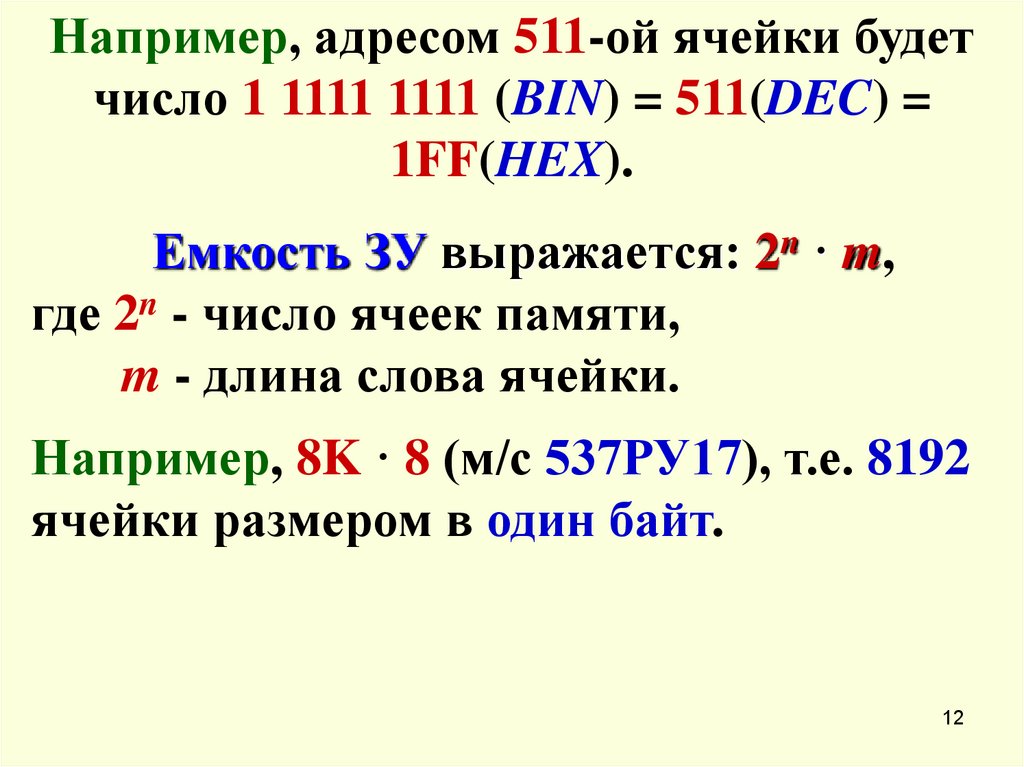

12.

Например, адресом 511-ой ячейки будетчисло 1 1111 1111 (BIN) = 511(DEC) =

1FF(HEX).

Емкость ЗУ выражается: 2n · m,

где 2n - число ячеек памяти,

m - длина слова ячейки.

Например, 8K · 8 (м/с 537РУ17), т.е. 8192

ячейки размером в один байт.

12

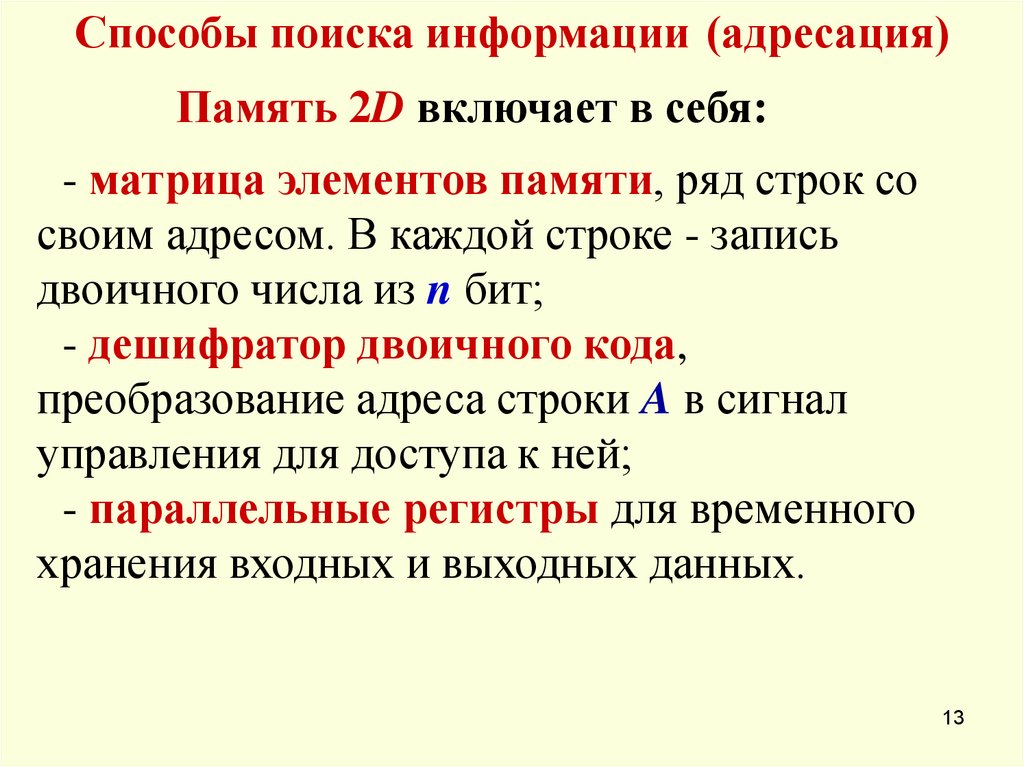

13.

Способы поиска информации (адресация)Память 2D включает в себя:

- матрица элементов памяти, ряд строк со

своим адресом. В каждой строке - запись

двоичного числа из n бит;

- дешифратор двоичного кода,

преобразование адреса строки A в сигнал

управления для доступа к ней;

- параллельные регистры для временного

хранения входных и выходных данных.

13

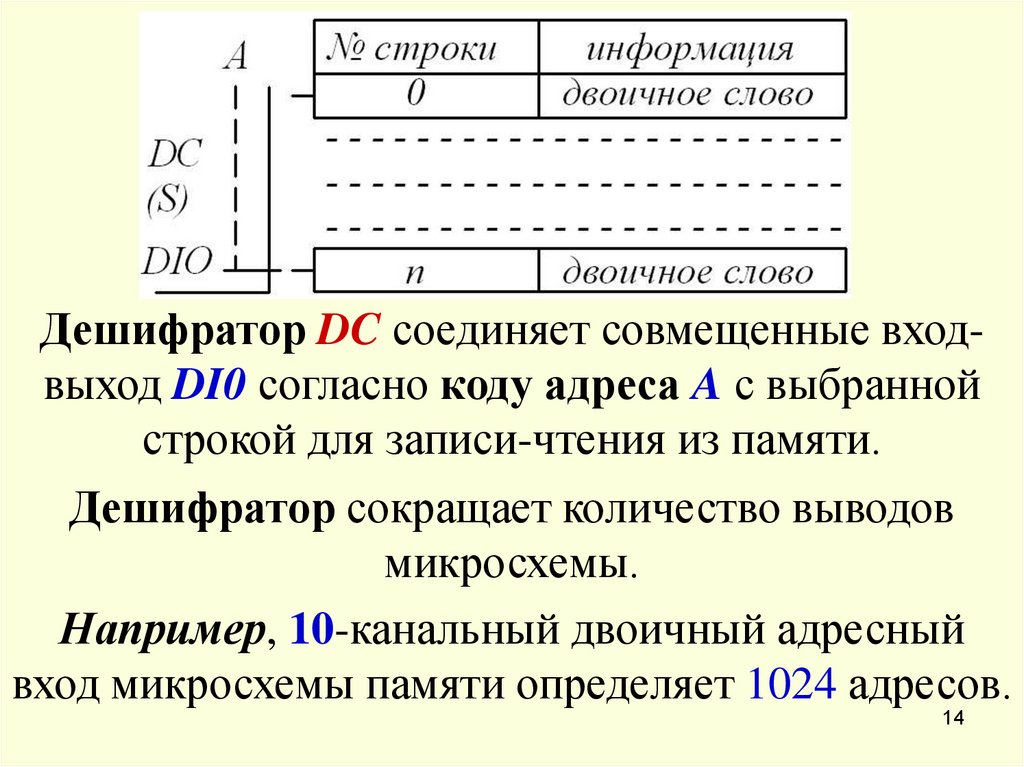

14.

Дешифратор DC соединяет совмещенные входвыход DI0 согласно коду адреса A с выбраннойстрокой для записи-чтения из памяти.

Дешифратор сокращает количество выводов

микросхемы.

Например, 10-канальный двоичный адресный

вход микросхемы памяти определяет 1024 адресов.

14

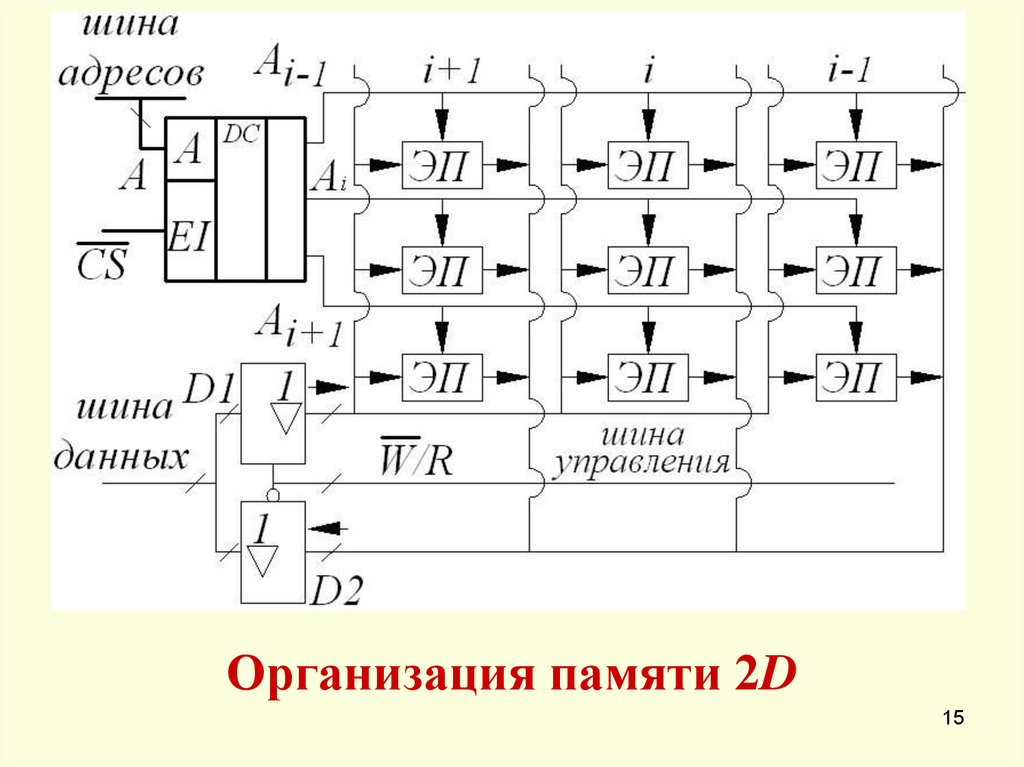

15.

Организация памяти 2D15

16.

При записи, информация с шины данныхпараллельным кодом передается через буферы

D1 в элементы памяти.

Буферы D2 отключены управляющим сигналом.

При считывании, информация из элементов памяти

параллельным кодом, через буферы D2 поступает

на шину данных.

Буферы D1 отключены.

Работа разрешена, когда на входе CS = 0

(шина управления).

Операция (запись, чтение) определяется шиной

управления W/R.

16

17.

Память 3D включает в себя:- матрица элементов памяти из n квадратных

подматриц (для записи-чтения одного из

разрядов всех двоичных слов памяти, n -ширина

выборки);

- дешифратор адреса X, преобразование первой

половины кода адреса в сигнал доступа к строке

подматриц;

- дешифратор адреса Y, преобразование второй

половины кода адреса в сигнал доступа к столбцу

подматриц;

- параллельные регистры входных и выходных

17

данных.

18.

Функциональная схема подматрицыпамяти 3D

18

19.

При записи или считывании информациивыбираются n элементов памяти, по одному

из каждой подматрицы.

Они находятся на пересечении столбца

и строки, соответствующих

дешифрированному адресу.

Тип операции определяется сигналом

шины управления W/R.

19

20.

При записи информационный сигнал сшины данных записывается через буферы D1

в элементы памяти. Буферы D2 отключены

управляющим сигналом.

При считывании, информация из элементов

памяти, через буферы D2 поступает на шину

данных. Буферы D1 отключены.

Микросхема работает при поступлении с шины

управления логического «0» на вход CS.

Недостаток – сложность элементов памяти

с двумя адресными входами.

20

21.

Память 2DM включает в себя:- матрица элементов памяти (ряд строк

с адресами (первая часть адресного кода)) - для

записи двоичных чисел;

- дешифратор адреса X, преобразование первой

части кода адреса в сигнал управления, для

доступа к выбранной строке матрицы;

-мультиплексоры, выбор элементов памяти из

строк согласно второй части адресного кода;

- дешифратор адреса Y, управление работой

мультиплексоров.

21

22.

строка из двух двоичных n – разрядных чисел:первое слово: D10…D1n-1, второе слово: D20…D2n-1

Часть схемы памяти 2DM

22

23.

Дешифратор X выбирает строки, каждаясодержит группы элементов памяти,

равные по емкости.

Первая группа - для первых разрядов слов,

размещенных в строке,

вторая группа - для вторых разрядов и т.д.

Дешифратор Y вырабатывает сигнал

управления для мультиплексоров (считывают

из каждой группы по одному разряду

двоичного слова).

23

24.

Например, дешифратор X, в соответствии садресом, выбирает седьмую строку.

Согласно сигналу управления дешифратора Y,

мультиплексоры во всех группах этой строки

обращаются к четвертому элементу памяти.

Из первой группы первый мультиплексор

считывает первый разряд слова, из второй

группы второй мультиплексор –

второй разряд и.т.д.

Операция записи информации происходит

аналогично.

24

25.

Пример организации памяти с емкостью 1024 разрядов, длявыборки 256 слов длиной по четыре двоичных разряда (256 · 4).

Матрица содержит 32 строк, 32 столбцов, всего 1024 ячейки

памяти. Для адресации 32 строк нужно пять адресных разрядов

(число наборов 000002 …111112 равно 3210).

Дешифратор адреса X выбирает одну строку из 32 по коду адреса.

Столбцы разделены на восемь групп, по четыре столбца.

Для выборки группы нужно три адресных разряда

(число наборов 0002…1112 равно 810).

Дешифратор адреса Y выбирает группу столбцов по коду адреса.

Пересечение строки и группы столбцов (4 ячейки) - элемент

памяти согласно адресному двоичному коду (8 разрядов).

Вывод: пятиразрядный адрес строки и трехразрядный адрес

столбцов позволяет обратиться к любому из 256

четырехразрядных слов, размещенных в памяти микросхемы.

25

26.

Оперативная память(Random Access Memory, с произвольной

выборкой) статическая (SRAM)

Применяется для хранения, приема и выдачи

оперативной информации.

Статические оперативные ЗУ выполняются

с произвольным доступом в каждый момент

времени к любому элементу памяти с

индивидуальным адресом.

Основным запоминающим элементом являются

триггеры.

26

27.

Поиск информации в матрице выполняется спомощью одномерной (2D) или двухмерной (3D)

адресации.

В дешифратор адреса поступает двоичный код

элемента памяти, для записи или считывания

информации.

Дешифратор адреса определяет в матрице

требуемую ячейку.

Данная память имеет высокое быстродействие

(цикл обращения 8-20 нс), относительно

небольшую информационную емкость,

энергетическую зависимость (при отключении

27

питания информация теряется).

28.

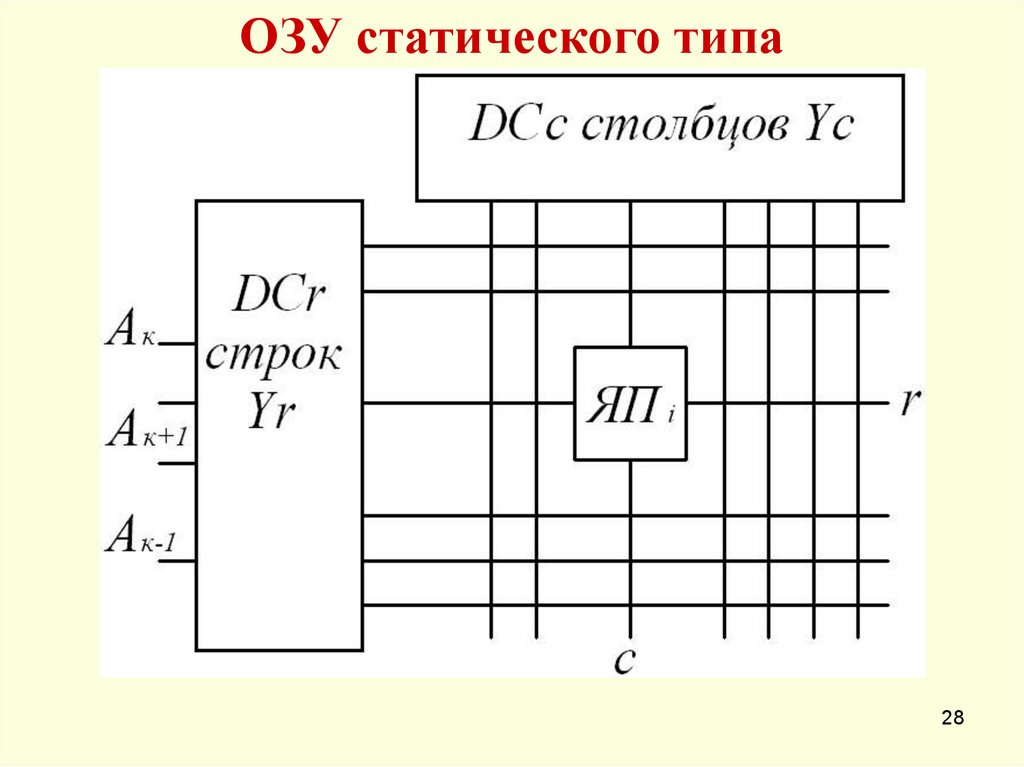

ОЗУ статического типа28

29.

В качестве элемента памяти используется D-триггер.В микросхеме 537РУ10, например, каждая ЯП состоит

из восьми триггеров и располагаются ячейки на

кристалле в виде прямоугольной матрицы.

Обозначения:

- n адресных входов (A0 .. An-1);

- DIO - двунаправленная восмиразрядная шина данных,

- вход разрешения выходов – E’;

- вход выбора микросхемы – CS’;

- вход разрешения записи – WE’, или W/R’ (при «0» –

запись байта, при «1» – чтение);

- EO, DI, WR внутренние сигналы вырабатываемые

блоком управления чтением/записью/хранением.

29

30.

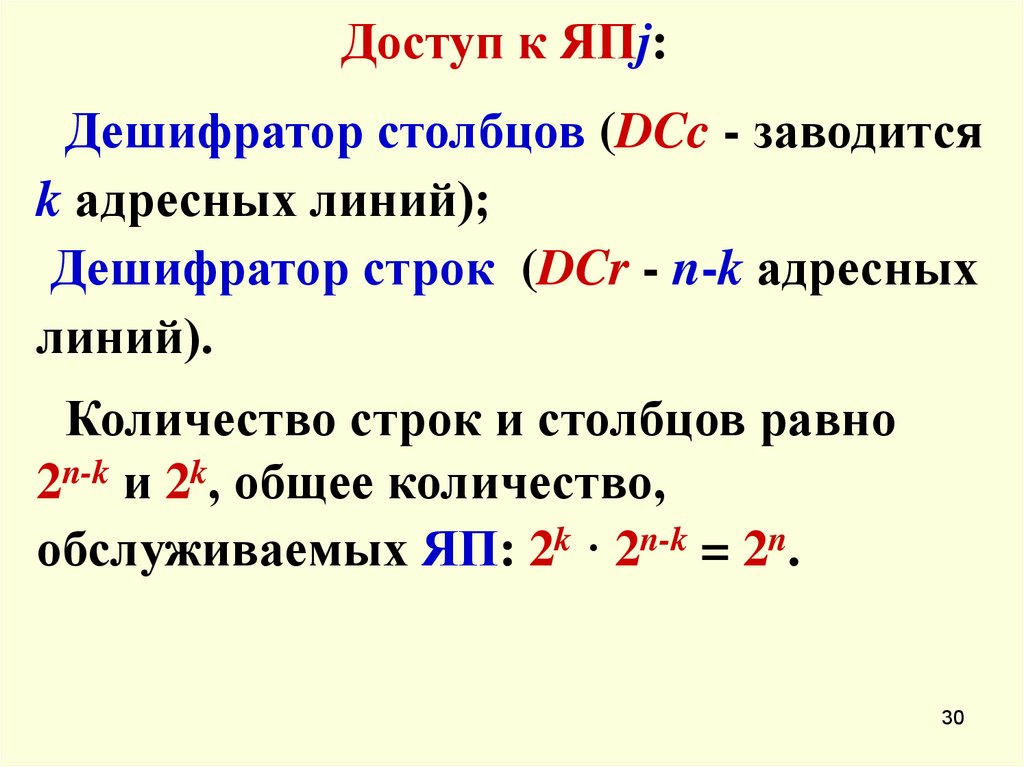

Доступ к ЯПj:Дешифратор столбцов (DCc - заводится

k адресных линий);

Дешифратор строк (DCr - n-k адресных

линий).

Количество строк и столбцов равно

2n-k и 2k, общее количество,

обслуживаемых ЯП: 2k · 2n-k = 2n.

30

31.

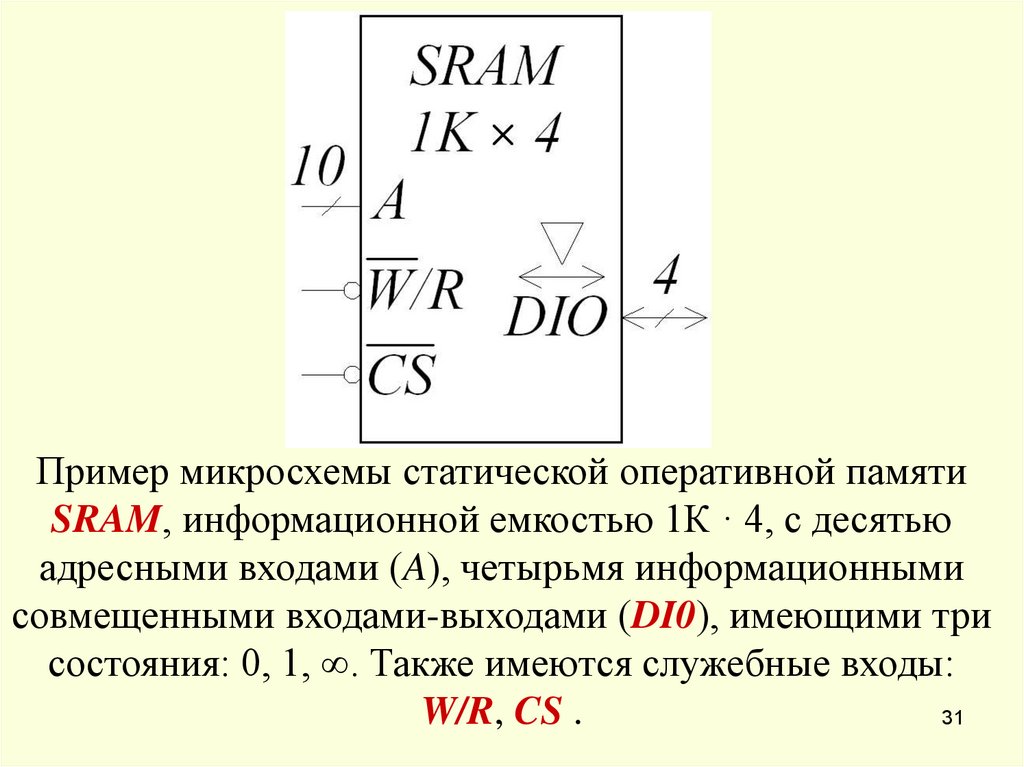

Пример микросхемы статической оперативной памятиSRAM, информационной емкостью 1К · 4, с десятью

адресными входами (A), четырьмя информационными

совмещенными входами-выходами (DI0), имеющими три

состояния: 0, 1, ∞. Также имеются служебные входы:

W/R, CS .

31

32.

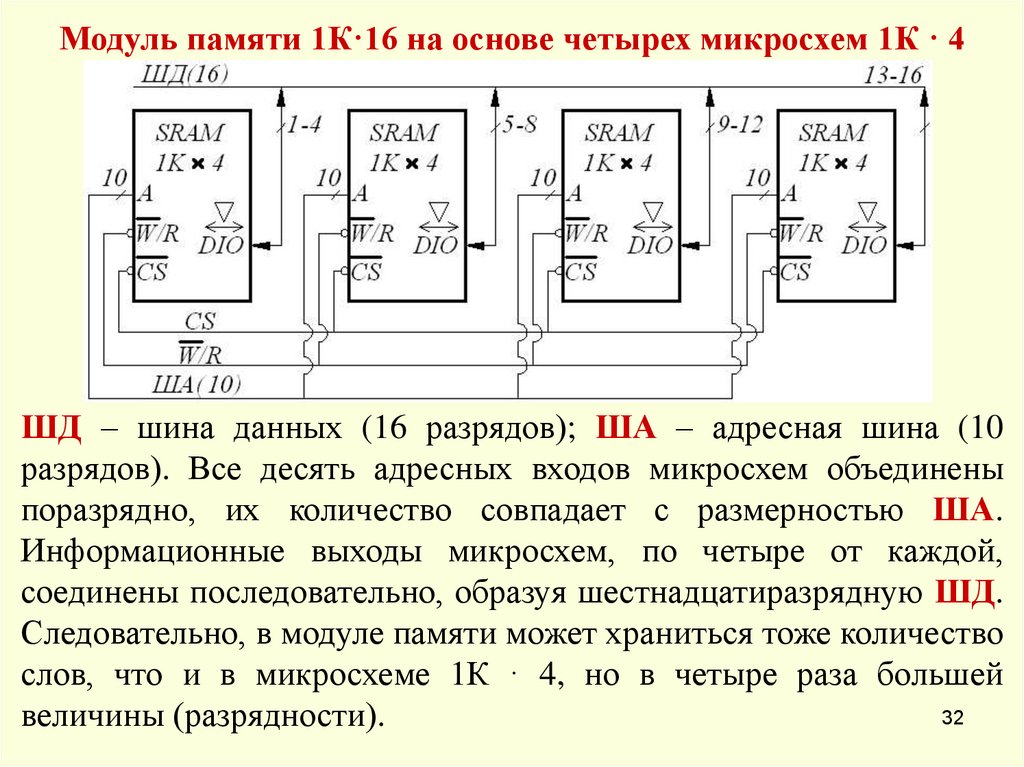

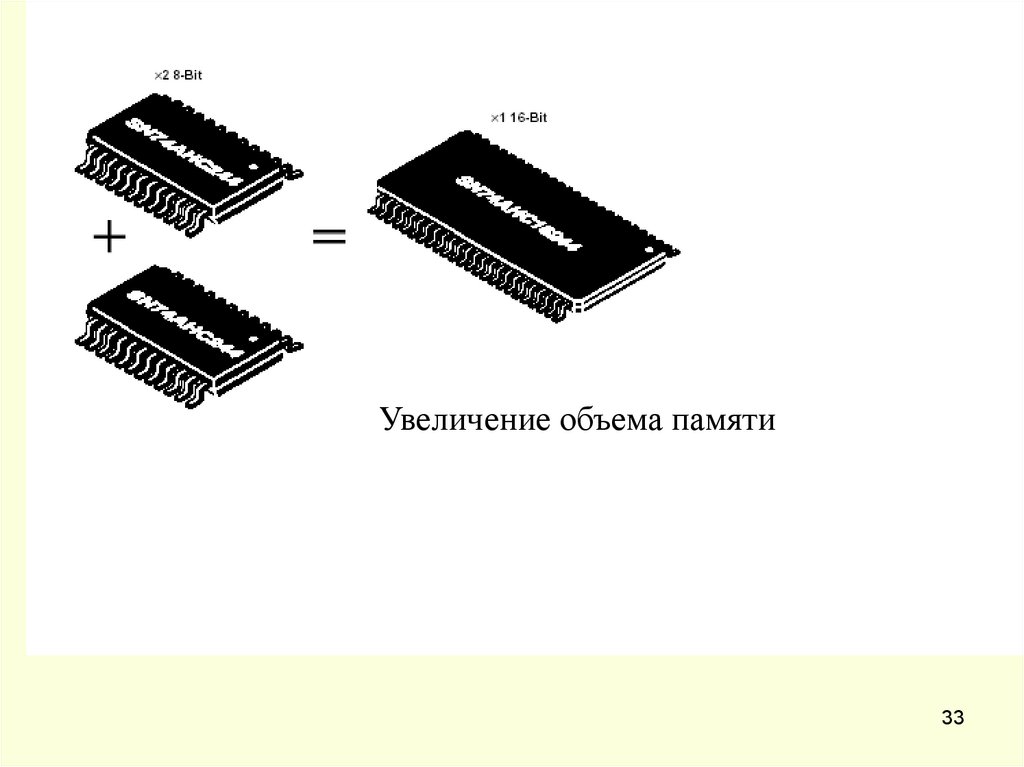

Модуль памяти 1К·16 на основе четырех микросхем 1К · 4ШД – шина данных (16 разрядов); ША – адресная шина (10

разрядов). Все десять адресных входов микросхем объединены

поразрядно, их количество совпадает с размерностью ША.

Информационные выходы микросхем, по четыре от каждой,

соединены последовательно, образуя шестнадцатиразрядную ШД.

Следовательно, в модуле памяти может храниться тоже количество

слов, что и в микросхеме 1К · 4, но в четыре раза большей

32

величины (разрядности).

33.

Увеличение объема памяти33

34.

ОЗУ динамического типаЭлемент памяти - микроконденсатор

в интегральном исполнении.

Адресные линии внутри микросхемы

разбиваются на две группы.

Две одноименные k-линии каждой

группы подключаются к двум выходам

внутреннего k-го DMC (1 – 2), а его вход

соединяется с k-ым адресным

входом микросхемы.

34

35.

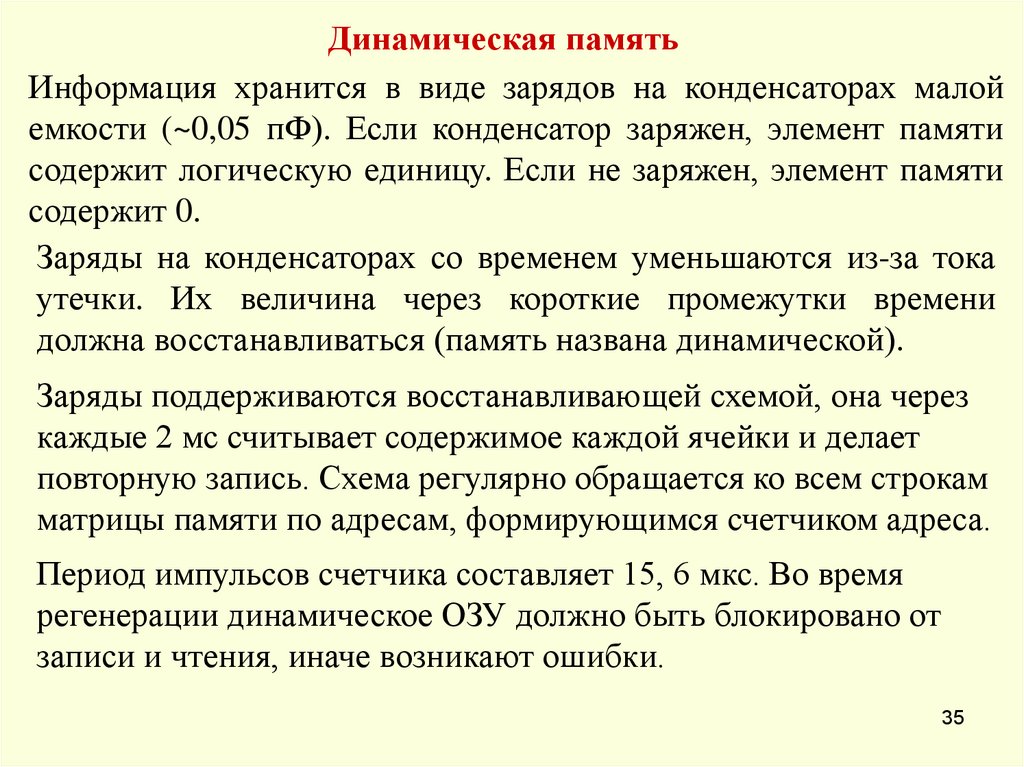

Динамическая памятьИнформация хранится в виде зарядов на конденсаторах малой

емкости (~0,05 пФ). Если конденсатор заряжен, элемент памяти

содержит логическую единицу. Если не заряжен, элемент памяти

содержит 0.

Заряды на конденсаторах со временем уменьшаются из-за тока

утечки. Их величина через короткие промежутки времени

должна восстанавливаться (память названа динамической).

Заряды поддерживаются восстанавливающей схемой, она через

каждые 2 мс считывает содержимое каждой ячейки и делает

повторную запись. Схема регулярно обращается ко всем строкам

матрицы памяти по адресам, формирующимся счетчиком адреса.

Период импульсов счетчика составляет 15, 6 мкс. Во время

регенерации динамическое ОЗУ должно быть блокировано от

записи и чтения, иначе возникают ошибки.

35

36.

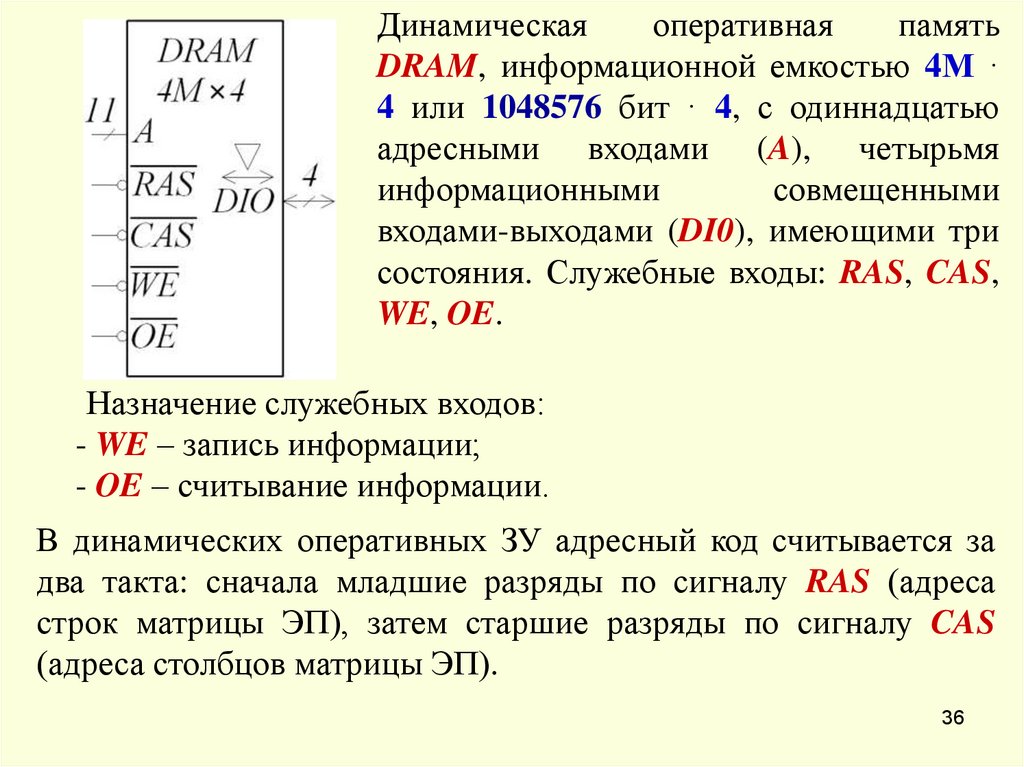

Динамическаяоперативная

память

DRAM, информационной емкостью 4М ·

4 или 1048576 бит · 4, с одиннадцатью

адресными входами (A), четырьмя

информационными

совмещенными

входами-выходами (DI0), имеющими три

состояния. Служебные входы: RAS, CAS,

WE, OE.

Назначение служебных входов:

- WE – запись информации;

- OE – считывание информации.

В динамических оперативных ЗУ адресный код считывается за

два такта: сначала младшие разряды по сигналу RAS (адреса

строк матрицы ЭП), затем старшие разряды по сигналу CAS

(адреса столбцов матрицы ЭП).

36

37.

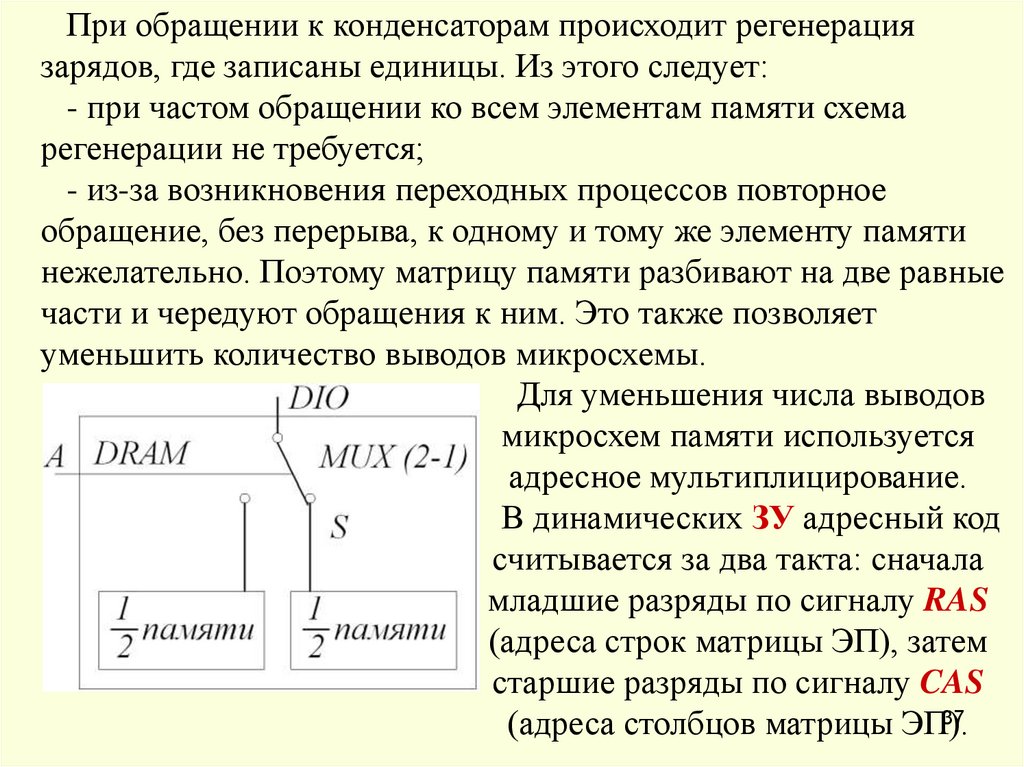

При обращении к конденсаторам происходит регенерациязарядов, где записаны единицы. Из этого следует:

- при частом обращении ко всем элементам памяти схема

регенерации не требуется;

- из-за возникновения переходных процессов повторное

обращение, без перерыва, к одному и тому же элементу памяти

нежелательно. Поэтому матрицу памяти разбивают на две равные

части и чередуют обращения к ним. Это также позволяет

уменьшить количество выводов микросхемы.

Для уменьшения числа выводов

микросхем памяти используется

адресное мультиплицирование.

В динамических ЗУ адресный код

считывается за два такта: сначала

младшие разряды по сигналу RAS

(адреса строк матрицы ЭП), затем

старшие разряды по сигналу CAS

37

(адреса столбцов матрицы ЭП).

38.

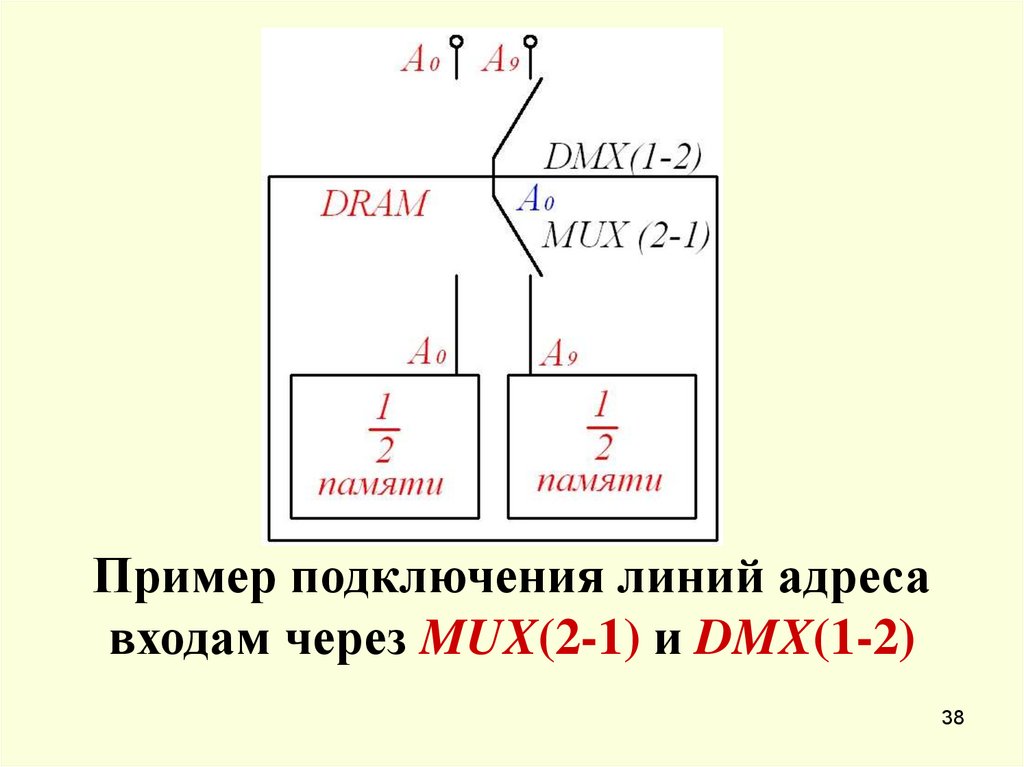

Пример подключения линий адресавходам через MUX(2-1) и DMX(1-2)

38

39.

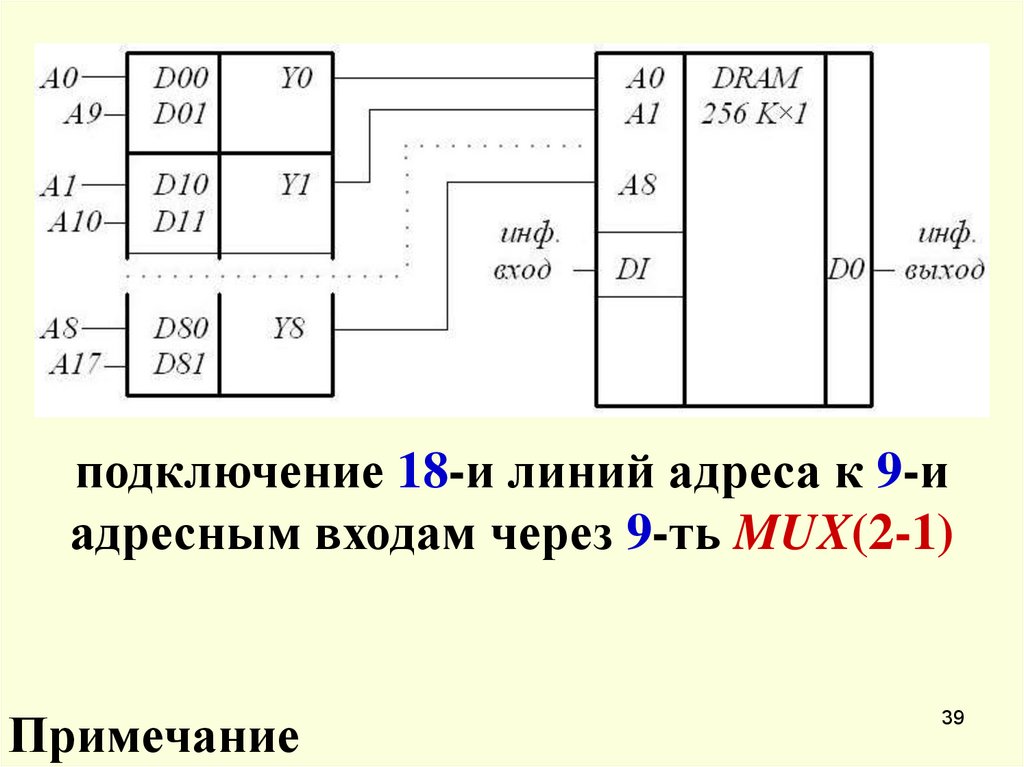

подключение 18-и линий адреса к 9-иадресным входам через 9-ть MUX(2-1)

Примечание

39

40.

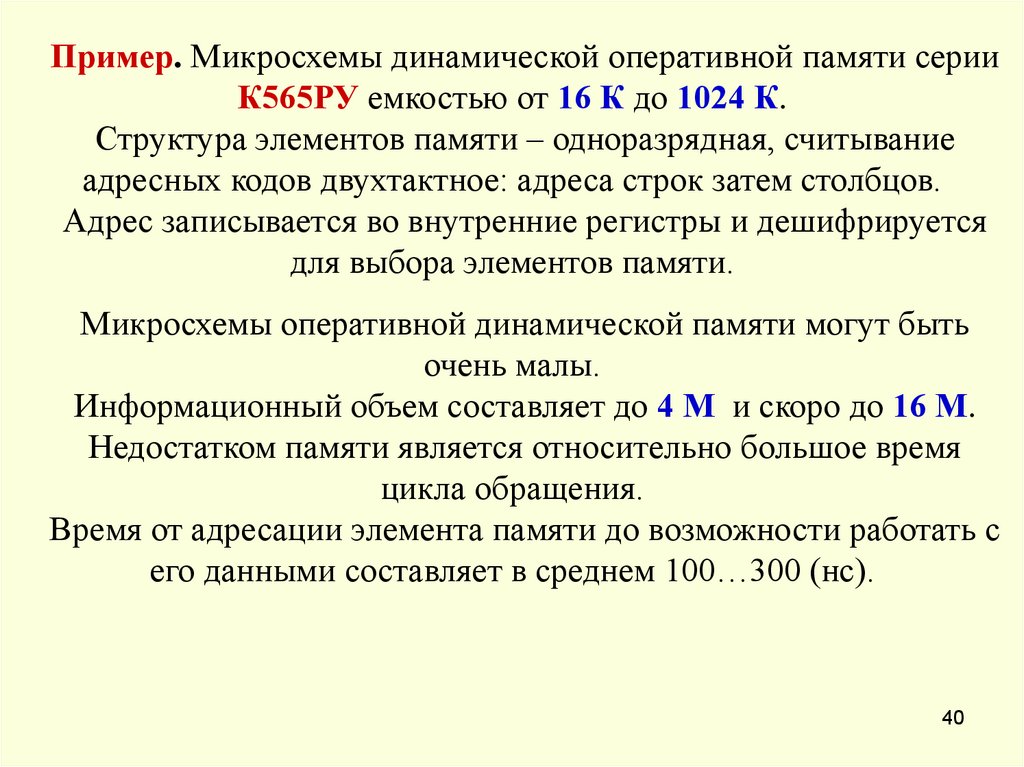

Пример. Микросхемы динамической оперативной памяти серииК565РУ емкостью от 16 К до 1024 К.

Структура элементов памяти – одноразрядная, считывание

адресных кодов двухтактное: адреса строк затем столбцов.

Адрес записывается во внутренние регистры и дешифрируется

для выбора элементов памяти.

Микросхемы оперативной динамической памяти могут быть

очень малы.

Информационный объем составляет до 4 М и скоро до 16 М.

Недостатком памяти является относительно большое время

цикла обращения.

Время от адресации элемента памяти до возможности работать с

его данными составляет в среднем 100…300 (нс).

40

41.

Динамическая оперативная памятьв компьютерах (SIMM, EDO, SDRAM) имеет цикл

обращения около10 нс, информационная емкость

микросхемы до 256 M.

Отличие динамического оперативного ЗУ

от статического ЗУ:

- мультиплексирование адресных входов;

- регенерация хранимой информации,

- повышенная информационная емкость;

- более сложная схема управления;

- ограничение температуры микросхемы

(не более 70º С) вследствие роста тока разряда

конденсаторов.

41

42.

Энергонезависимая память(NVSRAM)

Пример:

Статическая оперативная память:

Заряды поддерживаются встроенной в

микросхему литиевой батарейкой

большой емкости.

В перепрограммируемых ЗУ используется заряд области между двумя

диэлектриками, который может

храниться десятки лет.

42

43.

Постоянная памятьПостоянная память содержит неизменную информацию,

которую можно только считывать, длительно хранить и

многократно использовать (стандартные программы, константы,

таблицы данных).

Данная память представляет матрицу разомкнутых или

замкнутых контактов, пропускающих ток только в одном

направлении. Адресация при выборе строки и столбца матрицы

выполняется так же, как в оперативных ЗУ.

Существуют различные типы постоянных ЗУ. Главное различие

между ними состоит в получении замкнутых и разомкнутых

контактных соединений.

Для организации матрицы применяют два типа запоминающих

элементов: всегда содержащих значение 1, или значение 0.

43

44.

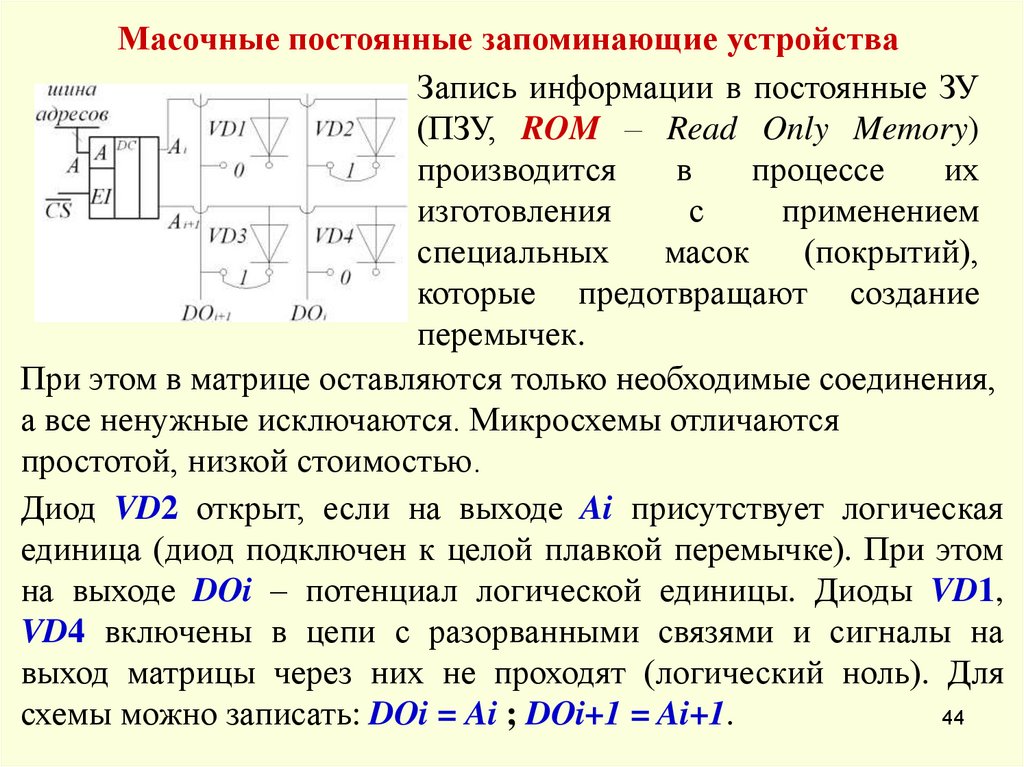

Масочные постоянные запоминающие устройстваЗапись информации в постоянные ЗУ

(ПЗУ, ROM – Read Only Memory)

производится

в

процессе

их

изготовления

с

применением

специальных

масок

(покрытий),

которые предотвращают создание

перемычек.

При этом в матрице оставляются только необходимые соединения,

а все ненужные исключаются. Микросхемы отличаются

простотой, низкой стоимостью.

Диод VD2 открыт, если на выходе Ai присутствует логическая

единица (диод подключен к целой плавкой перемычке). При этом

на выходе DOi – потенциал логической единицы. Диоды VD1,

VD4 включены в цепи с разорванными связями и сигналы на

выход матрицы через них не проходят (логический ноль). Для

схемы можно записать: DOi = Ai ; DOi+1 = Ai+1.

44

45.

Программируемые постоянные ЗУМикросхемы ППЗУ (PROM – Programmable Read Only Memory)

конструктивно аналогичны масочным постоянным ЗУ и

программируются один раз у потребителя.

Программирование микросхем является необратимым и состоит

в пережоге части плавких перемычек на специальном

программаторе импульсами тока амплитудой 20…30 мА.

Коррекция возможна только в случае, если требуется

дополнительно прожечь оставшиеся соединения.

Достоинство: экономически выгодное производство малых

партий цифровых устройств с использованием ППЗУ.

Пример. Микросхема К155РЕЗ. Информационная емкость 32 ·

8 или 256 бит = 32 байта.

45

46.

Перепрограммируемые постоянные ЗУДля этой памяти допустимо многократное стирание и запись

информации. Перепрограммируемые постоянные ЗУ (REPROM –

Re-programmable Read Only Memory) подразделяются на три

группы: с записью и стиранием электрическими сигналами

EEROM (Electrically Erasable Read Only Memory) и с записью

электрическими сигналами, стиранием ультрафиолетовым

излучением (EPROM – Erasable Programmable Read Only

Memory), флэш-память (Flash Memory).

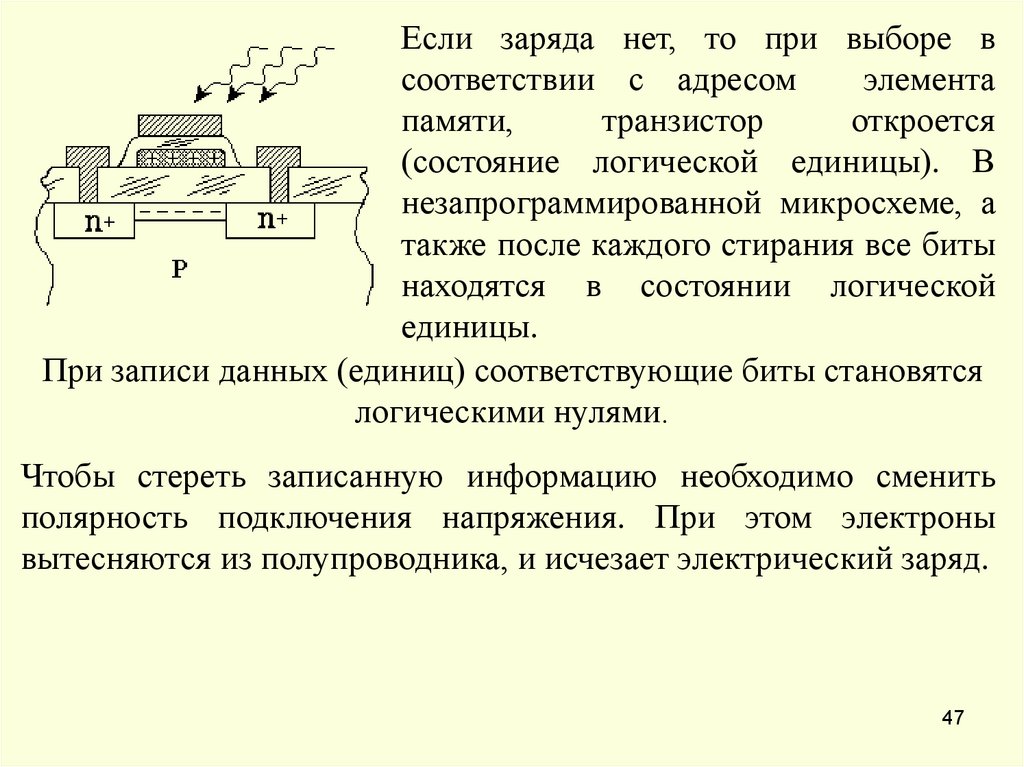

Элемент памяти представляет собой полевой транзистор,

который работает как управляемый нормально разомкнутый

контакт. Его управляющий вход отделяет от полупроводниковой

пластины тонкий слой диэлектрика. При записи информации к

полупроводнику прикладывается постоянное положительное

напряжение (20 В). Под действием электрического поля электроны

скапливаются в полупроводнике, попадая в примеси – ловушки.

46

47.

Если заряда нет, то при выборе всоответствии с адресом

элемента

памяти,

транзистор

откроется

(состояние логической единицы). В

незапрограммированной микросхеме, а

также после каждого стирания все биты

находятся в состоянии логической

единицы.

При записи данных (единиц) соответствующие биты становятся

логическими нулями.

Чтобы стереть записанную информацию необходимо сменить

полярность подключения напряжения. При этом электроны

вытесняются из полупроводника, и исчезает электрический заряд.

47

48.

Флэш-память отличается способом получения и сохранениязаряда, управляющего работой транзистора.

Управляющий вход полевого транзистора размещен внутри

диэлектрика и не имеет металлического вывода (транзистор с

плавающем затвором). При записи информации к диэлектрику

прикладывается импульс постоянного напряжения 25 В, под

действием электрического поля электроны проникают через

тонкий слой диэлектрика и накапливаются на управляющем

входе.

48

49.

Электрический заряд открывает транзистор (замыканиеконтакта). Это состояние соответствует логической единице. В

случае если электрического заряда нет, то состояние

соответствует логическому нулю и транзистор закрыт.

Гарантированный срок хранения информации без питания в

Flash Memory 5…10 лет, количество циклов перезаписи

1000000. Информационная емкость 8 Мбит и более. Время

считывания 65…200 нс.

49

50.

Отличие динамического ОЗУот статического:

- мультиплексирование адресных входов;

- регенерация хранимой информации;

- повышенная емкость (до нескольких

Мбит);

- более сложная схема управления.

50

51.

Программируемыецифровые интегральные микросхемы

Основаны на реализации дизъюнктивной

нормальной формы (ДНФ) с помощью

элементов И, ИЛИ, ИСКЛЮЧАЮЩЕЕ

ИЛИ и инверторов.

В ПЦИС входят триггеры,

мультиплексоры.

51

52.

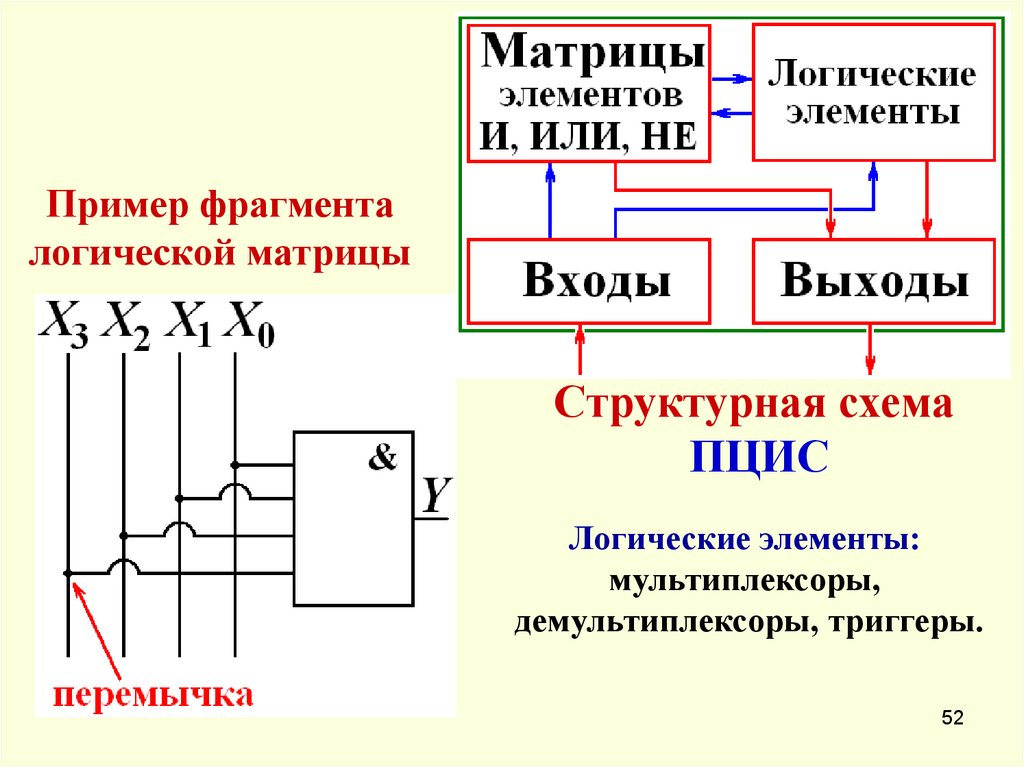

Пример фрагменталогической матрицы

Структурная схема

ПЦИС

Логические элементы:

мультиплексоры,

демультиплексоры, триггеры.

52

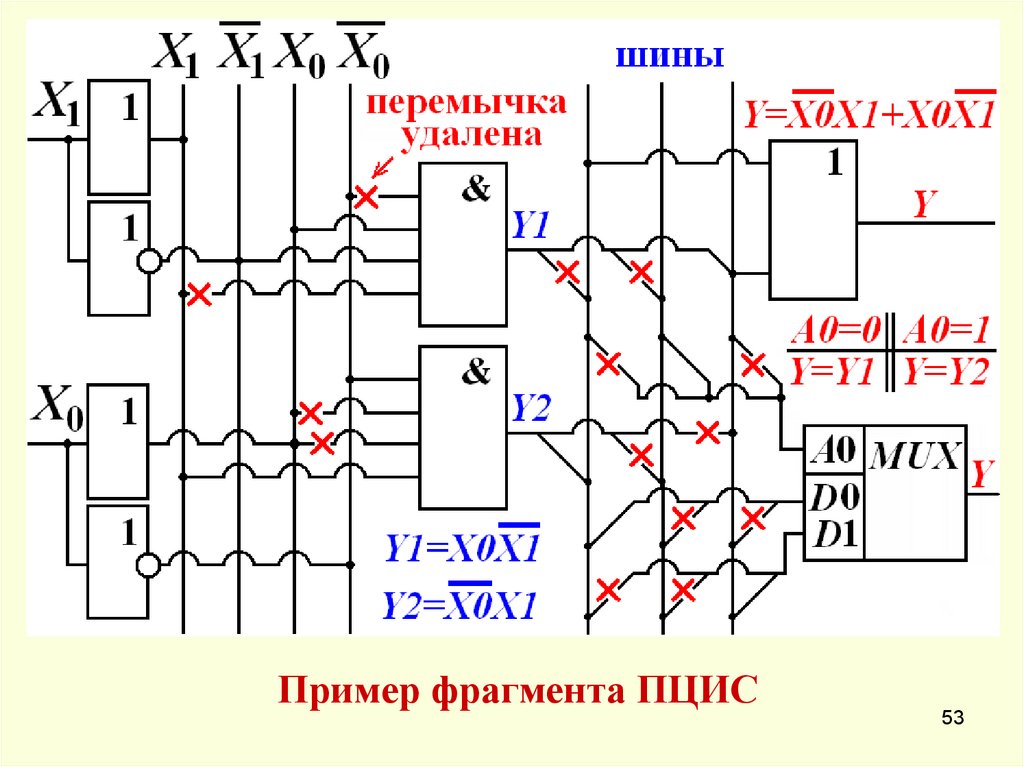

53.

Пример фрагмента ПЦИС53

54.

Преимущества перед дискретнымиэлементами:

- Уменьшение габаритов;

- Увеличение быстродействия;

- Повышение надежности;

- Защита от копирования разработки;

- Скорость разработки и модификации

потребитель.

54

55.

ВОПРОСЫ55

56.

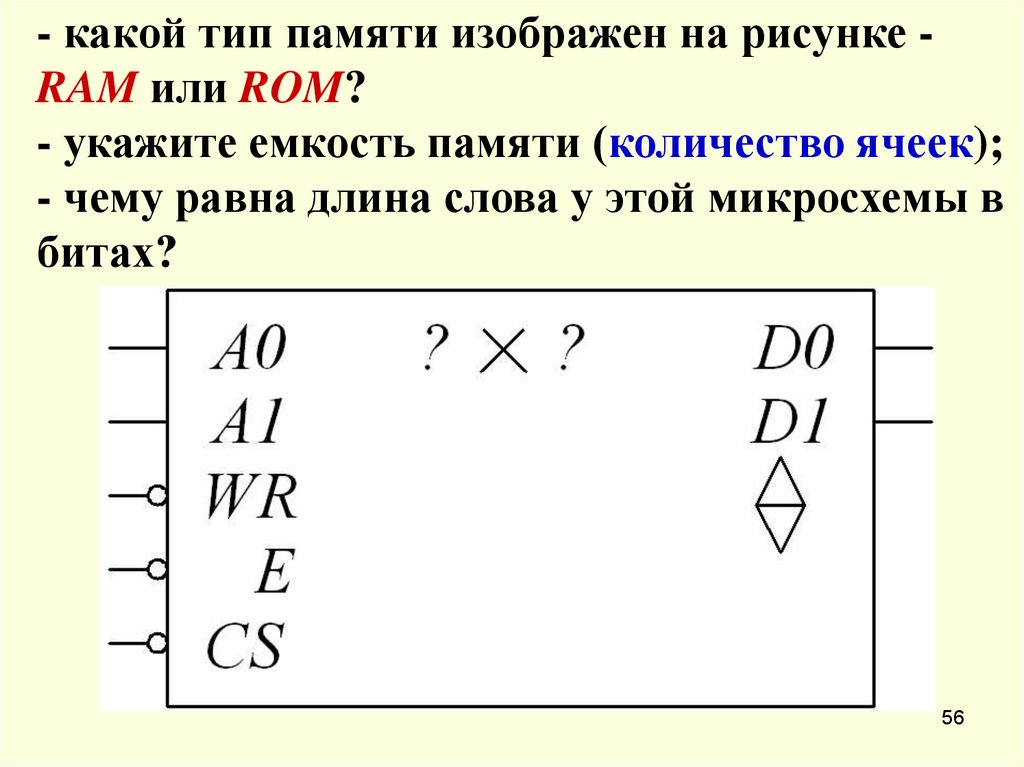

- какой тип памяти изображен на рисунке RAM или ROM?- укажите емкость памяти (количество ячеек);

- чему равна длина слова у этой микросхемы в

битах?

56

electronics

electronics