Similar presentations:

Процессоры. Лекция 3

1. Процессоры

2. По числу интегральной схем (ИС)

• Однокристальные• Многокристальные

• Многокристальные секционные

3. Функциональная структура процессора

а) общая структураб) секционных БИС

4. По назначению

• Универсальные• Специализированные

5. По виду обрабатываемых входных сигналов

• Цифровые• Аналоговые

6. По способу организации передачи и обработки информации

• Последовательного действия• Параллельного действия

• Параллельно-последовательного

действия.

7. По характеру временной организации работы процессоры

• Синхронные• Асинхронные

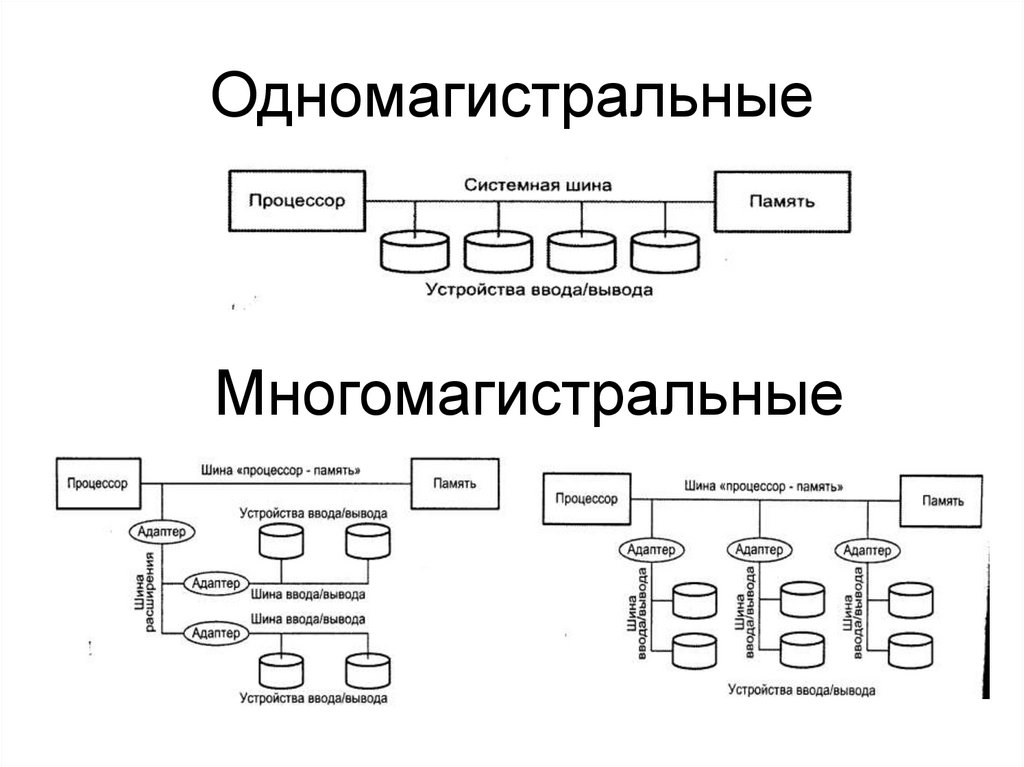

8. По организации структуры процессорных систем

• Одномагистральные• Многомагистральные

9. Одномагистральные

Многомагистральные10. По количеству выполняемых программ

• Однопрограммные процессоры• Многопрограммные процессоры

11. В зависимости от набора и порядка выполнения команд

• CISC (Сomplex Instruction Set Computer)Полный набор команд

• RISC (Redused Instruction Set Computer)

Сокращенный набор команд

• Процессор MISC, работающий с

минимальным набором длинных команд.

• Процессор VLIW, работающий с системой

команд сверхбольшой разрядности.

12. Современные процессоры RISC характеризуются

• упрощенный набор команд, имеющих одинаковую длину;• большинство команд выполняются за один такт процессора;

• отсутствуют макрокоманды, усложняющие структуру процессора и уменьшающие скорость его работы;

• взаимодействие с оперативной памятью ограничивается

операциями пересылки данных;

• резко уменьшено число способов адресации памяти (не

используется косвенная адресация);

• используется конвейер команд, позволяющий обрабатывать не

сколько из них одновременно;

• применяется высокоскоростная память.

13. Обобщенная структура процессора

Буфер адресаБуфер данных

Арифметическое и

логическое устройство

(АЛУ)

Сдвигатель

Флаги состояния

Обращение знака

Арифметикологические

операции

Внутренняя шина

процессора

Сигналы управления

Данные, адреса

Регистры

Устройство управления

(УУ)

Дешифратор

Счетчик команд

electronics

electronics