Similar presentations:

Основная терминология курса: шейдер, SM, ROP, TPC, SP. Типы параллельных архитектур: SISD, MISD, SIMD, MIMD, DSP

1.

МОСКОВСКИЙ АВИАЦИОННЫЙ ИНСТИТУТ(национальный исследовательский университет)

Факультет прикладной математики и физики

Кафедра вычислительной математики и программирования

Лекция 2

«Основная терминология курса: шейдер, SM, ROP,

TPC, SP. Типы параллельных архитектур: SISD,

MISD, SIMD, MIMD, DSP»

Выполнил: Семенов С.А.

Руководитель: Ревизников Д.Л.

2.

ВведениеСхематическое изображение графического

адаптера

Классификация вычислительных систем по

Флинну

Схематическое устройство SMP

Multithreading

Bottleneck

Московский авиационный институт

(национальный исследовательский университет)

2

Факультет прикладной математики и физики

Кафедра Вычислительной математики и

программирования

3. Графическая плата NVIDIA

Московский авиационный институт(национальный исследовательский университет)

3

Факультет прикладной математики и физики

Кафедра Вычислительной математики и

программирования

4. Средства обмена данными в компьютере

Обмен данными –важнейшая составляющая

компьютера

Примеры:

многопроцессорные

системы, FPGA etc.

По традиции отдельные

устройства имеют разные

возможности (уровни и

способы) обмена данными

Традиционная

архитектура ориентирована

на одно, центральное

счётное устройство

Московский авиационный институт

(национальный исследовательский университет)

4

Факультет прикладной математики и физики

Кафедра Вычислительной математики и

программирования

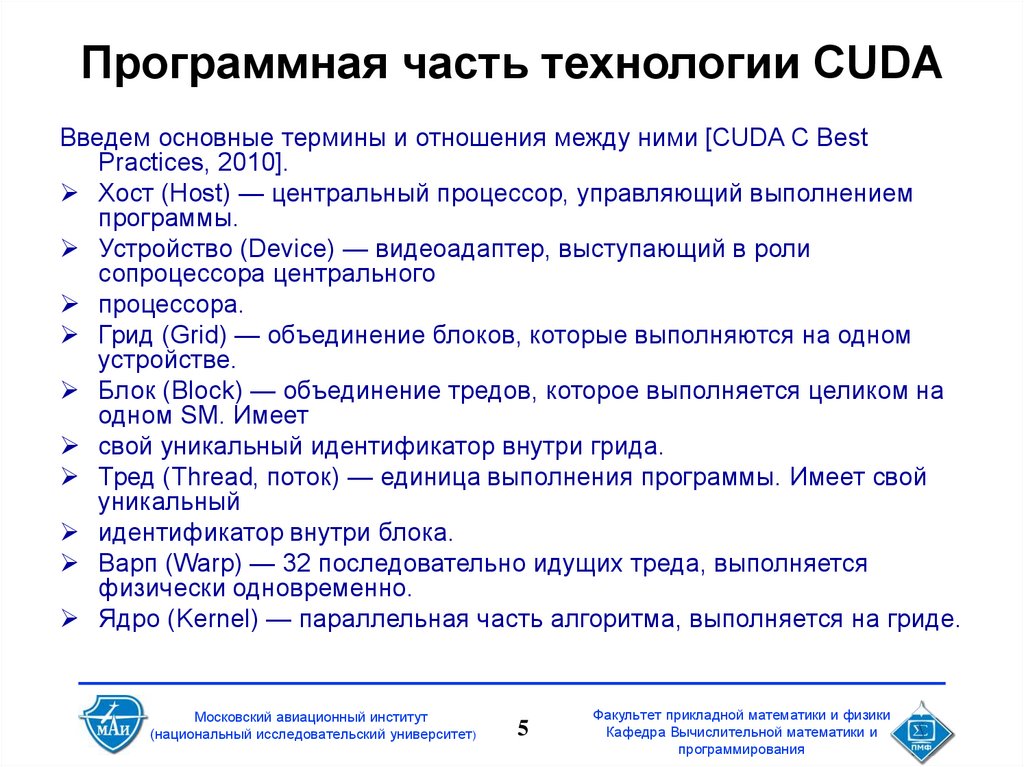

5. Программная часть технологии CUDA

Введем основные термины и отношения между ними [CUDA C BestPractices, 2010].

Хост (Host) — центральный процессор, управляющий выполнением

программы.

Устройство (Device) — видеоадаптер, выступающий в роли

сопроцессора центрального

процессора.

Грид (Grid) — объединение блоков, которые выполняются на одном

устройстве.

Блок (Block) — объединение тредов, которое выполняется целиком на

одном SM. Имеет

свой уникальный идентификатор внутри грида.

Тред (Thread, поток) — единица выполнения программы. Имеет свой

уникальный

идентификатор внутри блока.

Варп (Warp) — 32 последовательно идущих треда, выполняется

физически одновременно.

Ядро (Kernel) — параллельная часть алгоритма, выполняется на гриде.

Московский авиационный институт

(национальный исследовательский университет)

5

Факультет прикладной математики и физики

Кафедра Вычислительной математики и

программирования

6. Схематическое изображение графического адаптера

Московский авиационный институт(национальный исследовательский университет)

6

Факультет прикладной математики и физики

Кафедра Вычислительной математики и

программирования

7. DSP

Цифровой сигнальный процессор (англ. Digital signalprocessor, DSP; сигнальный микропроцессор, СМП; процессор

цифровых сигналов, ПЦС) — специализированный

микропроцессор, предназначенный для цифровой обработки

сигналов (обычно в реальном масштабе времени).

ЦСП строятся на основе Гарвардской архитектуры

Стандартные ЦСП

Московский авиационный институт

(национальный исследовательский университет)

7

Факультет прикладной математики и физики

Кафедра Вычислительной математики и

программирования

8.

Московский авиационный институт(национальный исследовательский университет)

8

Факультет прикладной математики и физики

Кафедра Вычислительной математики и

программирования

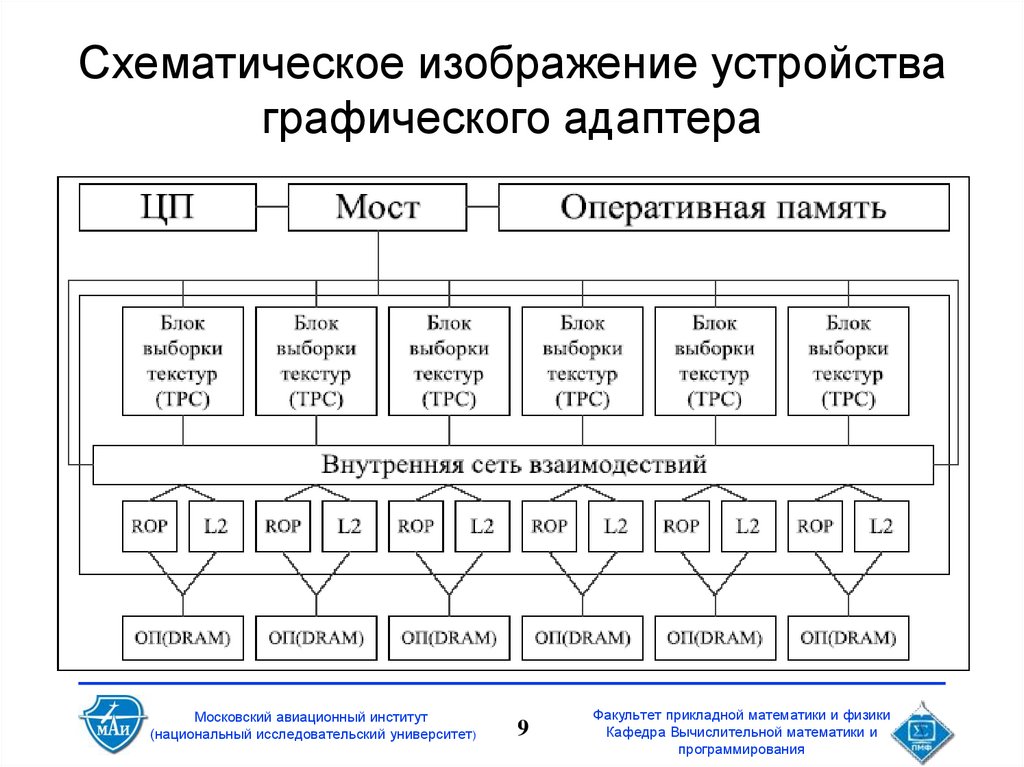

9. Схематическое изображение устройства графического адаптера

Московский авиационный институт(национальный исследовательский университет)

9

Факультет прикладной математики и физики

Кафедра Вычислительной математики и

программирования

10. Схематические особенности видеочипа

Московский авиационный институт(национальный исследовательский университет)

10

Факультет прикладной математики и физики

Кафедра Вычислительной математики и

программирования

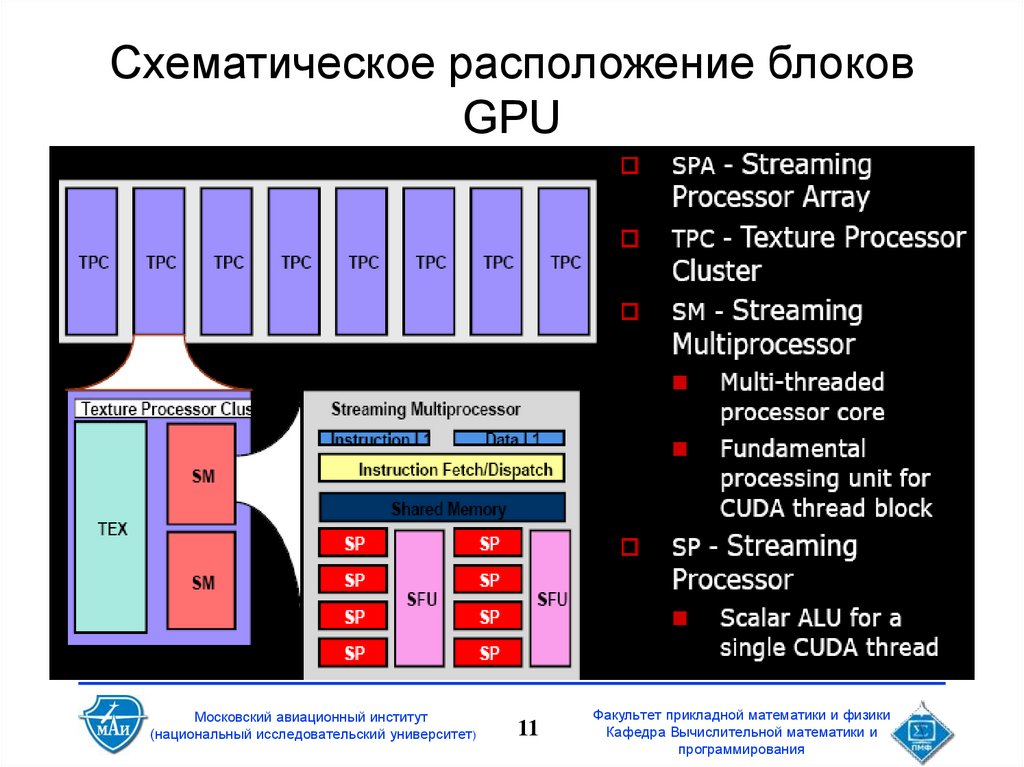

11. Схематическое расположение блоков GPU

Московский авиационный институт(национальный исследовательский университет)

11

Факультет прикладной математики и физики

Кафедра Вычислительной математики и

программирования

12. Графический адаптер на «аппаратном» уровне

TPC (Texture process cluster)

ROP — Raster Operations Pipeline

SP (Streaming Processor)

SM (Streaming Multiprocessor)

SFU (Super Function Unit)

WS — Warp Scheduler

Московский авиационный институт

(национальный исследовательский университет)

12

Факультет прикладной математики и физики

Кафедра Вычислительной математики и

программирования

13. Классификация вычислительных систем по Флинну

Московский авиационный институт(национальный исследовательский университет)

13

Факультет прикладной математики и физики

Кафедра Вычислительной математики и

программирования

14. Классы систем

CPU (одноядерный) — SISD (одновременно выполняется толькоодна инструкция над одним набором операндов);

CPU (многоядерный) — MIMD (Одновременно несколько ядер

могут работать совершенно независимо, каждое как SISD);

GPU (NVIDIA ComputeCapability версии < 2.0) — SIMD

(одновременно на графическом адаптере может выполняться

только один поток вычислений, который работает с большим

набором данных);

GPU (NVIDIA ComputeCapability версии ≥ 2.0) — MIMD

(одновременно на графическом адаптере может выполняться

несколько потоков вычислений, каждый из которых работает с

большим набором данных).

Таким образом видно, что графические процессоры изначально

предназначены для параллельного решения одной массивнопараллельной задачи.

Московский авиационный институт

(национальный исследовательский университет)

14

Факультет прикладной математики и физики

Кафедра Вычислительной математики и

программирования

15. Классификация систем

• CPU – SISD– Multithreading: позволяет запускать множество

потоков – параллелизм на уровне задач (MIMD)

или данных (SIMD)

– SSE: набор 128 битных регистров ЦПУ

• можно запаковать 4 32битных скаляра и проводить над

ними операции одновременно (SIMD)

• GPU – SIMD*

Звездочка стоит для того, чтобы вы обратили внимание.

На следующих лекциях вы увидите, что GPU не совсем SIMD архитектура а скорее

SIMT (simultaneous multithreading):

* разные блоки могут выполнять разный код (без потери производительности)

* внутри одного блока можно выполнять разный код (с потерей

производиетльности)

Московский авиационный институт

(национальный исследовательский университет)

15

Факультет прикладной математики и физики

Кафедра Вычислительной математики и

программирования

16. SIMT (Single instruction, multiple threads)

Параллельно на каждом SMвыполняется большое число отдельных

нитей (threads)

Нити подряд разбиваются на warp (по

32 нити) и SM управляет выполнением

warp

Нити в пределах одного warp

выполняются физически параллельно

Большое число warp покрывает

латентность

Московский авиационный институт

(национальный исследовательский университет)

16

Факультет прикладной математики и физики

Кафедра Вычислительной математики и

программирования

17. Схематическое изображение устройства TPC и SM

Московский авиационный институт(национальный исследовательский университет)

17

Факультет прикладной математики и физики

Кафедра Вычислительной математики и

программирования

18. Symmetric Multiprocessor Architecture (SMP)

Каждый процессоримеет свои L1 и L2 кэши

подсоединен к общей шине

отслеживает доступ других

процессоров к памяти для

обеспечения единого образа памяти

(например, один процессор хочет

изменить данные, кэшированные

другим процессором)

Московский авиационный институт

(национальный исследовательский университет)

18

Факультет прикладной математики и физики

Кафедра Вычислительной математики и

программирования

19. Symmetric Multiprocessor Architecture (SMP)

BusCache Control

Cache Control

Cache Control

L2 cache

L2 cache

L2 cache

L1-I

L1-D

L1-I

P0

Московский авиационный институт

(национальный исследовательский университет)

L1-D

P1

19

L1-I

L1-D

P2

Факультет прикладной математики и физики

Кафедра Вычислительной математики и

программирования

20. Программная модель CUDA

Параллельная часть кода выполняетсякак большое количество нитей (threads)

Нити группируются в блоки (blocks)

фиксированного размера

Блоки объединяются в сеть блоков (grid)

Ядро выполняется на сетке из блоков

Каждая нить и блок имеют свой

уникальный идентификатор

Московский авиационный институт

(национальный исследовательский университет)

20

Факультет прикладной математики и физики

Кафедра Вычислительной математики и

программирования

21. Что такое ВОРП (WARP)?

Device делает 1 grid в любоймомент

SM обрабатывает 1 или более

blocks

Каждый Block разделён на

SIMD группы, внутри которых

одни и те же

инструкциивыполняются

реально одновременно над

различными данными (warps)

warp size=16/32

Связывание в ворпы

детерминировано в порядке

нарастания threadID

threadID=TIDX.x+TIDX.y*Dx+TI

DX.z*Dx*Dy

Полуворп – первая или

вторая половина ворпа

Московский авиационный институт

(национальный исследовательский университет)

21

Факультет прикладной математики и физики

Кафедра Вычислительной математики и

программирования

22. Итоги лекции

В результате лекции Вы должны :Понимать возможности

использования GPU для расчётов с

точки зрения пропускной

способности системы обмена

данными компьютера

Иметь понятие об организации

разработки приложений

Достаточные знания для начала

самостоятельной работы

Московский авиационный институт

(национальный исследовательский университет)

22

Факультет прикладной математики и физики

Кафедра Вычислительной математики и

программирования

23.

Московский авиационный институт(национальный исследовательский университет)

23

Факультет прикладной математики и физики

Кафедра Вычислительной математики и

программирования

mathematics

mathematics programming

programming