Similar presentations:

Устройства программируемой логикой (УПЛ)

1.

Харьковский национальный университет радиоэлектроникиЛЕКЦИЯ 2-10

УСТРОЙСТВА ПРОГРАММИРУЕМОЙ

ЛОГИКОЙ (УПЛ)

Кафедра КИТС

Кораблев Н.М.

2.

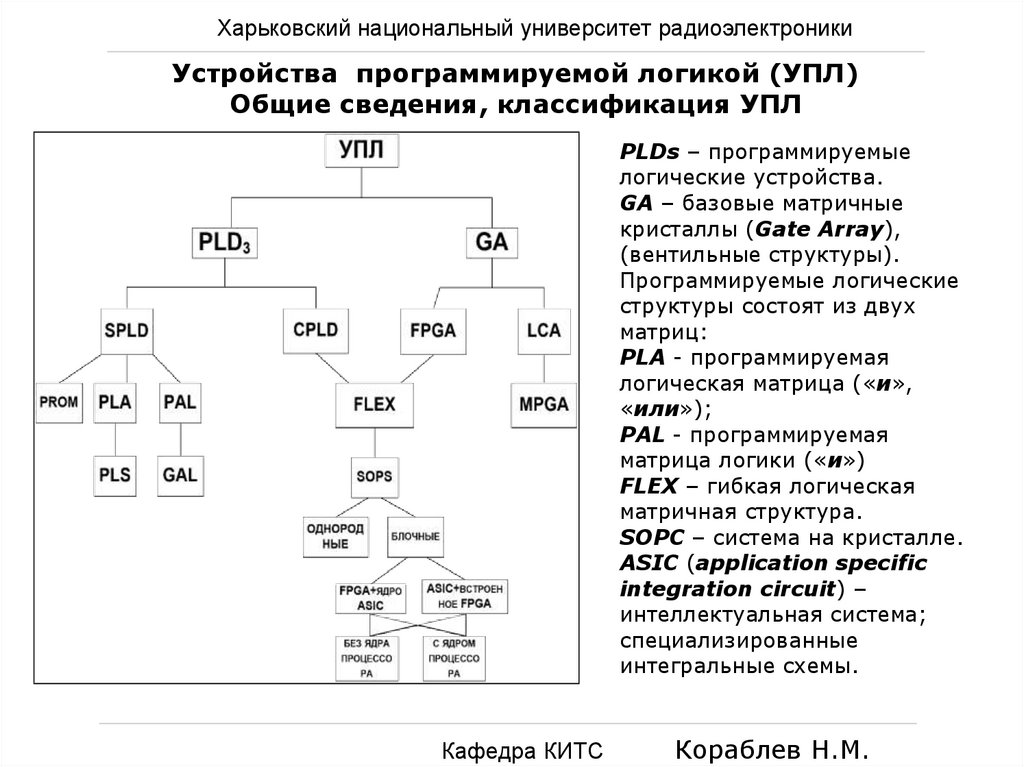

Харьковский национальный университет радиоэлектроникиУстройства программируемой логикой (УПЛ)

Общие сведения, классификация УПЛ

PLDs – программируемые

логические устройства.

GA – базовые матричные

кристаллы (Gate Array),

(вентильные структуры).

Программируемые логические

структуры состоят из двух

матриц:

PLA - программируемая

логическая матрица («и»,

«или»);

PAL - программируемая

матрица логики («и»)

FLEX – гибкая логическая

матричная структура.

SOPC – система на кристалле.

ASIC (application specific

integration circuit) –

интеллектуальная система;

специализированные

интегральные схемы.

Кафедра КИТС

Кораблев Н.М.

3.

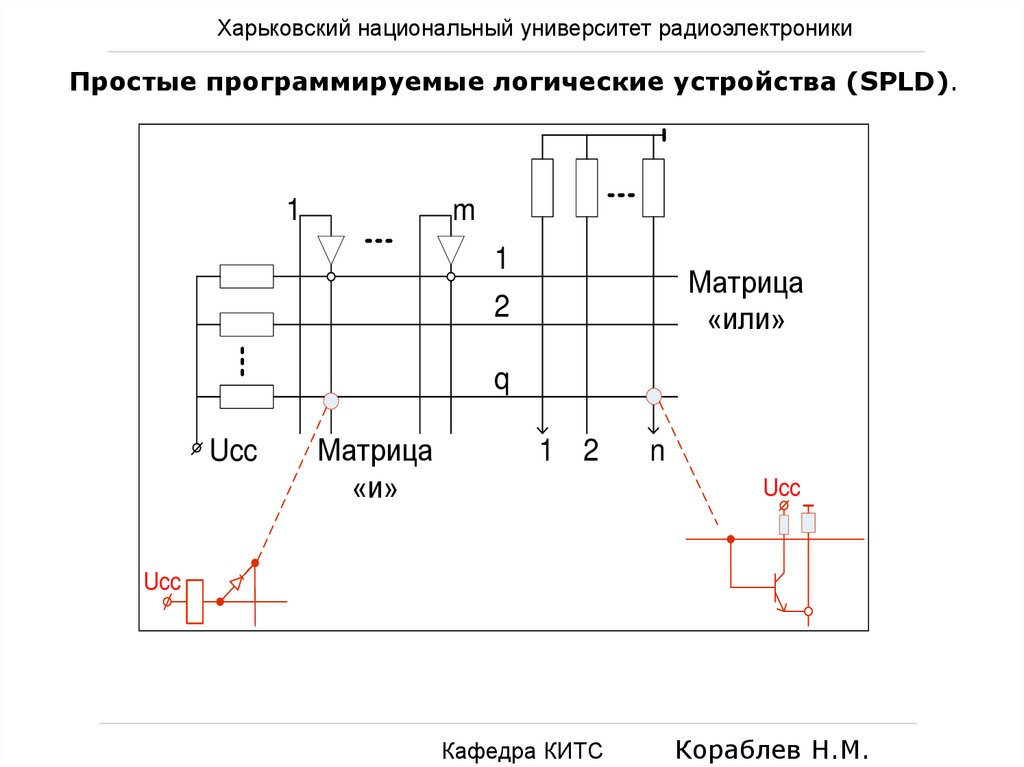

Харьковский национальный университет радиоэлектроникиПростые программируемые логические устройства (SPLD).

1

m

1

Матрица

«или»

2

q

Ucc

Матрица

«и»

1 2

n

Ucc

Ucc

Кафедра КИТС

Кораблев Н.М.

4.

Харьковский национальный университет радиоэлектроникиПростые программируемые логические устройства (SPLD).

Кафедра КИТС

Кораблев Н.М.

5.

Харьковский национальный университет радиоэлектроникиУ PROM матрица «и» полная. Она не программируется, она задана.

Программируется только «или».

PLA (m, q, n)

PLA (16, 18, 8)

Для PAL характерно то, что программируется только матрица «и»,

а матрица «или» не программируется.

Термы разбиты на группы и в соответствующих группах они

объединяются элементом «или».

В PAL упрощение матрицы «или» позволило добавить в структуру

цепи обратной связи и выходные буферы, что качественно изменяет

элемент.

Выходные буферы представляют собой программируемые

макроячейки, которые определяют PAL.

Макроячейки могут включать выходной инвертор с тремя

состояниями, триггеры различного типа, вентили и другие элементы.

Макроячейка может быть комбинационная (без памяти) либо

регистровая (с памятью), без обратной связи и с обратной.

Путём программирования управлять ячейкой можно либо внешними

сигналами (CLK, Reset, OE), либо внутренними сигналами, которые

формируются в матрице «и».

Кафедра КИТС

Кораблев Н.М.

6.

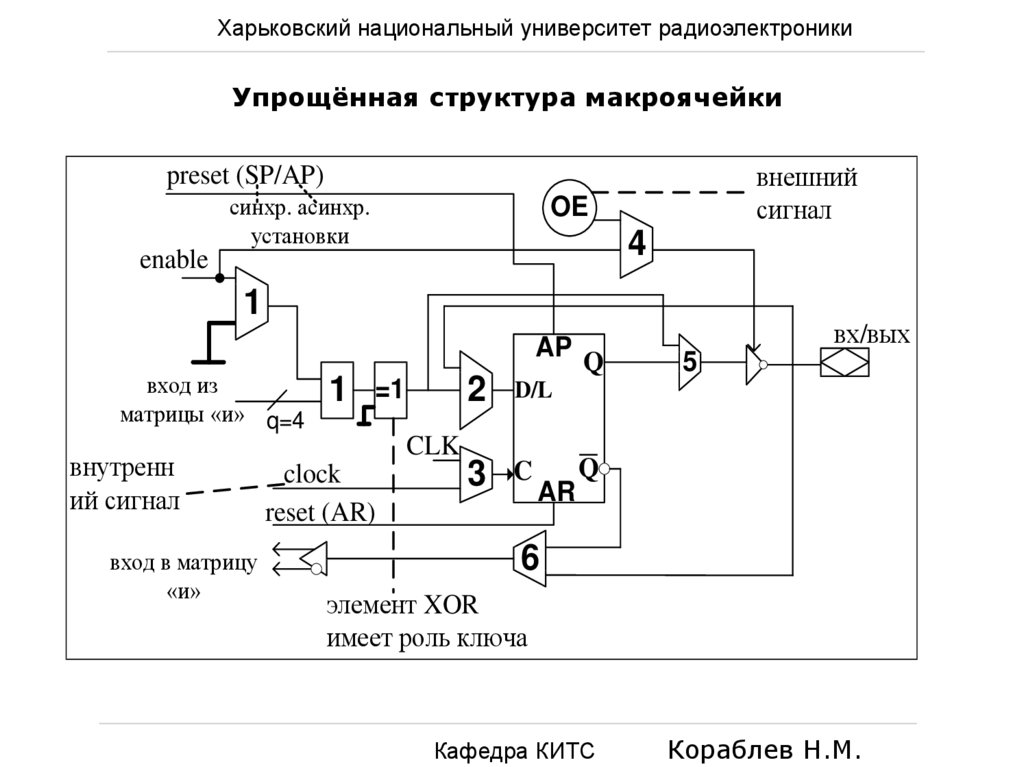

Харьковский национальный университет радиоэлектроникиУпрощённая структура макроячейки

внешний

сигнал

preset (SP/AP)

синхр. асинхр.

установки

OE

4

enable

1

AP

вход из

матрицы «и» q=4

внутренн

ий сигнал

вход в матрицу

«и»

1

=1

CLK

clock

reset (AR)

2

D/L

3

C

AR

вх/вых

Q

5

Q

6

элемент XOR

имеет роль ключа

Кафедра КИТС

Кораблев Н.М.

7.

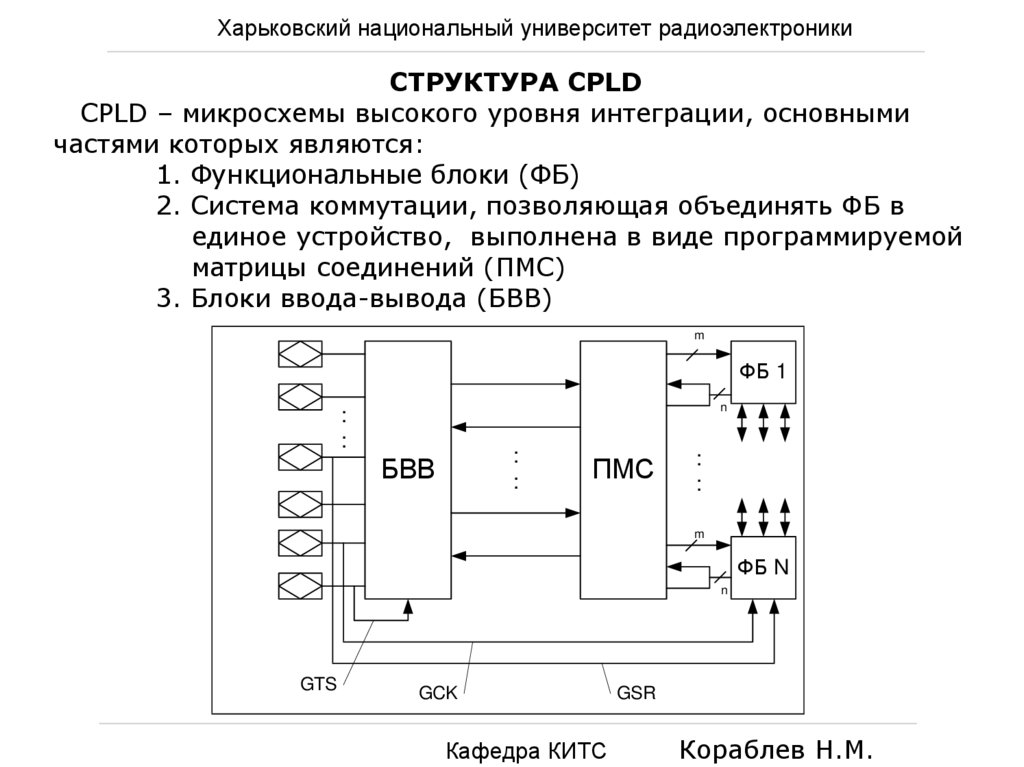

Харьковский национальный университет радиоэлектроникиСТРУКТУРА CPLD

CPLD – микросхемы высокого уровня интеграции, основными

частями которых являются:

1. Функциональные блоки (ФБ)

2. Система коммутации, позволяющая объединять ФБ в

единое устройство, выполнена в виде программируемой

матрицы соединений (ПМС)

3. Блоки ввода-вывода (БВВ)

m

ФБ 1

n

:

:

:

:

БВВ

ПМС

:

:

m

ФБ N

n

GTS

GCK

Кафедра КИТС

GSR

Кораблев Н.М.

8.

Харьковский национальный университет радиоэлектроникиСТРУКТУРА CPLD

Программируемая логическая интегральная схема CPLD состоит из

нескольких макроячеек, расположенных на одном кристалле. Каждая

макроячейка соединена с блоками ввода-вывода, осуществляющими

формирование необходимого вида входов или выходов для работы с

внешними схемами. Кроме того, все макроячейки и блоки вводавывода связаны между собой внутренними параллельными шинами.

Пример внутренней схемы CPLD приведен на рисунке

Кафедра КИТС

Кораблев Н.М.

9.

Харьковский национальный университет радиоэлектроникиВнутренняя схема макроячейки микросхемы CPLD

Кафедра КИТС

Кораблев Н.М.

10.

Харьковский национальный университет радиоэлектроникиCPLD может содержать N ФБ, каждый из которых может иметь n

макроячеек.

ФБ получают информацию от ПМС (m-сигналы), каждый ФБ

может формировать n выходных сигналов, которые могут

подаваться в ПМС или БВВ.

ПМС обеспечивает полную коммутируемость ФБ, т.е.

возможность подавать сигналы с любого выхода на любой вход.

БВВ связаны внешними двунаправленными выводами и могу быть

запрограммированы как на вход, так и на выход.

Нижние три вывода могут использоваться как ввод-вывод либо

для подачи внешних управляющих сигналов.

Кроме указанных частей в CPLD могут входить:

• Контролирующие внешние интерфейсы jTAG (для

тестирования микропрограммы)

• Контроллер для управления операциями программирования и

др.

Кафедра КИТС

Кораблев Н.М.

11.

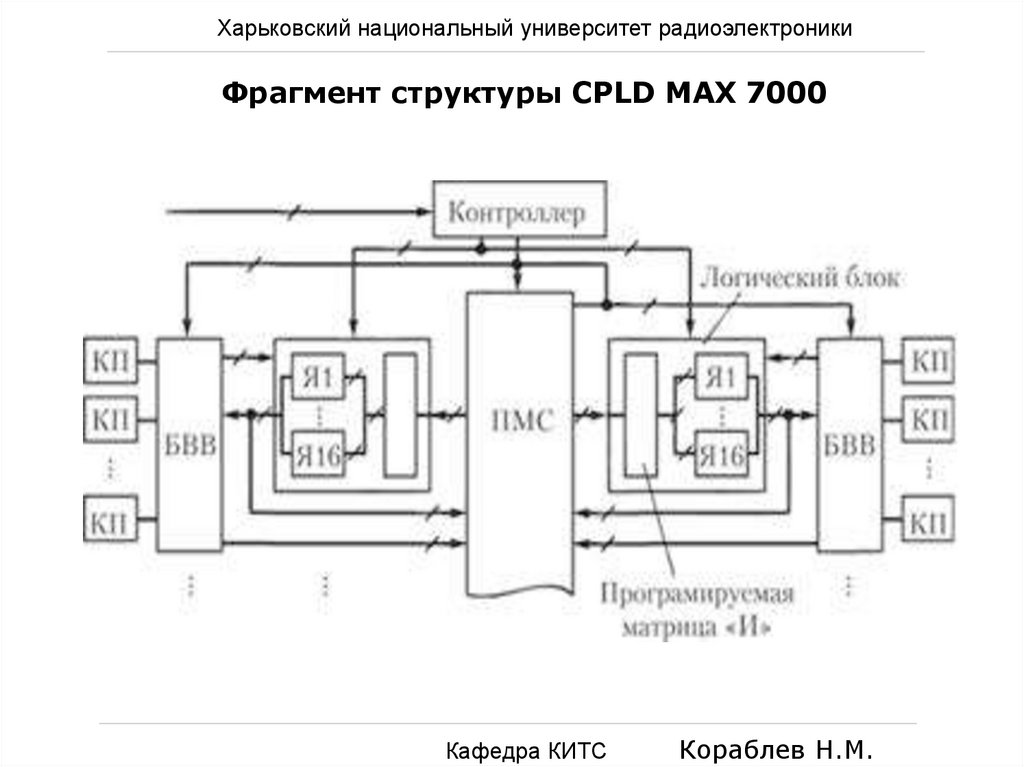

Харьковский национальный университет радиоэлектроникиФрагмент структуры CPLD МАХ 7000

Кафедра КИТС

Кораблев Н.М.

12.

Харьковский национальный университет радиоэлектроникиПрограммируемая матрица соединений

ПМС выходы ФБ подключаются к вертикальным

непрерывным, несегментируемым линиям, при этом каждому

выходу соответствует своя линия.

Входы ФБ связаны с горизонтальными линиями,

пересекающими все вертикальные линии. На пересечении

вертикальных и горизонтальных линий могут быть связующие

элементы.

Для подключения необходимой линии на вход ФБ

используется управление потенциалом точки, т.е. управляется

потенциал, а он управляет ключом.

ФБ 1

i-й

вход

&

Uc

…

…

…

ФБ N

Кафедра КИТС

На

ИЛИ

Тг

Кораблев Н.М.

13.

Харьковский национальный университет радиоэлектроникиДостоинством ПМС являются малая и предсказуемая задержка

коммутируемых сигналов, так как для каждого соединения образуется

идентичный всем другим канал связи с малым числом программируемых

ключей.

ПМС такого типа эффективны в схемах с относительно небольшим

числом коммутируемых блоков.

Функциональные блоки

Основными частями ФБ являются:

Программируемая матрица элементов «И»

Матрица распределения термов

Группа из нескольких макроячеек

Есть m-входов и n-выходов. Основа каждого блока является PAL

подобные структуры.

В CPLD матрица элементов ИЛИ не является полностью

фиксированной и, благодаря введению в схему матицы распределения

термов, возможно варьирование числа термов в вырабатываемой

функции.

МИ

МРТ1

МЯ 1

МРТ2

МЯ 2

...

...

МРТn

n

n

МЯ N

Кафедра КИТС

Кораблев Н.М.

14.

Харьковский национальный университет радиоэлектроникиПри этом термы заимствуют у других каналов выработки

функций или отдаются им.

Проще всего организовать коммутацию между соседними

каналами.

Схемотехнически в операциях распределения термов по

каналам ФБ задействованы как непосредственно цепи коммутации

между входами и выходами матрицы распределения термов, так и

логические распределители последовательного и параллельного

типов.

Последовательные (разделяемые общие) логические

расширители создаются подачей инвертируемого значения терма из

матрицы распределения термов данного канала обратно на один из

входов МИ, который становится доступным другим каналам.

Параллельный расширитель позволяет передавать термы

одного канала другому.

Термы от матрицы распределения термов поступают далее на

часть ФБ, называемую макроячейкой, которая содержит в качестве

основы программируемых мультиплексоров, триггеров, ключей и

формирует группу выходных сигналов в нескольких вариантах.

Кафедра КИТС

Кораблев Н.М.

15.

Харьковский национальный университет радиоэлектроникиБлоки ввода-вывода

Основой служат входной и выходной буферы. Структурно можно

представить следующим образом:

к другим

МЯ

К ПМС

1

Ucc

От МЯ

PTOE

2

3

0

1

ПрСт

ОЕ

1

ПрКф

ПрК

GOE 1

int

GOE 2

Ucc

2

Согласно принятой классификации в классе CPLD попадает ПЛИС с уровнем

интеграции от 600 до 20000 эквивалентных вентилей с числом макроячеек

от 32 до 512, числом ФБ от 2 до 16 и временем распределения сигнала от

любого входа до любого выхода от 5 до 20 ns.

Кафедра КИТС

Кораблев Н.М.

16.

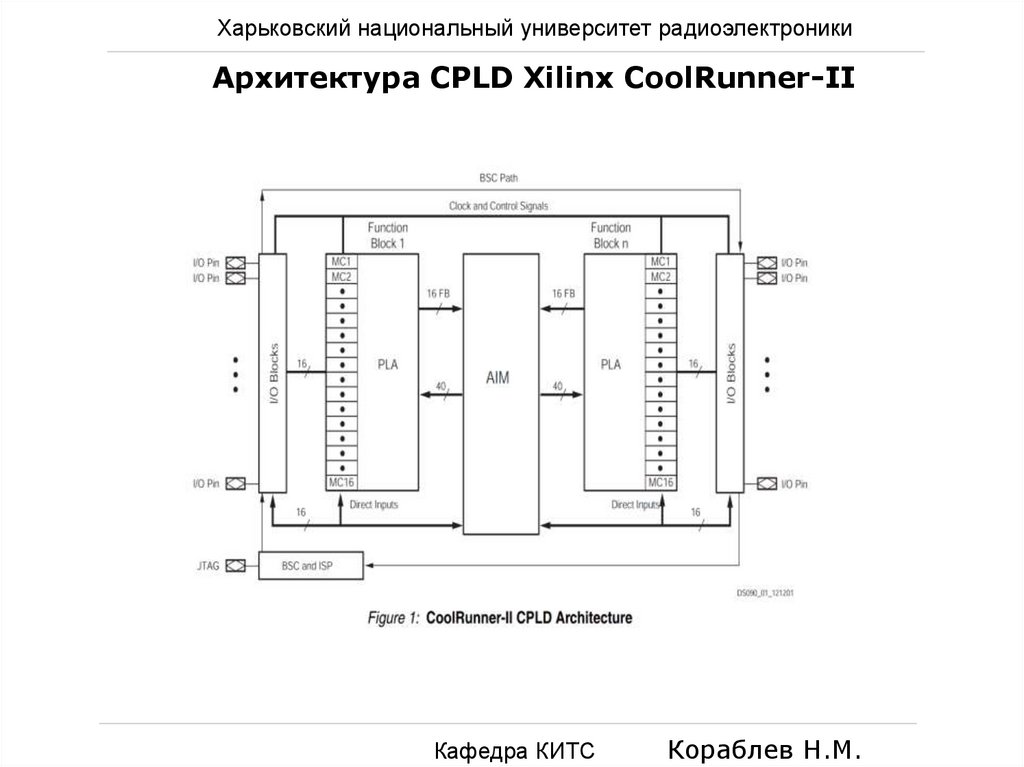

Харьковский национальный университет радиоэлектроникиАрхитектура CPLD Xilinx CoolRunner-II

Кафедра КИТС

Кораблев Н.М.

17.

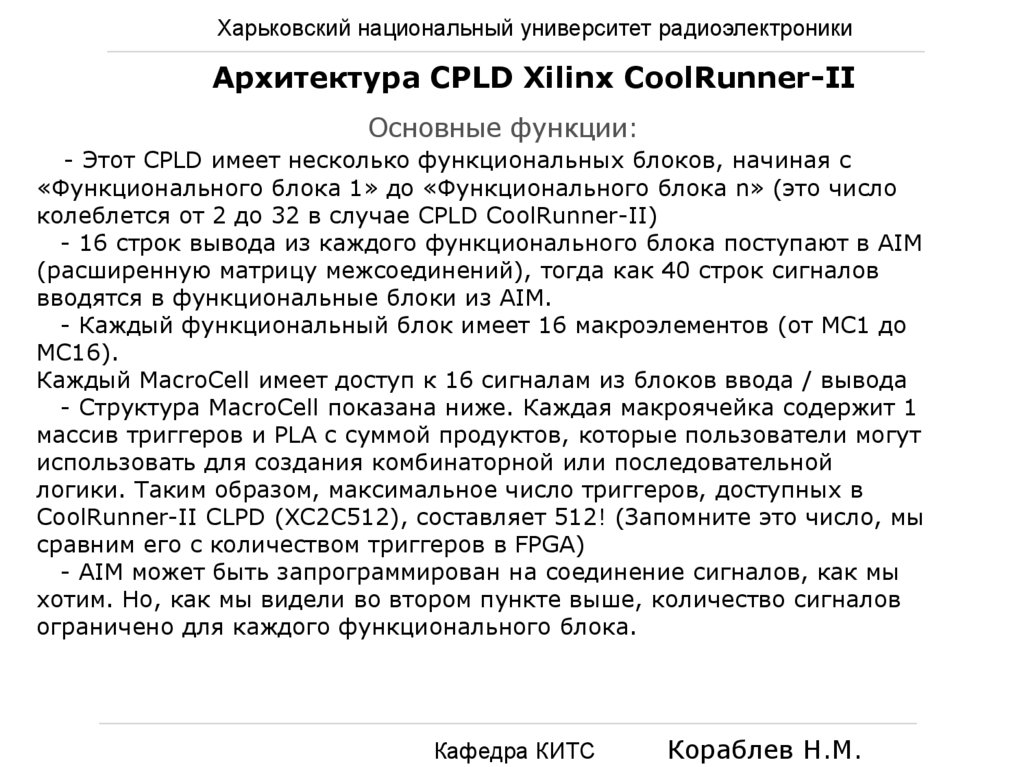

Харьковский национальный университет радиоэлектроникиАрхитектура CPLD Xilinx CoolRunner-II

Основные функции:

- Этот CPLD имеет несколько функциональных блоков, начиная с

«Функционального блока 1» до «Функционального блока n» (это число

колеблется от 2 до 32 в случае CPLD CoolRunner-II)

- 16 строк вывода из каждого функционального блока поступают в AIM

(расширенную матрицу межсоединений), тогда как 40 строк сигналов

вводятся в функциональные блоки из AIM.

- Каждый функциональный блок имеет 16 макроэлементов (от MC1 до

MC16).

Каждый MacroCell имеет доступ к 16 сигналам из блоков ввода / вывода

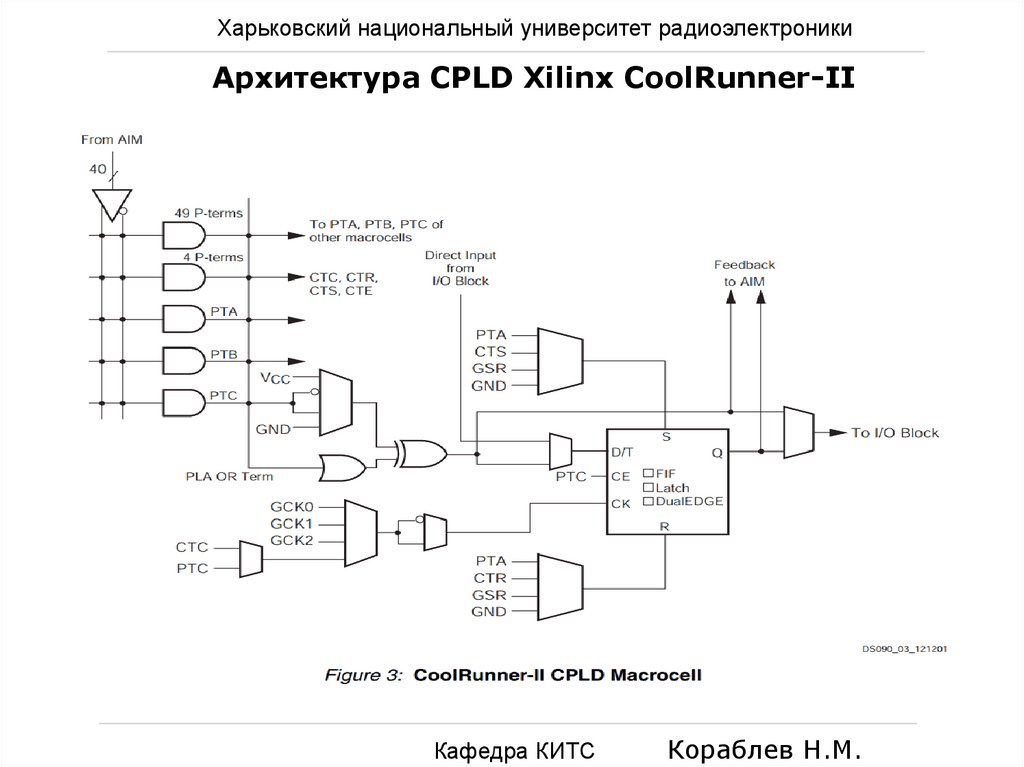

- Структура MacroCell показана ниже. Каждая макроячейка содержит 1

массив триггеров и PLA с суммой продуктов, которые пользователи могут

использовать для создания комбинаторной или последовательной

логики. Таким образом, максимальное число триггеров, доступных в

CoolRunner-II CLPD (XC2C512), составляет 512! (Запомните это число, мы

сравним его с количеством триггеров в FPGA)

- AIM может быть запрограммирован на соединение сигналов, как мы

хотим. Но, как мы видели во втором пункте выше, количество сигналов

ограничено для каждого функционального блока.

Кафедра КИТС

Кораблев Н.М.

18.

Харьковский национальный университет радиоэлектроникиАрхитектура CPLD Xilinx CoolRunner-II

Кафедра КИТС

Кораблев Н.М.

electronics

electronics