Similar presentations:

Аппаратные средства ЦОС. Часть 2

1.

Часть 2Лекции для магистров направления 210400.68 «Радиотехника» магистерская программа

«Системы цифровой обработки сигналов в радиолокации, связи и управлении»

1

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

2.

1. Справочник по радиоэлектронным системам. В 2-х томах. Т.1. Захаров В.Н., Кривицкий Б.Х., Мамаев Н.С. и др.; Под ред. Б.Х.Кривицкого – М.: Энергия, 1979 –352 c., ил.

2. Miles Murdocca PRINCIPLES OF COMPUTER ARCHITECTURE An Integrated Approach http://www.cs.rutgers.edu/~murdocca/

3. Сверхбольшие интегральные схемы и современная обработка сигналов: Пер. с англ./Под ред. С. Гуна, Х. Уайтхауса, Т.

Кайлата. – М.: Радио и связь, 1989.– 472 с.

4. Труды института инженеров по электротехнике и радиоэлектронике. Тематический выпуск ЦИФРОВАЯ ОБРАБОТКА

СИГНАЛОВ. ТИИЭР т. 63, №4 апрель 1975. – М.: Мир, 1975 –195 с.

5. Steven W. Smith The Scientist and Engineer's Guide to Digital Signal Processing, California Technical Publishing, San Diego,

California. 1999.

6. Оппенгейм А.В., Шафер Р.В. Цифровая обработка сигналов: Пер. с англ./ Под ред. С.Я.Шаца.– М.: Связь, 1979.– 416с.

7. Хемминг Р.В. Цифровые фильтры: Пер. с англ./ Под ред. А.М.Трахтмана. – М.: Сов. радио, 1980.– 224 с., ил.

8. Сергиенко А.Б. Цифровая обработка сигналов: – СПб.: Питер, 2002.–608с.:ил.

9. Стешенко В. Школа разработки аппаратуры цифровой обработки сигналов на ПЛИС. Chip News,1999, №8–10, 2000, № 1, 3–5.

10. Стешенко В. Б. Школа схемотехнического проектирования устройств обработки сигналов. Компоненты и технологии, № 3–6,

2000

11. http://www.andraka.com/files/crdcsrvy.pdf

12. Application Note 73 (Implementing FIR Filters in FLEX Device) v.1.01. Altera Corporation, 1998

13. LogiCore Digital Down Converter v1.0. Xilinx Inc., 2002

14. LogiCore Cascaded Integrator-Comb (CIC) Filter v2.0. Xilinx Inc., 2001

15. LogiCore Distributed Arithmetic FIR Filter v7.0. Xilinx Inc., 2002

16. LogiCore MAC FIR v2.0. Xilinx Inc., 2002

17. LogiCore CORDIC v1.1. Xilinx Inc., 2002

18. AD6620. 65 MSPS Digital Receive Signal Processor. Analog Devices, Inc., 1998

19. GC4016 Multi-Standard Quad DDC Chip Data Sheet. Rev.1.0. Graychip, Inc., 2001

20. CORDIC Core Specification. Rev.0.3 http://www.opencores.org, 2001

21. A Technical Tutorial on Digital Signal Syntesis. Analog Devices, Inc. 1999

22. High Speed Design Techniques. Section 6 in ANALOG DEVICES TECHNICAL REFERENCE BOOKS. Analog Devices, Inc. 1996

23. А.И.Солонина, Д.А.Улахович, С.М.Арбузов, Е.Б.Соловьева. Основы цифровой обработки сигналов. СПб, БХВ-Петербург, 2005

2

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

3.

3Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

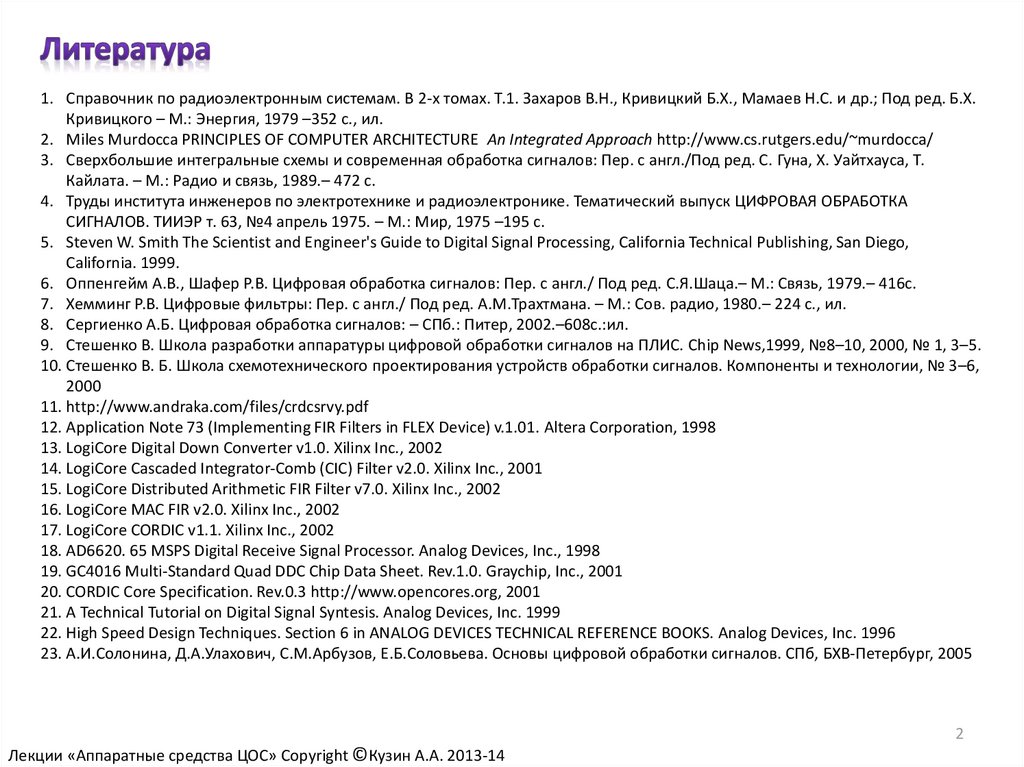

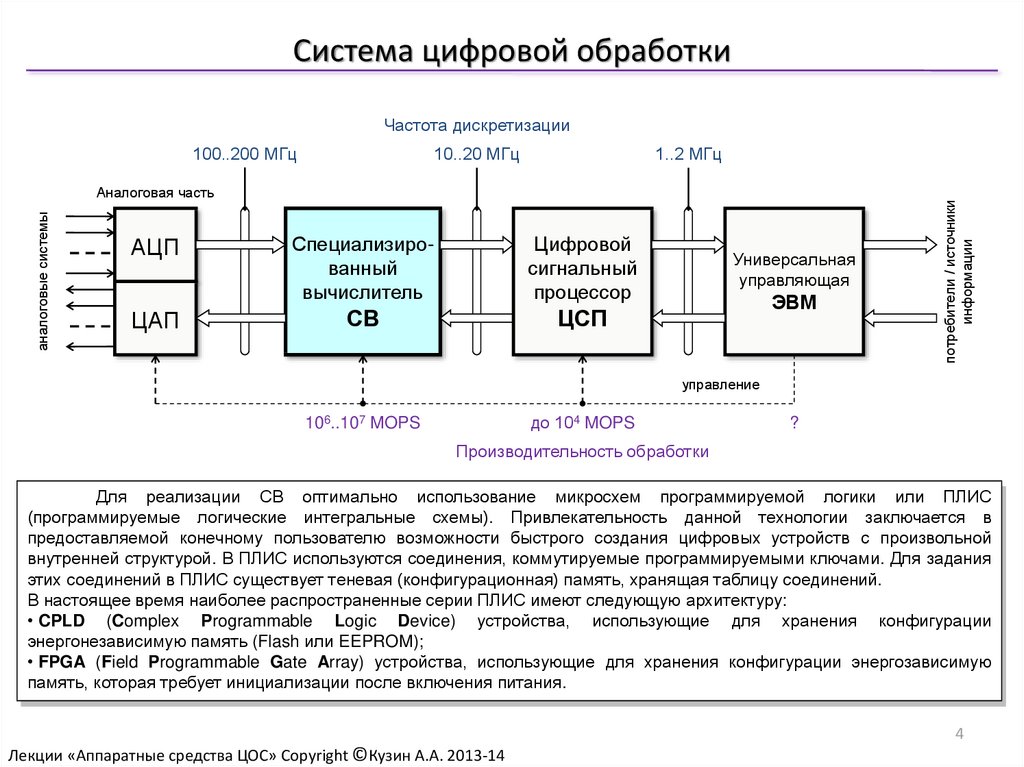

4. Система цифровой обработки

Частота дискретизации10..20 МГц

1..2 МГц

аналоговые системы

Аналоговая часть

АЦП

Специализированный

вычислитель

Цифровой

сигнальный

процессор

ЦАП

СВ

ЦСП

Универсальная

управляющая

ЭВМ

потребители / источники

информации

100..200 МГц

управление

до 104 MOPS

106..107 MOPS

?

Производительность обработки

Для реализации СВ оптимально использование микросхем программируемой логики или ПЛИС

(программируемые логические интегральные схемы). Привлекательность данной технологии заключается в

предоставляемой конечному пользователю возможности быстрого создания цифровых устройств с произвольной

внутренней структурой. В ПЛИС используются соединения, коммутируемые программируемыми ключами. Для задания

этих соединений в ПЛИС существует теневая (конфигурационная) память, хранящая таблицу соединений.

В настоящее время наиболее распространенные серии ПЛИС имеют следующую архитектуру:

• CPLD (Complex Programmable Logic Device) устройства, использующие для хранения конфигурации

энергонезависимую память (Flash или EEPROM);

• FPGA (Field Programmable Gate Array) устройства, использующие для хранения конфигурации энергозависимую

память, которая требует инициализации после включения питания.

4

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

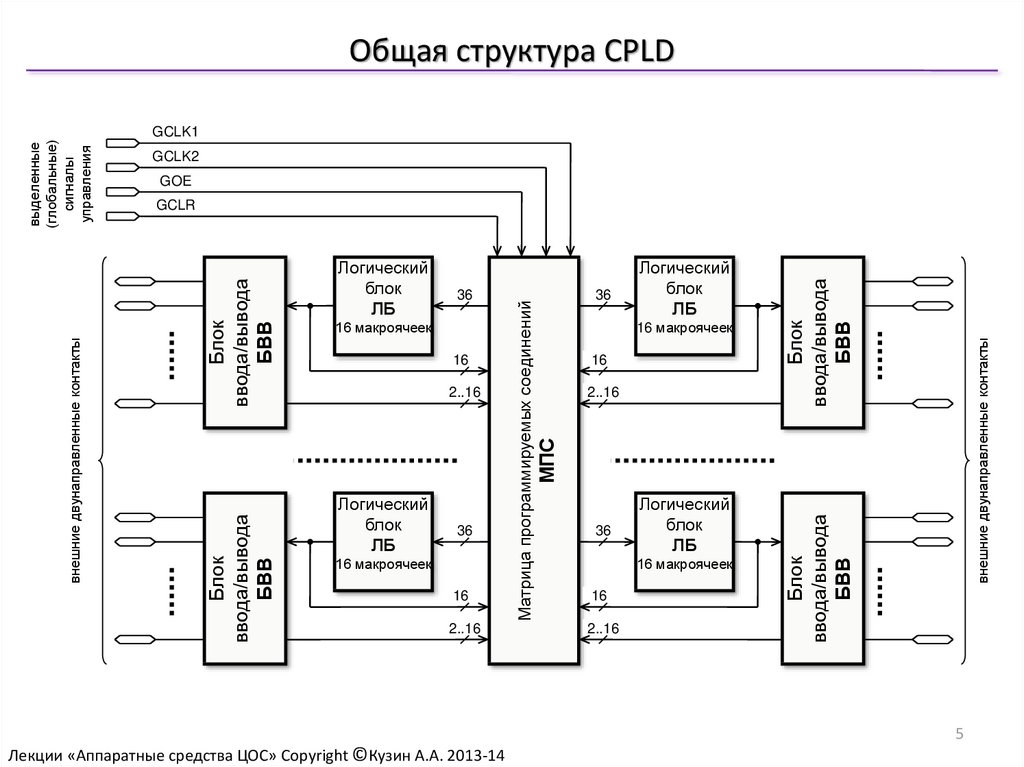

5. Общая структура CPLD

GCLK2GOE

2..16

Логический

блок

ЛБ

36

16 макроячеек

16

2..16

16

2..16

внешние двунаправленные контакты

16

16 макроячеек

Блок

ввода/вывода

БВВ

16 макроячеек

36

36

Логический

блок

ЛБ

16 макроячеек

16

2..16

Блок

ввода/вывода

БВВ

36

Логический

блок

ЛБ

МПС

Логический

блок

ЛБ

Матрица программируемых соединений

Блок

ввода/вывода

БВВ

GCLR

Блок

ввода/вывода

БВВ

внешние двунаправленные контакты

выделенные

(глобальные)

сигналы

управления

GCLK1

5

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

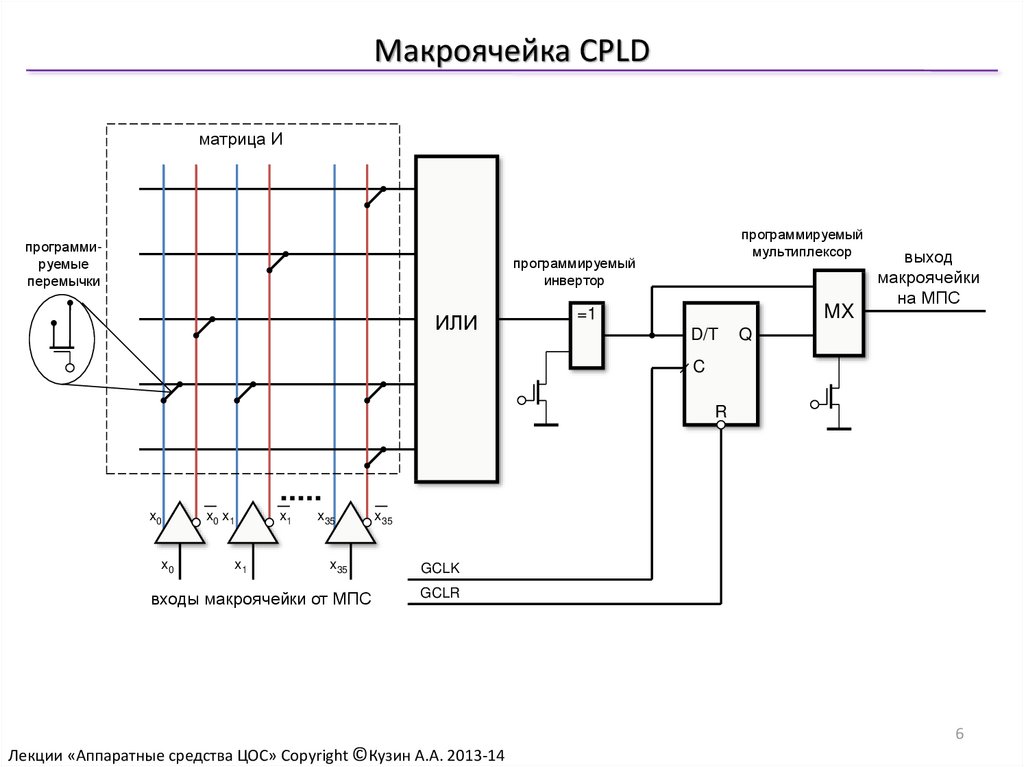

6. Макроячейка CPLD

матрица Ипрограммируемые

перемычки

программируемый

мультиплексор

программируемый

инвертор

ИЛИ

MX

=1

D/T

выход

макроячейки

на МПС

Q

C

R

x0

x0

x0 x1

x1

x1

x35

x35

входы макроячейки от МПС

x35

GCLK

GCLR

6

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

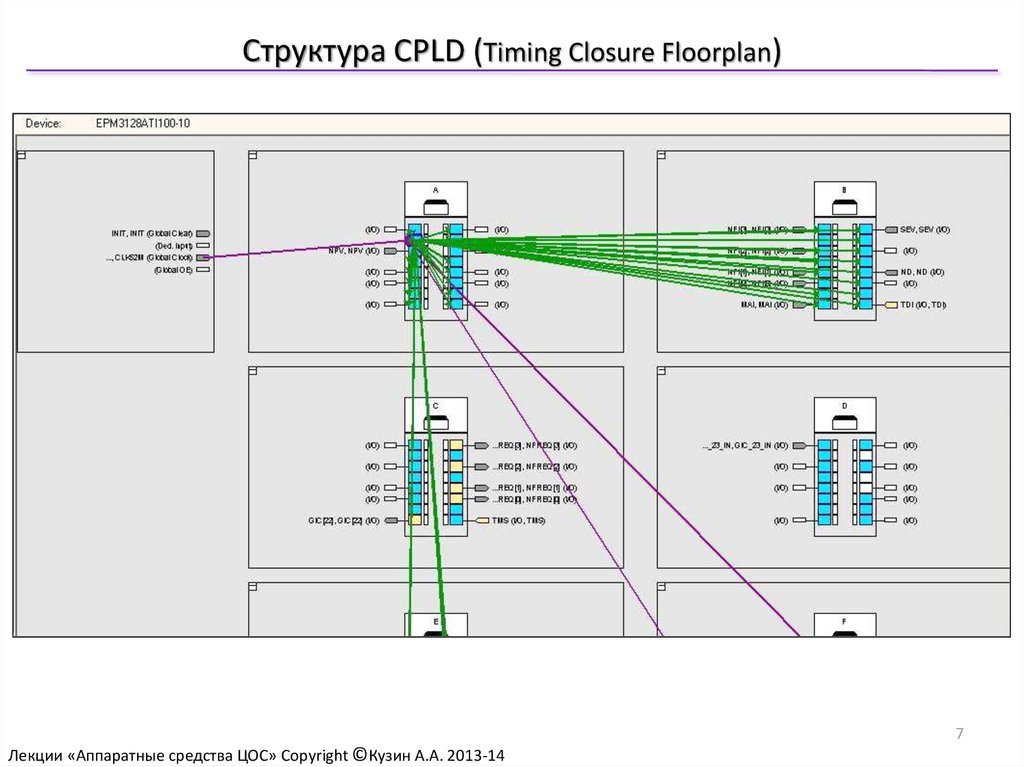

7. Структура CPLD (Timing Closure Floorplan)

7Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

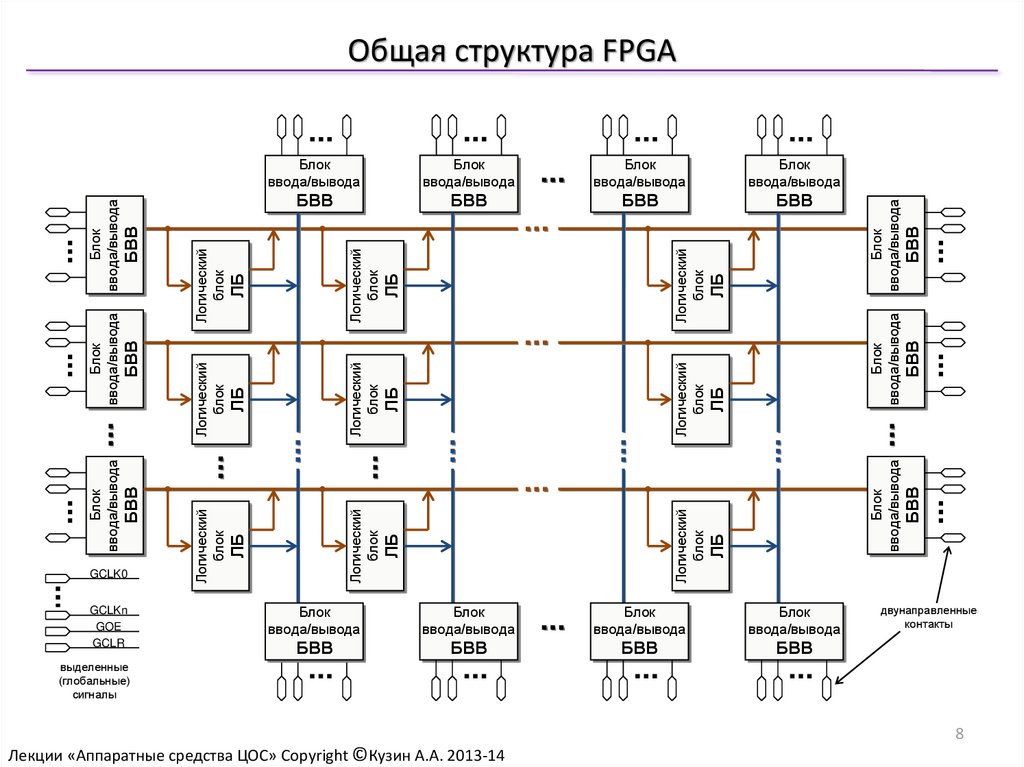

8. Общая структура FPGA

GCLKnGOE

GCLR

Блок

ввода/вывода

Блок

ввода/вывода

Блок

ввода/вывода

БВВ

БВВ

БВВ

БВВ

Логический

блок

ЛБ

Логический

блок

ЛБ

ЛБ

ЛБ

ЛБ

Логический

блок

Логический

блок

БВВ

Блок

ввода/вывода

БВВ

БВВ

БВВ

БВВ

Блок

ввода/вывода

БВВ

Блок

ввода/вывода

БВВ

Блок

ввода/вывода

Блок

ввода/вывода

ЛБ

Блок

ввода/вывода

Логический

блок

Блок

ввода/вывода

Логический

блок

Блок

ввода/вывода

ЛБ

ЛБ

ЛБ

Логический

блок

Логический

блок

GCLK0

Логический

блок

БВВ

БВВ

БВВ

Блок

ввода/вывода

Блок

ввода/вывода

Блок

ввода/вывода

Общая структура FPGA

двунаправленные

контакты

выделенные

(глобальные)

сигналы

8

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

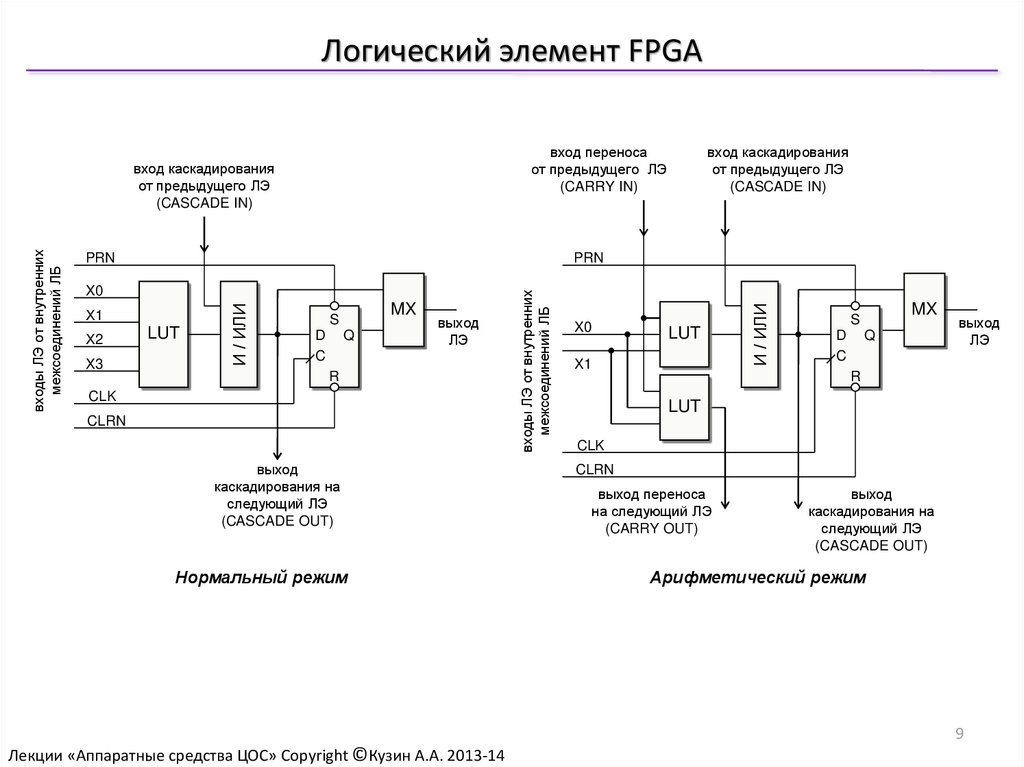

9. Логический элемент FPGA

вход переносаот предыдущего ЛЭ

(CARRY IN)

X1

X3

LUT

MX

S

D

C

Q

выход

ЛЭ

R

CLK

CLRN

выход

каскадирования на

следующий ЛЭ

(CASCADE OUT)

Нормальный режим

X0

LUT

X1

И / ИЛИ

X0

X2

вход каскадирования

от предыдущего ЛЭ

(CASCADE IN)

PRN

входы ЛЭ от внутренних

межсоединений ЛБ

PRN

И / ИЛИ

входы ЛЭ от внутренних

межсоединений ЛБ

вход каскадирования

от предыдущего ЛЭ

(CASCADE IN)

MX

S

D

C

Q

выход

ЛЭ

R

LUT

CLK

CLRN

выход переноса

на следующий ЛЭ

(CARRY OUT)

выход

каскадирования на

следующий ЛЭ

(CASCADE OUT)

Арифметический режим

9

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

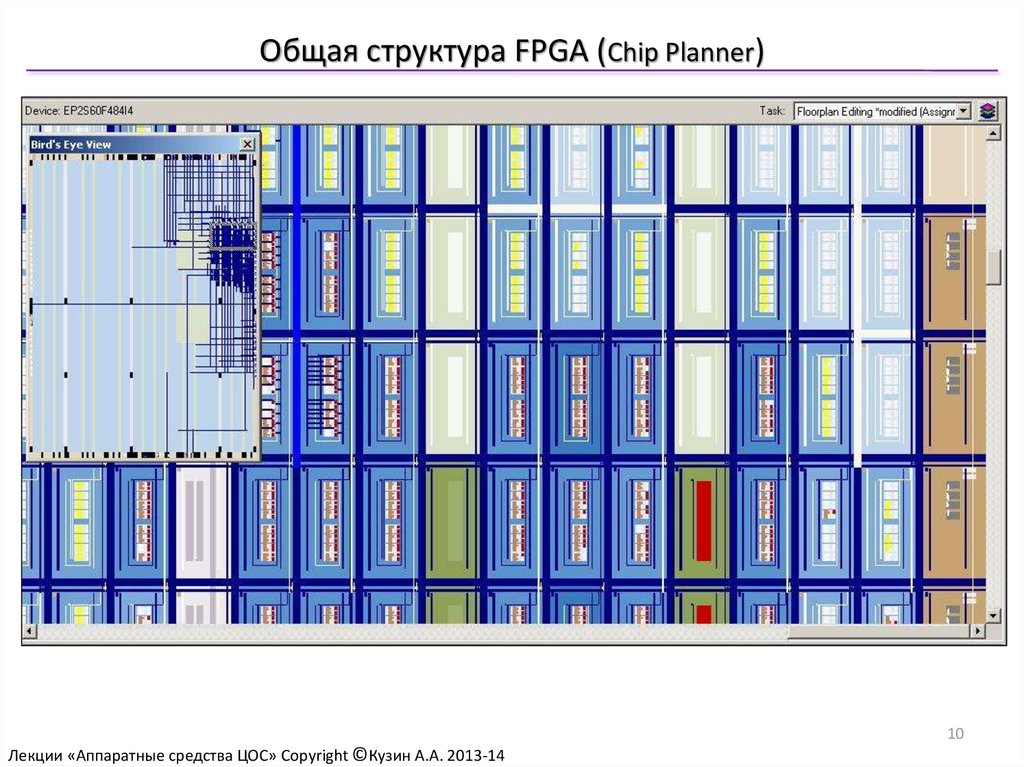

10. Общая структура FPGA (Chip Planner)

10Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

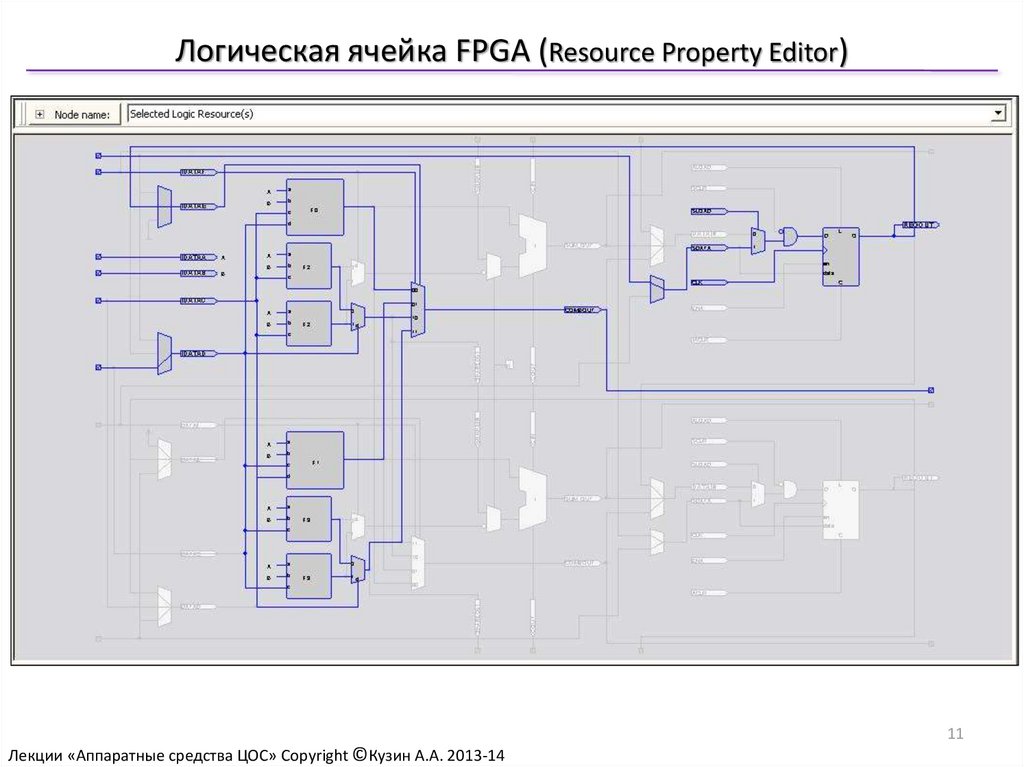

11. Логическая ячейка FPGA (Resource Property Editor)

11Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

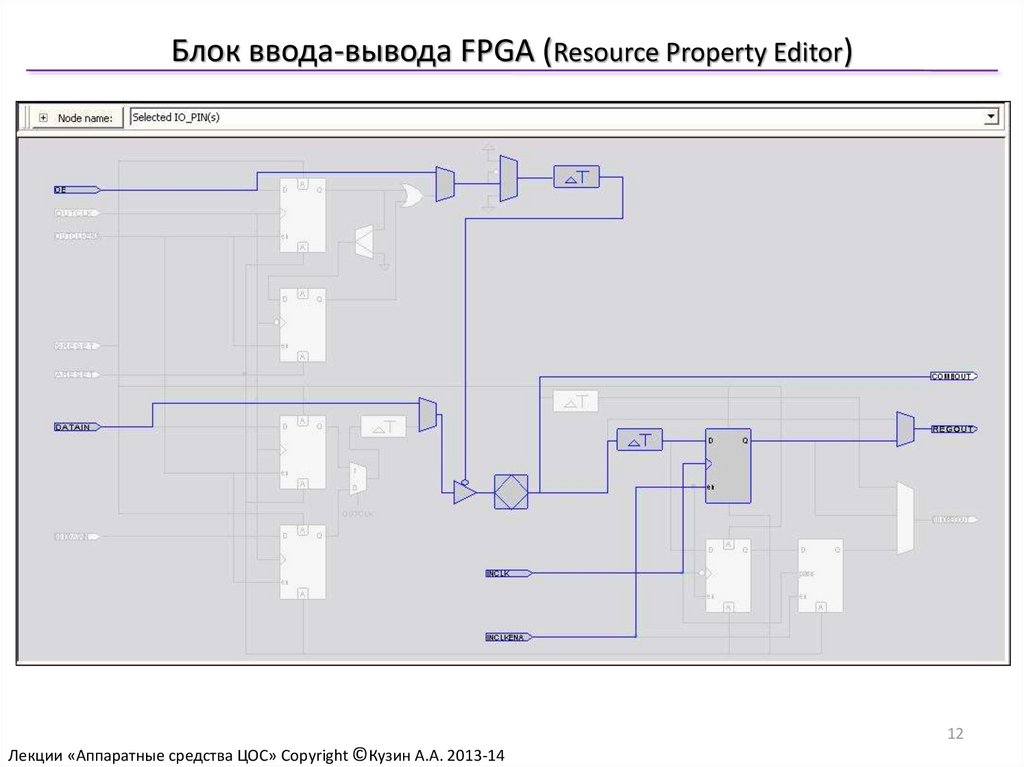

12. Блок ввода-вывода FPGA (Resource Property Editor)

12Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

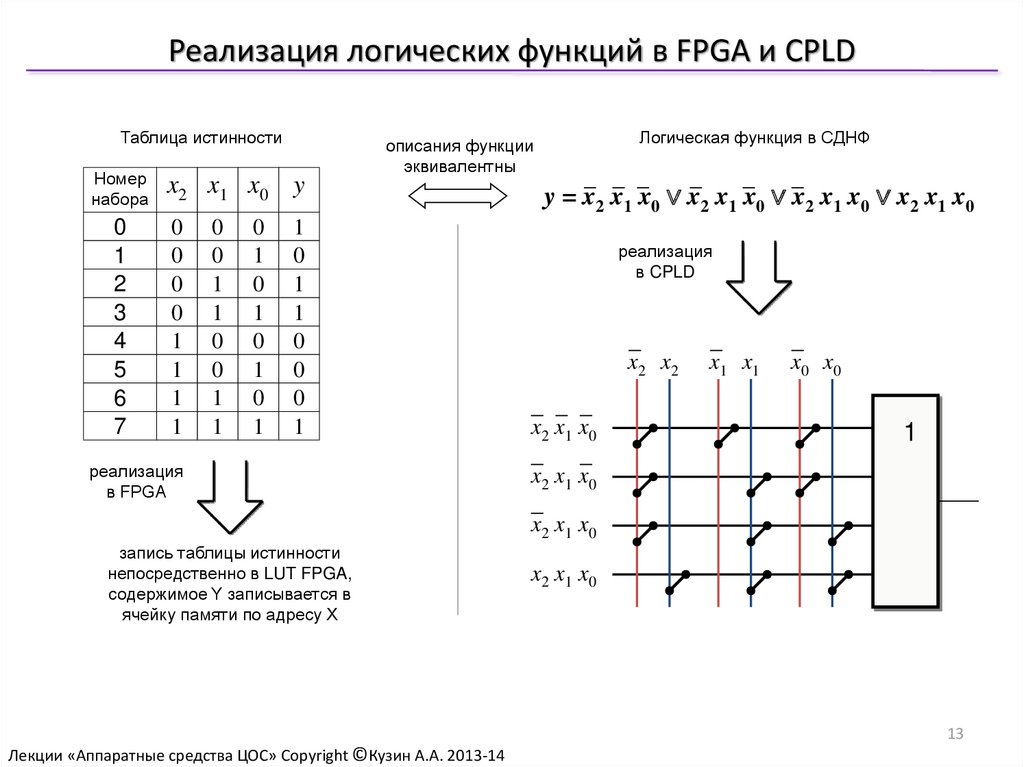

13. Реализация логических функций в FPGA и CPLD

Таблица истинностиНомер

набора

0

1

2

3

4

5

6

7

x2 x1 x0 y

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

Логическая функция в СДНФ

описания функции

эквивалентны

1

0

1

1

0

0

0

1

реализация

в FPGA

y = x2 x1 x0 ∨ x2 x1 x0 ∨ x2 x1 x0 ∨ x2 x1 x0

реализация

в CPLD

x2 x2

x2 x1 x0

x1 x1

x0 x0

1

x2 x1 x0

x2 x1 x0

запись таблицы истинности

непосредственно в LUT FPGA,

содержимое Y записывается в

ячейку памяти по адресу X

x2 x1 x0

13

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

14. Основной элемент памяти CPLD/FPGA – D-триггер

Основные временные соотношения D-триггераC (Clock, CLK) – вход тактовых

(синхронизирующих)

импульсов

1

PRN

D

Q

E

C

CLRN

D (Data)

– информационный

вход (вход данных),

синхронный

E (Enable)

– вход разрешения

тактирования,

синхронный,

H-активный

– вход предустановки,

асинхронный, L-активный

PRN (PReset)

CLRN (CLeaR)

– вход сброса, асинхронный, Lактивный

Q

– выход триггера

Таблица переходов D-триггера

C

X

X

E

0

1

1

X

X

D

X

0

1

X

X

PRN CLRN Q(n)

1

1

Q(n-1)

1

1

0

1

1

1

0

1

1

1

0

0

2

3

4

5

6

7

8

CLK

D

E

PRN

4а

5а

CLRN

Q

tCQ01

tSU

tSQ

tRQ

tH

tSU

tH

tCQ10

безразличные состояния

сигналов

CLK

D

E

Q

tCQ01 –

tCQ10 –

tRQ –

tSQ –

tSU –

tH

–

время задержки переключения выхода из 0 в 1 относительно

переднего фронта сигнала синхронизации CLK

время задержки переключения выхода из 1 в 0 относительно

переднего фронта сигнала синхронизации CLK

время задержки переключения выхода в 0 относительно

асинхронного сигнала сброса CLRN

время задержки переключения выхода в 1 относительно

асинхронного сигнала установки PRN

время предустановки (SetUp) управляющего сигнала

относительно фронта синхронизации CLK

время удержания (Hold) управляющего сигнала относительно

фронта синхронизации CLK

14

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

15.

15Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

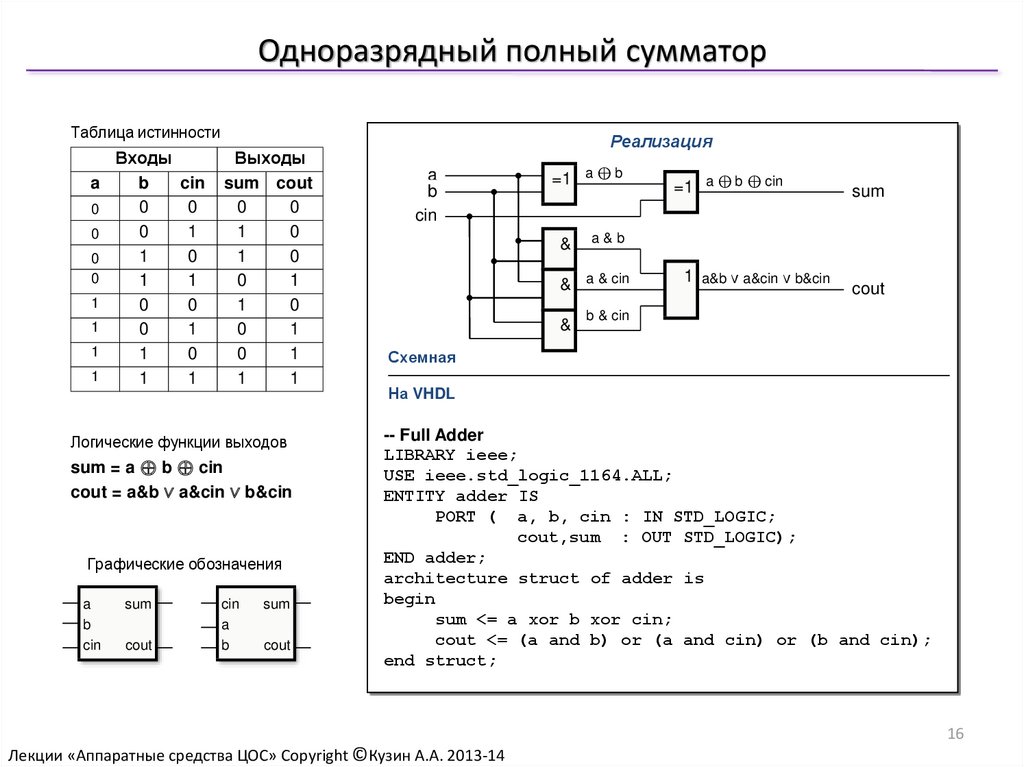

16. Одноразрядный полный сумматор

Таблица истинностиa

0

0

0

0

1

1

1

1

Входы

b

0

0

1

1

0

0

1

1

cin

0

1

0

1

0

1

0

1

Выходы

sum cout

0

0

1

0

1

0

0

1

1

0

0

1

0

1

1

1

Логические функции выходов

sum = a ⊕ b ⊕ cin

cout = a&b ∨ a&cin ∨ b&cin

Графические обозначения

a

b

cin

sum

cout

cin

a

b

sum

cout

Реализация

a

b

cin

=1 a ⊕ b

&

sum

a&b

& a & cin

&

=1 a ⊕ b ⊕ cin

1 a&b ∨ a&cin ∨ b&cin

cout

b & cin

Схемная

На VHDL

-- Full Adder

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY adder IS

PORT ( a, b, cin : IN STD_LOGIC;

cout,sum : OUT STD_LOGIC);

END adder;

architecture struct of adder is

begin

sum <= a xor b xor cin;

cout <= (a and b) or (a and cin) or (b and cin);

end struct;

16

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

17. Многоразрядный параллельный сумматор

Схемная и VHDL реализации многоразрядногопараллельного сумматора с последовательным

переносом

Лог. 0

A[0]

B[0]

A[1]

B[1]

A[2]

B[2]

A[N-1]

B[N-1]

cin

sum

sum[0]

a

b

cout

cin

sum

sum[1]

a

b

cout

cin

sum

sum[2]

a

b

cout

cin

sum

sum[N-1]

cout

cout

a

b

Логические функции выходов

sum[i] = a[i] ⊕ b[i] ⊕ c[i]

c[i+1] = a[i]&b[i] ∨ a[i]&c[i] ∨ b[i]&c[i],

c[0] = 0, cout = c[i+1]

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

-- 32-bit Full Adder

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

entity add_32 is

generic(N: natural:=32);

port( A, B : IN STD_LOGIC_VECTOR(N-1 DOWNTO 0);

sum : OUT STD_LOGIC_VECTOR(N-1 DOWNTO 0);

cout : OUT STD_LOGIC);

end add_32;

architecture struct of add_32 is

component

adder

PORT ( a, b, cin : IN STD_LOGIC;

cout, sum : OUT STD_LOGIC);

end component;

component

add

PORT ( a, b : IN STD_LOGIC;

cout, sum : OUT STD_LOGIC);

end component;

signal cc : STD_LOGIC_VECTOR(0 to N-1);

begin

adder32: for i in 0 to N-1 generate

first_bit:

if(i=0) generate

fistr_cell: add

port map( A(i), B(i), cc(i), sum(i));

end generate first_bit;

middle_bit:

if(i>0) generate

middle_cell: adder

port map(A(i),B(i),cc(i-1),cc(i), sum(i));

end generate middle_bit;

end generate adder32;

cout <= cc(N-1);

end struct;

17

18. Многоразрядный последовательный сумматор

Последовательный сумматорИсточник данных в

последовательном коде

Пример сложения

A = 0 01011(+11)

Возникающий при сложении перенос

учитывается в дополнительном такте

(расширение знакового разряда), все

последующие переносы

отбрасываются

=1

A[N-1 ..0]

B = 1 11001 (–7)

A+B = 1 0 00100 (+4)

Комбинационный сумматор

Регистр сдвига вправо

Регистр сдвига вправо

A[i]

&

B[i]

b[i]

&

Bit0

&

c[i]

&

PRN

D

Q

S[i]

C

CLRN

a[i]

Load

B[N-1 ..0]

=1 sum[i]

1

c[i+1]

PRN

D

Q

C

CLRN

CLK

CLK

Load

Серым цветом выделена

загрузка регистров сдвига

A

001011

B

111001

Расширение знакового разряда –

дополнительный такт

Знаковый

разряд

Bit0

a[i]

a[0]

a[1]

a[2]

a[3]

a[4]

a[4]

b[i]

b[0]

b[1]

b[2]

b[3]

b[4]

b[4]

c[i]

с[0] = 0

с[1]

с[2]

с[3]

с[4]

с[5]

S[0]

S[1]

S[2]

S[3]

S[4]

S[i]

Знаковый

разряд суммы

S[5]

18

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

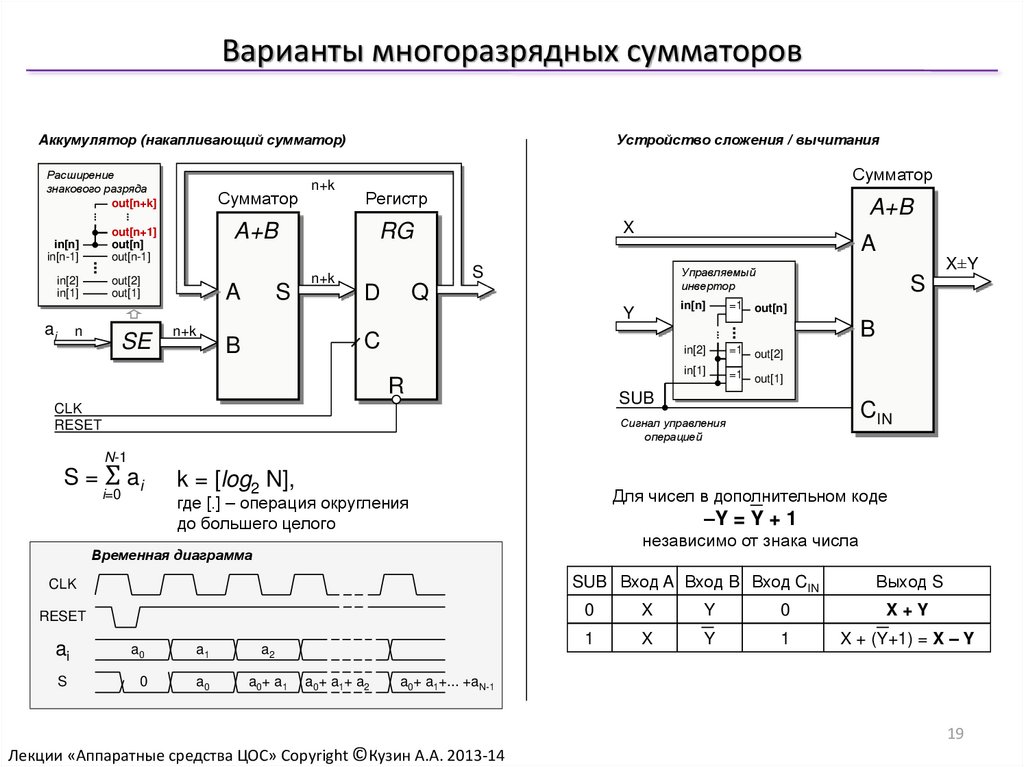

19. Варианты многоразрядных сумматоров

Аккумулятор (накапливающий сумматор)Расширение

знакового разряда

out[n+k]

Сумматор

in[2]

in[1]

Сумматор

Регистр

out[2]

out[1]

A

S

A+B

X

RG

A+B

out[n+1]

out[n]

out[n-1]

in[n]

in[n-1]

n+k

Устройство сложения / вычитания

n+k

A

S

Q

D

Y

ai

n

SE

n+k

R

S

in[n]

=1

in[2]

=1

out[2]

in[1]

=1

out[1]

out[n]

B

C

B

X±Y

Управляемый

инвертор

SUB

CLK

RESET

CIN

Сигнал управления

операцией

N-1

S = Σ ai

i=0

k = [log2 N],

Для чисел в дополнительном коде

где [.] – операция округления

до большего целого

–Y = Y + 1

независимо от знака числа

Временная диаграмма

SUB Вход A Вход B Вход CIN

CLK

RESET

ai

a0

a1

a2

S

0

a0

a0+ a1

a0+ a1+ a2

Выход S

0

X

Y

0

X+Y

1

X

Y

1

X + (Y+1) = X – Y

a0+ a1+... +aN-1

19

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

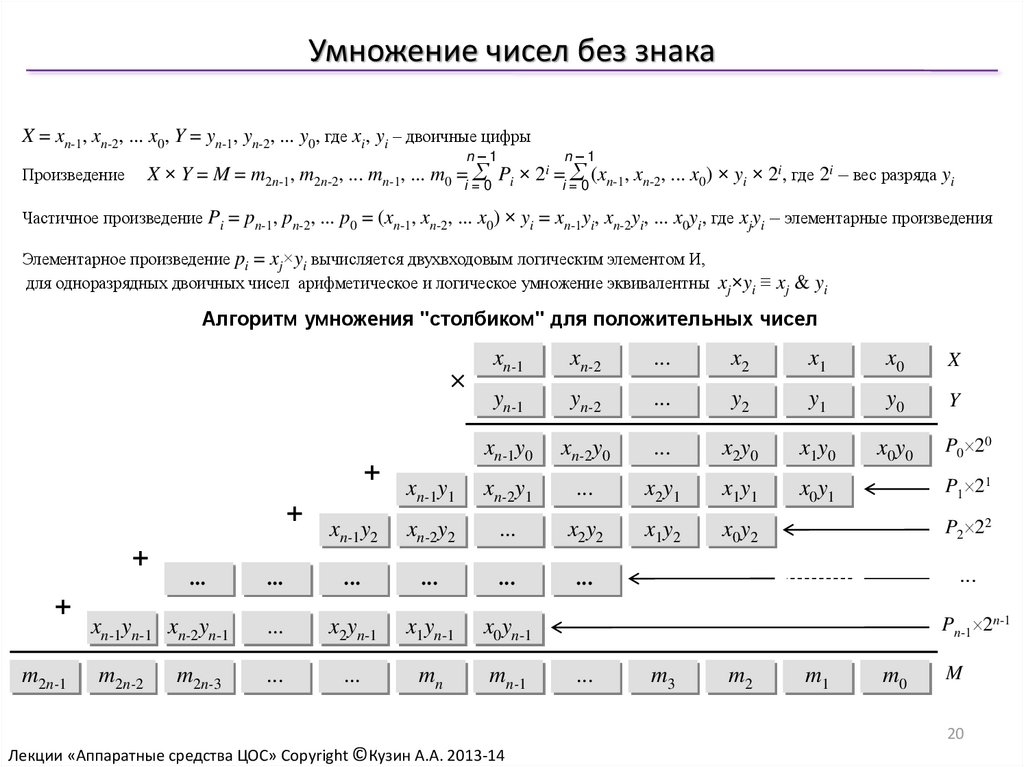

20. Умножение чисел без знака

X = xn-1, xn-2, ... x0, Y = yn-1, yn-2, ... y0, где xi, yi – двоичные цифрыn–1

n–1

X × Y = M = m2n-1, m2n-2, ... mn-1, ... m0 =i =Σ0 Pi × 2i =i =Σ0 (xn-1, xn-2, ... x0) × yi × 2i, где 2i – вес разряда yi

Произведение

Частичное произведение Pi = pn-1, pn-2, ... p0 = (xn-1, xn-2, ... x0) × yi = xn-1yi, xn-2yi, ... x0yi, где xjyi – элементарные произведения

Элементарное произведение pi = xj×yi вычисляется двухвходовым логическим элементом И,

для одноразрядных двоичных чисел арифметическое и логическое умножение эквивалентны xj×yi ≡ xj & yi

Алгоритм умножения "столбиком" для положительных чисел

xn-1

xn-2

...

x2

x1

x0

X

yn-1

yn-2

...

y2

y1

y0

Y

xn-1y0

xn-2y0

...

x2y0

x1y0

x0y0

xn-1y1

xn-2y1

...

x2y1

x1y1

x0y1

xn-1y2

xn-2y2

...

x2y2

x1y2

x0y2

...

...

...

...

...

...

x2yn-1

x1yn-1

x0yn-1

...

...

mn

mn-1

×

+

+

+

+

m2n-1

...

xn-1yn-1 xn-2yn-1

m2n-2

m2n-3

P0 20

P1 21

P2 22

...

Pn-1 2n-1

...

m3

m2

m1

m0

M

20

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

21. Структура умножителя для чисел без знака

coutB

cin

A

x4y0

x4y1

0

x3y0

0

x2y0

0

x3y1

x2y1

x1y1

x0y2

x1y0

0

x0y0

x0y1

S

x4y2

полный сумматор

x4y3

x3y4

x3y2

x2y2

x1y2

x0y3

x3y3

x2y3

x1y3

x2y4

x1y4

x0y4

0

x4y4

m9 m8

m7

m6

m5

m4

m3

m2

m1

m0

21

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

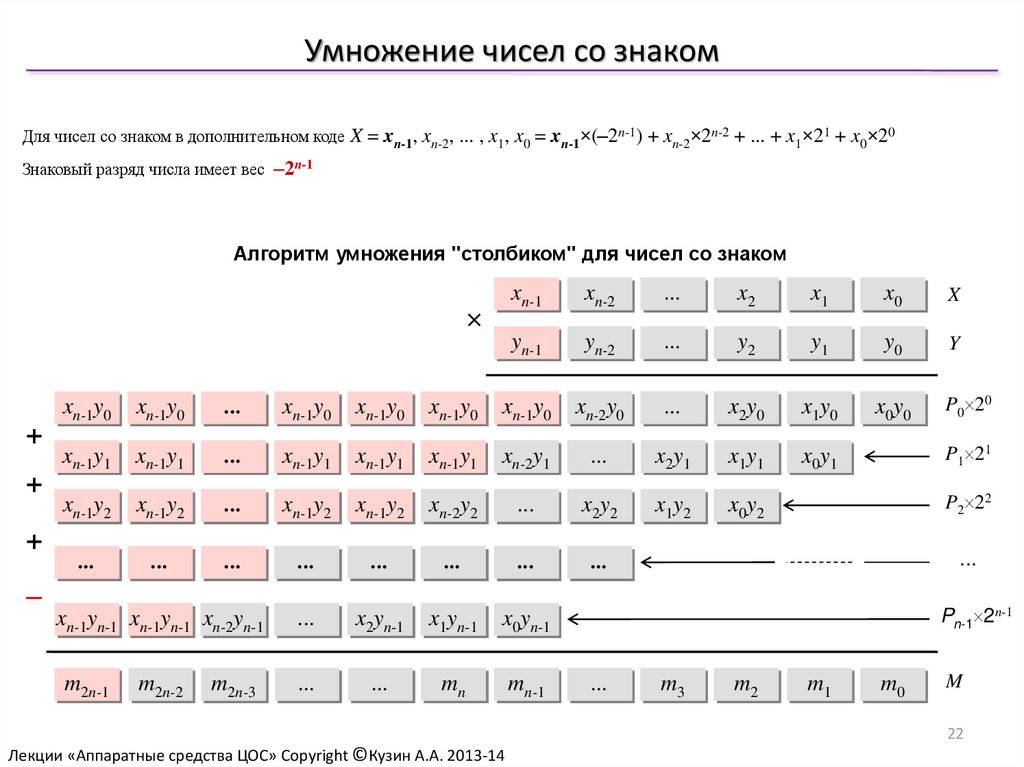

22. Умножение чисел со знаком

Для чисел со знаком в дополнительном коде X = xn-1, xn-2, ... , x1, x0 = xn-1×(–2n-1) + xn-2×2n-2 + ... + x1×21 + x0×20Знаковый разряд числа имеет вес –2n-1

Алгоритм умножения "столбиком" для чисел со знаком

×

+

+

+

–

xn-1

xn-2

...

x2

x1

x0

X

yn-1

yn-2

...

y2

y1

y0

Y

x0y0

xn-1y0

xn-1y0

...

xn-1y0

xn-1y0

xn-1y0

xn-1y0

xn-2y0

...

x2y0

x1y0

xn-1y1

xn-1y1

...

xn-1y1

xn-1y1

xn-1y1

xn-2y1

...

x2y1

x1y1

x0y1

xn-1y2

xn-1y2

...

xn-1y2

xn-1y2

xn-2y2

...

x2y2

x1y2

x0y2

...

...

...

...

...

...

...

...

...

x2yn-1

x1yn-1

x0yn-1

...

...

mn

mn-1

xn-1yn-1 xn-1yn-1 xn-2yn-1

m2n-1

m2n-2

m2n-3

P0 20

P1 21

P2 22

...

Pn-1 2n-1

...

m3

m2

m1

m0

M

22

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

23. Структура умножителя для чисел со знаком

Bcin

x3y0

0

+

cout

0

0

0

A

+

+

+

+

+

+

–

–

––

––

––

m7

m6

m5

+

x3y1

x2y0

0

+

x2y1

0

+

x0y0

x1y0

x1y1

0

+

x0y1

S

A + B + Cin

cout

B

cin

–

A

S

x3y3

–

x3y2

x2y3

+

x2y2

–

x1y3

––

0

+

–

x1y2

+

x0y2

x0y3

A – B + Cin

cout

B

cin

––

A

S

m4

m3

m2

m1

m0

A – B – Cin

23

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

24. Примеры умножения чисел со знаком

a = –3 = 11012a = –3 = 11012

b = –7 = 10012

b = +7 = 01112

1 1 0 1

1 0 0 1

+

+

–

1 1 0 1

0 1 1 1

1 1 1 1 1 1 0 1

P0

0 0 0 0 0 0 0

P1

0 0 0 0 0 0

P2

1 1 1 0 1

P3

0 0 0 1 0 1 0 1

M

M = 000101012 = +21

+

+

–

1 1 1 1 1 1 0 1

P0

1 1 1 1 1 0 1

P1

1 1 1 1 0 1

P2

0 0 0 0 0

P3

1 1 1 0 1 0 1 1

M

M = 111010112 = –21

24

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

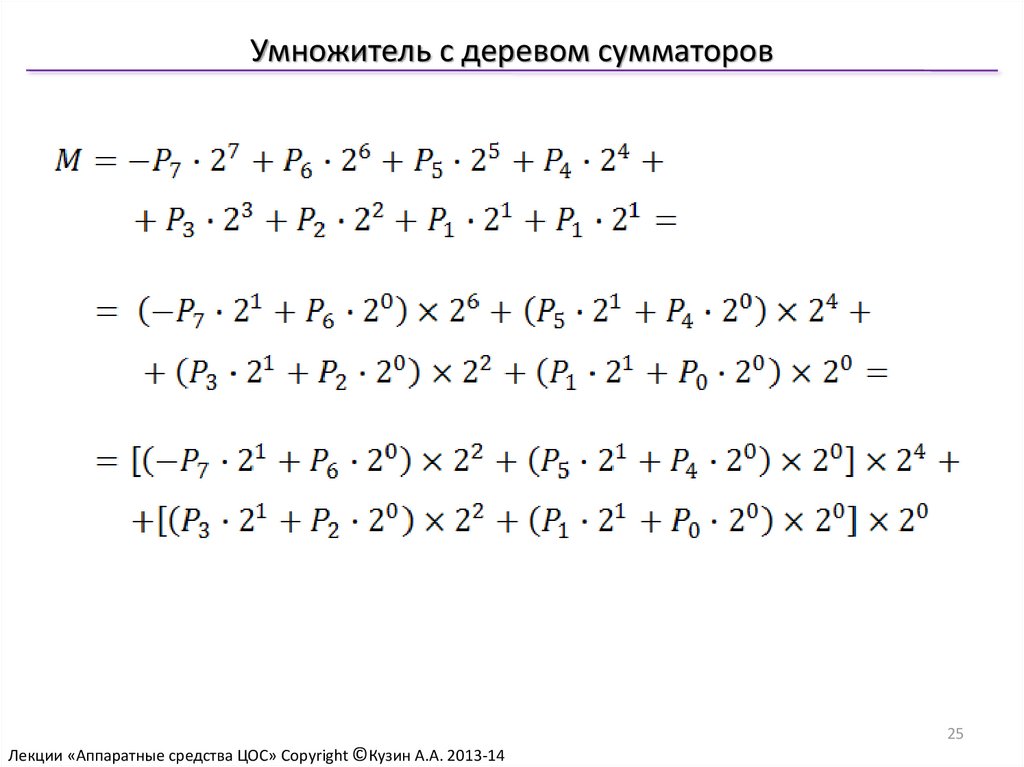

25. Умножитель с деревом сумматоров

25Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

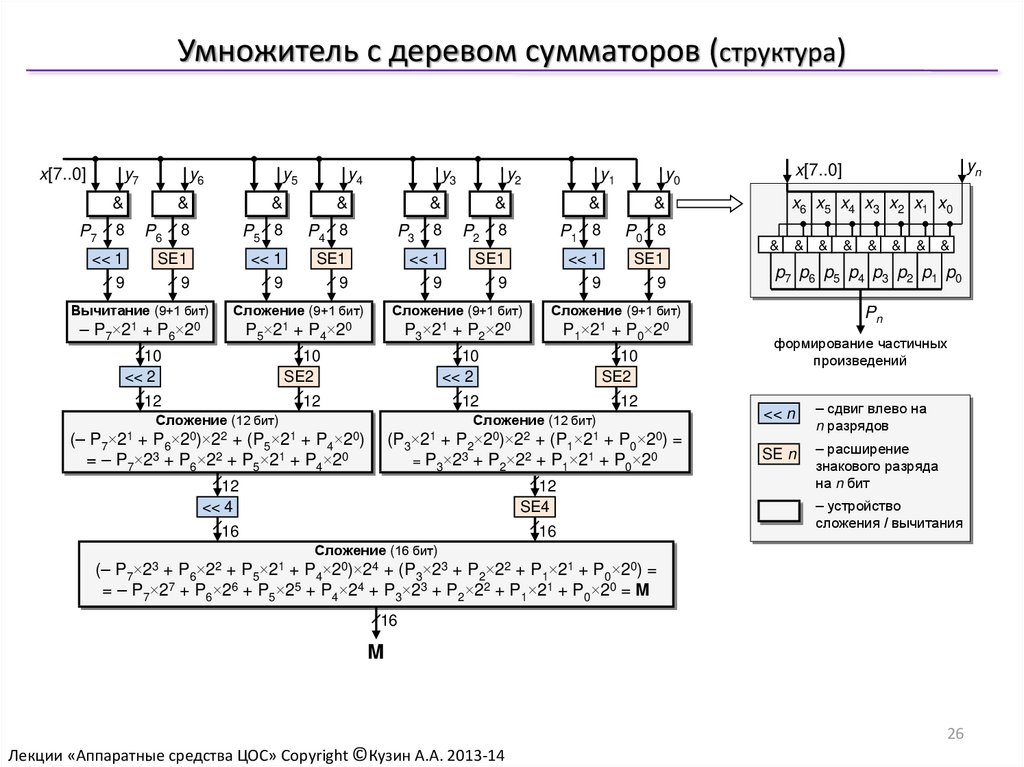

26. Умножитель с деревом сумматоров (структура)

x[7..0]y7

y6

&

y4

&

&

&

8

P5 8

P4 8

<< 1

SE1

<< 1

SE1

9

9

9

9

P7

8

P6

Вычитание (9+1 бит)

–

y5

P7×21

+

y3

&

P5×21

+

&

8

P1 8

P0 8

<< 1

SE1

<< 1

SE1

9

9

9

9

8

P2

P3×21

+

x6 x5 x4 x3 x2 x1 x0

&

&

P1×21 + P0×20

10

<< 2

10

SE2

10

<< 2

10

SE2

12

12

12

12

&

&

&

&

&

Pn

формирование частичных

произведений

Сложение (12 бит)

Сложение (12 бит)

<< n

(– P7×21 + P6×20)×22 + (P5×21 + P4×20)

= – P7×23 + P6×22 + P5×21 + P4×20

(P3×21 + P2×20)×22 + (P1×21 + P0×20) =

= P3×23 + P2×22 + P1×21 + P0×20

– сдвиг влево на

n разрядов

SE n

12

<< 4

12

SE4

– расширение

знакового разряда

на n бит

16

16

&

p 7 p6 p5 p4 p3 p2 p1 p0

Сложение (9+1 бит)

P2×20

yn

x[7..0]

y0

&

Сложение (9+1 бит)

P4×20

y1

&

P3

Сложение (9+1 бит)

P6×20

y2

– устройство

сложения / вычитания

Сложение (16 бит)

(– P7×23 + P6×22 + P5×21 + P4×20)×24 + (P3×23 + P2×22 + P1×21 + P0×20) =

= – P7×27 + P6×26 + P5×25 + P4×24 + P3×23 + P2×22 + P1×21 + P0×20 = M

16

M

26

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

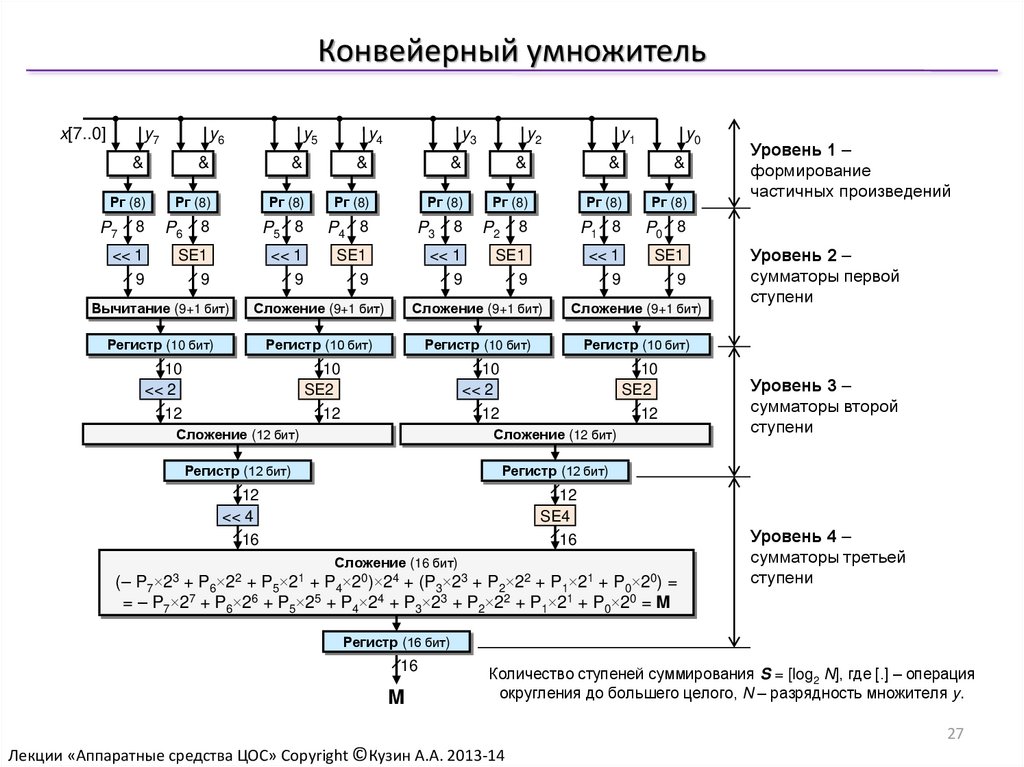

27. Конвейерный умножитель

x[7..0]y7

y6

y5

y4

y3

y2

y1

y0

&

&

&

&

&

&

&

&

Рг (8)

Рг (8)

Рг (8)

Рг (8)

Рг (8)

Рг (8)

Рг (8)

Рг (8)

8

P5 8

P4 8

8

P1 8

P0 8

<< 1

SE1

<< 1

SE1

<< 1

SE1

<< 1

SE1

9

9

9

9

9

9

9

9

P7

8

P6

P3

8

P2

Вычитание (9+1 бит)

Сложение (9+1 бит)

Сложение (9+1 бит)

Сложение (9+1 бит)

Регистр (10 бит)

Регистр (10 бит)

Регистр (10 бит)

Регистр (10 бит)

10

<< 2

10

SE2

10

<< 2

10

SE2

12

12

12

12

Сложение (12 бит)

Сложение (12 бит)

Регистр (12 бит)

Регистр (12 бит)

12

<< 4

16

12

SE4

16

Сложение (16 бит)

P7×23

P6×22

P5×21

(–

+

+

+ P4×20)×24 + (P3×23 + P2×22 + P1×21 + P0×20) =

7

6

= – P7×2 + P6×2 + P5×25 + P4×24 + P3×23 + P2×22 + P1×21 + P0×20 = M

Уровень 1 –

формирование

частичных произведений

Уровень 2 –

сумматоры первой

ступени

Уровень 3 –

сумматоры второй

ступени

Уровень 4 –

сумматоры третьей

ступени

Регистр (16 бит)

16

M

Количество ступеней суммирования S = [log2 N], где [.] – операция

округления до большего целого, N – разрядность множителя y.

27

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

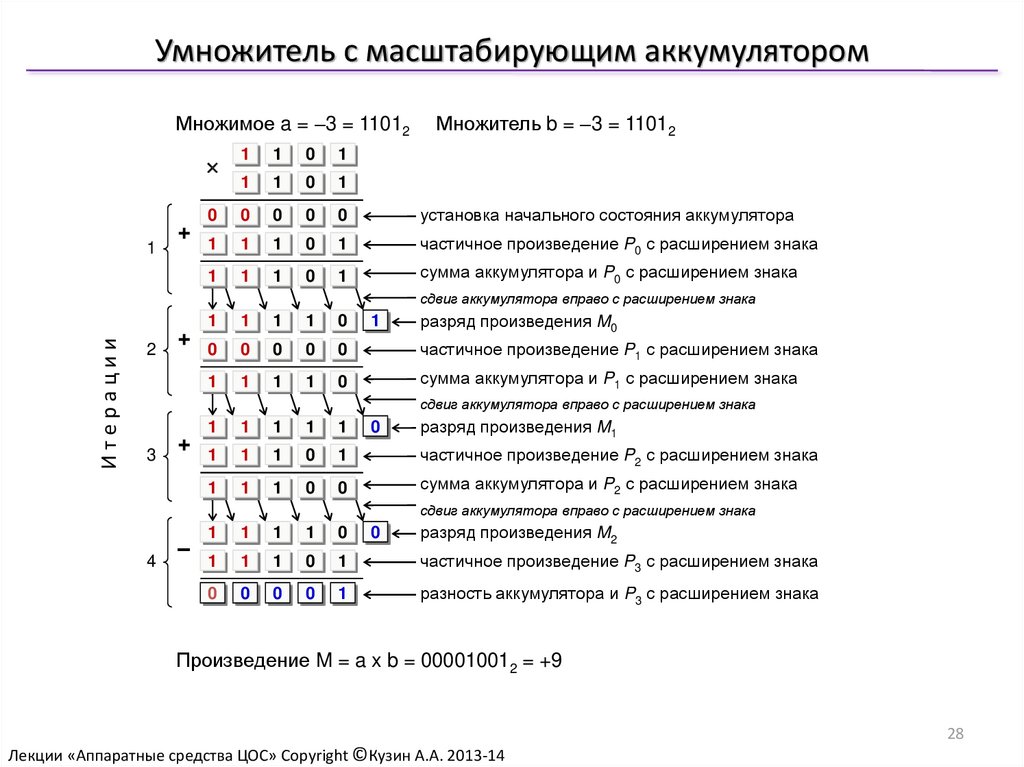

28. Умножитель с масштабирующим аккумулятором

Множимое a = –3 = 110121

+

Множитель b = –3 = 11012

1

1

0

1

1

1

0

1

0

0

0

0

0

установка начального состояния аккумулятора

1

1

1

0

1

частичное произведение P0 с расширением знака

1

1

1

0

1

сумма аккумулятора и P0 с расширением знака

Итерации

сдвиг аккумулятора вправо с расширением знака

2

+

1

разряд произведения M0

1

1

1

1

0

0

0

0

0

0

частичное произведение P1 с расширением знака

1

1

1

1

0

сумма аккумулятора и P1 с расширением знака

сдвиг аккумулятора вправо с расширением знака

3

+

0

разряд произведения M1

1

1

1

1

1

1

1

1

0

1

частичное произведение P2 с расширением знака

1

1

1

0

0

сумма аккумулятора и P2 с расширением знака

сдвиг аккумулятора вправо с расширением знака

4

–

0

разряд произведения M2

1

1

1

1

0

1

1

1

0

1

частичное произведение P3 с расширением знака

0

0

0

0

1

разность аккумулятора и P3 с расширением знака

Произведение M = a x b = 000010012 = +9

28

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

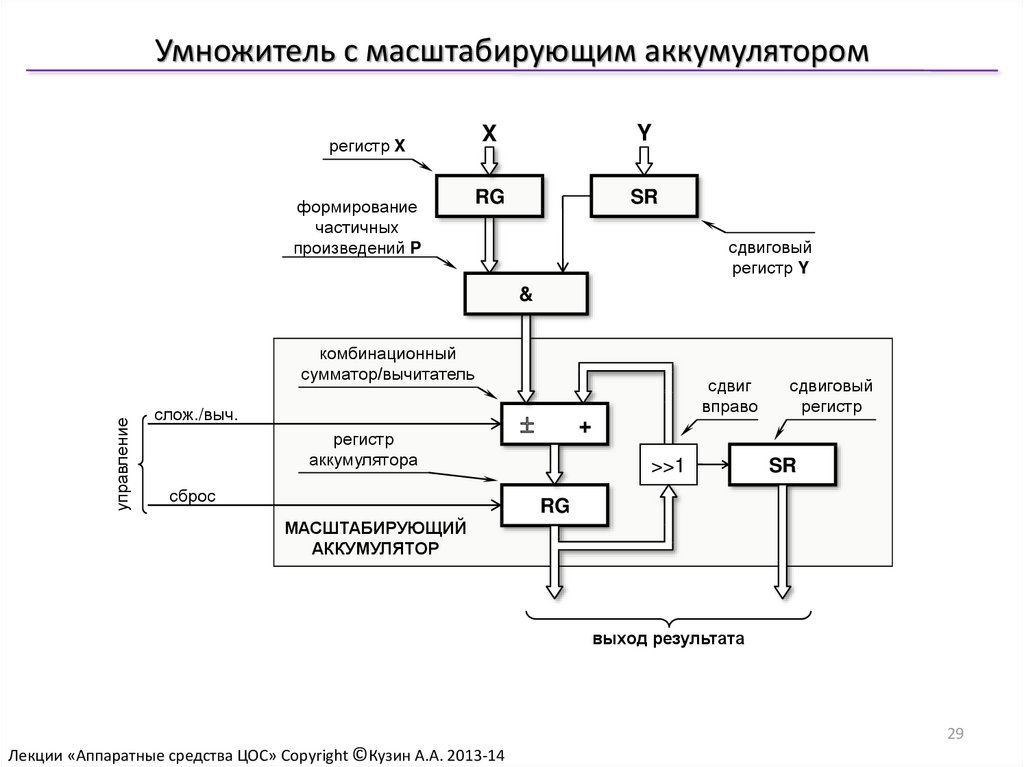

29. Умножитель с масштабирующим аккумулятором

регистр Xформирование

частичных

произведений P

X

Y

RG

SR

сдвиговый

регистр Y

&

управление

комбинационный

сумматор/вычитатель

слож./выч.

регистр

аккумулятора

сброс

сдвиг

вправо

сдвиговый

регистр

+

>>1

SR

RG

МАСШТАБИРУЮЩИЙ

АККУМУЛЯТОР

выход результата

29

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

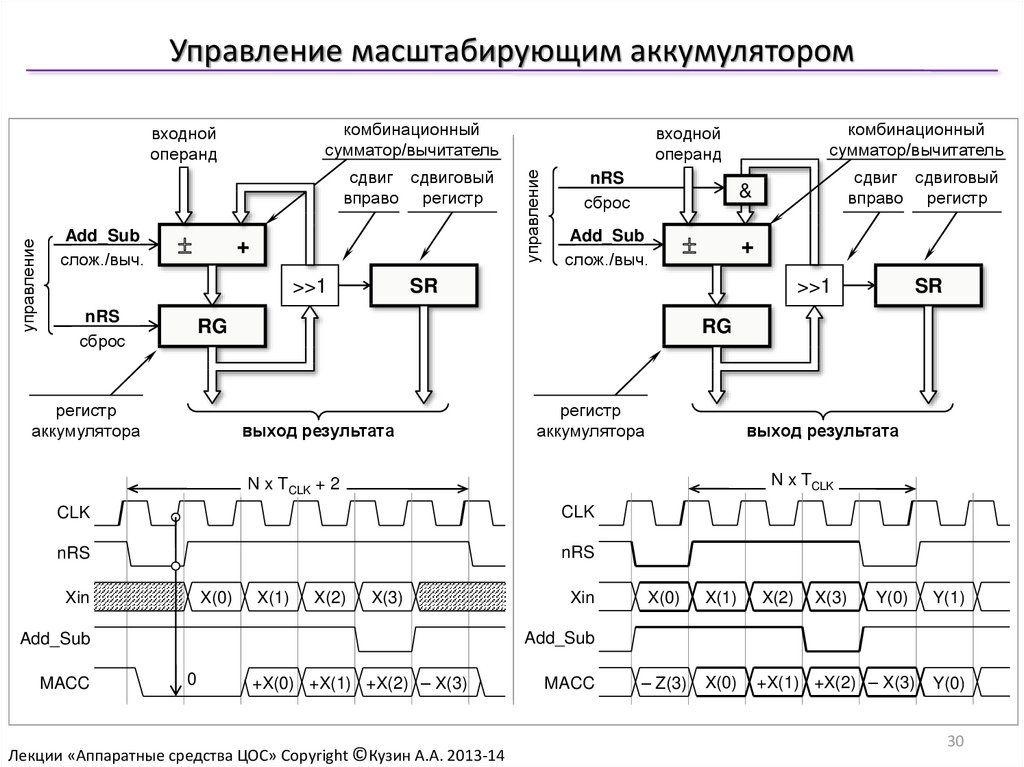

30. Управление масштабирующим аккумулятором

комбинационныйсумматор/вычитатель

управление

сдвиг сдвиговый

вправо регистр

Add_Sub

слож./выч.

+

>>1

nRS

сброс

nRS

сброс

Add_Sub

слож./выч.

+

SR

>>1

регистр

аккумулятора

выход результата

N x TCLK

N x TCLK + 2

CLK

CLK

nRS

nRS

X(0)

X(1)

X(2)

X(3)

Xin

X(0)

X(1)

X(2)

X(3)

Y(0)

– Z(3)

X(0)

+X(1) +X(2) – X(3)

Y(1)

Add_Sub

Add_Sub

MACC

SR

RG

выход результата

Xin

сдвиг сдвиговый

вправо регистр

&

RG

регистр

аккумулятора

комбинационный

сумматор/вычитатель

входной

операнд

управление

входной

операнд

0

+X(0) +X(1) +X(2) – X(3)

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

MACC

Y(0)

30

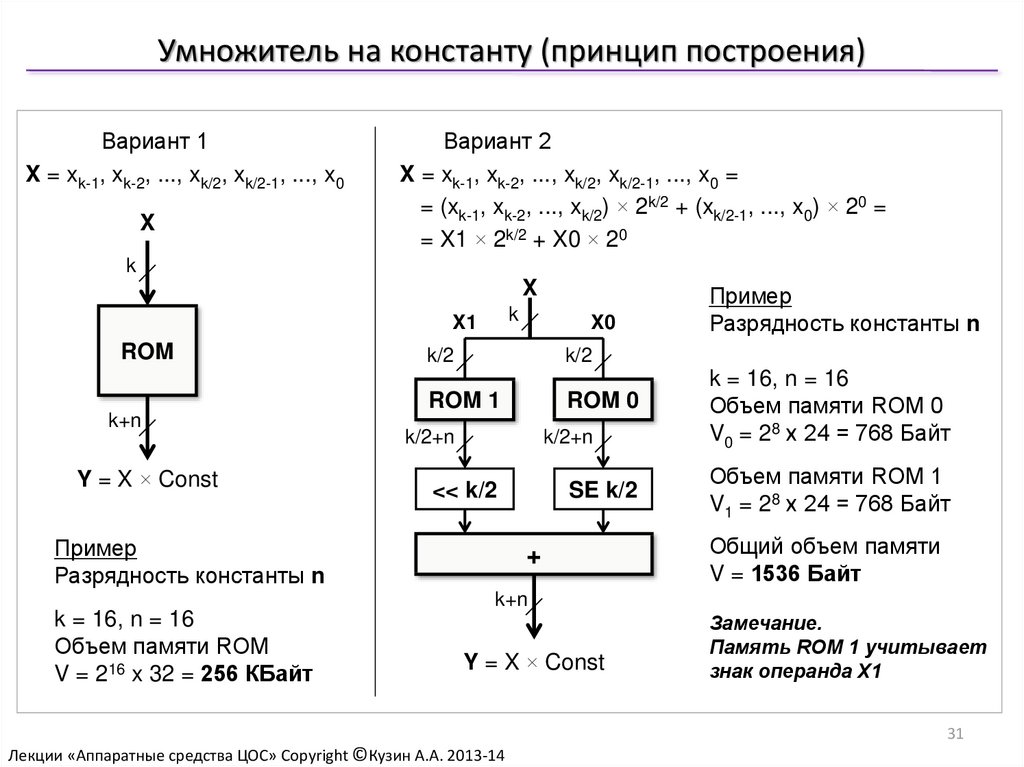

31. Умножитель на константу (принцип построения)

Вариант 1X = xk-1, xk-2, ..., xk/2, xk/2-1, ..., x0

X

Вариант 2

X = xk-1, xk-2, ..., xk/2, xk/2-1, ..., x0 =

= (xk-1, xk-2, ..., xk/2) × 2k/2 + (xk/2-1, ..., x0) × 20 =

= X1 × 2k/2 + X0 × 20

k

X

k

X1

ROM

k+n

Y = X × Const

k/2

k/2

ROM 1

ROM 0

k/2+n

k/2+n

<< k/2

Пример

Разрядность константы n

k = 16, n = 16

Объем памяти ROM

V = 216 x 32 = 256 КБайт

X0

Пример

Разрядность константы n

SE k/2

+

k = 16, n = 16

Объем памяти ROM 0

V0 = 28 x 24 = 768 Байт

Объем памяти ROM 1

V1 = 28 x 24 = 768 Байт

Общий объем памяти

V = 1536 Байт

k+n

Y = X × Const

Замечание.

Память ROM 1 учитывает

знак операнда X1

31

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

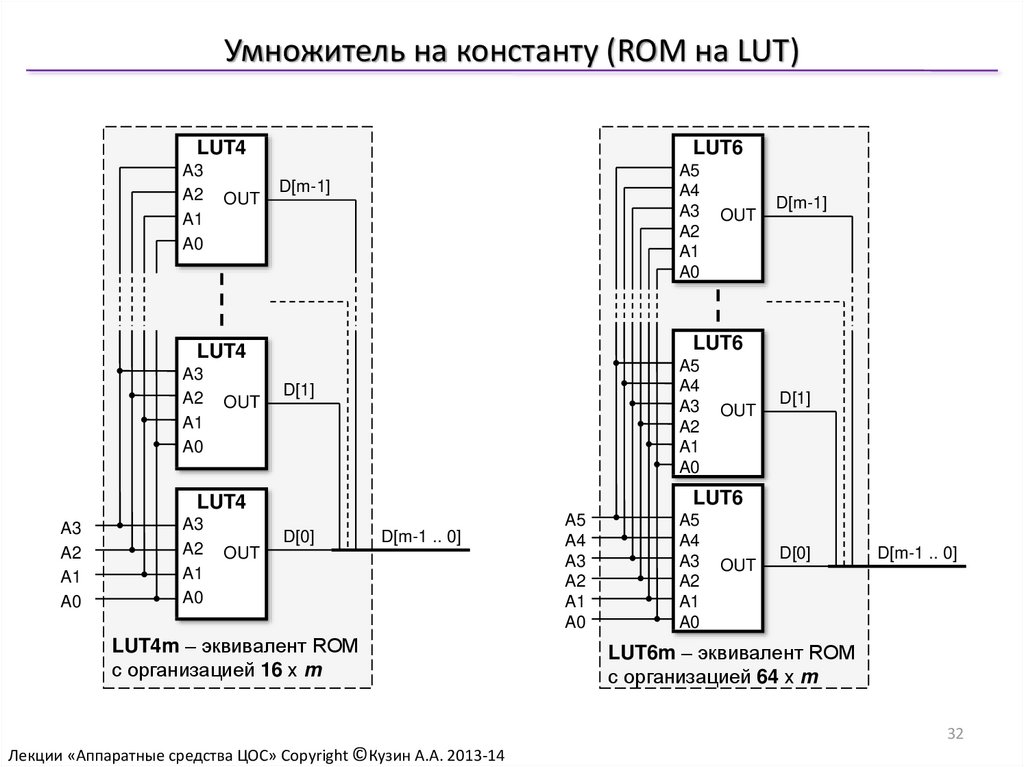

32. Умножитель на константу (ROM на LUT)

LUT4A3

A2

A1

A0

OUT

LUT6

A5

A4

A3

A2

A1

A0

D[m-1]

OUT

A5

A4

A3

A2

A1

A0

D[1]

A3

A2

A1

A0

OUT

D[1]

LUT6

LUT4

A3

A2

A1

A0

D[m-1]

LUT6

LUT4

A3

A2

A1

A0

OUT

D[0]

D[m-1 .. 0]

OUT

LUT4m – эквивалент ROM

с организацией 16 х m

A5

A4

A3

A2

A1

A0

A5

A4

A3

A2

A1

A0

OUT

D[0]

D[m-1 .. 0]

LUT6m – эквивалент ROM

с организацией 64 х m

32

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

33. Умножитель на константу (структура)

X3X2

X1

X0

x15 x14 x13 x12

x11 x10 x9 x8

x7 x6 x5 x4

x3 x2 x1 x0

A3 A2 A1 A0

A3 A2 A1 A0

A3 A2 A1 A0

A3 A2 A1 A0

LUT B

LUT A

LUT A

LUT A

k+4

k+4

<< 4

k+4

SE 4

k+8

k+4

<< 4

k+8

SE 4

k+8

k+8

+

+

k+8

k+8

<< 8

SE 8

k+16

k+16

+

k+16

Y = X × Const

Для операндов произвольной

разрядности

X = xn-1, xn-2, ... , x1, x0 и

Y = yk-1, yk-2, ... , y1, y0, где

Y – константа, потребуется

[n/4] таблиц LUT с организацией

16 × (k+4) и [log2 (n/4)] ступеней

суммирования.

[.] – операция округления до большего

целого.

Пример

Разрядность операнда X равна 16

(n=16).

Операнд разбивается на 4 группы

по 4 разряда X0, X1, X2, X3.

Группы X0, X1 и X2 – числа без

знака, группа X3 – число со

знаком (учитывается вес

знакового разряда x15).

Разряды каждой группы являются

адресами таблиц LUT.

Для групп X0, X1 и X2

используются таблицы LUT A, для

группы X3 – таблица LUT B.

33

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

34. Умножитель на константу (содержимое LUT)

ТАБЛИЦА LUT A(адрес – число без знака)

ТАБЛИЦА LUT B

(адрес – число со знаком)

АДРЕС

СОДЕРЖИМОЕ

ЯЧЕЙКИ

код значение

0000

+0

+0 × Const

0001

+1

+1 × Const

0010

+2

+2 × Const

0011

+3

+3 × Const

0100

+4

+4 × Const

0101

+5

+5 × Const

0110

+6

+6 × Const

0111

+7

+7 × Const

1000

+8

+8 × Const

1001

+9

+9 × Const

1010

+10

+10 × Const

1011

+11

+11 × Const

1100

+12

+12 × Const

1101

+13

+13 × Const

1110

+14

+14 × Const

1111

+15

+15 × Const

АДРЕС

СОДЕРЖИМОЕ

ЯЧЕЙКИ

код значение

0000

+0

+0 × Const

0001

+1

+1 × Const

0010

+2

+2 × Const

0011

+3

+3 × Const

0100

+4

+4 × Const

0101

+5

+5 × Const

0110

+6

+6 × Const

0111

+7

+7 × Const

1000

–8

– 8 × Const

1001

–7

– 7 × Const

1010

–6

– 6 × Const

1011

–5

– 5 × Const

1100

–4

– 4 × Const

1101

–3

– 3 × Const

1110

–2

– 2 × Const

1111

–1

– 1 × Const

34

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

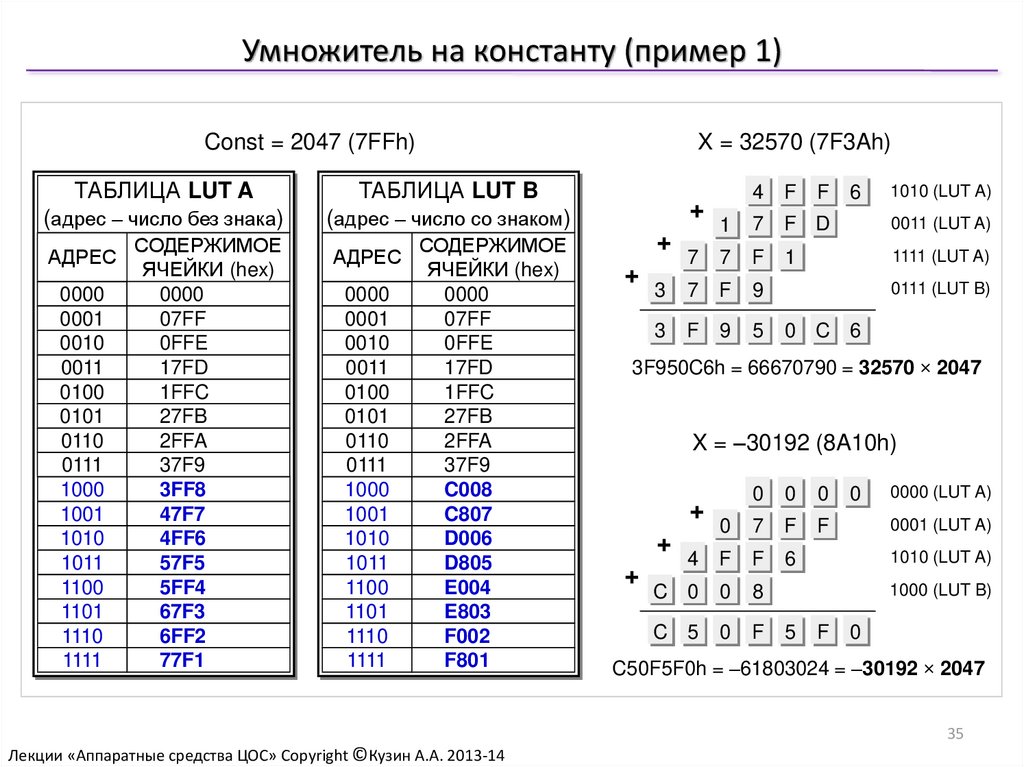

35. Умножитель на константу (пример 1)

Const = 2047 (7FFh)X = 32570 (7F3Ah)

ТАБЛИЦА LUT A

ТАБЛИЦА LUT B

(адрес – число без знака)

(адрес – число со знаком)

АДРЕС

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

СОДЕРЖИМОЕ

ЯЧЕЙКИ (hex)

0000

07FF

0FFE

17FD

1FFC

27FB

2FFA

37F9

3FF8

47F7

4FF6

57F5

5FF4

67F3

6FF2

77F1

АДРЕС

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

СОДЕРЖИМОЕ

ЯЧЕЙКИ (hex)

0000

07FF

0FFE

17FD

1FFC

27FB

2FFA

37F9

C008

C807

D006

D805

E004

E803

F002

F801

F

1

7

F D

0011 (LUT A)

7

7

F

1

1111 (LUT A)

3

7

F

9

3

F

9

5

+

+

+

F

6

1010 (LUT A)

4

0111 (LUT B)

0 C 6

3F950C6h = 66670790 = 32570 × 2047

X = –30192 (8A10h)

0

0

0

0

7

F

F

4

F

F

6

C 0

0

8

C 5

0

F

+

+

+

0

0000 (LUT A)

0001 (LUT A)

1010 (LUT A)

1000 (LUT B)

5

F

0

C50F5F0h = –61803024 = –30192 × 2047

35

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

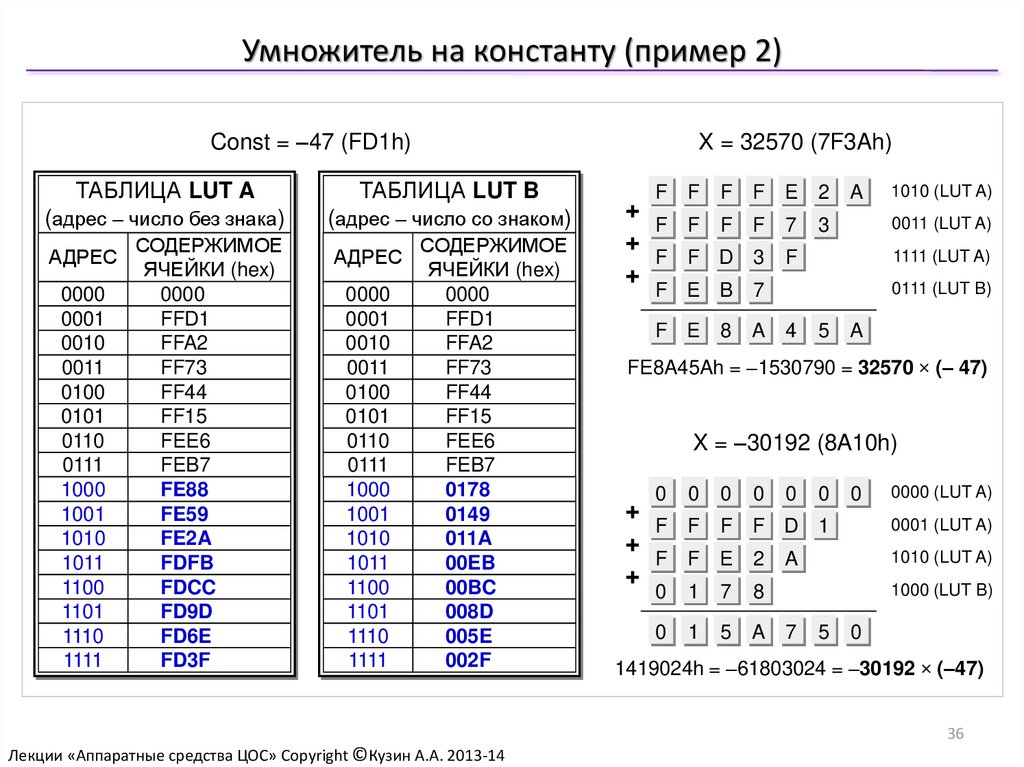

36. Умножитель на константу (пример 2)

Const = –47 (FD1h)X = 32570 (7F3Ah)

ТАБЛИЦА LUT A

ТАБЛИЦА LUT B

(адрес – число без знака)

(адрес – число со знаком)

АДРЕС

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

СОДЕРЖИМОЕ

ЯЧЕЙКИ (hex)

0000

FFD1

FFA2

FF73

FF44

FF15

FEE6

FEB7

FE88

FE59

FE2A

FDFB

FDCC

FD9D

FD6E

FD3F

АДРЕС

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

СОДЕРЖИМОЕ

ЯЧЕЙКИ (hex)

0000

FFD1

FFA2

FF73

FF44

FF15

FEE6

FEB7

0178

0149

011A

00EB

00BC

008D

005E

002F

+

+

+

F

F

F

F E

2

F

F

F

F

7

3

F

F D 3

F

F E B

7

F E

A

8

A

1010 (LUT A)

0011 (LUT A)

1111 (LUT A)

0111 (LUT B)

4

5

A

FE8A45Ah = –1530790 = 32570 × (– 47)

X = –30192 (8A10h)

+

+

+

0

0

0

0000 (LUT A)

0

0

0

0

F

F

F

F D 1

0001 (LUT A)

F

F E

2

1010 (LUT A)

0

1

7

8

0

1

5

A

A

1000 (LUT B)

7

5

0

1419024h = –61803024 = –30192 × (–47)

36

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

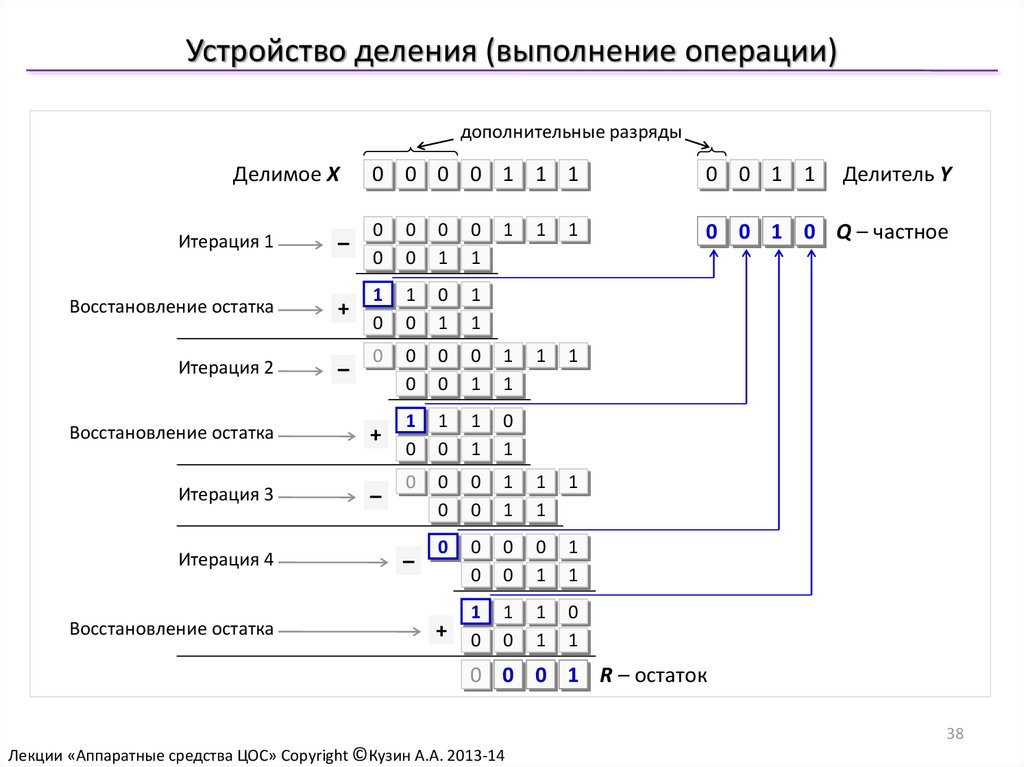

37. Устройство деления (алгоритм)

Для выполнения деления используется алгоритм с восстановлением остатка, позволяющийполучить одновременно частное и остаток. Операция выполняется над двоичными

положительными числами с фиксированной точкой. В случае чисел со знаком ввиду сложности

алгоритма, рекомендуется исходные операнды сделать положительными, а результат деления

откорректировать в зависимости от знака исходных операндов. Алгоритм содержит n итераций

(по количеству разрядов делимого X), каждая из которых включает несколько шагов.

Начальная установка

Приравниваем частичный остаток X'(0) = X

Итерация 1 (i=1)

Шаг 1. Определяем, содержится ли число Y×2n-1-i в частичном остатке X'(i-1), для чего

выполняем операцию вычитания X'(i-1) – Y×2n-1-i и анализируем знак полученной разности.

Если результат положителен (знаковый разряд 0 – число содержится в частичном остатке),

записываем цифру частного Qn-1=1. Если результат вычитания отрицателен (знаковый разряд 1

– число в частичном остатке не содержится), записываем цифру частного Qn-1=0.

Шаг2. Если разность X'(i-1) – Y×2n-1-i положительна, формируем новый частичный остаток,

равный этой разности X'(i) = X'(i-1) – Y×2n-1-i. Если разность отрицательна, то

X'(i) = X'(i-1) – Y×2n-1-i + Y×2n-1-i = X'(i-1). Этот шаг называется восстановлением остатка

(то, что вычли, снова прибавили).

Итерации 2...n. Повторяются шаги 1 и 2, формируется последняя цифра частного Q0 и остаток

операции деления R = X'(n-1).

37

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

38. Устройство деления (выполнение операции)

дополнительные разрядыДелимое X

0 0 0 0 1 1 1

0 0 1 1

0 0 1 0 Q – частное

Итерация 1

–

0

0

0

0

0

1

0

1

Восстановление остатка

+

1

0

1

0

0

1

1

1

Итерация 2

–

0

0

0

0

0

1

0

0

Восстановление остатка

+

Итерация 3

–

Итерация 4

Восстановление остатка

–

1

1

1

0

1

1

1

1

1

1

0

1

1

0

1

0

0

0

0

1

1

1

1

1

0

0

0

0

0

0

1

1

1

1

0

1

0

1

1

0

1

+

Делитель Y

0 0 0 1 R – остаток

38

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

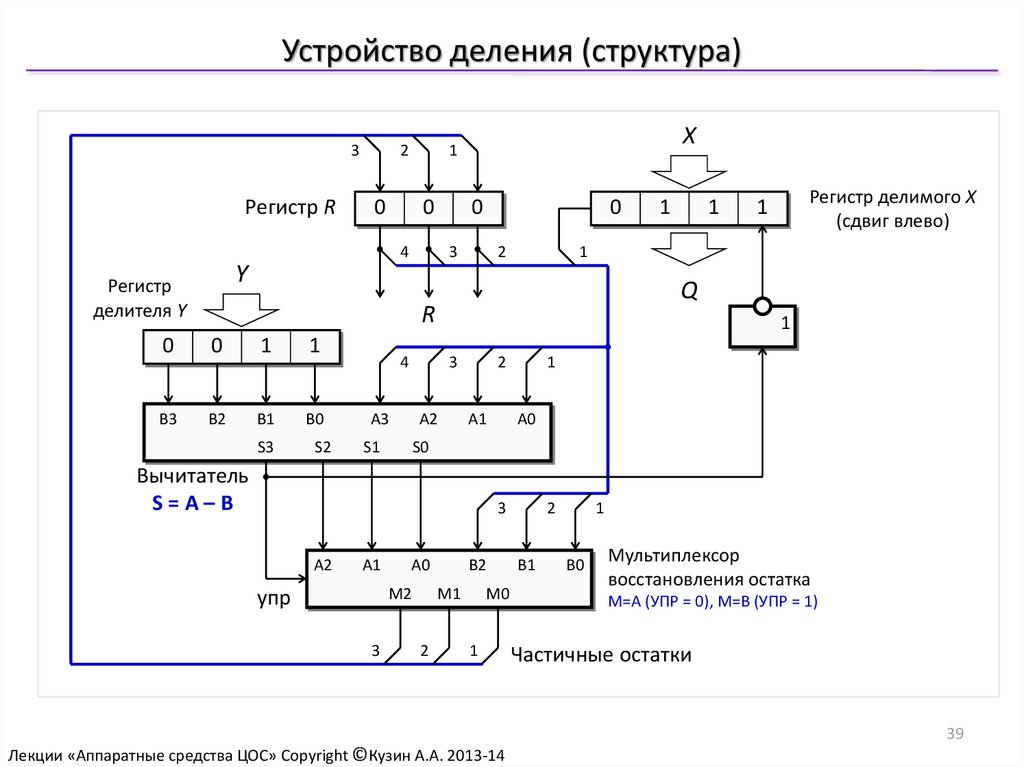

39. Устройство деления (структура)

3Регистр R

2

X

1

0

0

0

4

0

3

2

0

1

1

B3

B2

B1

B0

S3

S2

1

4

3

A3

A2

S1

2

A1

1

A0

S0

Вычитатель

S=A–B

3

A2

A1

A0

M2

упр

3

Регистр делимого X

(сдвиг влево)

1

Q

R

0

1

1

Y

Регистр

делителя Y

1

B2

M1

2

M0

1

2

B1

1

B0

Мультиплексор

восстановления остатка

M=A (УПР = 0), M=B (УПР = 1)

Частичные остатки

39

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

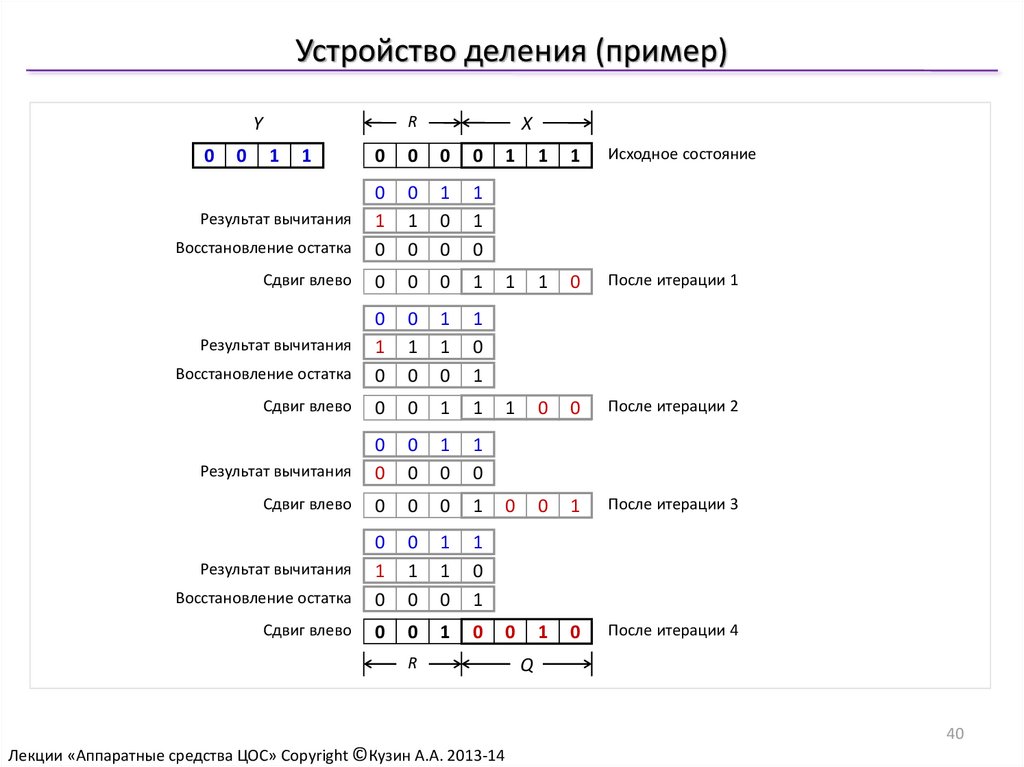

40. Устройство деления (пример)

RY

0

0

1

1

X

0

0

0

0

Восстановление остатка

0

1

0

0

1

0

1

0

0

1

1

0

Сдвиг влево

0

0

0

1

Результат вычитания

Восстановление остатка

0

1

0

0

1

0

1

1

0

1

0

1

Сдвиг влево

0

0

1

1

Результат вычитания

0

0

0

0

1

0

1

0

Сдвиг влево

0

0

0

1

Результат вычитания

Восстановление остатка

0

1

0

0

1

0

1

1

0

1

0

1

Сдвиг влево

0

0

1

0

Результат вычитания

R

1

1

1

Исходное состояние

1

1

0

После итерации 1

1

0

0

После итерации 2

0

0

1

После итерации 3

0

1

0

После итерации 4

Q

40

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

41.

41Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

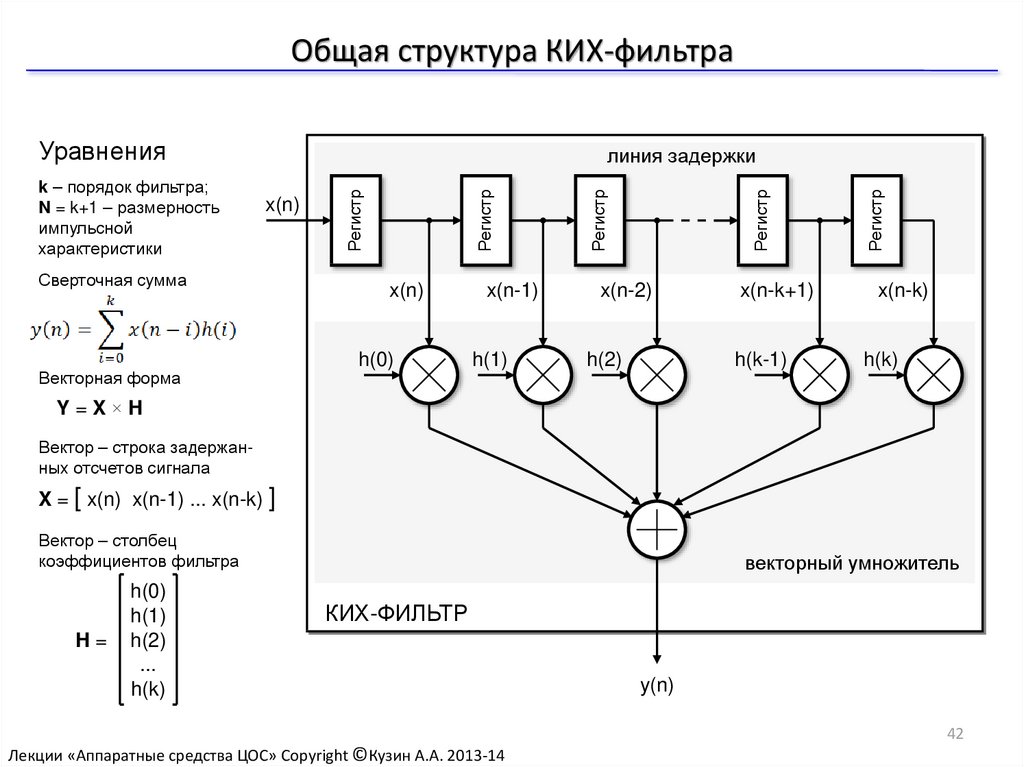

42. Общая структура КИХ-фильтра

УравненияСверточная сумма

Векторная форма

x(n)

h(0)

x(n-1)

h(1)

x(n-2)

h(2)

x(n-k+1)

h(k-1)

Регистр

Регистр

Регистр

Регистр

x(n)

Регистр

k – порядок фильтра;

N = k+1 – размерность

импульсной

характеристики

линия задержки

x(n-k)

h(k)

Y=X×H

Вектор – строка задержанных отсчетов сигнала

X = [ x(n) x(n-1) ... x(n-k) ]

Вектор – столбец

коэффициентов фильтра

H=

h(0)

h(1)

h(2)

...

h(k)

векторный умножитель

КИХ-ФИЛЬТР

y(n)

42

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

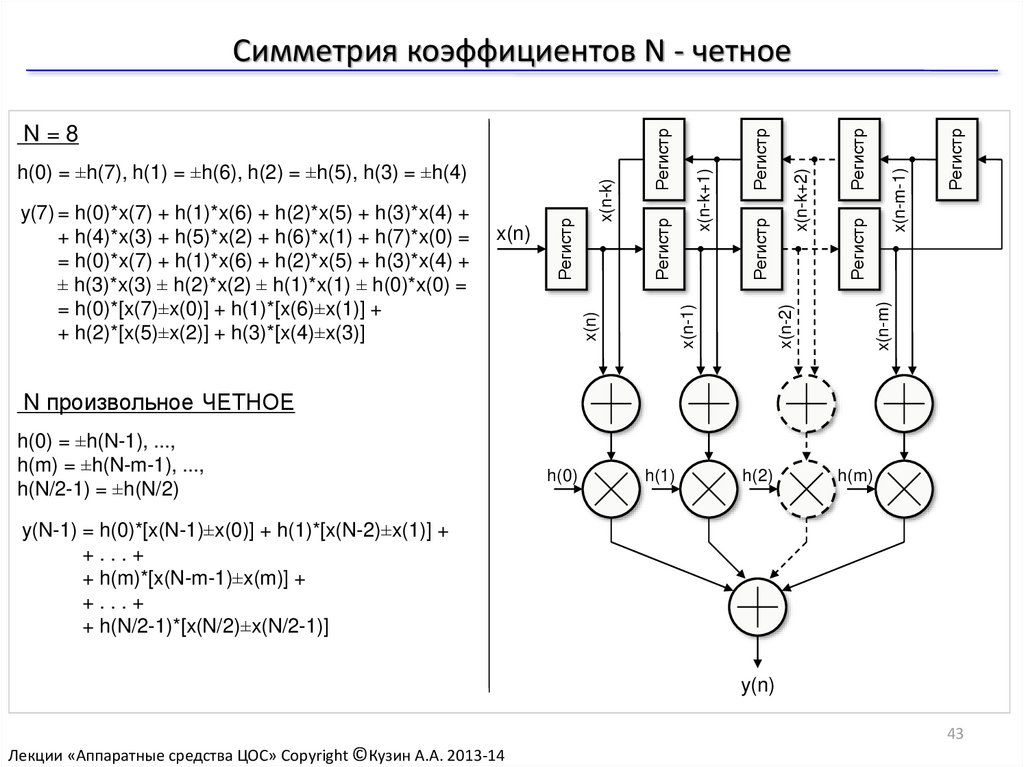

43. Симметрия коэффициентов N - четное

x(n-2)x(n-m)

Регистр

x(n-m-1)

Регистр

Регистр

x(n-k+2)

Регистр

Регистр

x(n-k+1)

x(n-1)

x(n)

x(n)

Регистр

y(7) = h(0)*x(7) + h(1)*x(6) + h(2)*x(5) + h(3)*x(4) +

+ h(4)*x(3) + h(5)*x(2) + h(6)*x(1) + h(7)*x(0) =

= h(0)*x(7) + h(1)*x(6) + h(2)*x(5) + h(3)*x(4) +

± h(3)*x(3) ± h(2)*x(2) ± h(1)*x(1) ± h(0)*x(0) =

= h(0)*[x(7)±x(0)] + h(1)*[x(6)±x(1)] +

+ h(2)*[x(5)±x(2)] + h(3)*[x(4)±x(3)]

x(n-k)

h(0) = ±h(7), h(1) = ±h(6), h(2) = ±h(5), h(3) = ±h(4)

Регистр

N=8

Регистр

Симметрия коэффициентов N - четное

N произвольное ЧЕТНОЕ

h(0) = ±h(N-1), ...,

h(m) = ±h(N-m-1), ...,

h(N/2-1) = ±h(N/2)

h(0)

h(1)

h(2)

h(m)

y(N-1) = h(0)*[x(N-1)±x(0)] + h(1)*[x(N-2)±x(1)] +

+...+

+ h(m)*[x(N-m-1)±x(m)] +

+...+

+ h(N/2-1)*[x(N/2)±x(N/2-1)]

y(n)

43

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

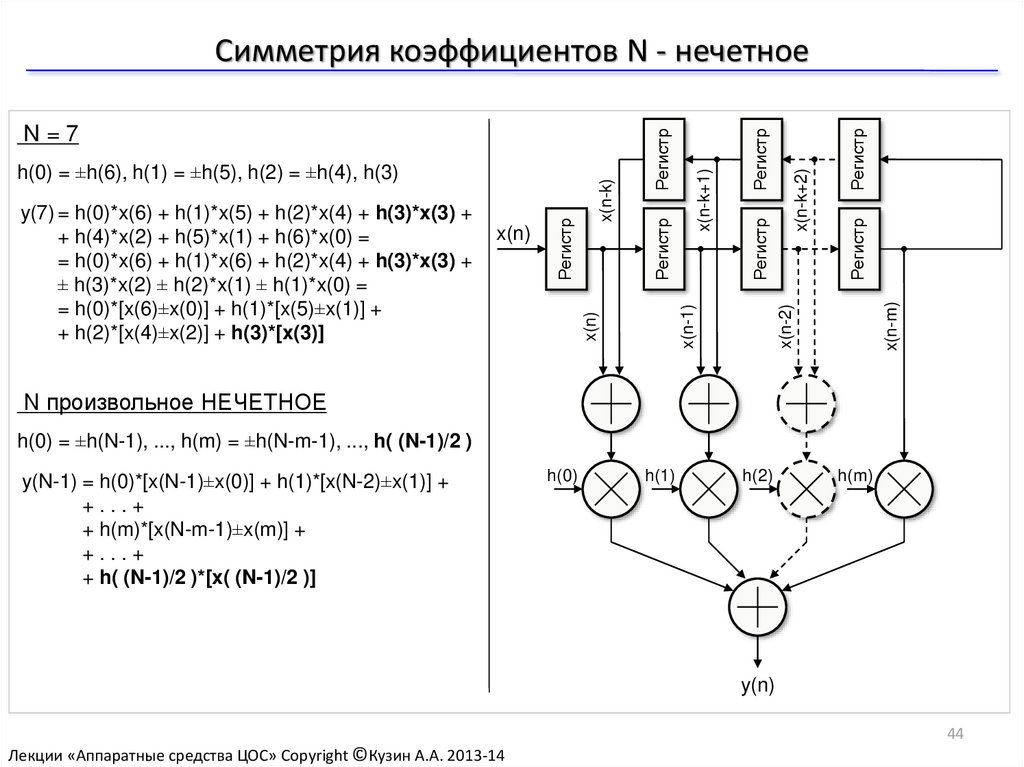

44. Симметрия коэффициентов N - нечетное

Регистрx(n-2)

x(n-m)

Регистр

x(n-k+2)

Регистр

Регистр

x(n-k+1)

x(n-1)

x(n)

x(n)

Регистр

y(7) = h(0)*x(6) + h(1)*x(5) + h(2)*x(4) + h(3)*x(3) +

+ h(4)*x(2) + h(5)*x(1) + h(6)*x(0) =

= h(0)*x(6) + h(1)*x(6) + h(2)*x(4) + h(3)*x(3) +

± h(3)*x(2) ± h(2)*x(1) ± h(1)*x(0) =

= h(0)*[x(6)±x(0)] + h(1)*[x(5)±x(1)] +

+ h(2)*[x(4)±x(2)] + h(3)*[x(3)]

x(n-k)

h(0) = ±h(6), h(1) = ±h(5), h(2) = ±h(4), h(3)

Регистр

N=7

Регистр

Симметрия коэффициентов N - нечетное

N произвольное НЕЧЕТНОЕ

h(0) = ±h(N-1), ..., h(m) = ±h(N-m-1), ..., h( (N-1)/2 )

y(N-1) = h(0)*[x(N-1)±x(0)] + h(1)*[x(N-2)±x(1)] +

+...+

+ h(m)*[x(N-m-1)±x(m)] +

+...+

+ h( (N-1)/2 )*[x( (N-1)/2 )]

h(0)

h(1)

h(2)

h(m)

y(n)

44

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

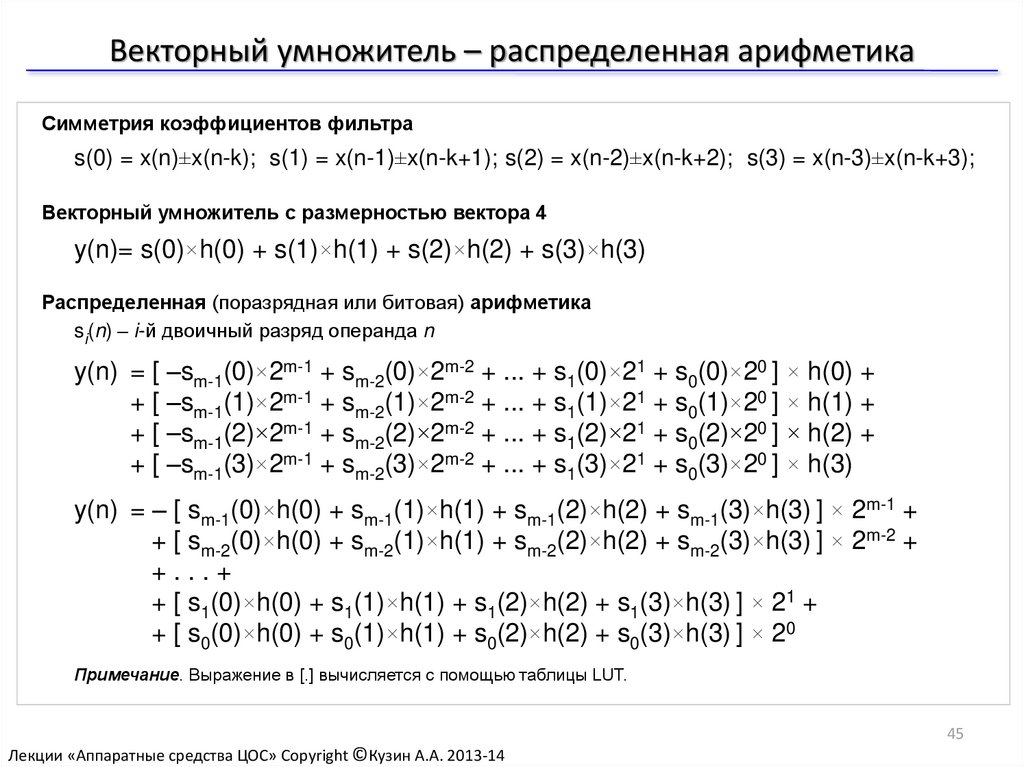

45. Векторный умножитель – распределенная арифметика

Симметрия коэффициентов фильтраs(0) = x(n)±x(n-k); s(1) = x(n-1)±x(n-k+1); s(2) = x(n-2)±x(n-k+2); s(3) = x(n-3)±x(n-k+3);

Векторный умножитель с размерностью вектора 4

y(n)= s(0)×h(0) + s(1)×h(1) + s(2)×h(2) + s(3)×h(3)

Распределенная (поразрядная или битовая) арифметика

si(n) – i-й двоичный разряд операнда n

y(n) = [ –sm-1(0)×2m-1 + sm-2(0)×2m-2 + ... + s1(0)×21 + s0(0)×20 ] × h(0) +

+ [ –sm-1(1)×2m-1 + sm-2(1)×2m-2 + ... + s1(1)×21 + s0(1)×20 ] × h(1) +

+ [ –sm-1(2)×2m-1 + sm-2(2)×2m-2 + ... + s1(2)×21 + s0(2)×20 ] × h(2) +

+ [ –sm-1(3)×2m-1 + sm-2(3)×2m-2 + ... + s1(3)×21 + s0(3)×20 ] × h(3)

y(n) = – [ sm-1(0)×h(0) + sm-1(1)×h(1) + sm-1(2)×h(2) + sm-1(3)×h(3) ] × 2m-1 +

+ [ sm-2(0)×h(0) + sm-2(1)×h(1) + sm-2(2)×h(2) + sm-2(3)×h(3) ] × 2m-2 +

+...+

+ [ s1(0)×h(0) + s1(1)×h(1) + s1(2)×h(2) + s1(3)×h(3) ] × 21 +

+ [ s0(0)×h(0) + s0(1)×h(1) + s0(2)×h(2) + s0(3)×h(3) ] × 20

Примечание. Выражение в [.] вычисляется с помощью таблицы LUT.

45

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

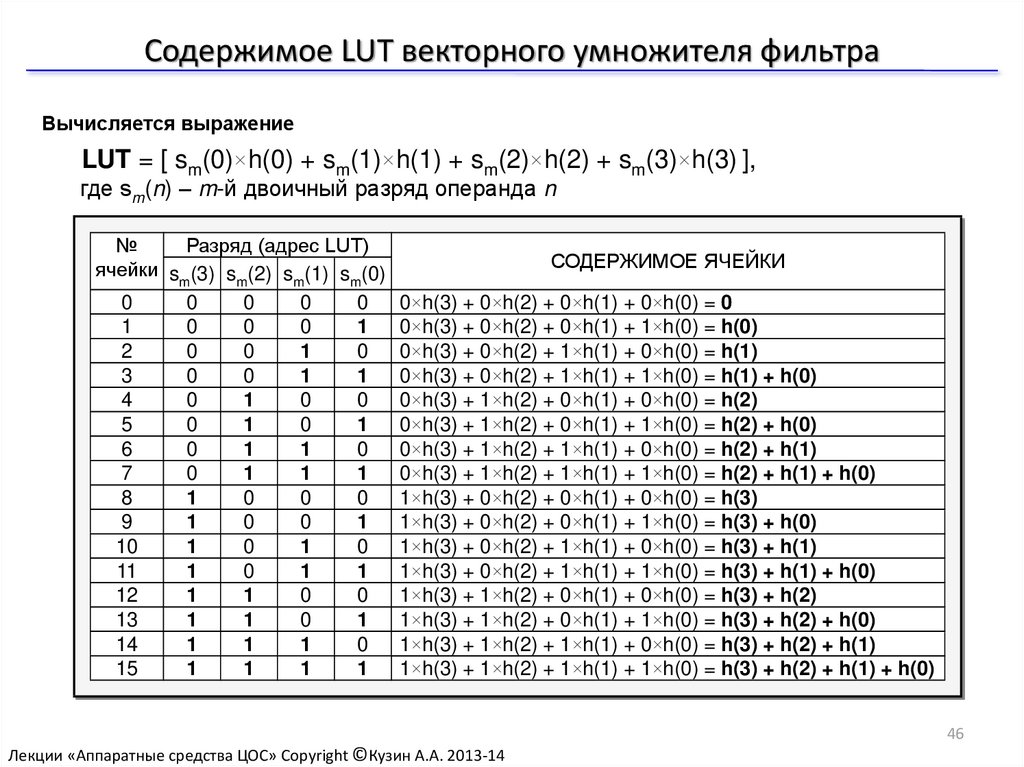

46. Содержимое LUT векторного умножителя фильтра

Вычисляется выражениеLUT = [ sm(0)×h(0) + sm(1)×h(1) + sm(2)×h(2) + sm(3)×h(3) ],

где sm(n) – m-й двоичный разряд операнда n

№

Разряд (адрес LUT)

ячейки s (3) s (2) s (1) s (0)

m

m

m

m

0

0

0

0

0

1

0

0

0

1

2

0

0

1

0

3

0

0

1

1

4

0

1

0

0

5

0

1

0

1

6

0

1

1

0

7

0

1

1

1

8

1

0

0

0

9

1

0

0

1

10

1

0

1

0

11

1

0

1

1

12

1

1

0

0

13

1

1

0

1

14

1

1

1

0

15

1

1

1

1

СОДЕРЖИМОЕ ЯЧЕЙКИ

0×h(3) + 0×h(2) + 0×h(1) + 0×h(0) = 0

0×h(3) + 0×h(2) + 0×h(1) + 1×h(0) = h(0)

0×h(3) + 0×h(2) + 1×h(1) + 0×h(0) = h(1)

0×h(3) + 0×h(2) + 1×h(1) + 1×h(0) = h(1) + h(0)

0×h(3) + 1×h(2) + 0×h(1) + 0×h(0) = h(2)

0×h(3) + 1×h(2) + 0×h(1) + 1×h(0) = h(2) + h(0)

0×h(3) + 1×h(2) + 1×h(1) + 0×h(0) = h(2) + h(1)

0×h(3) + 1×h(2) + 1×h(1) + 1×h(0) = h(2) + h(1) + h(0)

1×h(3) + 0×h(2) + 0×h(1) + 0×h(0) = h(3)

1×h(3) + 0×h(2) + 0×h(1) + 1×h(0) = h(3) + h(0)

1×h(3) + 0×h(2) + 1×h(1) + 0×h(0) = h(3) + h(1)

1×h(3) + 0×h(2) + 1×h(1) + 1×h(0) = h(3) + h(1) + h(0)

1×h(3) + 1×h(2) + 0×h(1) + 0×h(0) = h(3) + h(2)

1×h(3) + 1×h(2) + 0×h(1) + 1×h(0) = h(3) + h(2) + h(0)

1×h(3) + 1×h(2) + 1×h(1) + 0×h(0) = h(3) + h(2) + h(1)

1×h(3) + 1×h(2) + 1×h(1) + 1×h(0) = h(3) + h(2) + h(1) + h(0)

46

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

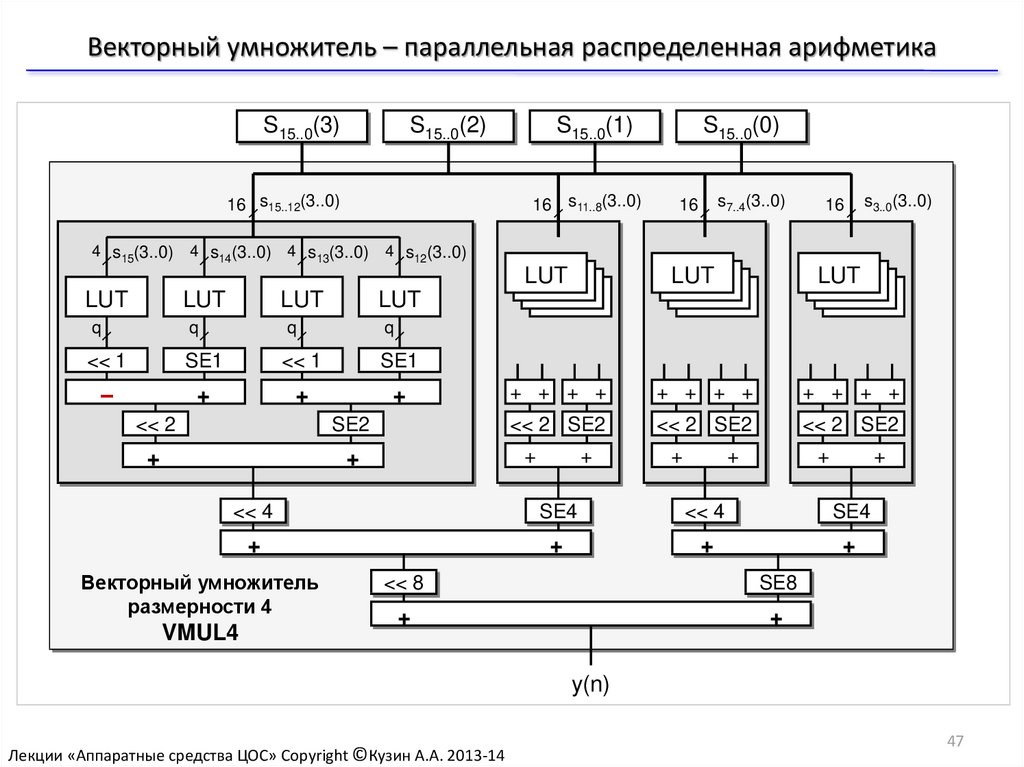

47. Векторный умножитель – параллельная распределенная арифметика

S15..0(3)S15..0(2)

16 s15..12(3..0)

4 s15(3..0)

LUT

4 s14(3..0)

LUT

S15..0(1)

16 s11..8(3..0)

4 s13(3..0)

LUT

q

q

q

q

<< 1

SE1

<< 1

SE1

–

+

+

+

SE2

+

+

s7..4(3..0)

16

16

s3..0(3..0)

4 s12(3..0)

LUT

<< 2

S15..0(0)

LUT

LUT

LUT

LUT

LUT

LUT

LUT

LUT

LUT

LUT

LUT

LUT

+ + + +

+ + + +

+ + + +

<< 2 SE2

<< 2 SE2

<< 2 SE2

+

+

+

+

+

+

<< 4

SE4

<< 4

SE4

+

+

+

+

Векторный умножитель

размерности 4

VMUL4

<< 8

SE8

+

+

y(n)

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

47

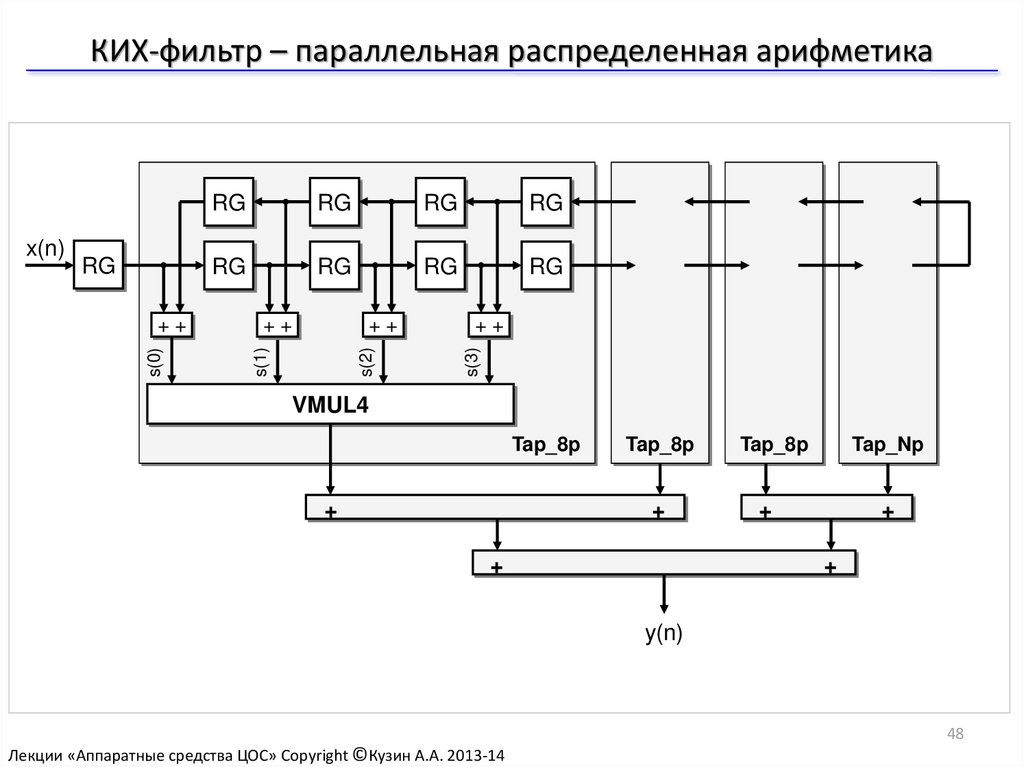

48. КИХ-фильтр – параллельная распределенная арифметика

RGRG

RG

RG

RG

++

++

++

s(3)

s(0)

++

RG

s(2)

RG

RG

s(1)

x(n)

RG

VMUL4

Tap_8p

+

Tap_8p

+

+

Tap_8p

Tap_Np

+

+

+

y(n)

48

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

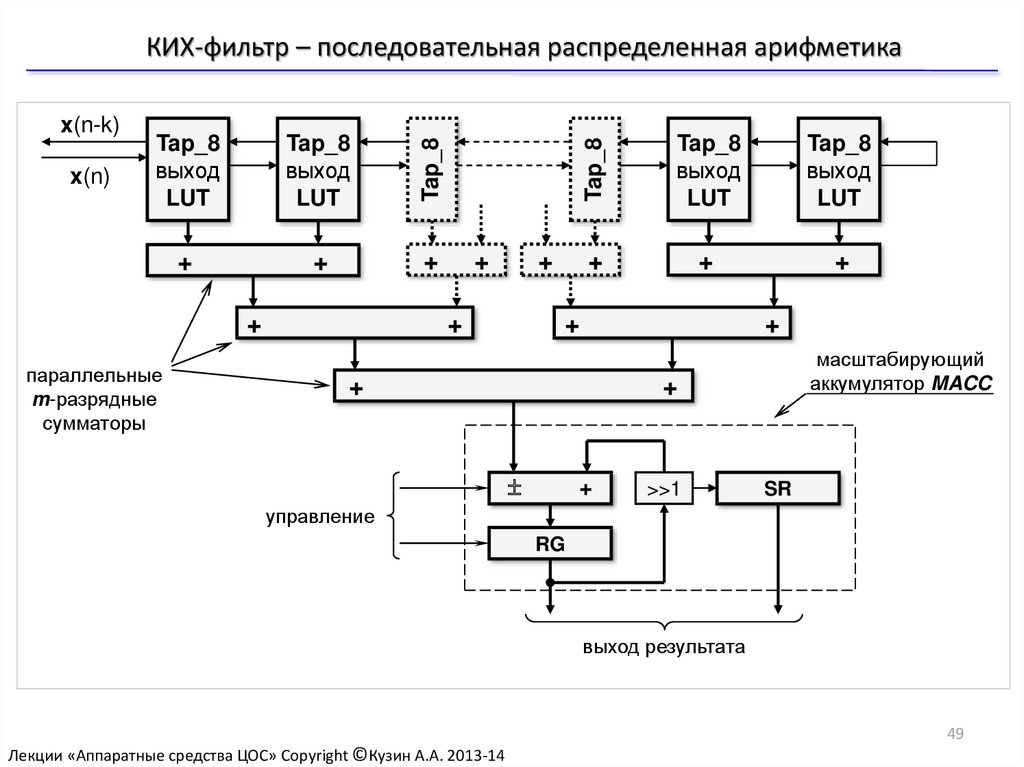

49. КИХ-фильтр – последовательная распределенная арифметика

x(n)Tap_8

выход

LUT

Tap_8

выход

LUT

+

+

+

+

параллельные

m-разрядные

сумматоры

+

+

+

Tap_8

x(n-k)

Tap_8

КИХ-фильтр – последовательная распределенная арифметика

Tap_8

выход

LUT

Tap_8

выход

LUT

+

+

+

+

+

+

масштабирующий

аккумулятор MACC

+

+

>>1

SR

управление

RG

выход результата

49

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

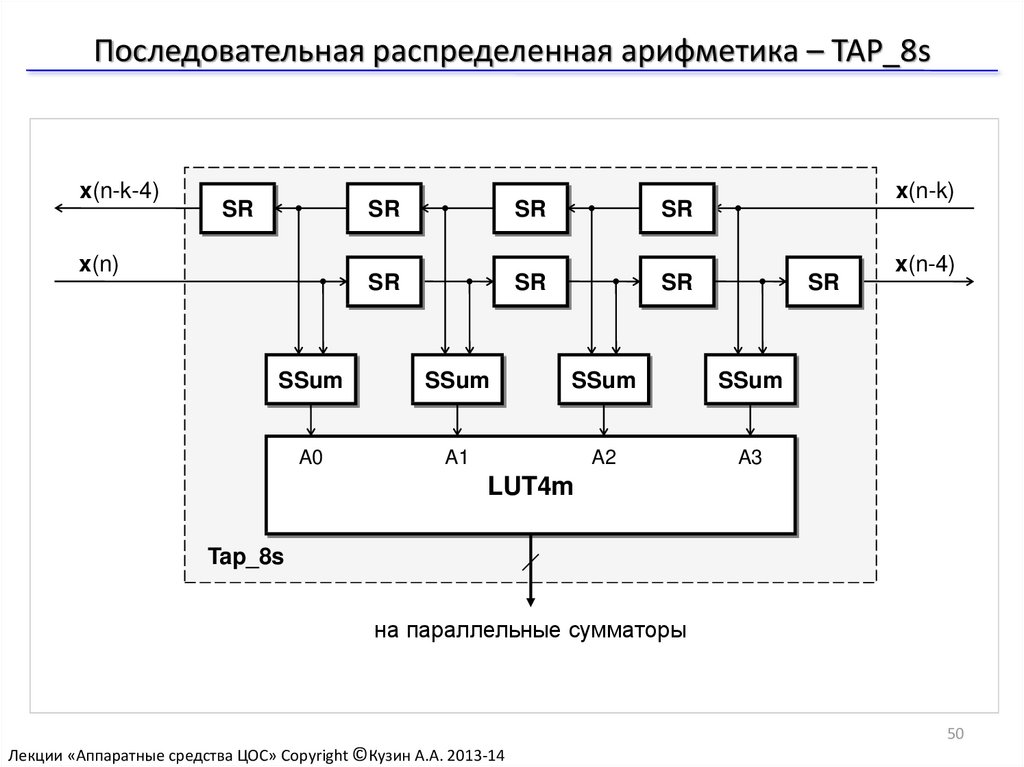

50. Последовательная распределенная арифметика – TAP_8s

x(n-k-4)SR

SR

x(n)

SR

SR

x(n-k)

SR

SR

SR

SR

SSum

SSum

SSum

SSum

A0

A1

A2

A3

x(n-4)

LUT4m

Tap_8s

m

на параллельные сумматоры

50

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

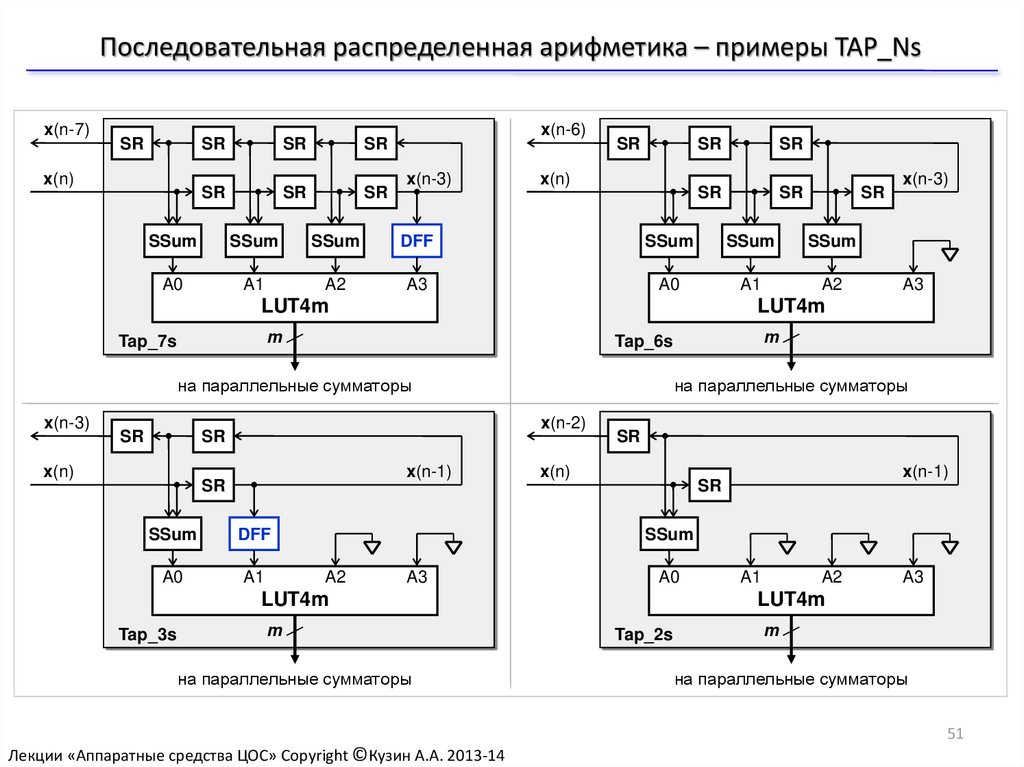

51. Последовательная распределенная арифметика – примеры TAP_Ns

x(n-7)SR

x(n)

SR

SR

SR

SR

SR

SR

x(n-6)

x(n-3)

SR

x(n)

SR

SR

SR

SR

SSum

SSum

SSum

DFF

SSum

SSum

SSum

A0

A1

A2

A3

A0

A1

A2

LUT4m

на параллельные сумматоры

x(n-2)

SR

x(n)

x(n-1)

SR

SSum

DFF

A0

A1

SR

x(n)

x(n-1)

SR

SSum

A2

A3

A0

LUT4m

Tap_3s

A3

m

Tap_6s

на параллельные сумматоры

SR

x(n-3)

LUT4m

m

Tap_7s

x(n-3)

SR

m

на параллельные сумматоры

A1

A2

A3

LUT4m

Tap_2s

m

на параллельные сумматоры

51

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

52. Потоки данных фильтра – последовательно-параллельная обработка

CLKEN

X(n)

SR

k

SR

SR

SR

SR

SR

SR

Конвейер

1

Уровень 0

PSR

LOAD

BIT0

1

1

1

SSum

1

1

1

1

1

SR

1

1

1

SSum

SSum

SSum

1

1

1

A

Уровень 1

B

LUT4m

LUT4m

m

m

C

Σ(1)

(1)

m+1

m+1

Уровень 3

D

(2)

Уровень 4

m+2

ADD_SUB

E

MACC

MAC_RST

m+2

– одноразрядные данные

– тактовый сигнал (Clock)

– многоразрядные данные

– управляющие сигналы

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

Уровень 2

Уровень 5

k

m+k+2

F

52

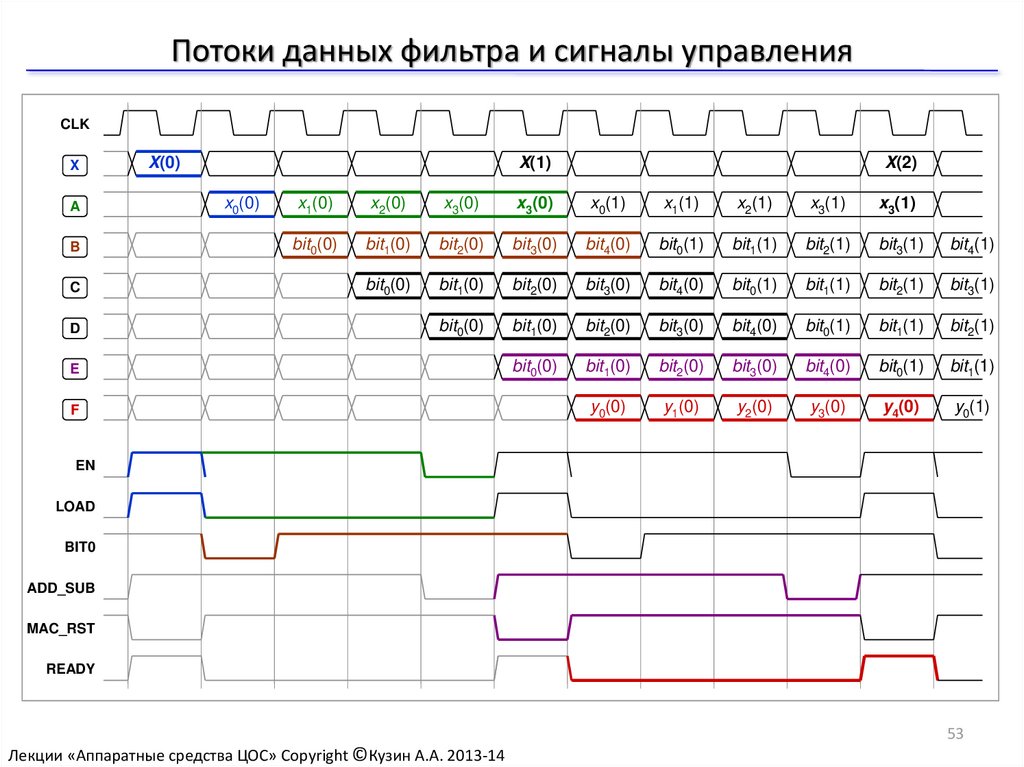

53. Потоки данных фильтра и сигналы управления

CLKX

A

B

C

D

X(0)

X(1)

x0(0)

X(2)

x1(0)

x2(0)

x3(0)

x3(0)

x0(1)

x1(1)

x2(1)

x3(1)

x3(1)

bit0(0)

bit1(0)

bit2(0)

bit3(0)

bit4(0)

bit0(1)

bit1(1)

bit2(1)

bit3(1)

bit4(1)

bit0(0)

bit1(0)

bit2(0)

bit3(0)

bit4(0)

bit0(1)

bit1(1)

bit2(1)

bit3(1)

bit0(0)

bit1(0)

bit2(0)

bit3(0)

bit4(0)

bit0(1)

bit1(1)

bit2(1)

bit0(0)

bit1(0)

bit2(0)

bit3(0)

bit4(0)

bit0(1)

bit1(1)

y0(0)

y1(0)

y2(0)

y3(0)

y4(0)

y0(1)

E

F

EN

LOAD

BIT0

ADD_SUB

MAC_RST

READY

53

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

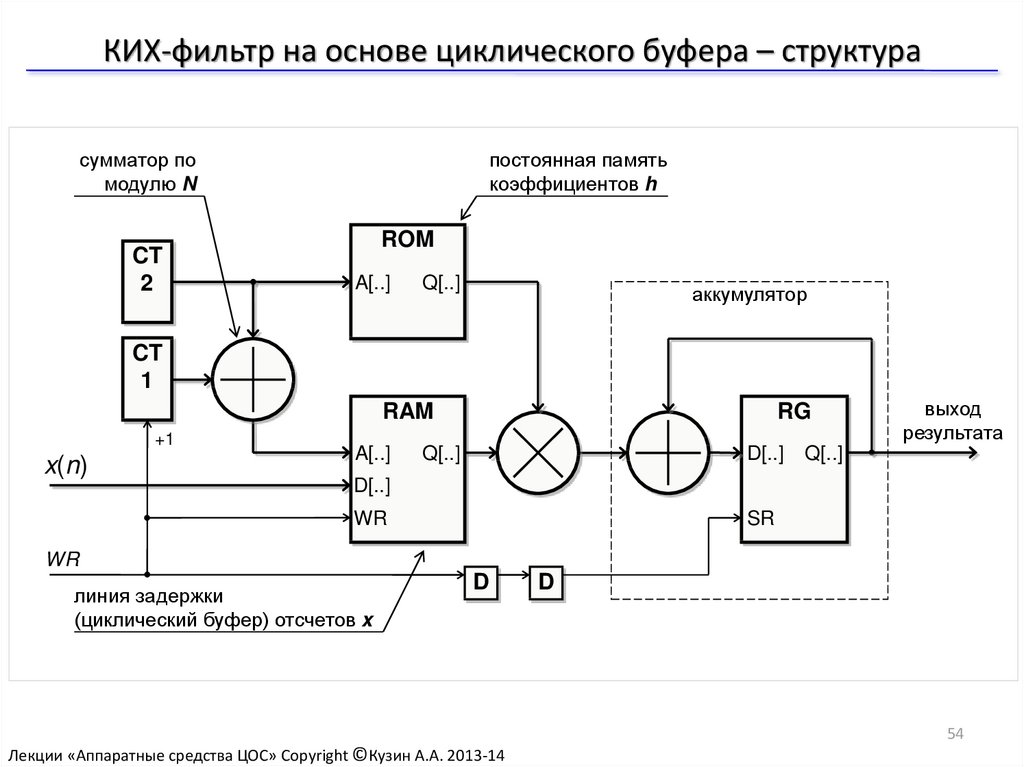

54. КИХ-фильтр на основе циклического буфера – структура

сумматор помодулю N

CT

2

постоянная память

коэффициентов h

ROM

A[..]

Q[..]

аккумулятор

CT

1

RAM

+1

x(n)

A[..]

RG

Q[..]

D[..]

выход

результата

Q[..]

D[..]

WR

SR

WR

линия задержки

(циклический буфер) отсчетов x

D

D

54

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

55. КИХ-фильтр на основе циклического буфера – работа

Таблица Адресация памяти для случая N = 5Запись

Время

n

n+1

n+2

n+3

n+4

n+5

n+6

Адрес ROM

Содержимое ROM

Адрес RAM

Содержимое RAM

Адрес RAM

Содержимое RAM

Адрес RAM

Содержимое RAM

Адрес RAM

Содержимое RAM

Адрес RAM

Содержимое RAM

Адрес RAM

Содержимое RAM

Адрес RAM

Содержимое RAM

Номер такта считывания (CT2)

0

1

2

3

4

0

1

2

3

4

h(4)

h(3)

h(2)

h(1)

h(0)

0

1

2

3

4

0

x(n)

0

0

0

0

x(n)

1

2

3

4

0

1

x(n+1) 0

0

0

x(n)

x(n+1)

2

3

4

0

1

2

x(n+2) 0

0

x(n)

x(n+1) x(n+2)

3

4

0

1

2

3

x(n+3) 0

x(n)

x(n+1) x(n+2) x(n+3)

4

0

1

2

3

4

x(n+4) x(n)

x(n+1) x(n+2) x(n+3) x(n+4)

0

1

2

3

4

0

x(n+5) x(n+1) x(n+2) x(n+3) x(n+4) x(n+5)

1

2

3

4

0

1

x(n+6) x(n+2) x(n+3) x(n+4) x(n+5) x(n+6)

...

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

55

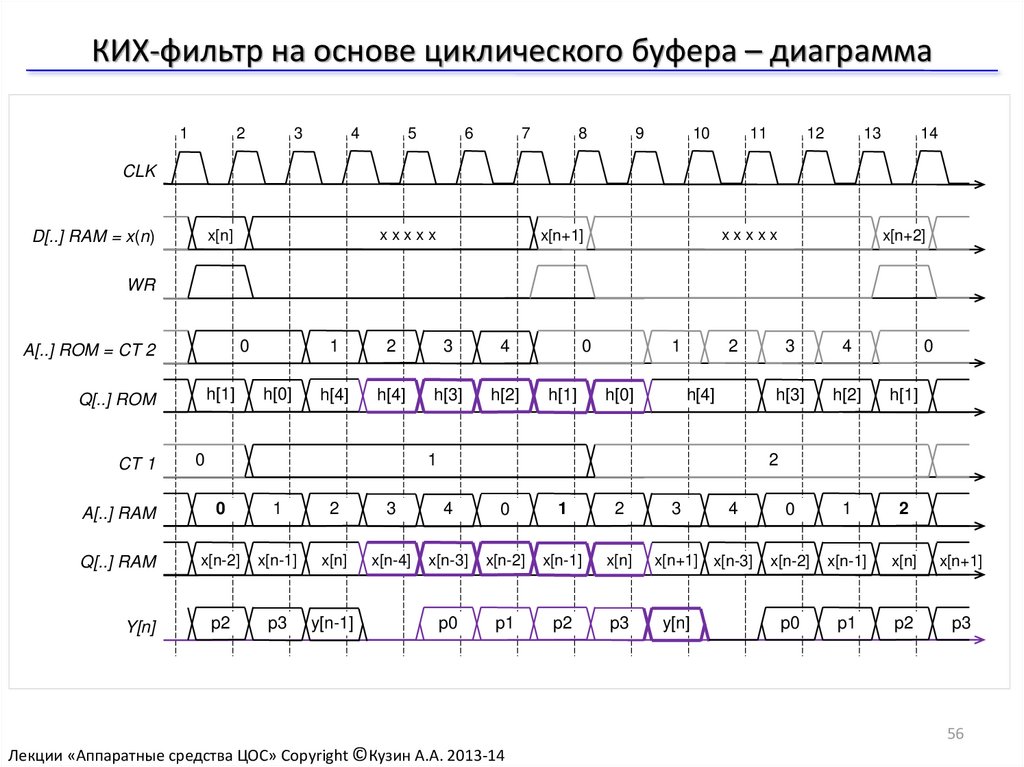

56. КИХ-фильтр на основе циклического буфера – диаграмма

12

3

4

5

6

7

8

9

10

11

12

13

14

CLK

xxxxx

x[n]

D[..] RAM = x(n)

xxxxx

x[n+1]

x[n+2]

WR

0

A[..] ROM = CT 2

h[1]

Q[..] ROM

CT 1

h[0]

1

2

3

4

h[4]

h[4]

h[3]

h[2]

0

1

0

h[1]

2

h[4]

h[0]

1

0

3

4

h[3]

h[2]

h[1]

2

A[..] RAM

0

1

2

3

4

0

1

2

3

4

0

1

2

Q[..] RAM

x[n-2]

x[n-1]

x[n]

x[n-4]

x[n-3]

x[n-2]

x[n-1]

x[n]

x[n+1]

x[n-3]

x[n-2]

x[n-1]

x[n]

x[n+1]

p2

p3

y[n-1]

p0

p1

p2

p3

y[n]

p0

p1

p2

p3

Y[n]

56

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

57. Полифазный децимирующий фильтр (спектры)

|S(f)||S(f)|

1

f

0

fs1/4

fs1/2

3fs1/4

f

fs1

0

fs1/4

fs1/2

3fs1/4

fs1

fs1/4

fs1/2

3fs1/4

fs1

fs1/4

fs1/2

3fs1/4

fs1

fs2/2

fs2

|H(f)|

2

f

0

|S(f)|

3

f

0

|S(f)|

|S(f)|

наложение

спектров

4

f

0

fs2/2

fs2

f

0

57

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

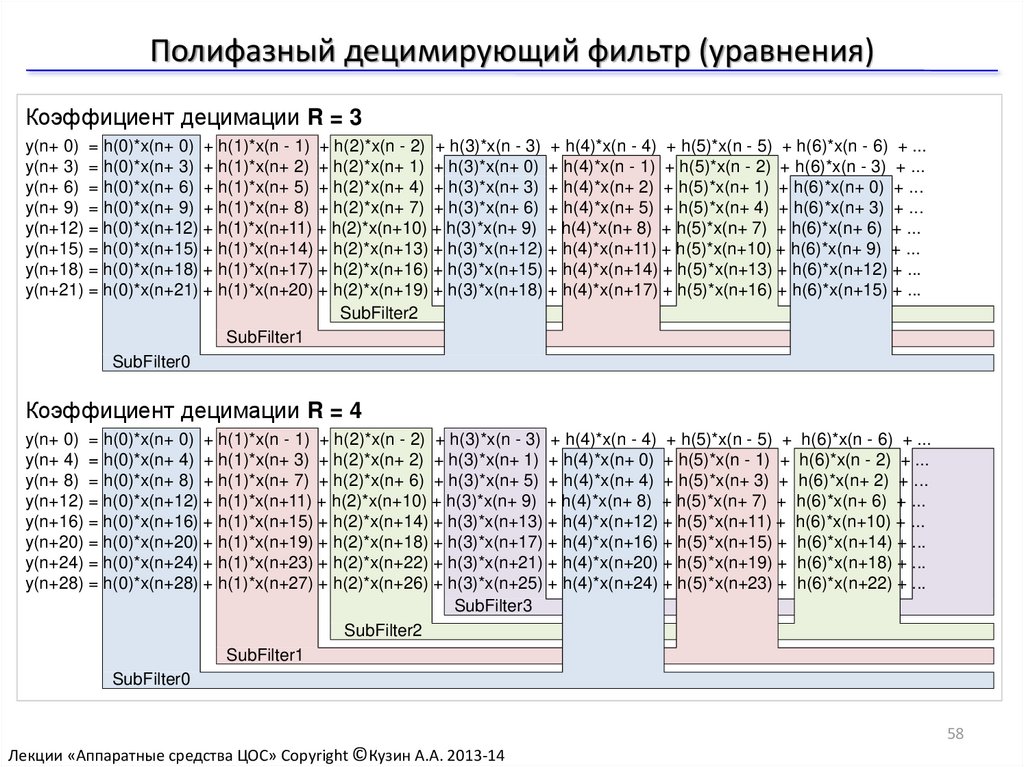

58. Полифазный децимирующий фильтр (уравнения)

Коэффициент децимации R = 3y(n+ 0) = h(0)*x(n+ 0) + h(1)*x(n - 1) + h(2)*x(n - 2) + h(3)*x(n - 3) + h(4)*x(n - 4) + h(5)*x(n - 5) + h(6)*x(n - 6) + ...

y(n+ 3) = h(0)*x(n+ 3) + h(1)*x(n+ 2) + h(2)*x(n+ 1) + h(3)*x(n+ 0) + h(4)*x(n - 1) + h(5)*x(n - 2) + h(6)*x(n - 3) + ...

y(n+ 6) = h(0)*x(n+ 6) + h(1)*x(n+ 5) + h(2)*x(n+ 4) + h(3)*x(n+ 3) + h(4)*x(n+ 2) + h(5)*x(n+ 1) + h(6)*x(n+ 0) + ...

y(n+ 9) = h(0)*x(n+ 9) + h(1)*x(n+ 8) + h(2)*x(n+ 7) + h(3)*x(n+ 6) + h(4)*x(n+ 5) + h(5)*x(n+ 4) + h(6)*x(n+ 3) + ...

y(n+12) = h(0)*x(n+12) + h(1)*x(n+11) + h(2)*x(n+10) + h(3)*x(n+ 9) + h(4)*x(n+ 8) + h(5)*x(n+ 7) + h(6)*x(n+ 6) + ...

y(n+15) = h(0)*x(n+15) + h(1)*x(n+14) + h(2)*x(n+13) + h(3)*x(n+12) + h(4)*x(n+11) + h(5)*x(n+10) + h(6)*x(n+ 9) + ...

y(n+18) = h(0)*x(n+18) + h(1)*x(n+17) + h(2)*x(n+16) + h(3)*x(n+15) + h(4)*x(n+14) + h(5)*x(n+13) + h(6)*x(n+12) + ...

y(n+21) = h(0)*x(n+21) + h(1)*x(n+20) + h(2)*x(n+19) + h(3)*x(n+18) + h(4)*x(n+17) + h(5)*x(n+16) + h(6)*x(n+15) + ...

SubFilter2

SubFilter1

SubFilter0

Коэффициент децимации R = 4

y(n+ 0) = h(0)*x(n+ 0) + h(1)*x(n - 1) + h(2)*x(n - 2) + h(3)*x(n - 3) + h(4)*x(n - 4) + h(5)*x(n - 5) + h(6)*x(n - 6) + ...

y(n+ 4) = h(0)*x(n+ 4) + h(1)*x(n+ 3) + h(2)*x(n+ 2) + h(3)*x(n+ 1) + h(4)*x(n+ 0) + h(5)*x(n - 1) + h(6)*x(n - 2) + ...

y(n+ 8) = h(0)*x(n+ 8) + h(1)*x(n+ 7) + h(2)*x(n+ 6) + h(3)*x(n+ 5) + h(4)*x(n+ 4) + h(5)*x(n+ 3) + h(6)*x(n+ 2) + ...

y(n+12) = h(0)*x(n+12) + h(1)*x(n+11) + h(2)*x(n+10) + h(3)*x(n+ 9) + h(4)*x(n+ 8) + h(5)*x(n+ 7) + h(6)*x(n+ 6) + ...

y(n+16) = h(0)*x(n+16) + h(1)*x(n+15) + h(2)*x(n+14) + h(3)*x(n+13) + h(4)*x(n+12) + h(5)*x(n+11) + h(6)*x(n+10) + ...

y(n+20) = h(0)*x(n+20) + h(1)*x(n+19) + h(2)*x(n+18) + h(3)*x(n+17) + h(4)*x(n+16) + h(5)*x(n+15) + h(6)*x(n+14) + ...

y(n+24) = h(0)*x(n+24) + h(1)*x(n+23) + h(2)*x(n+22) + h(3)*x(n+21) + h(4)*x(n+20) + h(5)*x(n+19) + h(6)*x(n+18) + ...

y(n+28) = h(0)*x(n+28) + h(1)*x(n+27) + h(2)*x(n+26) + h(3)*x(n+25) + h(4)*x(n+24) + h(5)*x(n+23) + h(6)*x(n+22) + ...

SubFilter3

SubFilter2

SubFilter1

SubFilter0

58

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

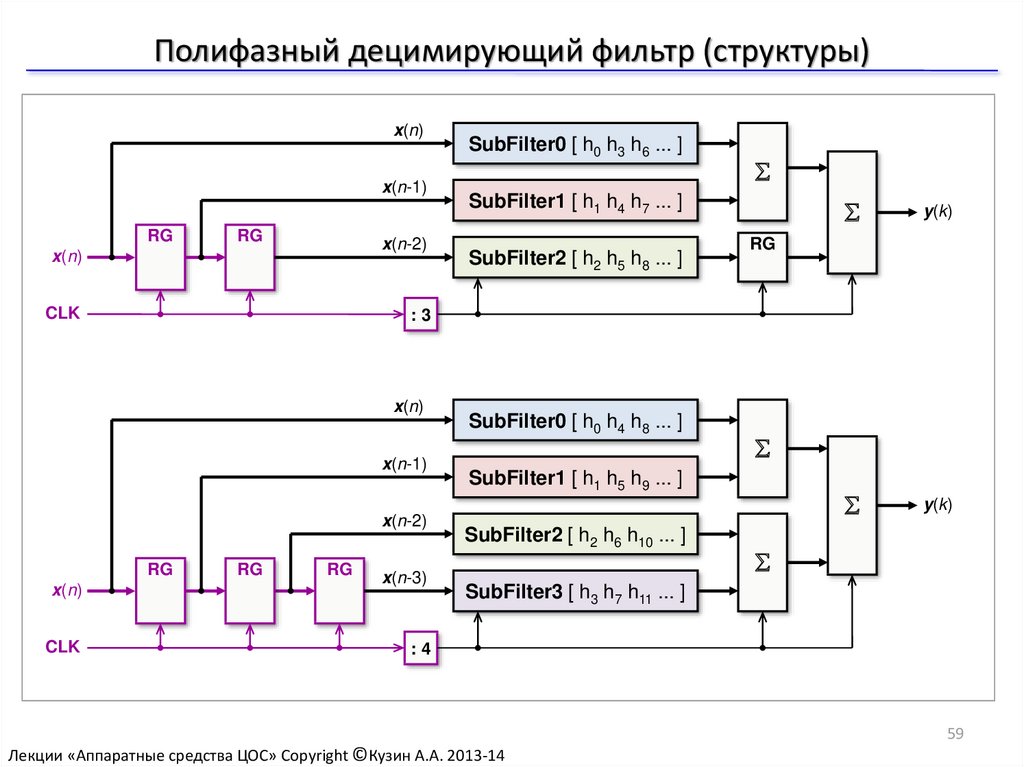

59. Полифазный децимирующий фильтр (структуры)

x(n)x(n-1)

RG

RG

x(n-2)

x(n)

CLK

x(n-1)

x(n-2)

RG

CLK

SubFilter1 [ h1 h4 h7 ... ]

SubFilter2 [ h2 h5 h8 ... ]

y(k)

y(k)

RG

:3

x(n)

x(n)

SubFilter0 [ h0 h3 h6 ... ]

RG

RG

x(n-3)

SubFilter0 [ h0 h4 h8 ... ]

SubFilter1 [ h1 h5 h9 ... ]

SubFilter2 [ h2 h6 h10 ... ]

SubFilter3 [ h3 h7 h11 ... ]

:4

59

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

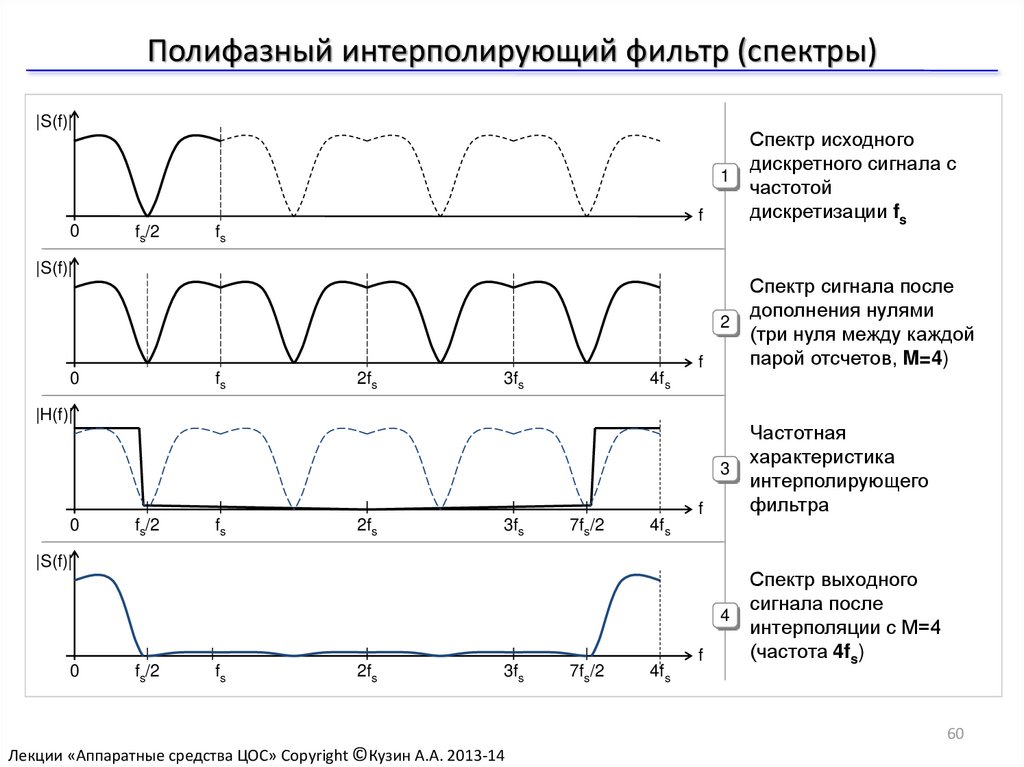

60. Полифазный интерполирующий фильтр (спектры)

|S(f)|0

fs/2

Спектр исходного

дискретного сигнала с

1

частотой

дискретизации fs

f

fs

|S(f)|

Спектр сигнала после

дополнения нулями

2

(три нуля между каждой

парой отсчетов, M=4)

f

0

fs

2fs

3fs

4fs

|H(f)|

0

Частотная

характеристика

3

интерполирующего

фильтра

f

fs/2

fs

2fs

3fs

7fs/2

4fs

|S(f)|

0

fs/2

fs

2fs

3fs

7fs/2

4fs

Спектр выходного

сигнала после

4

интерполяции с M=4

(частота 4fs)

f

60

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

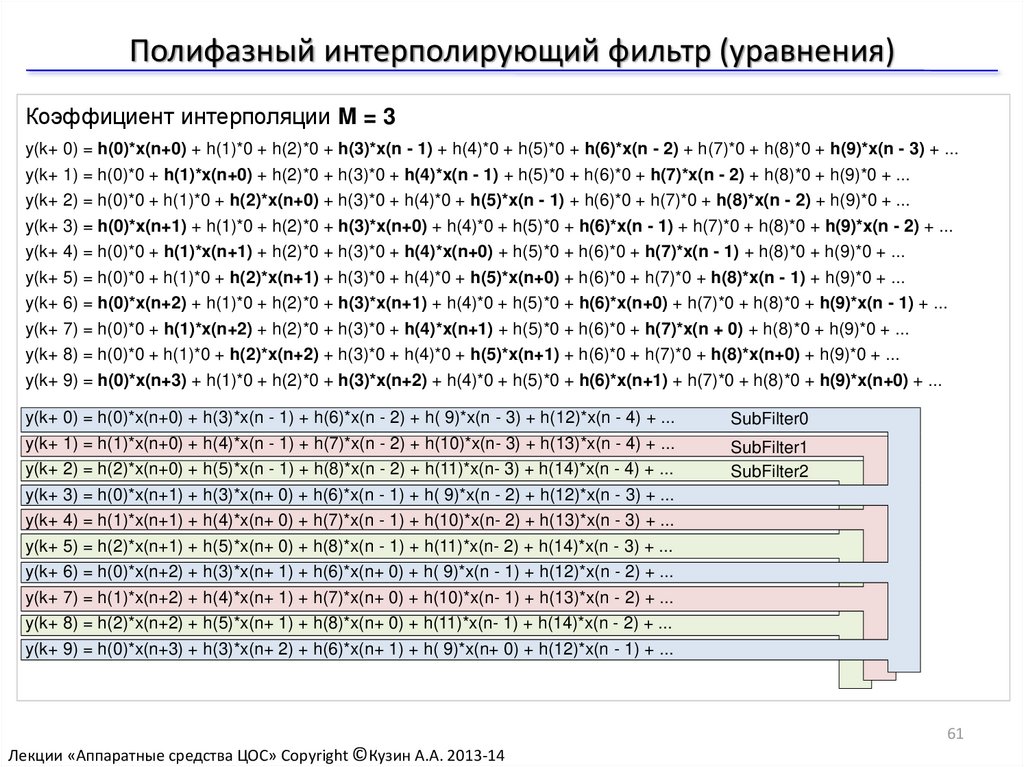

61. Полифазный интерполирующий фильтр (уравнения)

Коэффициент интерполяции M = 3y(k+ 0) = h(0)*x(n+0) + h(1)*0 + h(2)*0 + h(3)*x(n - 1) + h(4)*0 + h(5)*0 + h(6)*x(n - 2) + h(7)*0 + h(8)*0 + h(9)*x(n - 3) + ...

y(k+ 1) = h(0)*0 + h(1)*x(n+0) + h(2)*0 + h(3)*0 + h(4)*x(n - 1) + h(5)*0 + h(6)*0 + h(7)*x(n - 2) + h(8)*0 + h(9)*0 + ...

y(k+ 2) = h(0)*0 + h(1)*0 + h(2)*x(n+0) + h(3)*0 + h(4)*0 + h(5)*x(n - 1) + h(6)*0 + h(7)*0 + h(8)*x(n - 2) + h(9)*0 + ...

y(k+ 3) = h(0)*x(n+1) + h(1)*0 + h(2)*0 + h(3)*x(n+0) + h(4)*0 + h(5)*0 + h(6)*x(n - 1) + h(7)*0 + h(8)*0 + h(9)*x(n - 2) + ...

y(k+ 4) = h(0)*0 + h(1)*x(n+1) + h(2)*0 + h(3)*0 + h(4)*x(n+0) + h(5)*0 + h(6)*0 + h(7)*x(n - 1) + h(8)*0 + h(9)*0 + ...

y(k+ 5) = h(0)*0 + h(1)*0 + h(2)*x(n+1) + h(3)*0 + h(4)*0 + h(5)*x(n+0) + h(6)*0 + h(7)*0 + h(8)*x(n - 1) + h(9)*0 + ...

y(k+ 6) = h(0)*x(n+2) + h(1)*0 + h(2)*0 + h(3)*x(n+1) + h(4)*0 + h(5)*0 + h(6)*x(n+0) + h(7)*0 + h(8)*0 + h(9)*x(n - 1) + ...

y(k+ 7) = h(0)*0 + h(1)*x(n+2) + h(2)*0 + h(3)*0 + h(4)*x(n+1) + h(5)*0 + h(6)*0 + h(7)*x(n + 0) + h(8)*0 + h(9)*0 + ...

y(k+ 8) = h(0)*0 + h(1)*0 + h(2)*x(n+2) + h(3)*0 + h(4)*0 + h(5)*x(n+1) + h(6)*0 + h(7)*0 + h(8)*x(n+0) + h(9)*0 + ...

y(k+ 9) = h(0)*x(n+3) + h(1)*0 + h(2)*0 + h(3)*x(n+2) + h(4)*0 + h(5)*0 + h(6)*x(n+1) + h(7)*0 + h(8)*0 + h(9)*x(n+0) + ...

y(k+ 0) = h(0)*x(n+0) + h(3)*x(n - 1) + h(6)*x(n - 2) + h( 9)*x(n - 3) + h(12)*x(n - 4) + ...

y(k+ 1) = h(1)*x(n+0) + h(4)*x(n - 1) + h(7)*x(n - 2) + h(10)*x(n- 3) + h(13)*x(n - 4) + ...

y(k+ 2) = h(2)*x(n+0) + h(5)*x(n - 1) + h(8)*x(n - 2) + h(11)*x(n- 3) + h(14)*x(n - 4) + ...

y(k+ 3) = h(0)*x(n+1) + h(3)*x(n+ 0) + h(6)*x(n - 1) + h( 9)*x(n - 2) + h(12)*x(n - 3) + ...

SubFilter0

SubFilter1

SubFilter2

y(k+ 4) = h(1)*x(n+1) + h(4)*x(n+ 0) + h(7)*x(n - 1) + h(10)*x(n- 2) + h(13)*x(n - 3) + ...

y(k+ 5) = h(2)*x(n+1) + h(5)*x(n+ 0) + h(8)*x(n - 1) + h(11)*x(n- 2) + h(14)*x(n - 3) + ...

y(k+ 6) = h(0)*x(n+2) + h(3)*x(n+ 1) + h(6)*x(n+ 0) + h( 9)*x(n - 1) + h(12)*x(n - 2) + ...

y(k+ 7) = h(1)*x(n+2) + h(4)*x(n+ 1) + h(7)*x(n+ 0) + h(10)*x(n- 1) + h(13)*x(n - 2) + ...

y(k+ 8) = h(2)*x(n+2) + h(5)*x(n+ 1) + h(8)*x(n+ 0) + h(11)*x(n- 1) + h(14)*x(n - 2) + ...

y(k+ 9) = h(0)*x(n+3) + h(3)*x(n+ 2) + h(6)*x(n+ 1) + h( 9)*x(n+ 0) + h(12)*x(n - 1) + ...

61

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

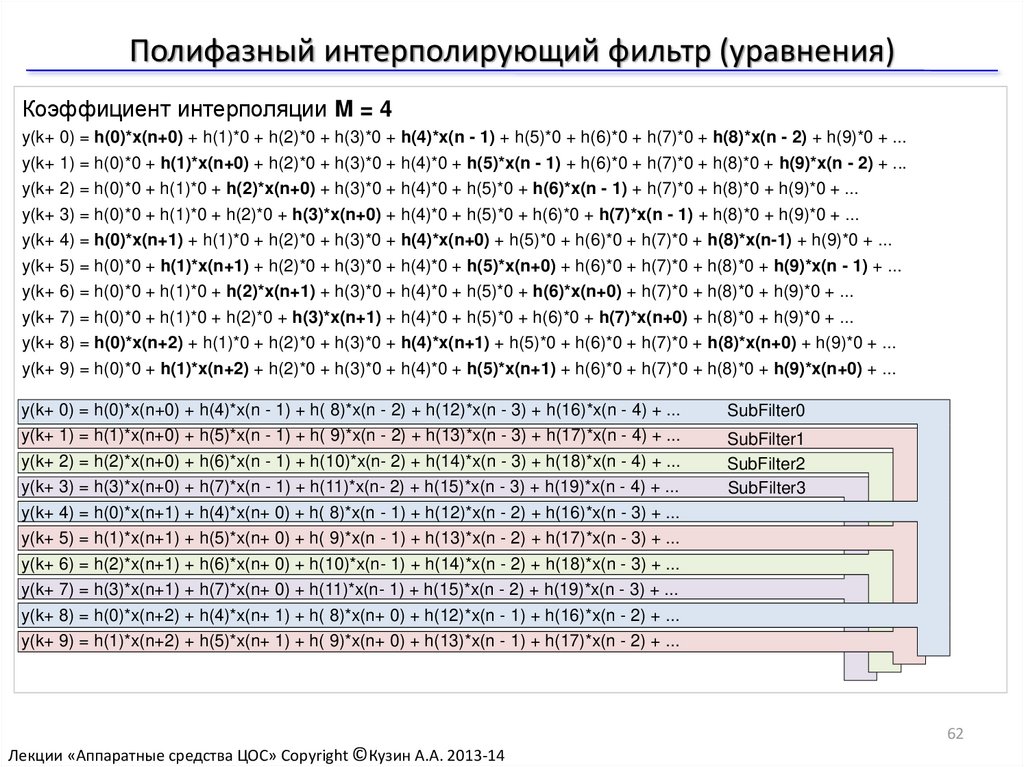

62. Полифазный интерполирующий фильтр (уравнения)

Коэффициент интерполяции M = 4y(k+ 0) = h(0)*x(n+0) + h(1)*0 + h(2)*0 + h(3)*0 + h(4)*x(n - 1) + h(5)*0 + h(6)*0 + h(7)*0 + h(8)*x(n - 2) + h(9)*0 + ...

y(k+ 1) = h(0)*0 + h(1)*x(n+0) + h(2)*0 + h(3)*0 + h(4)*0 + h(5)*x(n - 1) + h(6)*0 + h(7)*0 + h(8)*0 + h(9)*x(n - 2) + ...

y(k+ 2) = h(0)*0 + h(1)*0 + h(2)*x(n+0) + h(3)*0 + h(4)*0 + h(5)*0 + h(6)*x(n - 1) + h(7)*0 + h(8)*0 + h(9)*0 + ...

y(k+ 3) = h(0)*0 + h(1)*0 + h(2)*0 + h(3)*x(n+0) + h(4)*0 + h(5)*0 + h(6)*0 + h(7)*x(n - 1) + h(8)*0 + h(9)*0 + ...

y(k+ 4) = h(0)*x(n+1) + h(1)*0 + h(2)*0 + h(3)*0 + h(4)*x(n+0) + h(5)*0 + h(6)*0 + h(7)*0 + h(8)*x(n-1) + h(9)*0 + ...

y(k+ 5) = h(0)*0 + h(1)*x(n+1) + h(2)*0 + h(3)*0 + h(4)*0 + h(5)*x(n+0) + h(6)*0 + h(7)*0 + h(8)*0 + h(9)*x(n - 1) + ...

y(k+ 6) = h(0)*0 + h(1)*0 + h(2)*x(n+1) + h(3)*0 + h(4)*0 + h(5)*0 + h(6)*x(n+0) + h(7)*0 + h(8)*0 + h(9)*0 + ...

y(k+ 7) = h(0)*0 + h(1)*0 + h(2)*0 + h(3)*x(n+1) + h(4)*0 + h(5)*0 + h(6)*0 + h(7)*x(n+0) + h(8)*0 + h(9)*0 + ...

y(k+ 8) = h(0)*x(n+2) + h(1)*0 + h(2)*0 + h(3)*0 + h(4)*x(n+1) + h(5)*0 + h(6)*0 + h(7)*0 + h(8)*x(n+0) + h(9)*0 + ...

y(k+ 9) = h(0)*0 + h(1)*x(n+2) + h(2)*0 + h(3)*0 + h(4)*0 + h(5)*x(n+1) + h(6)*0 + h(7)*0 + h(8)*0 + h(9)*x(n+0) + ...

y(k+ 0) = h(0)*x(n+0) + h(4)*x(n - 1) + h( 8)*x(n - 2) + h(12)*x(n - 3) + h(16)*x(n - 4) + ...

SubFilter0

y(k+ 1) = h(1)*x(n+0) + h(5)*x(n - 1) + h( 9)*x(n - 2) + h(13)*x(n - 3) + h(17)*x(n - 4) + ...

y(k+ 2) = h(2)*x(n+0) + h(6)*x(n - 1) + h(10)*x(n- 2) + h(14)*x(n - 3) + h(18)*x(n - 4) + ...

y(k+ 3) = h(3)*x(n+0) + h(7)*x(n - 1) + h(11)*x(n- 2) + h(15)*x(n - 3) + h(19)*x(n - 4) + ...

y(k+ 4) = h(0)*x(n+1) + h(4)*x(n+ 0) + h( 8)*x(n - 1) + h(12)*x(n - 2) + h(16)*x(n - 3) + ...

y(k+ 5) = h(1)*x(n+1) + h(5)*x(n+ 0) + h( 9)*x(n - 1) + h(13)*x(n - 2) + h(17)*x(n - 3) + ...

y(k+ 6) = h(2)*x(n+1) + h(6)*x(n+ 0) + h(10)*x(n- 1) + h(14)*x(n - 2) + h(18)*x(n - 3) + ...

SubFilter1

SubFilter2

SubFilter3

y(k+ 7) = h(3)*x(n+1) + h(7)*x(n+ 0) + h(11)*x(n- 1) + h(15)*x(n - 2) + h(19)*x(n - 3) + ...

y(k+ 8) = h(0)*x(n+2) + h(4)*x(n+ 1) + h( 8)*x(n+ 0) + h(12)*x(n - 1) + h(16)*x(n - 2) + ...

y(k+ 9) = h(1)*x(n+2) + h(5)*x(n+ 1) + h( 9)*x(n+ 0) + h(13)*x(n - 1) + h(17)*x(n - 2) + ...

62

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

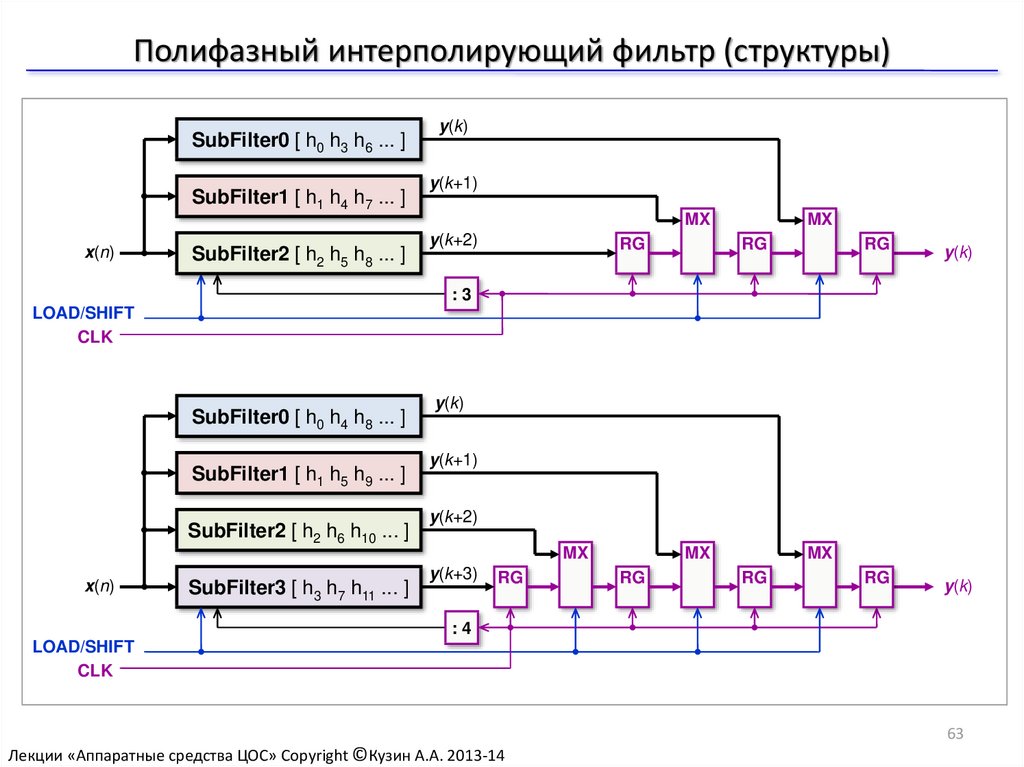

63. Полифазный интерполирующий фильтр (структуры)

SubFilter0 [ h0 h3 h6 ... ]SubFilter1 [ h1 h4 h7 ... ]

y(k)

y(k+1)

MX

x(n)

SubFilter2 [ h2 h5 h8 ... ]

y(k+2)

RG

MX

RG

RG

y(k)

RG

y(k)

:3

LOAD/SHIFT

CLK

SubFilter0 [ h0 h4 h8 ... ]

SubFilter1 [ h1 h5 h9 ... ]

SubFilter2 [ h2 h6 h10 ... ]

y(k)

y(k+1)

y(k+2)

MX

x(n)

SubFilter3 [ h3 h7 h11 ... ]

y(k+3)

RG

MX

RG

MX

RG

:4

LOAD/SHIFT

CLK

63

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

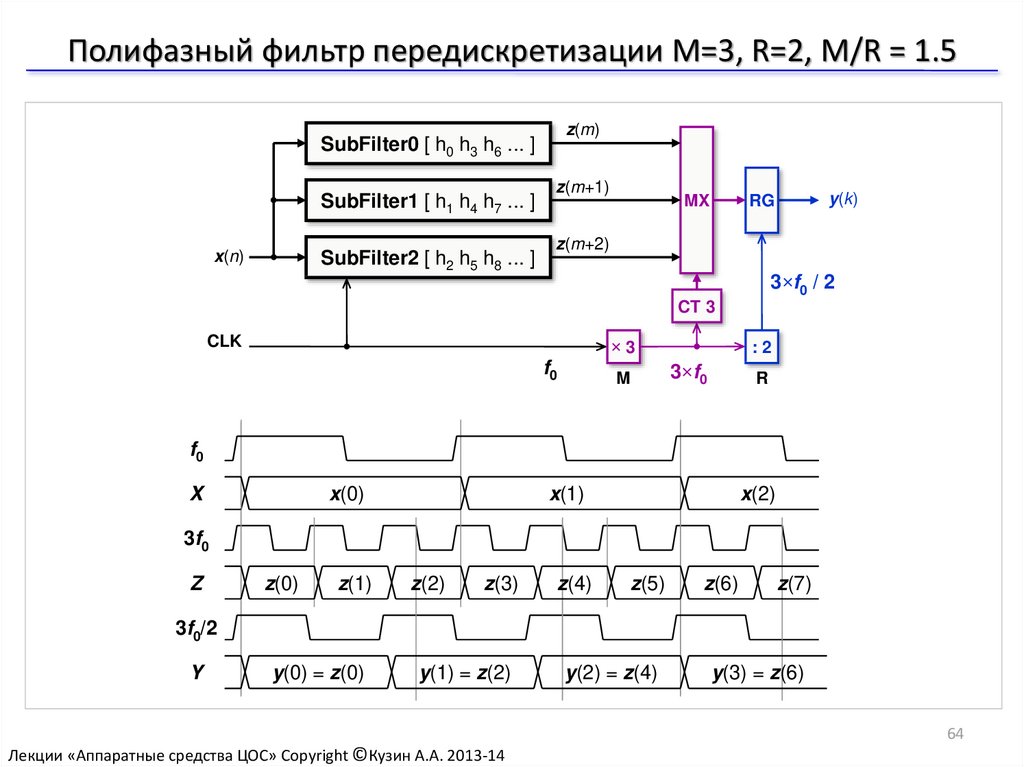

64. Полифазный фильтр передискретизации M=3, R=2, M/R = 1.5

z(m)SubFilter0 [ h0 h3 h6 ... ]

SubFilter1 [ h1 h4 h7 ... ]

x(n)

SubFilter2 [ h2 h5 h8 ... ]

z(m+1)

MX

y(k)

RG

z(m+2)

3×f0 / 2

CT 3

CLK

×3

f0

M

:2

3×f0

R

f0

X

x(0)

x(1)

x(2)

3f0

Z

z(0)

z(1)

z(2)

z(3)

z(4)

z(5)

z(6)

z(7)

3f0/2

Y

y(0) = z(0)

y(1) = z(2)

y(2) = z(4)

y(3) = z(6)

64

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

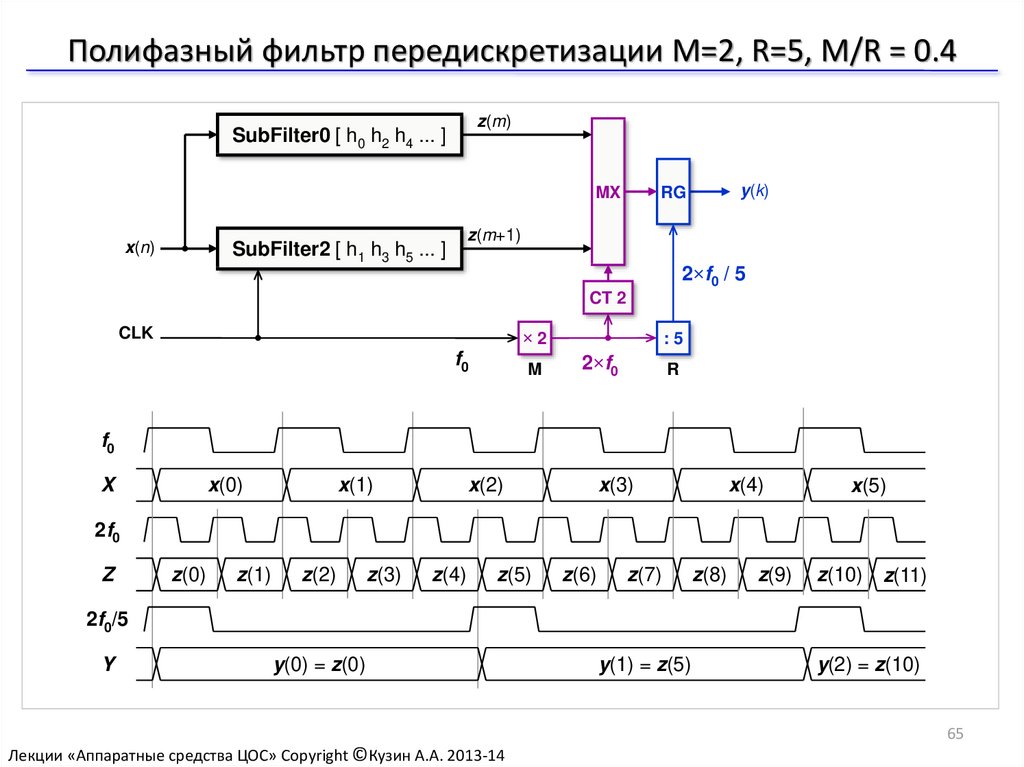

65. Полифазный фильтр передискретизации M=2, R=5, M/R = 0.4

z(m)SubFilter0 [ h0 h2 h4 ... ]

MX

x(n)

y(k)

RG

z(m+1)

SubFilter2 [ h1 h3 h5 ... ]

2×f0 / 5

CT 2

CLK

×2

f0

M

:5

2×f0

R

f0

X

x(0)

x(1)

x(2)

x(3)

x(4)

x(5)

2f0

Z

z(0)

z(1)

z(2)

z(3)

z(4)

z(5)

z(6)

z(7)

z(8)

z(9)

z(10)

z(11)

2f0/5

Y

y(0) = z(0)

y(1) = z(5)

y(2) = z(10)

65

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

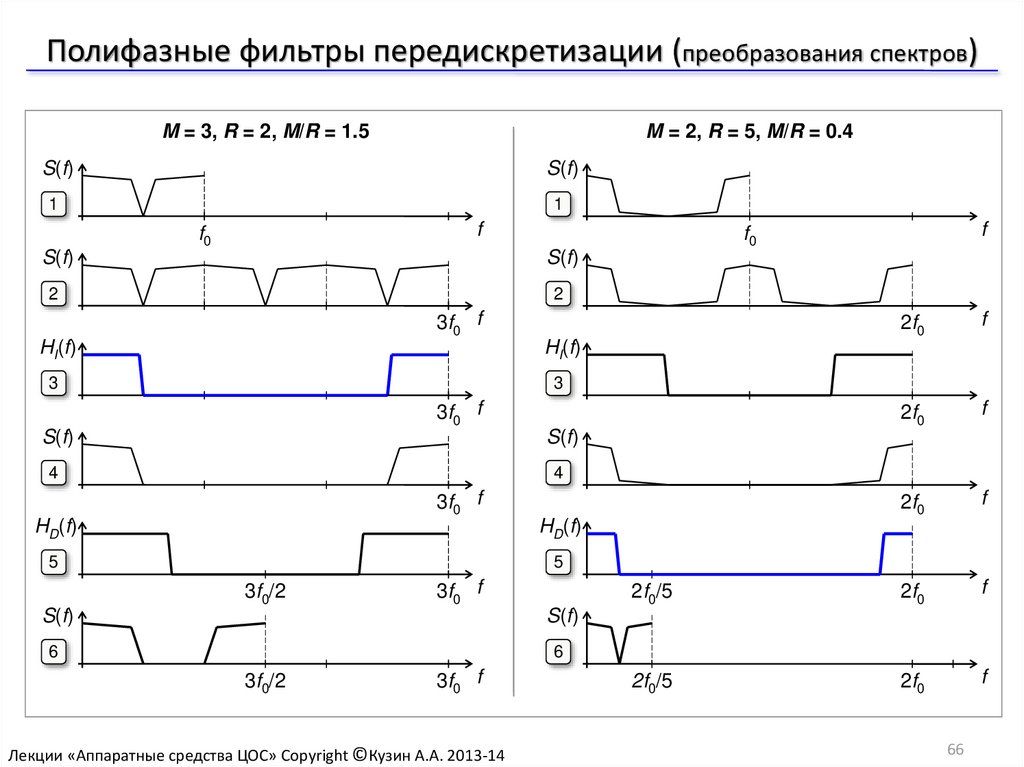

66. Полифазные фильтры передискретизации (преобразования спектров)

M = 3, R = 2, M/R = 1.5M = 2, R = 5, M/R = 0.4

S(f)

S(f)

1

1

f

f0

S(f)

S(f)

2

2

3f0 f

HI(f)

HI(f)

3

3

2f0

f

2f0

f

2f0

f

2f0/5

2f0

f

2f0/5

2f0

f

3f0 f

S(f)

S(f)

4

4

3f0 f

HD(f)

HD(f)

5

5

3f0/2

3f0 f

S(f)

S(f)

6

6

3f0/2

3f0 f

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

f

f0

66

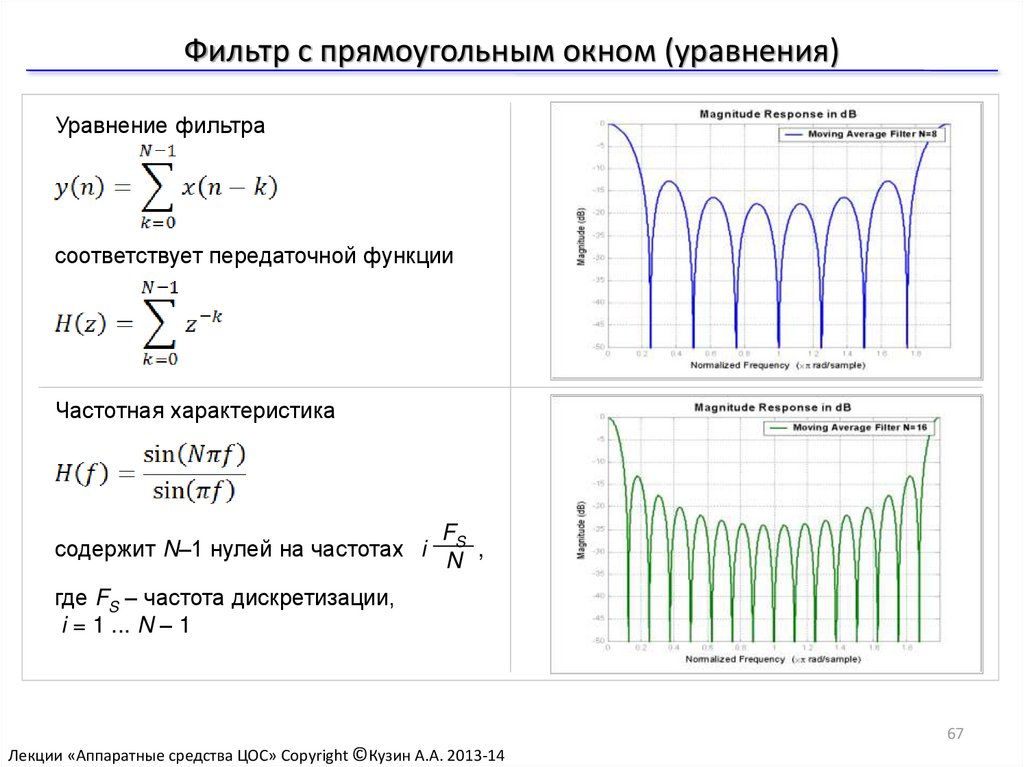

67. Фильтр с прямоугольным окном (уравнения)

Уравнение фильтрасоответствует передаточной функции

Частотная характеристика

содержит N–1 нулей на частотах i

FS

,

N

где FS – частота дискретизации,

i = 1 ... N – 1

67

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

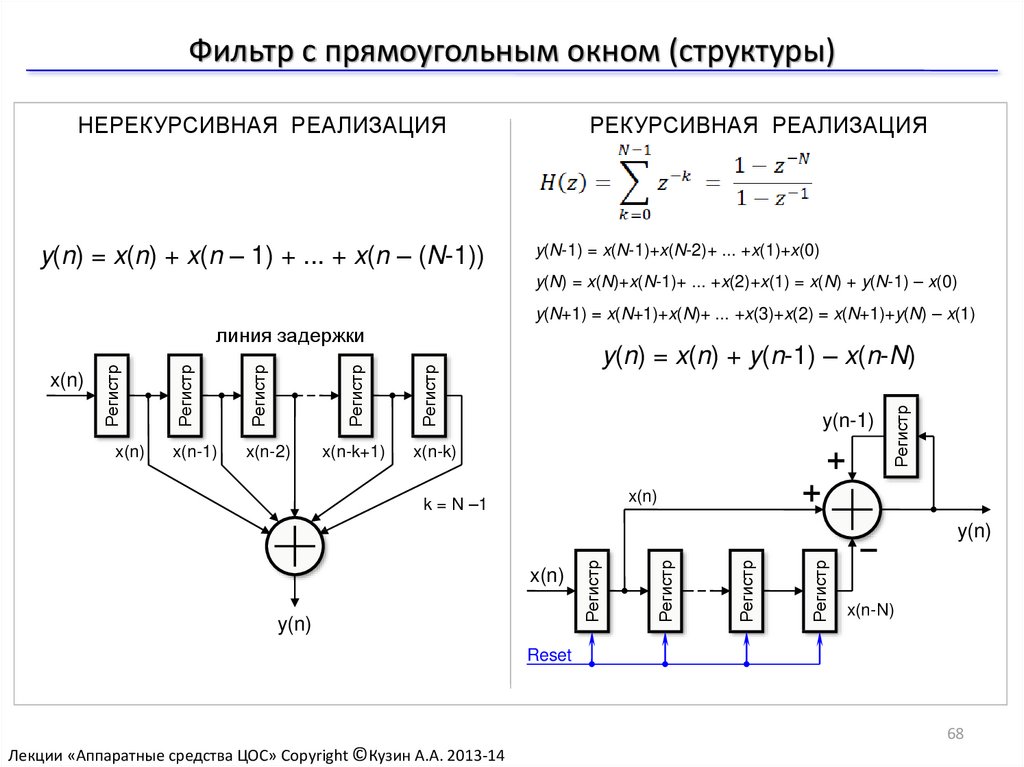

68. Фильтр с прямоугольным окном (структуры)

НЕРЕКУРСИВНАЯ РЕАЛИЗАЦИЯy(n) = x(n) + x(n – 1) + ... + x(n – (N-1))

РЕКУРСИВНАЯ РЕАЛИЗАЦИЯ

y(N-1) = x(N-1)+x(N-2)+ ... +x(1)+x(0)

y(N) = x(N)+x(N-1)+ ... +x(2)+x(1) = x(N) + y(N-1) – x(0)

y(N+1) = x(N+1)+x(N)+ ... +x(3)+x(2) = x(N+1)+y(N) – x(1)

x(n-2)

x(n-k+1)

y(n-1)

x(n-k)

Регистр

x(n-1)

y(n) = x(n) + y(n-1) – x(n-N)

Регистр

Регистр

Регистр

x(n)

Регистр

x(n)

Регистр

линия задержки

x(n)

k = N –1

Регистр

Регистр

y(n)

Регистр

x(n)

Регистр

y(n)

x(n-N)

Reset

68

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

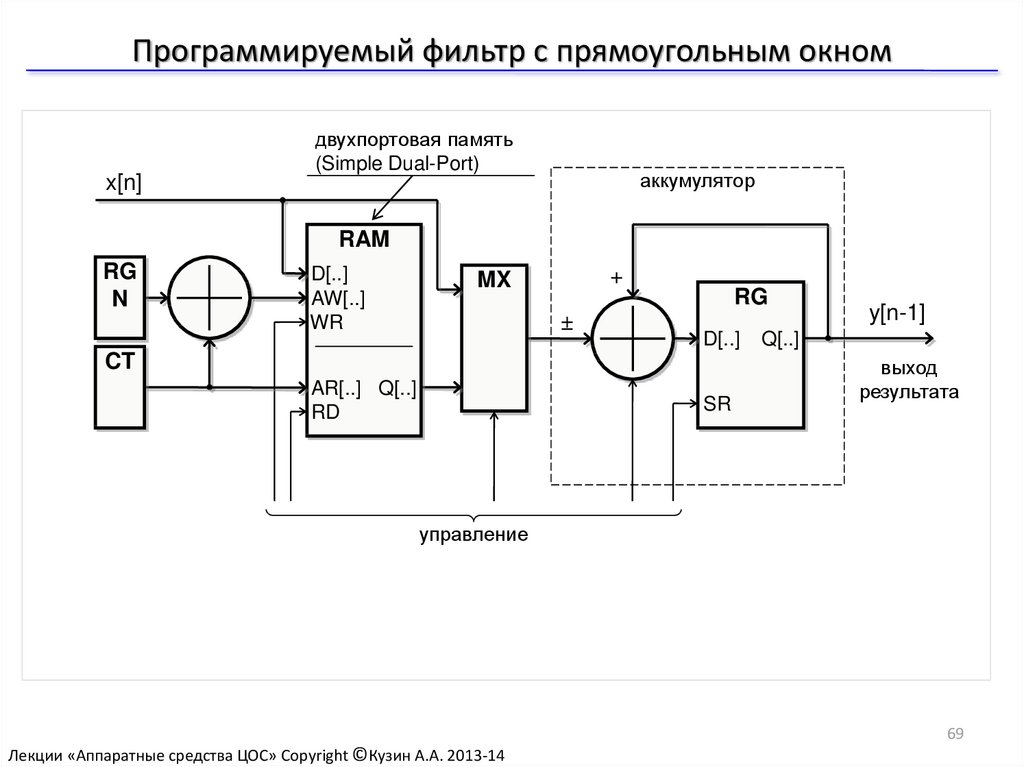

69. Программируемый фильтр с прямоугольным окном

x[n]двухпортовая память

(Simple Dual-Port)

аккумулятор

RAM

RG

N

D[..]

AW[..]

WR

+

MX

RG

D[..]

CT

AR[..] Q[..]

RD

SR

y[n-1]

Q[..]

выход

результата

управление

69

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

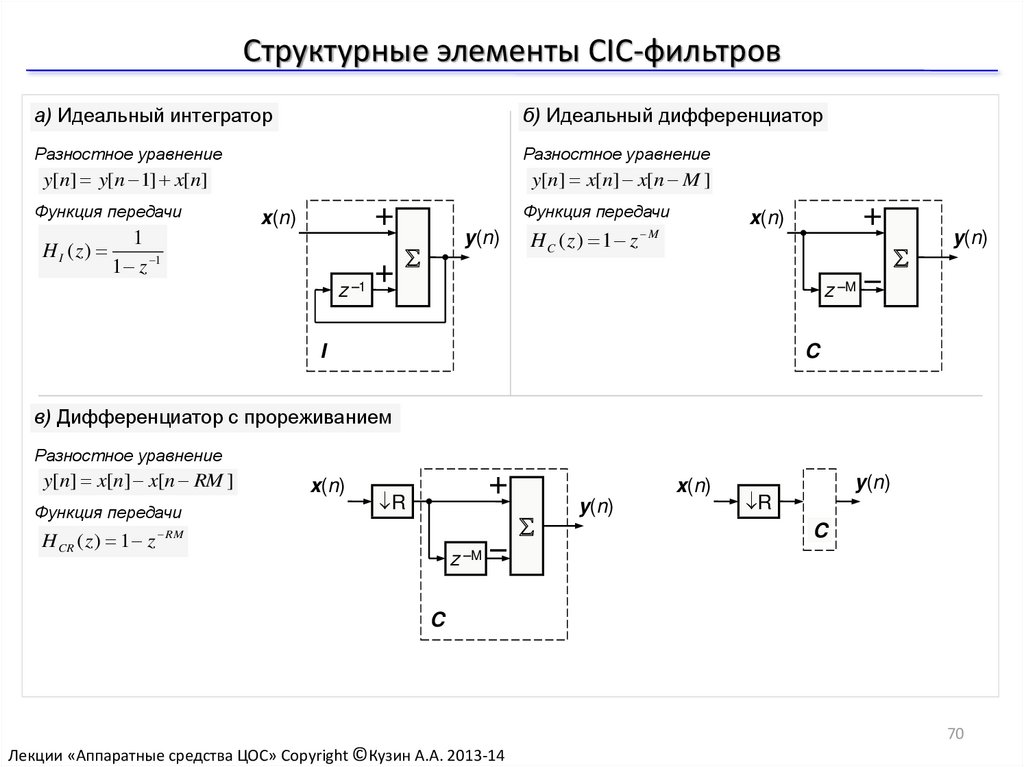

70. Структурные элементы CIC-фильтров

а) Идеальный интеграторб) Идеальный дифференциатор

Разностное уравнение

Разностное уравнение

y[n] y[n 1] x[n]

y[n] x[n] x[n M ]

Функция передачи

H I ( z)

Функция передачи

x(n)

1

1 z 1

y(n)

H C ( z) 1 z

x(n)

M

z –1

y(n)

z –M

I

C

в) Дифференциатор с прореживанием

Разностное уравнение

y[n] x[n] x[n RM ]

Функция передачи

x(n)

x(n)

R

H CR ( z ) 1 z RM

y(n)

y(n)

R

C

z –M

C

70

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

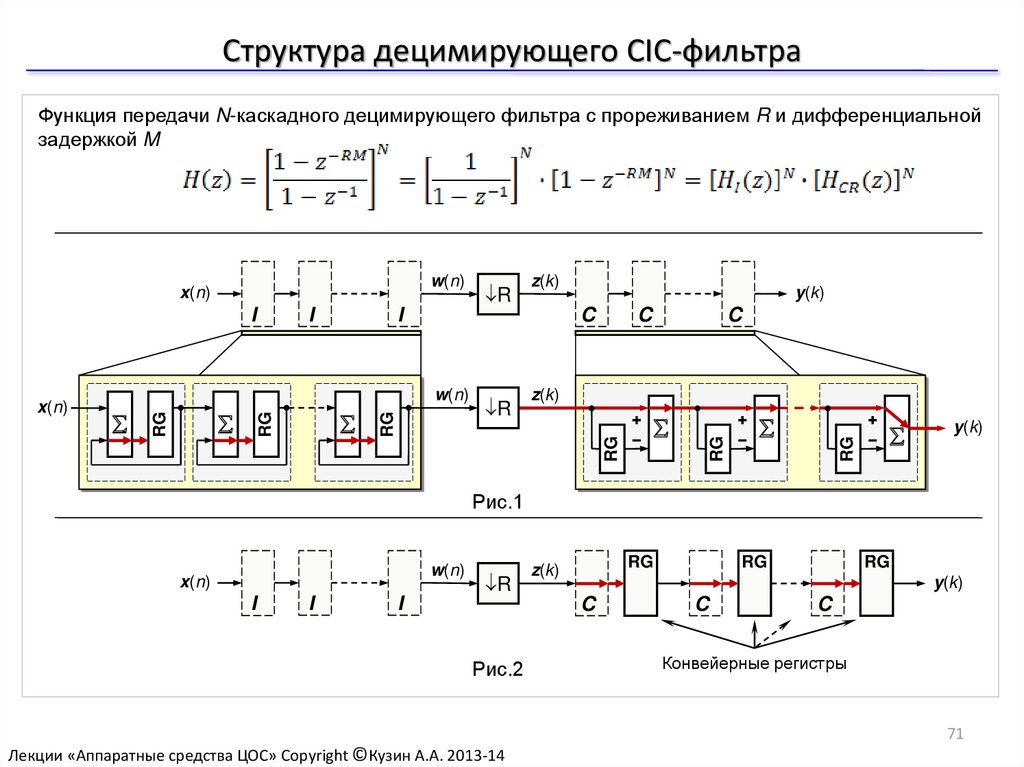

71. Структура децимирующего CIC-фильтра

Функция передачи N-каскадного децимирующего фильтра с прореживанием R и дифференциальнойзадержкой M

I

C

R

C

z(k)

RG

RG

RG

y(k)

C

w(n)

RG

x(n)

I

z(k)

RG

I

R

RG

w(n)

x(n)

y(k)

Рис.1

w(n)

x(n)

I

I

R

I

RG

z(k)

RG

y(k)

C

Рис.2

RG

C

C

Конвейерные регистры

71

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

72. Компенсация переполнения в CIC-дециматоре

4 (01002)5 (01012)

3 (00112)

6 (01102)

2 (00102)

7 (01112)

1 (00012)

–8 (10002)

0 (00002)

–7 (10012)

–1 (11112)

–6 (10102)

–2 (11102)

–5 (10112)

–3 (11012)

–4 (11002)

72

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

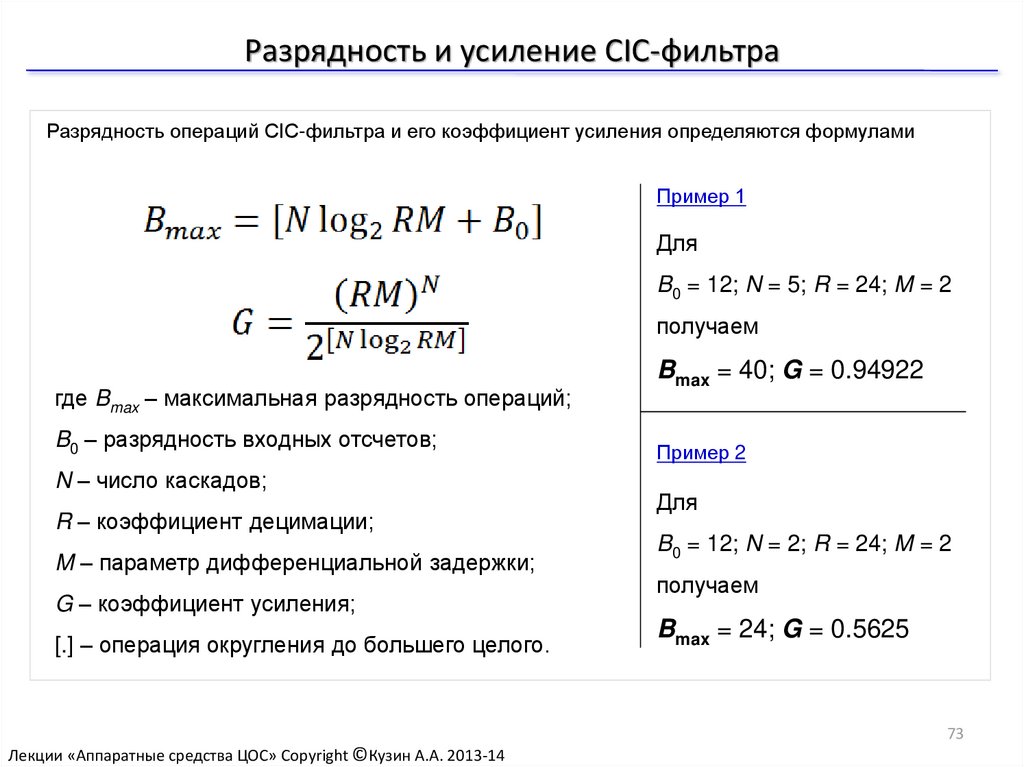

73. Разрядность и усиление CIC-фильтра

Разрядность операций CIC-фильтра и его коэффициент усиления определяются формуламиПример 1

Для

B0 = 12; N = 5; R = 24; M = 2

получаем

где Bmax – максимальная разрядность операций;

B0 – разрядность входных отсчетов;

N – число каскадов;

R – коэффициент децимации;

M – параметр дифференциальной задержки;

G – коэффициент усиления;

[.] – операция округления до большего целого.

Bmax = 40; G = 0.94922

Пример 2

Для

B0 = 12; N = 2; R = 24; M = 2

получаем

Bmax = 24; G = 0.5625

73

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

74.

74Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

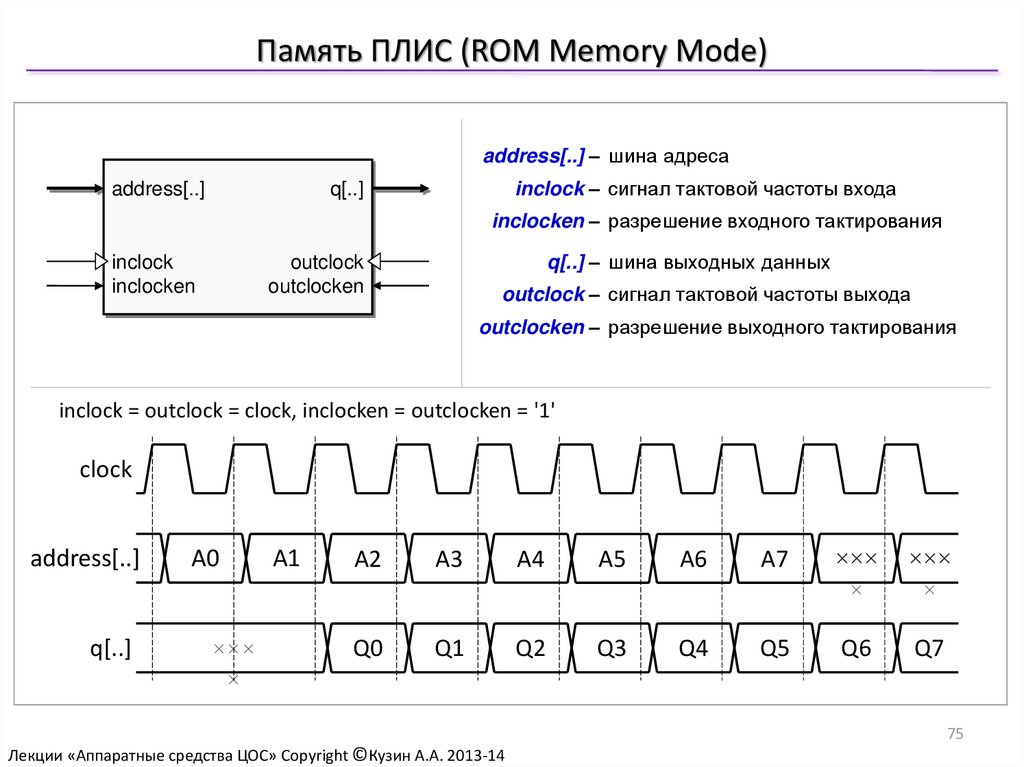

75. Память ПЛИС (ROM Memory Mode)

address[..] – шина адресаaddress[..]

inclock – сигнал тактовой частоты входа

q[..]

inclocken – разрешение входного тактирования

inclock

inclocken

q[..] – шина выходных данных

outclock

outclocken

outclock – сигнал тактовой частоты выхода

outclocken – разрешение выходного тактирования

inclock = outclock = clock, inclocken = outclocken = '1'

clock

address[..]

q[..]

A0

×××

×

A1

A2

A3

A4

A5

A6

A7

×××

×

×××

×

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

75

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

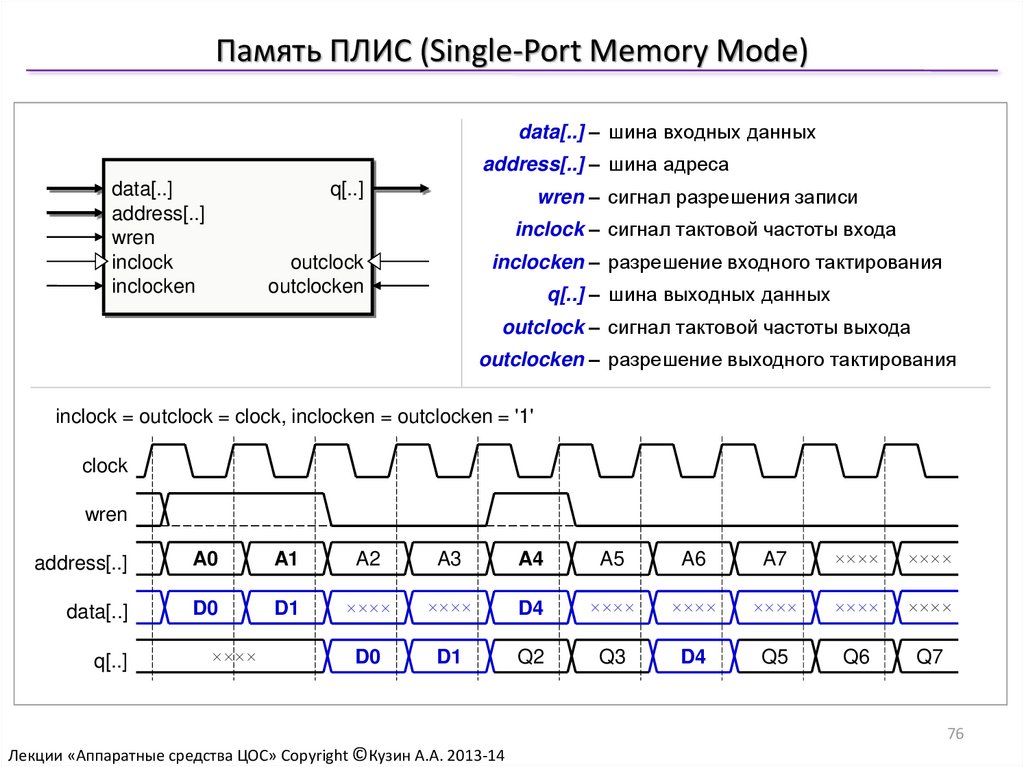

76. Память ПЛИС (Single-Port Memory Mode)

data[..] – шина входных данныхaddress[..] – шина адреса

data[..]

address[..]

wren

inclock

inclocken

q[..]

wren – сигнал разрешения записи

inclock – сигнал тактовой частоты входа

inclocken – разрешение входного тактирования

outclock

outclocken

q[..] – шина выходных данных

outclock – сигнал тактовой частоты выхода

outclocken – разрешение выходного тактирования

inclock = outclock = clock, inclocken = outclocken = '1'

clock

wren

address[..]

A0

A1

A2

A3

A4

A5

A6

A7

××××

××××

data[..]

D0

D1

××××

××××

D4

××××

××××

××××

××××

××××

D0

D1

Q2

Q3

D4

Q5

Q6

Q7

q[..]

××××

76

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

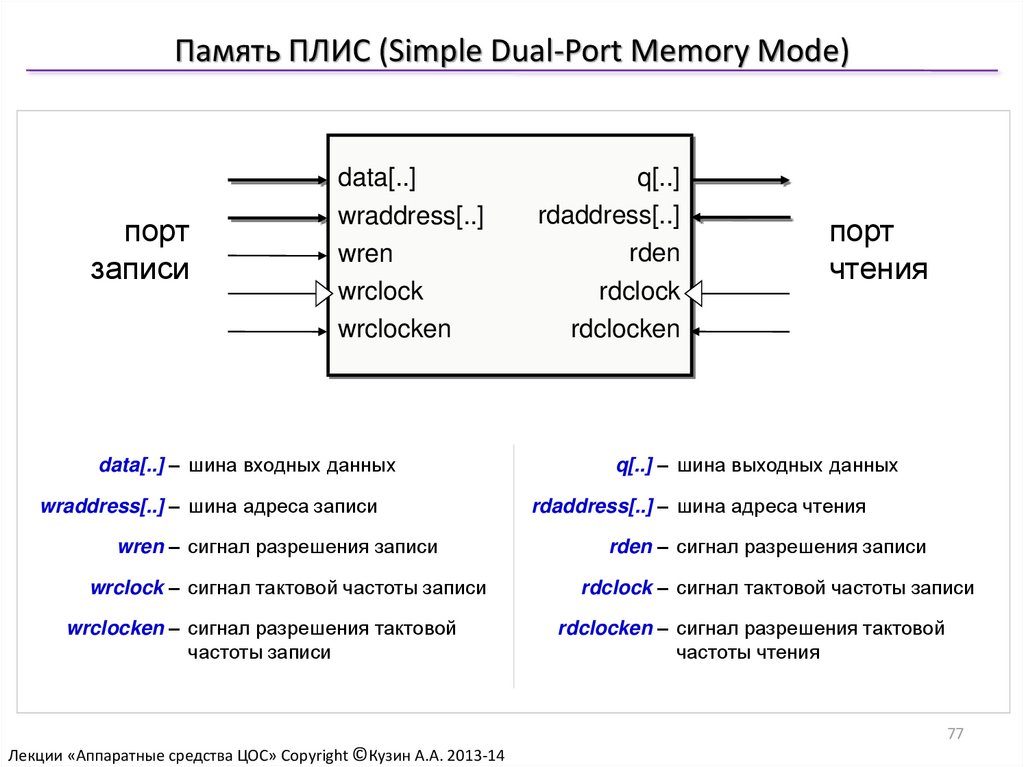

77. Память ПЛИС (Simple Dual-Port Memory Mode)

портзаписи

data[..]

wraddress[..]

wren

wrclock

wrclocken

data[..] – шина входных данных

wraddress[..] – шина адреса записи

wren – сигнал разрешения записи

wrclock – сигнал тактовой частоты записи

wrclocken – сигнал разрешения тактовой

частоты записи

q[..]

rdaddress[..]

rden

rdclock

rdclocken

порт

чтения

q[..] – шина выходных данных

rdaddress[..] – шина адреса чтения

rden – сигнал разрешения записи

rdclock – сигнал тактовой частоты записи

rdclocken – сигнал разрешения тактовой

частоты чтения

77

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

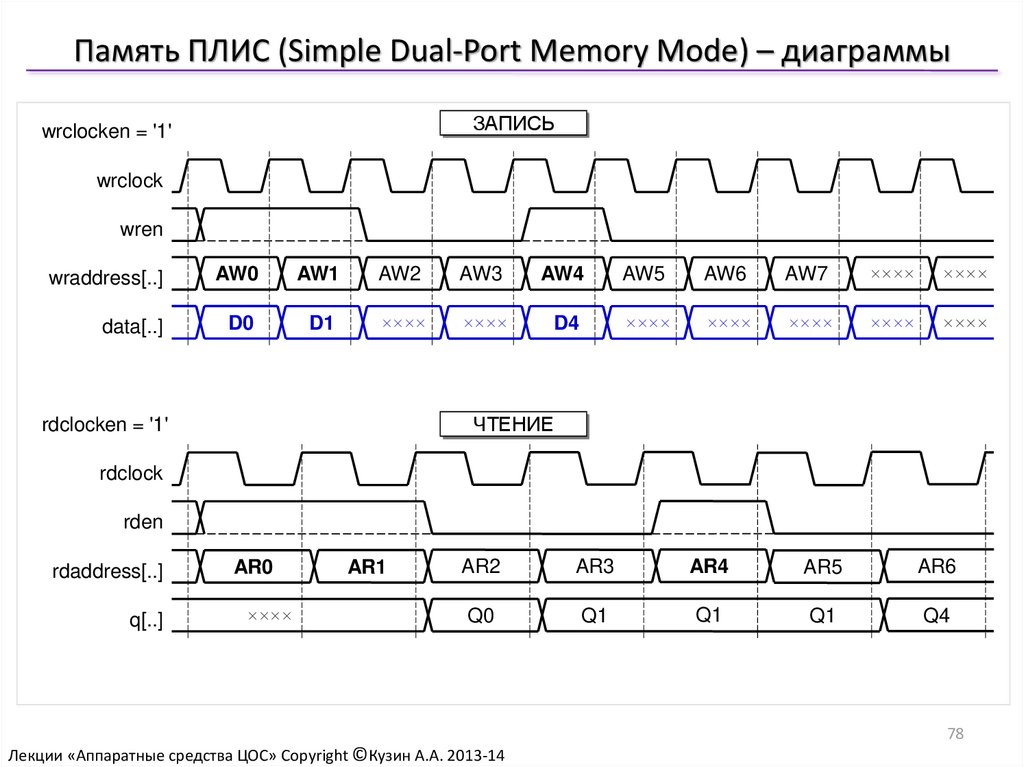

78. Память ПЛИС (Simple Dual-Port Memory Mode) – диаграммы

ЗАПИСЬwrclocken = '1'

wrclock

wren

wraddress[..]

AW0

AW1

AW2

AW3

AW4

AW5

AW6

AW7

××××

××××

data[..]

D0

D1

××××

××××

D4

××××

××××

××××

××××

××××

ЧТЕНИЕ

rdclocken = '1'

rdclock

rden

rdaddress[..]

q[..]

AR0

××××

AR1

AR2

AR3

AR4

AR5

AR6

Q0

Q1

Q1

Q1

Q4

78

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

79. Память ПЛИС (True Dual-Port Memory Mode)

порт Аdata_a[..]

address_a[..]

wren_a

clock_a

enable_a

q_a[..]

data_a[..] – шина входных данных

address_a[..] – шина адреса

data_b[..]

address_b[..]

wren_b

clock_b

enable_b

q_b[..]

порт В

data_b[..] – шина входных данных

address_b[..] – шина адреса

wren_a – сигнал разрешения записи

wren_b – сигнал разрешения записи

clock_a – сигнал тактовой частоты

clock_b – сигнал тактовой частоты

enable_a – сигнал разрешения тактирования

q_a[..] – шина выходных данных

enable_b – сигнал разрешения тактирования

q_b[..] – шина выходных данных

79

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

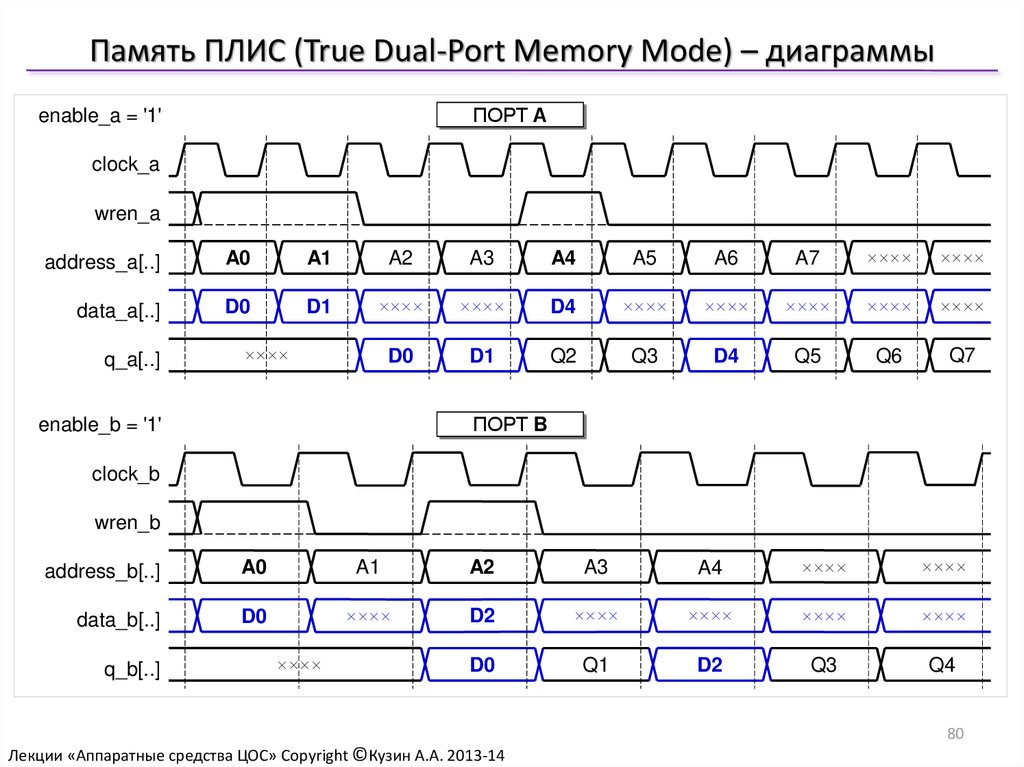

80. Память ПЛИС (True Dual-Port Memory Mode) – диаграммы

ПОРТ Аenable_a = '1'

clock_a

wren_a

address_a[..]

A0

A1

A2

A3

A4

A5

A6

A7

××××

××××

data_a[..]

D0

D1

××××

××××

D4

××××

××××

××××

××××

××××

D0

D1

Q2

Q3

D4

Q5

Q6

Q7

q_a[..]

××××

ПОРТ B

enable_b = '1'

clock_b

wren_b

address_b[..]

A0

A1

A2

A3

A4

××××

××××

data_b[..]

D0

××××

D2

××××

××××

××××

××××

D0

Q1

D2

Q3

Q4

q_b[..]

××××

80

Лекции «Аппаратные средства ЦОС» Copyright ©Кузин А.А. 2013-14

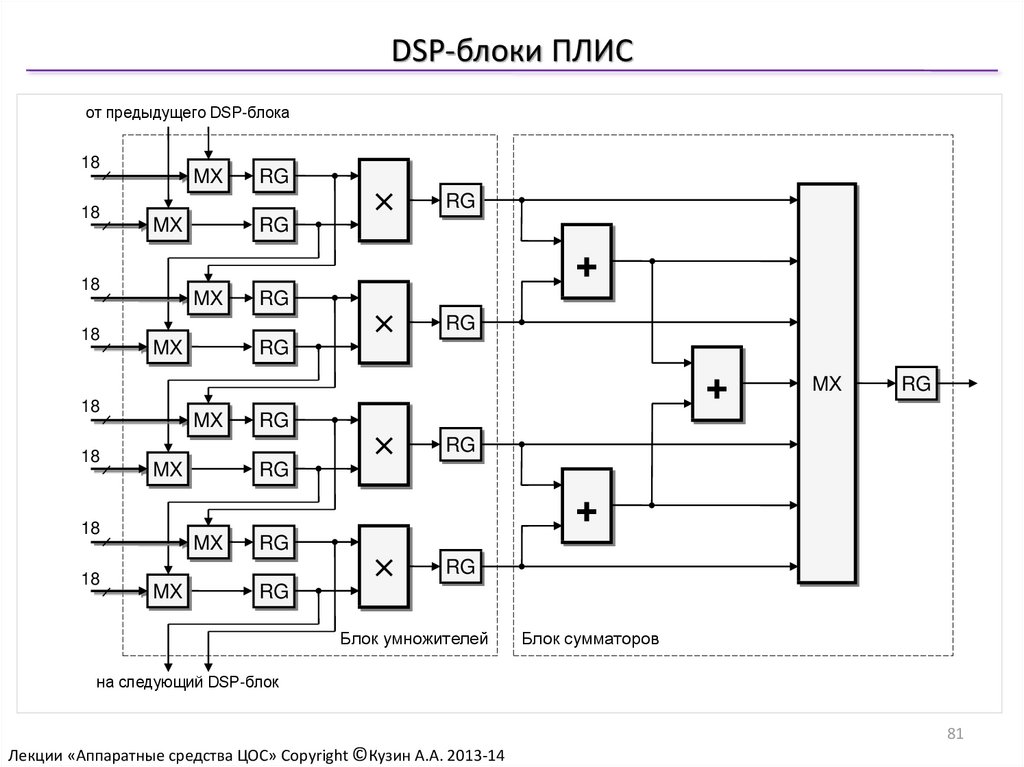

81. DSP-блоки ПЛИС

от предыдущего DSP-блока18

18

MX

MX

MX

MX

RG

RG

MX

MX

×

RG

RG

RG

×

MX

RG

RG

+