Similar presentations:

Архитектура вычислительных систем реального времени

1.

В.И. ЖабинАРХИТЕКТУРА ВЫЧИСЛИТЕЛЬНЫХ

СИСТЕМ РЕАЛЬНОГО ВРЕМЕНИ

Киев ТОО "ВЕК +"

2003

2.

ББК 84Р7Ж12

УДК 681.3

Ответственный за выпуск Стиренко С.Г.

Рецензенты: Жуков И.А., доктор технических наук, профессор,

заведующий кафедрой вычислительной техники Национального авиационного университета Украины;

Тарасенко В.П., доктор технических наук, профессор,

заведующий кафедрой специализированных компьютерных систем Национального технического университета

Украины "КПИ"

Жабин В.И.

Ж12 Архитектура вычислительных систем реального времени / В.И. Жабин, — К.: ВЕК +, 2003. – 176 с., ил.

ISBN 966–7140–21–0

Рассматриваются вопросы повышения эффективности мультипроцессорных вычислительных систем реального времени. Предложен комплексный подход к организации параллельных вычислительных процессов и

масштабирования производительности систем с использованием концепции

модульной организации аппаратніх средств. Проанализированы возникающие при этом проблемы и предложены пути их решения. Показана эффективность совместного использования классической и потоковой моделей

вычислений при реализации параллельных алгоритмов. Приведены примеры организации модульных вычислительных систем.

Для научных работников и специалистов, занимающихся вопросами организации вычислительных процессов в параллельных системах.

ББК 84Р7

ISBN 966–7140–21–0

Жабин В.И., 2003

3.

ГЛАВА 2КЛАССИФИКАЦИЯ И ЯЗЫКИ ОПИСАНИЯ

АРХИТЕКТУРЫ ВЫЧИСЛИТЕЛЬНЫХ СИСТЕМ

2.1. Классификация параллельных систем

В процессе развития ВС было предложено много разнообразных параллельных структур, часть из которых была реализована. По мере увеличения числа и разнообразия структур их классификация становится важным этапом при разработке новых проектов. Она позволяет выявить недостатки и определить пути повышения эффективности систем.

Как отмечалось в разделе 1.2, одной из наиболее широко известных и

часто используемых является классификация Флинна [22]. Данная классификация учитывает только характер взаимодействия в системе потоков

команд и данных. В связи с этим в один класс попадают системы, которые

существенно отличаются по архитектуре, не говоря о структурных отличиях и способах взаимодействия устройств. В ряде работ классы по Флинну

рассматириваются более детально. Например, классификация по Джонсону

[35] разделяет класс MIMD на четыре подкласса в зависимости от организации памяти и способа передачи данных между процессорами:

общая память – разделяемые переменные (GMSV);

распределенная память – разделяемые переменные (DMSV);

распределенная память – передача сообщений (DMMP);

общая память – передача сообщений (GMMP).

Другой подход к классификации, претендующий на универсальность,

связан с количественными характеристиками систем.

Классификация систем по Фенгу [36] использует две характеристики:

количество параллельно обрабатываемых слов (m);

число разрядов данных (n), которые обрабатываются параллельно

в устройстве обработки данных.

Тип системы в этом случае отображается точкой на плоскости. По

осям координат откладываются значения m и n. Возможна запись в виде

формулы СИСТЕМА=(m,n). Например, 16-процессорная система C.mmp, в

которой каждый процессор обрабатывает 16-разрядные слова, отображается точкой (16, 16). Это записывается в виде C.mmp=(16, 16). Матричный

процессор ILLIAC-IV можно определить как ILLIAC-IV=(64, 64). Классификация дает только общее представление о структуре и степени параллелизма, но не отражает организацию коммуникационной среды и ряда

структурных особенностей систем, в том числе, наличие конвейерной обработки. Например, система TIASC содержит 4 конвейера на 8 этапов и 64

разряда каждый. Это отображается в виде TIASC(64, 2048). Число 2048

4.

Глава 2. Классификация и языки описания архитектуры систем17

получено как произведение 4 8 64, но оно может быть получено и другим

образом, например, 8 8 32.

Классификация Хендлера [37] основана на рассмотрении трех характеристик:

количество устройств управления (c);

число арифметико-логических устройств (a);

количество логических секций (w), каждая из которых обрабатывает один разрядный срез слов данных в арифметико-логическом

устройстве.

В данном случае система представляется точкой в трехмерном пространстве и записывается в форме СИСТЕМА=(c,a,w). Характеристика a

показывает, сколько арифметико-логических устройств связано с одним

устройством управления. Учитывая это, получим C.mmp=(16, 1, 16) и

ILLIAC-IV=(1, 64, 64). В отличие от классификации Фенга параллельные

структуры описываются более подробно. Появляется возможность указать

число устройств обработки данных, которые работают под управлением

одного потока команд (одного устройства управления). Однако отразить

особенности коммуникационной среды и наличие конвейера на рассматриваемых уровнях также не представляется возможным.

Для отображения наличия конвейерной обработки информации на различных уровнях Валяхом предложено расширить классификацию Хандлера

введением дополнительных характеристик на соответствующих уровнях

обработки информации, а именно: c’, a’ и w’ [15]. Каждая из введенных

характеристик показывает число этапов конвейера на данном уровне. В

этом случае системы отображаются в виде СИСТЕМА(c c’, a a’, w w’).

Например, систему TIASC, в которой используется конвейерная обработка,

можно теперь охарактеризовать более полно, а именно – TIASC(1, 4, 64 8).

Тем не менее, данная классификация дает только общее представление о

структуре систем, причем, возникают трудности при описании неоднородных систем.

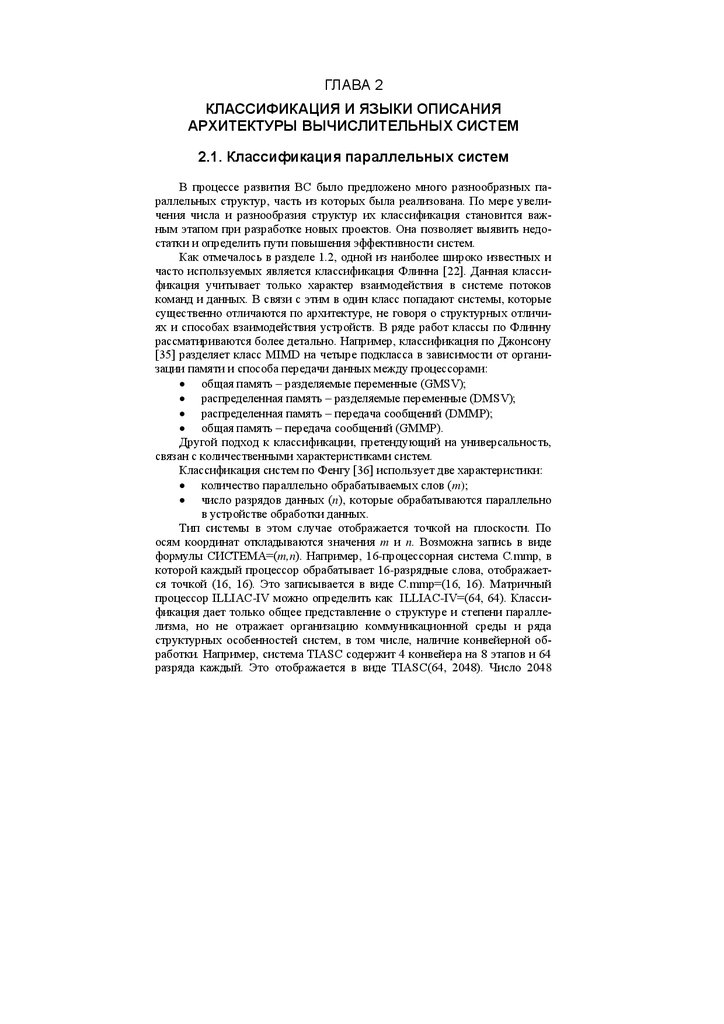

Одной из ранних попыток классификации систем в соответствии с их

структурой можно считать работу Шора [38]. В соответствии с указанной

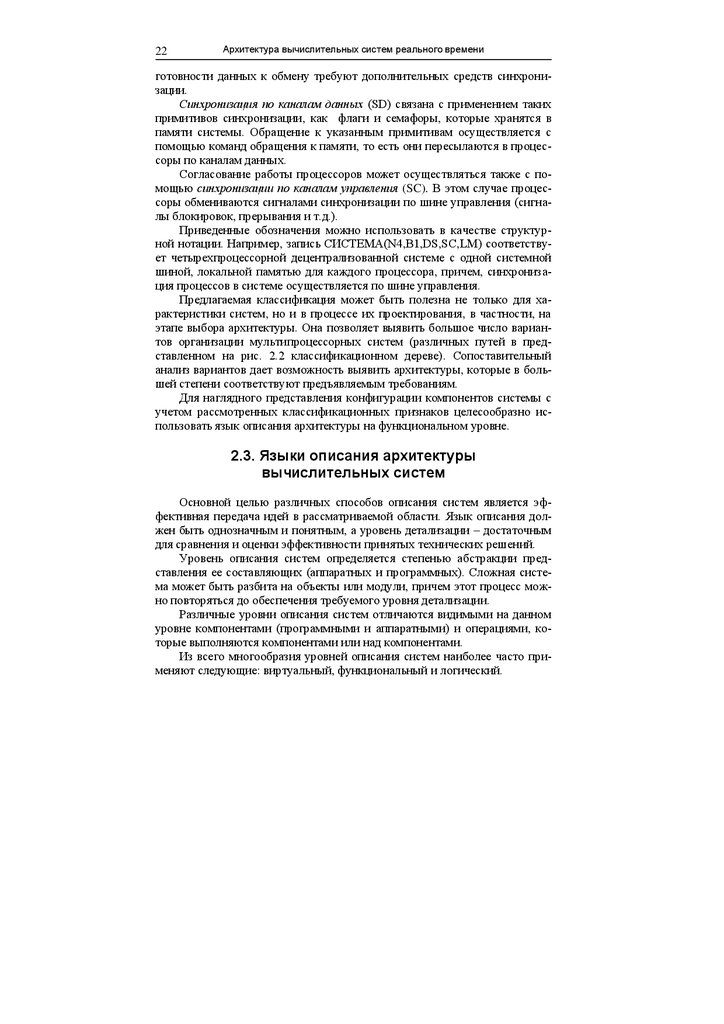

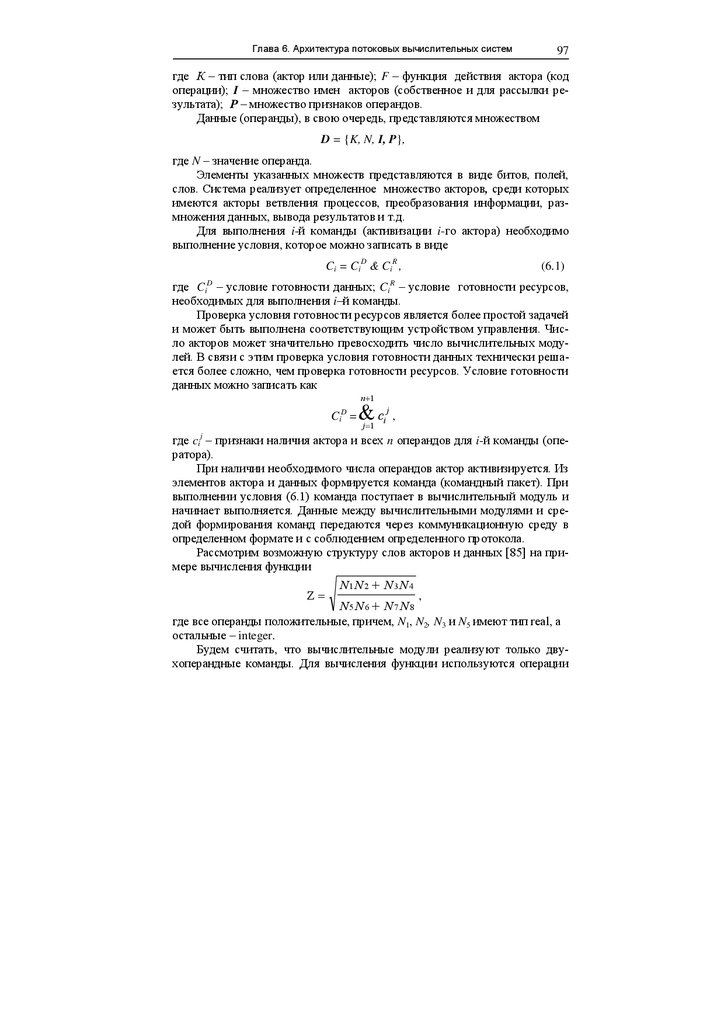

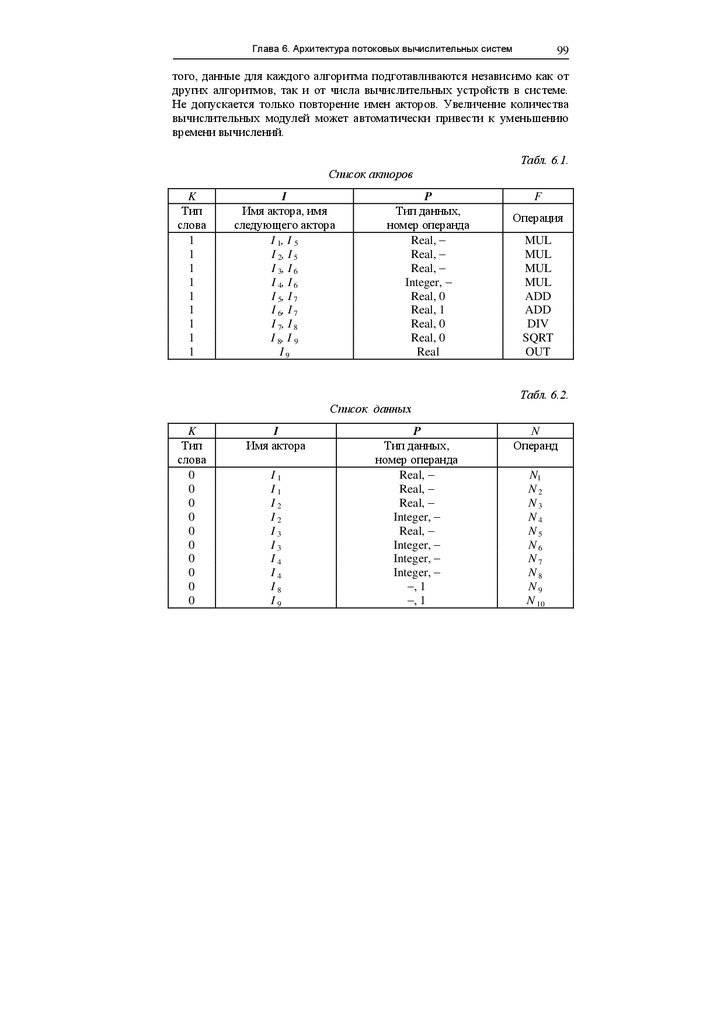

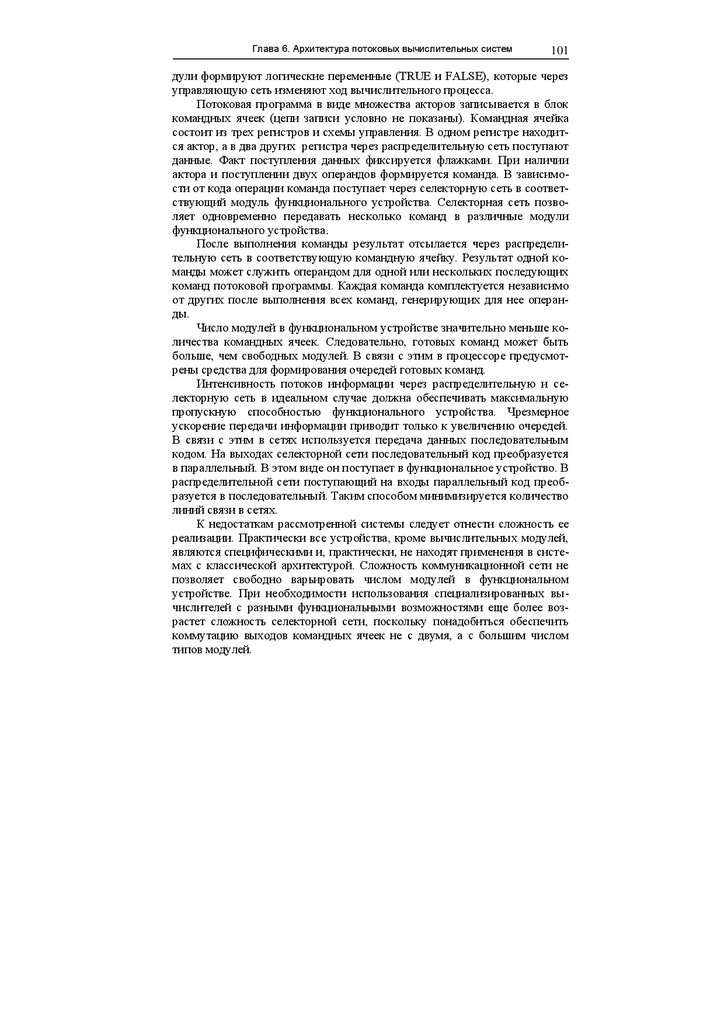

классификацией различают шесть классов систем (базовых машин), представленных на рис. 2.1. Системы отличаются способом соединения основных устройств, в качестве которых рассматриваются устройства управления (УУ), операционные устройства (ОУ) и память. При этом память с УУ

обменивается словами, а с ОУ – словами (вертикальный доступ) или разрядными срезами слов (горизонтальный доступ). В связи с этим память

рассматривается раздельно для команд (ПК) и данных (ПД).

Машины класса I соответствуют классу SISD по Флинну. Это архитектура фон Неймана с одним УУ и одним ОУ. Никаких ограничений на внутреннюю организацию ОУ не накладывается. В связи с этим, например,

конвейерную машину CDC 7600 относят к данному классу.

5.

18Архитектура вычислительных систем реального времени

Машины II – это модификация класса машин I, касающаяся обработки

данных. В таких машинах ОУ реализуют методы последовательной арифметики. Представителем данного класса является система STARAN. К

классу III относят машины, которые могут обрабатывать как считываемые

из ПД слова, так и разрядные срезы слов (комбинация машин I и II). ПД

должна быть организована в виде двухмерного массива.

ПК

УУ

ПК

ПК

ОУ

УУ

УУ

ОУ

ПД

ОУ

ОУ

ПД

I

ПД

II

УУ

ОУ

ОУ

III

УУ

ОУ

ОУ

ОУ

УУ

ОУ

ОУ

ПД

ПД

ПД

IV

ПД

ПД

ПД

V

ПД

VI

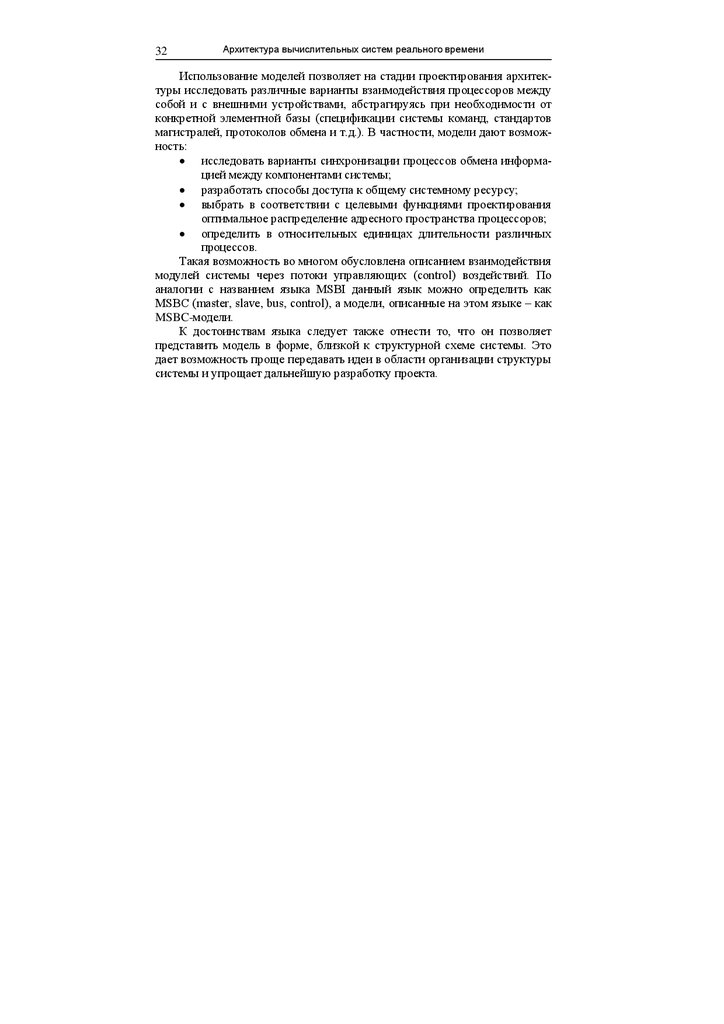

Рис. 2.1. Схематическое представление классов систем

Машины IV и V являются фактически разновидностями класса SIMD

по Флинну. Все ОУ (процессорные элементы) управляются одним УУ.

Один поток команд реализует преобразование нескольких потоков данных

в разных ОУ. Машины V обладают более широкими функциональными

возможностями, поскольку в них предусмотрен обмен информацией между

соседними ОУ. К классу IV относится система PEPE, а в классу V –

ILLIAC-IV.

Машины класса VI имеют память данных, которая выполняет функции

среды обработки информации (память со встроенной логикой, функциональная память). К данному классу относятся, в частности, ассоциативные

процессоры.

Данная классификация, хотя и учитывает некоторые структурные признаки систем, ограничивает круг систем проектами, которые были известны на момент разработки классификации. Кроме того, существуют системы, которые нельзя однозначно отнести к одному классу, а некоторые системы остаются вообще вне данной классификации. В первую очередь это

относится к системам MIMD, представляющим в настоящее время многочисленный класс параллельных систем.

К издержкам универсальности рассмотренных классификаций можно

отнести то, что в один класс попадает множество структур, отличающихся

6.

Глава 2. Классификация и языки описания архитектуры систем19

способом обмена информацией между компонентами систем, организацией

коммуникационной среды и рядом других структурных особенностей.

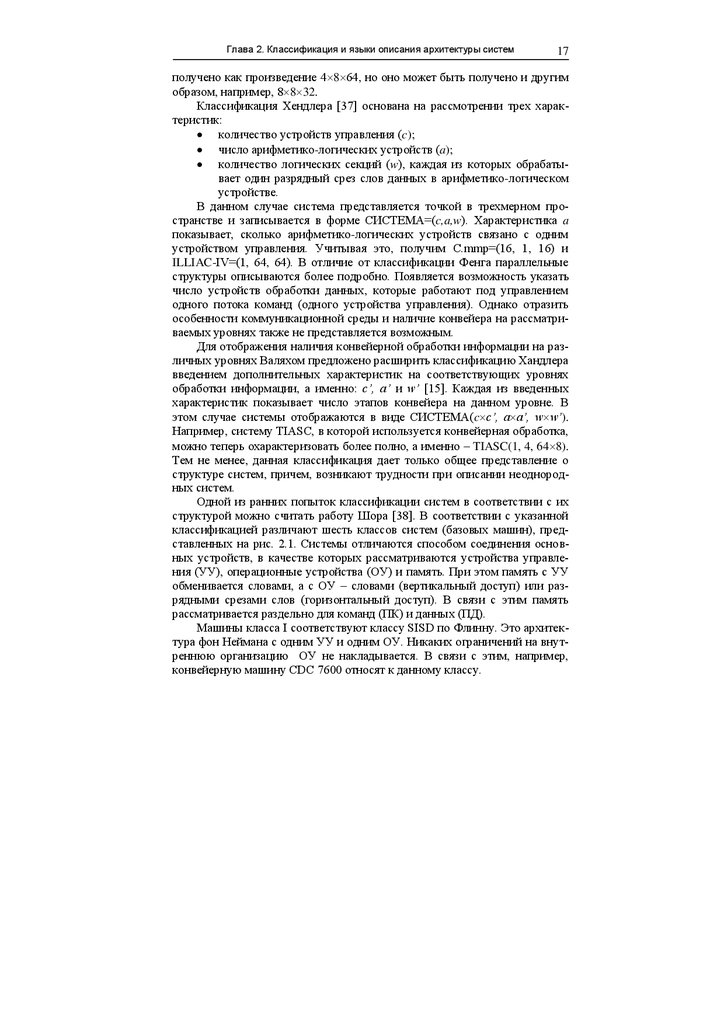

2.2. Структурная классификация систем

с магистральной топологией

Рассмотрим классификацию систем MIMD с шинной топологией.

Учитывая, что современный подход к проектированию систем предполагает максимальное применение готовых компонентов (off-the-shelf), основное

внимание будем уделять взаимодействию компонентов, а не их внутренней

организации (наличие уровней конвейерной обработки, построение арифметико-логических цепей, внутренней памяти и т.д.). Эффективность МВС,

зависит не только от количества тех или иных устройств и их характеристик. На эффективность реализации вычислительных процессов существенное влияние оказывают такие структурные признаки систем:

принцип управления (централизованный или децентрализованный);

число магистралей (каналов, шин) обмена информацией;

распределение адресного пространства процессоров;

способы доступа к различным областям памяти процессоров;

способы синхронизации процессов при обмене информацией между процессорами и доступе к общему системному ресурсу.

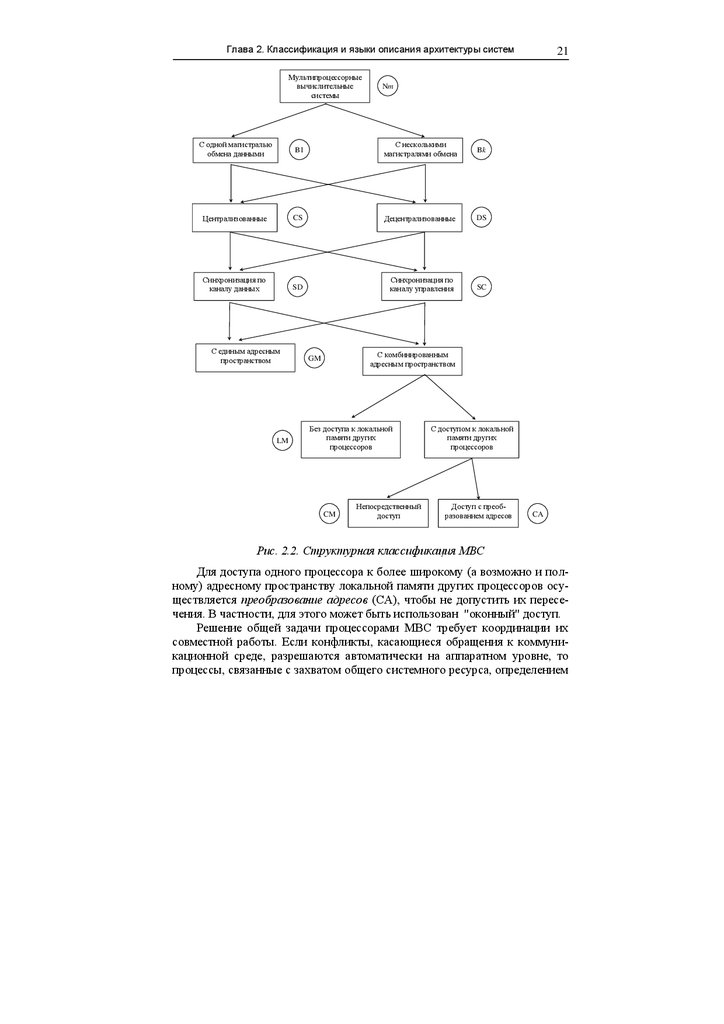

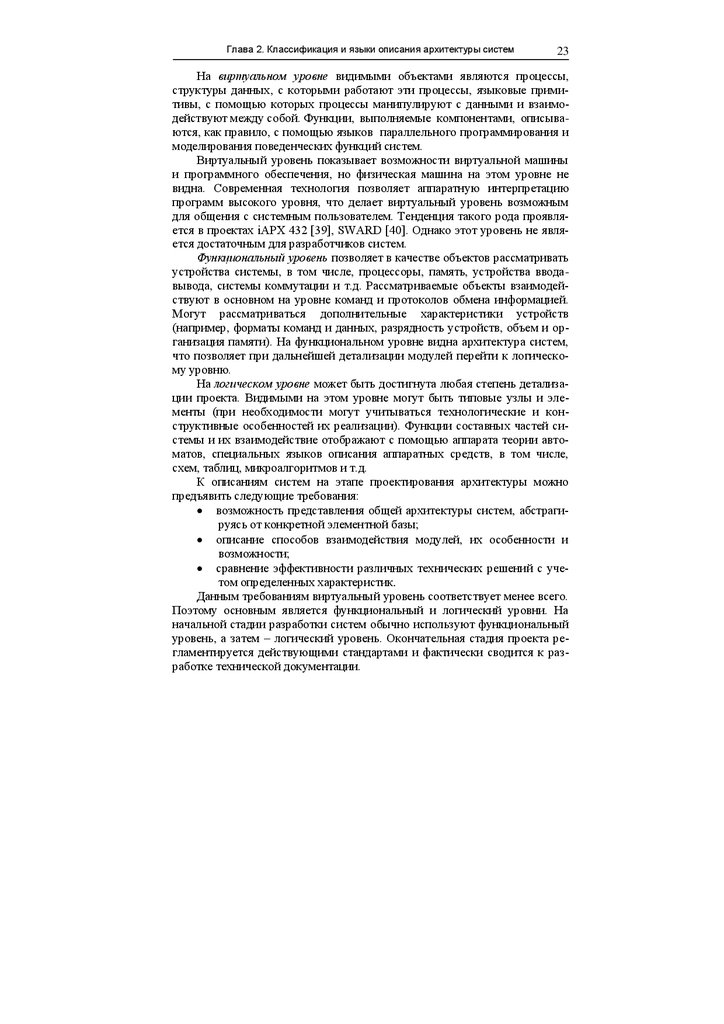

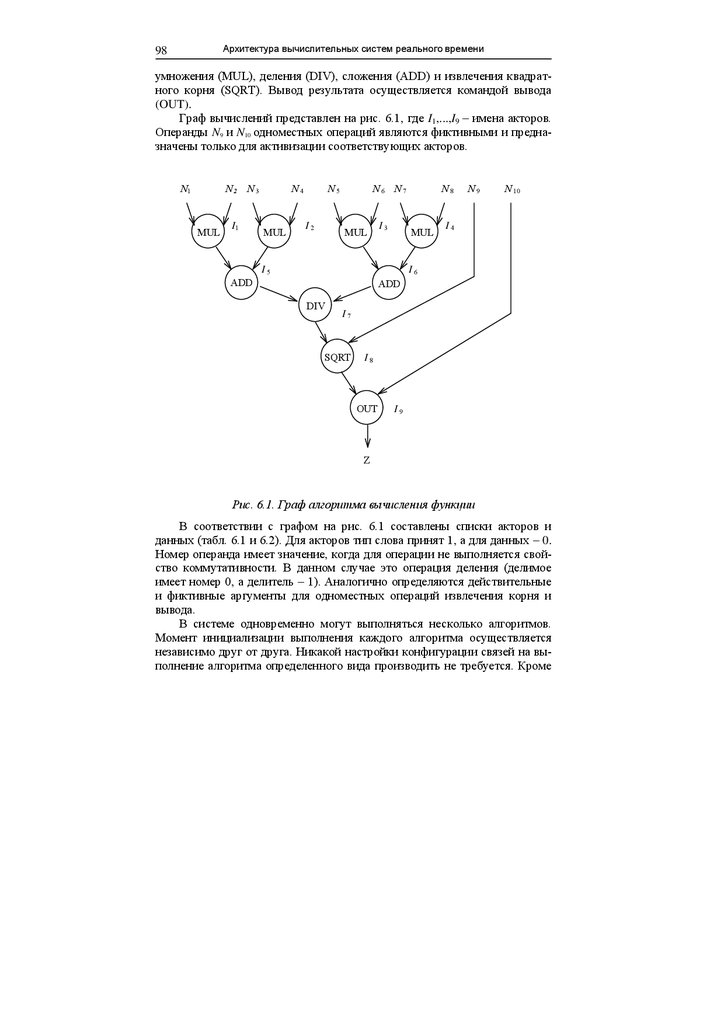

Классификация систем, учитывающая указанные признаки, может

быть представлена в виде дерева (рис. 2.2). Классификация рассматривает

организацию систем на функциональном уровне, на котором видны укрупненные компоненты (процессоры, модули памяти и другие устройства).

Способы реализации самих компонентов систем могут уточняться на более

низких уровнях описания.

Прежде всего, мультипроцессорные системы характеризуются числом

процессоров (Nm) (см. обозначения на рис. 2.2).

В системах с несколькими магистралями обмена информацией (Bk)

имеется возможность совмещения во времени передачи информации между

различными устройствами. В системах с одной магистралью (B1) в один

момент времен в качестве источника информации может быть только одно

устройство, а приемником информации может быть одно или несколько

устройств.

В централизованных системах (CS) функции управления процессом

обработки информации возлагаются на один управляющий (master) процессор. К основным функциям управляющего процессора можно отнести:

планирование и распределение работ между подчиненными (slave)

процессорами;

7.

Архитектура вычислительных систем реального времени20

синхронизация процессов при использовании общего системного

ресурса;

организация взаимодействия между подчиненными (slave) процесссорами;

обработка прерываний, в том числе от подчиненных процессоров;

реконфигурация системы и перераспределение процессов в случае

выхода из строя ресурсов.

В децентрализованных системах (DS) функции управления распределяются между всеми процессорами. Задачи синхронизации процессов решаются процессорами совместно.

Совокупность всех адресов, которые может генерировать процессор,

составляет его адресное пространство. При этом не имеют значения способы адресации, которые используются в процессоре (прямая, косвенная,

относительная, сегментная, страничная и др.), а также физическая организация памяти (плоская память или иерархическая когерентная структура,

включающая несколько уровней, в том числе уровни кэш-памяти).

В системах с единым адресным пространством имеется только общая

память (GM), к которой имеет доступ каждый процессор. В этой памяти,

кроме общей системной информации, хранятся программы, которые выполняются разными процессорами. В этом случае существенно возрастает

число конфликтов при обращении к общей памяти.

В системах с комбинированным адресным пространством, кроме общей памяти, доступной для всех процессоров, каждый процессор имеет

свою собственную локальную память. Способ доступа к локальному и общему адресному пространству физически реализуется различным образом.

При обращении к общему адресному пространству каждый раз осуществляется арбитраж с учетом приоритетов процессоров. Наличие локальной

памяти позволяет хранить в ней программу для данного процессора, что

обеспечивает одновременное выполнение ветвей алгоритмов в разных процессорах практически независимо друг от друга. Каждый процессор обращается за командами в свою локальную память. Общая память используется в основном для обмена данными и хранения общей системной информации.

В системах с локальной памятью (LM) может быть разрешен или запрещен доступ одного процессора к локальной памяти другого. В системах

без доступа к локальной памяти других процессоров межпроцессорный

обмен осуществляется исключительно через общую память.

В системах с разрешением доступа к локальной памяти других процессоров часть локальной памяти каждого процессора выделяется в общее

адресное пространство системы. Обычно такая память называется коммуникационной (CM) и используется в основном для обмена данными между

процессорами.

8.

Глава 2. Классификация и языки описания архитектуры системМультипроцессорные

вычислительные

системы

Nm

С одной магистралью

обмена данными

B1

С несколькими

магистралями обмена

Bk

Централизованные

CS

Децентрализованные

DS

Синхронизация по

каналу данных

SD

Синхронизация по

каналу управления

SC

С единым адресным

пространством

LM

21

С комбинированным

адресным пространством

GM

Без доступа к локальной

памяти других

процессоров

CM

Непосредственный

доступ

С доступом к локальной

памяти других

процессоров

Доступ с преобразованием адресов

CA

Рис. 2.2. Структурная классификация МВС

Для доступа одного процессора к более широкому (а возможно и полному) адресному пространству локальной памяти других процессоров осуществляется преобразование адресов (CA), чтобы не допустить их пересечения. В частности, для этого может быть использован "оконный" доступ.

Решение общей задачи процессорами МВС требует координации их

совместной работы. Если конфликты, касающиеся обращения к коммуникационной среде, разрешаются автоматически на аппаратном уровне, то

процессы, связанные с захватом общего системного ресурса, определением

9.

22Архитектура вычислительных систем реального времени

готовности данных к обмену требуют дополнительных средств синхронизации.

Синхронизация по каналам данных (SD) связана с применением таких

примитивов синхронизации, как флаги и семафоры, которые хранятся в

памяти системы. Обращение к указанным примитивам осуществляется с

помощью команд обращения к памяти, то есть они пересылаются в процессоры по каналам данных.

Согласование работы процессоров может осуществляться также с помощью синхронизации по каналам управления (SC). В этом случае процессоры обмениваются сигналами синхронизации по шине управления (сигналы блокировок, прерывания и т.д.).

Приведенные обозначения можно использовать в качестве структурной нотации. Например, запись СИСТЕМА(N4,B1,DS,SC,LM) соответствует четырехпроцессорной децентрализованной системе с одной системной

шиной, локальной памятью для каждого процессора, причем, синхронизация процессов в системе осуществляется по шине управления.

Предлагаемая классификация может быть полезна не только для характеристики систем, но и в процессе их проектирования, в частности, на

этапе выбора архитектуры. Она позволяет выявить большое число вариантов организации мультипроцессорных систем (различных путей в представленном на рис. 2.2 классификационном дереве). Сопоставительный

анализ вариантов дает возможность выявить архитектуры, которые в большей степени соответствуют предъявляемым требованиям.

Для наглядного представления конфигурации компонентов системы с

учетом рассмотренных классификационных признаков целесообразно использовать язык описания архитектуры на функциональном уровне.

2.3. Языки описания архитектуры

вычислительных систем

Основной целью различных способов описания систем является эффективная передача идей в рассматриваемой области. Язык описания должен быть однозначным и понятным, а уровень детализации – достаточным

для сравнения и оценки эффективности принятых технических решений.

Уровень описания систем определяется степенью абстракции представления ее составляющих (аппаратных и программных). Сложная система может быть разбита на объекты или модули, причем этот процесс можно повторяться до обеспечения требуемого уровня детализации.

Различные уровни описания систем отличаются видимыми на данном

уровне компонентами (программными и аппаратными) и операциями, которые выполняются компонентами или над компонентами.

Из всего многообразия уровней описания систем наиболее часто применяют следующие: виртуальный, функциональный и логический.

10.

Глава 2. Классификация и языки описания архитектуры систем23

На виртуальном уровне видимыми объектами являются процессы,

структуры данных, с которыми работают эти процессы, языковые примитивы, с помощью которых процессы манипулируют с данными и взаимодействуют между собой. Функции, выполняемые компонентами, описываются, как правило, с помощью языков параллельного программирования и

моделирования поведенческих функций систем.

Виртуальный уровень показывает возможности виртуальной машины

и программного обеспечения, но физическая машина на этом уровне не

видна. Современная технология позволяет аппаратную интерпретацию

программ высокого уровня, что делает виртуальный уровень возможным

для общения с системным пользователем. Тенденция такого рода проявляется в проектах іАРХ 432 [39], SWARD [40]. Однако этот уровень не является достаточным для разработчиков систем.

Функциональный уровень позволяет в качестве объектов рассматривать

устройства системы, в том числе, процессоры, память, устройства вводавывода, системы коммутации и т.д. Рассматриваемые объекты взаимодействуют в основном на уровне команд и протоколов обмена информацией.

Могут рассматриваться дополнительные характеристики устройств

(например, форматы команд и данных, разрядность устройств, объем и организация памяти). На функциональном уровне видна архитектура систем,

что позволяет при дальнейшей детализации модулей перейти к логическому уровню.

На логическом уровне может быть достигнута любая степень детализации проекта. Видимыми на этом уровне могут быть типовые узлы и элементы (при необходимости могут учитываться технологические и конструктивные особенностей их реализации). Функции составных частей системы и их взаимодействие отображают с помощью аппарата теории автоматов, специальных языков описания аппаратных средств, в том числе,

схем, таблиц, микроалгоритмов и т.д.

К описаниям систем на этапе проектирования архитектуры можно

предъявить следующие требования:

возможность представления общей архитектуры систем, абстрагируясь от конкретной элементной базы;

описание способов взаимодействия модулей, их особенности и

возможности;

сравнение эффективности различных технических решений с учетом определенных характеристик.

Данным требованиям виртуальный уровень соответствует менее всего.

Поэтому основным является функциональный и логический уровни. На

начальной стадии разработки систем обычно используют функциональный

уровень, а затем – логический уровень. Окончательная стадия проекта регламентируется действующими стандартами и фактически сводится к разработке технической документации.

11.

24Архитектура вычислительных систем реального времени

Для описания систем на функциональном уровне используются различные языки, выбор которых определяется начальным уровнем детализации и целевой функцией проектирования. В ряде работ предлагается рассматривать архитектуру систем в виде совокупности базовых элементов. В

работе [41] предлагается рассматривать архитектуру любого компьютера,

как абстрактную структуру, состоящую из четырех базовых элементов:

процессор команд (IP – Instruction Processor);

процессор данных (DP – Data Processor);

иерархия памяти (IM – Instruction Memory, DM – Data Memory);

элемент коммутации.

В работе [42] предлагается иерархическое описание архитектуры на

основе семи базовых элементов:

iM – память, из которой можно выбрать несколько единиц информации за один цикл обращения;

sM – память, из которой можно выбрать одну единицу информации за

цикл обращения;

C – кэш-память;

sI – простой (неконвейерный) процессор для подготовки команды к

выполнению;

pI – конвейерный процессор для подготовки команды к выполнению;

sX – простой процессор для выполнения команды;

pX – конвейерный процессор для выполнения команды.

Более подробно такой подход к описанию систем рассмотрим на примере нотации Хокни-Джессхоупа [43], в которой используется большее

число базовых элементов. Элементы обозначаются следующим образом:

I – устройство управления, декодирующее одиночный поток команд;

E – устройство обработки данных, манипулирующее с одиночным потоком данных, которое может подразделяться на устройства B и F;

B – устройство обработки данных с фиксированной запятой;

F – устройство обработки данных с плавающей запятой;

M – устройство памяти с одномерной выборкой;

O – устройство памяти с ортогональной (двумерной) выборкой;

P – процессорный элемент (включает E, но не включает I);

IO – устройство ввода-вывода;

C – система (компьютер) в целом.

Конвейерная обработка обозначается строчной буквой p. Например, Ip

и Ep – соответственно конвейерные устройства I и E. Наличие векторных

команд отмечается буквой v (Ipv – конвейерное устройство управления с

векторными командами). Для отражения сложных иерархических структур

используется подстановка обобщенных символов, которые описываются

отдельно. Дублирование элементов обозначается чертой над символом,

группы устройств заключаются в фигурные скобки. С помощью подстрочных индексов возле символов устройств указывается число разрядов, с ко-

12.

Глава 2. Классификация и языки описания архитектуры систем25

торыми устройство оперирует, а надстрочные индексы могут использоваться для уточнения временных характеристик устройств. После скобок

надстрочные символы определяют степень связности между устройствами

(0-nn – нет связи между соседями, 1-nn – есть связь между ближайшими

соседями). Подстрочные символы в этом случае показывают тип управления (в частности, l – синхронное управление). Способы соединения

устройств обозначаются дополнительными символами, в том числе различными линиями, стрелками и т.д. В круглых скобках могут уточняться типы

используемых устройств. После точки с запятой возможны комментарии. В

качестве примера приведем предлагаемые авторами описания нескольких

систем.

C(IBM 7090) = I[F36 – M];

C(IBM 360/195) = Ip54[2C – 32M1160(1 KB) – 16M2800];

C(TIASC(2IPU, 4 конвейера)) = 2Ipv[2 F ] – 8M – 8 P ;

C(ILLIAC-IV (4 квадранта)) = С1[4C280[64 P ]l1-nn]; P =

400

I600

64 – M 2K*64 ;

C(PEPE) = C1 [3I[288{ 3E - M }]l0-nn]; C1 = C(CDC 7600).

Нотация позволяет описывать как последовательные, так и параллельные системы. Кроме того, формуле можно поставить в соответствие граф,

определяющий топологию связей, но особенности взаимодействия базовых

компонентов и способы синхронизации процессов отобразить при этом не

представляется возможным.

Для описания поведенческих функций систем применяется аппарат

теории массового обслуживания, стохастические сети Петри, цепи Маркова

и другие методы моделирования поведения взаимосвязанных автоматов.

При этом фактически рассматривается система массового обслуживания

(СМО), в которой исследуются потоки заявок. Указанные средства исследования базируются на знании информационных и управляющих потоков в

системе, то есть их применению должна предшествовать разработка архитектуры системы. Для этого необходимы средства описания систем, которые бы отображали взаимодействие информационных и управляющих потоков. Наиболее удобными с этой точки зрения являются графические языки описания систем.

2.4. Графический язык описания архитектуры систем

Известны графические языки описания архитектуры ВС [44]. Один из

первых языков, базирующихся на графическом представлении элементов

системы, получил название PMS (processor, memory, switch). Язык обеспе-

13.

26Архитектура вычислительных систем реального времени

чивает общее описание структуры системы и соединений между ее компонентами. Основным недостатком является то, что в данном случае не рассматривается взаимодействие управляющих потоков, что существенно затрудняет разработку поведенческих моделей системы. Больше информации

о системе представляет графический язык MSBI (master, slave, bus,

interface). Описание систем в данном случае составляется из четырех видов

модулей, соответствующих названию метода. Связи между компонентами

ориентированы в направлении передачи управляющих воздействий от активных устройств к пассивным, что делает описание более информативным, в том числе, и для исследования поведенческих функций систем. Однако возникает целый ряд проблем, ограничивающих применение графических моделей. К ним можно отнести, например, невозможность отображения доступа к общему ресурсу с преобразованием параметров, передачи

управляющих воздействий активным элементам, отображения структуры

адресного пространства процессоров. Все это не дает возможности исследовать эффективность различных способов синхронизации процессов и

обмена данными между устройствами.

Рассмотрим графический язык описания архитектуры систем, являющийся развитием языка MSBI и позволяющий устранить ряд его недостатков [45].

Будем использовать две формы отображения архитектуры, а именно:

графическое описание с использованием унифицированных функциональных обозначений;

карту распределения адресного пространства.

Эти формы взаимно дополняют друг друга, но могут использоваться и

самостоятельно при рассмотрении различных аспектов функционирования

систем.

Графическое описание архитектуры представляется ориентированным (возможно взвешенным) графом G=(E, C, F), где E – множество вершин, соответствующих компонентам архитектуры; C – множество дуг, соответствующих направлению управляющих потоков; F – функциональные

правила построения графа.

Множество E={Ea, Ep, Ec} включает вершины трех типов:

Ea – вершины, соответствующие активным элементам архитектуры

(процессорам, устройствам прямого доступа);

Ep – вершины, соответствующие пассивным элементам (модулям памяти, внешним устройствам);

Ec – вершины, соответствующие компонентам коммуникационной

среды системы (магистралям передачи информации).

Множество C может включать различные типы дуг, причем, каждый

тип соответствует определенному потоку управляющих воздействий,

обеспечивающему выполнение заданного действия. В данном случае будет

14.

Глава 2. Классификация и языки описания архитектуры систем27

достаточным рассмотрение множества C={Cm, Cc, Cw, Ca}, включающего

дуги четырех типов:

Cm – дуги, соответствующие управляющим потокам стандартных циклов обращения к собственному адресному пространству (доступ к ресурсу

без арбитража);

Cc – дуги, соответствующие управляющим потокам стандартных циклов обращения к общему адресному пространству, когда доступ сопровождается процедурой арбитража;

Cw – дуги, соответствующие управляющим потокам с преобразованием

параметров доступа (например, преобразование адресов для “оконного”

доступа);

Ca – дуги, соответствующие передаче управляющего воздействия активному элементу.

Функциональные правила F включают следующие требования:

1. Правила должны определять функцию инцидентности I:C E E.

2. Дуги должны быть ориентированы в направлении от активного элемента, который является инициатором действия, к элементу, с которым

это действие должно осуществляться. При этом направление ответных

управляющих сигналов и направление передачи данных может не совпадать с ориентацией дуг. Например, инициатором чтения информации

из памяти является процессор (вырабатывает сигнал READ), а данные

пересылаются из памяти в регистр процессора. Процессор также принимает ответный сигнал подтверждения готовности памяти.

3. Сложные взаимодействия представляются составными дугами. Например, доступу к общему ресурсу с одновременным преобразованием адресов соответствует составная дуга.

4. Дуги, соответствующие передаче управляющего воздействия активному элементу, изображаются пунктирной линией, а остальные – сплошной.

Таким образом, графическое описание архитектуры является графом,

который отображает основные компоненты систем и потоки управляющей

информации, которые определяют способ их взаимодействия. Управляющий поток, направленный к пассивному элементу, вызывает соответствующий информационный поток (команд или данных), а к активному – изменяет режим работы последнего.

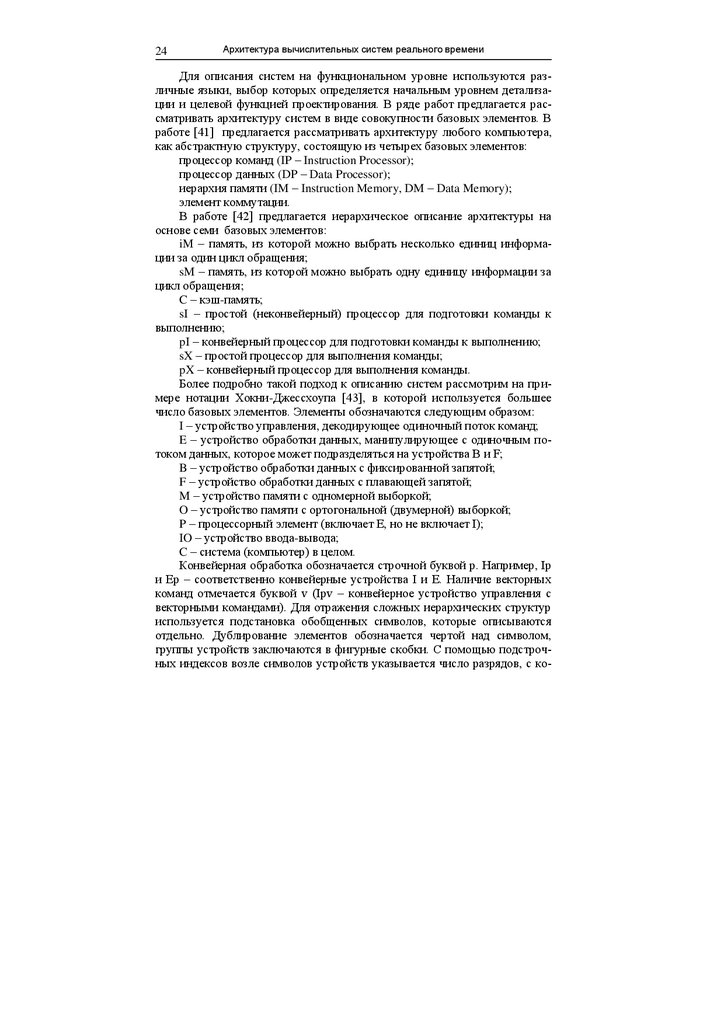

Граф составляется с использованием функциональных обозначений,

представленных на рис. 2.3.

Основным активным элементом является процессор. Он может с помощью команд обращаться к адресному пространству памяти или адресному пространству внешних устройств. В первом случае выполняются стандартные циклы чтение, запись или чтение-модификация-запись, а во втором – ввод или вывод. Адресное пространство внешних устройств может

быть включено в адресное пространство памяти.

15.

28Архитектура вычислительных систем реального времени

Пассивные элементы не могут быть инициаторами событий. Примерами таких устройств являются модули памяти и внешние устройства. Пассивные устройства представлены в адресном пространстве процессоров

совокупностью адресов, которым соответствуют ячейки памяти, порты или

регистры внешних устройств.

— активный

элемент (Ea)

— доступ к ресурсу без

— пассивный

— доступ к общему ресурсу

арбитража (Cm)

с арбитражем (Cc)

элемент (Ep)

— доступ к ресурсу

— комбинированный

с преобразованием

параметров (Cw)

элемент (Ea, Ep)

— элемент коммуника-

ционной среды (Ec)

i

— управляющее воздействие

на активный элемент (Ca)

Рис.2.3. Функциональные обозначения

Комбинированные устройства могут одновременно выполнять функции активных и пассивных элементов. Такими устройствами, например,

являются контроллеры прямого доступа к памяти. Они, как и процессоры,

могут обращаться к памяти, но, в то же время, процессоры могут обращаться к ним в программном режиме как к пассивным устройствам.

Элемент коммуникационной среды используется для обозначения магистрали (шины, канала) передачи данных совместно с интерфейсами

устройств, которые подключены к данной магистрали.

К собственному адресному пространству процессор обращается путем

выполнения стандартных циклов обращения (чтения, записи и т.д.).

Доступ к общему аппаратному ресурсу требует наличия арбитров для

разрешения конфликтов при одновременном обращении к ресурсу нескольких активных устройств. Конфликты при попытках одновременного

доступа разрешаются с учетом определенных дисциплин обслуживания

запросов.

Доступ с преобразованием параметров требует наличия в системе специального устройства. Например, это может быть устройство преобразования адресов, которое позволяет осуществить «оконный» доступ к адресно-

16.

Глава 2. Классификация и языки описания архитектуры систем29

му пространству другого процессора. Предварительно это устройство

должно быть настроено процессором путем записи в него определенной

информации. При необходимости на дугах можно использовать обозначения, поясняющие характер преобразования параметров.

Примером управляющего воздействия на активный элемент может

служить запрос на прерывание программы процессора или перевод процессора в режим ожидания. Если на активный элемент действуют различные

сигналы, то соответствующие дуги могут отмечаться различными буквами

(например, сигнал прерывания можно обозначить через i (interrupt), как на

рис. 2.3).

Ориентация функциональных элементов на графе может быть произвольной. На изображения функциональных элементов могут наноситься

буквенные обозначения.

В дальнейшем, в качестве основных, будем использовать такие обозначения:

P – процессор;

GM – общая (глобальная) память;

LM – собственная (локальная) память;

IO – устройство ввода-вывода;

GB – системная (глобальная) магистраль;

LB – внутренняя (локальная) магистраль.

Каждой дуге графа может быть приписан вес, соответствующий времени выполнения заданного действия в определенных условных единицах.

Взвешенные графы используются для сравнительной оценки временных

параметров различных систем.

Карта распределения адресного пространства отображает память

всей системы и распределение ее между активными архитектурными элементами (процессорами, сопроцессорами и т.д.). Процессор при этом рассматривается как совокупность регистров, которые не включаются в адресное пространство, но могут участвовать в пересылках информации.

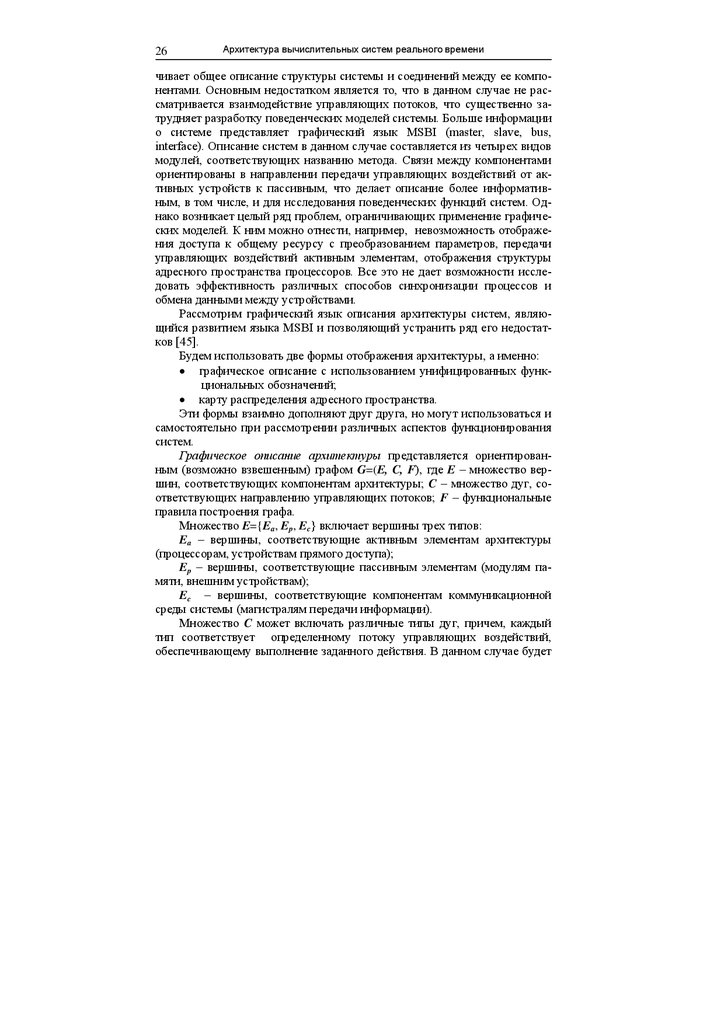

Пример описания архитектуры двухпроцессорной системы показан на

рис. 2.4. Он отражает общую организацию системы и разные варианты доступа процессоров к пассивным элементам.

Процессоры P1 и P2 имеют собственную локальную память (LM1 и

LM2), а также общую (глобальную) память GM. Как следует из карты распределения памяти (рис. 2.4 б), Адресное пространство каждого процессора

включает M адресов. Старшие M-L адресов образуют общее адресное пространство, а L младших – локальное пространство каждого процессора.

Доступ к общей памяти возможен для каждого процессора. Конфликты

разрешаются с помощью системы арбитража. Адреса внешних устройств в

данном примере включены в адресное пространство соответствующей памяти. Устройства IO1 и IO2 доступны только первому процессору. С

устройствами IO3 и IO4 могут работать оба процессора.

17.

30Архитектура вычислительных систем реального времени

Процессору P1 также доступна память LM2 второго процессора. Для

этого используется механизм «оконного» доступа, который обеспечивается

специальным устройством (на функциональном уровне описания архитектуры отображаются только функции этого устройства). Для работы с «окном» в общем адресном пространстве выделена область W, через которую

процессор P1 обращается к LM2.

Первый процессор может воспринимать сигналы внешних прерываний

от устройства IO1 и от второго процессора. Если процессор P 2 не имеет отдельных выходов для формирования внешних управляющих сигналов (как

в данном примере), то он может формировать сигнал прерывания путем

обращения к определенному адресу I собственного адресного пространства. В интерфейсе шины процессора LB 2 селектор данного адреса может

исполнить роль формирователя сигнала прерывания.

Граф управляющих потоков на рис. 2.4,а является взвешенным. Такой

граф можно использовать для определения времени доступа процессоров к

различным ресурсам системы. Каждой дуге графа приписан определенный

вес, который выражает длительность выполнения соответствующих действий, а именно:

tm – длительность цикла обращения к памяти;

tw – длительность инициализации «окна»;

tal – длительность арбитража локальной магистрали;

tag– длительность арбитража системной магистрали.

Временные параметры можно оценивать через определенные условные единицы времени, например, через длительность цикла обращения к

памяти, цикла процессора и т.д.

Времени доступа к определенному ресурсу соответствует сумма весов

всех дуг графа, соединяющих вершины процессора и этого ресурса.

Например, для рассматриваемой архитектуры время одного обращения

первого процессора к общей памяти (ТОП) и к локальной памяти другого

процессора (ТЛП2) можно отобразить соответственно в виде

ТОП = ta g + tm,

ТЛП2 = ta g + tw + ta l + tm.

Для представленной архитектуры характерной особенностью является

необходимость предварительной инициализации «окна» при обращении к

локальной памяти второго процессора. Однако при многократном обращении это осуществляется один раз. Если подряд выполняется M обращений,

то среднее время на инициализацию «окна» составляет tw/M. Следует также

учитывать, что время арбитража для разных магистральных протоколов в

общем случае различно. Оно определяется числом активных устройств и

дисциплинами обслуживания запросов, которые реализуют арбитры. Таким

образом, определение временных параметров систем в каждом конкретном

18.

Глава 2. Классификация и языки описания архитектуры систем31

случае обусловлено особенностями архитектуры. Ниже этот вопрос будет

рассмотрен более подробно.

P1

IO1

ti o

P2

LM1

IO2

ti o

LM2

tm

tm

LB1

LB2

ta g

ta l

ta l

ta g

tw

tm

GM

ti o

ti o

GB

IO4

IO3

а)

0

P1

P2

LM1

LM2

I

IO1

L-1

L

Адрес для

формирования

запроса на

прерывание

IO2

GM

W

Область

внешних

устройств

IO3

IO4

M-1

б)

Рис.2.4. Описание архитектуры двухпроцессорной системы (а – граф

управляющих потоков; б – карта распределения памяти)

Графическое описание архитектуры систем с использованием предлагаемого языка отображает существенные свойства и отношения изучаемого объекта и, следовательно, является моделью систем на функциональном уровне описания.

19.

32Архитектура вычислительных систем реального времени

Использование моделей позволяет на стадии проектирования архитектуры исследовать различные варианты взаимодействия процессоров между

собой и с внешними устройствами, абстрагируясь при необходимости от

конкретной элементной базы (спецификации системы команд, стандартов

магистралей, протоколов обмена и т.д.). В частности, модели дают возможность:

исследовать варианты синхронизации процессов обмена информацией между компонентами системы;

разработать способы доступа к общему системному ресурсу;

выбрать в соответствии с целевыми функциями проектирования

оптимальное распределение адресного пространства процессоров;

определить в относительных единицах длительности различных

процессов.

Такая возможность во многом обусловлена описанием взаимодействия

модулей системы через потоки управляющих (control) воздействий. По

аналогии с названием языка MSBI данный язык можно определить как

MSBC (master, slave, bus, control), а модели, описанные на этом языке – как

MSBC-модели.

К достоинствам языка следует также отнести то, что он позволяет

представить модель в форме, близкой к структурной схеме системы. Это

дает возможность проще передавать идеи в области организации структуры

системы и упрощает дальнейшую разработку проекта.

20.

ГЛАВА 3АРХИТЕКТУРА СИСТЕМ С МАГИСТРАЛЬНОЙ

ТОПОЛОГИЕЙ

3.1. Системы с единым адресным пространством

Рассмотрим типовые архитектуры МВС с общей магистралью, получившие наибольшее распространение. Для описания архитектуры систем

будем использовать MSBC-модели.

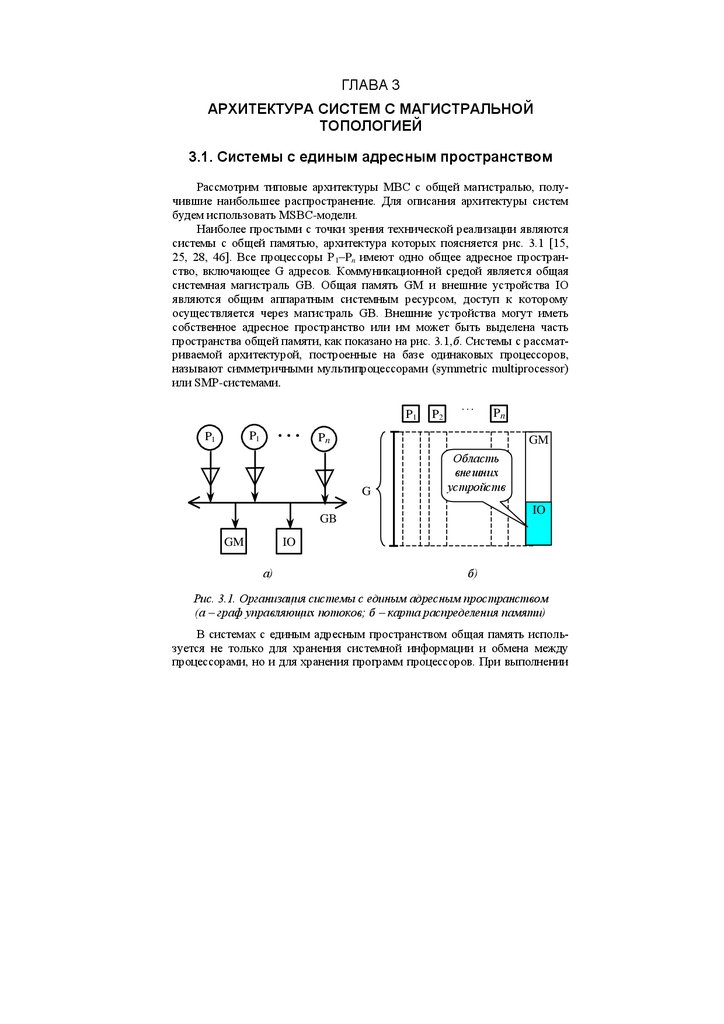

Наиболее простыми с точки зрения технической реализации являются

системы c общей памятью, архитектура которых поясняется рис. 3.1 [15,

25, 28, 46]. Все процессоры P 1–Pn имеют одно общее адресное пространство, включающее G адресов. Коммуникационной средой является общая

системная магистраль GB. Общая память GM и внешние устройства IO

являются общим аппаратным системным ресурсом, доступ к которому

осуществляется через магистраль GB. Внешние устройства могут иметь

собственное адресное пространство или им может быть выделена часть

пространства общей памяти, как показано на рис. 3.1,б. Системы с рассматриваемой архитектурой, построенные на базе одинаковых процессоров,

называют симметричными мультипроцессорами (symmetric multiprocessor)

или SMP-системами.

P1

...

P1

P1

P2

…

Pn

GM

G

Область

внешних

устройств

IO

GB

GM

Pn

IO

а)

б)

Рис. 3.1. Организация системы с единым адресным пространством

(а – граф управляющих потоков; б – карта распределения памяти)

В системах с единым адресным пространством общая память используется не только для хранения системной информации и обмена между

процессорами, но и для хранения программ процессоров. При выполнении

21.

34Архитектура вычислительных систем реального времени

программ процессоры обращаются к памяти за командами, что приводит к

большим затратам времени на ожидание доступа и разрешение конфликтов.

Наличие в каждом процессорном модуле кэш-памяти уменьшает число

конфликтов при обращении к общей памяти. Однако в этом случае возникают трудности с обеспечением когерентности данных, что усложняет взаимодействие процессоров.

В системах с такой организацией памяти используется небольшое число процессоров (например, SMP-серверы обычно строятся на основе 2, 4

или 8 процессоров).

Увеличение количества процессоров в системе связано с необходимостью уменьшения числа конфликтных ситуаций при обращении процессоров к общей памяти. Это может быть достигнуто за счет использования в

каждом процессорном модуле собственной локальной памяти.

Ниже рассматриваются архитектуры систем с комбинированным адресным пространством, особенностью которых является наличие локальной памяти в каждом процессорном модуле. Для определенности будем

считать, что адреса внешних устройств включены в адресное пространство

памяти.

3.2. Системы с локальной памятью

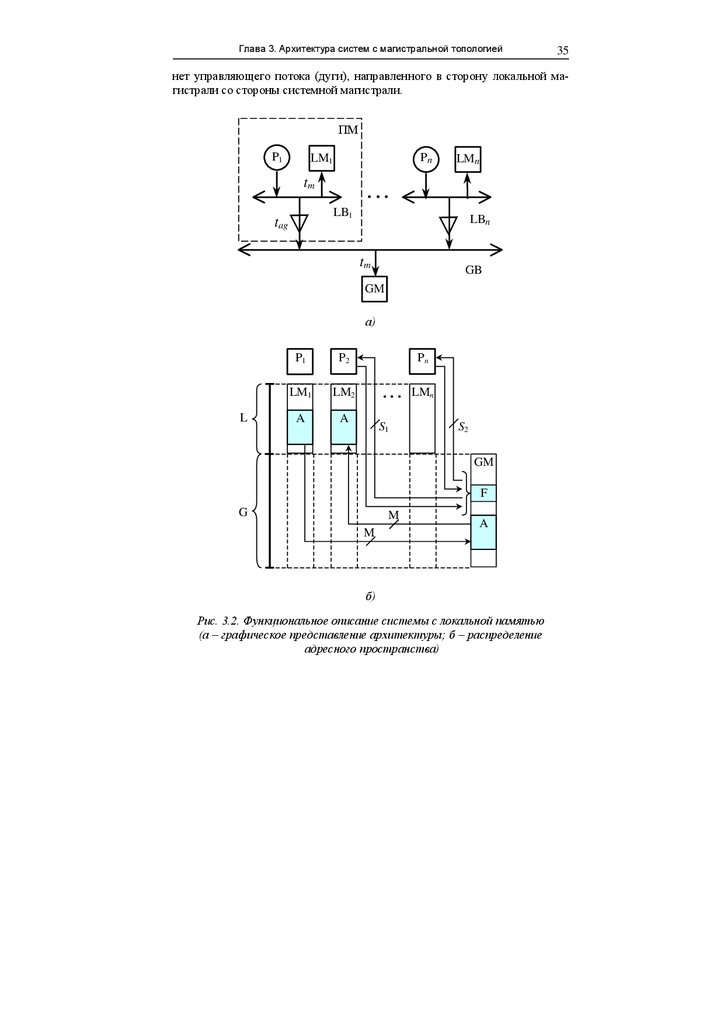

Широкое применение находят системы, в которых наряду с общей памятью каждый процессор имеет свою локальную память [15, 25, 44]. На

рис. 3.2 показана обобщенная модель системы с локальной памятью. Процессор Pi, локальная память LMi и интерфейсные схемы могут быть выполнены в виде процессорного модуля (ПМ). При выполнении программ

процессоры по локальной магистрали LBi обмениваются информацией со

своей локальной памятью, объемом L слов. При этом выполняются стандартные циклы обращения к памяти: "чтение", "запись", "чтениемодификация-запись". В связи с этим при обработке параллельных ветвей

алгоритмов процессоры работают независимо друг от друга до тех пор,

пока не наступает необходимость обратиться к общей памяти GM, объемом

G слов. Адресное пространство каждого процессора включает L+G=2 m адресов (m – длина адреса). Если процессор генерирует адрес, попадающий в

область GM, то селектор адреса в интерфейсе процессора формирует сигнал требования доступа к системной магистрали GB. После предоставления

арбитром доступа выполняется цикл обращения к общей памяти. Поскольку арбитраж осуществляется аппаратно, то на программном уровне доступ

осуществляется одинаково ко всему адресному пространству процессора.

В системе не предусмотрен непосредственный доступ одного процессора к локальной памяти другого процессора. Действительно, на рис. 3.2,а

22.

Глава 3. Архитектура систем с магистральной топологией35

нет управляющего потока (дуги), направленного в сторону локальной магистрали со стороны системной магистрали.

ПМ

P1

Pn

LM1

tm

LMn

...

LB1

tag

LBn

tm

GB

GM

а)

L

P1

P2

LM1

LM2

A

A

Pn

. . . LMn

S1

S2

GM

F

G

M

M

A

б)

Рис. 3.2. Функциональное описание системы с локальной памятью

(а – графическое представление архитектуры; б – распределение

адресного пространства)

23.

Архитектура вычислительных систем реального времени36

По карте распределения адресного пространства (рис. 3.2,б) видно, что

в адресном пространстве процессора не представлена локальная память

других процессоров. Какой бы адрес не генерировал процессор Pi, он будет

относиться либо к LMi, либо к GM, то есть локальная память другого процессора остается недоступной. Этот факт должен учитываться при разработке процедур взаимодействия процессоров.

Для синхронизации процессов обмена могут применяться примитивы

операционной системы, использующие общую память (например, флажки

и семафоры). В этом случае управление процессами осуществляется с использованием шины данных.

Повысить эффективность совместной работы процессоров можно за

счет синхронизации процессов по шине управления. На этой шине арбитраж

не производится, так как для каждого сигнала выделяется собственная линия, что обеспечивает большую скорость обмена управляющей информацией. Процессор, на который поступает управляющий сигнал, воспринимает его как внешнее прерывание и переходит на соответствующую подпрограмму обслуживания прерывания.

Модель трехпроцессорной системы с возможностью синхронизации

процессов по шине управления показана на рис. 3.3. Распределение памяти

в этом случае остается таким же, как показано на рис. 3.2,б. Выработка

сигналов прерывания может быть осуществлена специальным блоком, подключенным к локальной шине процессора. Для взаимодействия процессора

с блоком выделяются адреса в адресном пространстве ввода-вывода или

локальной памяти процессора. Записи слова по определенному адресу

обеспечивает выработку сигналов требования прерывания для других процессоров.

P1

P2

LM1

P3

LM2

LM3

3

LB2

LB1

LB3

GB

GM

Рис. 3.3. Организация системы с синхронизацией процессов

по шине управления

24.

Глава 3. Архитектура систем с магистральной топологией37

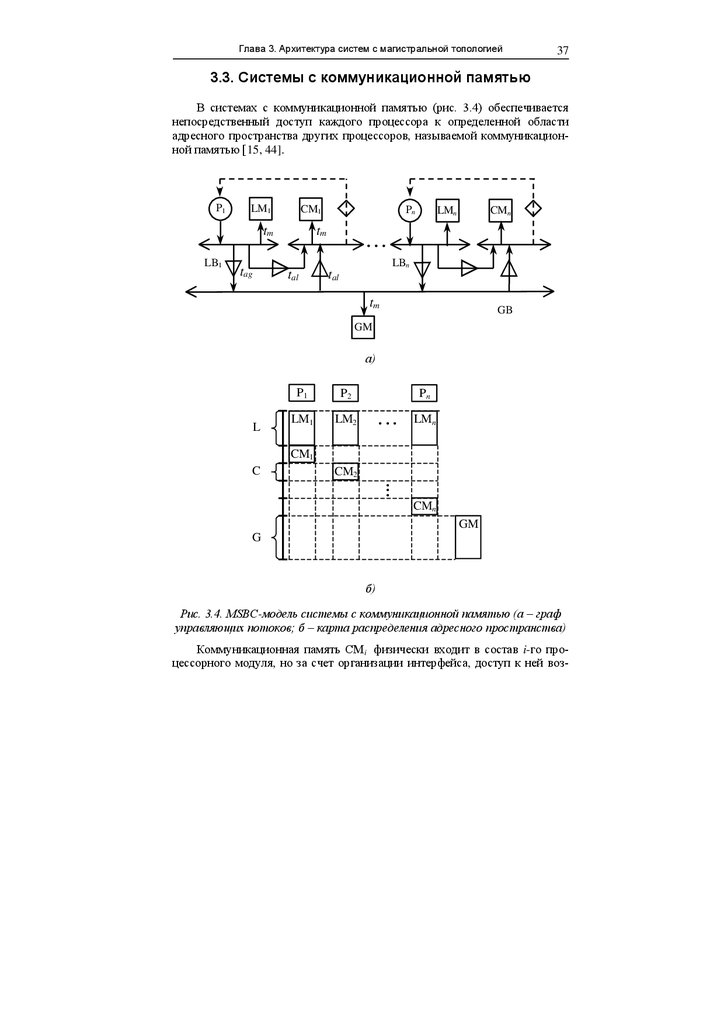

3.3. Системы с коммуникационной памятью

В системах с коммуникационной памятью (рис. 3.4) обеспечивается

непосредственный доступ каждого процессора к определенной области

адресного пространства других процессоров, называемой коммуникационной памятью [15, 44].

P1

LM1

CM1

tm

LB1

Pn

tm

LMn

CMn

...

LBn

tag

tal

tal

tm

GB

GM

а)

L

P1

P2

LM1

LM2

Pn

...

LMn

CM1

C

CM2

..

.

CMn

GM

G

б)

Рис. 3.4. MSBC-модель системы с коммуникационной памятью (а – граф

управляющих потоков; б – карта распределения адресного пространства)

Коммуникационная память CMi физически входит в состав i-го процессорного модуля, но за счет организации интерфейса, доступ к ней воз-

25.

Архитектура вычислительных систем реального времени38

можен как со стороны локальной, так и со стороны системной магистрали.

Коммуникационную память можно рассматривать как распределенные

между процессорами фрагменты общей памяти системы, объемом C слов.

Из приведенной MSBC-модели видно, что при обращении процессора

к последним G адресам своего адресного пространства арбитраж осуществляется один раз (управляющий поток представлен одной дугой, определяющей процесс арбитража). Доступ же со стороны i-го процессора к коммуникационной памяти j-го процессора осуществляется путем поочередного

захвата сначала системной магистрали, а потом и локальной магистрали jго процессора (двойной арбитраж).

В системах с коммуникационной памятью для синхронизации процессов могут применяться межпроцессорные прерывания, реализованные по

аналогии с рис. 3.3. В этом случае для передачи вектора прерывания системная магистраль не используется. Наличие коммуникационной памяти,

доступной другим процессорам, позволяет организовать прерывания более

экономично, как показано на рис. 3.4. В коммуникационной памяти процессора можно выделить адрес, обращение к которому со стороны другого

процессора вызывает инициализацию прерывания для данного процессора.

Идентификация источника прерывания может определяться словом, которое пересылается через системную магисталь по соответствующему адресу.

P1

LM1

CM1

Pn

LMn

CMn

...

LB1

LBn

GB

GM

Рис. 3.5. Система с двухпортовой коммуникационной памятью

Для уменьшения времени обращения к коммуникационной памяти используют двухпортовую память (рис. 3.5). Двухпортовая память организована таким образом, что возможно одновременное обращение к памяти со

стороны разных портов. Конфликт может возникнуть только при обращении к одному адресу. Такой конфликт разрешается интерфейсом самой памяти. При такой организации коммуникационной памяти длительность

доступа к ней в общем случае сокращается (не расходуется время на захват

локальной магистрали).

26.

Глава 3. Архитектура систем с магистральной топологией39

Возможность доступа к части адресного пространства локальной памяти позволяет процессорам более эффективно обмениваться информацией. Однако с увеличением числа процессорных модулей все больший объем

адресного пространства выделяется на блоки коммуникационной памяти, в

результате чего сокращается объем локальной памяти в каждом процессорном модуле.

3.4. Системы с «оконным» доступом

к локальной памяти

Для обеспечения доступа ко всему адресному пространству локальной

памяти каждого процессора со стороны других процессоров может быть

использован «оконный» механизм доступа [15]. Организация систем с таким доступом показана на рис. 3.6.

Возможны различные варианты построения «окна» (W). «Окно» может быть пассивным или активным устройством доступа к магистрали (рис.

3.6 соответствует пассивному устройству). От этого зависит и число адресов V, выделяемое каждому «окну». Структура пассивного «окна» показана

на рис. 3.7. Устройство подключается между системной (СМ) и локальной

(ЛМ) магистралями. В адресном пространстве общей памяти выделяется

два адреса для обращения к регистру адреса (РА) и регистру данных (РД).

Доступ к регистрам обеспечивается интерфейсом (ИСМ). В регистр адреса

записывается начальный адрес локальной памяти, к которой осуществляется доступ со стороны СМ. Передача данных (чтение или запись) осуществляется через РД. При обращении к РД интерфейс системной магистрали

(ИСМ) вырабатывает сигнал, который модифицирует адрес в РА (например, прибавляет или вычитает константу). Устройство доступа к локальной

магистрали (УДЛМ) осуществляет запись или чтение данных из локальной

памяти по адресу в РА. Обращение к ЛМ осуществляется в режиме прямого доступа (ПДП) с соблюдением протокола магистрали (режим DMA –

Direct Memory Access). Пассивное устройство фактически ретранслирует

стандартные циклы обращения к памяти, которые выполняет процессор,

осуществляющий доступ.

Активное “окно” является более сложным устройством, которое может

самостоятельно пересылать данные из локальной памяти одного процессора в локальную память другого. В данном случае процессор выполняет

инициализацию “окна”, передавая ему начальные адреса, объем пересылаемого массива и команду. После этого активное устройство самостоятельно

осуществляет пересылку массива. Для организации “окна” выпускаются

специальные микросхемы (в частности, фирмой DEC).

27.

Архитектура вычислительных систем реального времени40

P1

LM1

Pn

...

LMn

tm

LB1

tag

LBn

tal

tal

tw

tm

GB

GM

а)

L

P1

P2

LM1

LM2

Pn

...

LMn

Wn

..

.

V

W2

W1

GM

G

б)

Рис. 3.6. Организация системы с “оконным” доступом к локальной памяти

процессоров (а – граф потоков управления; б – карта распределения памяти)

Таким образом, рассматриваемая архитектура обеспечивает полный

доступ к локальной памяти каждого процессора со стороны других процессоров. Если порты внешних устройств включены в адресное пространство

локальной памяти, то с помощью механизма «окна» другим процессорам

становятся доступны и эти устройства.

28.

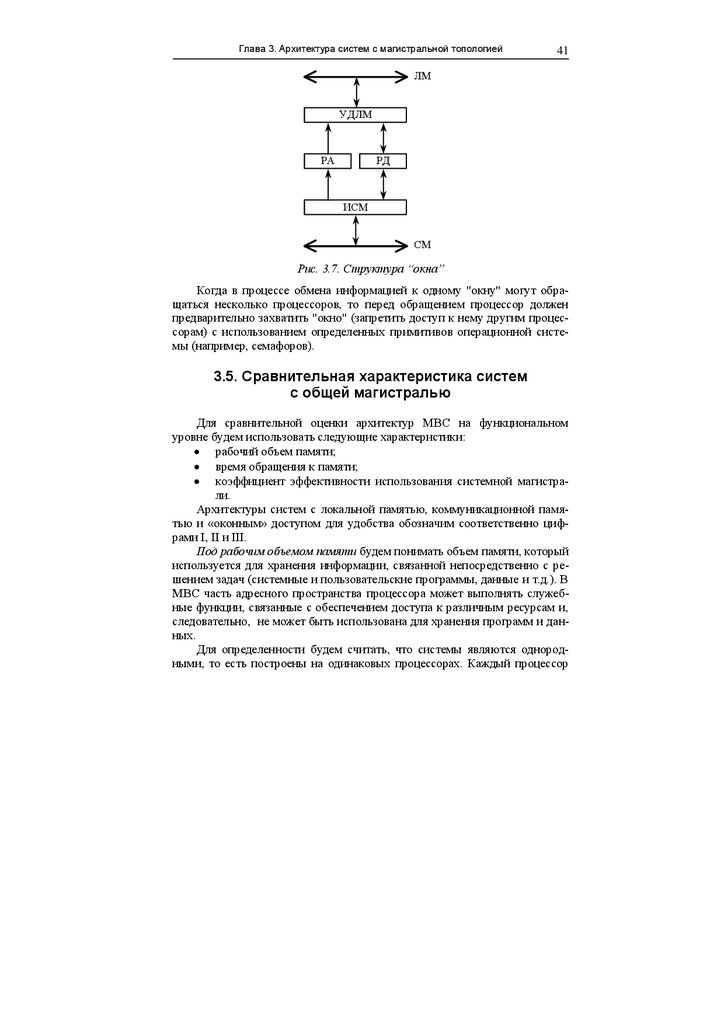

Глава 3. Архитектура систем с магистральной топологией41

ЛМ

УДЛМ

РА

РД

ИСМ

СМ

Рис. 3.7. Структура “окна”

Когда в процессе обмена информацией к одному "окну" могут обращаться несколько процессоров, то перед обращением процессор должен

предварительно захватить "окно" (запретить доступ к нему другим процессорам) с использованием определенных примитивов операционной системы (например, семафоров).

3.5. Сравнительная характеристика систем

с общей магистралью

Для сравнительной оценки архитектур МВС на функциональном

уровне будем использовать следующие характеристики:

рабочий объем памяти;

время обращения к памяти;

коэффициент эффективности использования системной магистрали.

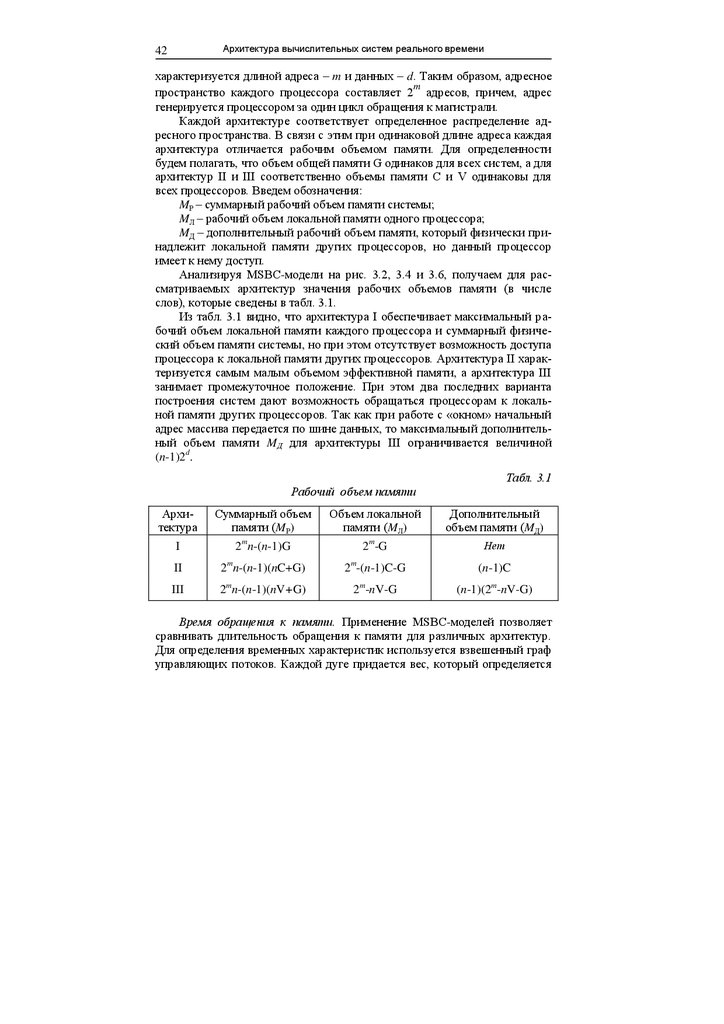

Архитектуры систем с локальной памятью, коммуникационной памятью и «оконным» доступом для удобства обозначим соответственно цифрами I, II и III.

Под рабочим объемом памяти будем понимать объем памяти, который

используется для хранения информации, связанной непосредственно с решением задач (системные и пользовательские программы, данные и т.д.). В

МВС часть адресного пространства процессора может выполнять служебные функции, связанные с обеспечением доступа к различным ресурсам и,

следовательно, не может быть использована для хранения программ и данных.

Для определенности будем считать, что системы являются однородными, то есть построены на одинаковых процессорах. Каждый процессор

29.

Архитектура вычислительных систем реального времени42

характеризуется длиной адреса – m и данных – d. Таким образом, адресное

m

пространство каждого процессора составляет 2 адресов, причем, адрес

генерируется процессором за один цикл обращения к магистрали.

Каждой архитектуре соответствует определенное распределение адресного пространства. В связи с этим при одинаковой длине адреса каждая

архитектура отличается рабочим объемом памяти. Для определенности

будем полагать, что объем общей памяти G одинаков для всех систем, а для

архитектур II и III соответственно объемы памяти C и V одинаковы для

всех процессоров. Введем обозначения:

MР – суммарный рабочий объем памяти системы;

MЛ – рабочий объем локальной памяти одного процессора;

MД – дополнительный рабочий объем памяти, который физически принадлежит локальной памяти других процессоров, но данный процессор

имеет к нему доступ.

Анализируя MSBC-модели на рис. 3.2, 3.4 и 3.6, получаем для рассматриваемых архитектур значения рабочих объемов памяти (в числе

слов), которые сведены в табл. 3.1.

Из табл. 3.1 видно, что архитектура I обеспечивает максимальный рабочий объем локальной памяти каждого процессора и суммарный физический объем памяти системы, но при этом отсутствует возможность доступа

процессора к локальной памяти других процессоров. Архитектура II характеризуется самым малым объемом эффективной памяти, а архитектура III

занимает промежуточное положение. При этом два последних варианта

построения систем дают возможность обращаться процессорам к локальной памяти других процессоров. Так как при работе с «окном» начальный

адрес массива передается по шине данных, то максимальный дополнительный объем памяти MД для архитектуры III ограничивается величиной

(n-1)2d.

Табл. 3.1

Рабочий объем памяти

Архитектура

Суммарный объем

памяти (MР)

Объем локальной

памяти (MЛ)

Дополнительный

объем памяти (MД)

I

2mn-(n-1)G

2m-G

Нет

II

2mn-(n-1)(nC+G)

2m-(n-1)C-G

(n-1)C

III

m

2 n-(n-1)(nV+G)

m

2 -nV-G

(n-1)(2m-nV-G)

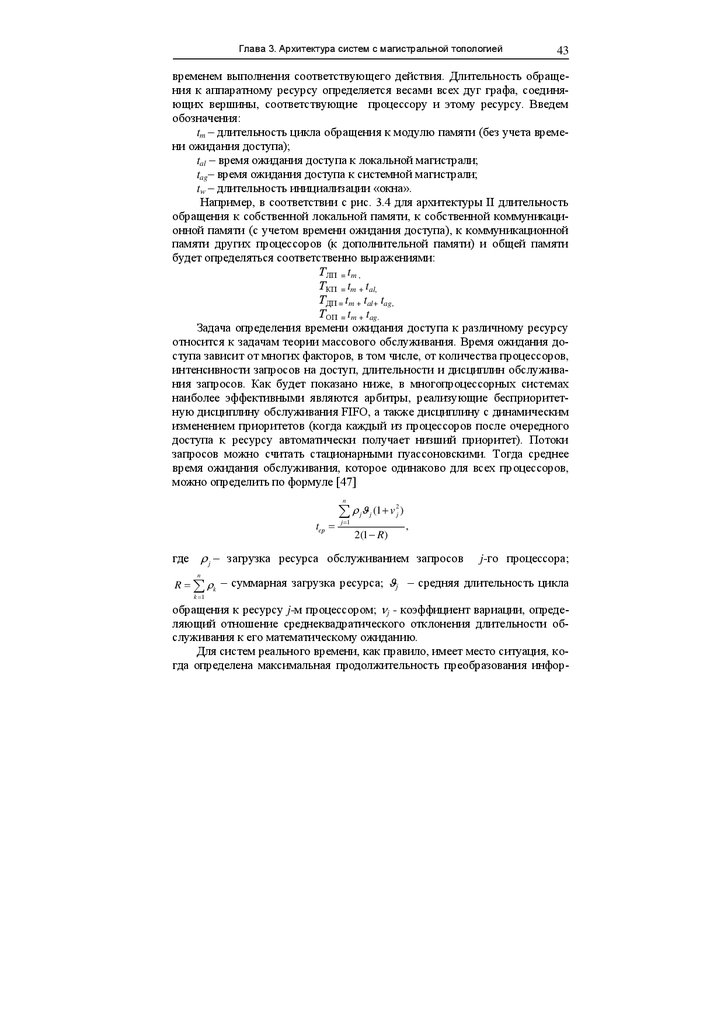

Время обращения к памяти. Применение MSBC-моделей позволяет

сравнивать длительность обращения к памяти для различных архитектур.

Для определения временных характеристик используется взвешенный граф

управляющих потоков. Каждой дуге придается вес, который определяется

30.

Глава 3. Архитектура систем с магистральной топологией43

временем выполнения соответствующего действия. Длительность обращения к аппаратному ресурсу определяется весами всех дуг графа, соединяющих вершины, соответствующие процессору и этому ресурсу. Введем

обозначения:

tm – длительность цикла обращения к модулю памяти (без учета времени ожидания доступа);

tal – время ожидания доступа к локальной магистрали;

tag– время ожидания доступа к системной магистрали;

tw – длительность инициализации «окна».

Например, в соответствии с рис. 3.4 для архитектуры II длительность

обращения к собственной локальной памяти, к собственной коммуникационной памяти (с учетом времени ожидания доступа), к коммуникационной

памяти других процессоров (к дополнительной памяти) и общей памяти

будет определяться соответственно выражениями:

ТЛП = tm ,

ТКП = tm + tal,

ТДП = tm + tal+ tag,

ТОП = tm + tag.

Задача определения времени ожидания доступа к различному ресурсу

относится к задачам теории массового обслуживания. Время ожидания доступа зависит от многих факторов, в том числе, от количества процессоров,

интенсивности запросов на доступ, длительности и дисциплин обслуживания запросов. Как будет показано ниже, в многопроцессорных системах

наиболее эффективными являются арбитры, реализующие бесприоритетную дисциплину обслуживания FIFO, а также дисциплину с динамическим

изменением приоритетов (когда каждый из процессоров после очередного

доступа к ресурсу автоматически получает низший приоритет). Потоки

запросов можно считать стационарными пуассоновскими. Тогда среднее

время ожидания обслуживания, которое одинаково для всех процессоров,

можно определить по формуле [47]

n

tср

(1 v

j 1

j

j

2(1 R)

2

j

)

,

где j – загрузка ресурса обслуживанием запросов

j-го процессора;

n

R k – суммарная загрузка ресурса; j – средняя длительность цикла

k 1

обращения к ресурсу j-м процессором; j - коэффициент вариации, определяющий отношение среднеквадратического отклонения длительности обслуживания к его математическому ожиданию.

Для систем реального времени, как правило, имеет место ситуация, когда определена максимальная продолжительность преобразования инфор-

31.

Архитектура вычислительных систем реального времени44

мации, превышение которой недопустимо. В этом случае необходимо учитывать максимальные временные параметры. При указанных дисциплинах

обслуживания заявок любому процессору гарантирован доступ к магистрали через (n-1) максимальных по длительности циклов обращения к ней со

стороны других процессоров, где n – число процессоров, участвующих в

арбитраже. Так как арбитраж локальной магистрали осуществляется только

между двумя процессорами, то максимальное время ожидания равно одному циклу. При обращении к системной магистрали, к которой подключены

n процессоров, время ожидания доступа не превышает (n-1) циклов. Заметим, что для архитектуры II при обращении процессора к однопортовой

коммуникационной памяти другого процессора вначале осуществляется

доступ к системной магистрали, а затем – к локальной, то есть выполняется

двойной арбитраж.

Характерной особенностью архитектуры III является необходимость

предварительной инициализации «окна» при обращении к локальной памяти других процессоров. Если к "окну" могут обращаться несколько процессоров, то инициализация включает захват "окна" (запрет доступа к ресурсу

другим процессорам) и его настройку. Захват может быть осуществлен с

использованием семафоров в общей памяти. Если "окно" используется другими процессорами, то для проверки семафора может понадобиться несколько попыток (обозначим максимальное значение количества попыток

через P). Настройка "окна", в свою очередь, требует одного обращения к

системной магистрали для записи начального адреса массива. Инициализация "окна" осуществляется один раз в процессе пересылки массива слов за

время tW. Следовательно, на каждое передаваемое слово приходится tW/M

времени инициализации (М – длина массива). Если к "окну" может обращаться только один процессор (например, при централизованном управлении процессом пересылки информации), то захватывать "окно" нет необходимости.

Табл. 3.2

Время обращения к памяти

Архитектура

TЛП, tm

TКП, tm

TОП, tm

TДП, tm

I

1

–

n

–

II

1

2

n

2n

III

2

–

n

2n+(P+1)( 2n-1)/M

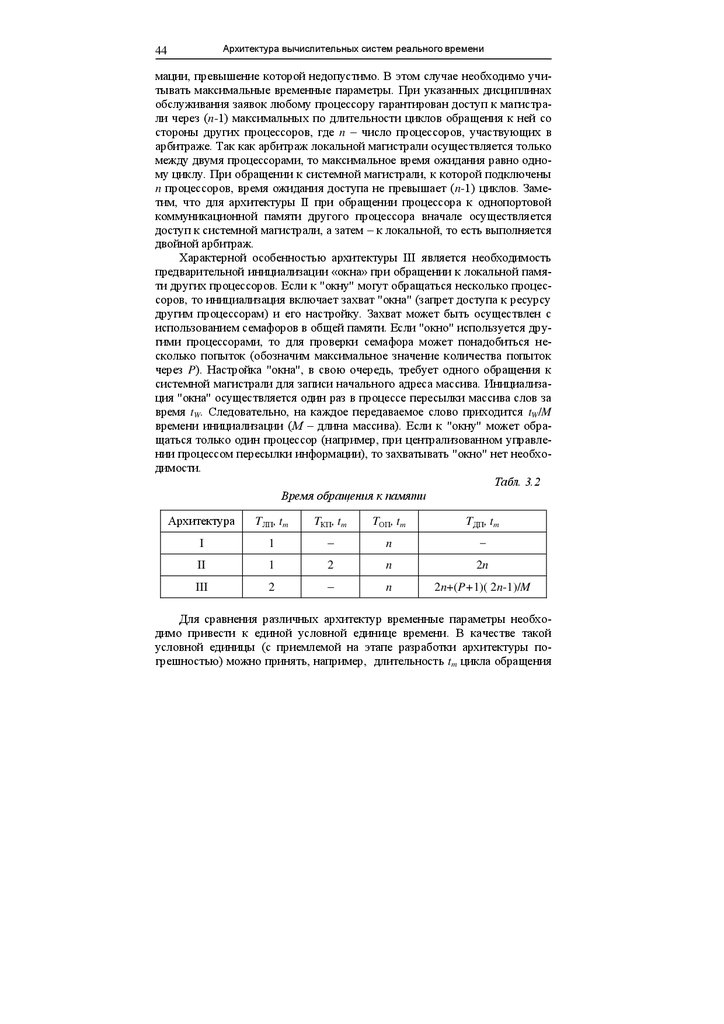

Для сравнения различных архитектур временные параметры необходимо привести к единой условной единице времени. В качестве такой

условной единицы (с приемлемой на этапе разработки архитектуры погрешностью) можно принять, например, длительность tm цикла обращения

32.

Глава 3. Архитектура систем с магистральной топологией45

к модулю памяти (без учета длительности ожидания доступа). Для рассматриваемых архитектур максимальные значения временных характеристик приведены в табл. 3.2.

Из табл. 3.2 следует, что архитектура I обеспечивает минимальное

время доступа ко всему адресному пространству собственной локальной

памяти. По отношению к общей памяти все архитектуры одинаковы. К памяти других процессоров обращение осуществляется быстрее в системах с

архитектурой II.

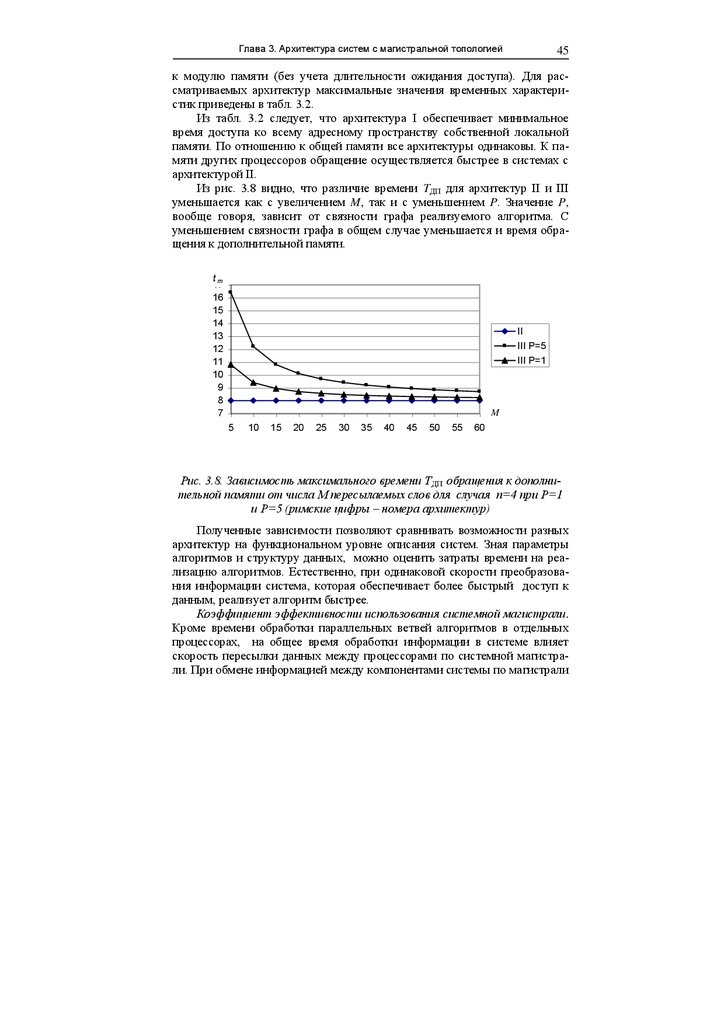

Из рис. 3.8 видно, что различие времени TДП для архитектур II и III

уменьшается как с увеличением M, так и с уменьшением P. Значение P,

вообще говоря, зависит от связности графа реализуемого алгоритма. С

уменьшением связности графа в общем случае уменьшается и время обращения к дополнительной памяти.

t

m

tm

17

16

15

14

13

12

11

10

9

8

7

II

III P=5

III P=1

M

5

10

15

20

25

30

35

40

45

50

55

60

Рис. 3.8. Зависимость максимального времени TДП обращения к дополнительной памяти от числа M пересылаемых слов для случая n=4 при P=1

и P=5 (римские цифры – номера архитектур)

Полученные зависимости позволяют сравнивать возможности разных

архитектур на функциональном уровне описания систем. Зная параметры

алгоритмов и структуру данных, можно оценить затраты времени на реализацию алгоритмов. Естественно, при одинаковой скорости преобразования информации система, которая обеспечивает более быстрый доступ к

данным, реализует алгоритм быстрее.

M

Коэффициент эффективности использования системной магистрали.

Кроме времени обработки параллельных ветвей алгоритмов в отдельных

процессорах, на общее время обработки информации в системе влияет

скорость пересылки данных между процессорами по системной магистрали. При обмене информацией между компонентами системы по магистрали

33.

46Архитектура вычислительных систем реального времени

кроме полезной информации (непосредственно данных) передается, как

правило, служебная информация, которая обеспечивает инициализацию и

синхронизацию процессов обмена информацией. Непроизводительные затраты времени обусловлены особенностями архитектуры.

Для сравнительной оценки эффективности использования системной

магистрали в различных системах будем использовать коэффициент KСМ,

который определяется по формуле

NS ND

(3.1)

,

M

где NS – число обращений к системной магистрали для инициализации и

синхронизации процедур обмена (непроизводительные затраты времени);

ND – число обращений к системной магистрали для передачи непосредственно данных; M – число передаваемых слов.

Коэффициент KСМ определяет среднее число обращений к системной

магистрали для передачи одного слова между компонентами системы. При

равной скорости обработки параллельных ветвей алгоритмов система с

меньшим значением KСМ будет затрачивать и меньше времени на решение

задач за счет более быстрого межпроцессорного обмена.

Непроизводительные затраты времени зависят от способов инициализации и синхронизации процессов. Инициализация и синхронизация может

осуществляться как по шине управления (например, с применением прерываний), так и по шине данных (с использованием флажков и семафоров).

Управление пересылкой информации по системной магистрали может быть

централизованным и децентрализованным. В первом случае обменом

управляет один процессор, который имеет доступ к памяти других процессоров. При децентрализованном управлении в синхронизации обмена данными принимает участие в определенной мере каждый процессор. Время

использования магистрали для систем с разной архитектурой и разным

способом управления при передаче данных может отличаться. Рассмотрим

организацию обмена данными в системах с разной архитектурой. Процессы

обмена будем рассматривать на уровне команд процессоров, а не операторов языков высокого уровня. При таком подходе более наглядно проявляются особенности архитектуры систем.

Определение KСМ в общем случае является нетривиальной задачей и

требует разработки программ (если известна система команд) или, по крайней мере, алгоритмов синхронизации и пересылки данных.

Вначале рассмотрим реализацию обмена информацией, когда синхронизация процессов осуществляется по шине данных. Возможный подход к

определению коэффициента эффективности KСМ покажем на примере децентрализованного обмена данными в системе с архитектурой I (рис. 3.2).

Будем считать, что необходимо передать массив данных из локальной памяти одного процессора в локальную память другого процессора. АрхитекK СМ

34.

Глава 3. Архитектура систем с магистральной топологией47

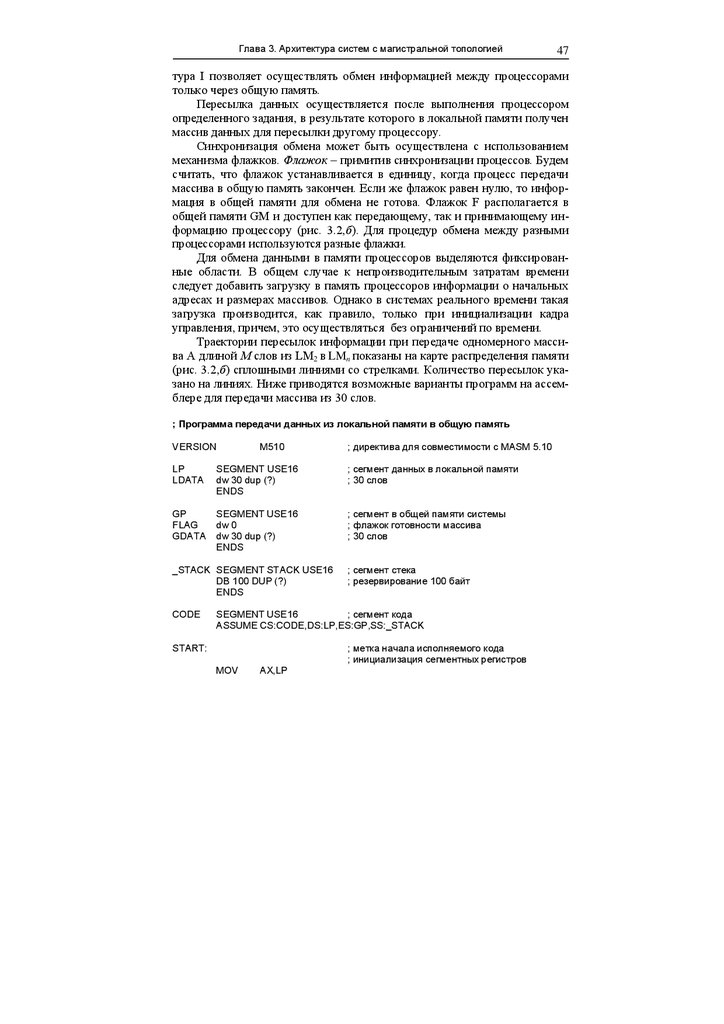

тура I позволяет осуществлять обмен информацией между процессорами

только через общую память.

Пересылка данных осуществляется после выполнения процессором

определенного задания, в результате которого в локальной памяти получен

массив данных для пересылки другому процессору.

Синхронизация обмена может быть осуществлена с использованием

механизма флажков. Флажок – примитив синхронизации процессов. Будем

считать, что флажок устанавливается в единицу, когда процесс передачи

массива в общую память закончен. Если же флажок равен нулю, то информация в общей памяти для обмена не готова. Флажок F располагается в

общей памяти GM и доступен как передающему, так и принимающему информацию процессору (рис. 3.2,б). Для процедур обмена между разными

процессорами используются разные флажки.

Для обмена данными в памяти процессоров выделяются фиксированные области. В общем случае к непроизводительным затратам времени

следует добавить загрузку в память процессоров информации о начальных

адресах и размерах массивов. Однако в системах реального времени такая

загрузка производится, как правило, только при инициализации кадра

управления, причем, это осуществляться без ограничений по времени.

Траектории пересылок информации при передаче одномерного массива А длиной М слов из LM2 в LMn показаны на карте распределения памяти

(рис. 3.2,б) сплошными линиями со стрелками. Количество пересылок указано на линиях. Ниже приводятся возможные варианты программ на ассемблере для передачи массива из 30 слов.

; Программа передачи данных из локальной памяти в общую память

VERSION

M510

; директива для совместимости с MASM 5.10

LP

LDATA

SEGMENT USE16

dw 30 dup (?)

ENDS

; сегмент данных в локальной памяти

; 30 слов

GP

FLAG

GDATA

SEGMENT USE16

dw 0

dw 30 dup (?)

ENDS

; сегмент в общей памяти системы

; флажок готовности массива

; 30 слов

_STACK SEGMENT STACK USE16

DB 100 DUP (?)

ENDS

CODE

; сегмент стека

; резервирование 100 байт

SEGMENT USE16

; сегмент кода

ASSUME CS:CODE,DS:LP,ES:GP,SS:_STACK

; метка начала исполняемого кода

; инициализация сегментных регистров

START:

MOV

AX,LP

35.

Архитектура вычислительных систем реального времени48

MOV

MOV

MOV

MOV

MOV

DS,AX

AX,GP

ES,AX

AX,_STACK

SS,AX

; Подготовка массива данных в локальной памяти

;______________________________________________________

LBLP1_1:

;

.

;

.

;______________________________________________________

; Пересылка данных из локальной памяти в общую память

mov

mov

mov

cld

LBLP1_2:

jnz

rep

cx, 30

si, offset LDATA

di, offset GDATA

; размерность массива

; смещение массива в локальной памяти

; смещение массива в общей памяти

; назначить инкремент регистров SI и DI

test

FLAG, 0ffffh

; проверка флажка готовности

LBLP1_2

; массива в общей памяти

movsw

mov

ES:FLAG, 1

; пересылка массива из 30 слов

; установка флажка готовности массива

jmp

LBLP1_1

; перейти к формированию массива

ENDS

END STAR

; Программа приема данных из общей памяти в локальную память

VERSION

M510

; директива для совместимости с MASM 5.10

LP

LDATA

SEGMENT USE16

dw 30 dup (?)

ENDS

; сегмент данных в локальной памяти

; 30 слов

GP

FLAG

GDATA

SEGMENT USE16

dw 0

dw 30 dup (?)

ENDS

; сегмент в общей памяти системы

; флажок готовности массива

; 30 слов

_STACK SEGMENT STACK USE16

DB 100 DUP (?)

ENDS

CODE

; сегмент стека

; резервирование 100 байт

SEGMENT USE16

; сегмент кода

ASSUME CS:CODE,DS:GP,ES:LP,SS:_STACK

; метка начала исполняемого кода

; инициализация сегментных регистров

START:

MOV

AX,GP

36.

Глава 3. Архитектура систем с магистральной топологиейMOV

MOV

MOV

MOV

MOV

49

DS,AX

AX,LP

ES,AX

AX,_STACK

SS,AX

; Пересылка данных из общей памяти в локальную память

; размерность массива

; смещение массива в общей памяти

; смещение массива в локальной памяти

; назначить инкремент регистров SI и DI

LBLP2_1 mov

mov

mov

cld

cx, 30

si, offset GDATA

di, offset LDATA

LBLP2_2:

jz

test

FLAG, 0ffffh

; проверка флажка

LBLP2_2

; готовности массива

rep

movsw

mov

FLAG, 0

; пересылка массива (из DS:SI в ES:DI)

; сброс флажка готовности

; Обработка полученного массива данных в локальной памяти

;_________________________________________________________

;

.

;

.

;

.

jmp

LBLP2_1

; переход на проверку готовности массива

;_________________________________________________________

ENDS

END START

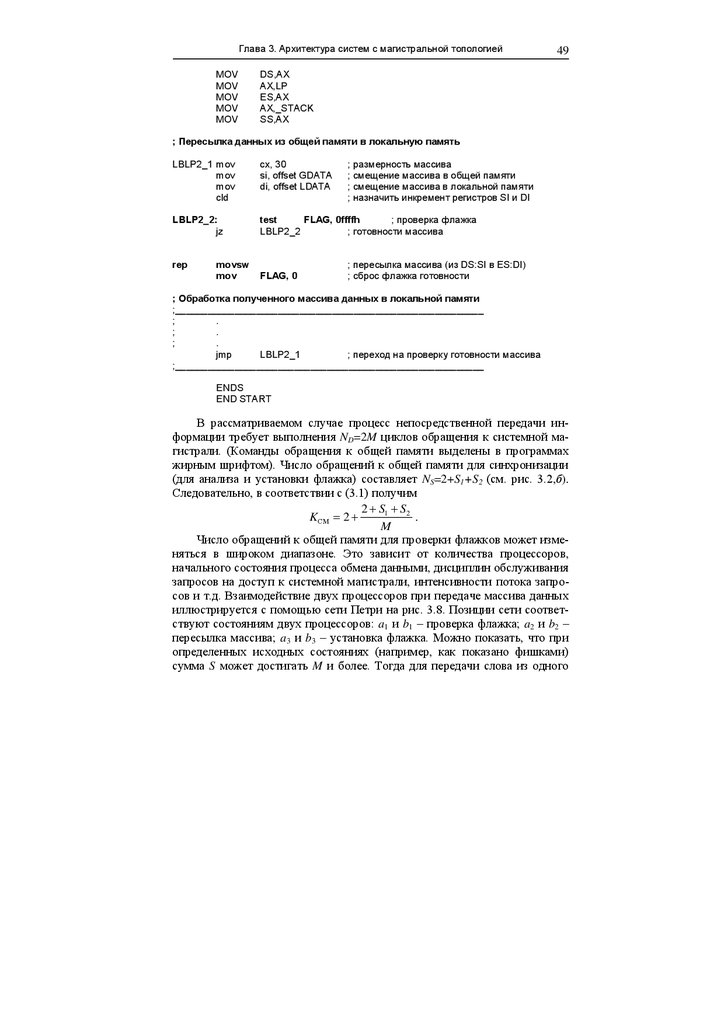

В рассматриваемом случае процесс непосредственной передачи информации требует выполнения ND=2M циклов обращения к системной магистрали. (Команды обращения к общей памяти выделены в программах

жирным шрифтом). Число обращений к общей памяти для синхронизации

(для анализа и установки флажка) составляет NS=2+S1+S2 (см. рис. 3.2,б).

Следовательно, в соответствии с (3.1) получим

2 S1 S2

KСМ 2

.

M

Число обращений к общей памяти для проверки флажков может изменяться в широком диапазоне. Это зависит от количества процессоров,

начального состояния процесса обмена данными, дисциплин обслуживания

запросов на доступ к системной магистрали, интенсивности потока запросов и т.д. Взаимодействие двух процессоров при передаче массива данных

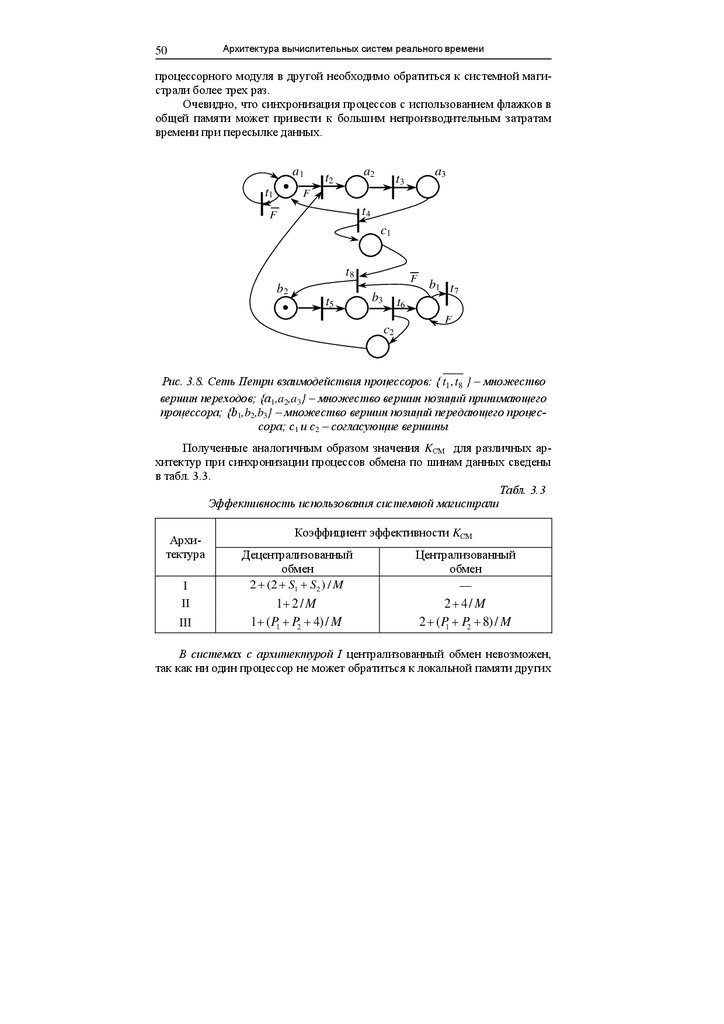

иллюстрируется с помощью сети Петри на рис. 3.8. Позиции сети соответствуют состояниям двух процессоров: a1 и b1 – проверка флажка; a2 и b2 –

пересылка массива; a3 и b3 – установка флажка. Можно показать, что при

определенных исходных состояниях (например, как показано фишками)

сумма S может достигать M и более. Тогда для передачи слова из одного

37.

Архитектура вычислительных систем реального времени50

процессорного модуля в другой необходимо обратиться к системной магистрали более трех раз.

Очевидно, что синхронизация процессов с использованием флажков в

общей памяти может привести к большим непроизводительным затратам

времени при пересылке данных.

a1

t1

a2

t2

a3

t3

F

t4

F

c1

t8

b2

t5

F

b3

b1 t 7

t6

c2

F

Рис. 3.8. Сеть Петри взаимодействия процессоров: { t1 , t8 } – множество

вершин переходов; {a1,a2,a3} – множество вершин позиций принимающего

процессора; {b1,b2,b3} – множество вершин позиций передающего процессора; с1 и c2 – согласующие вершины

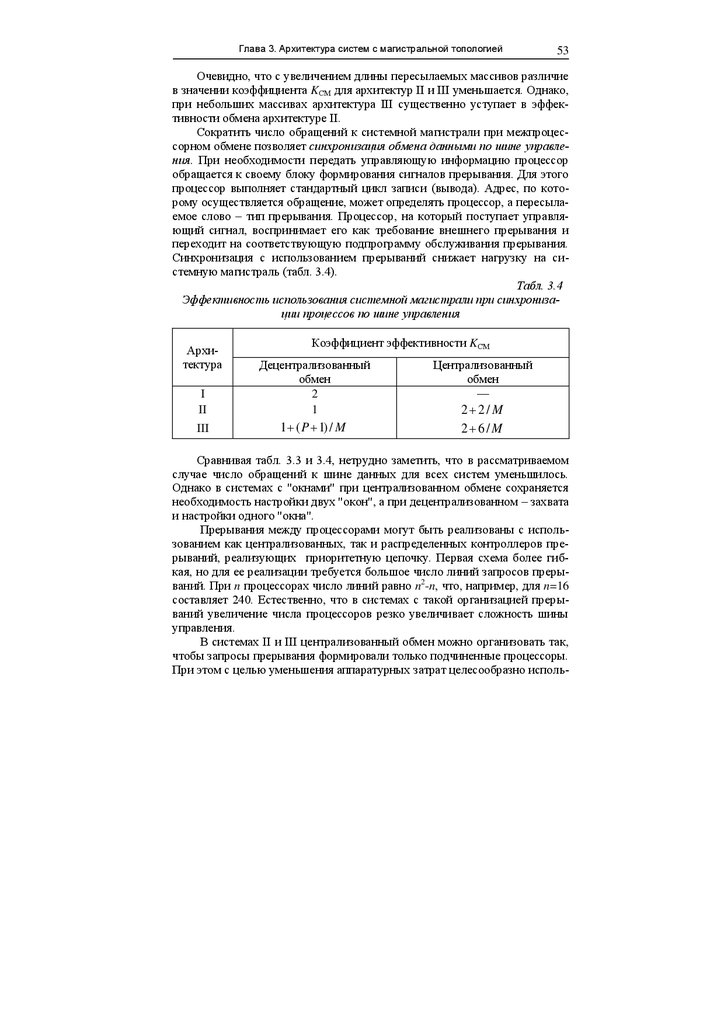

Полученные аналогичным образом значения KСМ для различных архитектур при синхронизации процессов обмена по шинам данных сведены

в табл. 3.3.

Табл. 3.3

Эффективность использования системной магистрали

Архитектура

I

II

III

Коэффициент эффективности KСМ

Децентрализованный

обмен

2 (2 S1 S2 ) / M

Централизованный

обмен

—

1 2 / M

1 ( P1 P2 4) / M

2 4/ M

2 ( P1 P2 8) / M

В системах с архитектурой I централизованный обмен невозможен,

так как ни один процессор не может обратиться к локальной памяти других

38.

Глава 3. Архитектура систем с магистральной топологией51

процессоров, то есть управляющий процессор не может самостоятельно

осуществлять пересылку данных между другими процессорными модулями.

В системах с коммуникационной памятью (архитектура II) передаваемый массив формируется процессором в своей коммуникационной памяти. При децентрализованном обмене процессор, для которого подготовлен

массив данных, самостоятельно переписывает массив в свою локальную

память, так как коммуникационная память другого процессора ему доступна (см. рис. 3.4). Следовательно, пересылка массива требует ND= М обращений к системной магистрали. Для синхронизации процесса пересылки

можно использовать флажки, которые находится в коммуникационной памяти каждого процессора. Проверка и сброс флажка в этом случае выполняется в памяти каждого процессора без обращения к системной магистрали, а установка флажка – в коммуникационной памяти другого процессора.

Для установки флажков системная магистраль захватывается только два

раза, то есть NS =2.

При централизованном управлении передачу массива между двумя

процессорами осуществляет управляющий процессор. В этом случае для

передачи массива необходимо ND=2M обращений к магистрали. Синхронизация процессов требует четырех обращений к магистрали (NS =4). Два обращения требуются для установки в памяти управляющего процессора

двух флажков подчиненными процессорами, готовыми к обмену, а еще два

– для установки управляющим процессором флажков в памяти подчиненных после завершения передачи массива. Таким образом, архитектура II

при централизованном управлении уступает в скорости обмена системам с

децентрализованным обменом.

К непроизводительным затратам при использовании механизма «окна»

(архитектура III, рис.3.6) добавляется необходимость инициализации “окна”. В децентрализованных системах для синхронизации процессов можно

использовать флажки в локальной памяти процессоров. Это позволяет при

работе с флажками уменьшить число обращений к системной магистрали.

Флажки проверяются в своей локальной памяти, а устанавливаются в локальной памяти другого процессора. Для доступа одного процессора к локальной памяти другого процессора производится настройка "окна" путем

записи начального адреса массива. Предварительно необходимо оградить

“окно” от других процессоров с помощью семафора в общей памяти. Пересылка массива после настройки "окна" выполняется одним процессором за

ND=М обращений к магистрали. По окончании пересылки массива процессоры поочередно устанавливают флажки в локальной памяти других процессоров. Для вспомогательных операций магистраль используется в общей сложности NS P1 P2 4 раз, где P1 и P2 – число обращений к магистрали для проверки и установки семафоров каждым из процессоров. Если

39.

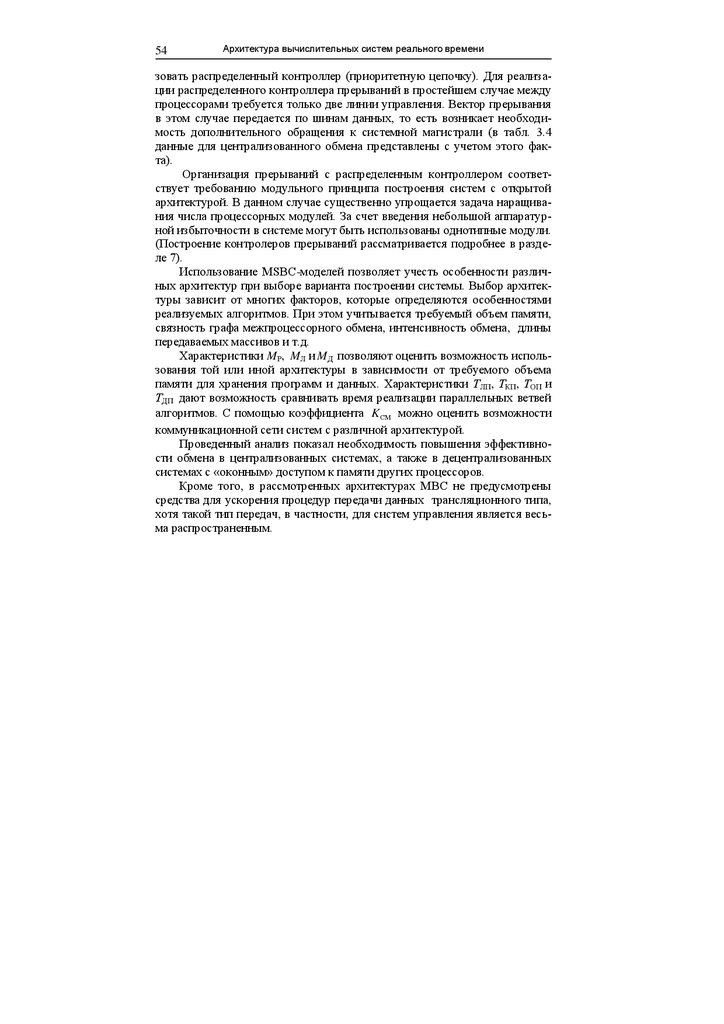

Архитектура вычислительных систем реального времени52