Similar presentations:

Последовательностные схемы. Элементы памяти. (Лекция 10)

1. Лекция 10. ПОСЛЕДОВАТЕЛЬНОСТНЫЕ СХЕМЫ (ЭЛЕМЕНТЫ ПАМЯТИ)

Триггеры. Устройства на триггерных схемах:регистры, счетчики

2.

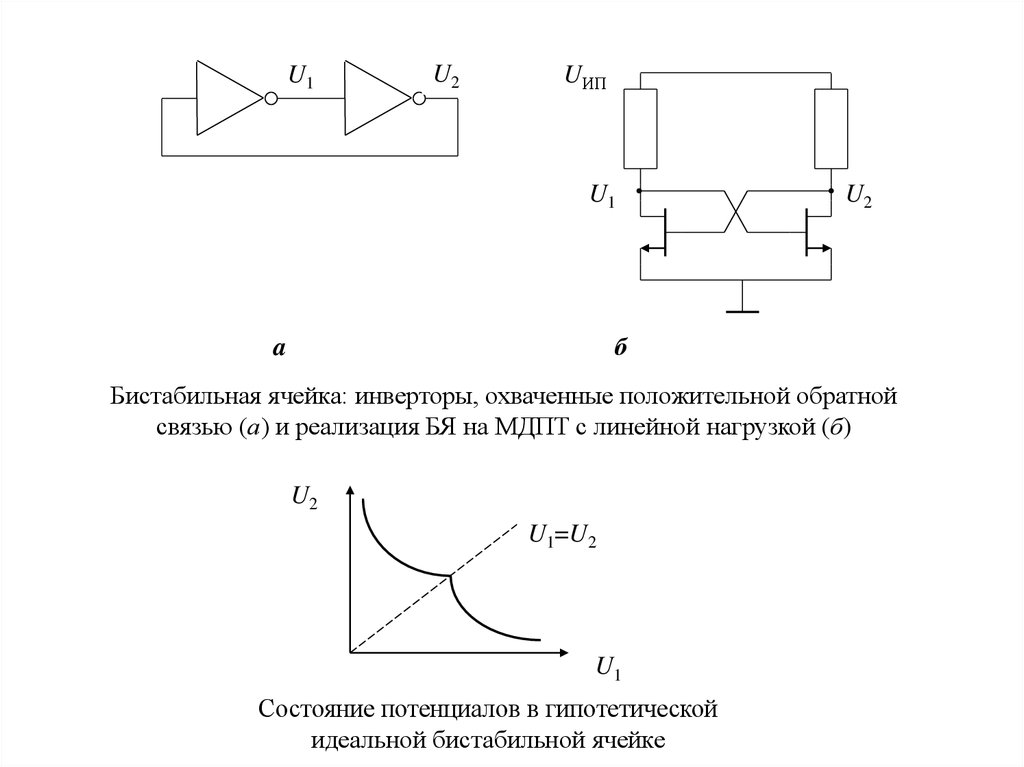

U1U2

UИП

U1

U2

б

a

Бистабильная ячейка: инверторы, охваченные положительной обратной

связью (а) и реализация БЯ на МДПТ с линейной нагрузкой (б)

U2

U1=U2

U1

Состояние потенциалов в гипотетической

идеальной бистабильной ячейке

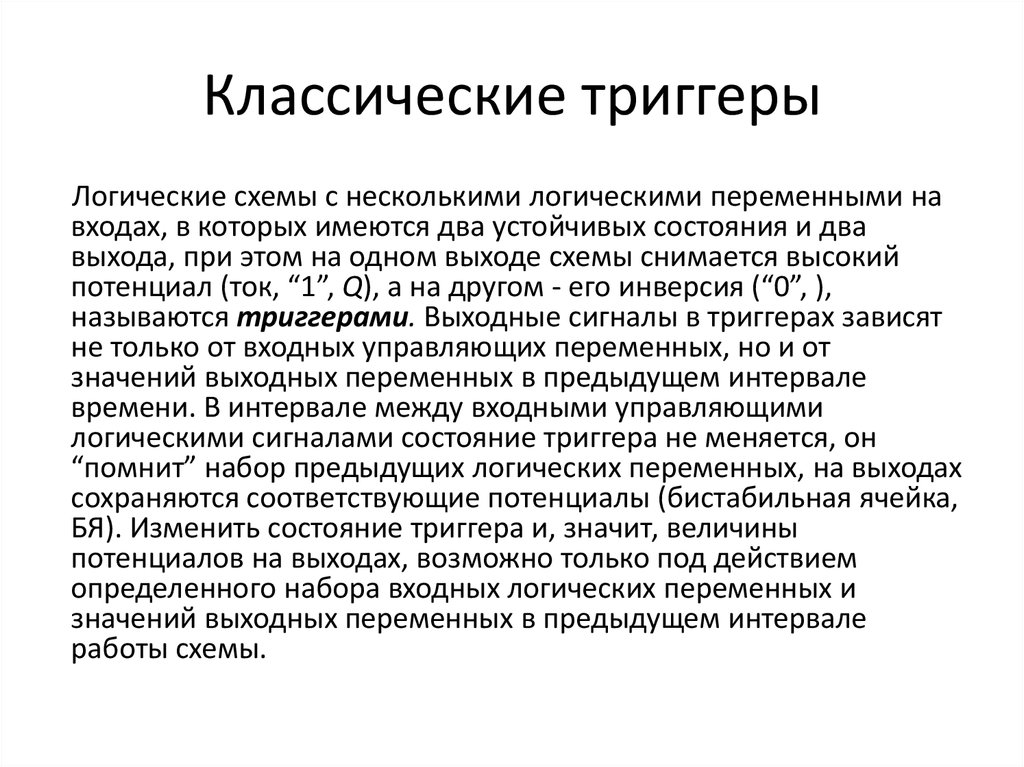

3. Классические триггеры

Логические схемы с несколькими логическими переменными навходах, в которых имеются два устойчивых состояния и два

выхода, при этом на одном выходе схемы снимается высокий

потенциал (ток, “1”, Q), а на другом - его инверсия (“0”, ),

называются триггерами. Выходные сигналы в триггерах зависят

не только от входных управляющих переменных, но и от

значений выходных переменных в предыдущем интервале

времени. В интервале между входными управляющими

логическими сигналами состояние триггера не меняется, он

“помнит” набор предыдущих логических переменных, на выходах

сохраняются соответствующие потенциалы (бистабильная ячейка,

БЯ). Изменить состояние триггера и, значит, величины

потенциалов на выходах, возможно только под действием

определенного набора входных логических переменных и

значений выходных переменных в предыдущем интервале

работы схемы.

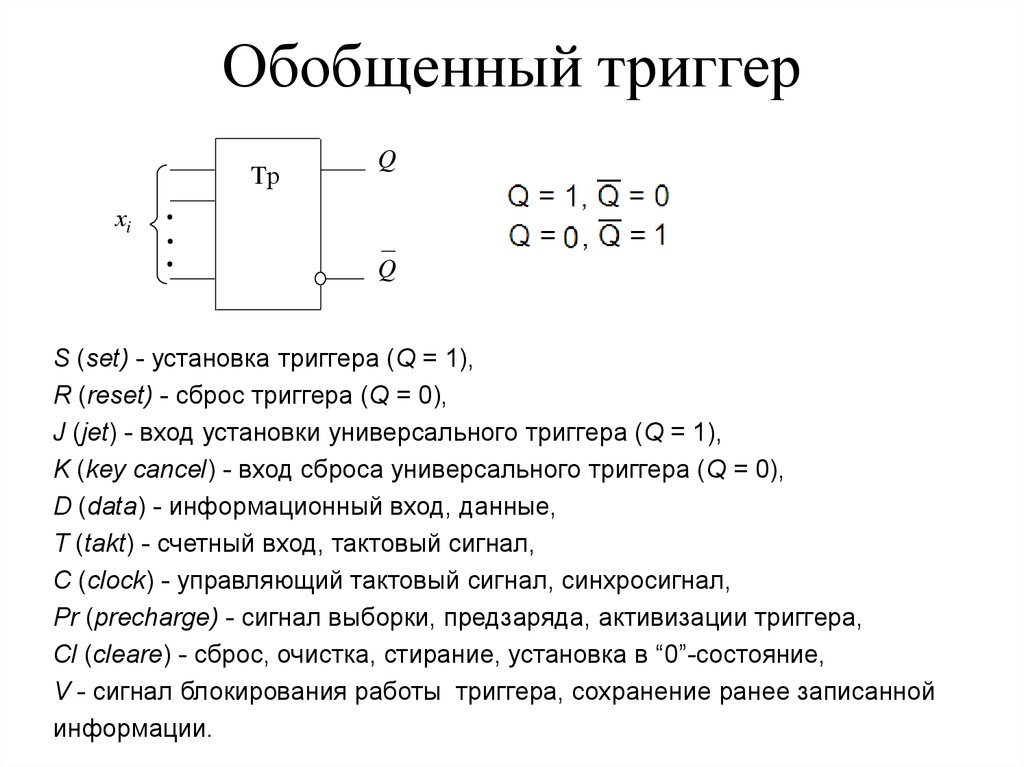

4. Обобщенный триггер

TрQ

хi

Q

S (set) - установка триггера (Q = 1),

R (reset) - сброс триггера (Q = 0),

J (jet) - вход установки универсального триггера (Q = 1),

K (key cancel) - вход сброса универсального триггера (Q = 0),

D (data) - информационный вход, данные,

T (takt) - счетный вход, тактовый сигнал,

C (clock) - управляющий тактовый сигнал, синхросигнал,

Pr (precharge) - сигнал выборки, предзаряда, активизации триггера,

Cl (cleare) - сброс, очистка, стирание, установка в “0”-состояние,

V - сигнал блокирования работы триггера, сохранение ранее записанной

информации.

5. Классификация триггеров

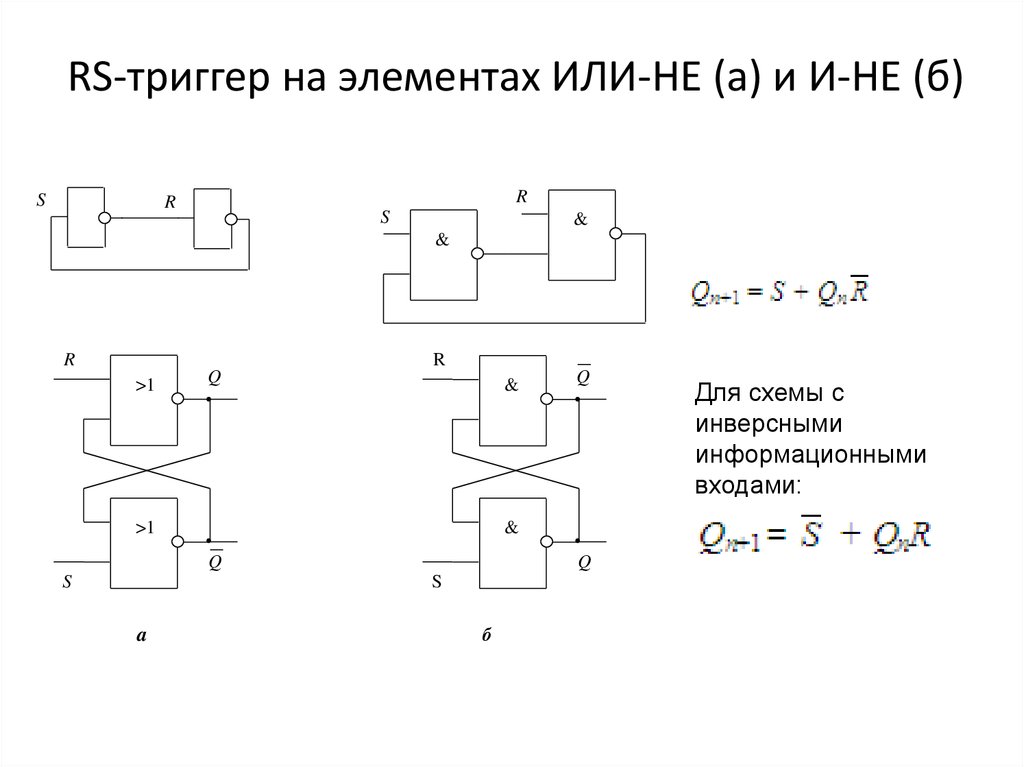

6. RS-триггер на элементах ИЛИ-НЕ (а) и И-НЕ (б)

SR

R

S

&

&

R

R

>1

Q

&

>1

&

Q

S

Q

S

a

Q

б

Для схемы с

инверсными

информационными

входами:

7. Таблица состояний RS-триггера

QnS

R

Qn+1

0

0

0

0

0

0

1

0

0

1

0

1

0

1

1

Неопределенность

1

0

0

1

1

0

1

0

1

1

0

1

1

1

1

Неопределенность

Qn

S

Карта Карно для RS-триггера

1

х

х

1

1

0

0

0

R

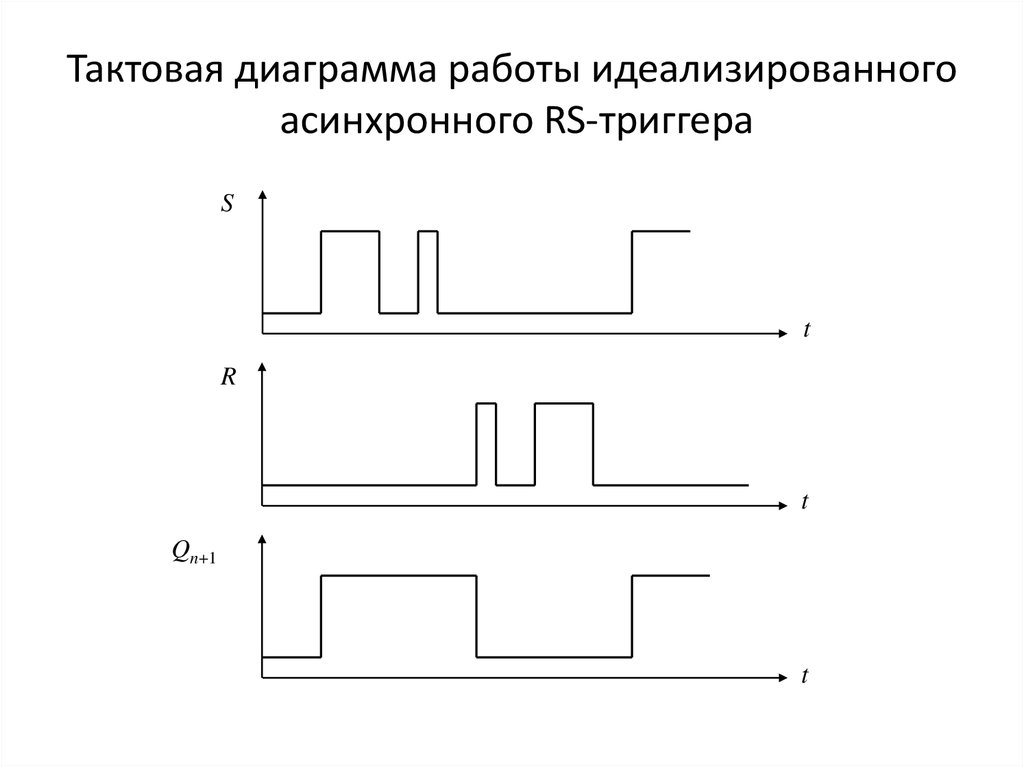

8. Тактовая диаграмма работы идеализированного асинхронного RS-триггера

St

R

t

Qn+1

t

9.

ST

Q

S

T

Q

Q

S

T

S

C

Q

R

а

R

Q

б

R

в

T

Q

C

Q

R

г

Условные обозначения RS-триггеров:

а - асинхронный с прямыми входами

б - асинхронный с инверсными входами

в - синхронный с прямыми статическими входами

г - синхронный с прямыми динамическими входами, управляемый срезом

Q

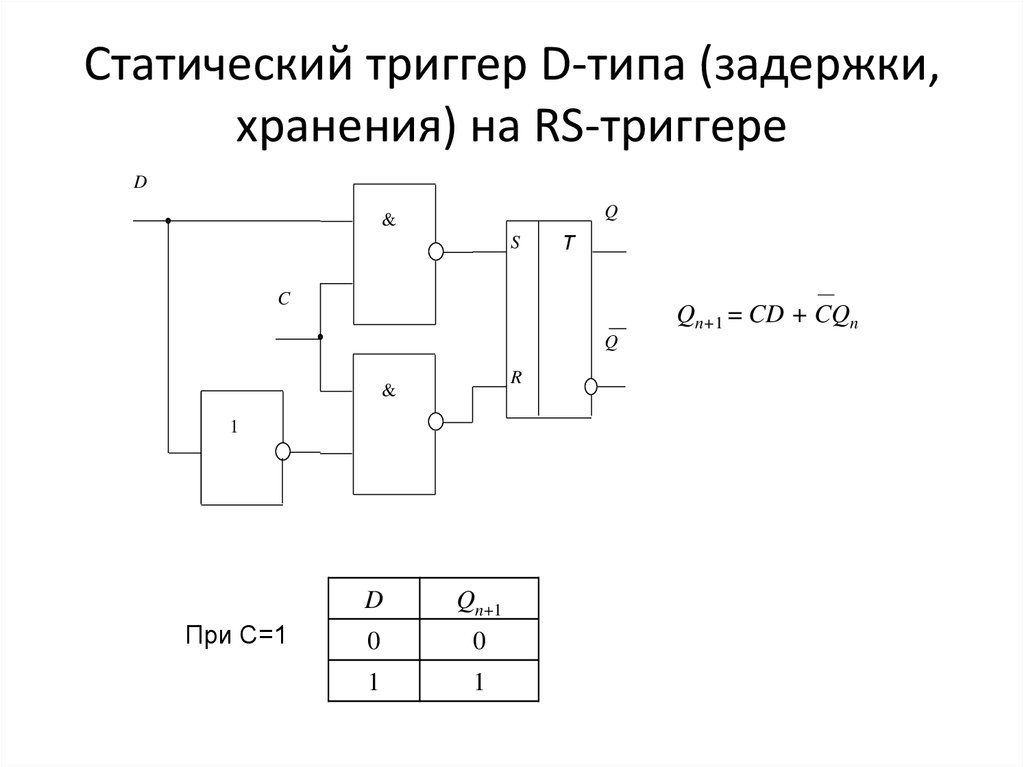

10. Статический триггер D-типа (задержки, хранения) на RS-триггере

DQ

&

S

T

__

C

Qn+1 = CD + CQn

Q

R

&

1

При С=1

D

Qn+1

0

0

1

1

11. Схема D-триггера на проходных ключах

Dp

n

C

p

n

Qn

Qn+1

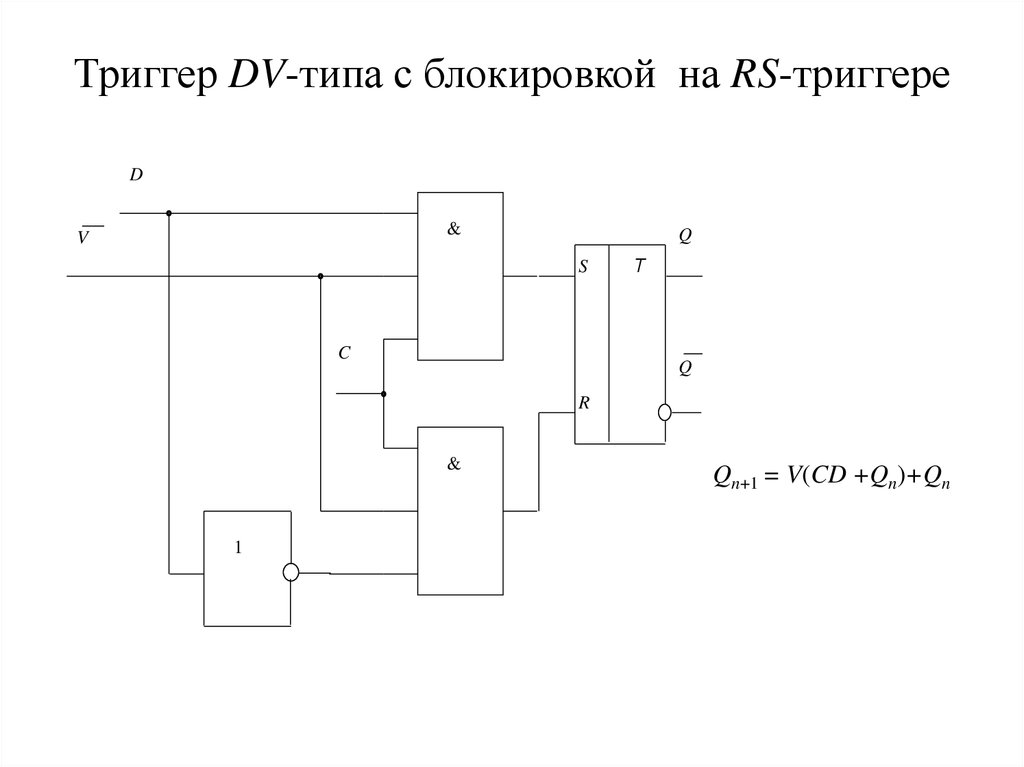

12. Триггер DV-типа с блокировкой на RS-триггере

D&

V

Q

S

C

T

Q

R

&

1

Qn+1 = V(CD +Qn)+Qn

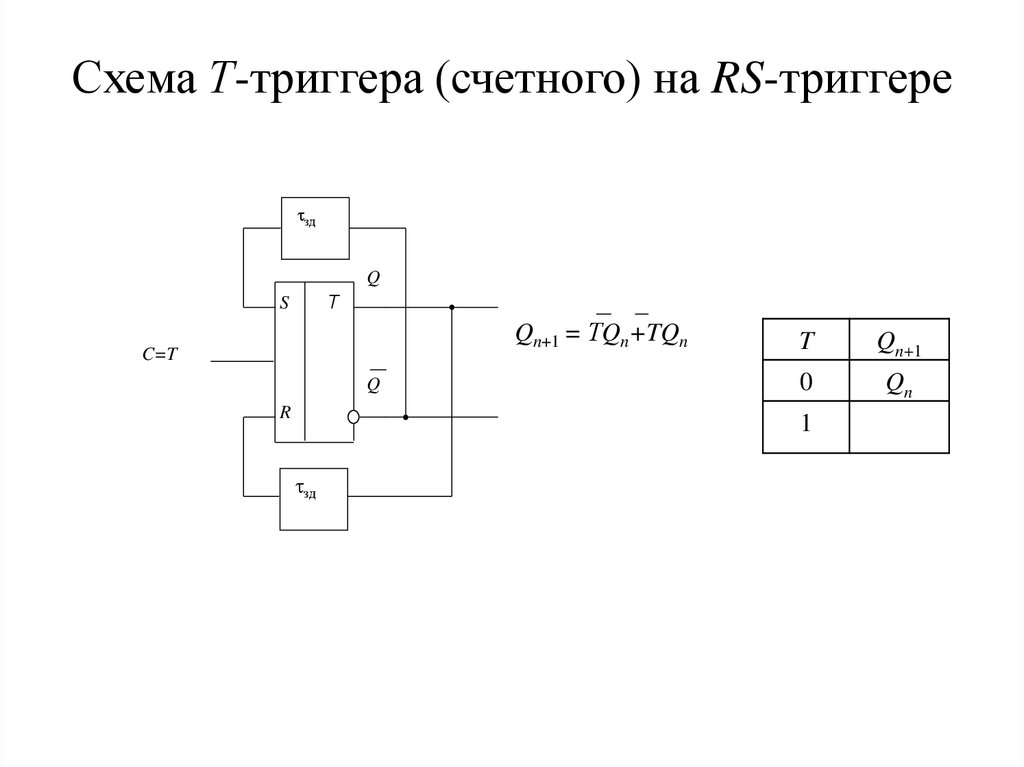

13. Схема Т-триггера (счетного) на RS-триггере

здQ

T

S

Qn+1 = ТQn+TQn

C=T

Q

R

T

Qn+1

0

Qn

1

зд

14. Структурная схема универсального статического JK-триггера на RS-триггере

J&

Q

S

J

=

C

J

T

C

Q

R

K

Q

T

Q

K

K

&

J

K

Qn

Qn+1

0

0

0

0

0

0

1

1

0

1

0

0

0

1

1

0

1

0

0

1

1

0

1

1

1

1

0

1

1

1

1

0

15.

QS

J

Q

D

TT

J

TT

C

C

K

а

б

J

C

б - DC-триггер

в – асинхронный Т-триггер

г - синхронный Т-триггер

TT

C

Q

K

Q

K

в

Построение триггеров на основе JK-триггера:

а - синхронный RS-триггер

Q

C

Q

K

T

TT

T

Q

R

Q

J

C

C

“1”

г

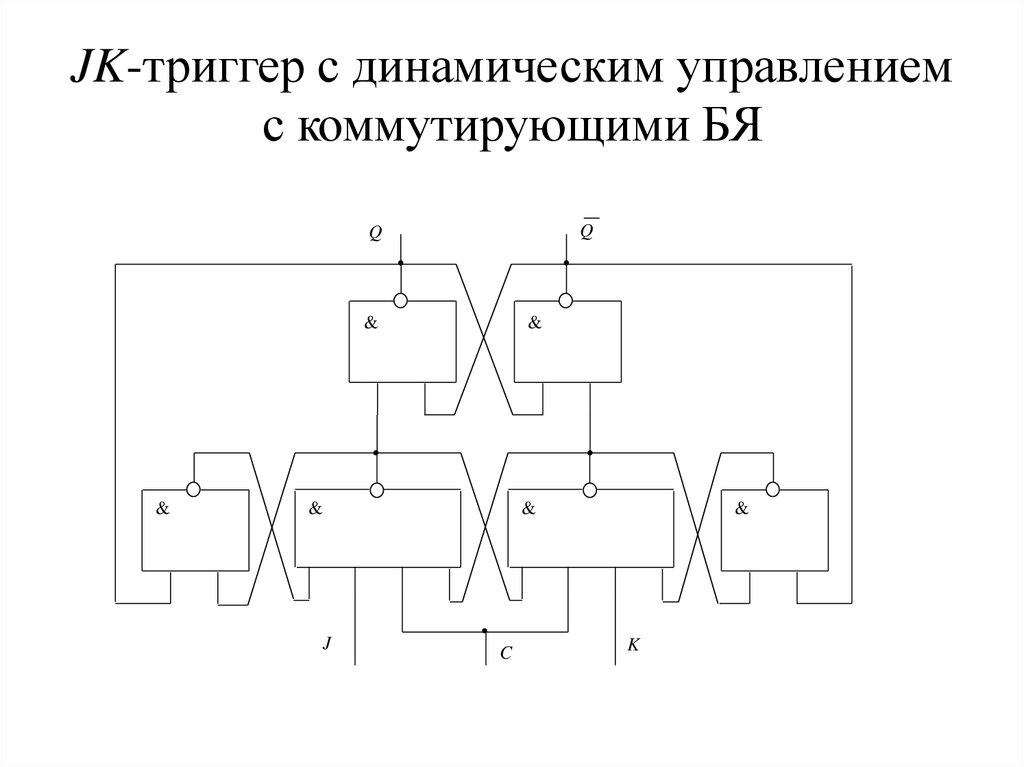

16. JK-триггер с динамическим управлением с коммутирующими БЯ

QQ

&

&

&

&

J

&

C

&

K

17.

J&

&

Q

J

T

J

T

C(C)

Q

K

&

K

K

&

C(C)

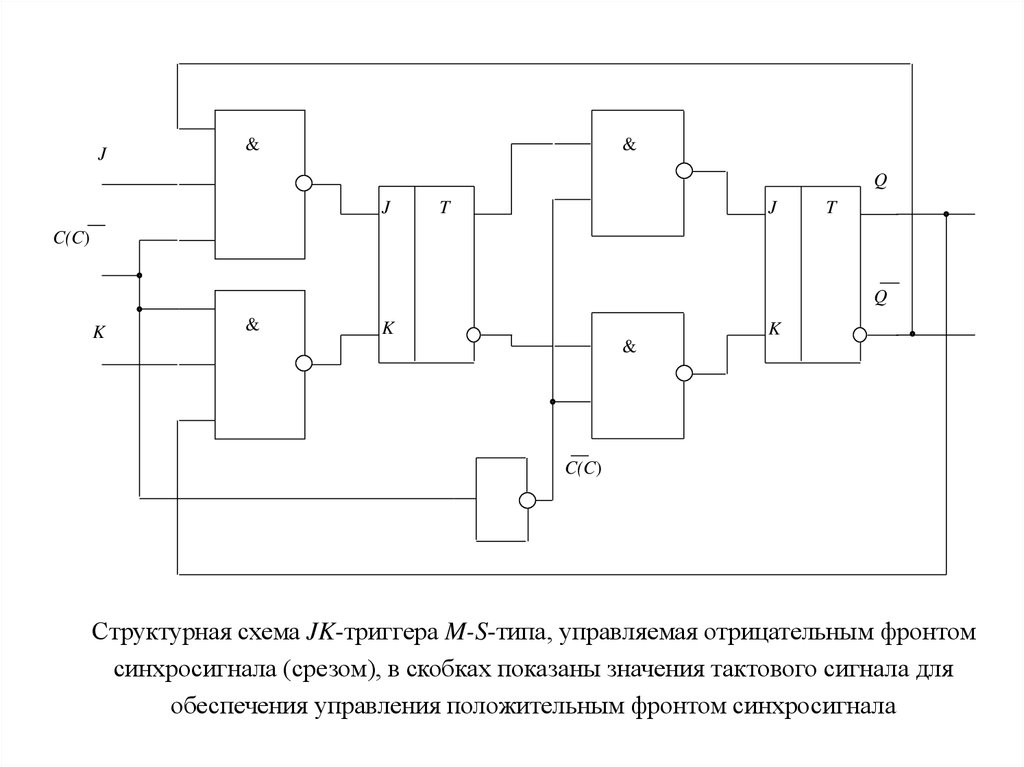

Структурная схема JK-триггера M-S-типа, управляемая отрицательным фронтом

синхросигнала (срезом), в скобках показаны значения тактового сигнала для

обеспечения управления положительным фронтом синхросигнала

18.

SS

&

V

&

&

Q

&

Q

&

C

&

&

&

R

R

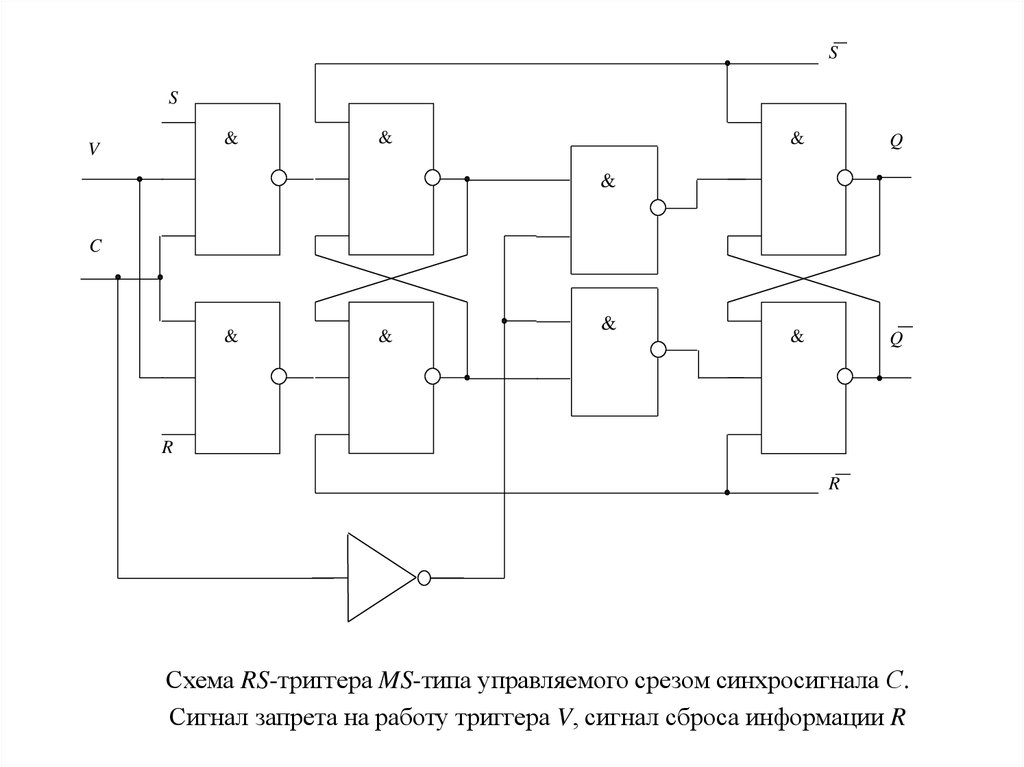

Схема RS-триггера MS-типа управляемого срезом синхросигнала С.

Сигнал запрета на работу триггера V, сигнал сброса информации R

19.

CS

R

V

R

Qn+1

Qn+1(V)

Qn+1(R)

Qn+1(V,R)

t

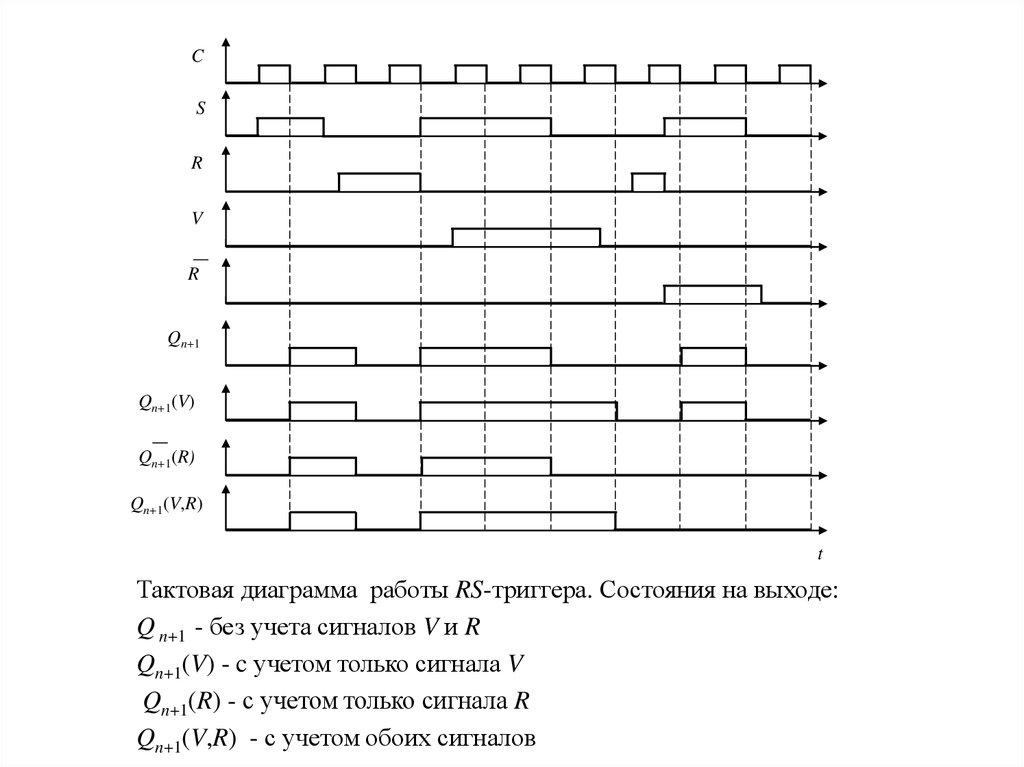

Тактовая диаграмма работы RS-триггера. Состояния на выходе:

Q n+1 - без учета сигналов V и R

Qn+1(V) - c учетом только сигнала V

Qn+1(R) - с учетом только сигнала R

Qn+1(V,R) - с учетом обоих сигналов

electronics

electronics