Similar presentations:

Параллельные архитектуры. Классификация параллельных систем по Флинну

1.

ТЕМА 1. АРХИТЕКТУРА ИФУНКЦИОНИРОВАНИЕ СОВРЕМЕННЫХ

ПАРАЛЛЕЛЬНЫХ ПРОЦЕССОРОВ.

Лекция 2. Параллельные архитектуры.

Классификация параллельных систем по

Флинну.

2. Литература:

1. Степанов А.Н. Архитектура вычислительныхсистем и компьютерных сетей. – СПб.: Питер, 2007.

– 509с.

2. Воеводин В.В., Воеводин Вл.В. Параллельные

вычисления. - СПб.: БХВ-Петербург, 2002.- 608 с.

3. Лацис А. Как построить и использовать

суперкомпьютер.- М.: Бестселлер, 2003.-240с.

4.

www.parallel.rb.ru

3.

4.

В узком смысле под архитектурой понимается архитектуранабора команд.

В широком смысле архитектура охватывает понятие организации

системы, включающее такие высокоуровневые аспекты разработки

компьютера как систему памяти, структуру системной шины,

организацию ввода/вывода и т.п.

Применительно к вычислительным системам - "архитектура" это

распределение функций, реализуемых системой, между ее уровнями,

точнее как определение границ между этими уровнями.

Архитектура первого уровня определяет, какие функции по

обработке данных выполняются системой в целом, а какие

возлагаются на внешний мир.

Архитектура следующего уровня определяет разграничение

функций между процессорами ввода/вывода и контроллерами

внешних устройств.

5.

АРХИТЕКТУРА СИСТЕМЫ - емкое понятие, включающеетри важнейших вида взаимосвязанных структур:

ФИЗИЧЕСКУЮ, ЛОГИЧЕСКУЮ и ПРОГРАММНУЮ.

Элементами ФИЗИЧЕСКОЙ

СТРУКТУРЫ являются

технические объекты. В

зависимости от того, какие

задачи решаются, этими

объектами могут быть

полупроводниковые кристаллы,

части вычислительных машин, а

также комплексы, составленные

из последних.

Элементами

ЛОГИЧЕСКОЙ

СТРУКТУРЫ являются

функции, определяющие

основные операции.

ПРОГРАММНУЮ

СТРУКТУРУ образуют

взаимосвязанные

программы: программы

обработки информации, и

др.

6.

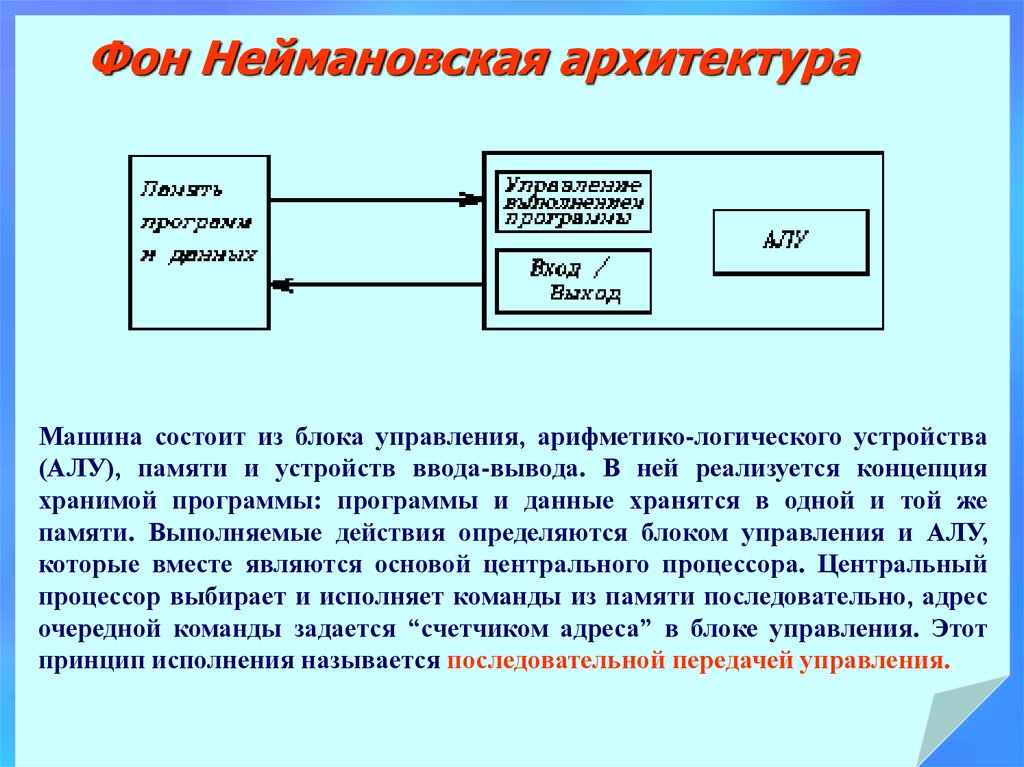

Фон Неймановская архитектураМашина состоит из блока управления, арифметико-логического устройства

(АЛУ), памяти и устройств ввода-вывода. В ней реализуется концепция

хранимой программы: программы и данные хранятся в одной и той же

памяти. Выполняемые действия определяются блоком управления и АЛУ,

которые вместе являются основой центрального процессора. Центральный

процессор выбирает и исполняет команды из памяти последовательно, адрес

очередной команды задается “счетчиком адреса” в блоке управления. Этот

принцип исполнения называется последовательной передачей управления.

7.

3 основных признака фон Неймановскойархитектуры (Принстонская):

1. память состоит из последовательности ячеек памяти с

адресами;

2. хранение команд программы и обрабатываемых ими

данных - на одинаковых принципах (с точки зрения

обработки сообщений);

3. программа выполняется покомандно, в соответствии с

их порядком. УУ – централизовано.

Почему ФН уже не удовлетворяет?

Первое – это скорость, сейчас в усредненной задачи от скорости

работы CPU зависит не так уж много – важнее скорость работы

памяти и других передач данных. Узкое место – единый тракт.

АЛЬТЕРНАТИВА – параллельная обработка, совмещение

операций.

8.

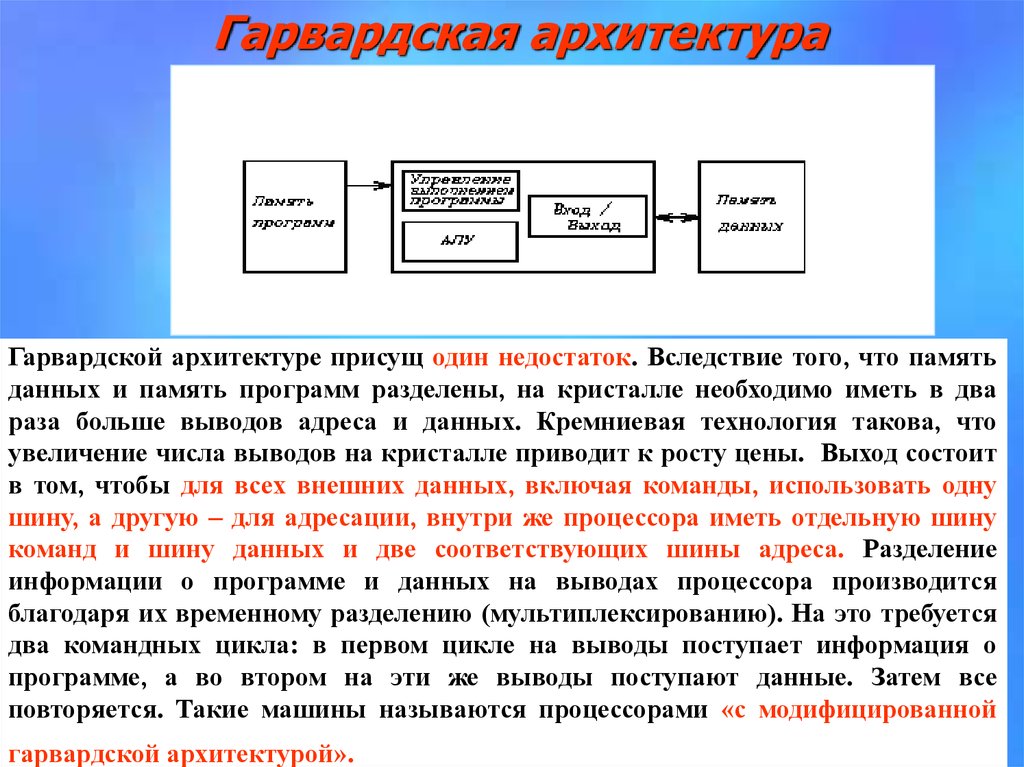

Гарвардская архитектураГарвардской архитектуре присущ один недостаток. Вследствие того, что память

данных и память программ разделены, на кристалле необходимо иметь в два

раза больше выводов адреса и данных. Кремниевая технология такова, что

увеличение числа выводов на кристалле приводит к росту цены. Выход состоит

в том, чтобы для всех внешних данных, включая команды, использовать одну

шину, а другую – для адресации, внутри же процессора иметь отдельную шину

команд и шину данных и две соответствующих шины адреса. Разделение

информации о программе и данных на выводах процессора производится

благодаря их временному разделению (мультиплексированию). На это требуется

два командных цикла: в первом цикле на выводы поступает информация о

программе, а во втором на эти же выводы поступают данные. Затем все

повторяется. Такие машины называются процессорами «с модифицированной

гарвардской архитектурой».

9.

10.

Упрощенные схемы коммутаторов: а) матричного; б)— каскадногоМП

ПЭ

МП

МП

МП

ПЭ – процессорный элемент

МП – модуль памяти

МК – матричный коммутатор

ПЭ

МК

2 2

МК

2 2

МП

ПЭ

ПЭ

МП

ПЭ

ПЭ

МП

ПЭ

ПЭ

МК

2 2

МК

2 2

МП

11.

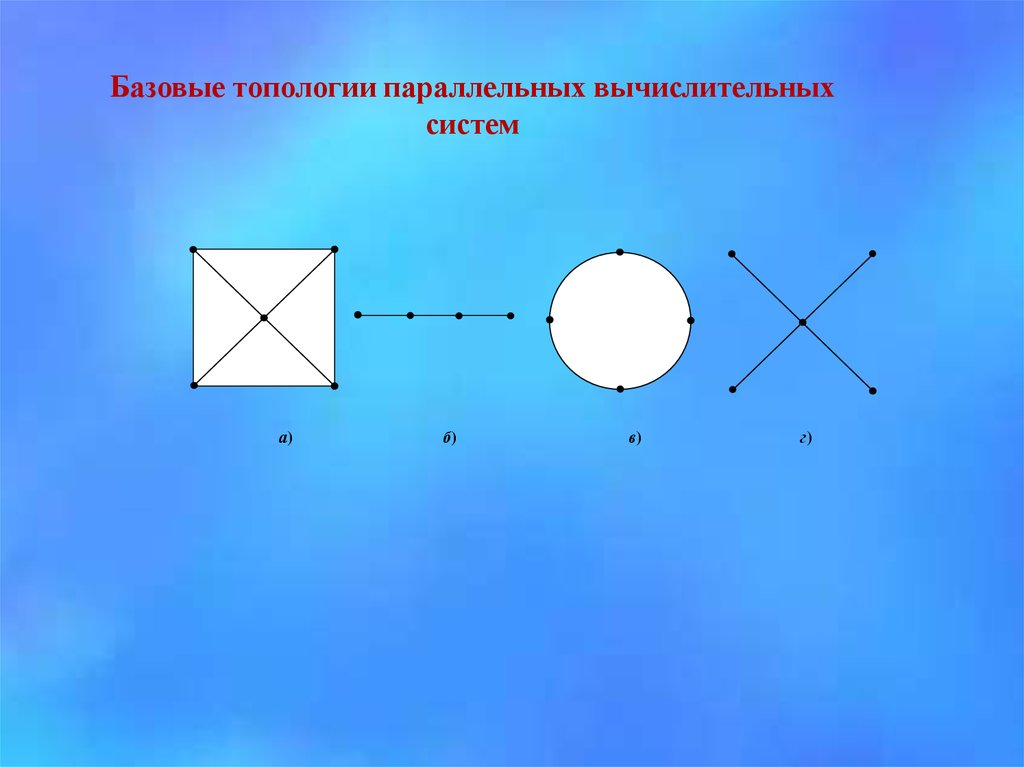

Базовые топологии параллельных вычислительныхсистем

а)

б)

в)

г)

12.

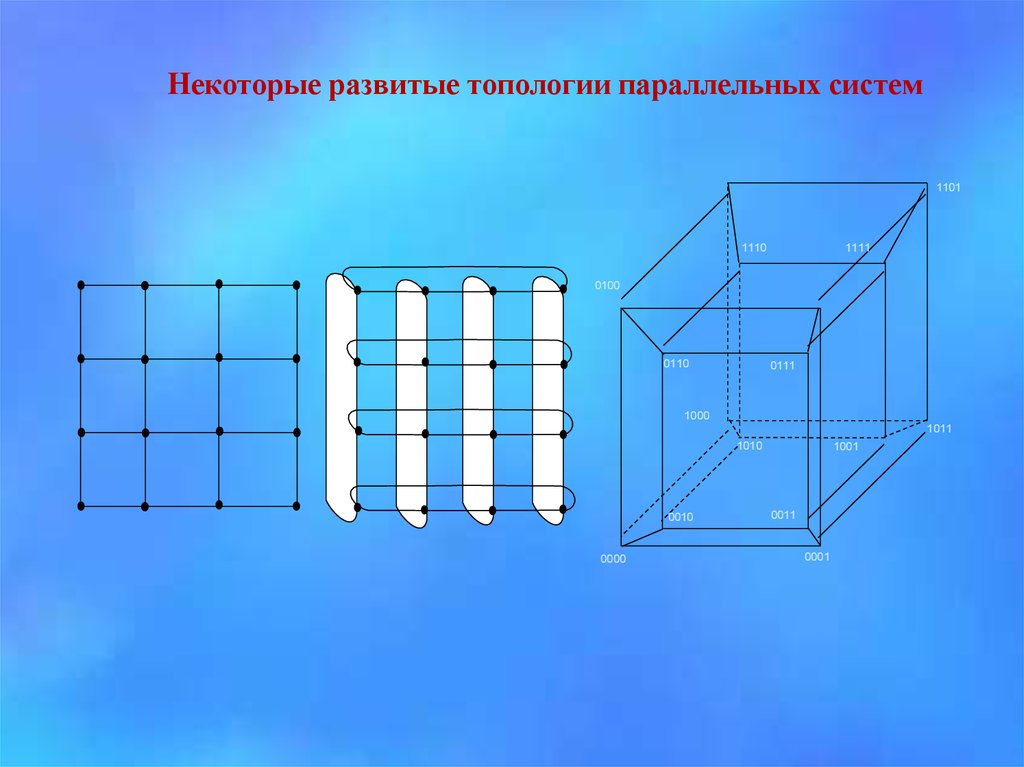

Некоторые развитые топологии параллельных систем1101

1110

1111

0100

0110

0111

1000

1011

1010

0010

0000

1001

0011

0001

13.

Многомашинная вычислительная система с косвеннойслабой связью

Процессор,

оперативная память

Процессор,

оперативная память

Устройства

ввода/вывода

Собственная

внешняя память,

ленты и диски

Общая внешняя

память, ленты

и диски

Собственная

внешняя память,

ленты и диски

Устройства

ввода/вывода

14.

Многомашинная вычислительная система спрямой слабой связью

Компьютер

Канал ввода/вывода

и/или адаптер

Канал ввода/вывода

и/или адаптер

Компьютер

15.

Многопроцессорная вычислительная система с сильнойсвязью

Процессорный элемент

Процессорный элемент

Оперативная

память

Внешняя память,

ленты и

диски

Устройства

ввода/вывода

16.

Фрагмент классификации ФлиннаВычислительные системы

МК

ОК

Фоннеймановские

системы

ОКОДР

ОКОДС

ПоразрядПословн

ная

обработка

ОКМД

ОКОД

ая

обработ

ка

ОКМДС

ОКМДР

МКОД

МКМД

МКОДС

МКОДР

Класс

пуст

Класс

пуст

Массивно- Ассоциативпараллельн ные системы

ые

векторноконвейерны

е системы

МКМДС

МКМДР

Класс

пуст

МКМДС/Нс

МКМДС/Вс

Многомашин-

Многопроцессор-

ные системы

ные системы

17.

Архитектуры с одиночным потоком команд: а —ОКОД; б — ОКМД

Процессорный элемент

Процессорный элемент

Процессорный

элемент

Одиночный

поток

данных

Одиночный

поток команд

Процессорный элемент

Множественн

ый поток

данных

Модуль памяти

Модуль памяти

18.

Упрощенная схема векторного процессора систем класса ОКМДСУстройство

управления

c a b

a

Векторный регистр

Векторное АЛУ

b

Векторный регистр

Векторный регистр

19.

Упрощенная схема вычислительной системы ILLIAС IVУстройство управления

Широковещательные команды

ПЭ

ПЭ

ПЭ

ПЭ

ПЭ

ПЭ

ПЭ

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

ПЭ

МП

МП

МП

МП

МП

МП

МП

МП

Матрица процессорных элементов (ПЭ)/модулей памяти (МП) 8х8 узлов

20.

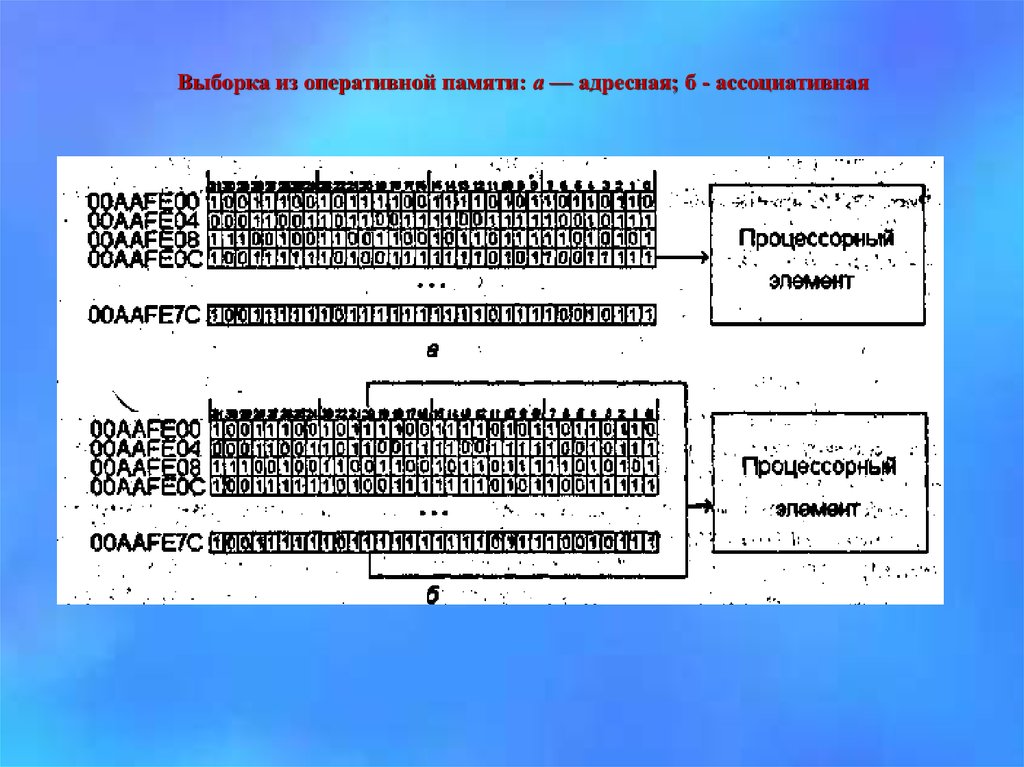

Выборка из оперативной памяти: а — адресная; б - ассоциативная21.

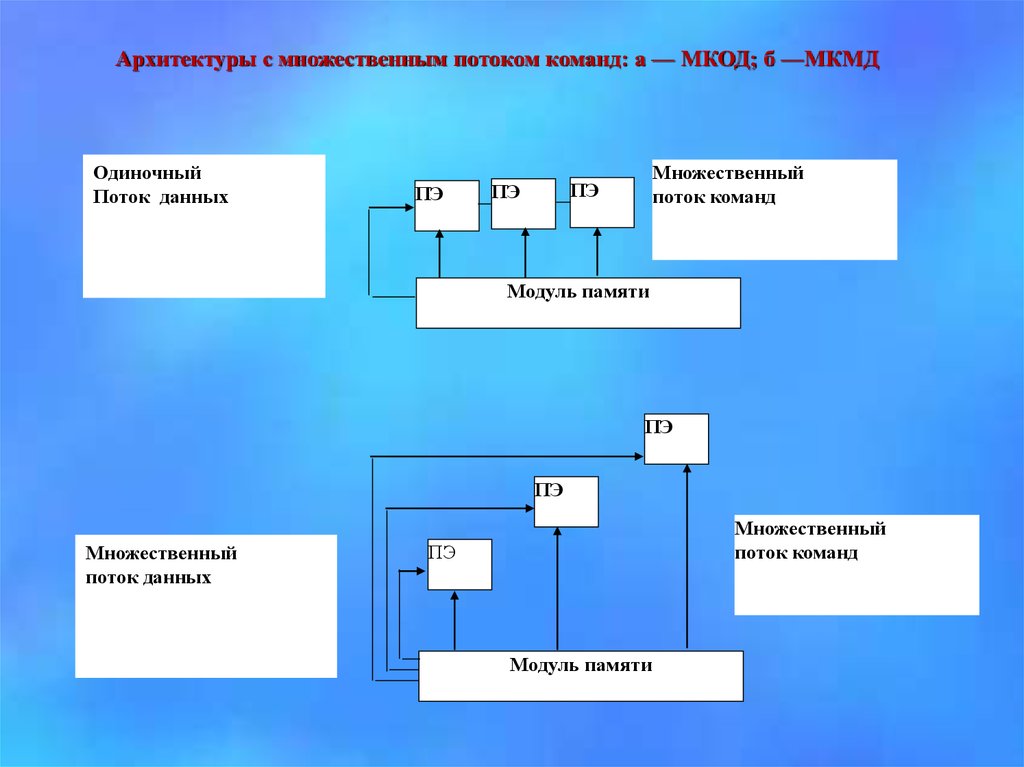

Архитектуры с множественным потоком команд: а — МКОД; б —МКМДОдиночный

Поток данных

ПЭ

Множественный

поток команд

ПЭ

ПЭ

Модуль памяти

ПЭ

ПЭ

Множественный

поток данных

Множественный

поток команд

ПЭ

Модуль памяти

22.

Современная классификация систем класса МКМДВычислительные системы класса МКМД

Многопроцессорные системы,

совместное использование памяти

UMA SMP

NUMA

NC NUMA

COMA

CC NUMA

Многомашинные системы,

Системы с передачей сообщений

MPP

COW

electronics

electronics