Similar presentations:

A-SSCC 2005 Tokyo Press Conference. Asian Solid-State Circuits Conference

1.

A-SSCC 2005 Tokyo Press Conference- Asian Solid-State Circuits Conference -

第一回アジア固体回路会議

http://www.a-sscc.org/

2005年9月5日

2005年9月6日

2005年9月7日

台湾 記者会見

韓国 記者会見

日本 記者会見

東京記者会見 2005年9月7日@東京大学

本日の電子データは以下のサイトにございます

http://www.vdec.u-tokyo.ac.jp/A-SSCC2005/

2.

記者会見次第開会のご挨拶

A-SSCC2005プログラム委員長

桜井 貴康 東京大学

A-SSCC概要のご説明

A-SSCC2005プログラム委員長

桜井 貴康 東京大学

招待講演・パネルのご説明

Invited Program Chair

黒田 忠広 慶応大学

インダストリープログラムのご説明

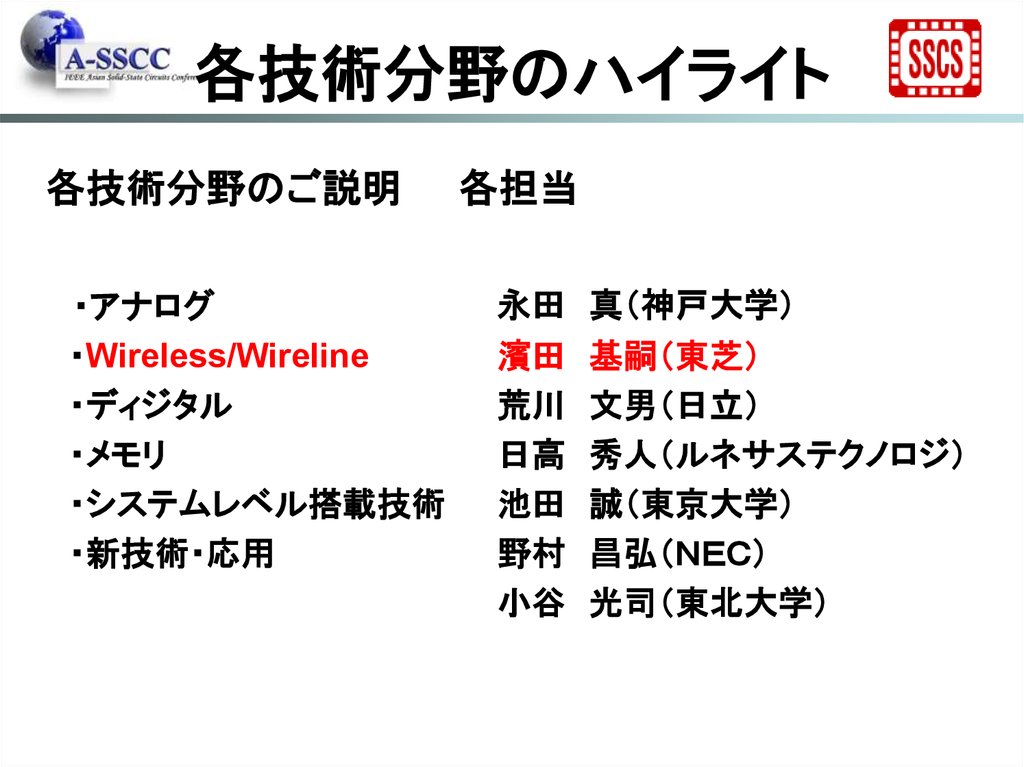

各技術分野のご説明

・アナログ

・Wireless/Wireline

・ディジタル

・メモリ

・システムレベルインテグレーション

・新技術・応用

質疑応答

黒田 忠広 慶応大学

各担当

永田

濱田

荒川

日高

池田

野村

真 神戸大学

基嗣 東芝

文男 日立

秀人 ルネサステクノロジ

誠 東京大学

昌弘 、小谷 光司 東北大学

時 分終了予定

3.

A-SSCCとは• IEEE Solid-State Circuits Society (SSCS)主催の 番目*

の学会として、Asian Solid-State Circuits Conference (ASSCC)が今年誕生。アジアに集積回路設計の新しい風を。今

後、毎年 月頃アジア地区で開催。

昨年までは2月のISSCC (International Solid-State Circuit

Conference)、 月のVLSI回路シンポジウム、 月のCICC (Custom

Integrated Circuits Conference) の つ

*)

• なぜ、今アジアか

– 今後急速に発展するアジア

– アジアの学生、研究者、技術者の啓蒙と技術交流の場

– アジアの技術論文の掘り起こし 現存の学会とは競合しない

4.

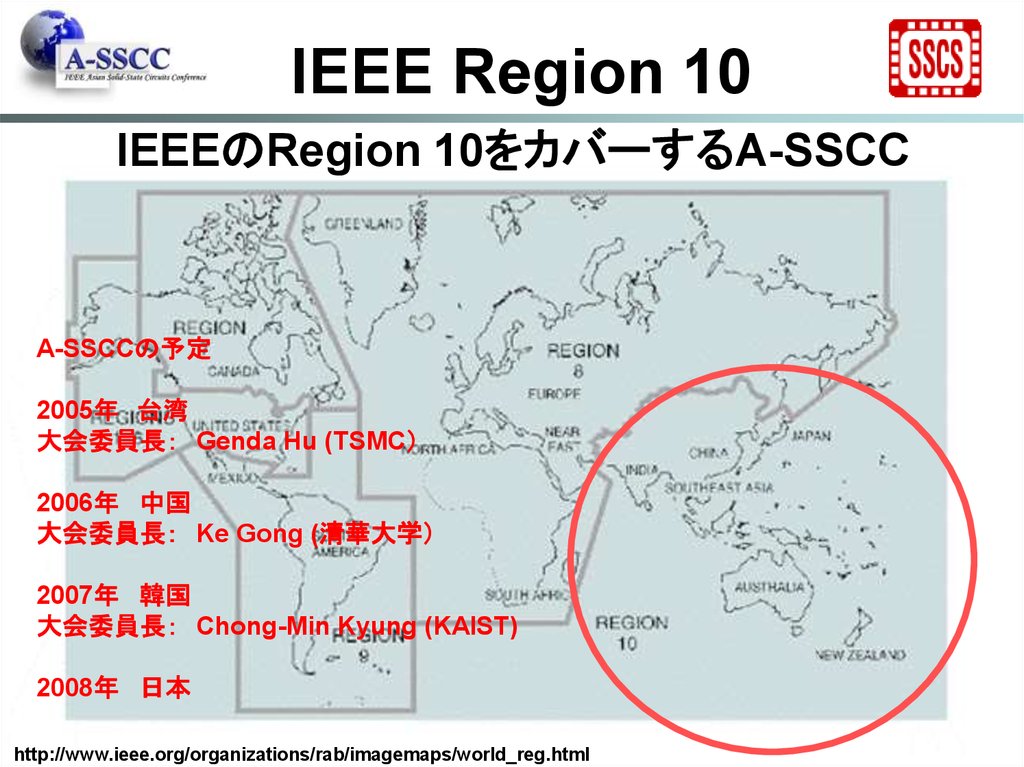

IEEE Region 10IEEEのRegion 10をカバーするA-SSCC

A-SSCCの予定

2005年 台湾

大会委員長 Genda Hu (TSMC

2006年 中国

大会委員長 Ke Gong (清華大学

2007年 韓国

大会委員長 Chong-Min Kyung (KAIST)

2008年 日本

http://www.ieee.org/organizations/rab/imagemaps/world_reg.html

5.

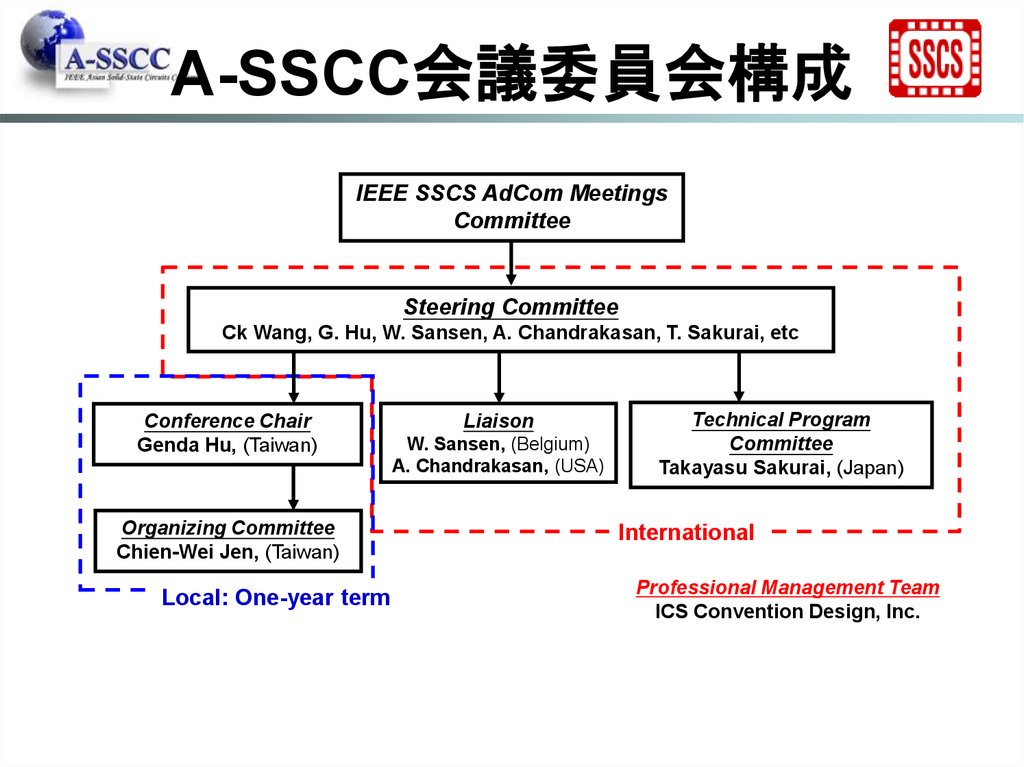

A-SSCC会議委員会構成IEEE SSCS AdCom Meetings

Committee

Steering Committee

Ck Wang, G. Hu, W. Sansen, A. Chandrakasan, T. Sakurai, etc

Conference Chair

Genda Hu, (Taiwan)

Organizing Committee

Chien-Wei Jen, (Taiwan)

Local: One-year term

Liaison

W. Sansen, (Belgium)

A. Chandrakasan, (USA)

Technical Program

Committee

Takayasu Sakurai, (Japan)

International

Professional Management Team

ICS Convention Design, Inc.

6.

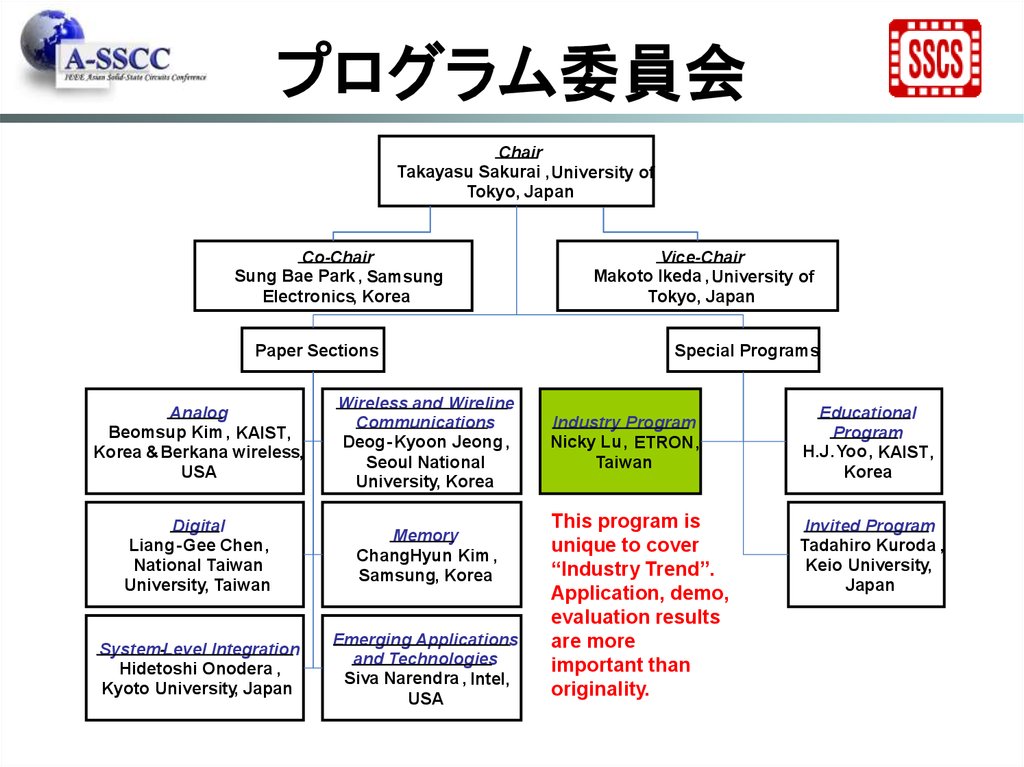

プログラム委員会Chair

Takayasu Sakurai , University of

Tokyo, Japan

Co-Chair

Sung Bae Park , Samsung

Electronics, Korea

Paper Sections

Analog

Beomsup Kim , KAIST,

Korea & Berkana wireless,

USA

Wireless and Wireline

Communications

Deog- Kyoon Jeong ,

Seoul National

University, Korea

Digital

Liang-Gee Chen,

National Taiwan

University, Taiwan

Memory

ChangHyun Kim ,

Samsung, Korea

System-Level Integration

Hidetoshi Onodera ,

Kyoto University, Japan

Emerging Applications

and Technologies

Siva Narendra , Intel,

USA

Vice-Chair

Makoto Ikeda , University of

Tokyo, Japan

Special Programs

Industry Program

Nicky Lu , ETRON,

Taiwan

This program is

unique to cover

“Industry Trend”.

Application, demo,

evaluation results

are more

important than

originality.

Educational

Program

H.J.Yoo, KAIST,

Korea

Invited Program

Tadahiro Kuroda ,

Keio University,

Japan

7.

A-SSCC 2005• 初回である今年は、”Digital Consumer Age in Asia”という

テーマのもと、11月1 3日、台湾 新竹市 アンバサダーホテ

ルにて開催

• アジアへの情報発信、アジアからの情報収集の場

産業界のトレンドがわかるインダストリー・プログラム

世界の講師を招いたチュートリアル

アジアならではの つの基調講演

高倍率の選別を受けたテクニカル論文

• ISSCC、IEEE Journal of Solid-State Circuitとも連携企画

8.

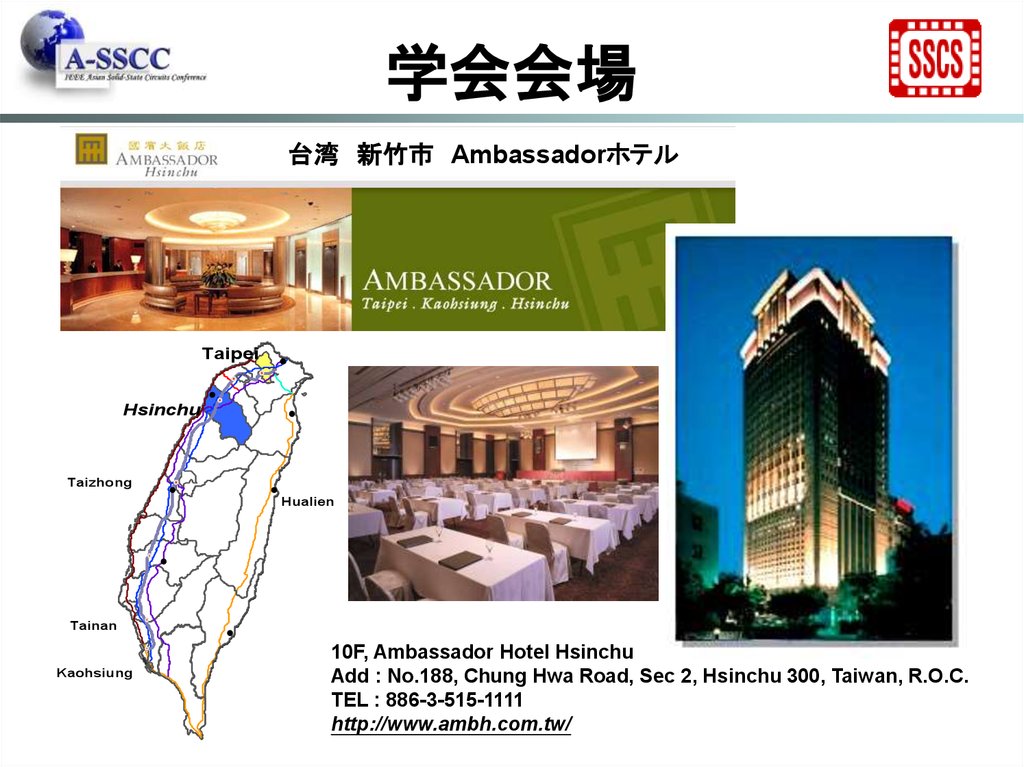

学会会場台湾 新竹市 Ambassadorホテル

Taipei

Hsinchu

Taizhong

Hualien

Tainan

Kaohsiung

10F, Ambassador Hotel Hsinchu

Add : No.188, Chung Hwa Road, Sec 2, Hsinchu 300, Taiwan, R.O.C.

TEL : 886-3-515-1111

http://www.ambh.com.tw/

9.

チュートリアル• 項目のチュートリアル講演を実施

– Analog/Wireless分野

”Analog Circuit Design Towards Nanometer Technologies”

M. Steyaert, K.U. Leuven

– Digital/Wireline分野

”PLL/DLL”

C.K. Ken Yang, UCLA

– Memory分野

”High Performance DRAM Design”

Young-Hyun Jun, Samsung

– New Technology分野

”Crypto Chip Design”

Cetin Kaya Koc, Oregon State Univ.

10.

ツアー11/4午前 テクニカルツアー

8:30am Set out from Ambassador Hotel, Hsinchu 新竹國賓飯店

9:00am Visit Hsinchu Science Based Industrial Park 新竹科學園區管理局

10:00am Visit TSMC 台灣積體電路製造股份有限公司

11:00am Industrial Technology Research Institute ( 工研院 )

12:00am Back to Ambassador Hotel, Hsinchu( 新竹國賓飯店 )

11/4午後 カルチャーツアー

12:30 Departure from Ambassador Hotel, Hsinchu 新竹國賓飯店

14:30 Visit National Palace Museum Taipei 台北故宮博物院

17:00 Departure to Shih-lin Night Market Taipei 台北士林夜市

17:30 Visit Shih-lin Night Market Taipei

19:00 Back to Ambassador Hotel Hsinchu 新竹國賓飯店

21:00 Arrive in Ambassador Hotel Hsinchu

11.

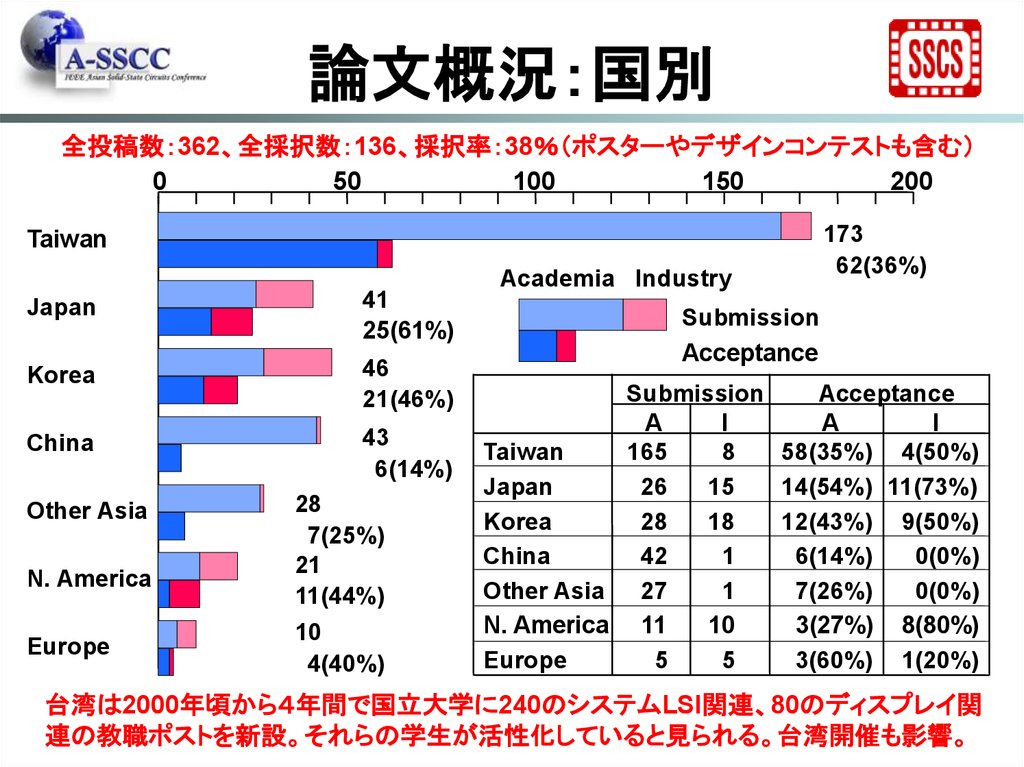

論文概況 国別全投稿数 362、全採択数 136、採択率 38 ポスターやデザインコンテストも含む

0

50

100

150

200

Taiwan

Japan

41

25(61%)

Korea

46

21(46%)

China

43

6(14%)

Other Asia

N. America

Europe

28

7(25%)

21

11(44%)

10

4(40%)

Academia Industry

173

62(36%)

Submission

Acceptance

Submission

Acceptance

A

I

A

I

Taiwan

165

8

58(35%) 4(50%)

Japan

26

15

14(54%) 11(73%)

Korea

28

18

12(43%) 9(50%)

China

42

1

6(14%)

0(0%)

Other Asia 27

1

7(26%)

0(0%)

N. America 11

10

3(27%) 8(80%)

Europe

5

5

3(60%) 1(20%)

台湾は2000年頃から 年間で国立大学に240のシステムLSI関連、80のディスプレイ関

連の教職ポストを新設。それらの学生が活性化していると見られる。台湾開催も影響。

12.

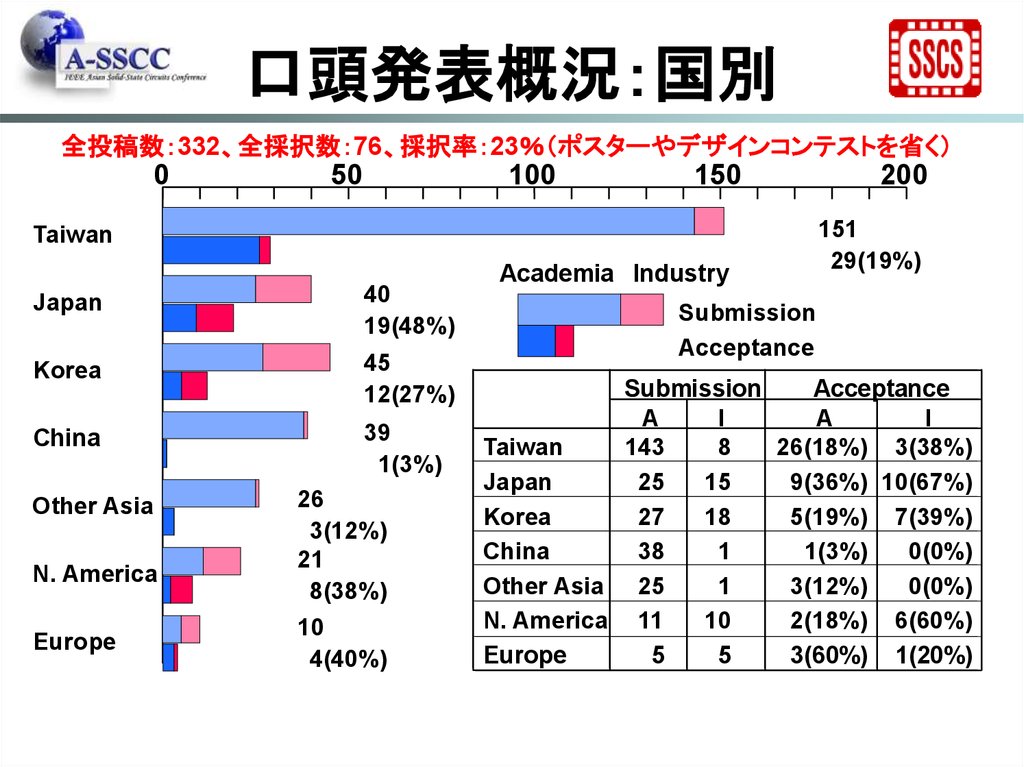

口頭発表概況 国別全投稿数 332、全採択数 76、採択率 23 ポスターやデザインコンテストを省く

0

50

100

150

Taiwan

Japan

40

19(48%)

Korea

45

12(27%)

China

39

1(3%)

Other Asia

N. America

Europe

26

3(12%)

21

8(38%)

10

4(40%)

Academia Industry

200

151

29(19%)

Submission

Acceptance

Submission

Acceptance

A

I

A

I

Taiwan

143

8

26(18%) 3(38%)

Japan

25

15

9(36%) 10(67%)

Korea

27

18

5(19%) 7(39%)

China

38

1

1(3%)

0(0%)

Other Asia 25

1

3(12%)

0(0%)

N. America 11

10

2(18%) 6(60%)

Europe

5

5

3(60%) 1(20%)

13.

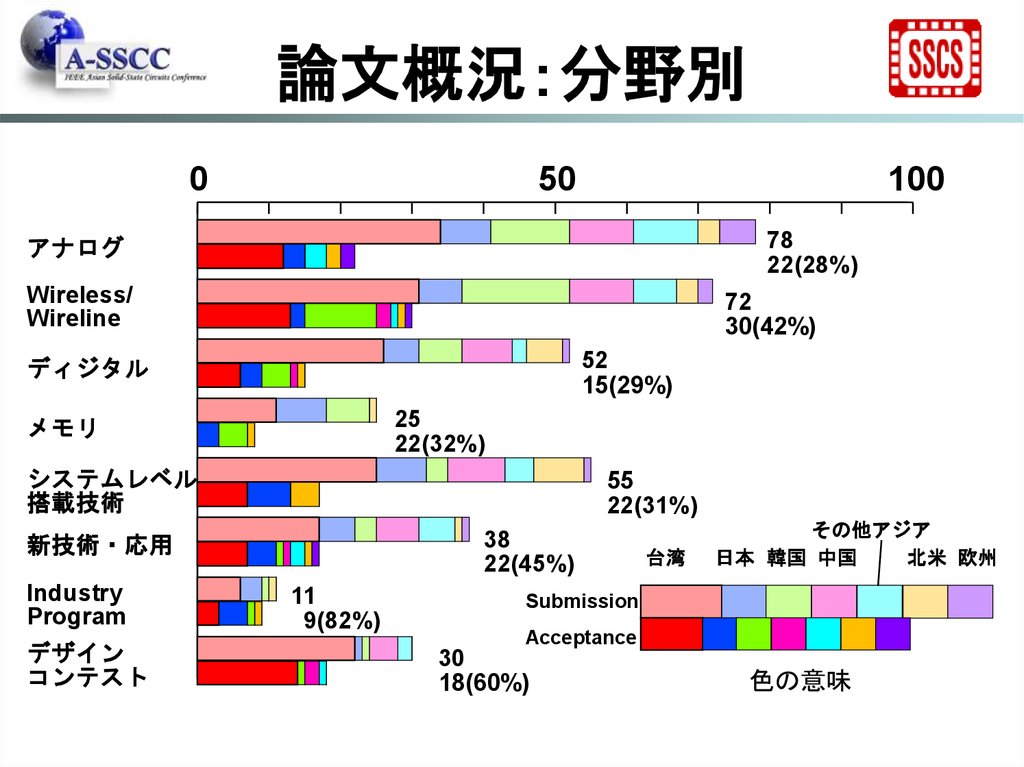

論文概況 分野別0

50

100

78

22(28%)

アナログ

Wireless/

Wireline

72

30(42%)

52

15(29%)

ディジタル

25

22(32%)

メモリ

システムレベル

搭載技術

55

22(31%)

38

22(45%)

新技術・応用

Industry

Program

デザイン

コンテスト

11

9(82%)

台湾

その他アジア

日本 韓国 中国

北米 欧州

Submission

Acceptance

30

18(60%)

色の意味

14.

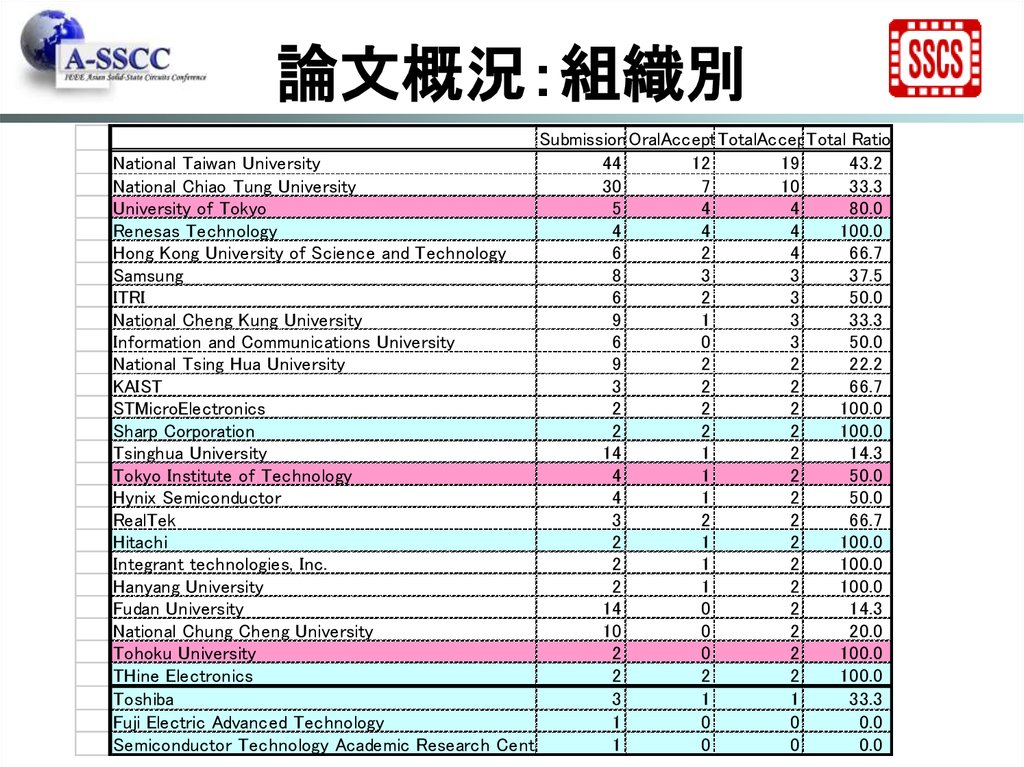

論文概況 組織別Submission OralAcceptTotalAcceptTotal Ratio

National Taiwan University

44

12

19

43.2

National Chiao Tung University

30

7

10

33.3

University of Tokyo

5

4

4

80.0

Renesas Technology

4

4

4

100.0

Hong Kong University of Science and Technology

6

2

4

66.7

Samsung

8

3

3

37.5

ITRI

6

2

3

50.0

National Cheng Kung University

9

1

3

33.3

Information and Communications University

6

0

3

50.0

National Tsing Hua University

9

2

2

22.2

KAIST

3

2

2

66.7

STMicroElectronics

2

2

2

100.0

Sharp Corporation

2

2

2

100.0

Tsinghua University

14

1

2

14.3

Tokyo Institute of Technology

4

1

2

50.0

Hynix Semiconductor

4

1

2

50.0

RealTek

3

2

2

66.7

Hitachi

2

1

2

100.0

Integrant technologies, Inc.

2

1

2

100.0

Hanyang University

2

1

2

100.0

Fudan University

14

0

2

14.3

National Chung Cheng University

10

0

2

20.0

Tohoku University

2

0

2

100.0

THine Electronics

2

2

2

100.0

Toshiba

3

1

1

33.3

Fuji Electric Advanced Technology

1

0

0

0.0

Semiconductor Technology Academic Research Center (STARC)

1

0

0

0.0

15.

A-SSCC2005注目論文A Low Power Digital IC Design Inside the Wireless Endoscopy Capsule

無線内視鏡カプセル用低電力ディジタルIC設計

論文番号[10-2] 中国清華 Tsinghua 大学の発表

無線送受信部と 部の混載された完成度の高いシステムLSI

A 0.1-25.5-GHz Differential Cascaded-Distributed Amplifier in 0.18-um CMOS

Technology

論文番号[5-1] 台湾大学の発表

世界最高帯域(100MHz ~ 25.5GHz) の増幅器 様々な帯域の無線信号を チッ

プで増幅可能

A 142dB Dynamic Range CMOS Image Sensor with Multiple Exposure Time

Signals

論文番号[3-1] 静岡大学の発表

線形性を有する イメージセンサーとしては世界最高のダイナミックレンジを

有する

16.

招待講演・パネルのご説明黒田 忠広 慶応大学

17.

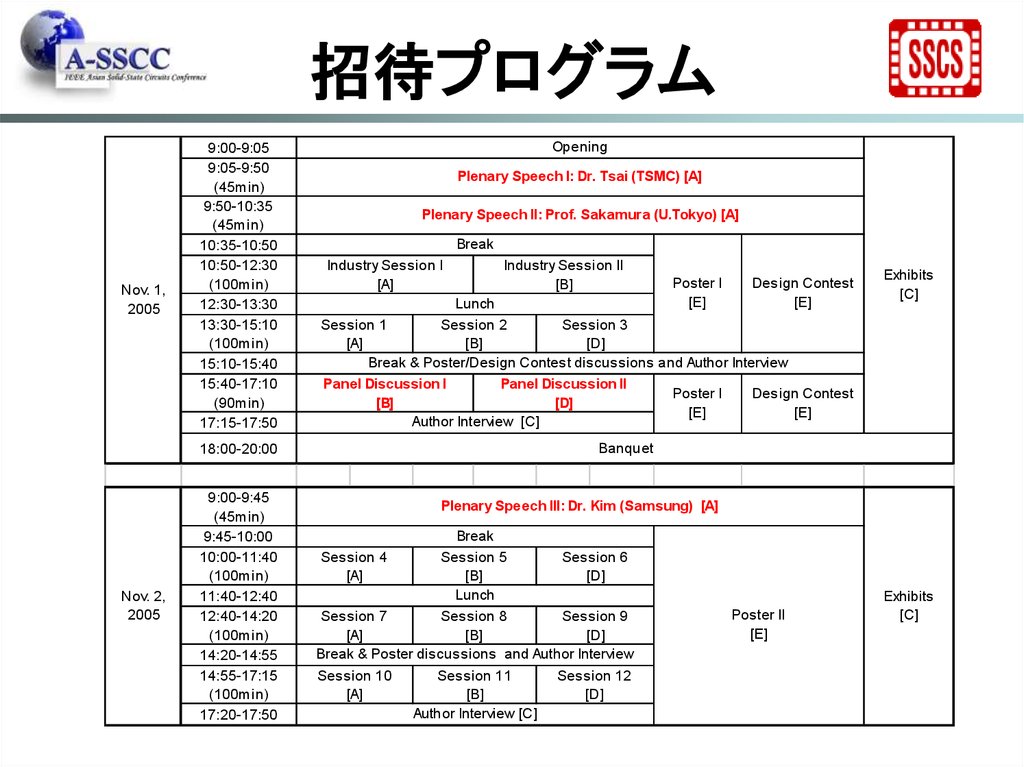

招待プログラムNov. 1,

2005

9:00-9:05

9:05-9:50

(45min)

9:50-10:35

(45min)

10:35-10:50

10:50-12:30

(100min)

12:30-13:30

13:30-15:10

(100min)

15:10-15:40

15:40-17:10

(90min)

17:15-17:50

18:00-20:00

Nov. 2,

2005

9:00-9:45

(45min)

9:45-10:00

10:00-11:40

(100min)

11:40-12:40

12:40-14:20

(100min)

14:20-14:55

14:55-17:15

(100min)

17:20-17:50

Opening

Plenary Speech I: Dr. Tsai (TSMC) [A]

Plenary Speech II: Prof. Sakamura (U.Tokyo) [A]

Break

Industry Session I

[A]

Industry Session II

[B]

Poster I

[E]

Design Contest

[E]

Lunch

Session 1

Session 2

Session 3

[A]

[B]

[D]

Break & Poster/Design Contest discussions and Author Interview

Panel Discussion I

Panel Discussion II

Poster I

Design Contest

[B]

[D]

[E]

[E]

Author Interview [C]

Exhibits

[C]

Banquet

Plenary Speech III: Dr. Kim (Samsung) [A]

Break

Session 4

Session 5

Session 6

[A]

[B]

[D]

Lunch

Session 7

Session 8

Session 9

[A]

[B]

[D]

Break & Poster discussions and Author Interview

Session 10

Session 11

Session 12

[A]

[B]

[D]

Author Interview [C]

Poster II

[E]

Exhibits

[C]

18.

プレナリー講演Rick Tsai 博士, TSMC CEO, 台湾

“Design and Technology Collaboration”

日時: 月 日 (火), 9:05-9:50

坂村 健 博士, 東京大学 教授, 日本

“T-Engine: The Open Platform for the Ubiquitous

Computing Age”

日時: 月 日 (火), 9:50-10:35

Kinam Kim 博士, サムスン電子 フェロー&上席副社長 , 韓国

“Memory Technologies for Mobile Era”

日時: 月 日 (水), 9:00-9:45

19.

プレナリー講演(1): Rick Tsai 博士“Design and Technology Collaboration”

Abstract: With the advancement of technology into nanometer

regime, the complexity of design at advanced technology has

escalated exponentially. Notable areas of difficulty are timing closure,

signal integrity, power optimization etc. Many of the issues facing

designers, however, can be lessened or resolved by close

collaboration with technology partners. Advanced foundries, with

estimated close to 40% of worldwide 90nm tapeouts, are taking

several initiatives to help designers make best use of the

technologies. The goal of the collaboration is to produce designs that

are competitive in both performance and cost structure. In this

presentation, I will discuss key initiatives in TSMC's design

collaboration and share collaboration results.

20.

プレナリー講演 (2): 坂村 健 教授“T-Engine: The Open Platform for the Ubiquitous

Computing Age”

Abstract: "T-Engine" is an open platform for embedded systems in

the ubiquitous computing age. It consists of standard real-time

kernel, T- Kernel, running on the standard hardware with networking

facilities. It provides infrastructure for the embedded system

development of highly networked and highly value-added products in

a short period of time. Providing a standard platform for the

ubiquitous computing network, the T Engine creates broad

application opportunities based on the collaboration of

nanoelectronics, software and embedded system technologies. This

plenary talk provides introduction of the T-Engine project and its

current status, and vision of the future of the ubiquitous computing

opened up by the T-Engine.

21.

プレナリー講演 (3): Kinam Kim 博士“Memory Technologies for Mobile Era”

Abstract: For last three decades, semiconductor memory business has

been greatly grown due to the tremendous progress of electronic data

processing (EDP) mainly led by outstanding evolution of PC technology.

Recently, various mobile appliances such as hand-held phone, DCS, and

MP3 drive new growth of semiconductor memory, which results in

unprecedented demand of non-volatile memories, especially mass

storage NAND Flash. The mobile appliances which aim for smaller and

lighter products while improving the performance under ever-increased

demand of longer battery lifetime impose different requirements on the

semiconductor memories. The newly defined requirements along with

short life cycle and customer orientation of mobile products transform

the memory semiconductor from standard data storage memory to

diverse solution memory. It is predicted that this trend will be magnified

in the future memory market. In this paper, it will be discussed about the

technology trend of memory semiconductor in the mobile era and also

the memory technology required to satisfy the mobile appliances.

22.

パネル討論 (1)“Wonder Drug for NRE Explosion: FPGA,

Reconfigurable Processor, Structured ASIC, SiP, or

Conventional Approach? ”

Abstract: Non-Recurring Engineering cost for chip design

is exploding. Design cost for chip and software is rapidly

increasing.

Only a handful of big projects can pay you with the

conventional approach. Middle and small volume products

may require a new solution. Could it be programmable

commodity devices such as FPGA and Reconfigurable

Processor, or emerging ASIC devices such as a structure

ASIC. Or, could it be an SiP approach where commodity

chips rather than IP’s are integrated in a package?

23.

パネル討論 (1)Organizer:

Moderator:

Panelists

Tadahiro Kuroda, Keio Univ., Japan

Tohru Furuyama, Toshiba, Japan

/ position:

Jiun-Hao Lai, GlobalUniChip, Taiwan /

Conventional

Hing Nan Cheng, Xilinx, Singapore / FPGA

Hideharu Amano, Keio Univ., Japan / DRP

Hsin-Shih Wang, Faraday Technology Corp.,

Taiwan / Structured ASIC

Kenji Yoshida, SFT, Japan / SiP

24.

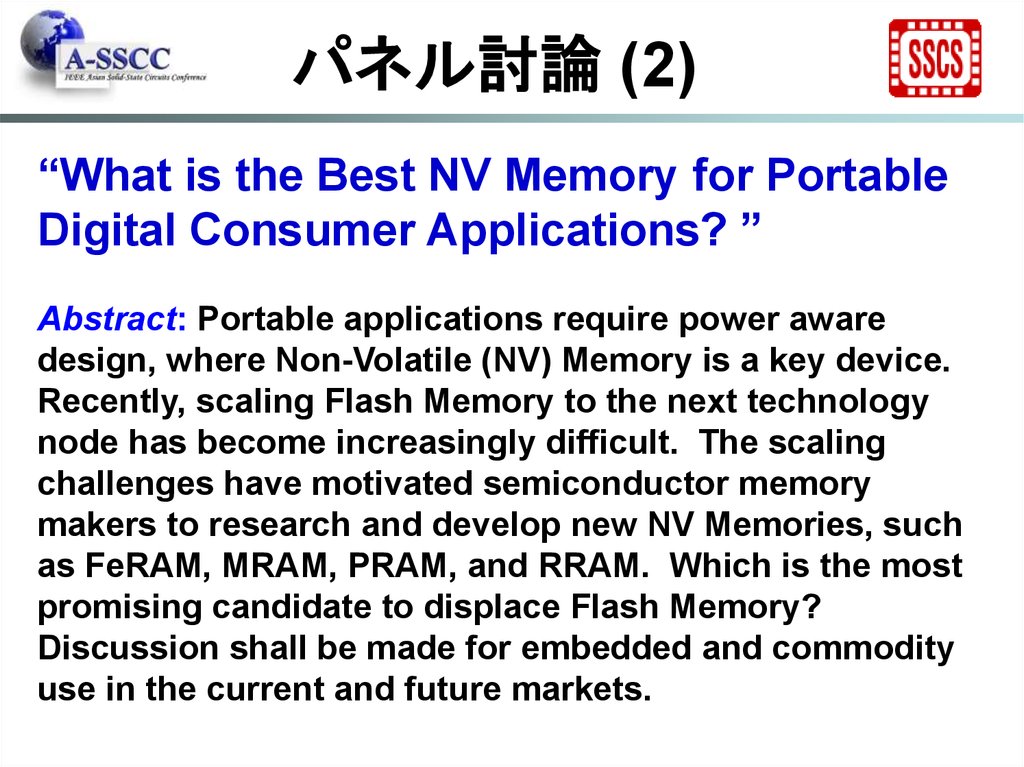

パネル討論 (2)“What is the Best NV Memory for Portable

Digital Consumer Applications? ”

Abstract: Portable applications require power aware

design, where Non-Volatile (NV) Memory is a key device.

Recently, scaling Flash Memory to the next technology

node has become increasingly difficult. The scaling

challenges have motivated semiconductor memory

makers to research and develop new NV Memories, such

as FeRAM, MRAM, PRAM, and RRAM. Which is the most

promising candidate to displace Flash Memory?

Discussion shall be made for embedded and commodity

use in the current and future markets.

25.

パネル討論 (2)Organizer:

Moderator:

Panelists

Tadahiro Kuroda, Keio Univ., Japan

Masao Taguchi, Spansion, Japan

/ position:

Shigeo Ohshima, Toshiba, Japan / Flash

Takashi Eshita, Fujitsu, Japan / FeRAM

Yoshiaki Asao, Toshiba, Japan / MRAM

Rich Liu, Micronix, Taiwan / PRAM

I. G. Baek, Samsung, Korea / RRAM

26.

インダストリー・プログラムのご説明黒田 忠広 慶応大学

27.

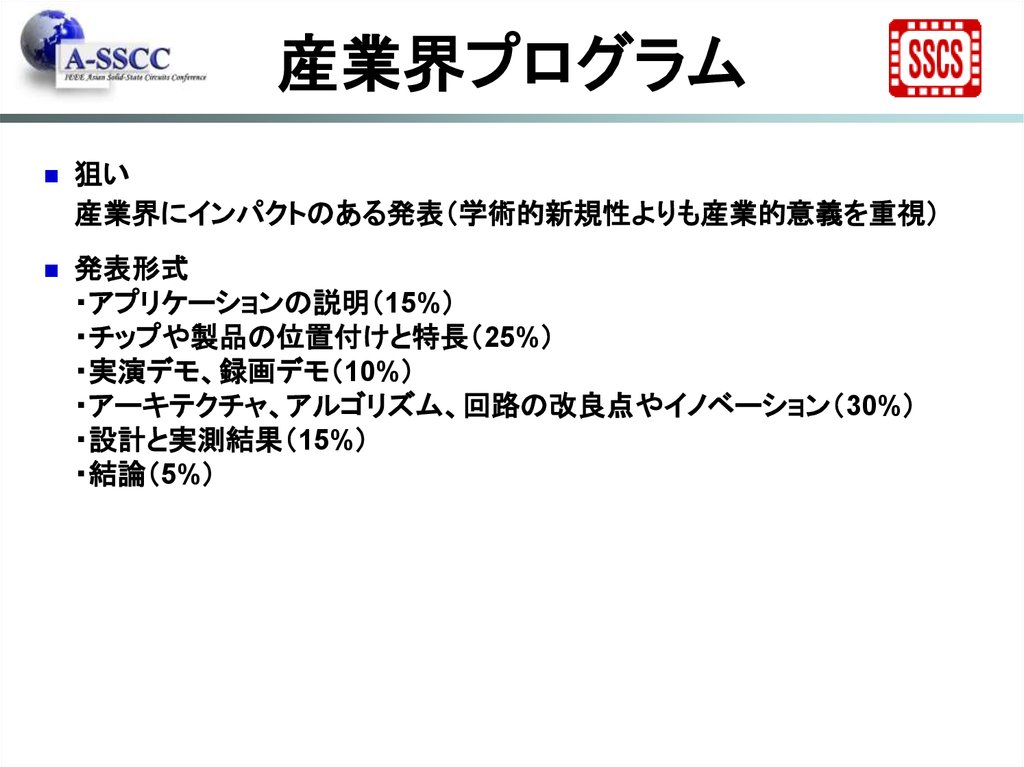

産業界プログラム狙い

産業界にインパクトのある発表 学術的新規性よりも産業的意義を重視

発表形式

・アプリケーションの説明 15%

・チップや製品の位置付けと特長 25%

・実演デモ、録画デモ 10%

・アーキテクチャ、アルゴリズム、回路の改良点やイノベーション 30%

・設計と実測結果 15%

・結論 5%

28.

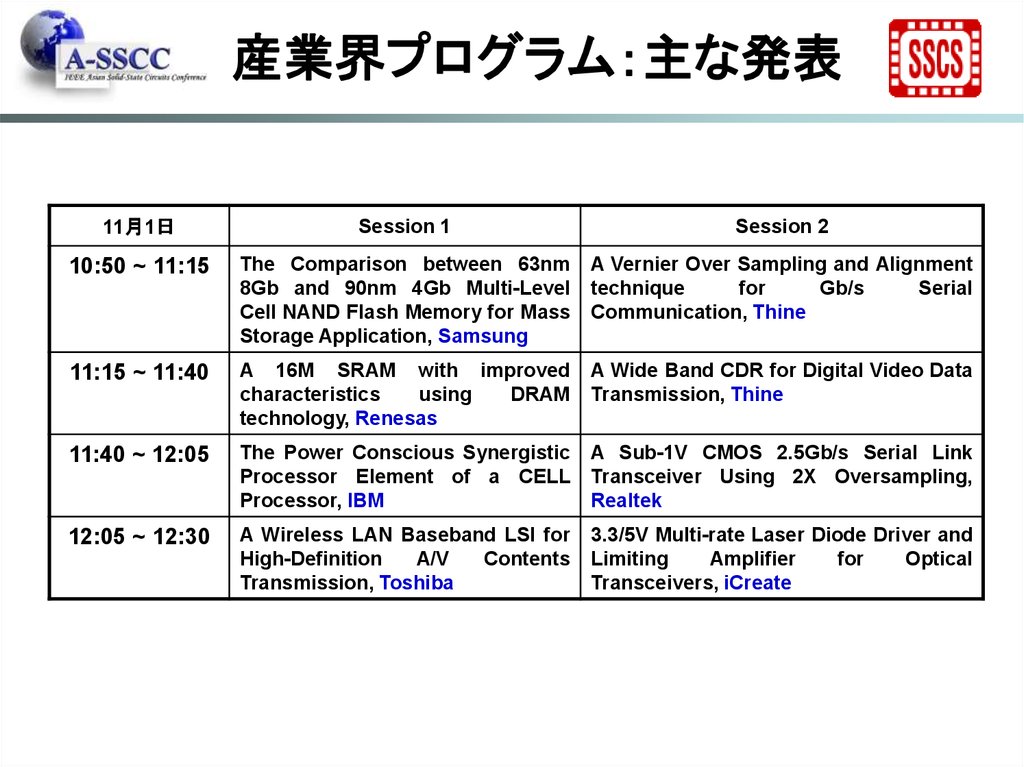

産業界プログラム 主な発表11月1日

Session 1

Session 2

10:50 ~ 11:15

The Comparison between 63nm

8Gb and 90nm 4Gb Multi-Level

Cell NAND Flash Memory for Mass

Storage Application, Samsung

A Vernier Over Sampling and Alignment

technique

for

Gb/s

Serial

Communication, Thine

11:15 ~ 11:40

A 16M SRAM with improved

characteristics

using

DRAM

technology, Renesas

A Wide Band CDR for Digital Video Data

Transmission, Thine

11:40 ~ 12:05

The Power Conscious Synergistic

Processor Element of a CELL

Processor, IBM

A Sub-1V CMOS 2.5Gb/s Serial Link

Transceiver Using 2X Oversampling,

Realtek

12:05 ~ 12:30

A Wireless LAN Baseband LSI for

High-Definition

A/V

Contents

Transmission, Toshiba

3.3/5V Multi-rate Laser Diode Driver and

Limiting

Amplifier

for

Optical

Transceivers, iCreate

29.

各技術分野のハイライト各技術分野のご説明

・アナログ

・Wireless/Wireline

・ディジタル

・メモリ

・システムレベル搭載技術

・新技術・応用

各担当

永田

濱田

荒川

日高

池田

野村

小谷

真 神戸大学

基嗣 東芝

文男 日立

秀人 ルネサステクノロジ

誠 東京大学

昌弘

光司 東北大学

30.

Analogアナログ回路技術

• SoC設計に欠かせないアナログ技術、ベースバンドからRFまで、

注目すべき新しい研究成果が採択

• 注目される2件の論文を紹介

– A 14-bit 20-MS/s Pipelined ADC with Digital Distortion

Calibration

• アンプの非線型による歪みをデジタル補正する技術により

、14ビット・20Mサンプル/秒のAD変換器を33.7mWで実現

、シャープの発表

– A Fully Integrated CMOS RF Power Amplifier with

Parallel Power Combining and Power Control

• 複数パワーアンプをオンチップ結合する技術、2.45GHz帯

送信回路の電力効率改善に効果、KUルーベン大学(ベル

ギー)の発表

31.

A 14-bit 20-MS/s Pipelined ADC with Digital DistortionCalibration

デジタル歪み補正を用いた14ビット・20Mサンプル/秒パイプラインAD変換器

• 論文番号[2-1] シャープの発表

• パイプラインADCに一般的なデジタル補正機構を用

いて、アンプのゲイン非線型による歪みを補正する(

取り除く)手法を新規開発

• アンプの非線型性による歪みを補正することで、アン

プのゲインを低減し、低消費電力化

• 14ビット・20Mサンプル/秒のAD変換器を33.7mWで実

現、0.18umプロセス、2.8V

• 3次歪みを15dB低減、SNDR 71.6dB、SFDR 82.3dB

32.

A Fully Integrated CMOS RF Power Amplifier with ParallelPower Combining and Power Control

電力結合機構を用いた集積化CMOS RFパワーアンプ

• 論文番号[6-3] ルーベン大学の発表

• パワーアンプ複数個をオンチップ結合する新しい回路

構成を提案、広い出力パワー範囲に対して高い電力

効率を達成

• 送信回路の電力効率改善に高い効果

• 0.13um CMOSプロセスを用いたBluetoothパワーアン

プ、出力23dBm、効率(出力電力/消費電力)28%

33.

A 0.1-25.5-GHz Differential Cascaded-Distributed Amplifierin 0.18-um CMOS Technology

0.1-25.5GHz, 0.18um CMOS差動カスケード分布アンプ

• 論文番号[5-1] 国立台湾大学の発表

• 差動分布アンプのカスケード接続により広帯域化を実

現する新しい回路トポロジーを提案、ゲイン-帯域幅積

で世界最高峰

• 0.18umCMOSプロセス、25.5GHz帯域で+15dBのゲイン

を達成

34.

各技術分野のハイライト各技術分野のご説明

・アナログ

・Wireless/Wireline

・ディジタル

・メモリ

・システムレベル搭載技術

・新技術・応用

各担当

永田

濱田

荒川

日高

池田

野村

小谷

真 神戸大学

基嗣 東芝

文男 日立

秀人 ルネサステクノロジ

誠 東京大学

昌弘

光司 東北大学

35.

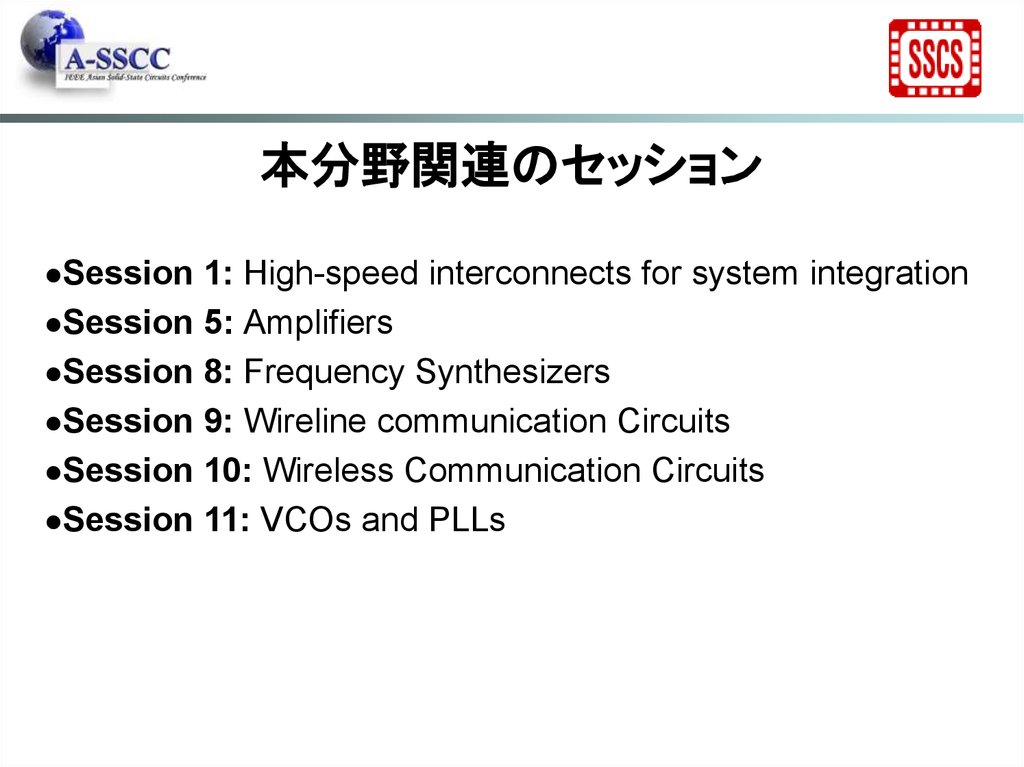

本分野関連のセッションSession

1: High-speed interconnects for system integration

Session 5: Amplifiers

Session 8: Frequency Synthesizers

Session 9: Wireline communication Circuits

Session 10: Wireless Communication Circuits

Session 11: VCOs and PLLs

36.

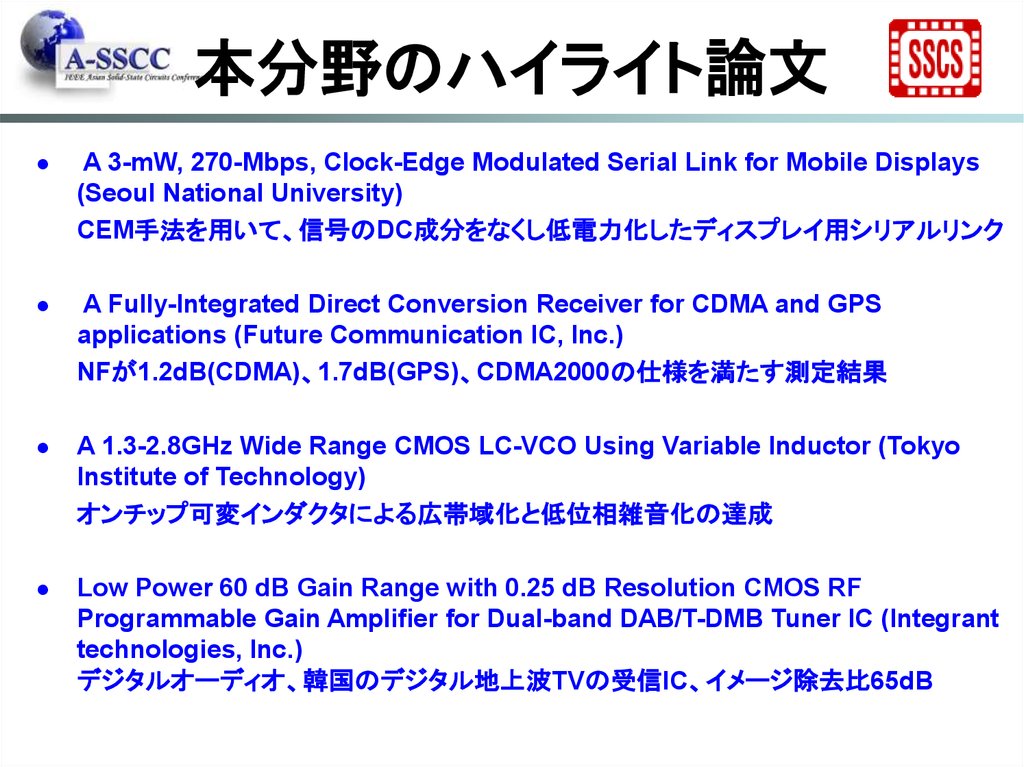

本分野のハイライト論文A 3-mW, 270-Mbps, Clock-Edge Modulated Serial Link for Mobile Displays

(Seoul National University)

CEM手法を用いて、信号のDC成分をなくし低電力化したディスプレイ用シリアルリンク

A Fully-Integrated Direct Conversion Receiver for CDMA and GPS

applications (Future Communication IC, Inc.)

NFが1.2dB(CDMA)、1.7dB(GPS)、CDMA2000の仕様を満たす測定結果

A 1.3-2.8GHz Wide Range CMOS LC-VCO Using Variable Inductor (Tokyo

Institute of Technology)

オンチップ可変インダクタによる広帯域化と低位相雑音化の達成

Low Power 60 dB Gain Range with 0.25 dB Resolution CMOS RF

Programmable Gain Amplifier for Dual-band DAB/T-DMB Tuner IC (Integrant

technologies, Inc.)

デジタルオーディオ、韓国のデジタル地上波TVの受信IC、イメージ除去比65dB

37.

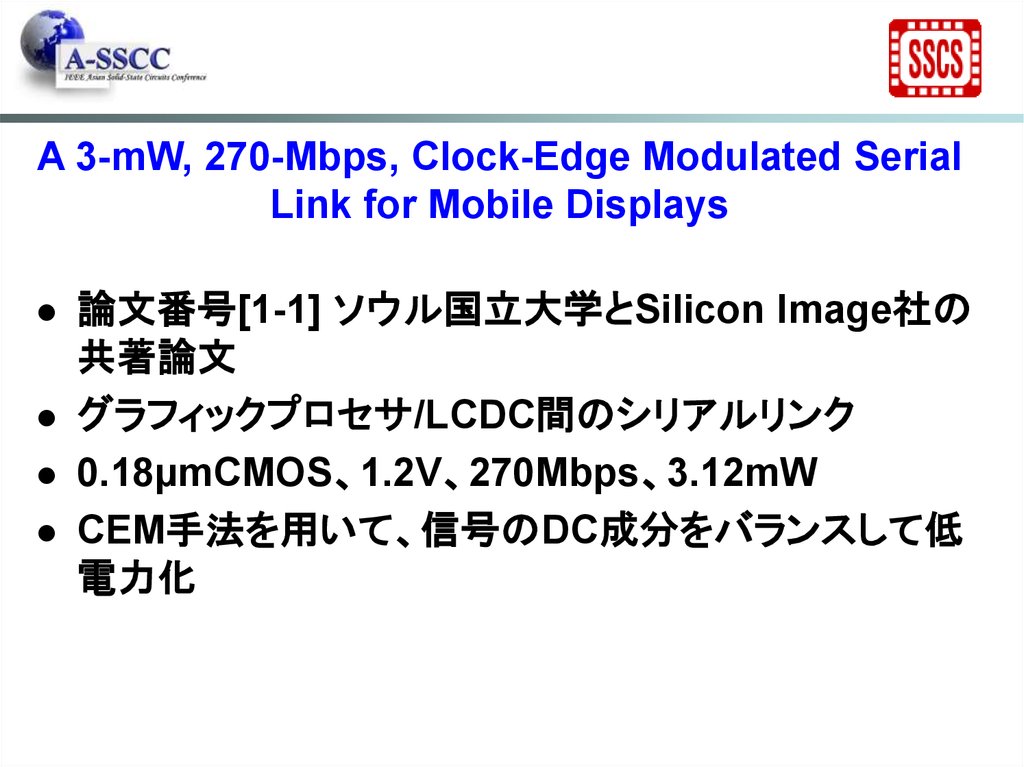

A 3-mW, 270-Mbps, Clock-Edge Modulated SerialLink for Mobile Displays

論文番号[1-1] ソウル国立大学とSilicon Image社の

共著論文

グラフィックプロセサ/LCDC間のシリアルリンク

0.18µmCMOS、1.2V、270Mbps、3.12mW

CEM手法を用いて、信号のDC成分をバランスして低

電力化

38.

A Fully-Integrated Direct Conversion Receiverfor CDMA and GPS applications

論文番号[10-3]

Future Communication IC社の論文

CDMAとGPSの低NF、ダイレクトコンバージョン受信器

0.35umBiCMOS、2.7-3.0V動作

消費電流は、51mA(CDMA)、42mA(GPS)

CDMA用のLNAのNF=1.2dB

GPSのNF_Total=1.7dB

39.

A 1.3-2.8GHz Wide Range CMOS LC-VCO UsingVariable Inductor

論文番号[11-1]

東京工業大学の論文

オンチップ可変インダクタによる広帯域化

チューニングレンジは72%

発振周波数、消費電力、位相雑音、チューニングレンジ

を加味した性能比較指標で、最高性能を実現

40.

Low Power 60 dB Gain Range with 0.25 dBResolution CMOS RF Programmable Gain Amplifier

for Dual-band DAB/T-DMB Tuner IC

論文番号[5-2] インテグラント・テクノロジーズとKAISTの

共著論文

DABとT-DMB受信ICのRF可変利得アンプ

0.18µmCMOS、NF=2.7dB、IIP3=-14dBm @Lバンド

(1450MHz-1492MHz)

Different Multiple Gate TRansistor (DMGTR) 回路

により、線形性を改善

41.

各技術分野のハイライト各技術分野のご説明

・アナログ

・Wireless/Wireline

・ディジタル

・メモリ

・システムレベル搭載技術

・新技術・応用

各担当

永田

濱田

荒川

日高

池田

野村

小谷

真 神戸大学

基嗣 東芝

文男 日立

秀人 ルネサステクノロジ

誠 東京大学

昌弘

光司 東北大学

42.

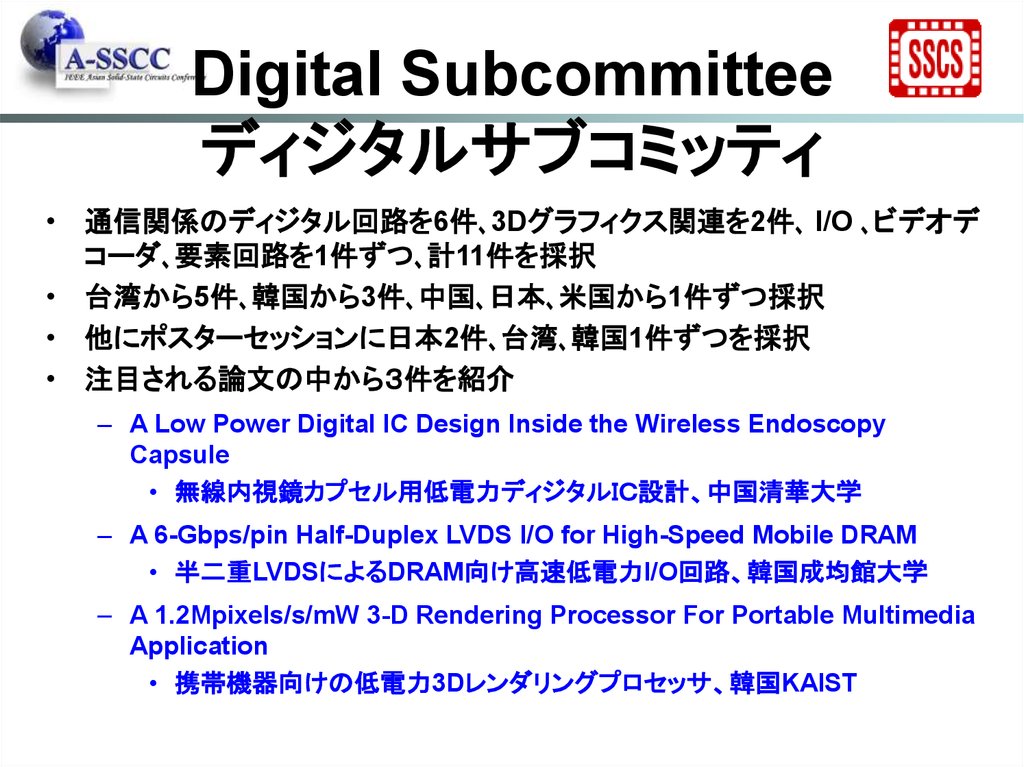

Digital Subcommitteeディジタルサブコミッティ

• 通信関係のディジタル回路を6件 3Dグラフィクス関連を2件 I/O ビデオデ

コーダ 要素回路を1件ずつ 計11件を採択

• 台湾から5件 韓国から3件 中国 日本 米国から1件ずつ採択

• 他にポスターセッションに日本2件 台湾 韓国1件ずつを採択

• 注目される論文の中から 件を紹介

– A Low Power Digital IC Design Inside the Wireless Endoscopy

Capsule

• 無線内視鏡カプセル用低電力ディジタル 設計、中国清華大学

– A 6-Gbps/pin Half-Duplex LVDS I/O for High-Speed Mobile DRAM

• 半二重LVDSによるDRAM向け高速低電力I/O回路、韓国成均館大学

– A 1.2Mpixels/s/mW 3-D Rendering Processor For Portable Multimedia

Application

• 携帯機器向けの低電力3Dレンダリングプロセッサ、韓国KAIST

43.

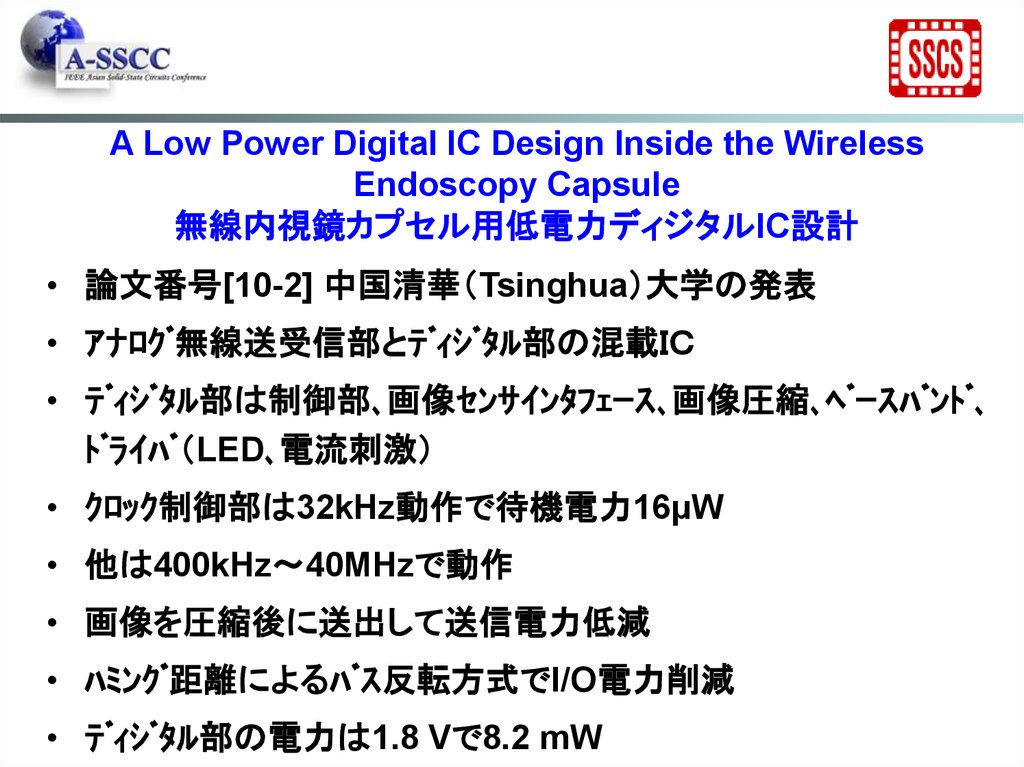

A Low Power Digital IC Design Inside the WirelessEndoscopy Capsule

無線内視鏡カプセル用低電力ディジタルIC設計

• 論文番号[10-2] 中国清華 Tsinghua 大学の発表

• 無線送受信部と 部の混載

• 部は制御部 画像 画像圧縮

LED 電流刺激

• 制御部は32kHz動作で待機電力16μW

• 他は400kHz 40MHzで動作

• 画像を圧縮後に送出して送信電力低減

• 距離による 反転方式でI/O電力削減

• 部の電力は1.8 Vで8.2 mW

44.

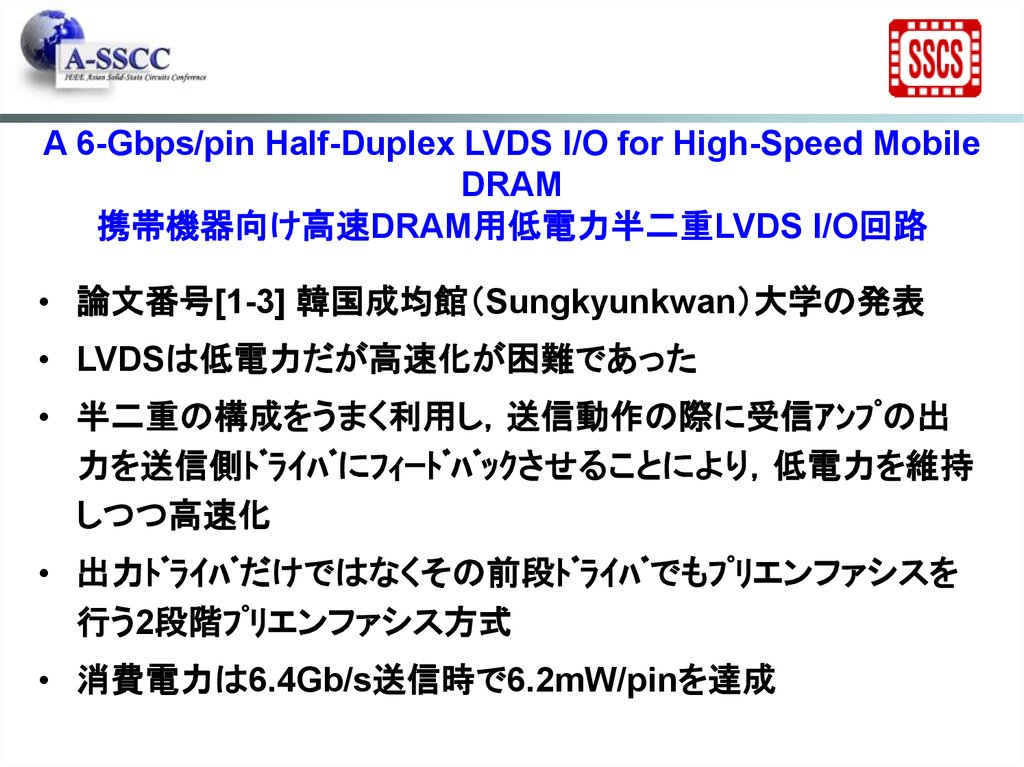

A 6-Gbps/pin Half-Duplex LVDS I/O for High-Speed MobileDRAM

携帯機器向け高速DRAM用低電力半二重LVDS I/O回路

• 論文番号[1-3] 韓国成均館 Sungkyunkwan 大学の発表

• LVDSは低電力だが高速化が困難であった

• 半二重の構成をうまく利用し 送信動作の際に受信 の出

力を送信側 に させることにより 低電力を維持

しつつ高速化

• 出力 だけではなくその前段 でも エンファシスを

行う2段階 エンファシス方式

• 消費電力は6.4Gb/s送信時で6.2mW/pinを達成

45.

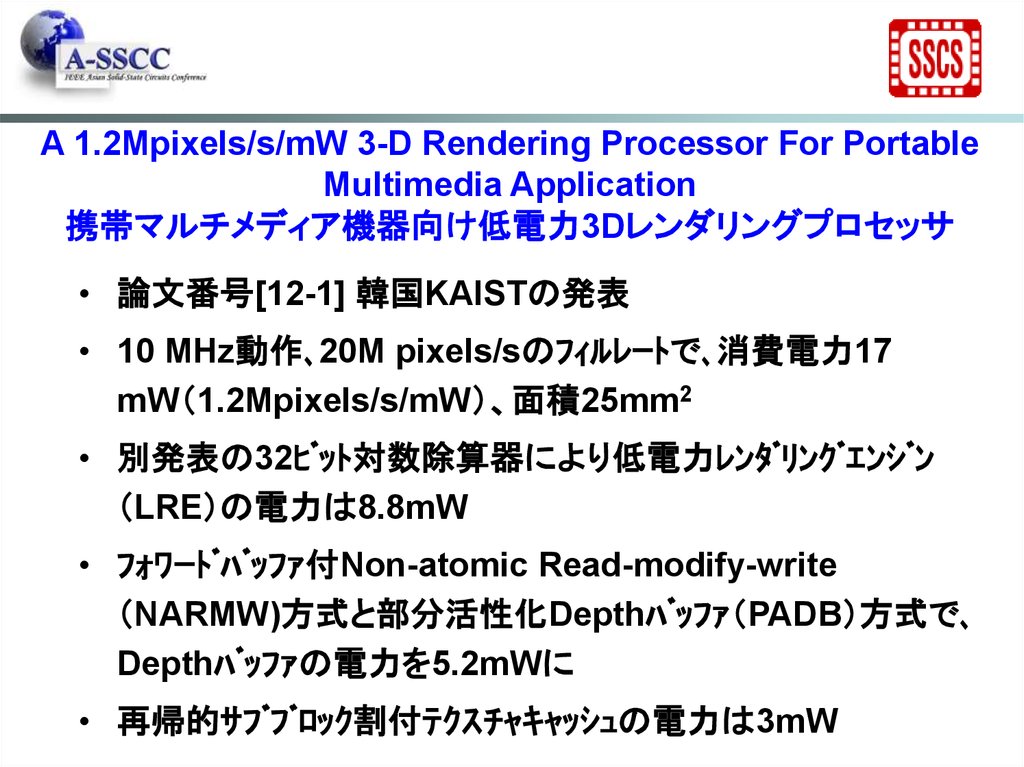

A 1.2Mpixels/s/mW 3-D Rendering Processor For PortableMultimedia Application

携帯マルチメディア機器向け低電力3Dレンダリングプロセッサ

• 論文番号[12-1] 韓国KAISTの発表

• 10 MHz動作 20M pixels/sの で 消費電力17

mW 1.2Mpixels/s/mW 、面積25mm2

• 別発表の32 対数除算器により低電力

LRE の電力は8.8mW

• 付Non-atomic Read-modify-write

NARMW)方式と部分活性化Depth PADB 方式で

Depth の電力を5.2mWに

• 再帰的 割付 の電力は3mW

46.

各技術分野のハイライト各技術分野のご説明

・アナログ

・Wireless/Wireline

・ディジタル

・メモリ

・システムレベル搭載技術

・新技術・応用

各担当

永田

濱田

荒川

日高

池田

野村

小谷

真 神戸大学

基嗣 東芝

文男 日立

秀人 ルネサステクノロジ

誠 東京大学

昌弘

光司 東北大学

47.

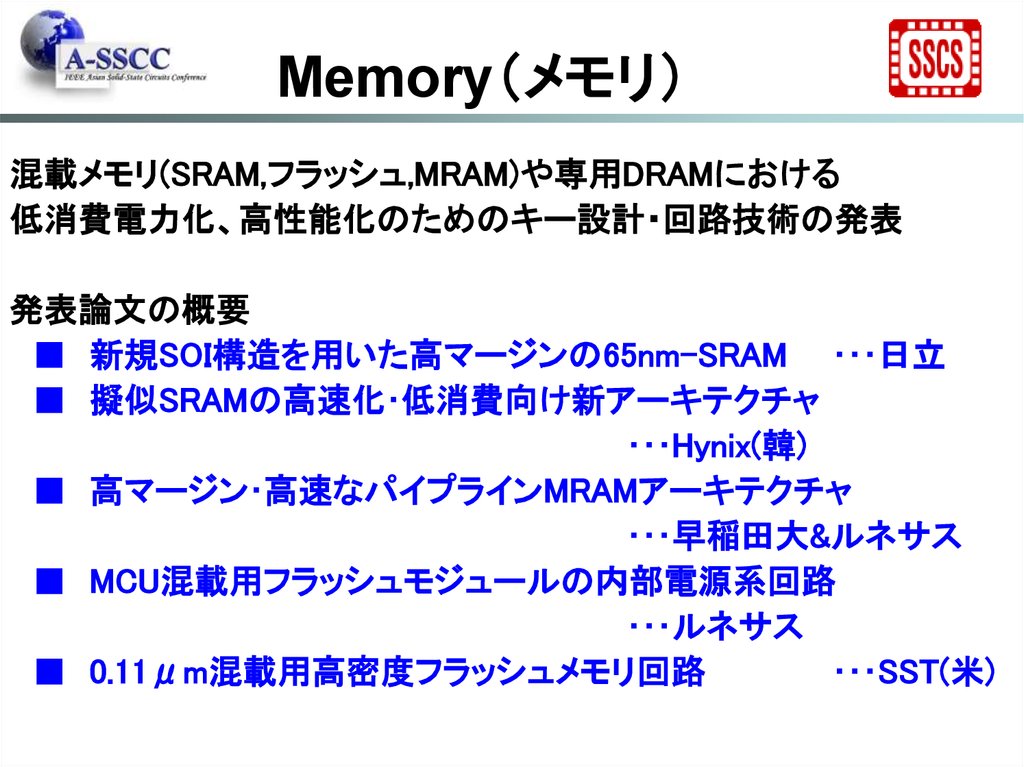

Memory メモリ混載メモリ(SRAM,フラッシュ,MRAM)や専用DRAMにおける

低消費電力化、高性能化のためのキー設計・回路技術の発表

発表論文の概要

■ 新規SOI構造を用いた高マージンの65nm-SRAM 日立

■ 擬似SRAMの高速化 低消費向け新アーキテクチャ

Hynix(韓)

■ 高マージン 高速なパイプラインMRAMアーキテクチャ

早稲田大&ルネサス

■ MCU混載用フラッシュモジュールの内部電源系回路

ルネサス

■ 0.11μm混載用高密度フラッシュメモリ回路

SST(米)

48.

SRAM Circuit with Expanded Operating Margin and Reduced Standby Leakage Current Using Thin-BOX FD-SOI Transistors新SOI構造を用いて動作マージン拡大とスタンドバイ

リーク電流の低減ができるSRAM

• 論文番号[4-1] 日立の発表

• SRAMは、セル縮小と、動作マージン確保・低スタンドバイ電流化の

両立が大きな問題になる

• 新規SOI構造 (薄膜BOXでチャネル上下にゲートを持つダブルゲート

構造) を用いて、コラム毎にRead/Write別のバックゲートバイアス制

御を行う回路を考案

• 65nmプロセスでデバイス試作し、書込み時間の30%低減とスタンド

バイ電流の90 低減(バルクデバイス比)の可能性を示した

49.

A Low Power 128Mb Pseudo SRAM Using Hyper DestructiveRead Architecture

(高速・低電力のための新アーキテクチャによる128Mb擬似SRAM)

• 論文番号[4-2] Hynix社(韓国)の発表

• DRAMは、データ読出し動作時にデータ破壊されるので、この後のデー

タリストア時間により高速化を妨げていた

• 読出しデータをセンスアンプキャッシュに保持し、次の読出しとオーバ

ラップさせて高速化するための新規アーキテクチャ(HyDRA)を考案

• 0.12μmプロセスで128Mb擬似SRAMチップを作り、動作確認

アクセスタイムが20 低減、また、同一アクセスタイム相当の低リークト

ランジスタ使用時にスタンドバイ電流が半減する効果有り。

50.

0.11um 4.5F2 1.8V Multilevel Vertical Split Gate SourceSide Injection Vehicle for Giga-Bit Density NOR Flash

Memory

スプリットゲート・NORフラッシュの次世代版試作

• 論文番号[4-5] SST社 (Silicon Storage Technology、米国) の発表

• フラッシュメモリ(SSTセル)の次世代版の発表

• 次元NOR型スプリットゲートセルによりNAND並みのセルサイズを実現し、

値/セルのデータストア新規高速回路を考案

• 0.11μmプロセスで1Mb規模のメモリアレイ回路を作り、1.8V動作を確認 セル

サイズ=0.055μm2(4.5F2)、1Mb面積=0.25mm2

センス線電圧の漸増による精密書込み(誤差=150mV→5mVに)

高速電流センスアンプ(従来より 倍速)によりTac=30ns

51.

A 75MHz MRAM with Pipe-Lined Self-Reference ReadScheme for Mobile/Robotics Memory System

高マージン 高速なパイプラインMRAMアーキテクチャ

• 論文番号[4-3] 早稲田大&ルネサスの発表

• MRAMは、高マージン・高速化のための回路技術が未開拓であり、

混載応用などに向けた設計技術が未開発である

• 新規セルフレファレンスセンスアンプとパイプライン動作を駆使

した、高マージン・高速な新規MRAMアーキテクチャを考案

• 75MH 1.2 という高速・高マージン動作を実現する見通しを得た 従

来の同種MRAMでは8MHzであった

52.

各技術分野のハイライト各技術分野のご説明

・アナログ

・Wireless/Wireline

・ディジタル

・メモリ

・システムレベル搭載技術

・新技術・応用

各担当

永田

濱田

荒川

日高

池田

野村

小谷

真 神戸大学

基嗣 東芝

文男 日立

秀人 ルネサステクノロジ

誠 東京大学

昌弘

光司 東北大学

53.

System Level Integrationシステムレベルの集積化技術

• SoC設計における低消費電力化、高性能化設計技術に焦点

をあてる

• 注目される論文の中から 件を紹介

– Vdd-Hopping Accelerator for On-Chip Power Supplies

Achieving Nano-Second Order Transient Time

• Vdd変更速度を高速化して低消費電力化する技術, 東京大学の発表

– A Self-Calibrate All-Digital 3Gbps SATA Driver Design

• 完全デジタル技術で自己補正機能を備えた3Gbps SATA ドライブ回路の

実現技術, 台湾交通大学の発表

– A 667MT/s 10.7GB/s Multiprocessor Bus Interface

• Itanium 2 のFront-side Bus(FSB)で使われているバスの高速化技術,

インテルの発表

54.

Vdd-Hopping Accelerator for On-Chip Power SuppliesAchieving Nano-Second Order Transient Time

ナノ秒で反応するオンチップ電源用Vdd可変回路の高速化技術

• 論文番号[6-1] 東京大学の発表

• アイドル時には電源電圧を下げることで低消費

電力化を図る(Vdd Hopping)が、アイドル状態

では電源電圧がなかなか下がらない

• 電源電圧を急速に下げるためのスイッチと、そ

の制御回路を考案

• 0.18µmプロセスで実験回路を作り5ns以下の速

さで電源電圧を降下できることを確認

55.

A Self-Calibrate All-Digital 3Gbps SATA Driver Design自己補正機能のついた完全デジタル型の3Gbps SATAドライバ

• 論文番号[1-4] 台湾交通大学の発表

• Serial-ATA(SATA II)用の低電圧差動信号ドライバ

(LVDS)

• 完全デジタル方式で、SATA規格に合わせるための

キャリブレーションも自動で行う

• ドライバ回路を徐々に動作させることで同時スイッチ

ングノイズを除去

• TSMC0.18mmプロセスで実現

• 3Gbps動作時の消費電力は11mW@1.8V

56.

A 667MT/s 10.7GB/s Multiprocessor Bus Interface667MT/s 10.7GB/sのマルチプロセッサバスインターフェイス

• 論文番号[1-2] Intel の発表

• Itanium 2のマルチプロセッサ構成をサポートするFront-side

Bus(FSB)で使われているインターフェイス回路を説明

• 667MT/s で 3CPU間通信を実現するための数々の工夫を開示

– 信号の立上り/立下りの整形回路

– 同時スイッチングノイズを除去するための電流経路制御回路

– 入出力タイミング制御回路

– PVT補償回路

• 130nmプロセスのItanium2で使用

57.

各技術分野のハイライト各技術分野のご説明

・アナログ

・Wireless/Wireline

・ディジタル

・メモリ

・システムレベル搭載技術

・新技術・応用

各担当

永田

濱田

荒川

日高

池田

野村

小谷

真 神戸大学

基嗣 東芝

文男 日立

秀人 ルネサステクノロジ

誠 東京大学

昌弘

光司 東北大学

58.

新技術・応用分野注目される論文の中から 件を紹介

– A Wireless-Interface SoC Powered by Energy

Harvesting for Short-range Data Communication

• ワイヤレス・バッテリーレスのマウス技術, マウス動作から短距離データ通信

用の電力を得るワイヤレスインタフェースSoC, 金沢大学他の発表

– An On-chip PVT Control System for Worst-caseless

Lower Voltage SoC Design

• eSRAMの低電圧動作のためのAVM (adaptive voltage management)か

らなるオンチップPVT制御システム, ルネサスの発表

– A 142dB Dynamic Range CMOS Image Sensor with

Multiple Exposure Time Signals

• 超々短時間蓄積信号を含む4種類の蓄積時間信号を列並列ADCで読み出し,

142dBのダイナミックレンジを実現, 静岡大学他の発表

59.

A Wireless-Interface SoC Powered by Energy Harvesting forShort-range Data Communication

エネルギー採取技術により電力供給される短距離データ通信用の

ワイヤレスインタフェースSoC

• 論文番号[10-1] 金沢大学, 神戸大学, リニアサーキットの発表

• ワイヤレス, バッテリーレス マウス用の短距離データ通信が可

能なワイヤレスインタフェースSoC開発, マウス動作発電機(4

13mW)搭載

• FSK (frequency shift keying)変調方式, シングルエンド構造の

RFトランスミッタ, マウス向けマイクロコントローラ設計を適用

• 0.18mm CMOSで試作, 電力2.2mW(RFトランスミッタ

2.17mW@1mレンジ, 16bマイクロコントローラ 0.03mW@1MHz),

fc=28MHz, 距離 0.2 1m, データレート 10kbps

60.

An On-chip PVT Control System for Worst-caseless LowerVoltage SoC Design

低電圧SoC設計用オンチップPVT制御システム

• 論文番号[12-5] ルネサスの発表

• 低電圧SoC設計のためのAVM (adaptive voltage management)

からなるオンチップPVT (process, voltage, and temperature)制

御システムの提案

• 温度特性の異なる2つのリングオシレータを用いた温度計測(40 125℃), テーブルルックアップ方式による最適電圧制御,

低電圧駆動特性改善(x2.7@1.18V)レベルシフト型レギュレータ

を適用

• 90nm CMOSの実験チップにより正確な制御と低電圧時の

SRAM動作マージンの確保を確認

61.

A 142dB Dynamic Range CMOS Image Sensor142dBのダイナミックレンジを有するCMOSイメージセンサ

• 論文番号[3-1] 静岡大学、仙台電波工専, ヤマハ,

静岡県浜松工業技術センターの発表

• 長蓄積時間の1/24,180の超々短時間 読出し時間

より短い 蓄積信号を含む4種類の蓄積時間信号読

出しにより141.8dBのダイナミックレンジを実現

• ノイズキャンセル機能を有する新規開発の列並列

12bサイクリックADCを搭載

• 0.25mmプロセスで1/2” VGAサイズのセンサを試

作

62.

A-SSCC2005-- Asian Solid-State Circuit Conference 2005 -A-SSCC 2005のご案内

会期 2005年11月1日 3日 4日はツアー

場所 台湾新竹市 アンバサダ新竹・ホテル

Web http://www.a-sscc.org/

本日の電子データは以下のサイトにございます

http://www.vdec.u-tokyo.ac.jp/A-SSCC2005/

software

software