Similar presentations:

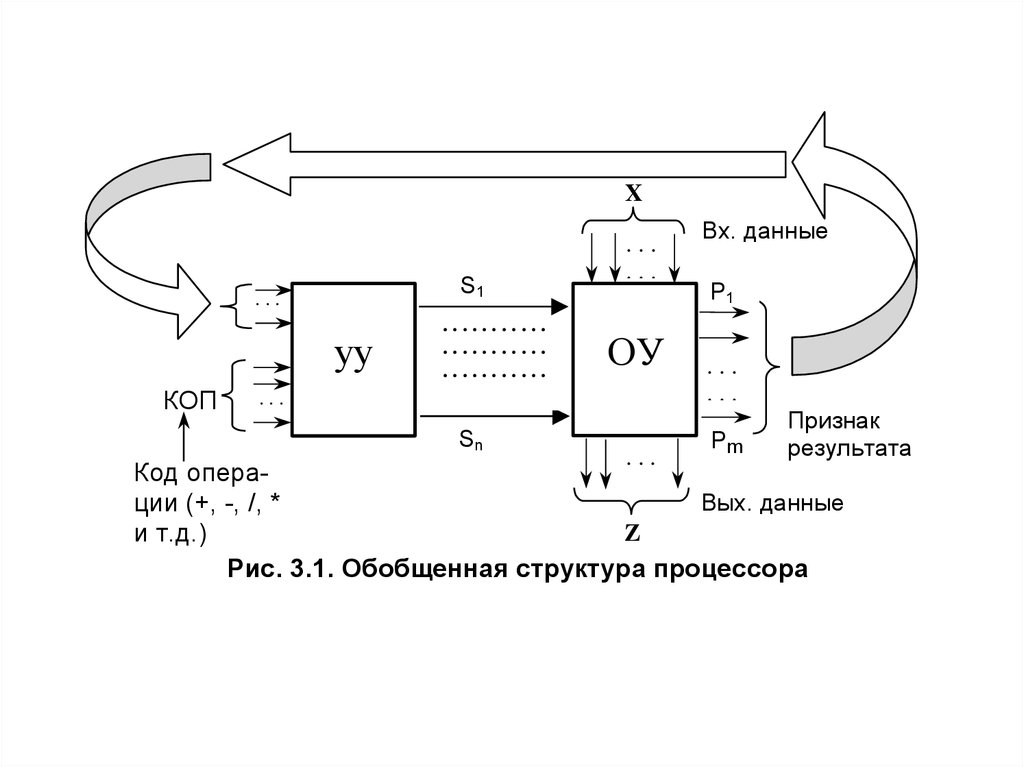

Обобщенная структура процессора

1.

XS1

...

уу

КОП

...........

...........

...........

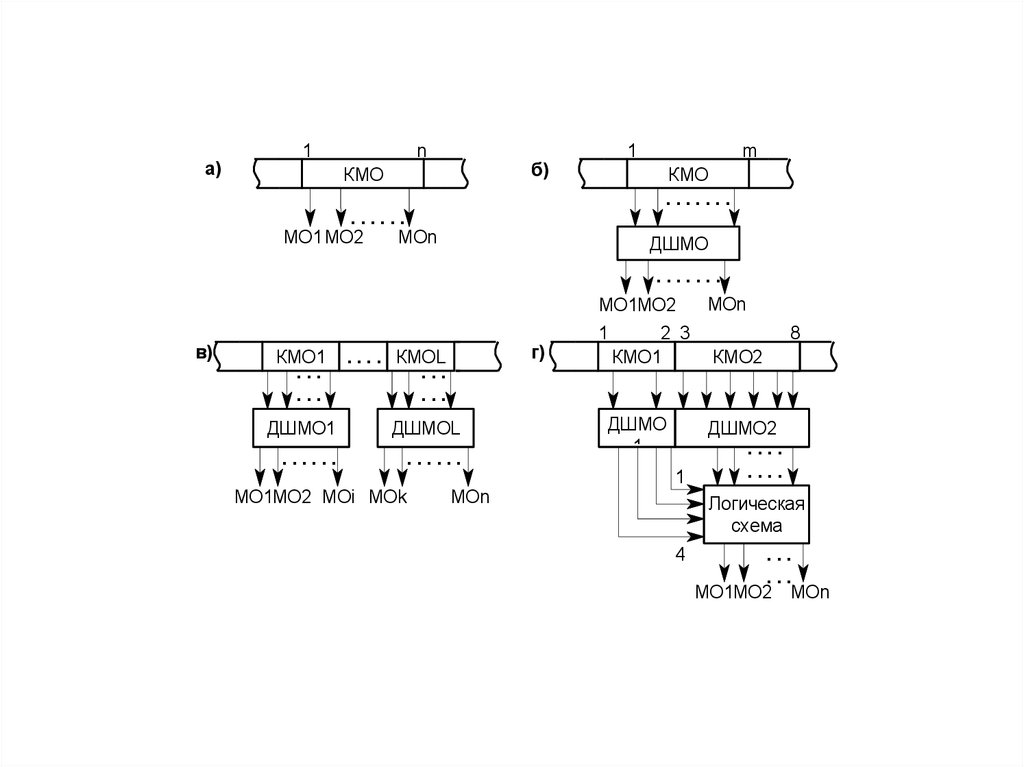

...

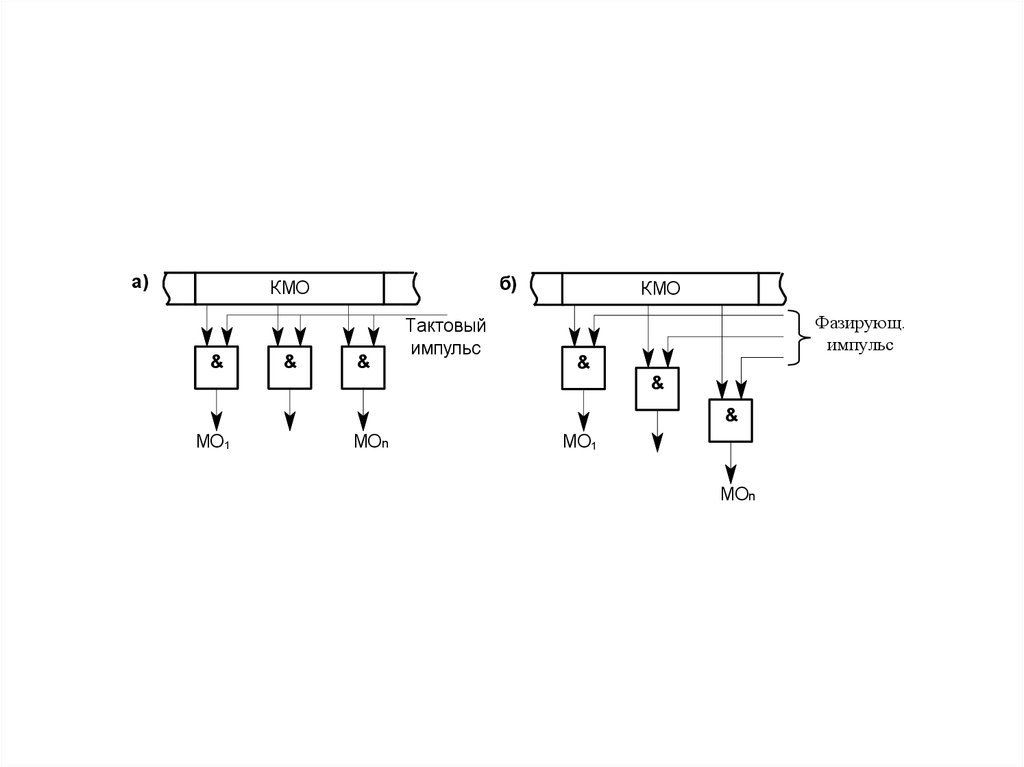

...

ОУ

...

Sn

...

Вх. данные

P1

...

...

Pm

Признак

результата

Код опера...

Вых. данные

ции (+, -, /, *

Z

и т.д.)

Рис. 3.1. Обобщенная структура процессора

2.

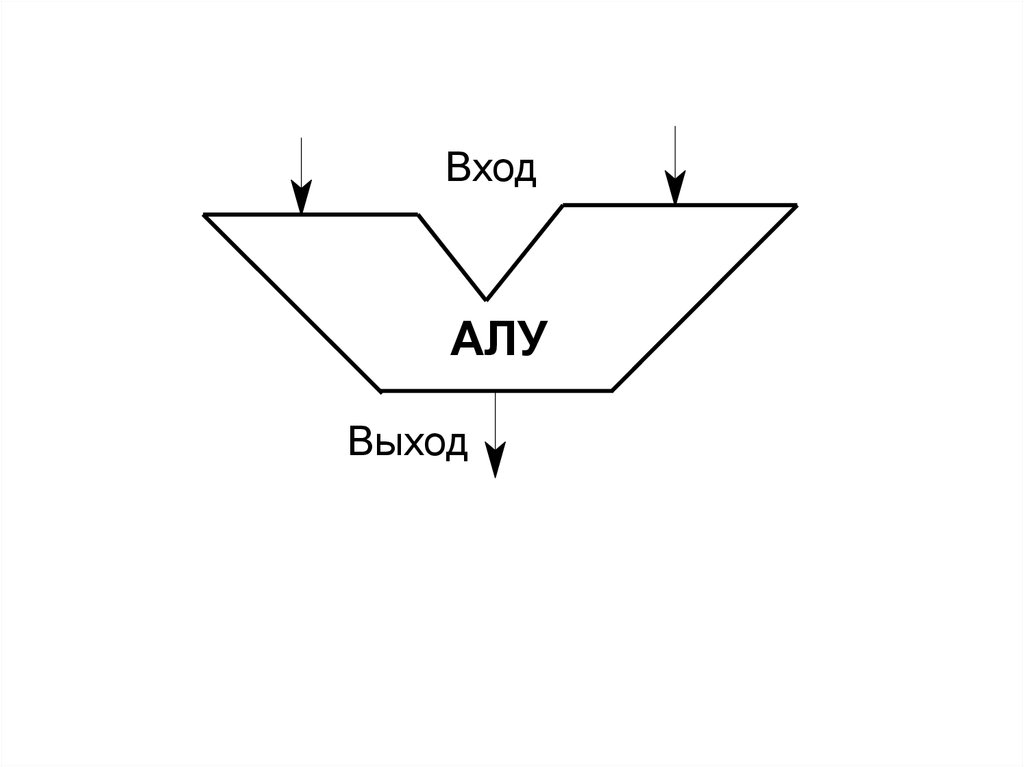

ВходАЛУ

Выход

3.

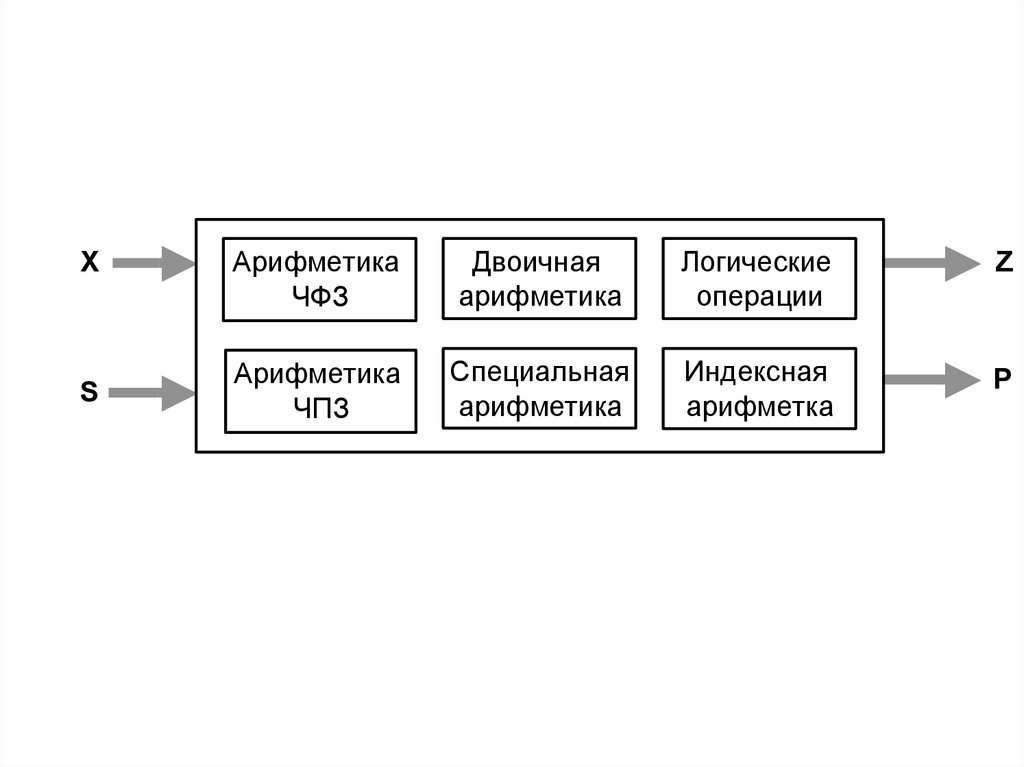

XS

Арифметика

ЧФЗ

Двоичная

арифметика

Логические

операции

Z

Арифметика

ЧПЗ

Специальная

арифметика

Индексная

арифметка

P

4.

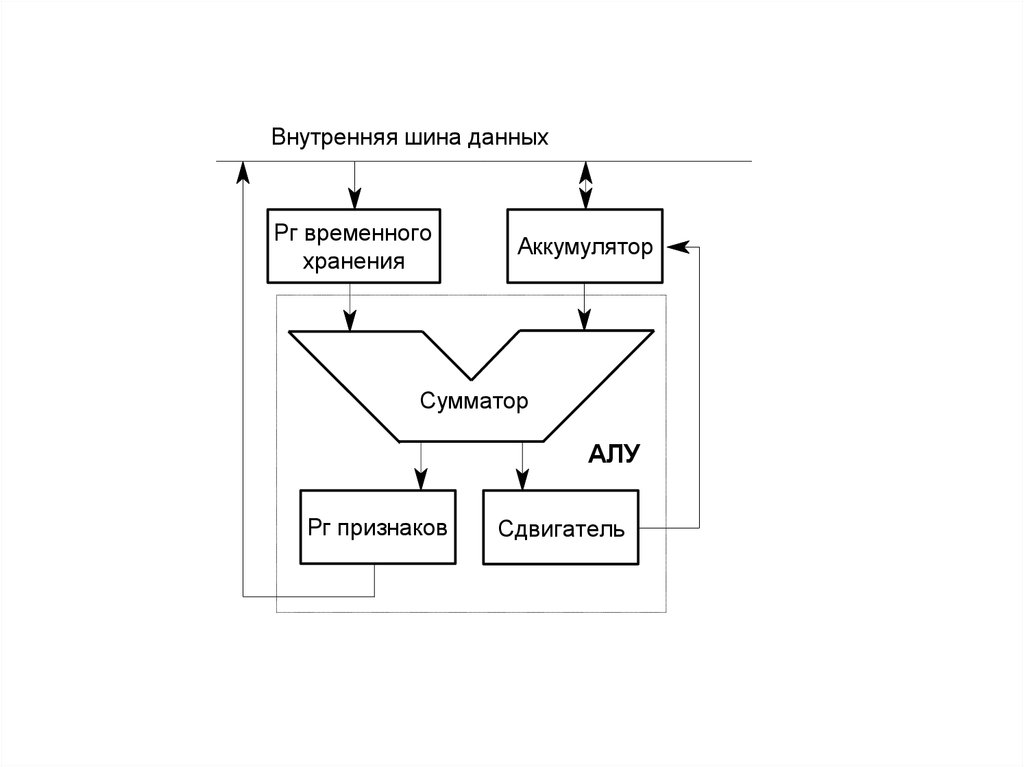

Внутренняя шина данныхРг временного

хранения

Аккумулятор

Сумматор

АЛУ

Рг признаков

Сдвигатель

5.

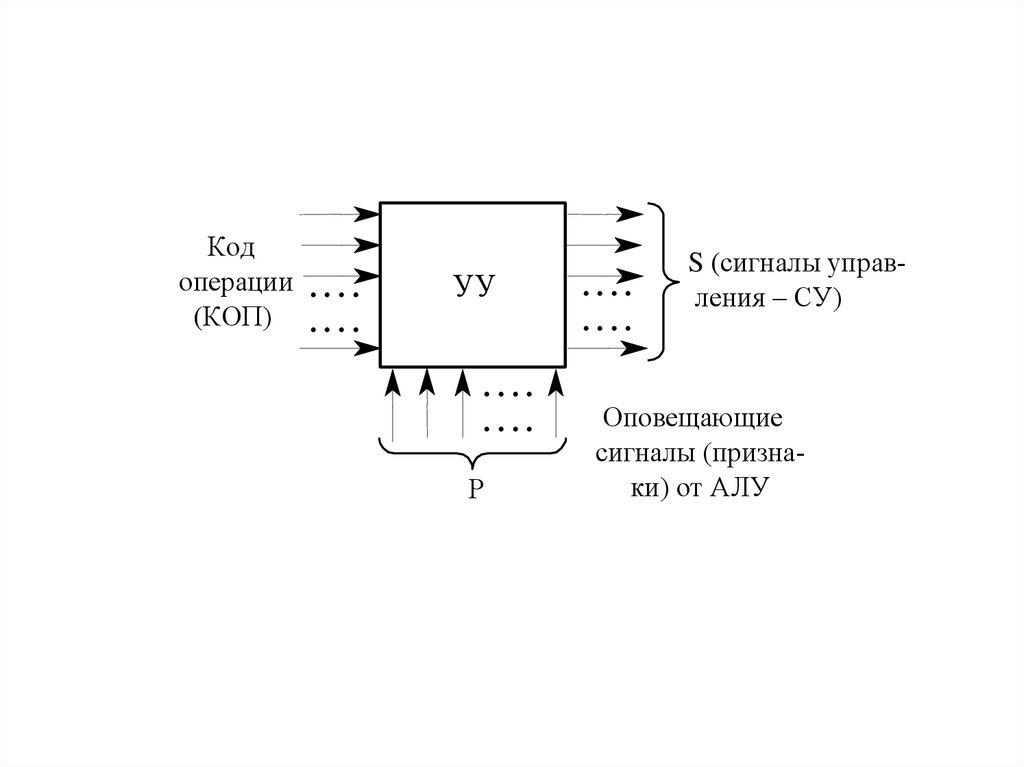

Кодоперации . . . .

(КОП) . . . .

УУ

....

....

Р

....

....

S (сигналы управления – СУ)

Оповещающие

сигналы (признаки) от АЛУ

6.

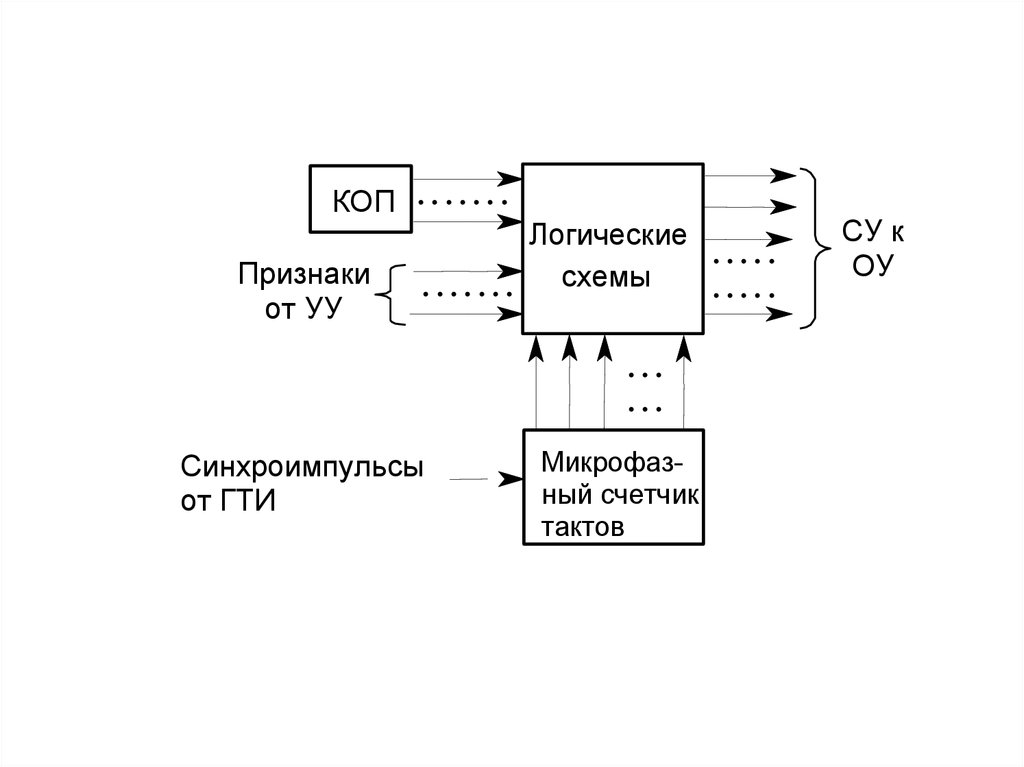

КОП . . . . . . .Признаки

от УУ

Логические

.....

схемы

.......

.....

...

...

Синхроимпульсы

от ГТИ

Микрофазный счетчик

тактов

СУ к

ОУ

7.

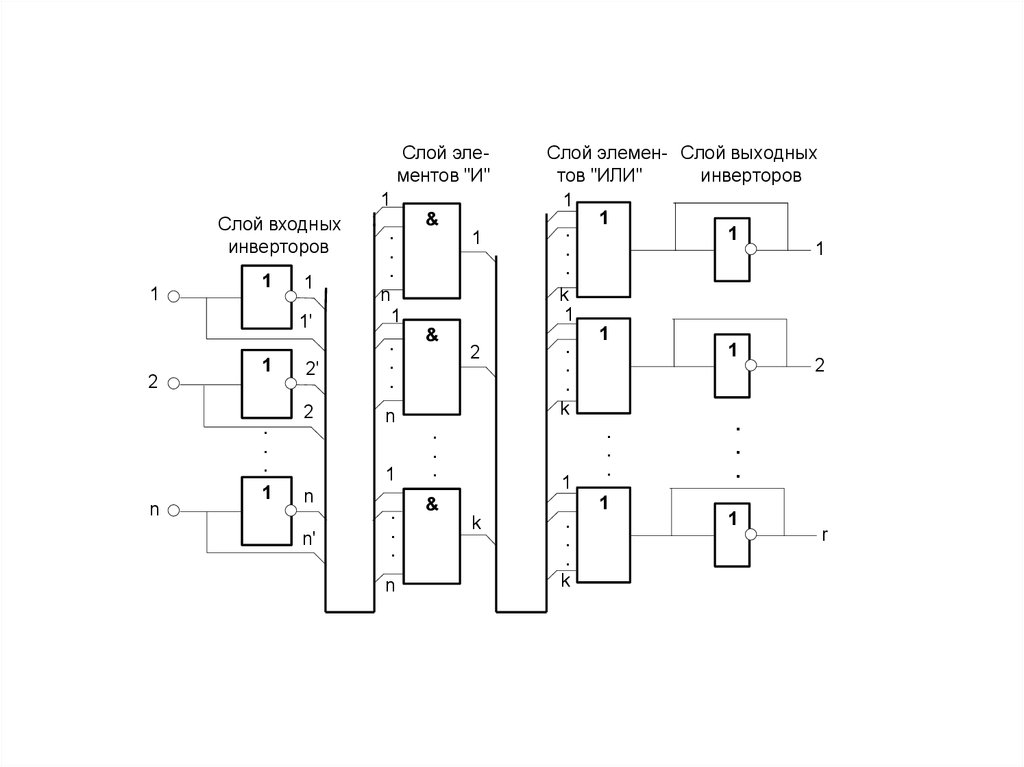

Слой элементов "И"1

Слой входных

инверторов

1

1

1

1'

2

1

n

1

.

k

1

1

2'

2

n

1

n

n'

&

n

.

.

.

.

.

.

1

.

.

.

.

.

.

n

Слой элемен- Слой выходных

тов "ИЛИ"

инверторов

1

1

.

1

1

.

&

2

.

.

.

1

k

.

.

.

1

.

.

.

1

&

k

.

.

.

k

1

2

.

.

.

1

r

8.

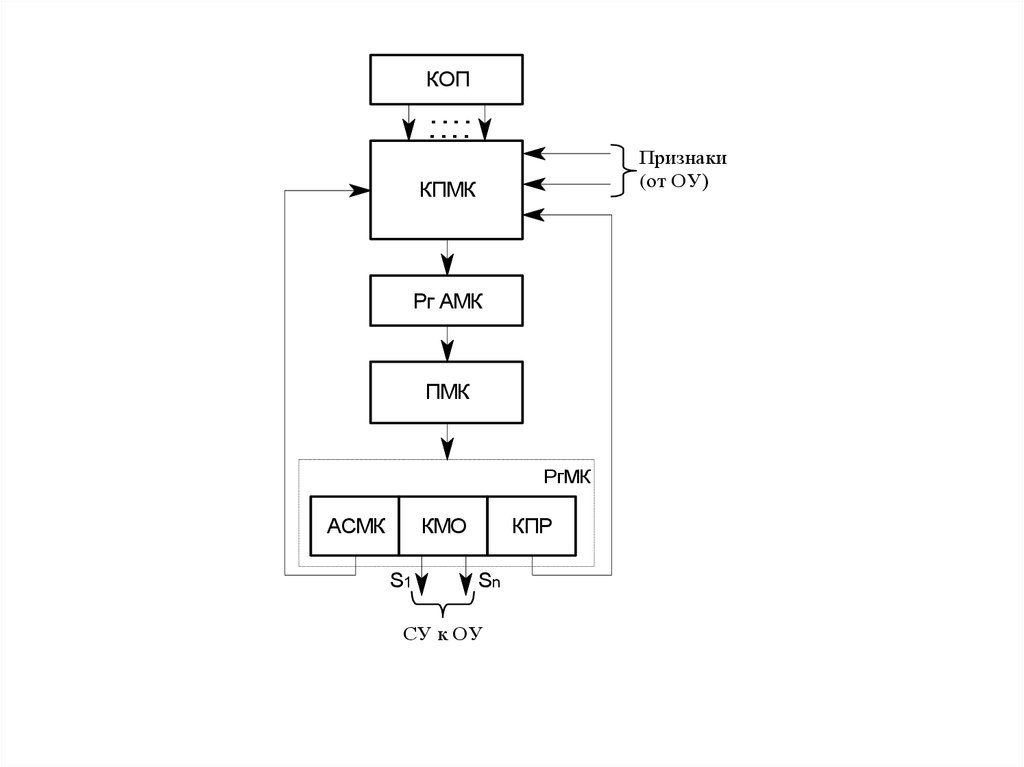

КОП....

....

Признаки

(от ОУ)

КПМК

Рг АМК

ПМК

РгМК

АСМК

КМО

S1

КПР

Sn

СУ к ОУ

9.

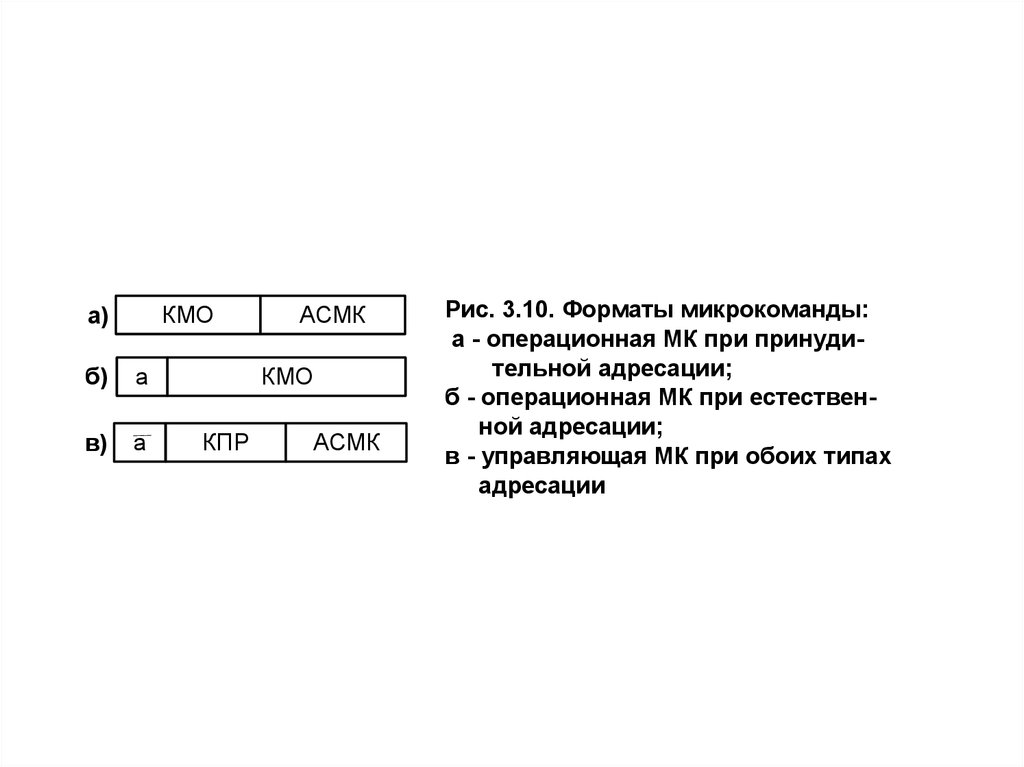

КМОa)

б)

a

в)

a

АСМК

КМО

КПР

АСМК

Рис. 3.10. Форматы микрокоманды:

а - операционная МК при принудительной адресации;

б - операционная МК при естественной адресации;

в - управляющая МК при обоих типах

адресации

10.

а)1

n

1

б)

КМО

m

КМО

.......

......

МО1 МО2

МОn

ДШМО

.......

МО1МО2

в)

КМО1

...

...

г)

. . . . КМОL

...

...

ДШМО1

ДШМОL

......

......

МО1МО2 МОi МОk

МОn

1

2 3

КМО1

ДШМО

1

1

МОn

8

КМО2

ДШМО2

....

....

Логическая

схема

4

...

...

МО1МО2 МОn

11.

а)б)

КМО

&

&

&

Тактовый

импульс

КМО

Фазирующ.

импульс

&

&

&

МО1

МОn

МО1

МОn

electronics

electronics