Similar presentations:

Багаторівнева організація пам'яті комп'ютера

1.

Полтавський національний технічний університет імені Юрія КондратюкаЛекція № 3 з навчальної дисципліни

“Архітектура обчислювальних систем”.

Розділ 1. Організація апаратної частини комп'ютерів

Модуль 1. Організація ядра обчислювальної системи (центрального

процесора, пам’яті та системного інтерфейса). Методи розміщення

інформації у пам’яті комп’ютерів.

Тема лекції:

Багаторівнева організація пам'яті комп'ютера

План лекції

1. Ієрархічна структура пам'яті комп'ютера.

2. Організація адресної (основної) пам'яті.

3. Організація кеш-пам'яті.

4. Стекова пам’ять.

5. Накопичувачі інформації на ЖМД.

6. Масиви НЖМД з надлишковістю.

Кафедра комп'ютерної інженерії

К.т.н., доцент Тиртишніков О.І.

2.

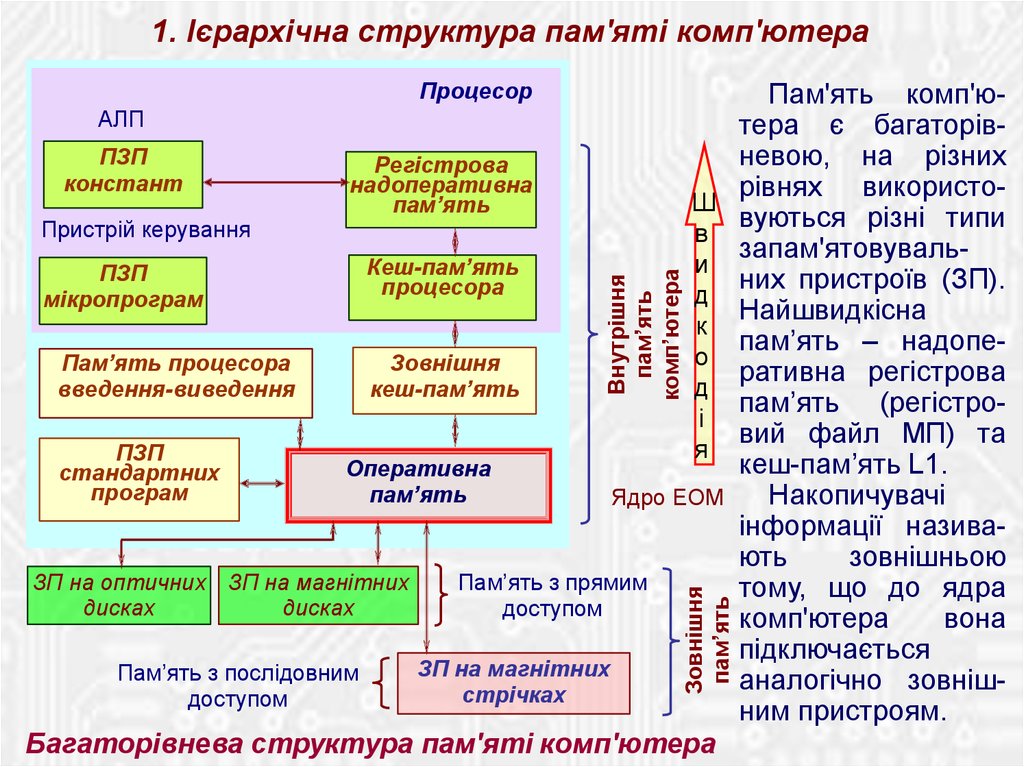

1. Ієрархічна структура пам'яті комп'ютераПам'ять комп'юАЛП

тера є багаторівПЗП

невою, на різних

Регістрова

констант

надоперативна

рівнях використоШ

пам’ять

вуються різні типи

Пристрій керування

в

запам'ятовувальи

Кеш-пам’ять

ПЗП

них пристроїв (ЗП).

процесора

д

мікропрограм

Найшвидкісна

к

пам’ять – надопео

Пам’ять процесора

Зовнішня

ративна регістрова

д

введення-виведення

кеш-пам’ять

пам’ять (регістроі

вий файл МП) та

я

ПЗП

кеш-пам’ять L1.

Оперативна

стандартних

програм

пам’ять

Накопичувачі

Ядро ЕОМ

інформації називають

зовнішньою

ЗП на оптичних ЗП на магнітних

Пам’ять з прямим

тому, що до ядра

дисках

дисках

доступом

комп'ютера

вона

підключається

ЗП

на

магнітних

Пам’ять з послідовним

аналогічно зовнішстрічках

доступом

ним пристроям.

Багаторівнева структура пам'яті комп'ютера

Зовнішня

пам’ять

Внутрішня

пам’ять

комп’ютера

Процесор

3.

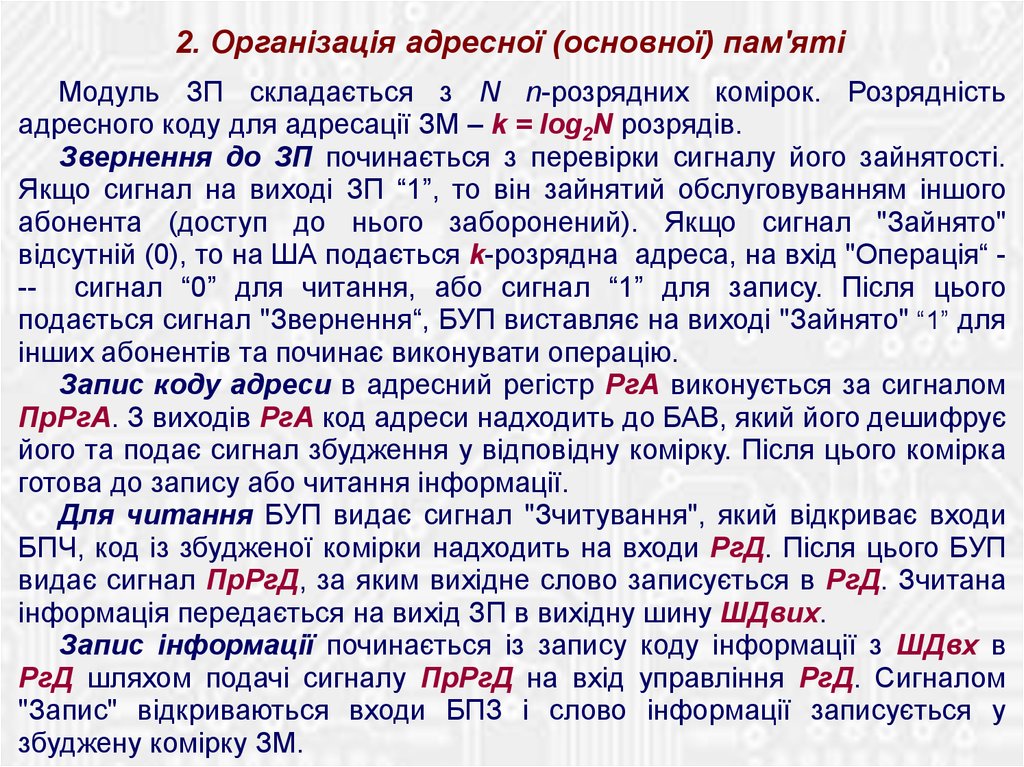

2. Організація адресної (основної) пам'ятіПочаток

БПЧ

0

ША

0

0

РгА

БАВ

n-1

ШДвих

n-1

0

0

Звернення

РгД

ЗМ

0

k-1

N-1

ШДвх

ПрРгА

Звернення

Z=1

n-1

N-1

Зчитування

Операція БУП ПрРгД

ПрШДвих

Зайнято

Запис

1

Аналіз Z

Читання

Операція

Запис

Читання

Пр РгД

ПрШДвих

Запис

БПЗ

0

n-1

Z=0

…

Структура адресної пам'яті та цикл її функціонування

РгА, РгД – регістри адреси і даних;

БАВ – блок адресної вибірки;

БПЗ, БПЧ – блоки підсилювачів запису

та читання;

ЗМ – запам'ятовувальний масив;

БУП – блок управління пам'яттю;

ШДвих, ШДвх – вихідна та

вхідна шини даних.

4.

2. Організація адресної (основної) пам'ятіМодуль ЗП складається з N n-розрядних комірок. Розрядність

адресного коду для адресації ЗМ – k = log2N розрядів.

Звернення до ЗП починається з перевірки сигналу його зайнятості.

Якщо сигнал на виході ЗП “1”, то він зайнятий обслуговуванням іншого

абонента (доступ до нього заборонений). Якщо сигнал "Зайнято"

відсутній (0), то на ША подається k-розрядна адреса, на вхід "Операція“ -- сигнал “0” для читання, або сигнал “1” для запису. Після цього

подається сигнал "Звернення“, БУП виставляє на виході "Зайнято" “1” для

інших абонентів та починає виконувати операцію.

Запис коду адреси в адресний регістр РгА виконується за сигналом

ПрРгА. З виходів РгА код адреси надходить до БАВ, який його дешифрує

його та подає сигнал збудження у відповідну комірку. Після цього комірка

готова до запису або читання інформації.

Для читання БУП видає сигнал "Зчитування", який відкриває входи

БПЧ, код із збудженої комірки надходить на входи РгД. Після цього БУП

видає сигнал ПрРгД, за яким вихідне слово записується в РгД. Зчитана

інформація передається на вихід ЗП в вихідну шину ШДвих.

Запис інформації починається із запису коду інформації з ШДвх в

РгД шляхом подачі сигналу ПрРгД на вхід управління РгД. Сигналом

"Запис" відкриваються входи БПЗ і слово інформації записується у

збуджену комірку ЗМ.

5.

2. Організація адресної (основної) пам'ятіПісля закінчення циклу звернення до пам'яті БПЗ видає на зовнішню

лінію "Зайнято" нульовий сигнал – ЗП вільний і готовий до виконання

наступного циклу.

Основна пам’ять більшості обчислювальних систем є адресною.

Багатопортова адресна пам’ять

N - портовий адресний ЗП (або ЗП з множинним доступом) має N

незалежних наборів шин адреси, даних та управління, що гарантують

одночасний та незалежний доступ до ОЗП N пристроям. Він

використовується в БПКС, а в однопроцесорному ПК, наприклад,яе

пам’ять відеокарти. Конфлікти усуваються за допомогою арбитражу на

основі переривань та семафорів (спеціальних булевих змінних).

Недоліки адресної пам'яті:

необхідність вказувати в командах адреси операндів, що збільшує

їхню довжину;

пошук інформації за адресою вимагає витрат часу на дешифрування

адреси;

часто в програмах послідовність операцій виконується над великої

кількістю даних, які розташовані в комірках пам'яті послідовно.

Звернення до адресної пам'яті для читання кожного такого операнда

значно зменшує швидкість обчислень.

Тому для виконання специфічних функцій в комп'ютерах

застосовуються різні типи безадресної пам'яті:

6.

3. Організація кеш-пам'ятіКеш-пам'ять це “прихована” пам'ять, до якої неможливе

безпосереднє звернення, тому що вона не має системи адресації

комірок. Процесор формує адреси для взаємодії з ОП і не враховує

наявність кеш-пам'яті. Усі завдання, пов'язані з перехопленням запитів

від процесора до основної пам'яті, виконує контролер кеш-пам'яті.

Контролер ЗП утворюють автономну, повністю або частково асоціативну

машину. Відповідно, кеш-пам’ять є “прозорою” для програміста, система

команд процесора не має команд роботи з кеш пам'яттю.

Асоціативний принцип побудови пам'яті передбачає збереження

разом із даними і їх ознаки (ознакою може бути дане або структура, що

містить адресну інформацію – адресний тег. Дані вибираються на основі

збігу їх ознак із заданім шаблоном (кодом пошуку) шляхом їх порівняння

(напрклад, за допомогою порозрядної кон'юнкції).

Асоціативна організація пам'яті дозволяє значно прискорити читання

й запис інформації та забезпечити логічну обробку даних без зчитування

їх із пам'яті.

Основна процедура, яка виконується у асоціативній пам'яті –

контроль асоціації – це пошук інформації за її змістом, який відбувається

паралельно в часі для усіх комірок ЗМ.

7.

3. Організація кеш-пам'ятіВластивість локальності за зверненням до пам'яті

Існує дві передбачувані властивості програм при зверненні до пам'яті:

Просторова локальність – якщо відбулося звернення до деякої

комірки пам'яті, то з великою ймовірністю можна стверджувати, що в

найближчий час відбудеться звернення до сусідньої комірки пам'яті

(послідовний

порядок

виконання

програми

з

використанням

структурованих даних).

Часова локальність – якщо відбулося звернення до деякої комірки

пам'яті, то з великою ймовірністю можна стверджувати, що в найближчий

час знову відбудеться звернення до тієї ж комірки пам'яті (багаторазове

повторення циклів та підпрограм).

Обидва види локальності об'єднує поняття локальності за

зверненням. Існує так зване правило “90/10”: 90% часу роботи

програми пов'язано з доступом до 10% адресного простору цієї

програми. Таким чином, програму розумно представити у вигляді

послідовно оброблювальних фрагментів – компактних груп команд і

даних. Поміщаючи такі фрагменти в швидшу пам'ять, можна істотно

зменшити затримки при багаторазовому зверненні до пам'яті.

8.

3. Організація кеш-пам'ятіПроцесор

Кеш пам'ять

2-го рівня

Оперативна

пам'ять

Типовий підхід до побудови кеш пам'яті -поєднання

характерних рис Гарвардської та Принстонської архітектур. У змішаній

пам'яті (L2) команди та данні зберігаються разом. Перевага: більш

висока імовірність “влучень”, тому що оптимальний баланс між

командами та даними встановлюється автоматично. Якщо

при

виконанні програми звернення до пам'яті в основному пов'язано з

вибіркою команд, (частина звернень до даних відносно мала), змішана

кеш-пам'ять має тенденцію насищатися командами, і навпаки. У

розділеній пам'яті (L2) команди та данні зберігаються в різних блоках

кеш-пам'яті. Перевага: вибірка команд і даних може здійснюватися

одночасно, при цьому виключаються можливі конфлікти.

В першу чергу процесор звертаКеш

ється до кеш-пам'ять L1. Якщо там

команд

немає потрібної команди або

L1

операнда, то він звертається до

кеш-пам'яті L2 другого рівня. За

Кеш

гарвардською архітектурою будуєтьДаних

ся тільки пам’ять L1, застосування

L1

більш трьох рівнів кеш-пам'яті

вважається недоцільним.

9.

3. Організація кеш-пам'ятіОсновні правила організації кеш-пам'яті та основної пам'яті,

які забезпечують їх ефективну взаємодію:

Кеш і ОП діляться на блоки однакового розміру, які можуть вміщувати

однакову кількість слів.

Блок є базовою порцією інформації, яка переміщується між ОП та

кеш- пам'яттю.

Кожній блок має власний номер, нумерація комірок в кожному блоці

однакова.

В блоках кеш пам'яті знаходиться вміст декількох переписаних із

основної пам'яті блоків.

Кожне слово кеш-пам'яті супроводжується адресним тегом, що

вказує, наприклад, початкову адресу відповідного блока у ОП.

Ідентичність вмісту блоків кеш-пам'яті та ОП забезпечується

використанням спеціальних методів оновлення вмісту блоків ОП

(наскрізний або зворотний запис).

Заміна вмісту блоків в кеш-пам'яті вмістом інших блоків з ОП

здійснюється за правилами, які називають алгоритмом заміщення.

Між блоками ОП та кеш-пам'яті встановлюється відповідність, яка

визначається функцією відображення (пряма, повністю або частково

асоціативна).

10.

4. Стекова пам'ятьСтекова пам'ять – безадресна з прямим або оберненим порядком

зчитування (прямий порядок – FIFO – First In, First Out; обернений

порядок – LIFO – Last In, First Out).

Стекова пам'ять з прямим зчитуванням

При запису слова в верхню комірку вміст стека зсувається на одну

комірку униз і до вмісту лічильника стека додається 1. Читання

інформації можливо тільки тоді, коли стек повністю заповнений.

При зчитуванні слова з нижньої комірки вміст стека зсувається на

одну комірку униз, а вміст лічильника стека зменшується на 1. Читання

супроводжується стиранням інформації.

Стекова пам'ять з оберненим зчитуванням

При запису слова в верхню комірку вміст стека зсувається на одну

комірку униз і до вмісту лічильника стека додається 1. При читанні слова

з верхньої комірки вміст стека зсувається уверх, із вмісту лічильника

стека віднімається 1. Таким чином лічильник стека завжди зберігає

кількість записаних в стек слів (зайнятих комірок).

11.

5. Накопичувачі інформації на ЖМДЗовнішня пам'ять (ЗП) відрізняється від внутрішньої способом доступу

процесора до неї. Накопичувачі оперують не байтами або словами, а

блоками інформації (кластерами), які звичайно мають фіксований

розмір, кратний 2n секторів. Блок може бути переписаний із ЗП у

внутрішню пам’ять або навпаки тільки цілком. Спеціальні процедури

обміну з пристроями ЗП прив'язані до типу пристрою, його контролеру і

способу підключення пристрою до системи (інтерфейсу).

У пристроях збереження даних можуть бути реалізовані різні фізичні

принципи збереження інформації – магнітний, оптичний, електронний у

будь-яких сполученнях.

За методом доступу до інформації пристрої ЗП розділяються

на пристрої з прямим (або безпосереднім) і послідовним

доступом. Традиційними пристроями з прямим доступом є дискові

накопичувачі, і часто поняття "диск" і "пристрій ЗП прямого доступу"

вживають як синоніми.

Пристрої ЗП можуть мати змінні або фіксовані носії інформації.

Наприклад, накопичувачі на гнучких магнітних дисках (НГМД)

використовують змінні носії – дискети, а носії накопичувачів на жорстких

магнітних дисках (НЖМД) – фіксовані. Основною ЗП комп'ютера є

НЖМД.

12.

5. Накопичувачі інформації на ЖМДФорм-фактори НЖМД різних поколінь

13.

5. Накопичувачі інформації на ЖМДКонструктивно НЖМД складається з двох основних частин –

герметизованого блока (HDA) і плати електроніки (PCB). У

гермоблоці розташовані всі механічні компоненти (пакет магнітних

дисків, насаджений на шпиндель двигуна, магнітні головки з системою

позиціювання) а також мікросхема попереднього підсилювачакомутатора, що забезпечує підсилювання сигналу з головок та

переключення між ними.

Важіль переміщення головок

Пакет

дисків

Привод

головок

Шасі

Склад гермоблоку

Кріпильні отвори

Голівка читання / запису

На PCB, яка розміщується за межами HDA, встановлені мікросхеми,

що керують механічними вузлами, кодуванням-декодуванням даних та

прийомом-передачею інформації через зовнішній інтерфейс.

14.

5. Накопичувачі інформації на ЖМДМетод зонно-секційного запису

Доріжки (циліндри):

- зовнішня;

Зовнішня

зона

- середня;

Внутрішня

зона

- внутрішня;

Сектор

Сектор

Дібіт

Індексний маркер

Ємність HDD:

V = C H S 512 байт (4 Кбайт у розширеному форматі),

С - кількість циліндрів, що дорівнює кількості доріжок на одному диску;

Н - кількість головок (по дві на один диск);

S - кількість секторів на доріжці;

512 байт або 4 Кбайт – доступна ємність сектора для збереження

даних (фізичний розмір сектора з урахуванням службової інформації

більше).

Кластер

15.

5. Накопичувачі інформації на ЖМДВихідний стан ЖМД після його виготовлення – це однорідна магнітна

поверхня, яку умовно можна уявити як невпорядковану сукупність

дібітів – елементарних ділянок, що можуть, за рахунок залишкової

намагніченості, зберігати один біт інформації. Для організації зберігання

інформації, її запису, пошуку та читання, необхідно цю сукупність

впорядкувати.

Групи дібітів об’єднуються у «інформаційні кільця» -- доріжки або

треки. Нумерація доріжок починається з нуля, нульова доріжка завжди

розташована з зовнішнього боку диска.

Якщо накопичувач має декілька робочих поверхонь, (тобто на

шпинделі розміщений пакет дисків, а у кожного диска можуть

використовуватися обидві поверхні), то сукупність усіх доріжок з

однаковими номерами називають циліндром. Для кожної робочої

поверхні в накопичувачі є своя головка, що забезпечує запис і

зчитування інформації.

Для забезпечення точного позиціювання БМГ на необхідну доріжку

(циліндр) на поверхню диска наносяться сервісні мітки. Нанесення

серворозмітки виконується тільки у заводських умовах і є базовим,

найбільш низькорівневим елементом форматування ЖМД.

16.

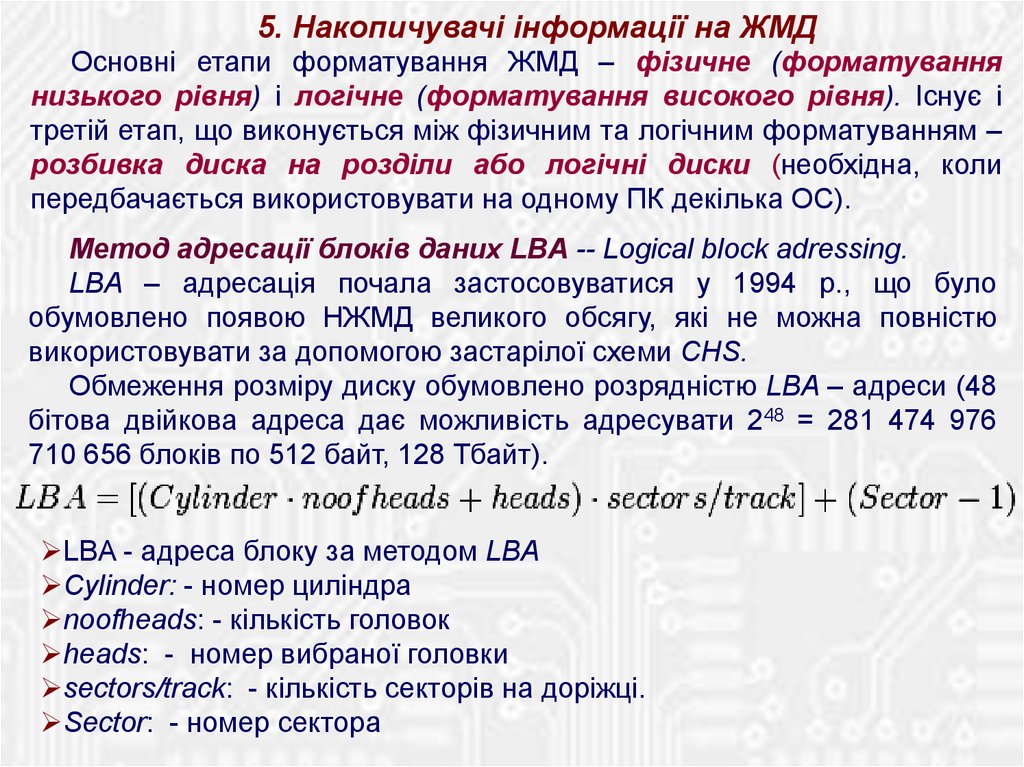

5. Накопичувачі інформації на ЖМДОсновні етапи форматування ЖМД – фізичне (форматування

низького рівня) і логічне (форматування високого рівня). Існує і

третій етап, що виконується між фізичним та логічним форматуванням –

розбивка диска на розділи або логічні диски (необхідна, коли

передбачається використовувати на одному ПК декілька ОС).

Метод адресації блоків даних LBA -- Logical block adressing.

LBA – адресація почала застосовуватися у 1994 р., що було

обумовлено появою НЖМД великого обсягу, які не можна повністю

використовувати за допомогою застарілої схеми CHS.

Обмеження розміру диску обумовлено розрядністю LBA – адреси (48

бітова двійкова адреса дає можливість адресувати 248 = 281 474 976

710 656 блоків по 512 байт, 128 Тбайт).

LBA - адреса блоку за методом LBA

Cylinder: - номер циліндра

noofheads: - кількість головок

heads: - номер вибраної головки

sectors/track: - кількість секторів на доріжці.

Sector: - номер сектора

17.

5. Накопичувачі інформації на ЖМДОсновні інтерфейси НЖМД

РАТА

ATA (Advanced Technology Attachment)

ATA / PATA — паралельний інтерфейс для

підключення НЖМД та оптичних приводів,

створений у 80-х роках минулого століття.

Після появи послідовного інтерфейсу SATA

отримав назву PATA (паралельний ATA).

Остання версія Ultra ATA / 133 має

теоретичну швидкість передачі даних

133 Мб/с., реальну -- 66 Мб/с.

SАТА

SATA (Serial ATA) – послідовний інтерфейс для підключення НЖМД,

використовується з початку 2000 років. Перша версія SATA / 150 має

теоретичну швидкість передачі даних до 150 Мб/с, остання SATA / 600 –

до 600 Мб/с. Середня швидкість сучасних НЖМД – близько 150 Мб/с.

Три версії послідовного інтерфейсу часто називають SATA I, SATA II,

SATA III. Різні версії інтерфейса мають зворотну сумісність. SATA III

підтримує “гарячу” заміну НЖМД.

18.

6. Масиви НЖМД з надлишковістюМетод RAID (Redundant Arrays of Inexpensive Disks) – масив

незалежних дисків з надлишковістю – був запропонований у 1987 р.

Для RAID - масивів характерні три загальні властивості:

це набір фізичних НЖМД, що розглядаються ОС як единий логічний

диск;

данні розподілені по фізичним дискам масиву;

“надлишковий” дисковий простір використовується для збереження

додаткової інформації, яка гарантує відновлення даних у випадку

відмови НЖМД.

Підвищення продуктивності досягається з допомогою розподілу

даних та дискового простору на сегменти (смуги). Смуги розподіляються

по різним дискам масиву, що дозволяє паралельно записувати або

зчитувати відразу декілька смуг.

Підвищення

відмовостійкості

досягається

за

рахунок

“надлишкового” дискового простору, який використовується для

збереження додаткової інформації, що дозволяє відновлювати

спотворені або втрачені данні. В RAID технології використовується

наступні способи підвищення відмовостійкості: дублювання інформації;

використання завадостійкого коду Хемінга; використання бітів контролю

парності.

19.

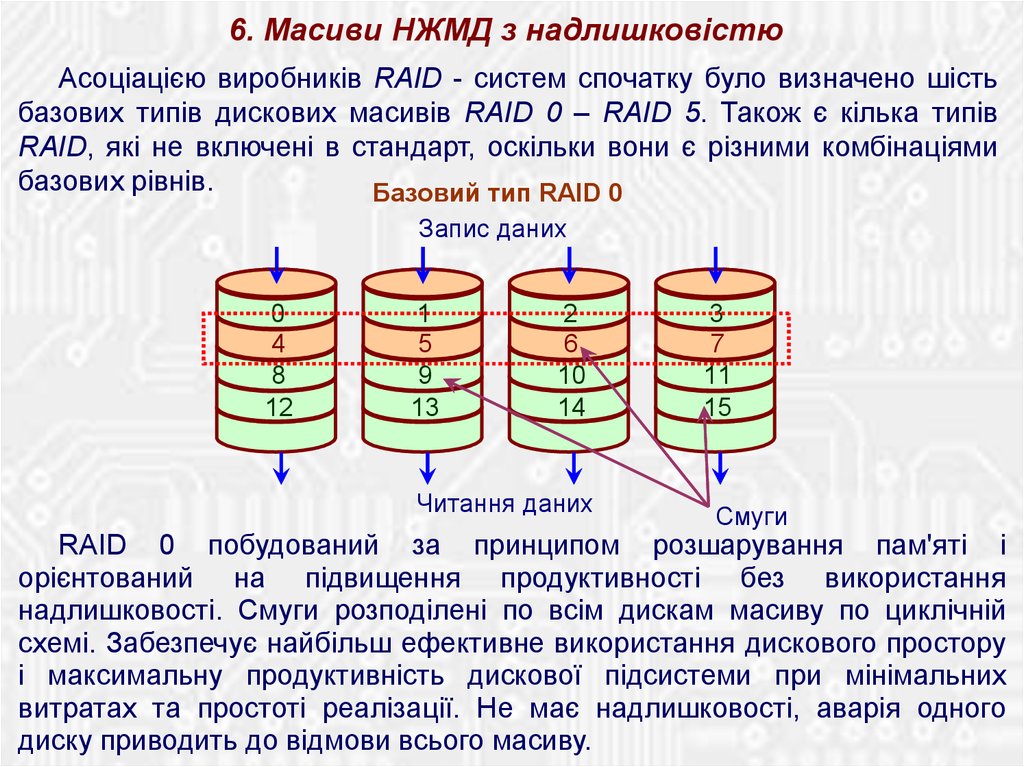

6. Масиви НЖМД з надлишковістюАсоціацією виробників RAID - систем спочатку було визначено шість

базових типів дискових масивів RAID 0 – RAID 5. Також є кілька типів

RAID, які не включені в стандарт, оскільки вони є різними комбінаціями

базових рівнів.

Базовий тип RAID 0

Запис даних

0

4

8

12

1

5

9

13

2

6

10

14

Читання даних

3

7

11

15

Смуги

Пояс

RAID 0 побудований за принципом розшарування пам'яті і

орієнтований на підвищення продуктивності без використання

надлишковості. Смуги розподілені по всім дискам масиву по циклічній

схемі. Забезпечує найбільш ефективне використання дискового простору

і максимальну продуктивність дискової підсистеми при мінімальних

витратах та простоті реалізації. Не має надлишковості, аварія одного

диску приводить до відмови всього масиву.

20.

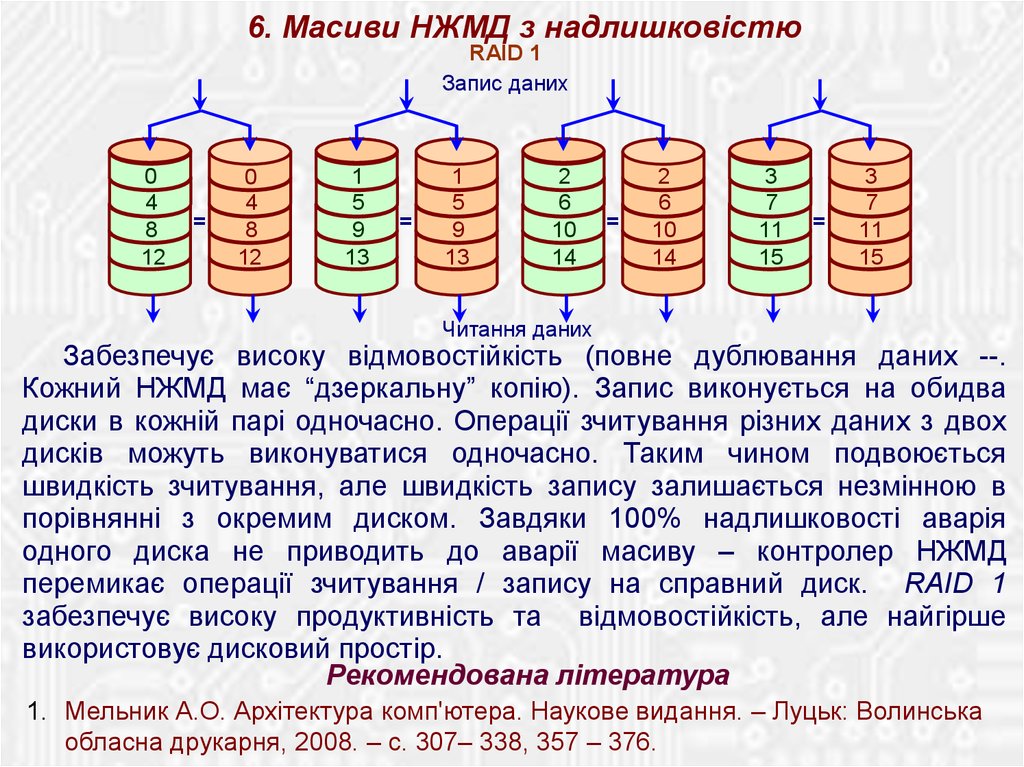

6. Масиви НЖМД з надлишковістюRAID 1

Запис даних

0

4

8

12

=

0

1

4

8

9

12

3

1

5

9

13

2

=

1

5

9

13

2

6

10

14

=

2

6

10

14

3

7

11

15

=

3

7

11

15

Читання даних

Забезпечує високу відмовостійкість (повне дублювання даних --.

Кожний НЖМД має “дзеркальну” копію). Запис виконується на обидва

диски в кожній парі одночасно. Операції зчитування різних даних з двох

дисків можуть виконуватися одночасно. Таким чином подвоюється

швидкість зчитування, але швидкість запису залишається незмінною в

порівнянні з окремим диском. Завдяки 100% надлишковості аварія

одного диска не приводить до аварії масиву – контролер НЖМД

перемикає операції зчитування / запису на справний диск. RAID 1

забезпечує високу продуктивність та відмовостійкість, але найгірше

використовує дисковий простір.

Рекомендована література

1. Мельник А.О. Архітектура комп'ютера. Наукове видання. – Луцьк: Волинська

обласна друкарня, 2008. – с. 307– 338, 357 – 376.

informatics

informatics