Similar presentations:

Введение в SPICE

1. План

Введение в SPICEDC анализ

Временной анализ

Подсхемы

Измерение мощности

SPICE

CMOS VLSI Design

Slide 1

2. Введение в SPICE

Simulation Program with Integrated Circuit Emphasis– Разработана в 1970 в Беркли

– Множество коммерческих продуктов

– HSPICE давно стал индустриальным

стандартом

• Множество возможностей

Написан на Фортране для машин на перфокартах

– Схемные элементы называются картами (cards)

– Полное описание называется - SPICE deck

(колода, дека)

SPICE

CMOS VLSI Design

Slide 2

3. Создание SPICE описания

Похоже на написание программы– Схема: нарисуйте на бумаге или в редакторе

• Проставьте узлы

• Если возможно используйте существующую

– Код: стремитесь к ясности

• Начните с имени, даты, цели

• Общий комментарий

– Тестирование:

• Предположите, что должно получиться

• Сравните с реальностью

• Garbage In, Garbage Out!

SPICE

CMOS VLSI Design

Slide 3

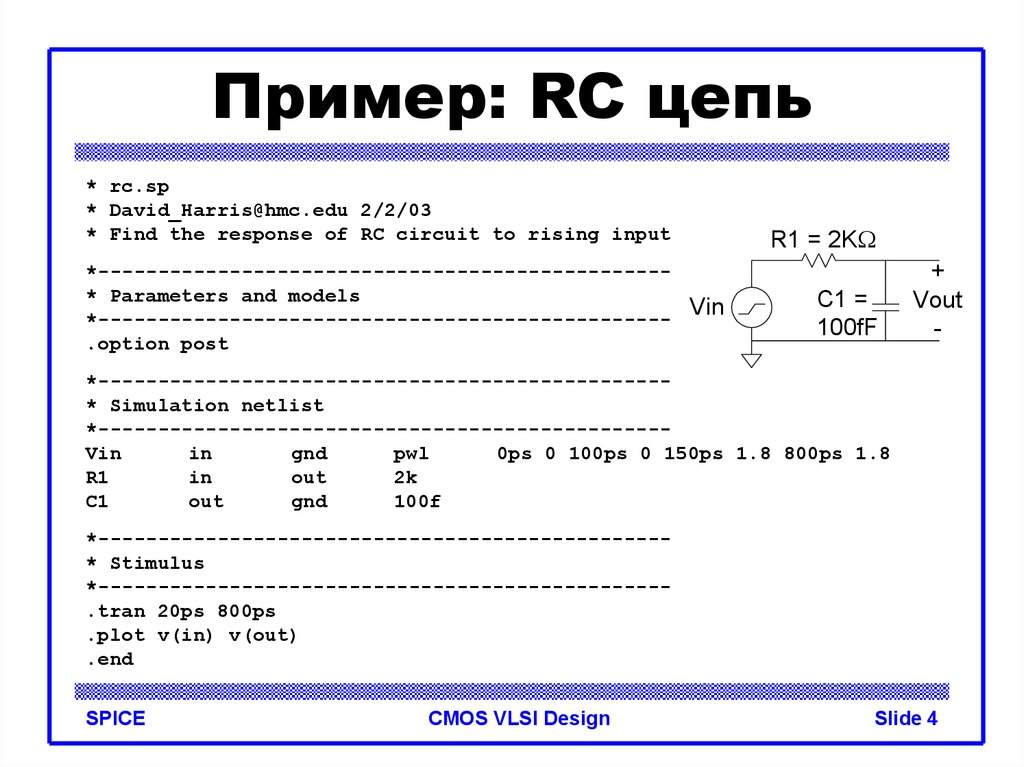

4. Пример: RC цепь

* rc.sp* David_Harris@hmc.edu 2/2/03

* Find the response of RC circuit to rising input

*-----------------------------------------------* Parameters and models

Vin

*-----------------------------------------------.option post

R1 = 2K

C1 =

100fF

+

Vout

-

*-----------------------------------------------* Simulation netlist

*-----------------------------------------------Vin

in

gnd

pwl

0ps 0 100ps 0 150ps 1.8 800ps 1.8

R1

in

out

2k

C1

out

gnd

100f

*-----------------------------------------------* Stimulus

*-----------------------------------------------.tran 20ps 800ps

.plot v(in) v(out)

.end

SPICE

CMOS VLSI Design

Slide 4

5. График результата

2.0v(in)

v(out)

1.5

1.0

0.5

0.0

0.0 100p 200p 300p 400p 500p 600p 700p 800p 900p

t(s)

SPICE

CMOS VLSI Design

Slide 5

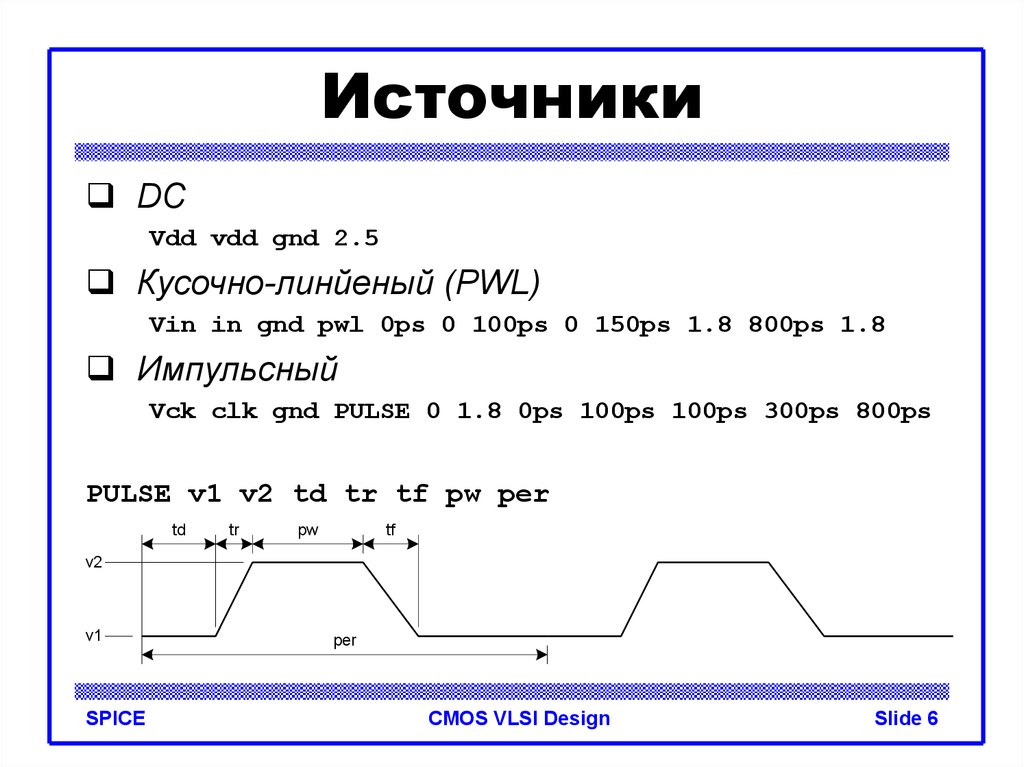

6. Источники

DCVdd vdd gnd 2.5

Кусочно-линйеный (PWL)

Vin in gnd pwl 0ps 0 100ps 0 150ps 1.8 800ps 1.8

Импульсный

Vck clk gnd PULSE 0 1.8 0ps 100ps 100ps 300ps 800ps

PULSE v1 v2 td tr tf pw per

td

tr

pw

tf

v2

v1

SPICE

per

CMOS VLSI Design

Slide 6

7. SPICE элементы

СимволR

C

L

K

V

I

M

D

Q

W

X

E

G

H

F

SPICE

Элемент

Резистор

Конденсатор

Индуктивность

Связанные индуктивности

Независимый источник напряжения

Независимый источник тока

МОП -транзистор

диод

Биполярный транзистор

Линия передачи с потерями

Подсхема

Управляемый напряжением источник напряжения

Управляемый напряжением источник тока

Управляемый током источник напряжения

Управляемый током источник тока

CMOS VLSI Design

Slide 7

8. Размерные приставки

СимволПриставка

Степень

a

атто

10-18

f

фемто

10-15

p

пико

10-12

n

нано

10-9

u

микро

10-6

m

милли

10-3

k

кило

103

x

мега

106

g

гига

109

Пример: емкость 100 фемтофарад = 100fF, 100f, 100e-15

SPICE

CMOS VLSI Design

Slide 8

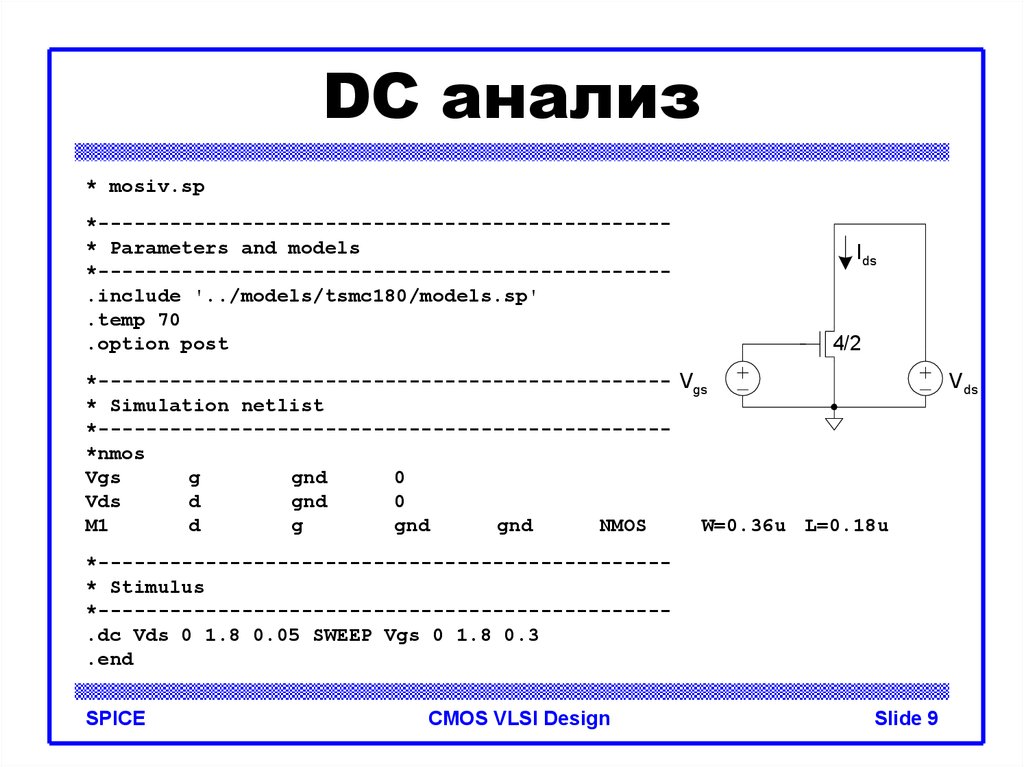

9. DC анализ

* mosiv.sp*-----------------------------------------------* Parameters and models

*-----------------------------------------------.include '../models/tsmc180/models.sp'

.temp 70

.option post

Ids

4/2

*------------------------------------------------ Vgs

* Simulation netlist

*-----------------------------------------------*nmos

Vgs

g

gnd

0

Vds

d

gnd

0

M1

d

g

gnd

gnd

NMOS

W=0.36u L=0.18u

*-----------------------------------------------* Stimulus

*-----------------------------------------------.dc Vds 0 1.8 0.05 SWEEP Vgs 0 1.8 0.3

.end

SPICE

CMOS VLSI Design

Slide 9

V ds

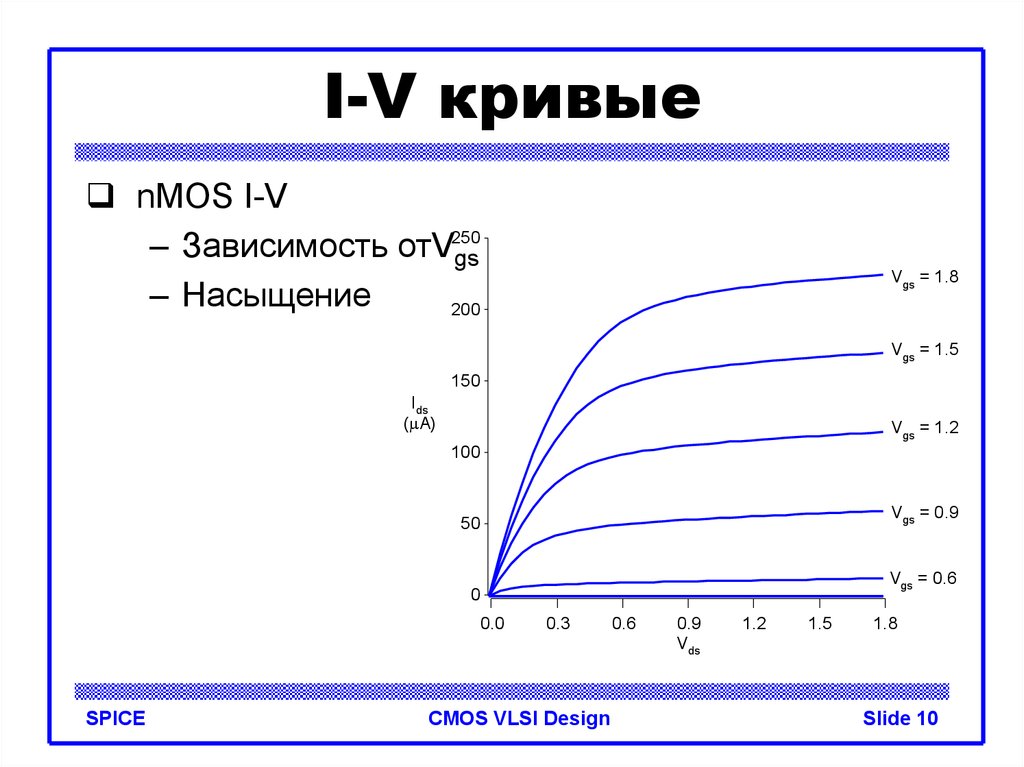

10. I-V кривые

nMOS I-V– Зависимость отV250

gs

– Насыщение

200

Vgs = 1.8

Vgs = 1.5

150

Ids

( A)

Vgs = 1.2

100

Vgs = 0.9

50

Vgs = 0.6

0

0.0

SPICE

0.3

CMOS VLSI Design

0.6

0.9

Vds

1.2

1.5

1.8

Slide 10

11. MOS транзистор

M элемент для MOSFETMname drain gate source body type

+ W=<width> L=<length>

+ AS=<area source> AD = <area drain>

+ PS=<perimeter source> PD=<perimeter drain>

SPICE

CMOS VLSI Design

Slide 11

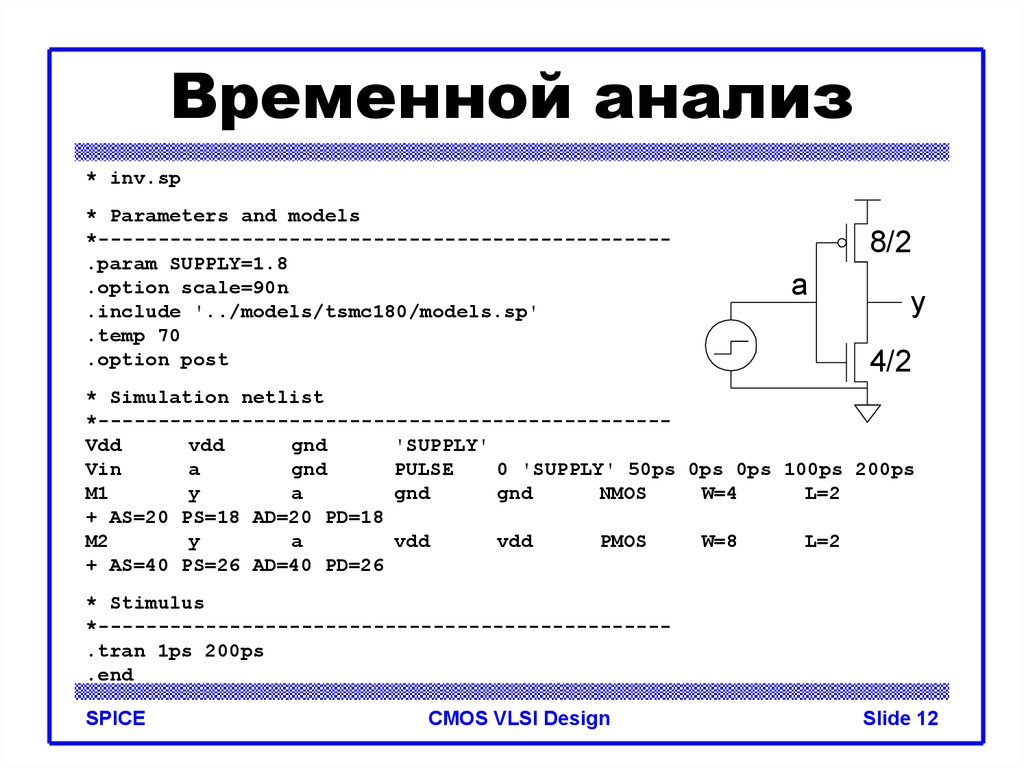

12. Временной анализ

* inv.sp* Parameters and models

*-----------------------------------------------.param SUPPLY=1.8

.option scale=90n

.include '../models/tsmc180/models.sp'

.temp 70

.option post

8/2

a

y

4/2

* Simulation netlist

*-----------------------------------------------Vdd

vdd

gnd

'SUPPLY'

Vin

a

gnd

PULSE

0 'SUPPLY' 50ps 0ps 0ps 100ps 200ps

M1

y

a

gnd

gnd

NMOS

W=4

L=2

+ AS=20 PS=18 AD=20 PD=18

M2

y

a

vdd

vdd

PMOS

W=8

L=2

+ AS=40 PS=26 AD=40 PD=26

* Stimulus

*-----------------------------------------------.tran 1ps 200ps

.end

SPICE

CMOS VLSI Design

Slide 12

13. Временной анализ

Ненагруженный инвертер– Перегурзка

– Крутые

1.8

Фронт/срез

v(a)

v(y)

1.44

tf = 10ps

(V) 1.0

tpdf = 12ps

tpdr = 15ps

tr = 16ps

0.36

0.0

0.0

SPICE

50p

CMOS VLSI Design

100p

t(s)

150p

200p

Slide 13

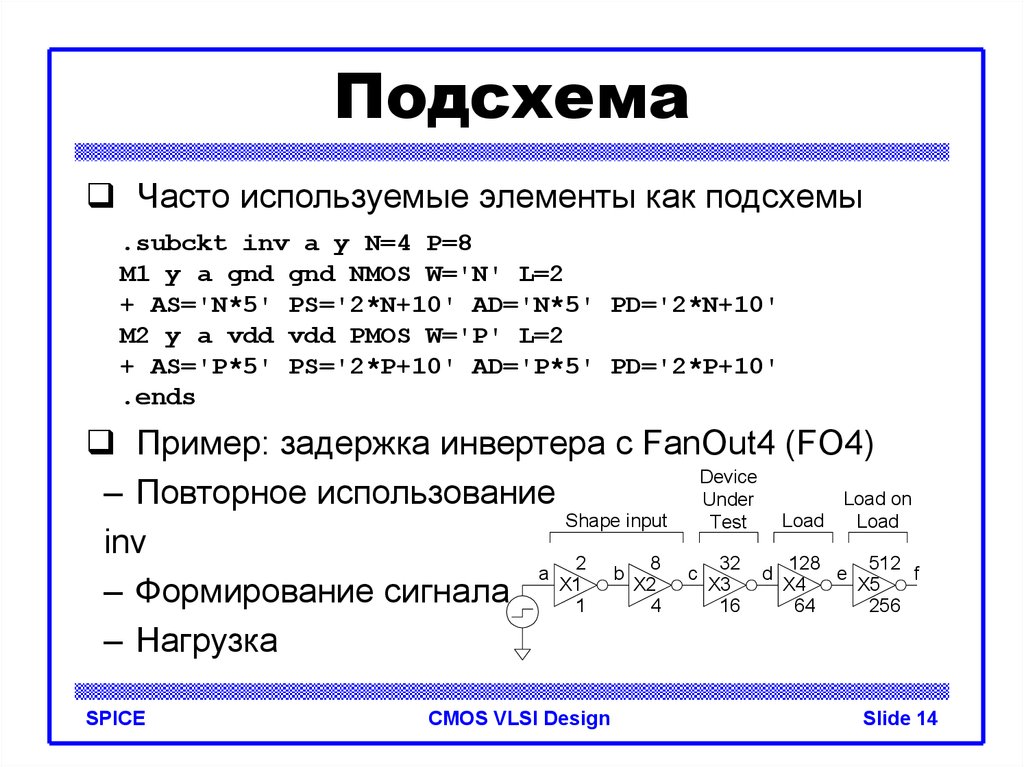

14. Подсхема

Часто используемые элементы как подсхемы.subckt inv a y N=4 P=8

M1 y a gnd gnd NMOS W='N' L=2

+ AS='N*5' PS='2*N+10' AD='N*5' PD='2*N+10'

M2 y a vdd vdd PMOS W='P' L=2

+ AS='P*5' PS='2*P+10' AD='P*5' PD='2*P+10'

.ends

Пример: задержка инвертера с FanOut4 (FO4)

Device

– Повторное использование

Load on

Under

Shape input

Load

Load

Test

inv

2

8

32

128

512

a

b

c

d

e

f

X1

X2

X3

X4

X5

– Формирование сигнала

1

4

16

64

256

– Нагрузка

SPICE

CMOS VLSI Design

Slide 14

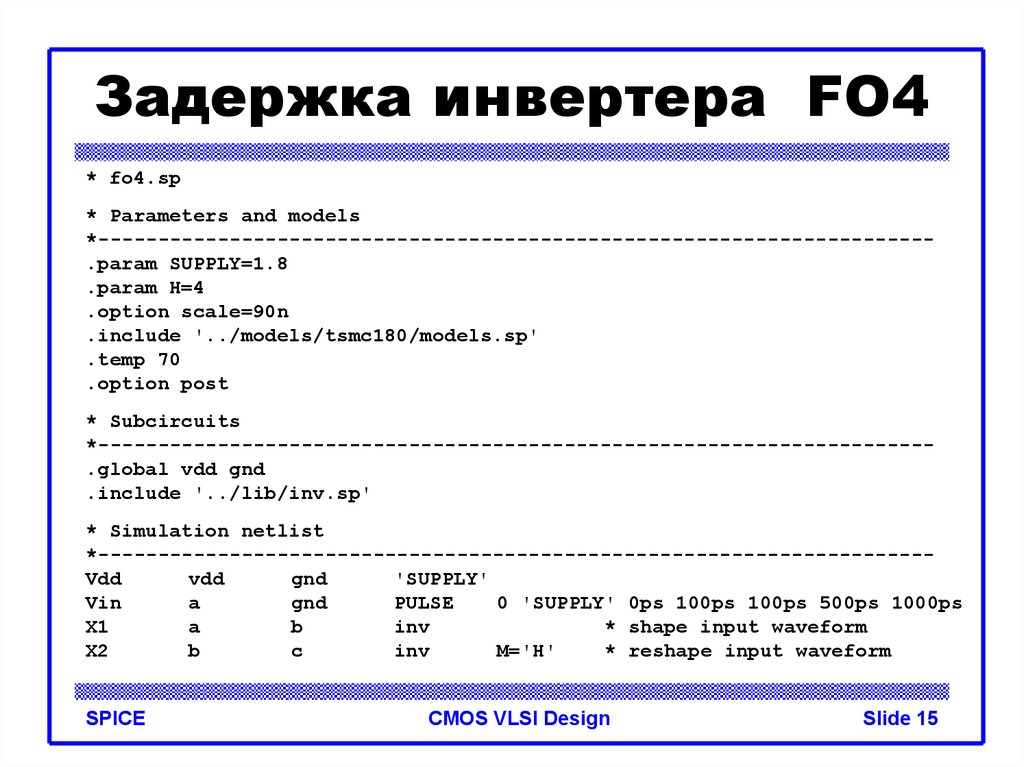

15. Задержка инвертера FO4

* fo4.sp* Parameters and models

*---------------------------------------------------------------------.param SUPPLY=1.8

.param H=4

.option scale=90n

.include '../models/tsmc180/models.sp'

.temp 70

.option post

* Subcircuits

*---------------------------------------------------------------------.global vdd gnd

.include '../lib/inv.sp'

* Simulation netlist

*---------------------------------------------------------------------Vdd

vdd

gnd

'SUPPLY'

Vin

a

gnd

PULSE

0 'SUPPLY' 0ps 100ps 100ps 500ps 1000ps

X1

a

b

inv

* shape input waveform

X2

b

c

inv

M='H'

* reshape input waveform

SPICE

CMOS VLSI Design

Slide 15

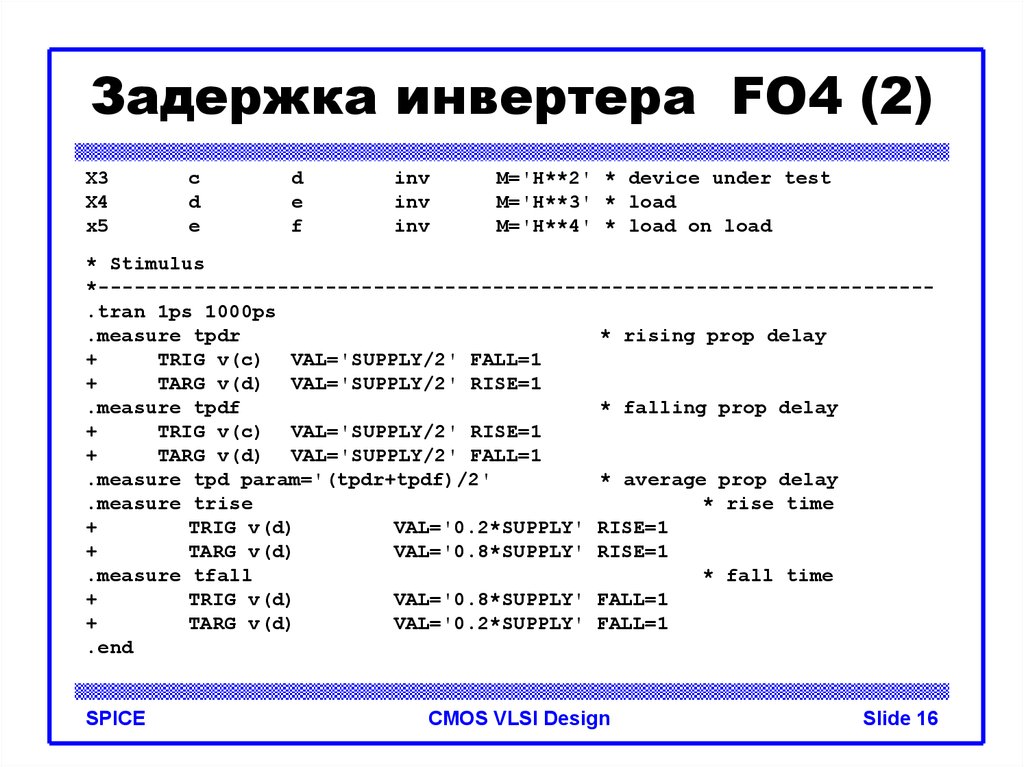

16. Задержка инвертера FO4 (2)

X3X4

x5

c

d

e

d

e

f

inv

inv

inv

M='H**2' * device under test

M='H**3' * load

M='H**4' * load on load

* Stimulus

*---------------------------------------------------------------------.tran 1ps 1000ps

.measure tpdr

* rising prop delay

+

TRIG v(c) VAL='SUPPLY/2' FALL=1

+

TARG v(d) VAL='SUPPLY/2' RISE=1

.measure tpdf

* falling prop delay

+

TRIG v(c) VAL='SUPPLY/2' RISE=1

+

TARG v(d) VAL='SUPPLY/2' FALL=1

.measure tpd param='(tpdr+tpdf)/2'

* average prop delay

.measure trise

* rise time

+

TRIG v(d)

VAL='0.2*SUPPLY' RISE=1

+

TARG v(d)

VAL='0.8*SUPPLY' RISE=1

.measure tfall

* fall time

+

TRIG v(d)

VAL='0.8*SUPPLY' FALL=1

+

TARG v(d)

VAL='0.2*SUPPLY' FALL=1

.end

SPICE

CMOS VLSI Design

Slide 16

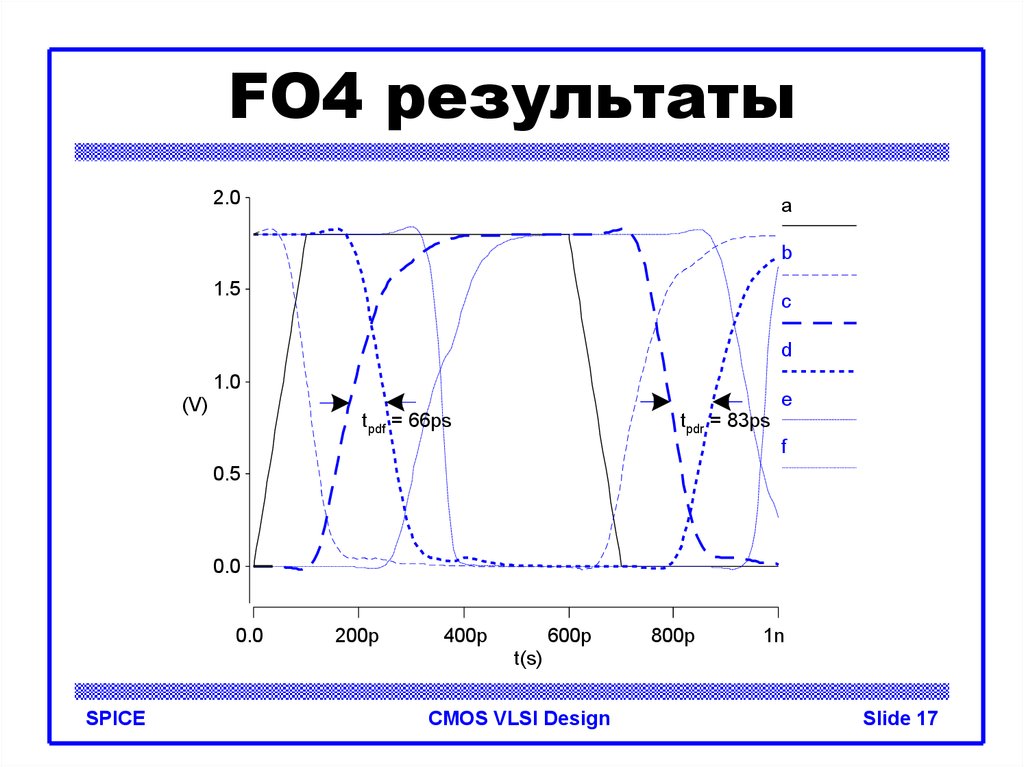

17. FO4 результаты

2.0a

b

1.5

c

d

1.0

(V)

e

tpdf = 66ps

tpdr = 83ps

f

0.5

0.0

0.0

200p

400p

600p

800p

1n

t(s)

SPICE

CMOS VLSI Design

Slide 17

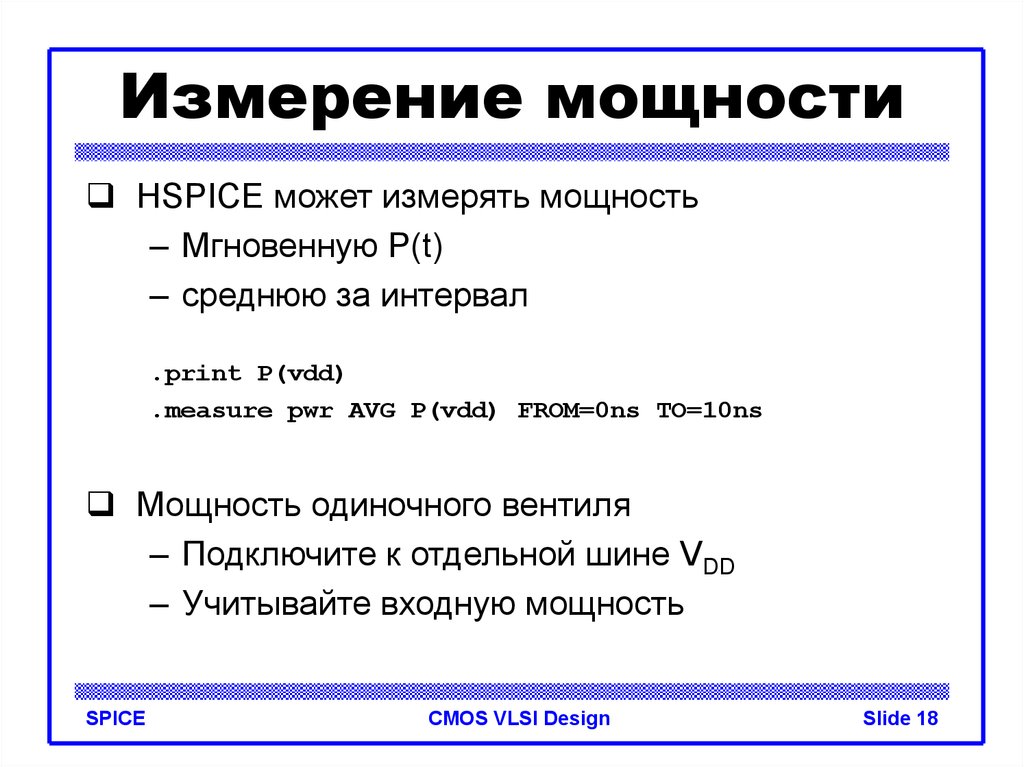

18. Измерение мощности

HSPICE может измерять мощность– Мгновенную P(t)

– среднюю за интервал

.print P(vdd)

.measure pwr AVG P(vdd) FROM=0ns TO=10ns

Мощность одиночного вентиля

– Подключите к отдельной шине VDD

– Учитывайте входную мощность

SPICE

CMOS VLSI Design

Slide 18

informatics

informatics