Similar presentations:

L09_sound(2)

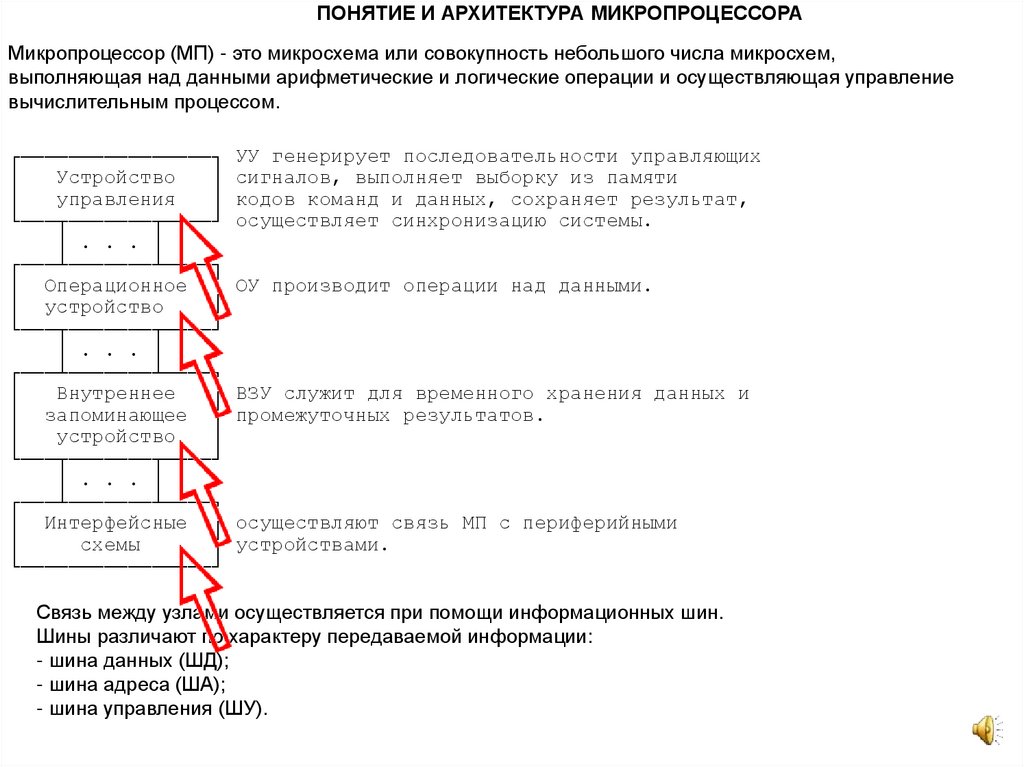

1. ПОНЯТИЕ И АРХИТЕКТУРА МИКРОПРОЦЕССОРА

Микропроцессор (МП) - это микросхема или совокупность небольшого числа микросхем,выполняющая над данными арифметические и логические операции и осуществляющая управление

вычислительным процессом.

┌────────────────┐ УУ генерирует последовательности управляющих

│

Устройство

│ сигналов, выполняет выборку из памяти

│

управления

│ кодов команд и данных, сохраняет результат,

└───┬───────┬────┘ осуществляет синхронизацию системы.

│ . . . │

┌───┴───────┴────┐

│ Операционное │ ОУ производит операции над данными.

│ устройство

│

└───┬───────┬────┘

│ . . . │

┌───┴───────┴────┐

│

Внутреннее

│ ВЗУ служит для временного хранения данных и

│ запоминающее │ промежуточных результатов.

│

устройство

│

└───┬───────┬────┘

│ . . . │

┌───┴───────┴────┐

│ Интерфейсные │ осуществляют связь МП с периферийными

│

схемы

│ устройствами.

└────────────────┘

Связь между узлами осуществляется при помощи информационных шин.

Шины различают по характеру передаваемой информации:

- шина данных (ШД);

- шина адреса (ША);

- шина управления (ШУ).

2. КЛАССИФИКАЦИЯ И ОСНОВНЫЕ ХАРАКТЕРИСТИКИ МП

Классификация микропроцессоров осуществляется по следующим показателям :1. Разрядность слова данных — 4, 8, 16, 32, 64, 128;

2. Архитектура

а) Фон-Неймана

б) Гарвардская

в) Модифицированная Гарвардская

3.Система и набор команд

а) Полный набор (CISC)

б) Ограниченный (RISC)

4.Тип управляющего устройства а) схемное управление - фиксированная система команд

б) микропрограммное управление - изменяемая с/к;

5.Тип микроэлектронной технологии, Отсюда:

а) Быстродействие;

б) Энергопотребление;

4.Количество кристаллов

а) Однокристальные;

б) Многокристальные;

6.Емкость адресуемой памяти, отсюда — разрядность шины адреса;

8.Микропроцессоры и однокристальные ЭВМ (микроконтроллеры);

и др. показатели.

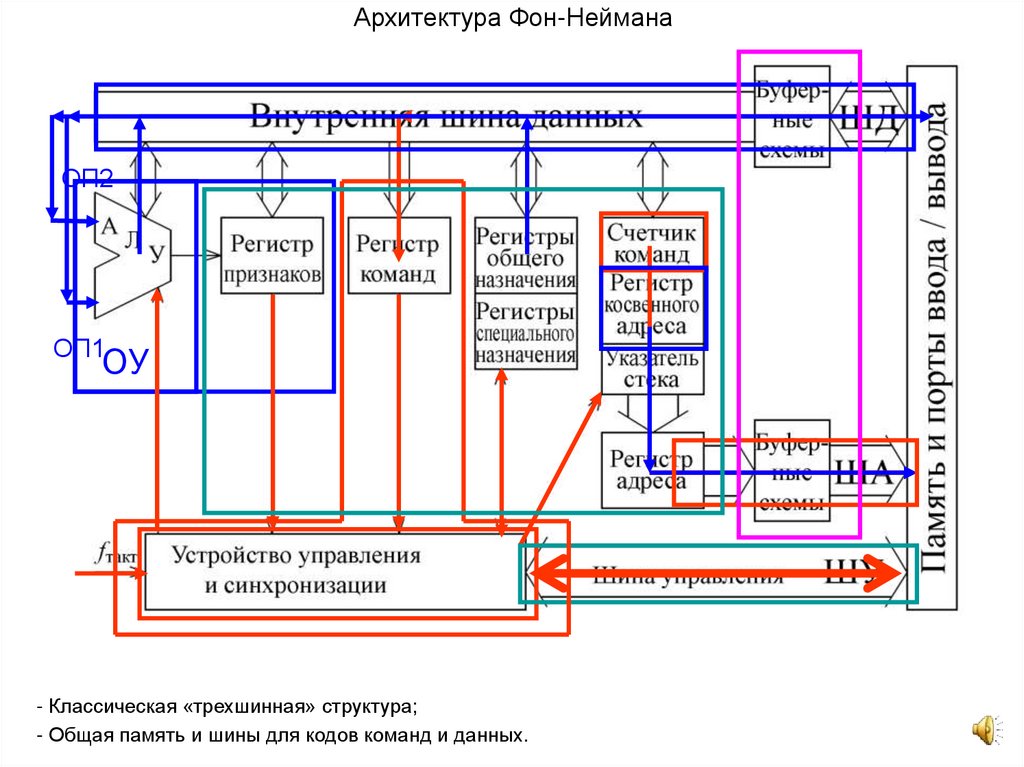

3. Архитектура Фон-Неймана

ОП2ОП1

ОУ

- Классическая «трехшинная» структура;

- Общая память и шины для кодов команд и данных.

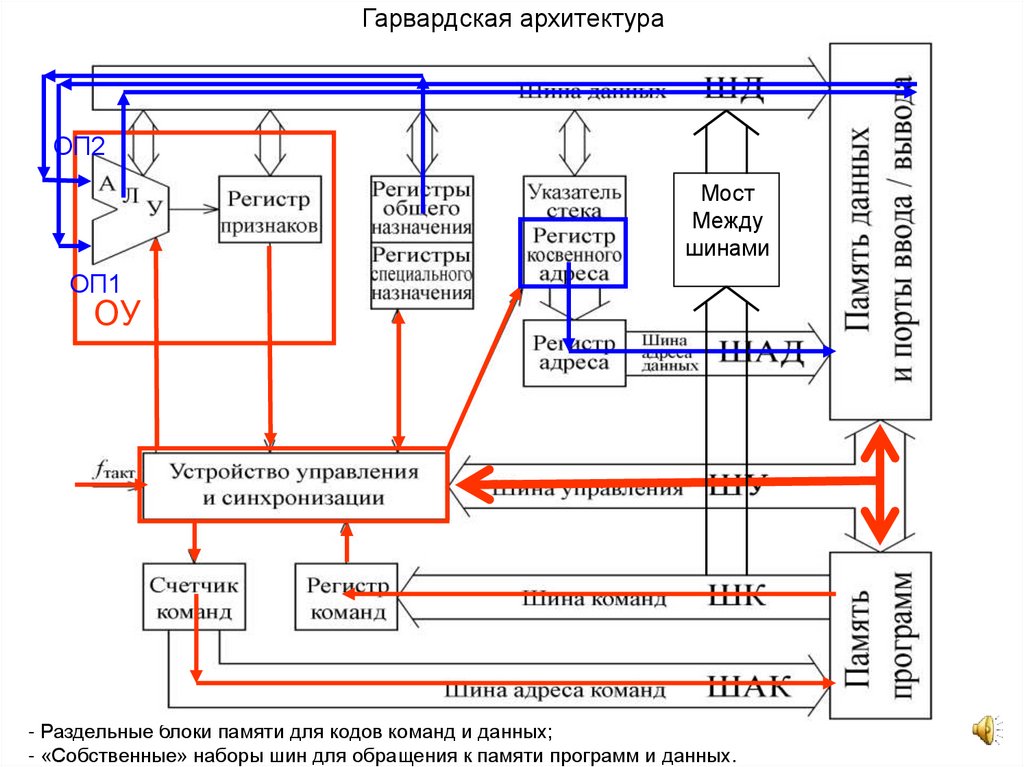

4. Гарвардская архитектура

ОП2Мост

Между

шинами

ОП1

ОУ

- Раздельные блоки памяти для кодов команд и данных;

- «Собственные» наборы шин для обращения к памяти программ и данных.

electronics

electronics