Similar presentations:

Урок - 5

1. Лекция №5 Принципы организации ЭВМ

ЛЕКЦИЯ №5ПРИНЦИПЫ ОРГАНИЗАЦИИ

ЭВМ

2. План лекции

1. Классификациямикропроцессоров.

2. Типовая структура

микропроцессора

ПЛАН ЛЕКЦИИ

(Архитектура фон Неймана и

Гарвардская).

3. Детальный разбор структуры

ядра МП (АЛУ, РОН, УУ).

4. Системный уровень: шины,

память, периферия.

5. Краткие итоги.

2

3. Давайте вспомним

ДАВАЙТЕ ВСПОМНИМ1) Что такое микропроцессор?

2) Почему один процессор мощный и требует

охлаждения, а другой — маломощный и

работает от батарейки?

1) Микропроцессор это устройство,

представляющее собой одну или несколько

больших интегральных схем (БИС),

выполняющих функции процессора ЭВМ.

Классическое вычислительное устройство состоит

из арифметического устройства (АУ), устройства

управления (УУ), запоминающего устройства (ЗУ)

и устройства ввода-вывода (УВВ).

2) Ответ кроется в их классификации и

внутренней структуре.

Цель сегодняшней лекции: разобраться, какие бывают микропроцессоры, как их классифицируют и

из каких основных блоков они состоят.

3

4. Классификация микропроцессоров

КЛАССИФИКАЦИЯ МИКРОПРОЦЕССОРОВПо архитектуре набора команд (ISA - Instruction Set

Architecture)

1) CISC (Complex Instruction Set Computing):

Большой набор сложных команд, каждая из

которых может выполнять несколько

низкоуровневых операций.

2) RISC (Reduced Instruction Set Computing):

Пример: архитектура x86 (Intel, AMD).

Плюсы: высокая плотность кода, упрощение

работы компилятора.

Минусы: сложность декодирования команд,

высокое энергопотребление

Сокращенный набор простых команд,

выполняющихся за один такт.

Пример: архитектуры ARM, RISC-V,

MIPS.

Плюсы: простота и высокая тактовая

частота, низкое энергопотребление.

Минусы: меньшая плотность кода,

программа может состоять из большего

числа команд.

4

5. Классификация микропроцессоров

КЛАССИФИКАЦИЯ МИКРОПРОЦЕССОРОВПо архитектуре набора команд (ISA - Instruction Set

Architecture)

3) VLIW (Very Long Instruction Word):

Длинная команда, содержащая

несколько операций, которые могут

выполняться параллельно.

Пример: некоторые процессоры для

цифровой обработки сигналов

(DSP).

4) MISC (Minimal Instruction Set

Computing):

Ультра-редуцированный набор

команд (например, архитектура

Transport Triggered).

5

6. Классификация микропроцессоров

КЛАССИФИКАЦИЯ МИКРОПРОЦЕССОРОВПо количеству ядер

Одноядерные процессоры — процессоры с

одним ядром.

Intel Celeron 220 — микропроцессор для

материнских плат Mini-ITX, также применяется в

некоторых бюджетных ноутбуках.

Многоядерный процессор — центральный

процессор, содержащий два и более

вычислительных ядра на одном

процессорном кристалле или в одном

корпусе.

Pentium 4 — одноядерный настольный процессор.

Xeon — одноядерный серверный процессор, в

котором изначально была реализована технология

гиперпоточности.

6

7. Классификация микропроцессоров

КЛАССИФИКАЦИЯ МИКРОПРОЦЕССОРОВПо назначению и сфере применения

o

Микропроцессоры общего назначения (CPU - Central

Processing Unit):

o

Универсальные процессоры для широкого круга задач

(ПК, серверы).

Микроконтроллер - "компьютер на одном

кристалле". Включает ядро, память и

периферию для управления устройствами.

Акцент на высокую производительность в

последовательных вычислениях.

Микроконтроллеры (MCU - Microcontroller Unit):

"Компьютер на одном кристалле". Включает в себя

ядро, память (ROM, RAM) и периферийные

устройства

Применение: встраиваемые системы, IoT, управление

устройствами.

7

8. Классификация микропроцессоров

КЛАССИФИКАЦИЯ МИКРОПРОЦЕССОРОВПо назначению и сфере применения

o

Цифровые сигнальные процессоры (DSP - Digital Signal

Processor):

o

Специализированы на быстром выполнении

математических операций (например, БПФ, свертка).

Оптимизированы для потоковой обработки данных в

реальном времени.

Применение: аудио/видео обработка,

телекоммуникации, радары.

Специализированные процессоры (ASIC):

Проектируются под одну конкретную задачу (майнинг

криптовалют, обработка нейросетей).

8

9. Классификация микропроцессоров

КЛАССИФИКАЦИЯ МИКРОПРОЦЕССОРОВПо назначению и сфере применения

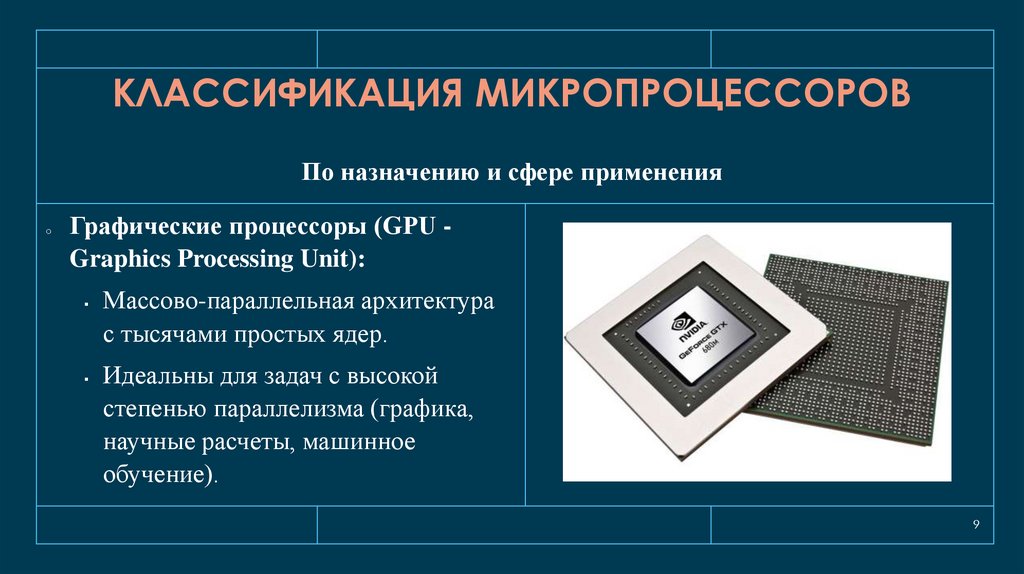

o

Графические процессоры (GPU Graphics Processing Unit):

Массово-параллельная архитектура

с тысячами простых ядер.

Идеальны для задач с высокой

степенью параллелизма (графика,

научные расчеты, машинное

обучение).

9

10. Типовая структура микропроцессора. Архитектурные подходы

ТИПОВАЯ СТРУКТУРА МИКРОПРОЦЕССОРА.АРХИТЕКТУРНЫЕ ПОДХОДЫ

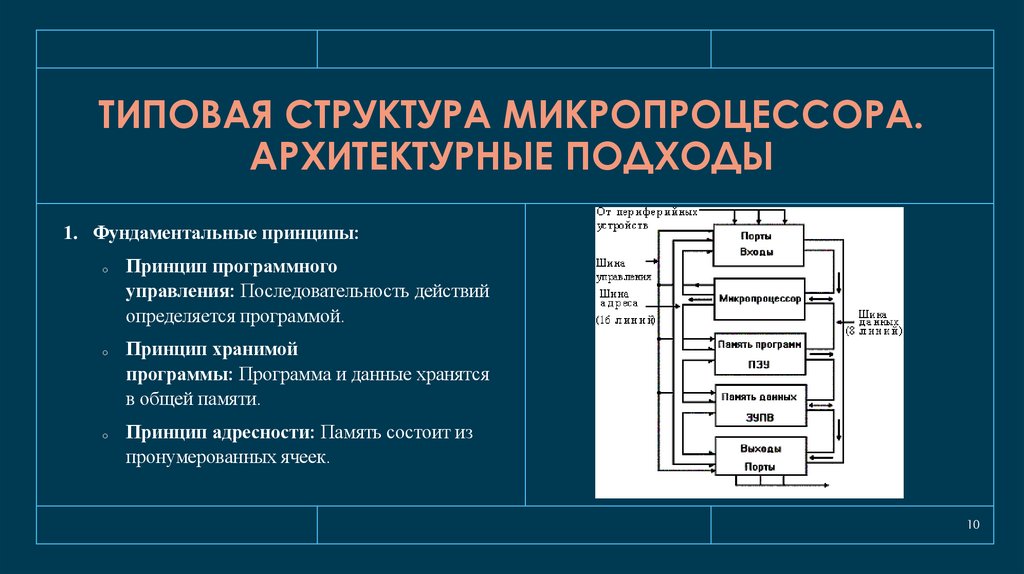

1. Фундаментальные принципы:

o

o

o

Принцип программного

управления: Последовательность действий

определяется программой.

Принцип хранимой

программы: Программа и данные хранятся

в общей памяти.

Принцип адресности: Память состоит из

пронумерованных ячеек.

10

11. Типовая структура микропроцессора. Архитектурные подходы

ТИПОВАЯ СТРУКТУРА МИКРОПРОЦЕССОРА.АРХИТЕКТУРНЫЕ ПОДХОДЫ

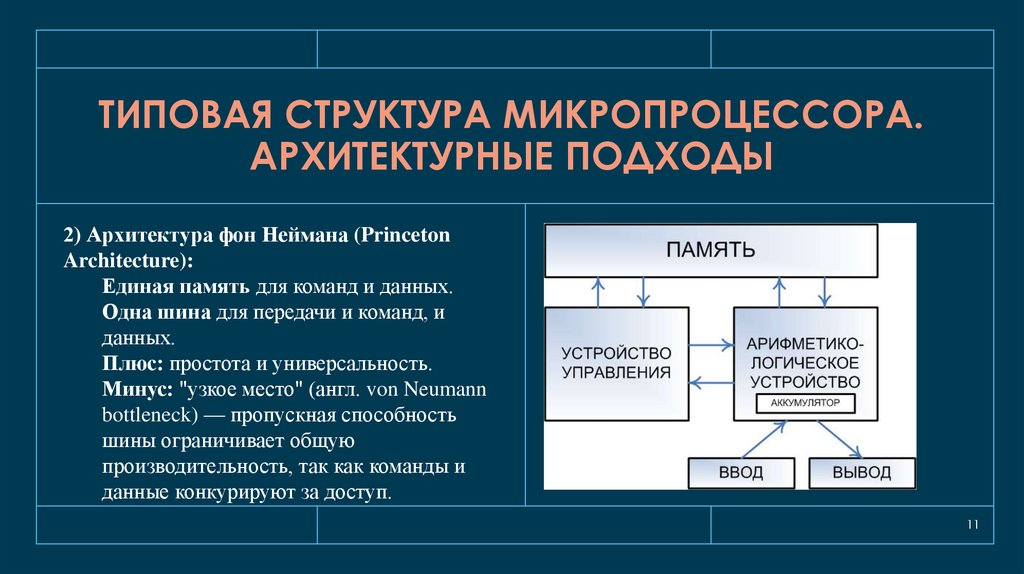

2) Архитектура фон Неймана (Princeton

Architecture):

Единая память для команд и данных.

Одна шина для передачи и команд, и

данных.

Плюс: простота и универсальность.

Минус: "узкое место" (англ. von Neumann

bottleneck) — пропускная способность

шины ограничивает общую

производительность, так как команды и

данные конкурируют за доступ.

11

12. Типовая структура микропроцессора. Архитектурные подходы

ТИПОВАЯ СТРУКТУРА МИКРОПРОЦЕССОРА.АРХИТЕКТУРНЫЕ ПОДХОДЫ

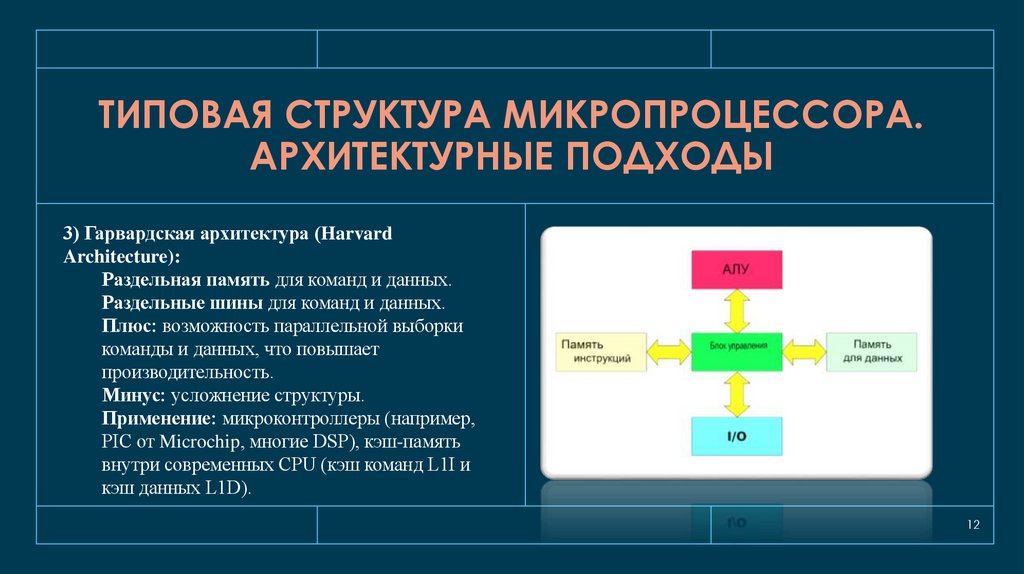

3) Гарвардская архитектура (Harvard

Architecture):

Раздельная память для команд и данных.

Раздельные шины для команд и данных.

Плюс: возможность параллельной выборки

команды и данных, что повышает

производительность.

Минус: усложнение структуры.

Применение: микроконтроллеры (например,

PIC от Microchip, многие DSP), кэш-память

внутри современных CPU (кэш команд L1I и

кэш данных L1D).

12

13. Детальный разбор структуры ядра МП

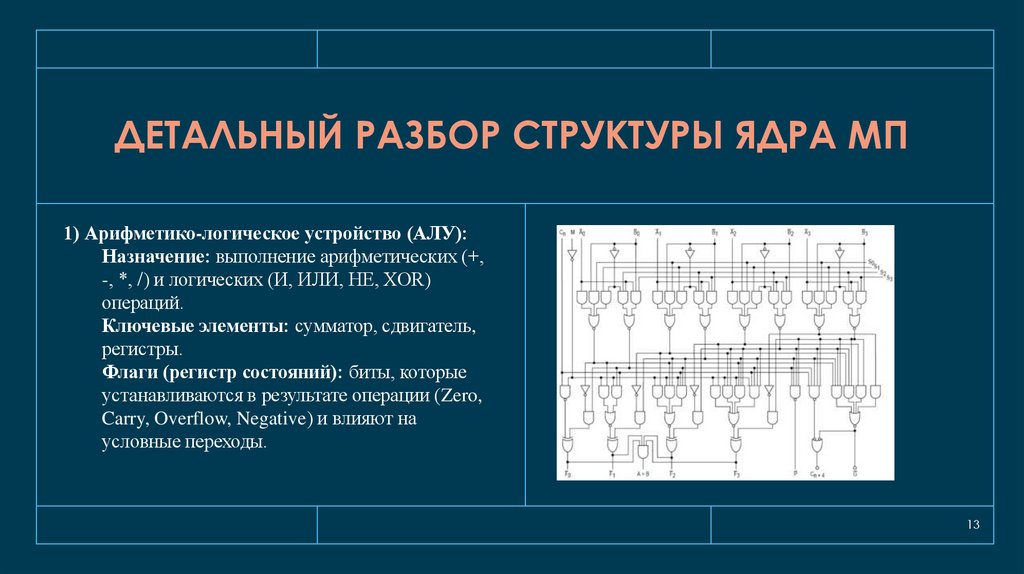

ДЕТАЛЬНЫЙ РАЗБОР СТРУКТУРЫ ЯДРА МП1) Арифметико-логическое устройство (АЛУ):

Назначение: выполнение арифметических (+,

-, *, /) и логических (И, ИЛИ, НЕ, XOR)

операций.

Ключевые элементы: сумматор, сдвигатель,

регистры.

Флаги (регистр состояний): биты, которые

устанавливаются в результате операции (Zero,

Carry, Overflow, Negative) и влияют на

условные переходы.

13

14. Детальный разбор структуры ядра МП

ДЕТАЛЬНЫЙ РАЗБОР СТРУКТУРЫ ЯДРА МП2) Регистровая память (РОН - Регистры Общего

Назначения):

Назначение: сверхбыстрая память

небольшого объема, расположенная внутри

ядра, для временного хранения данных и

адресов, с которыми работает АЛУ.

Скорость: доступ к регистрам в сотни раз

быстрее, чем к оперативной памяти.

Разрядность: определяет "битность"

процессора (8, 16, 32, 64 бита).

14

15. Детальный разбор структуры ядра МП

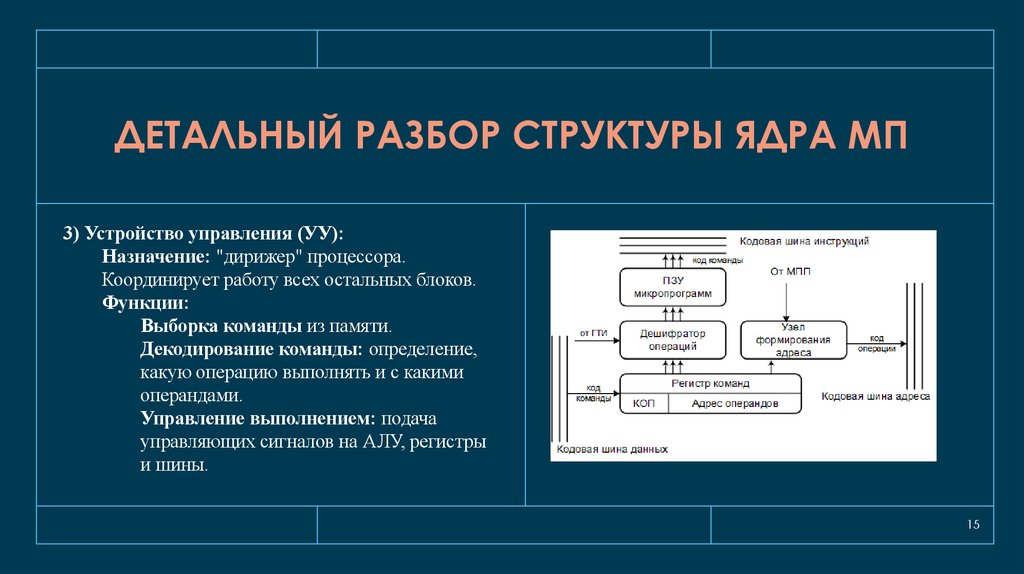

ДЕТАЛЬНЫЙ РАЗБОР СТРУКТУРЫ ЯДРА МП3) Устройство управления (УУ):

Назначение: "дирижер" процессора.

Координирует работу всех остальных блоков.

Функции:

Выборка команды из памяти.

Декодирование команды: определение,

какую операцию выполнять и с какими

операндами.

Управление выполнением: подача

управляющих сигналов на АЛУ, регистры

и шины.

15

16. Детальный разбор структуры ядра МП

ДЕТАЛЬНЫЙ РАЗБОР СТРУКТУРЫ ЯДРА МП4) Счетчик команд (Program Counter - PC):

Специальный регистр, который хранит адрес

следующей команды для выполнения.

5) Конвейерная обработка команд (Instruction

Pipeline):

Идея: разделение выполнения команды на этапы

(Fetch, Decode, Execute, Memory, Writeback) и их

совмещение во времени.

Аналогия: конвейер на заводе. Пока одна команда

выполняется, другая декодируется, а третья —

выбирается.

Цель: увеличение производительности (идеально —

одна команда за такт).

16

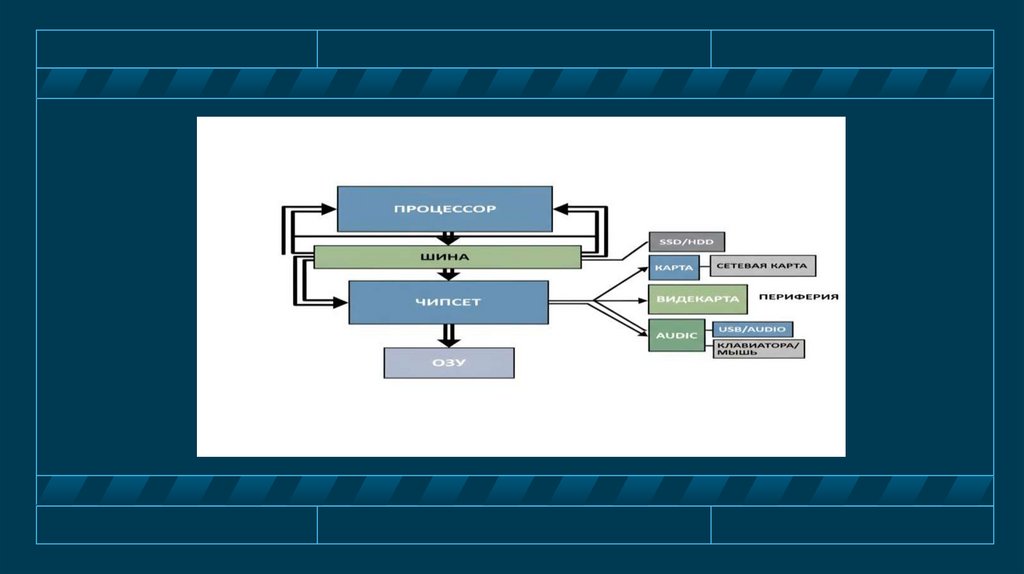

17. Системный уровень: шины, память, периферия

СИСТЕМНЫЙ УРОВЕНЬ: ШИНЫ, ПАМЯТЬ, ПЕРИФЕРИЯПроцессор не работает в вакууме. Он часть системы.

1) Системная шина (FSB - Front-Side Bus, в современных

системах - DMI, HyperTransport, QPI):

o

Назначение: связь процессора с чипсетом (контроллером

памяти и периферии).

o

Составляющие:

Шина адреса: определяет, к какой ячейке памяти или

устройству идет обращение.

Шина данных: по ней передаются сами данные или

команды.

Шина управления: передает управляющие сигналы

(чтение/запись, готовность, прерывание).

17

18. Системный уровень: шины, память, периферия

СИСТЕМНЫЙ УРОВЕНЬ: ШИНЫ, ПАМЯТЬ, ПЕРИФЕРИЯ2) Иерархия памяти:

Регистры (в ядре) -> Кэш-память L1/L2/L3 (на

кристалле/в процессоре) -> ОЗУ (RAM) (на

материнской плате) -> Внешняя

память (SSD/HDD).

Принцип: чем ближе память к ядру, тем она

быстрее и меньше по объему.

Кэш-память: быстрая буферная память,

хранящая копии часто используемых данных из

ОЗУ для ускорения доступа.

3) Подсистема прерываний (Interrupt Controller):

o

o

Назначение: позволяет процессору реагировать

на внешние события в реальном времени

(нажатие клавиши, приход пакета по сети).

Принцип: устройство посылает сигнал

прерывания -> процессор завершает текущую

команду -> сохраняет контекст -> переходит к

выполнению программы-обработчика

прерывания -> по завершении восстанавливает

контекст и продолжает работу.

18

19.

20. Вопросы

ВОПРОСЫ1. В чем главное отличие CISC от RISC?

2. Зачем нужны многоядерные процессоры?

3. Что такое микроконтроллер?

4. Главная задача АЛУ

5. Для чего нужны регистры?

6. Что делает устройство управления?

7. Что такое кэш-память и зачем она нужна?

20

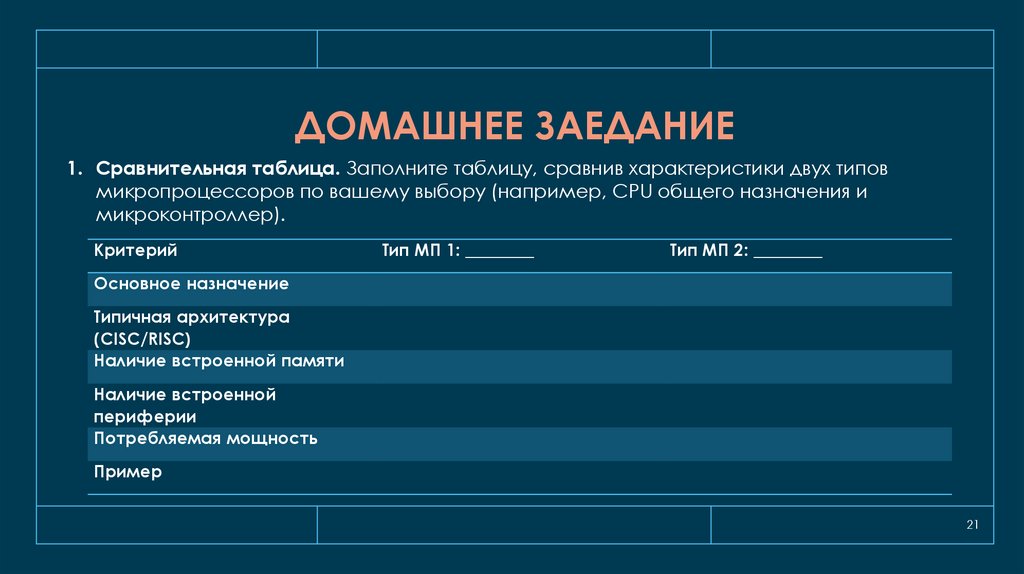

21. Домашнее заедание

ДОМАШНЕЕ ЗАЕДАНИЕ1. Сравнительная таблица. Заполните таблицу, сравнив характеристики двух типов

микропроцессоров по вашему выбору (например, CPU общего назначения и

микроконтроллер).

Критерий

Тип МП 1: ________

Тип МП 2: ________

Основное назначение

Типичная архитектура

(CISC/RISC)

Наличие встроенной памяти

Наличие встроенной

периферии

Потребляемая мощность

Пример

21

electronics

electronics